Module 5 AVR ATMega 32 Instructions Set Architecture

- Slides: 52

Module 5 AVR ATMega 32 Instructions Set Architecture

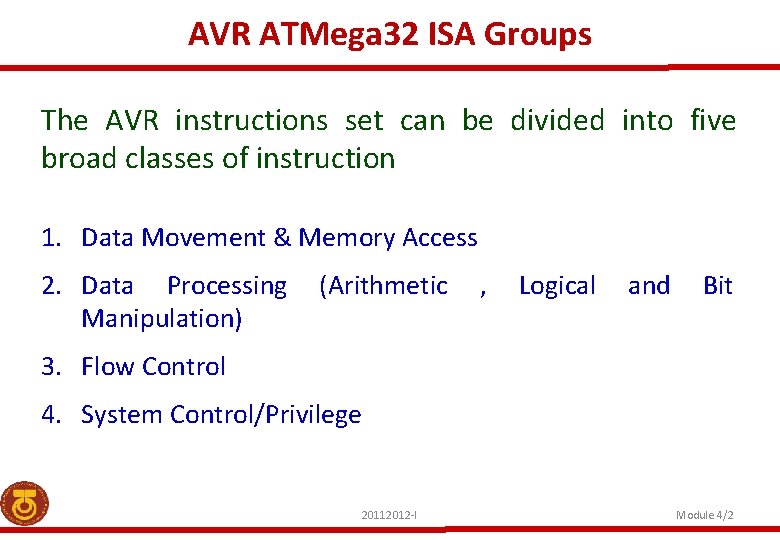

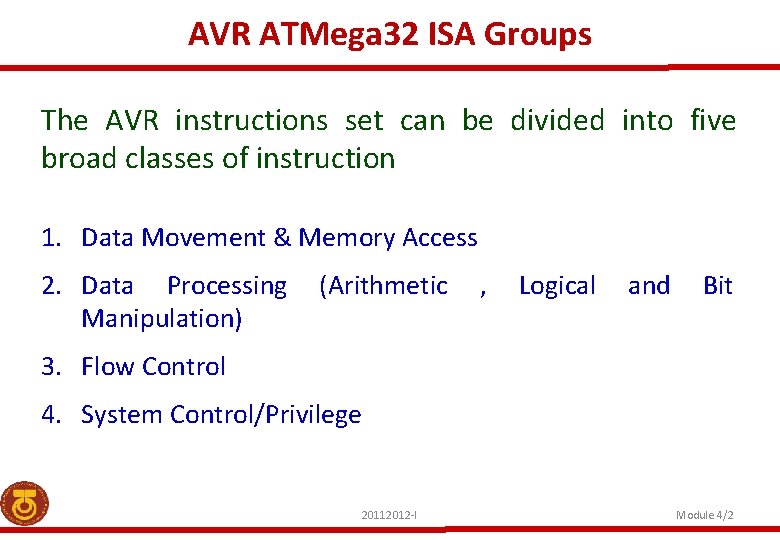

AVR ATMega 32 ISA Groups The AVR instructions set can be divided into five broad classes of instruction 1. Data Movement & Memory Access 2. Data Processing Manipulation) (Arithmetic , Logical and Bit 3. Flow Control 4. System Control/Privilege 20112012 -I Module 4/2

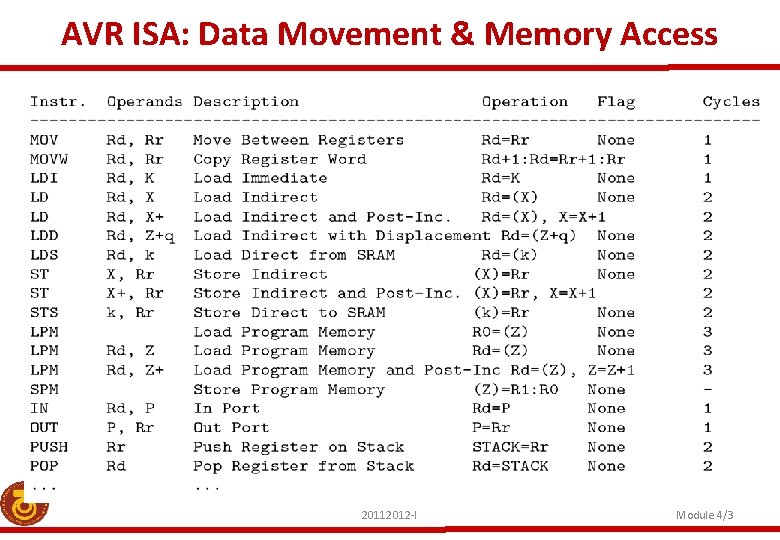

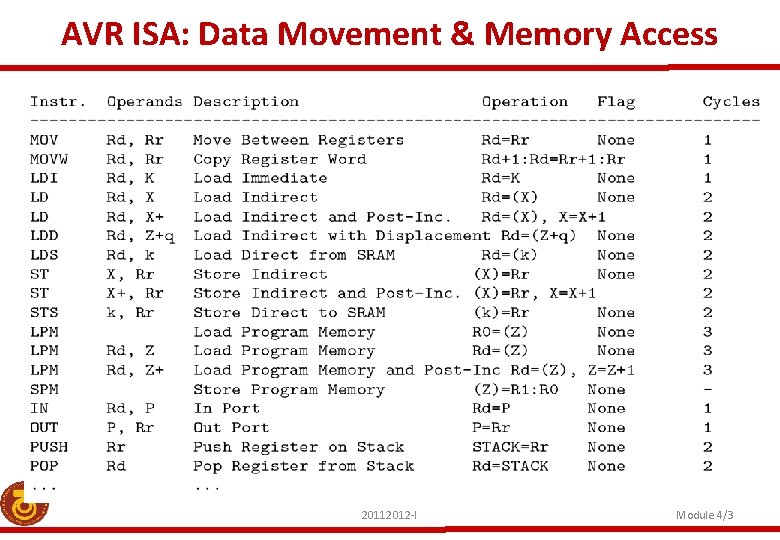

AVR ISA: Data Movement & Memory Access 20112012 -I Module 4/3

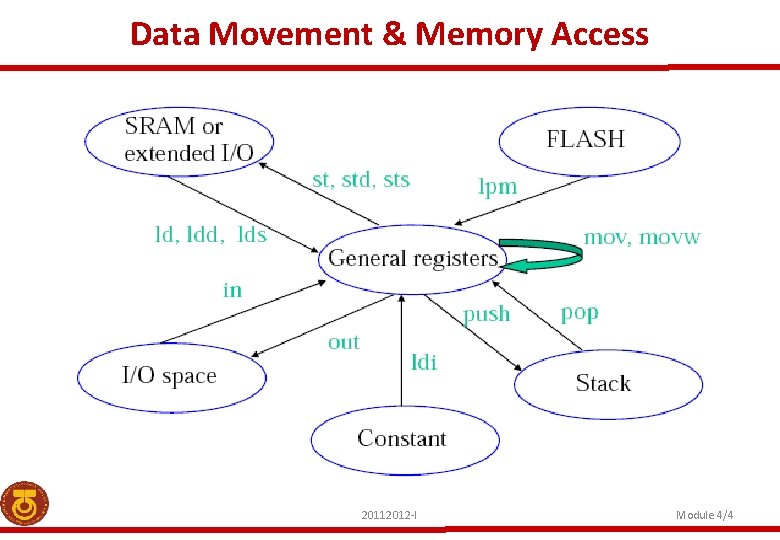

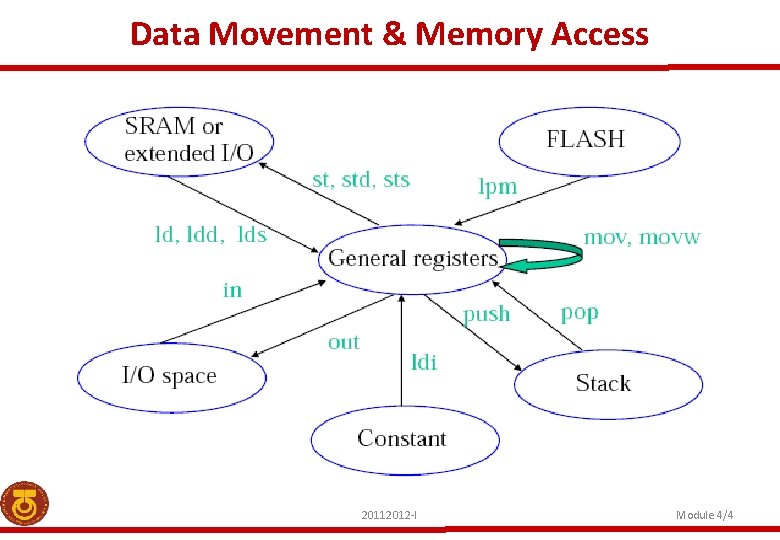

Data Movement & Memory Access 20112012 -I Module 4/4

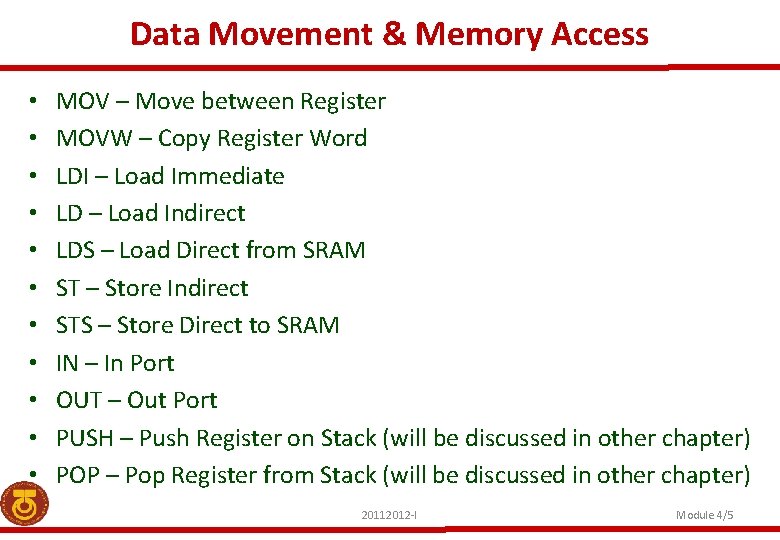

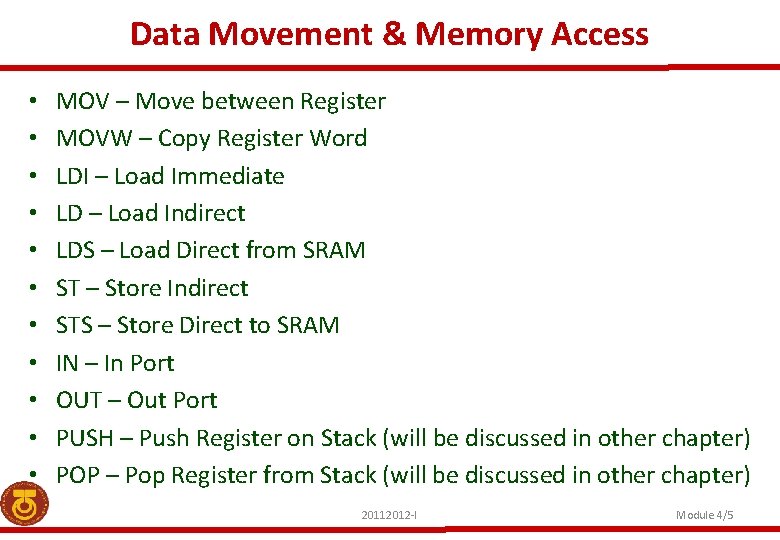

Data Movement & Memory Access • • • MOV – Move between Register MOVW – Copy Register Word LDI – Load Immediate LD – Load Indirect LDS – Load Direct from SRAM ST – Store Indirect STS – Store Direct to SRAM IN – In Port OUT – Out Port PUSH – Push Register on Stack (will be discussed in other chapter) POP – Pop Register from Stack (will be discussed in other chapter) 20112012 -I Module 4/5

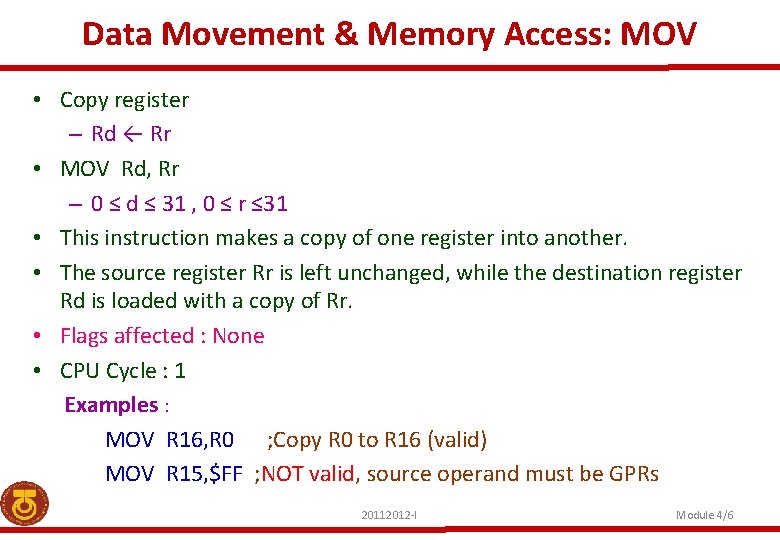

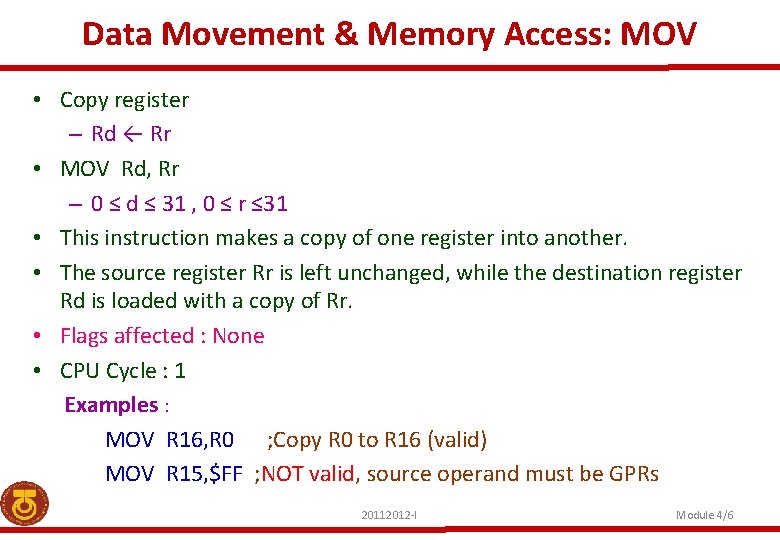

Data Movement & Memory Access: MOV • Copy register – Rd ← Rr • MOV Rd, Rr – 0 ≤ d ≤ 31 , 0 ≤ r ≤ 31 • This instruction makes a copy of one register into another. • The source register Rr is left unchanged, while the destination register Rd is loaded with a copy of Rr. • Flags affected : None • CPU Cycle : 1 Examples : MOV R 16, R 0 ; Copy R 0 to R 16 (valid) MOV R 15, $FF ; NOT valid, source operand must be GPRs 20112012 -I Module 4/6

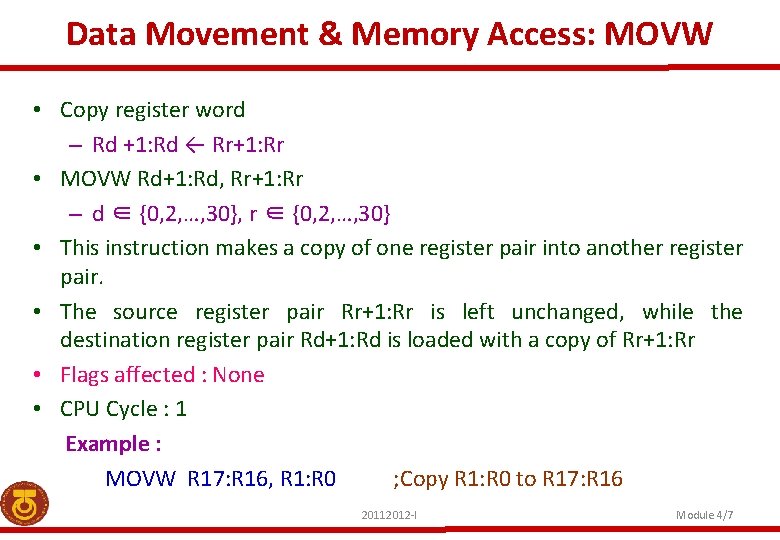

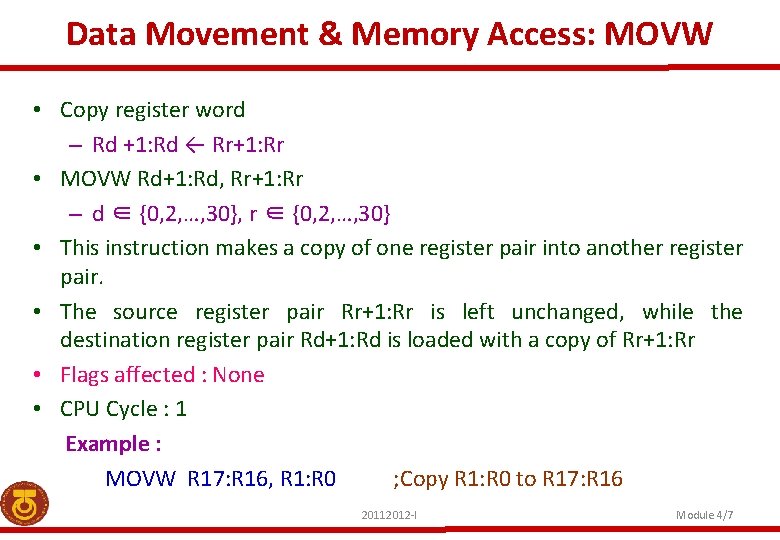

Data Movement & Memory Access: MOVW • Copy register word – Rd +1: Rd ← Rr+1: Rr • MOVW Rd+1: Rd, Rr+1: Rr – d ∈ {0, 2, …, 30}, r ∈ {0, 2, …, 30} • This instruction makes a copy of one register pair into another register pair. • The source register pair Rr+1: Rr is left unchanged, while the destination register pair Rd+1: Rd is loaded with a copy of Rr+1: Rr • Flags affected : None • CPU Cycle : 1 Example : MOVW R 17: R 16, R 1: R 0 ; Copy R 1: R 0 to R 17: R 16 20112012 -I Module 4/7

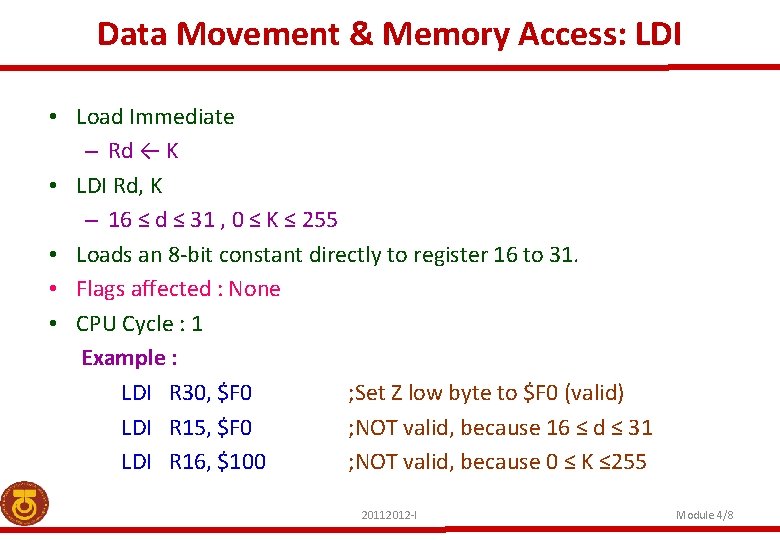

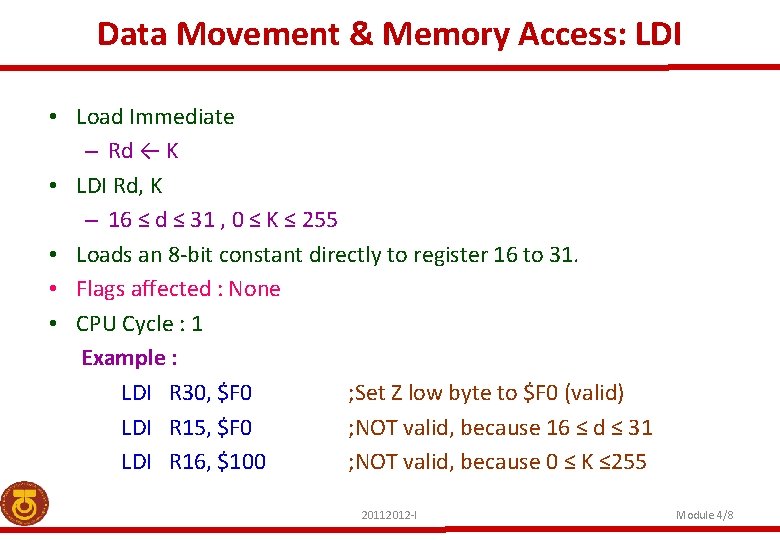

Data Movement & Memory Access: LDI • Load Immediate – Rd ← K • LDI Rd, K – 16 ≤ d ≤ 31 , 0 ≤ K ≤ 255 • Loads an 8 -bit constant directly to register 16 to 31. • Flags affected : None • CPU Cycle : 1 Example : LDI R 30, $F 0 ; Set Z low byte to $F 0 (valid) LDI R 15, $F 0 ; NOT valid, because 16 ≤ d ≤ 31 LDI R 16, $100 ; NOT valid, because 0 ≤ K ≤ 255 20112012 -I Module 4/8

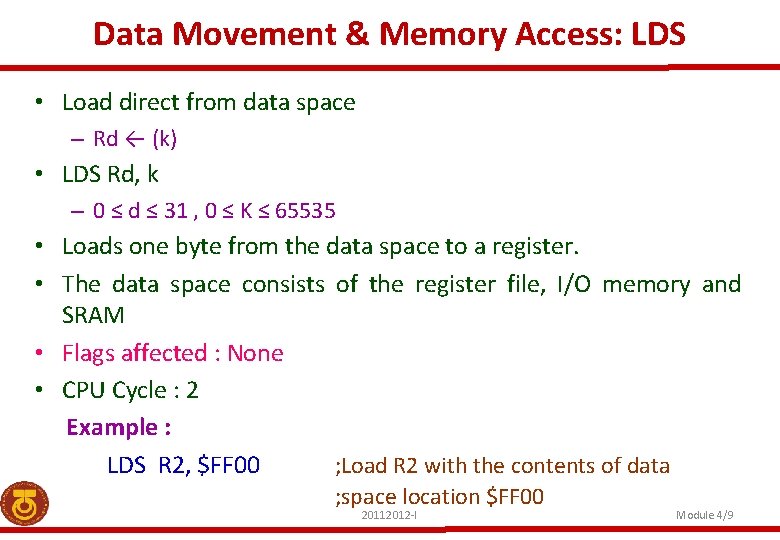

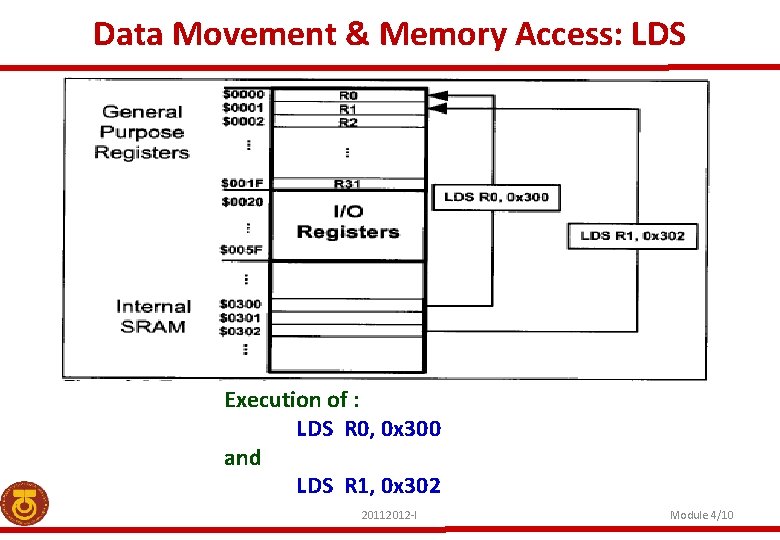

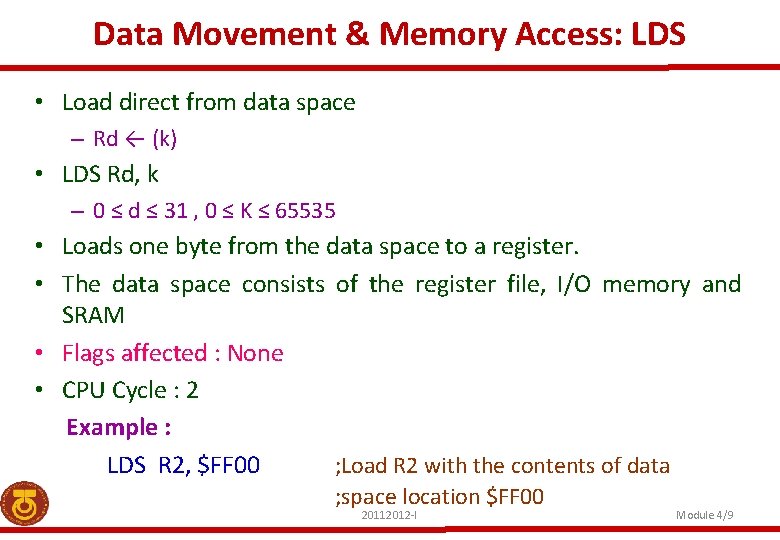

Data Movement & Memory Access: LDS • Load direct from data space – Rd ← (k) • LDS Rd, k – 0 ≤ d ≤ 31 , 0 ≤ K ≤ 65535 • Loads one byte from the data space to a register. • The data space consists of the register file, I/O memory and SRAM • Flags affected : None • CPU Cycle : 2 Example : LDS R 2, $FF 00 ; Load R 2 with the contents of data ; space location $FF 00 20112012 -I Module 4/9

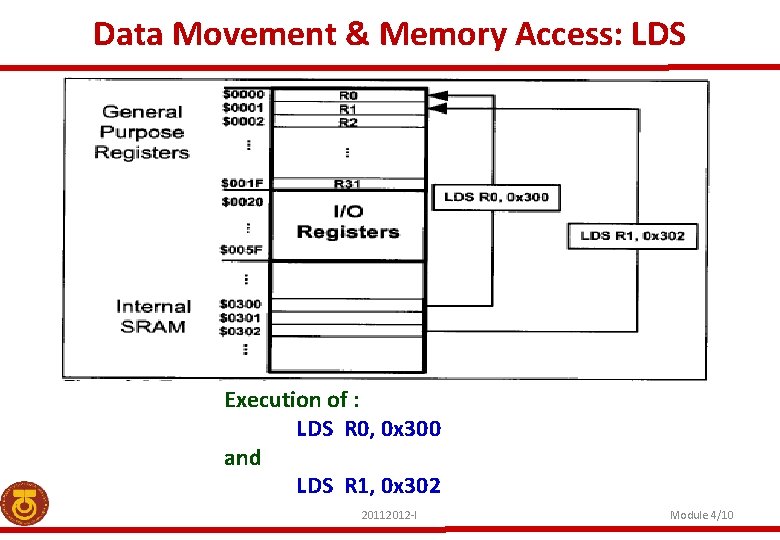

Data Movement & Memory Access: LDS Execution of : LDS R 0, 0 x 300 and LDS R 1, 0 x 302 20112012 -I Module 4/10

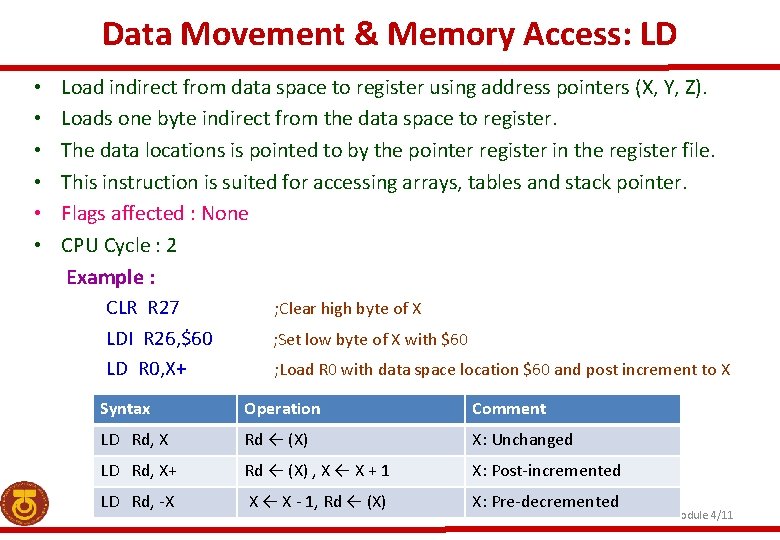

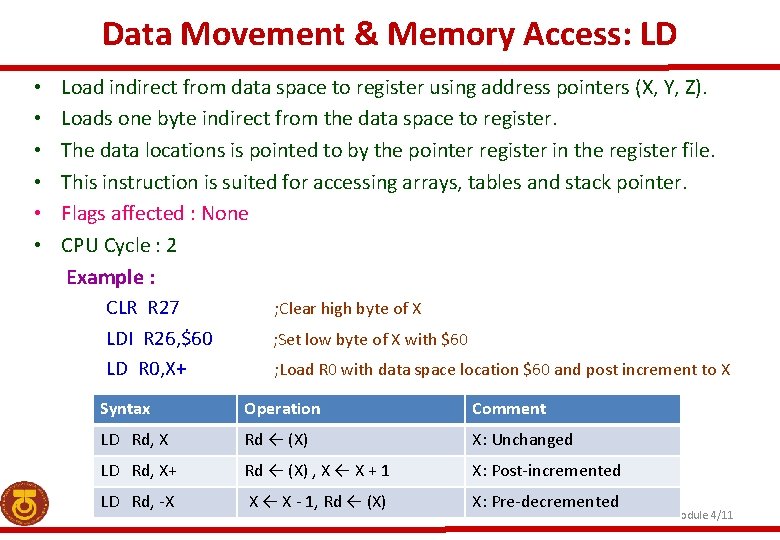

Data Movement & Memory Access: LD • • • Load indirect from data space to register using address pointers (X, Y, Z). Loads one byte indirect from the data space to register. The data locations is pointed to by the pointer register in the register file. This instruction is suited for accessing arrays, tables and stack pointer. Flags affected : None CPU Cycle : 2 Example : CLR R 27 ; Clear high byte of X LDI R 26, $60 ; Set low byte of X with $60 LD R 0, X+ ; Load R 0 with data space location $60 and post increment to X Syntax Operation Comment LD Rd, X Rd ← (X) X: Unchanged LD Rd, X+ Rd ← (X) , X ← X + 1 X: Post-incremented LD Rd, -X X ← X - 1, Rd ← (X) X: Pre-decremented 20112012 -I Module 4/11

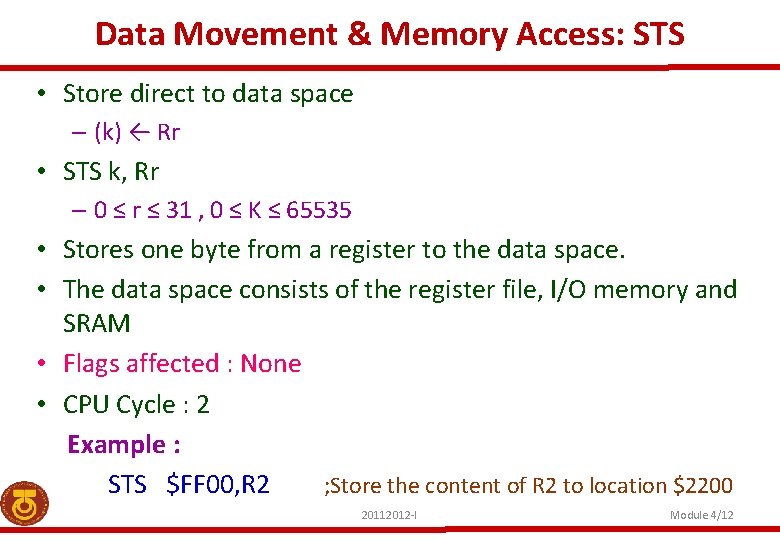

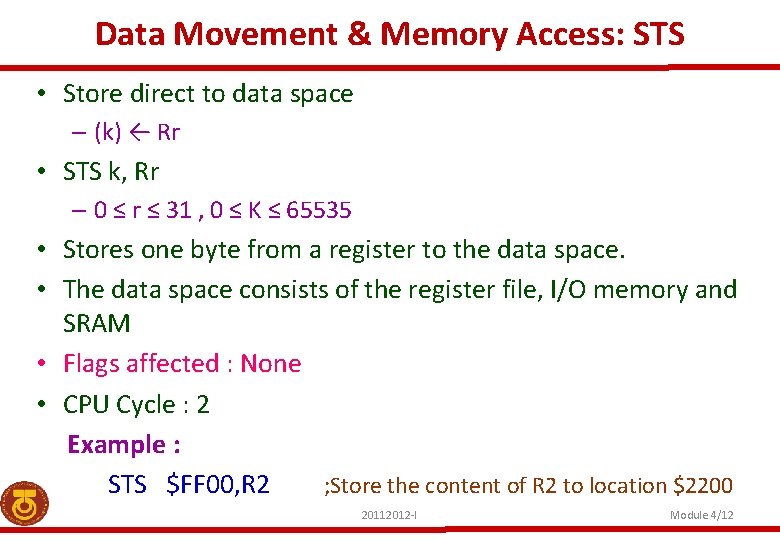

Data Movement & Memory Access: STS • Store direct to data space – (k) ← Rr • STS k, Rr – 0 ≤ r ≤ 31 , 0 ≤ K ≤ 65535 • Stores one byte from a register to the data space. • The data space consists of the register file, I/O memory and SRAM • Flags affected : None • CPU Cycle : 2 Example : STS $FF 00, R 2 ; Store the content of R 2 to location $2200 20112012 -I Module 4/12

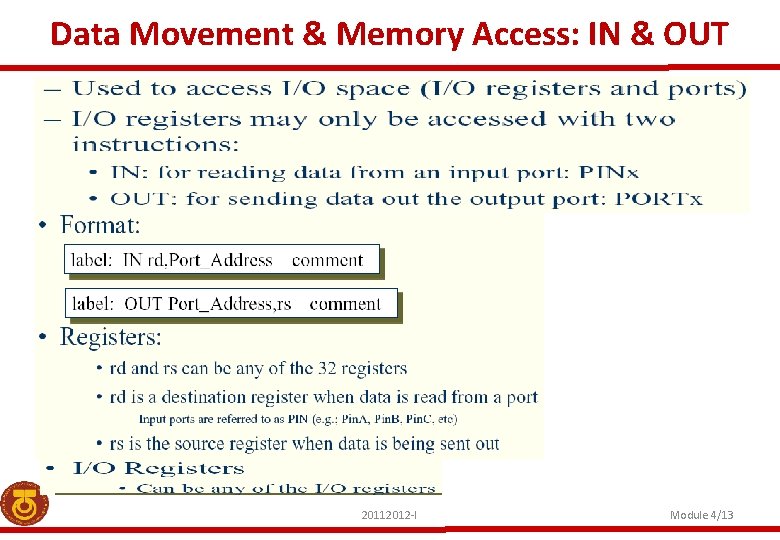

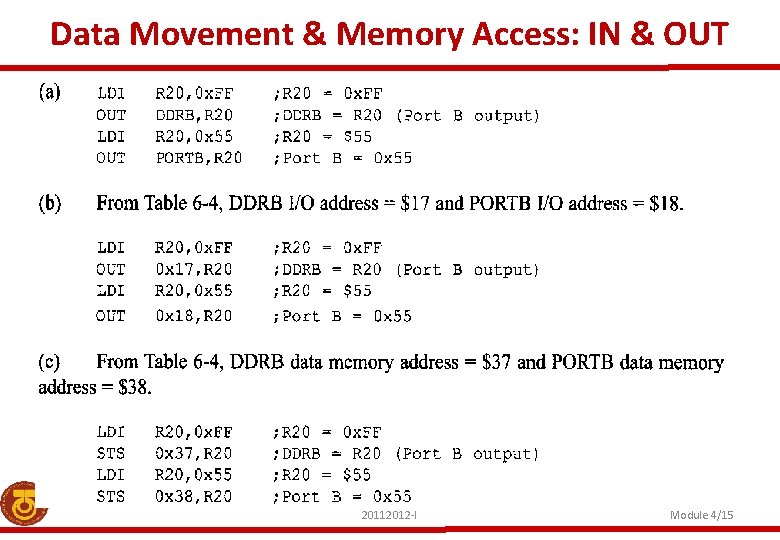

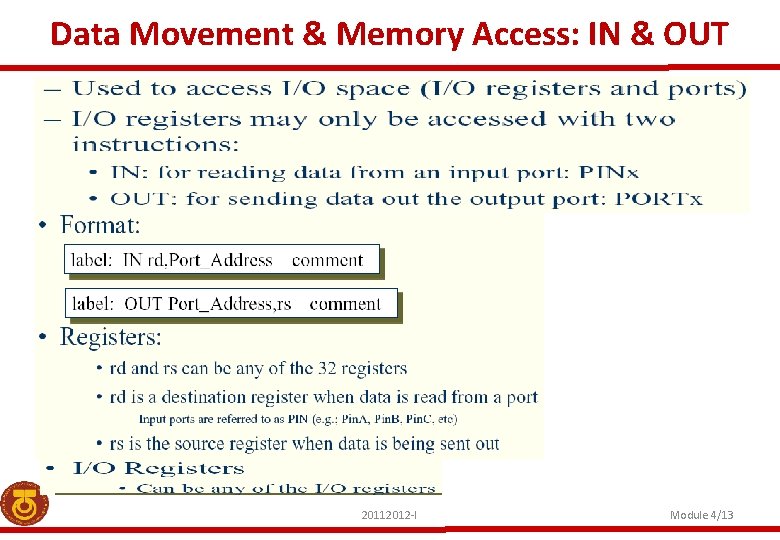

Data Movement & Memory Access: IN & OUT 20112012 -I Module 4/13

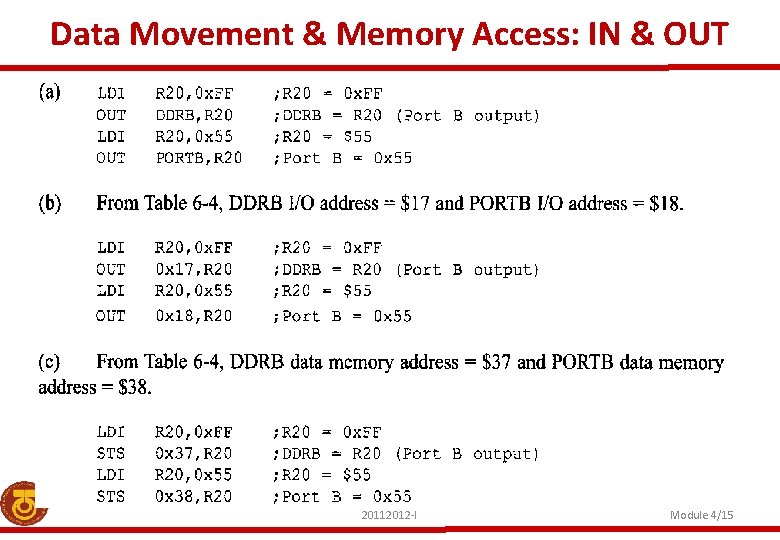

Data Movement & Memory Access: IN & OUT 20112012 -I Module 4/14

Data Movement & Memory Access: IN & OUT 20112012 -I Module 4/15

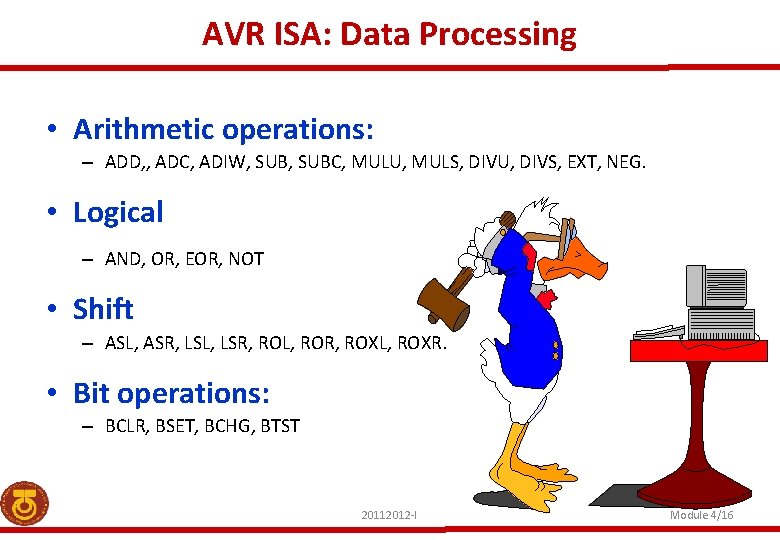

AVR ISA: Data Processing • Arithmetic operations: – ADD, , ADC, ADIW, SUBC, MULU, MULS, DIVU, DIVS, EXT, NEG. • Logical – AND, OR, EOR, NOT • Shift – ASL, ASR, LSL, LSR, ROL, ROR, ROXL, ROXR. • Bit operations: – BCLR, BSET, BCHG, BTST 20112012 -I Module 4/16

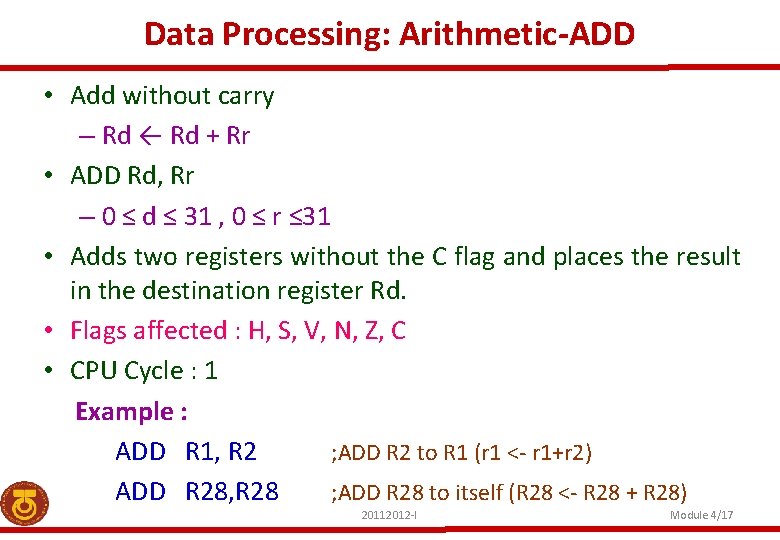

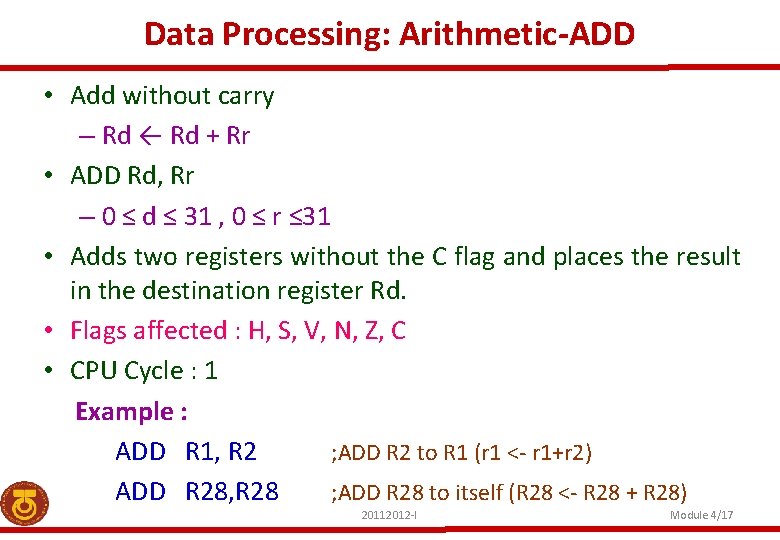

Data Processing: Arithmetic-ADD • Add without carry – Rd ← Rd + Rr • ADD Rd, Rr – 0 ≤ d ≤ 31 , 0 ≤ r ≤ 31 • Adds two registers without the C flag and places the result in the destination register Rd. • Flags affected : H, S, V, N, Z, C • CPU Cycle : 1 Example : ADD R 1, R 2 ; ADD R 2 to R 1 (r 1 <- r 1+r 2) ADD R 28, R 28 ; ADD R 28 to itself (R 28 <- R 28 + R 28) 20112012 -I Module 4/17

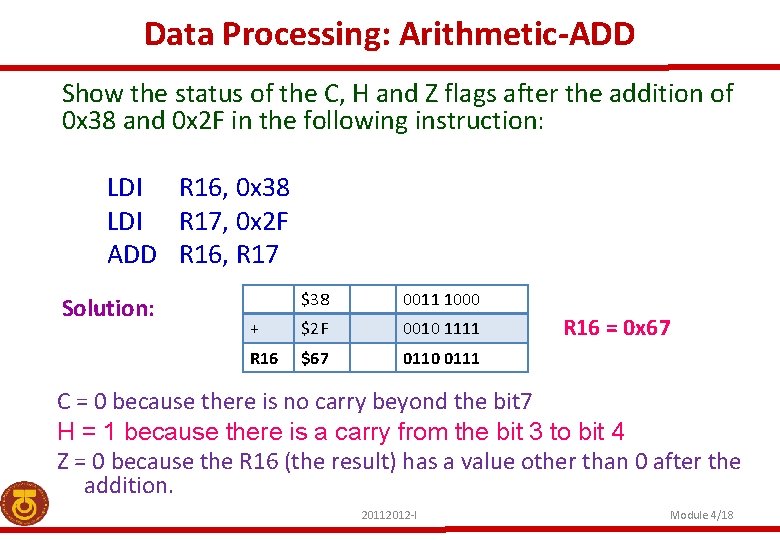

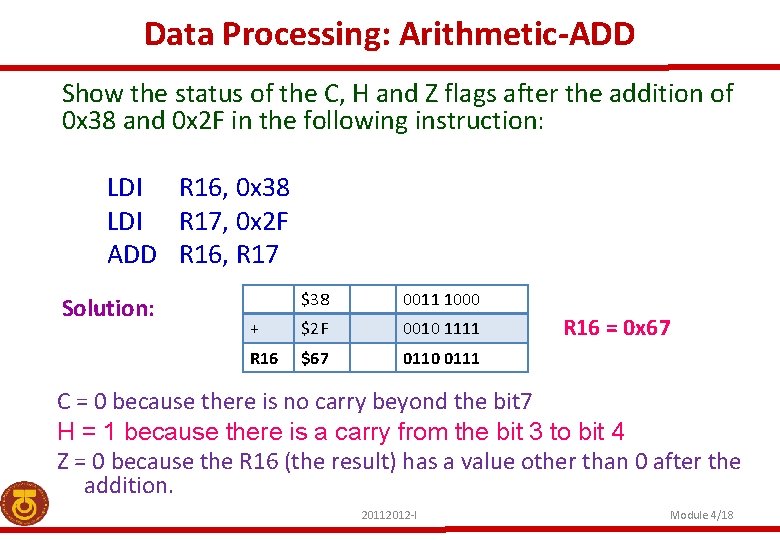

Data Processing: Arithmetic-ADD Show the status of the C, H and Z flags after the addition of 0 x 38 and 0 x 2 F in the following instruction: LDI R 16, 0 x 38 LDI R 17, 0 x 2 F ADD R 16, R 17 Solution: $38 0011 1000 + $2 F 0010 1111 R 16 $67 0110 0111 R 16 = 0 x 67 C = 0 because there is no carry beyond the bit 7 H = 1 because there is a carry from the bit 3 to bit 4 Z = 0 because the R 16 (the result) has a value other than 0 after the addition. 20112012 -I Module 4/18

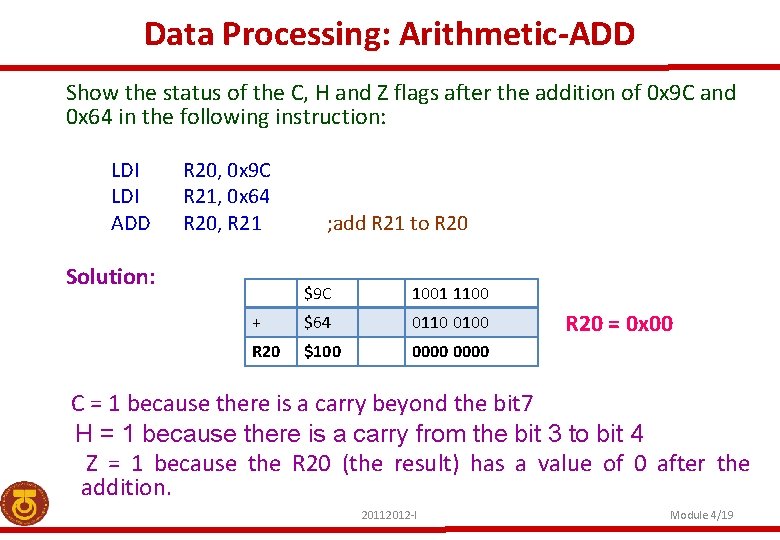

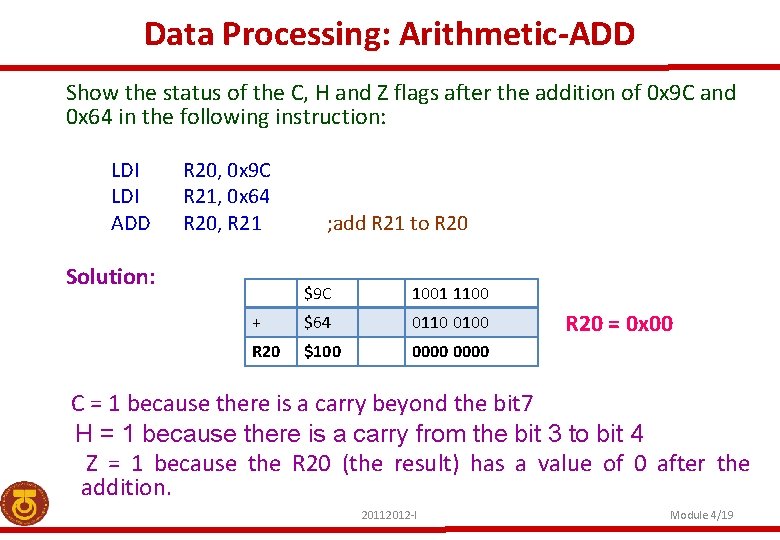

Data Processing: Arithmetic-ADD Show the status of the C, H and Z flags after the addition of 0 x 9 C and 0 x 64 in the following instruction: LDI ADD R 20, 0 x 9 C R 21, 0 x 64 R 20, R 21 Solution: ; add R 21 to R 20 $9 C 1001 1100 + $64 0110 0100 R 20 $100 0000 R 20 = 0 x 00 C = 1 because there is a carry beyond the bit 7 H = 1 because there is a carry from the bit 3 to bit 4 Z = 1 because the R 20 (the result) has a value of 0 after the addition. 20112012 -I Module 4/19

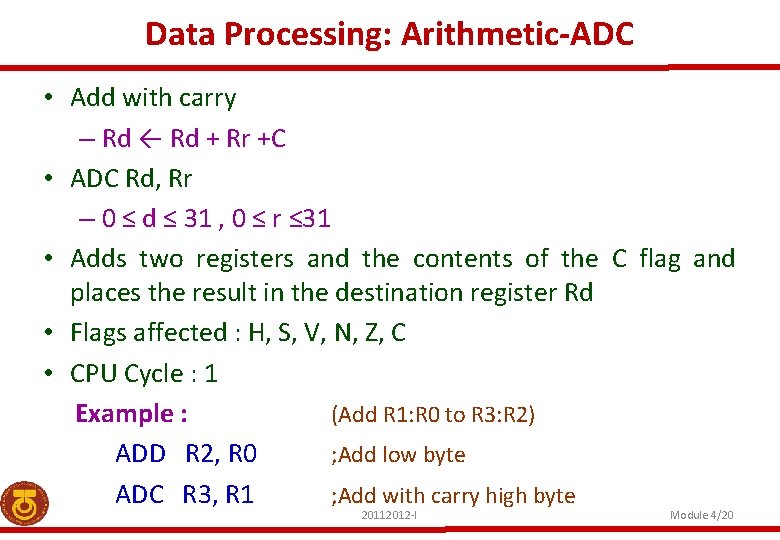

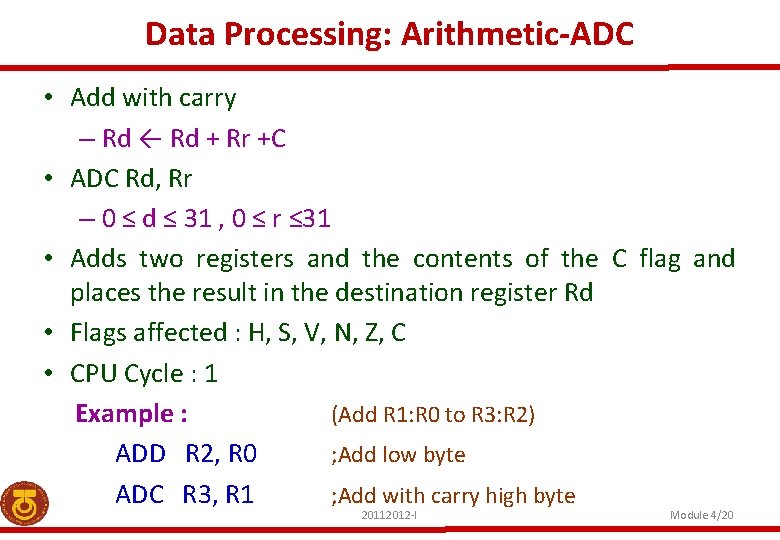

Data Processing: Arithmetic-ADC • Add with carry – Rd ← Rd + Rr +C • ADC Rd, Rr – 0 ≤ d ≤ 31 , 0 ≤ r ≤ 31 • Adds two registers and the contents of the C flag and places the result in the destination register Rd • Flags affected : H, S, V, N, Z, C • CPU Cycle : 1 Example : (Add R 1: R 0 to R 3: R 2) ADD R 2, R 0 ; Add low byte ADC R 3, R 1 ; Add with carry high byte 20112012 -I Module 4/20

Data Processing: Arithmetic-ADC Write a program to add two 16 -bit numbers. The numbers are $3 CE 7 and $3 B 8 D. Assume that R 1 = $8 D, R 2 = $3 B, R 3 = $E 7, and R 4 = $3 C. Place sum in R 3 and R 4; R 3 should have the lower byte Solution: ADD ADC R 3, R 1 R 4, R 2 Notice: Use ADD for lower byte and ADC for the higher byte 20112012 -I Module 4/21

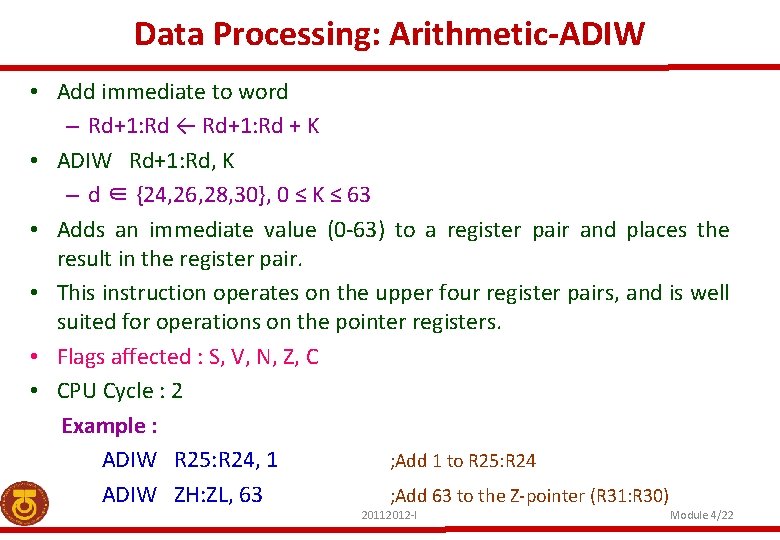

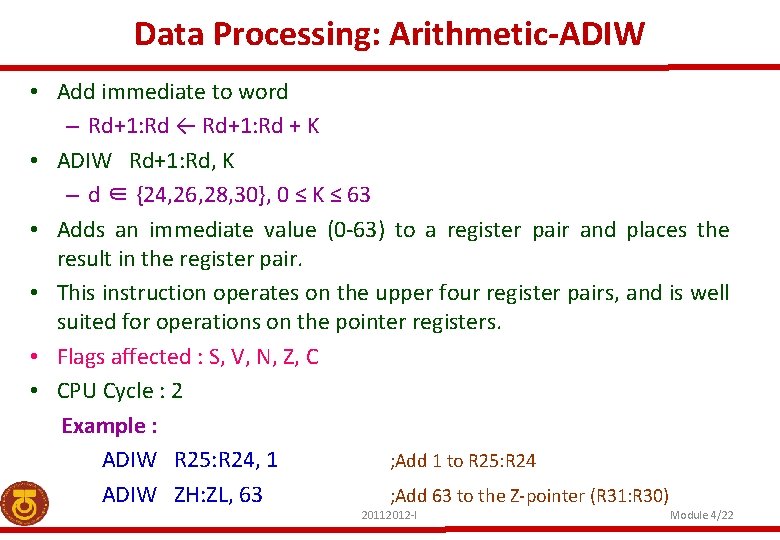

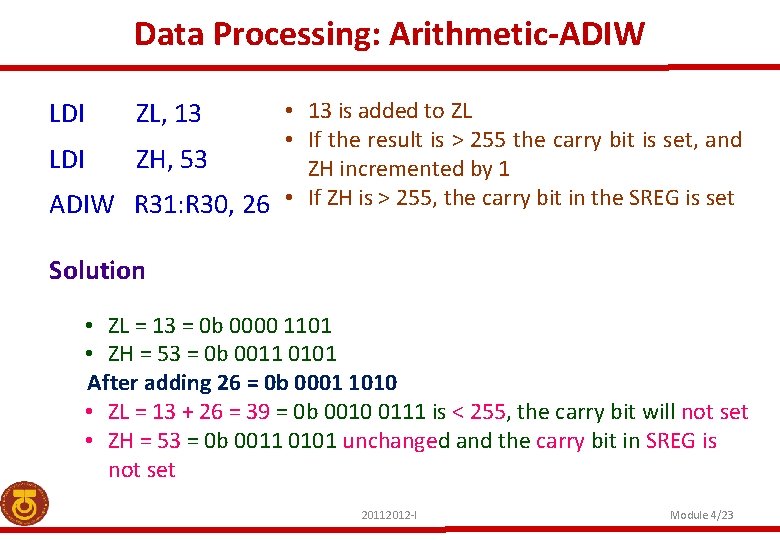

Data Processing: Arithmetic-ADIW • Add immediate to word – Rd+1: Rd ← Rd+1: Rd + K • ADIW Rd+1: Rd, K – d ∈ {24, 26, 28, 30}, 0 ≤ K ≤ 63 • Adds an immediate value (0 -63) to a register pair and places the result in the register pair. • This instruction operates on the upper four register pairs, and is well suited for operations on the pointer registers. • Flags affected : S, V, N, Z, C • CPU Cycle : 2 Example : ADIW R 25: R 24, 1 ; Add 1 to R 25: R 24 ADIW ZH: ZL, 63 ; Add 63 to the Z-pointer (R 31: R 30) 20112012 -I Module 4/22

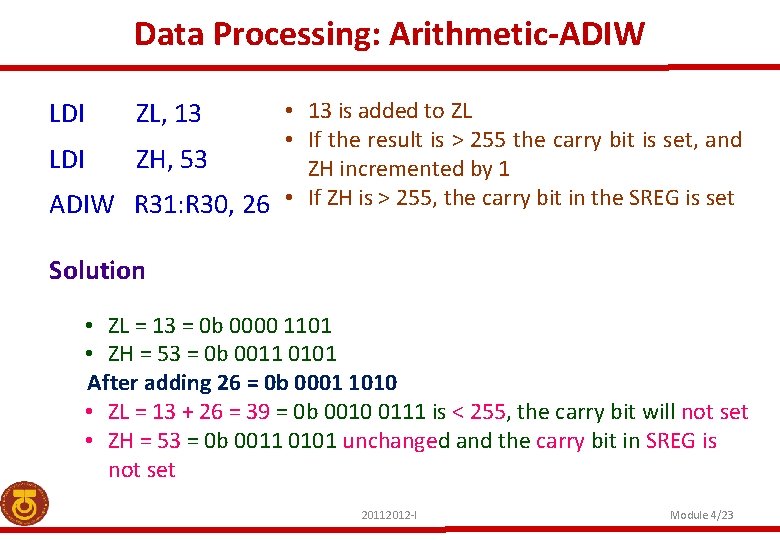

Data Processing: Arithmetic-ADIW LDI ZL, 13 • 13 is added to ZL • If the result is > 255 the carry bit is set, and LDI ZH, 53 ZH incremented by 1 ADIW R 31: R 30, 26 • If ZH is > 255, the carry bit in the SREG is set Solution • ZL = 13 = 0 b 0000 1101 • ZH = 53 = 0 b 0011 0101 After adding 26 = 0 b 0001 1010 • ZL = 13 + 26 = 39 = 0 b 0010 0111 is < 255, the carry bit will not set • ZH = 53 = 0 b 0011 0101 unchanged and the carry bit in SREG is not set 20112012 -I Module 4/23

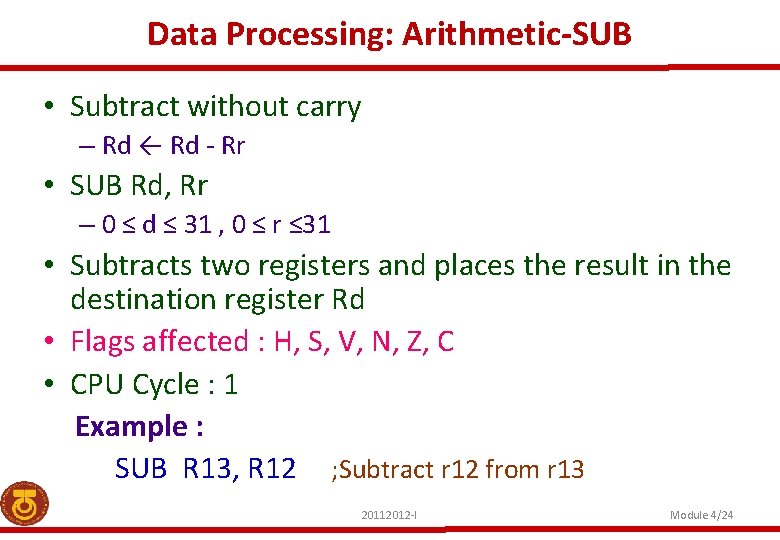

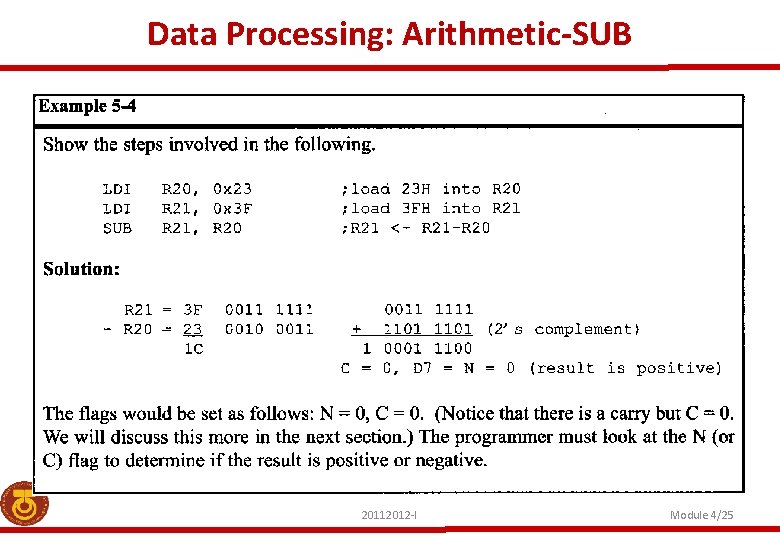

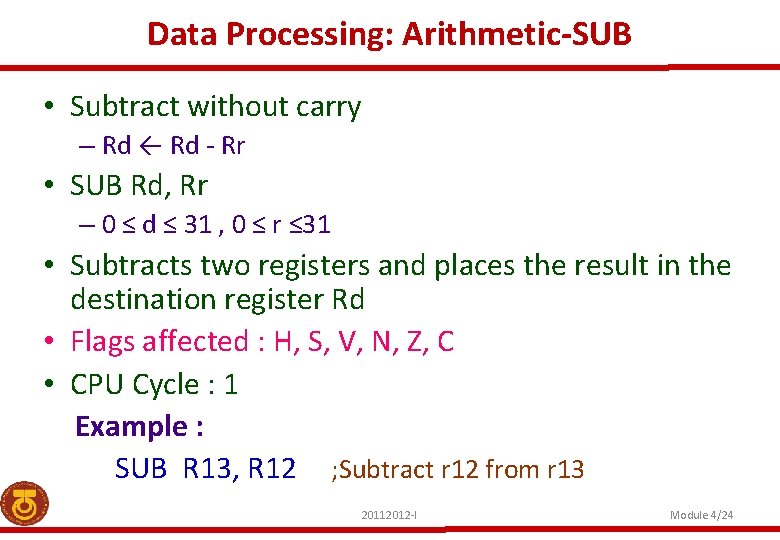

Data Processing: Arithmetic-SUB • Subtract without carry – Rd ← Rd - Rr • SUB Rd, Rr – 0 ≤ d ≤ 31 , 0 ≤ r ≤ 31 • Subtracts two registers and places the result in the destination register Rd • Flags affected : H, S, V, N, Z, C • CPU Cycle : 1 Example : SUB R 13, R 12 ; Subtract r 12 from r 13 20112012 -I Module 4/24

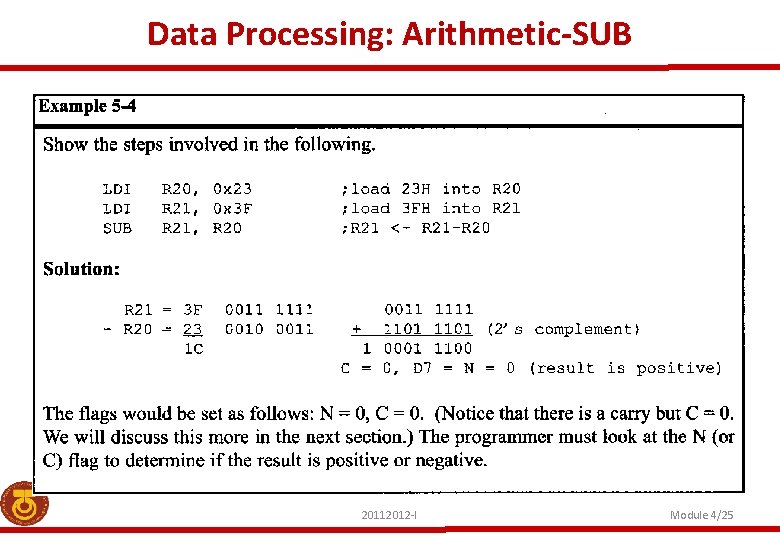

Data Processing: Arithmetic-SUB 20112012 -I Module 4/25

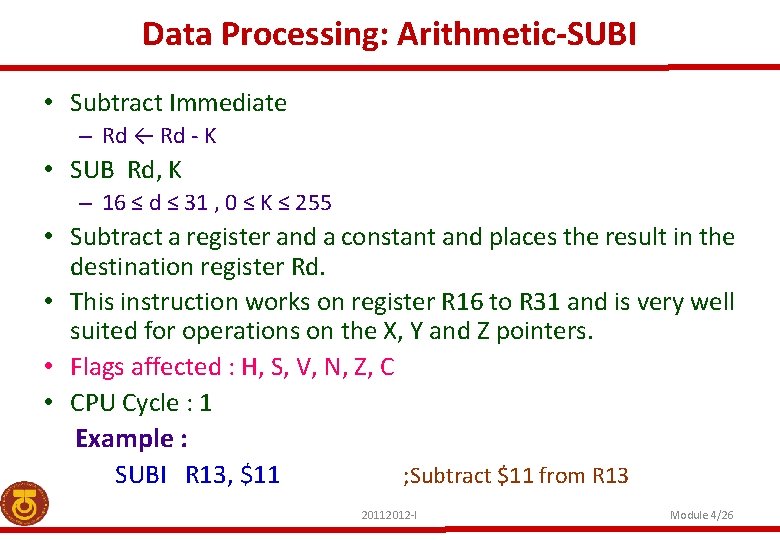

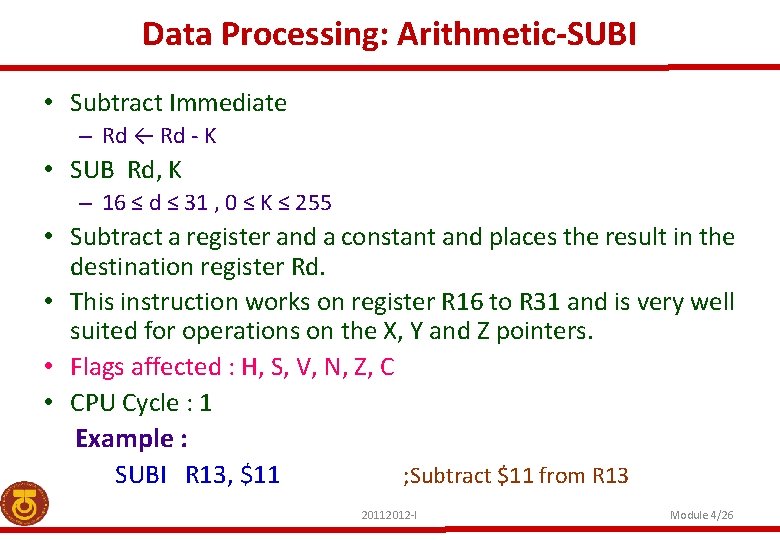

Data Processing: Arithmetic-SUBI • Subtract Immediate – Rd ← Rd - K • SUB Rd, K – 16 ≤ d ≤ 31 , 0 ≤ K ≤ 255 • Subtract a register and a constant and places the result in the destination register Rd. • This instruction works on register R 16 to R 31 and is very well suited for operations on the X, Y and Z pointers. • Flags affected : H, S, V, N, Z, C • CPU Cycle : 1 Example : SUBI R 13, $11 ; Subtract $11 from R 13 20112012 -I Module 4/26

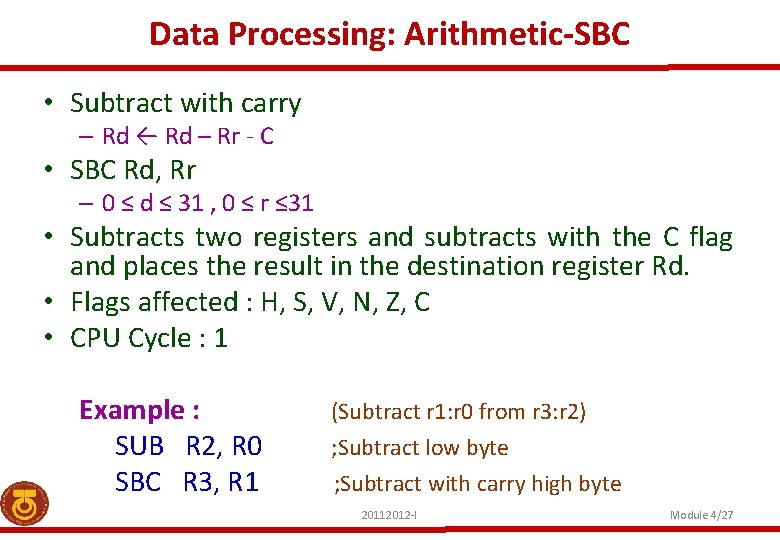

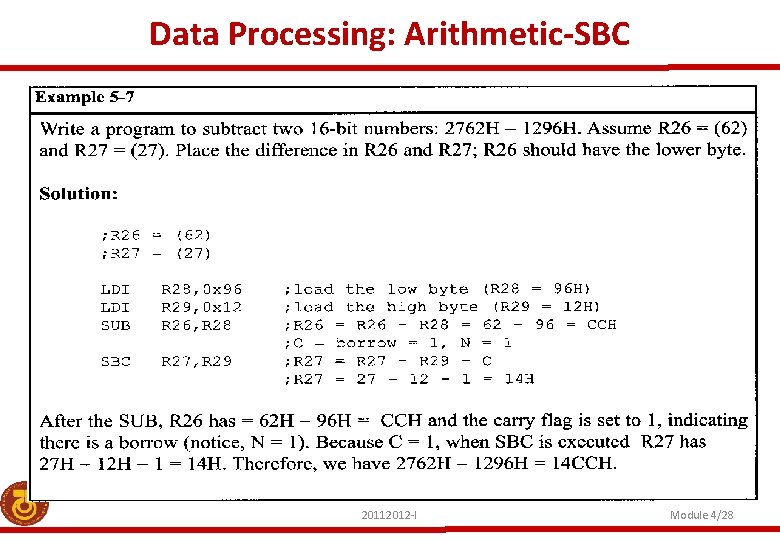

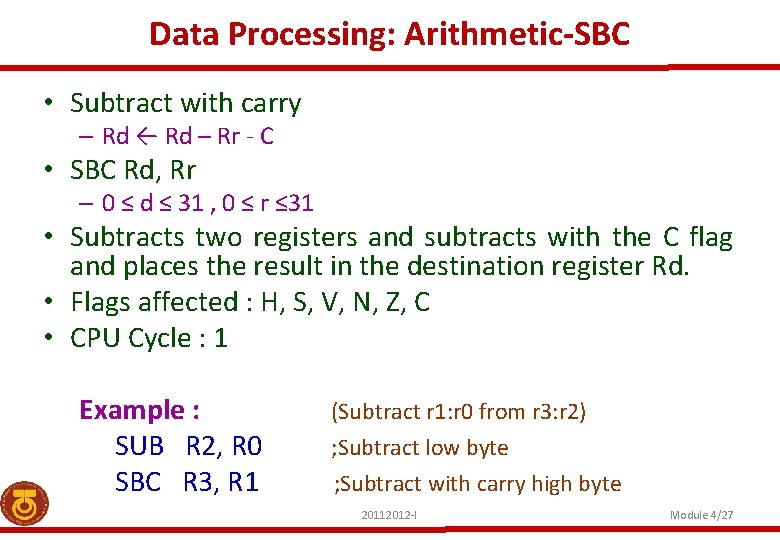

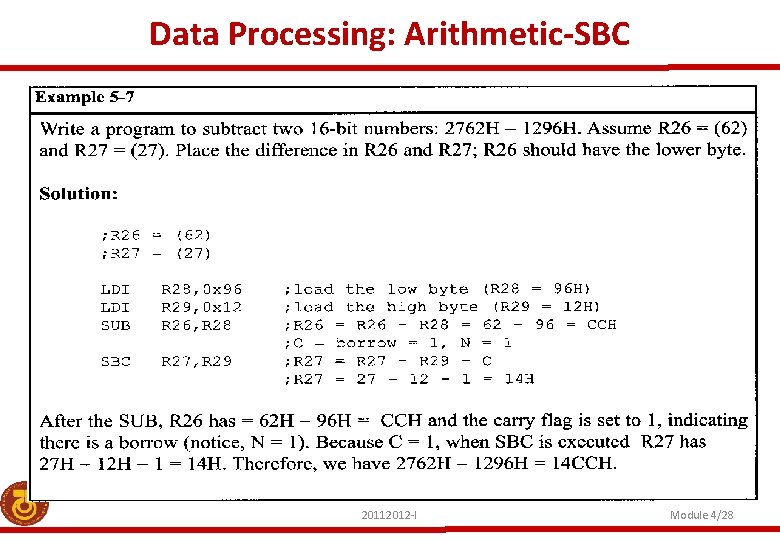

Data Processing: Arithmetic-SBC • Subtract with carry – Rd ← Rd – Rr - C • SBC Rd, Rr – 0 ≤ d ≤ 31 , 0 ≤ r ≤ 31 • Subtracts two registers and subtracts with the C flag and places the result in the destination register Rd. • Flags affected : H, S, V, N, Z, C • CPU Cycle : 1 Example : SUB R 2, R 0 SBC R 3, R 1 (Subtract r 1: r 0 from r 3: r 2) ; Subtract low byte ; Subtract with carry high byte 20112012 -I Module 4/27

Data Processing: Arithmetic-SBC 20112012 -I Module 4/28

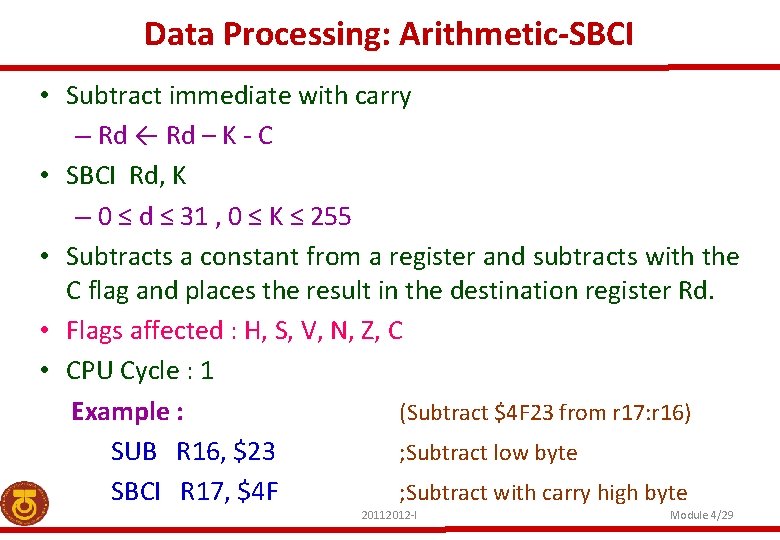

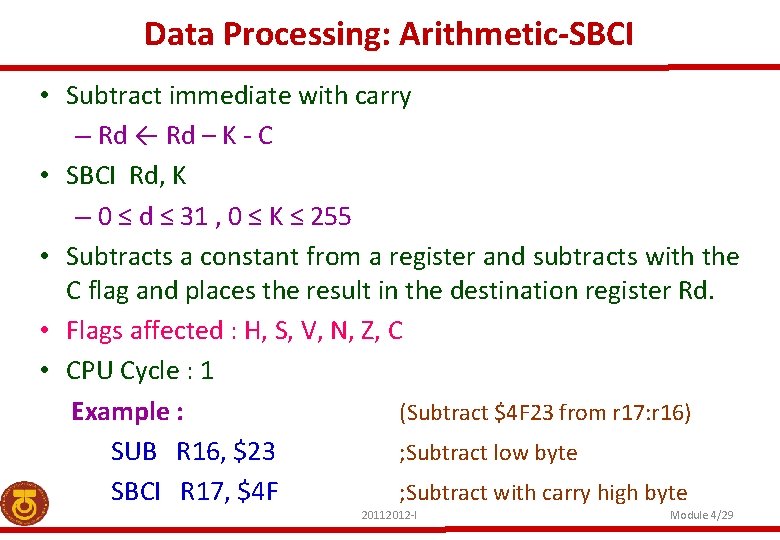

Data Processing: Arithmetic-SBCI • Subtract immediate with carry – Rd ← Rd – K - C • SBCI Rd, K – 0 ≤ d ≤ 31 , 0 ≤ K ≤ 255 • Subtracts a constant from a register and subtracts with the C flag and places the result in the destination register Rd. • Flags affected : H, S, V, N, Z, C • CPU Cycle : 1 Example : (Subtract $4 F 23 from r 17: r 16) SUB R 16, $23 ; Subtract low byte SBCI R 17, $4 F ; Subtract with carry high byte 20112012 -I Module 4/29

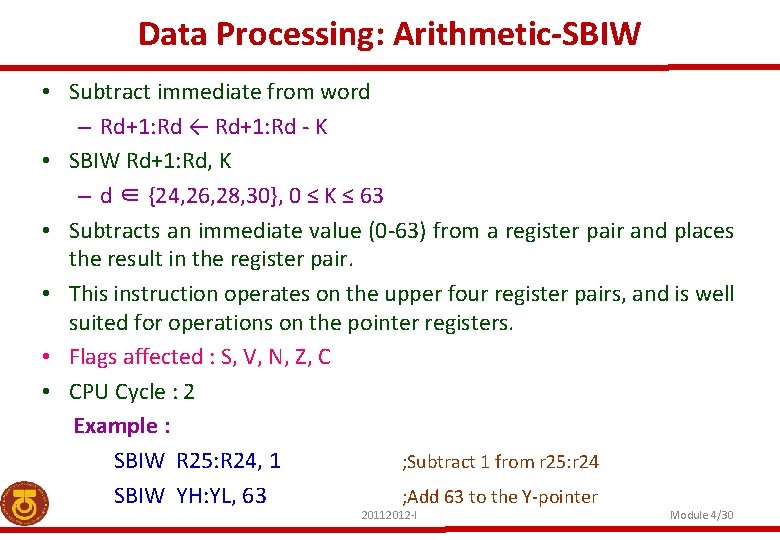

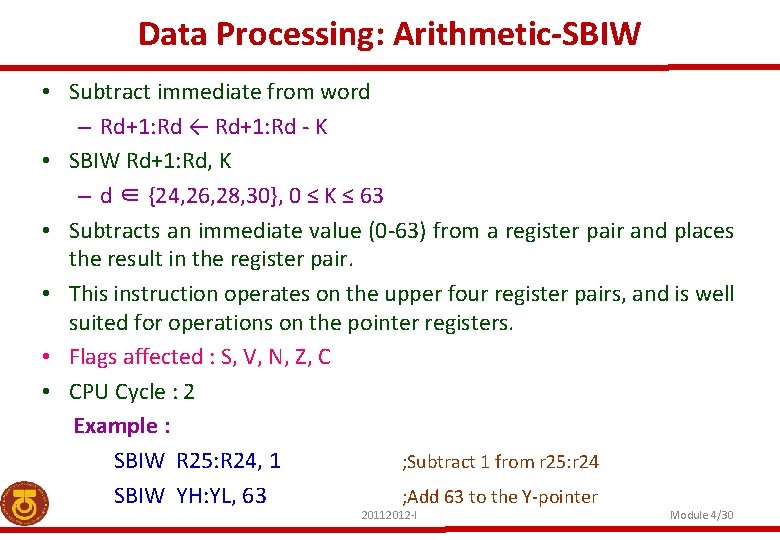

Data Processing: Arithmetic-SBIW • Subtract immediate from word – Rd+1: Rd ← Rd+1: Rd - K • SBIW Rd+1: Rd, K – d ∈ {24, 26, 28, 30}, 0 ≤ K ≤ 63 • Subtracts an immediate value (0 -63) from a register pair and places the result in the register pair. • This instruction operates on the upper four register pairs, and is well suited for operations on the pointer registers. • Flags affected : S, V, N, Z, C • CPU Cycle : 2 Example : SBIW R 25: R 24, 1 ; Subtract 1 from r 25: r 24 SBIW YH: YL, 63 ; Add 63 to the Y-pointer 20112012 -I Module 4/30

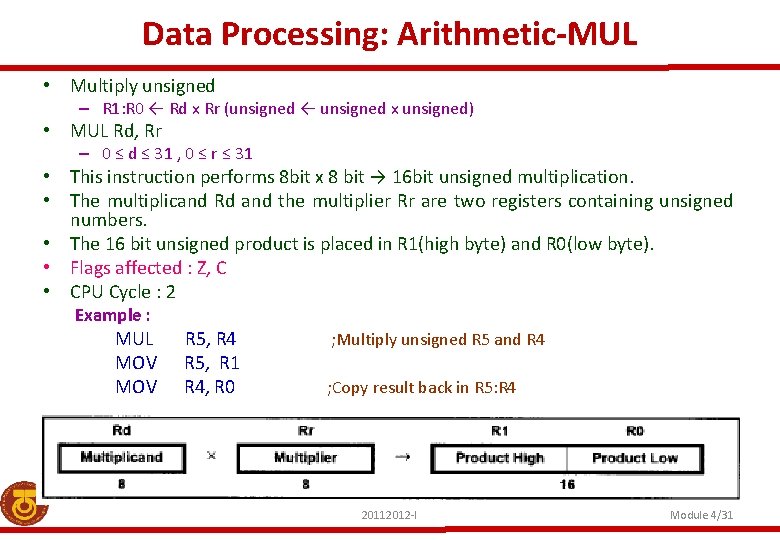

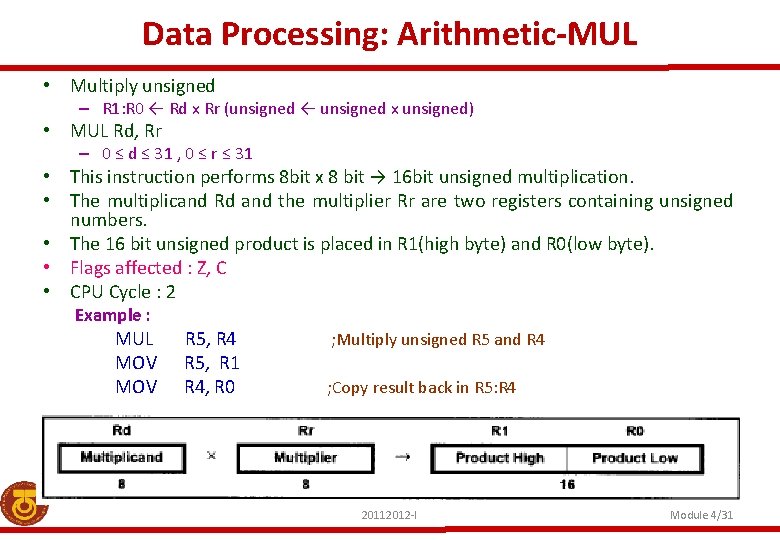

Data Processing: Arithmetic-MUL • Multiply unsigned – R 1: R 0 ← Rd x Rr (unsigned ← unsigned x unsigned) • MUL Rd, Rr – 0 ≤ d ≤ 31 , 0 ≤ r ≤ 31 • This instruction performs 8 bit x 8 bit → 16 bit unsigned multiplication. • The multiplicand Rd and the multiplier Rr are two registers containing unsigned numbers. • The 16 bit unsigned product is placed in R 1(high byte) and R 0(low byte). • Flags affected : Z, C • CPU Cycle : 2 Example : MUL MOV R 5, R 4 R 5, R 1 R 4, R 0 ; Multiply unsigned R 5 and R 4 ; Copy result back in R 5: R 4 20112012 -I Module 4/31

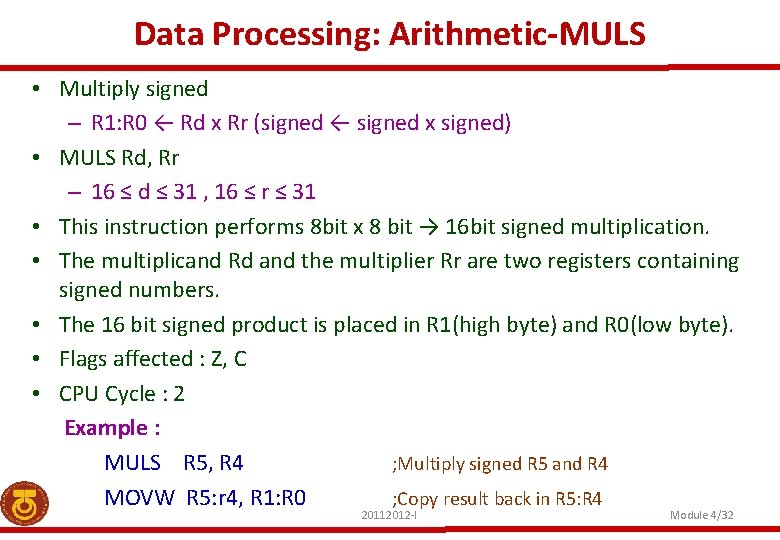

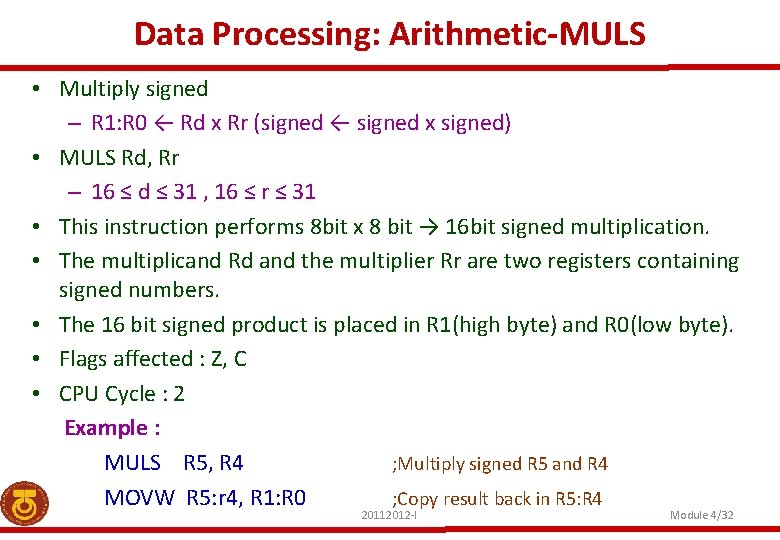

Data Processing: Arithmetic-MULS • Multiply signed – R 1: R 0 ← Rd x Rr (signed ← signed x signed) • MULS Rd, Rr – 16 ≤ d ≤ 31 , 16 ≤ r ≤ 31 • This instruction performs 8 bit x 8 bit → 16 bit signed multiplication. • The multiplicand Rd and the multiplier Rr are two registers containing signed numbers. • The 16 bit signed product is placed in R 1(high byte) and R 0(low byte). • Flags affected : Z, C • CPU Cycle : 2 Example : MULS R 5, R 4 ; Multiply signed R 5 and R 4 MOVW R 5: r 4, R 1: R 0 ; Copy result back in R 5: R 4 20112012 -I Module 4/32

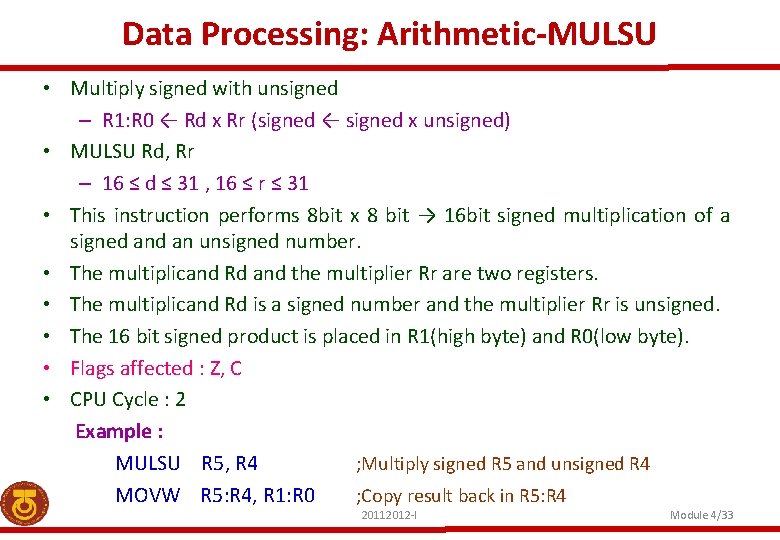

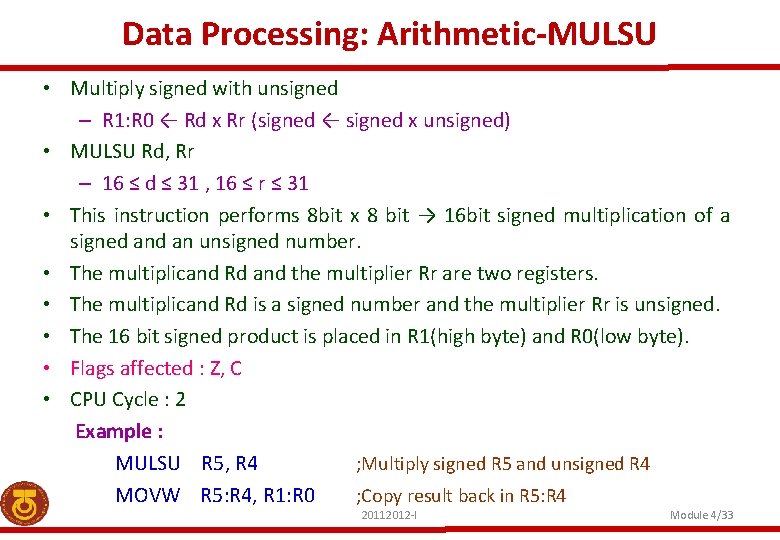

Data Processing: Arithmetic-MULSU • Multiply signed with unsigned – R 1: R 0 ← Rd x Rr (signed ← signed x unsigned) • MULSU Rd, Rr – 16 ≤ d ≤ 31 , 16 ≤ r ≤ 31 • This instruction performs 8 bit x 8 bit → 16 bit signed multiplication of a signed an unsigned number. • The multiplicand Rd and the multiplier Rr are two registers. • The multiplicand Rd is a signed number and the multiplier Rr is unsigned. • The 16 bit signed product is placed in R 1(high byte) and R 0(low byte). • Flags affected : Z, C • CPU Cycle : 2 Example : MULSU R 5, R 4 ; Multiply signed R 5 and unsigned R 4 MOVW R 5: R 4, R 1: R 0 ; Copy result back in R 5: R 4 20112012 -I Module 4/33

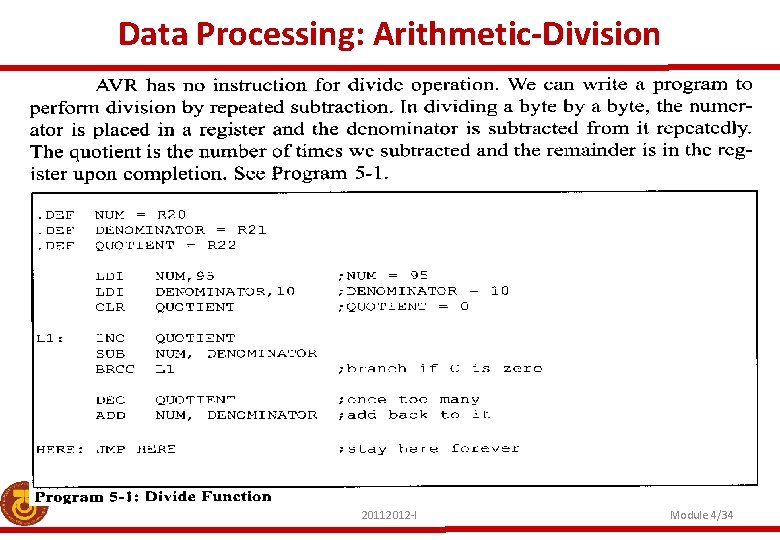

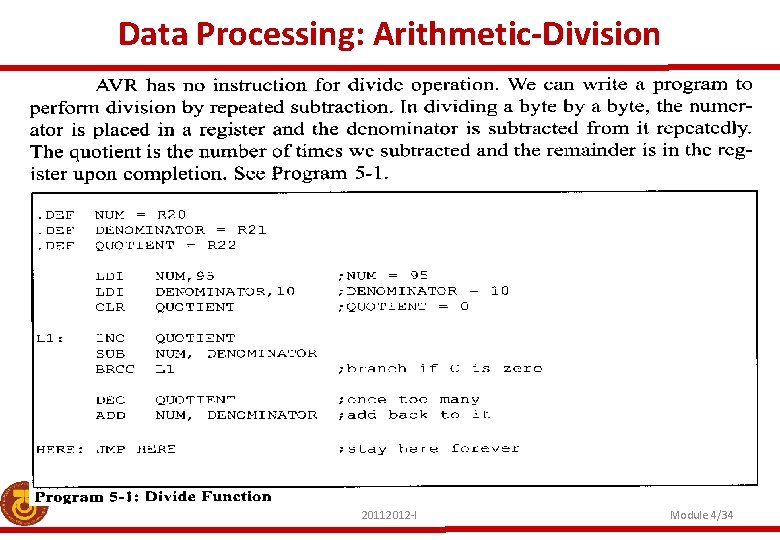

Data Processing: Arithmetic-Division 20112012 -I Module 4/34

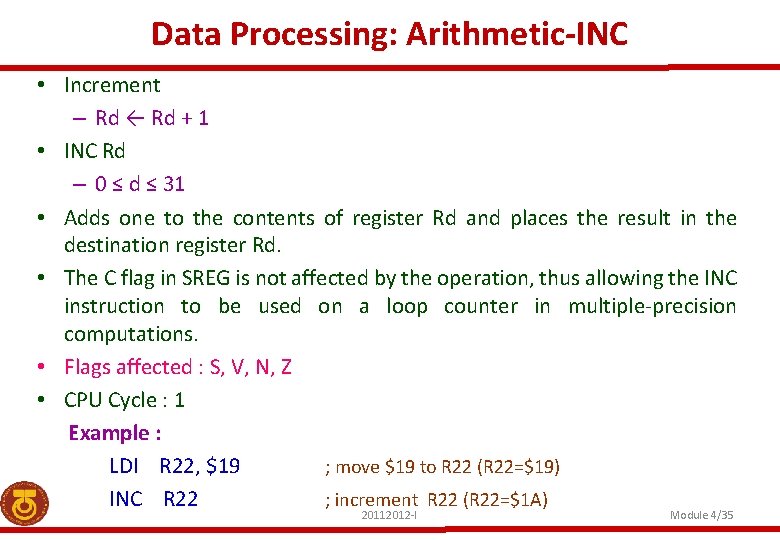

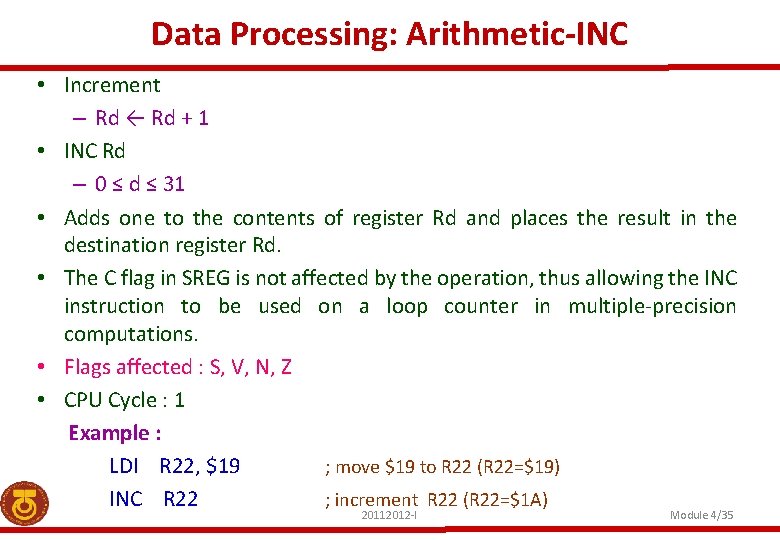

Data Processing: Arithmetic-INC • Increment – Rd ← Rd + 1 • INC Rd – 0 ≤ d ≤ 31 • Adds one to the contents of register Rd and places the result in the destination register Rd. • The C flag in SREG is not affected by the operation, thus allowing the INC instruction to be used on a loop counter in multiple-precision computations. • Flags affected : S, V, N, Z • CPU Cycle : 1 Example : LDI R 22, $19 ; move $19 to R 22 (R 22=$19) INC R 22 ; increment R 22 (R 22=$1 A) 20112012 -I Module 4/35

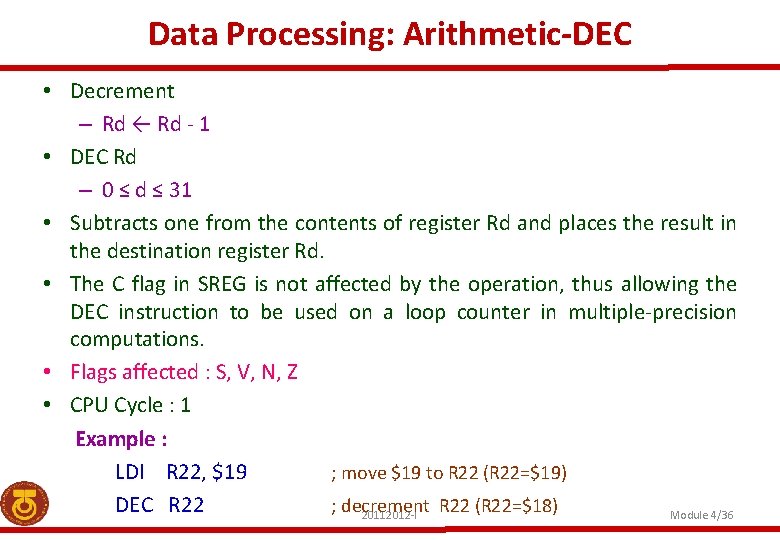

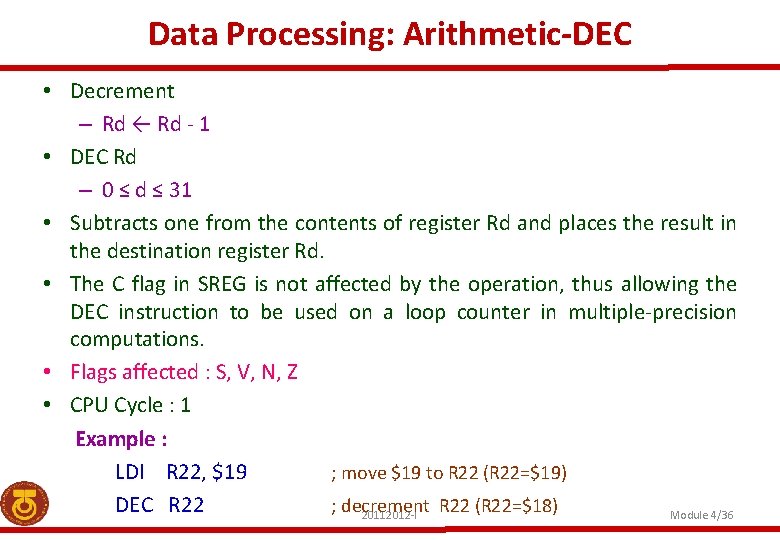

Data Processing: Arithmetic-DEC • Decrement – Rd ← Rd - 1 • DEC Rd – 0 ≤ d ≤ 31 • Subtracts one from the contents of register Rd and places the result in the destination register Rd. • The C flag in SREG is not affected by the operation, thus allowing the DEC instruction to be used on a loop counter in multiple-precision computations. • Flags affected : S, V, N, Z • CPU Cycle : 1 Example : LDI R 22, $19 ; move $19 to R 22 (R 22=$19) DEC R 22 ; decrement R 22 (R 22=$18) 20112012 -I Module 4/36

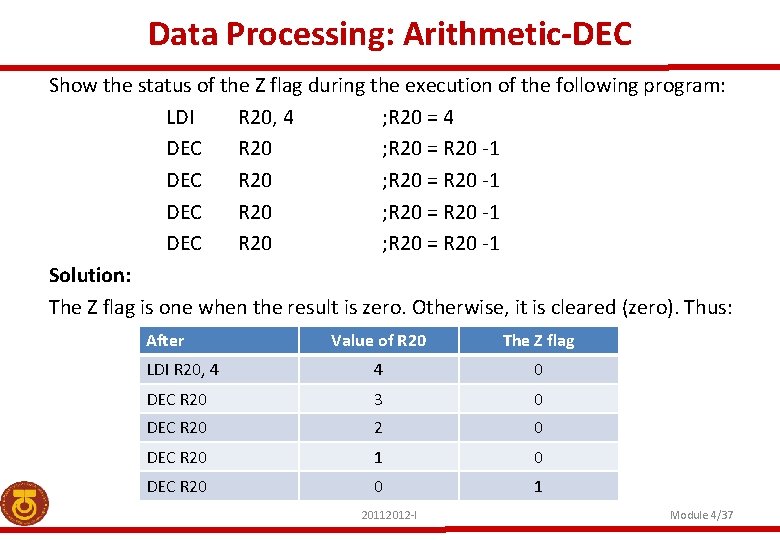

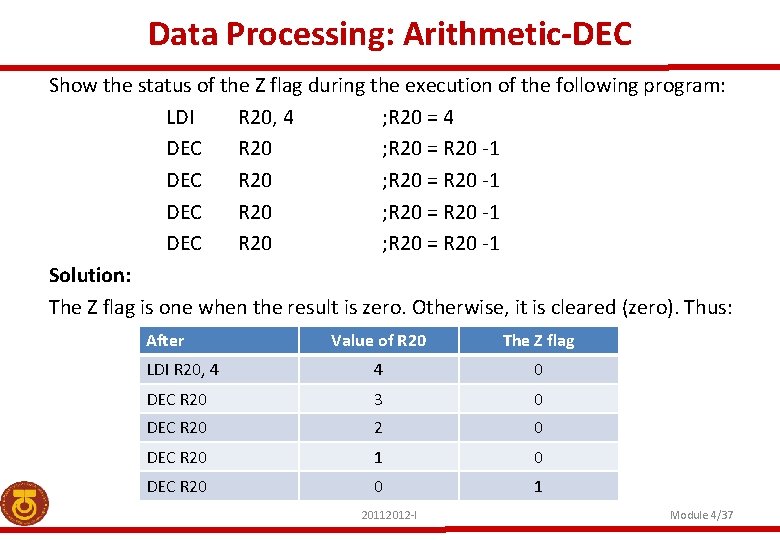

Data Processing: Arithmetic-DEC Show the status of the Z flag during the execution of the following program: LDI R 20, 4 ; R 20 = 4 DEC R 20 ; R 20 = R 20 -1 Solution: The Z flag is one when the result is zero. Otherwise, it is cleared (zero). Thus: After Value of R 20 The Z flag LDI R 20, 4 4 0 DEC R 20 3 0 DEC R 20 2 0 DEC R 20 1 0 DEC R 20 0 1 20112012 -I Module 4/37

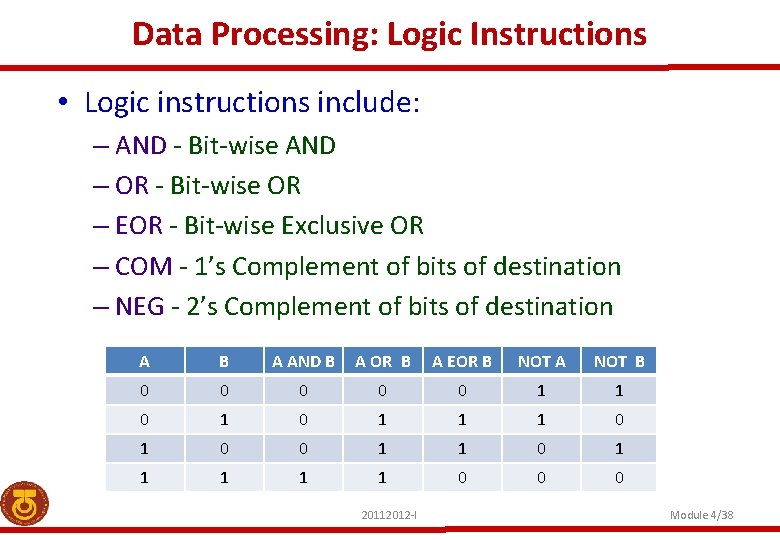

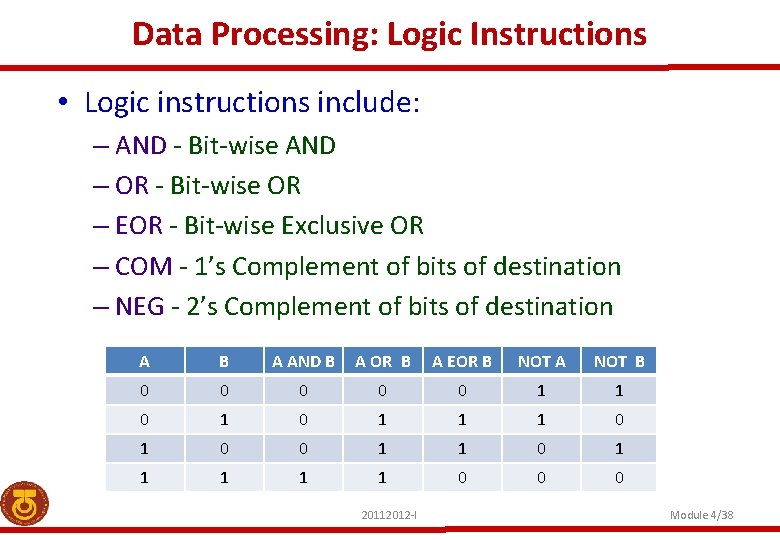

Data Processing: Logic Instructions • Logic instructions include: – AND - Bit-wise AND – OR - Bit-wise OR – EOR - Bit-wise Exclusive OR – COM - 1’s Complement of bits of destination – NEG - 2’s Complement of bits of destination A B A AND B A OR B A EOR B NOT A NOT B 0 0 0 1 1 1 0 0 1 1 1 1 1 0 0 0 20112012 -I Module 4/38

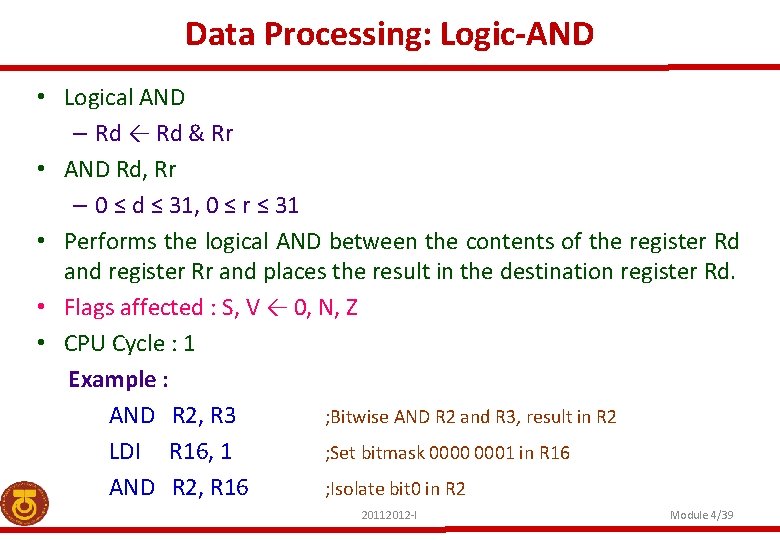

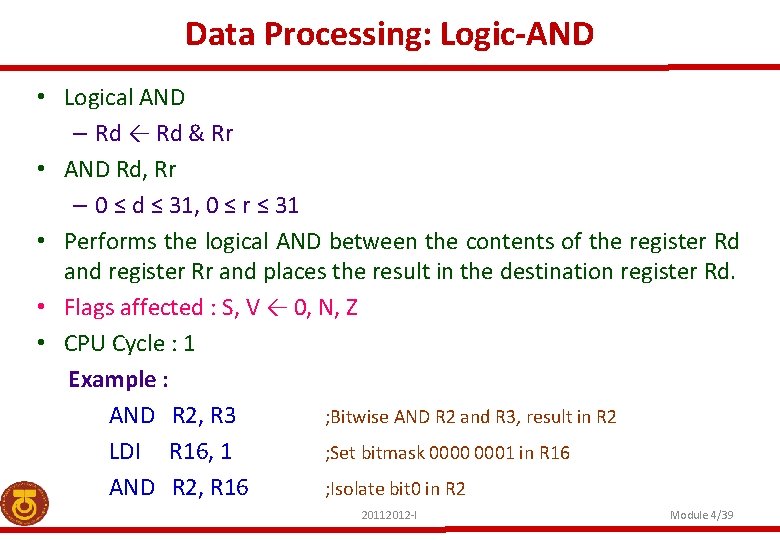

Data Processing: Logic-AND • Logical AND – Rd ← Rd & Rr • AND Rd, Rr – 0 ≤ d ≤ 31, 0 ≤ r ≤ 31 • Performs the logical AND between the contents of the register Rd and register Rr and places the result in the destination register Rd. • Flags affected : S, V ← 0, N, Z • CPU Cycle : 1 Example : AND R 2, R 3 ; Bitwise AND R 2 and R 3, result in R 2 LDI R 16, 1 ; Set bitmask 0000 0001 in R 16 AND R 2, R 16 ; Isolate bit 0 in R 2 20112012 -I Module 4/39

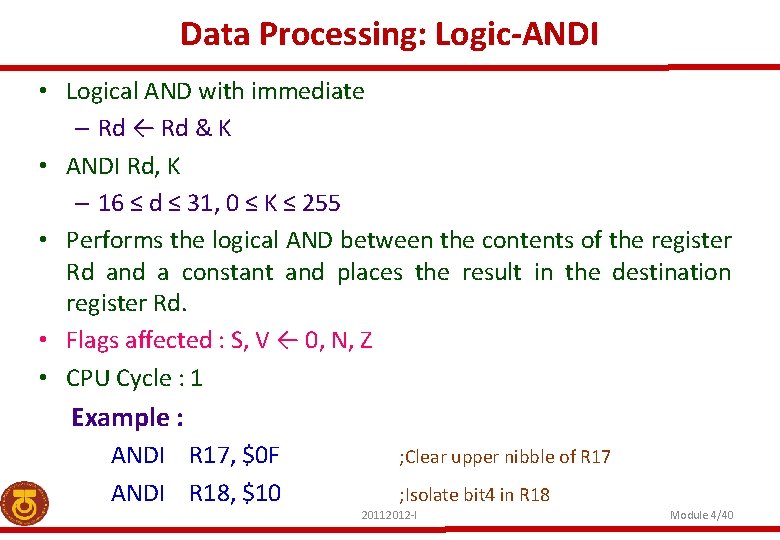

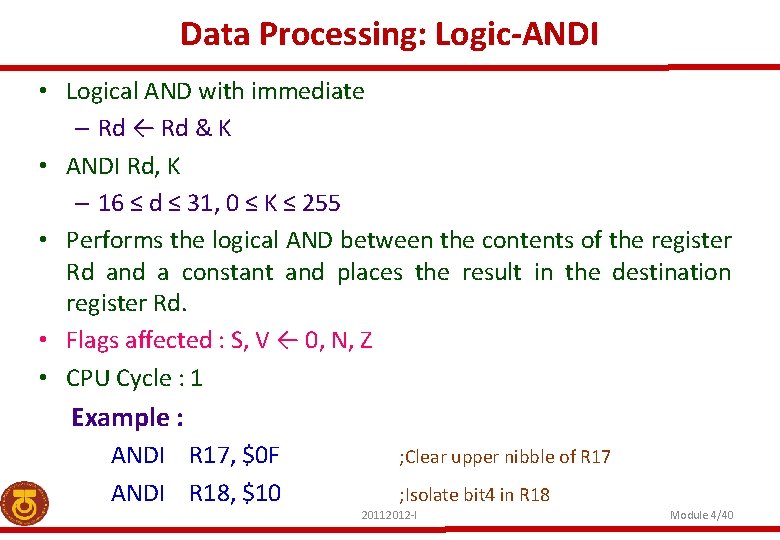

Data Processing: Logic-ANDI • Logical AND with immediate – Rd ← Rd & K • ANDI Rd, K – 16 ≤ d ≤ 31, 0 ≤ K ≤ 255 • Performs the logical AND between the contents of the register Rd and a constant and places the result in the destination register Rd. • Flags affected : S, V ← 0, N, Z • CPU Cycle : 1 Example : ANDI R 17, $0 F ANDI R 18, $10 ; Clear upper nibble of R 17 ; Isolate bit 4 in R 18 20112012 -I Module 4/40

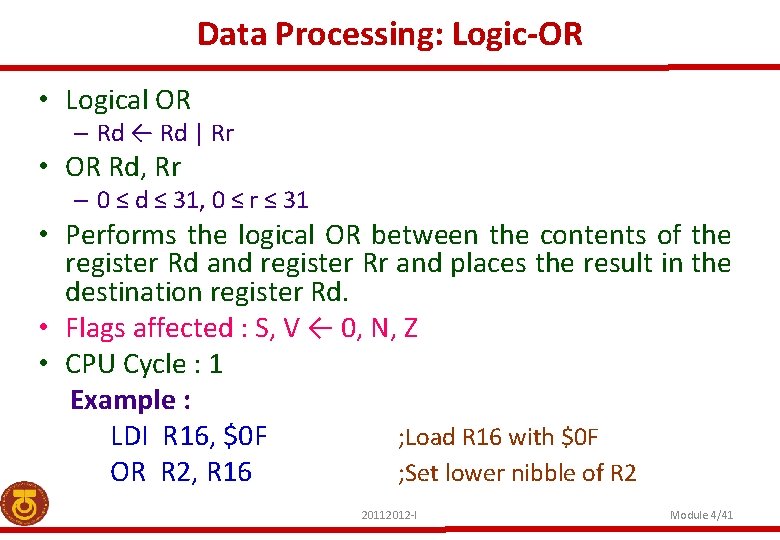

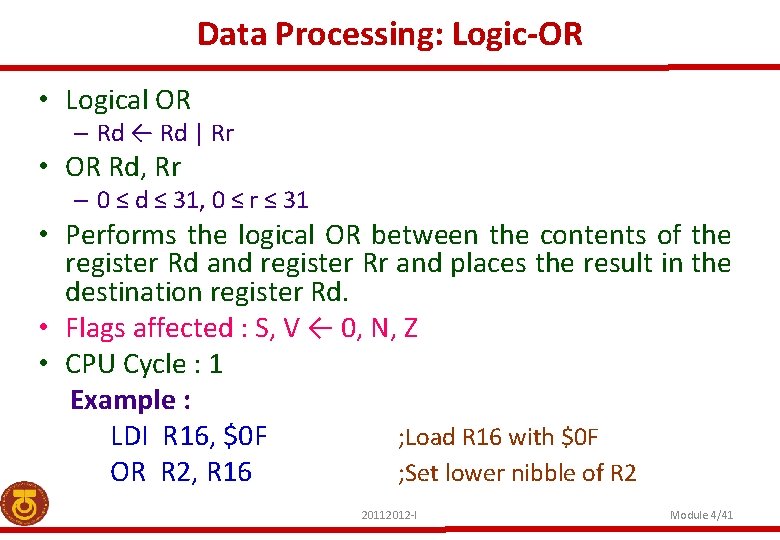

Data Processing: Logic-OR • Logical OR – Rd ← Rd | Rr • OR Rd, Rr – 0 ≤ d ≤ 31, 0 ≤ r ≤ 31 • Performs the logical OR between the contents of the register Rd and register Rr and places the result in the destination register Rd. • Flags affected : S, V ← 0, N, Z • CPU Cycle : 1 Example : LDI R 16, $0 F ; Load R 16 with $0 F OR R 2, R 16 ; Set lower nibble of R 2 20112012 -I Module 4/41

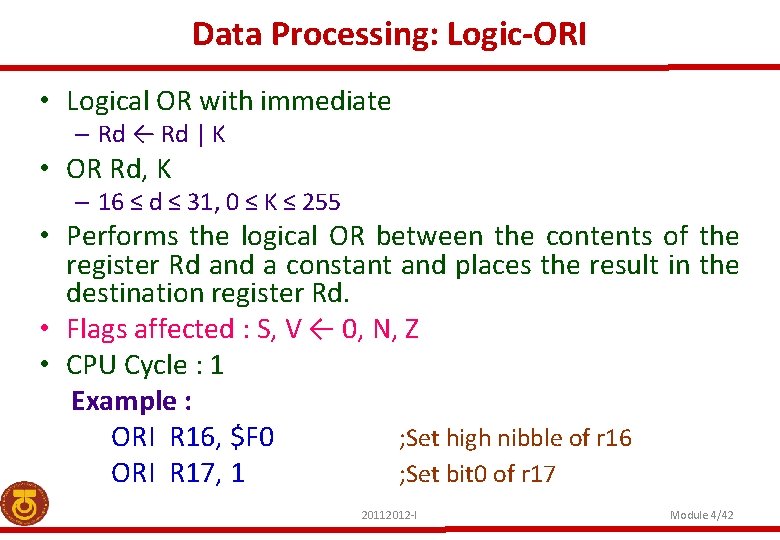

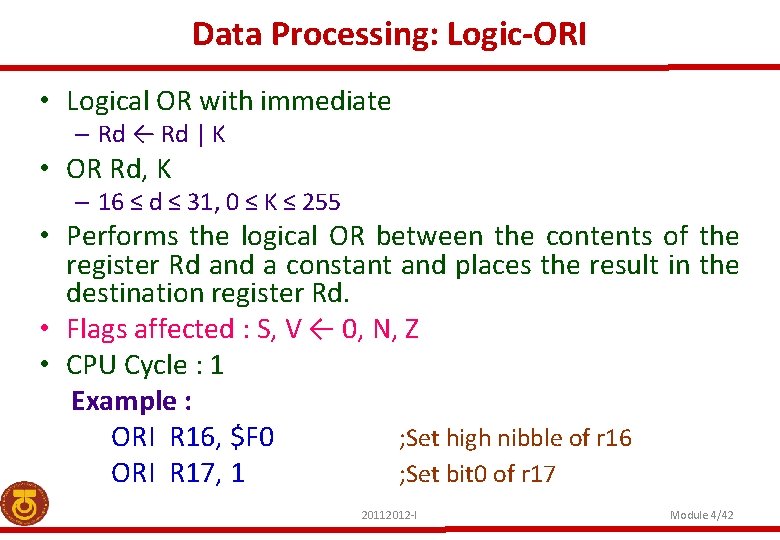

Data Processing: Logic-ORI • Logical OR with immediate – Rd ← Rd | K • OR Rd, K – 16 ≤ d ≤ 31, 0 ≤ K ≤ 255 • Performs the logical OR between the contents of the register Rd and a constant and places the result in the destination register Rd. • Flags affected : S, V ← 0, N, Z • CPU Cycle : 1 Example : ORI R 16, $F 0 ; Set high nibble of r 16 ORI R 17, 1 ; Set bit 0 of r 17 20112012 -I Module 4/42

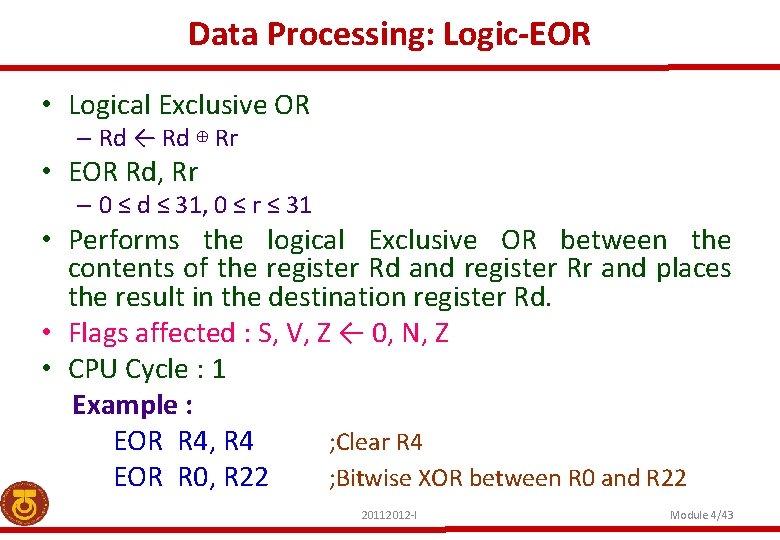

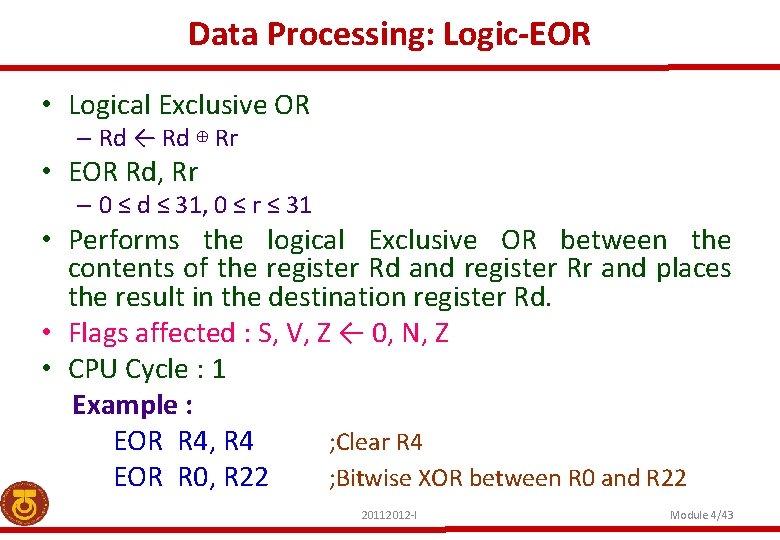

Data Processing: Logic-EOR • Logical Exclusive OR – Rd ← Rd ⊕ Rr • EOR Rd, Rr – 0 ≤ d ≤ 31, 0 ≤ r ≤ 31 • Performs the logical Exclusive OR between the contents of the register Rd and register Rr and places the result in the destination register Rd. • Flags affected : S, V, Z ← 0, N, Z • CPU Cycle : 1 Example : EOR R 4, R 4 ; Clear R 4 EOR R 0, R 22 ; Bitwise XOR between R 0 and R 22 20112012 -I Module 4/43

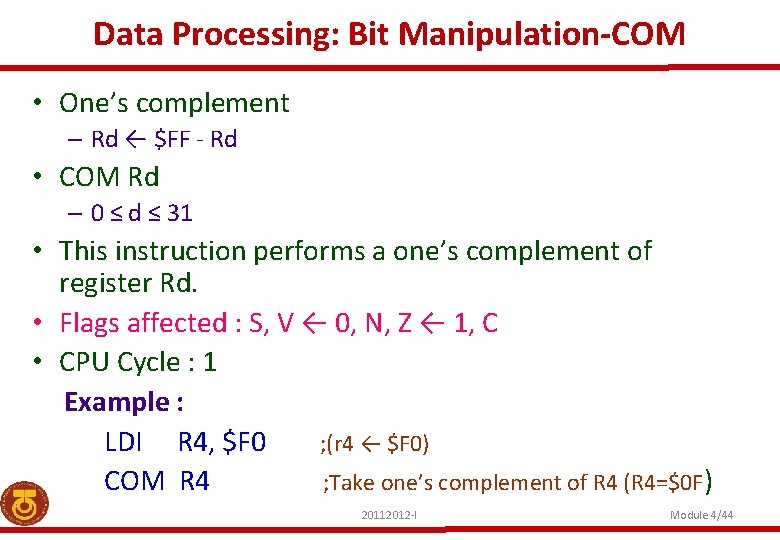

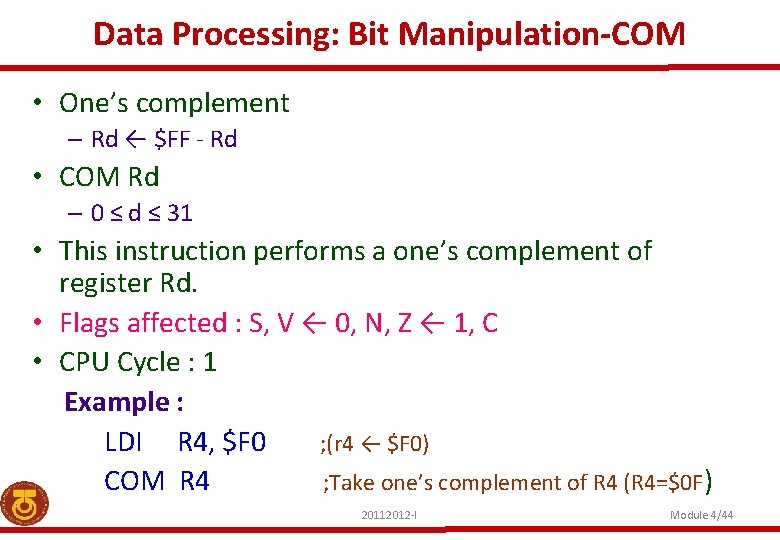

Data Processing: Bit Manipulation-COM • One’s complement – Rd ← $FF - Rd • COM Rd – 0 ≤ d ≤ 31 • This instruction performs a one’s complement of register Rd. • Flags affected : S, V ← 0, N, Z ← 1, C • CPU Cycle : 1 Example : LDI R 4, $F 0 ; (r 4 ← $F 0) COM R 4 ; Take one’s complement of R 4 (R 4=$0 F) 20112012 -I Module 4/44

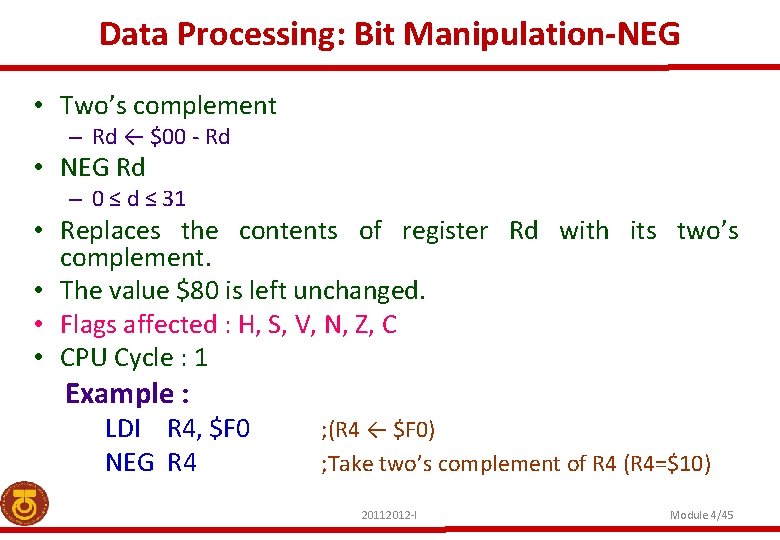

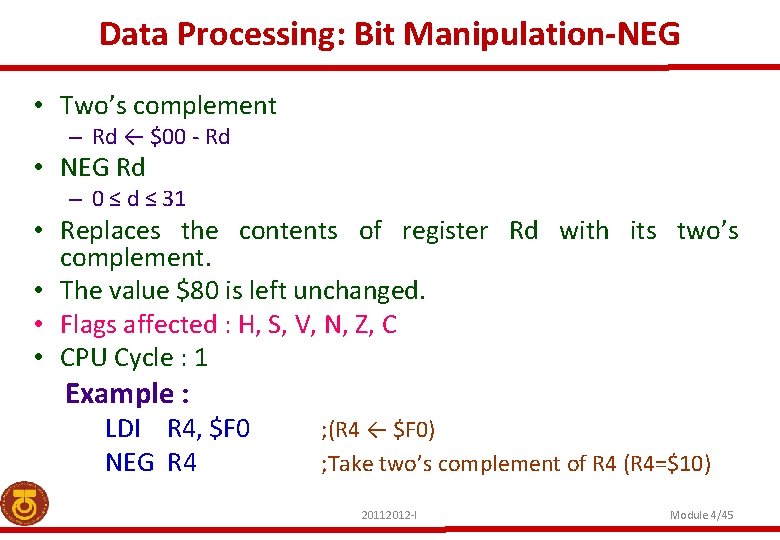

Data Processing: Bit Manipulation-NEG • Two’s complement – Rd ← $00 - Rd • NEG Rd – 0 ≤ d ≤ 31 • Replaces the contents of register Rd with its two’s complement. • The value $80 is left unchanged. • Flags affected : H, S, V, N, Z, C • CPU Cycle : 1 Example : LDI R 4, $F 0 NEG R 4 ; (R 4 ← $F 0) ; Take two’s complement of R 4 (R 4=$10) 20112012 -I Module 4/45

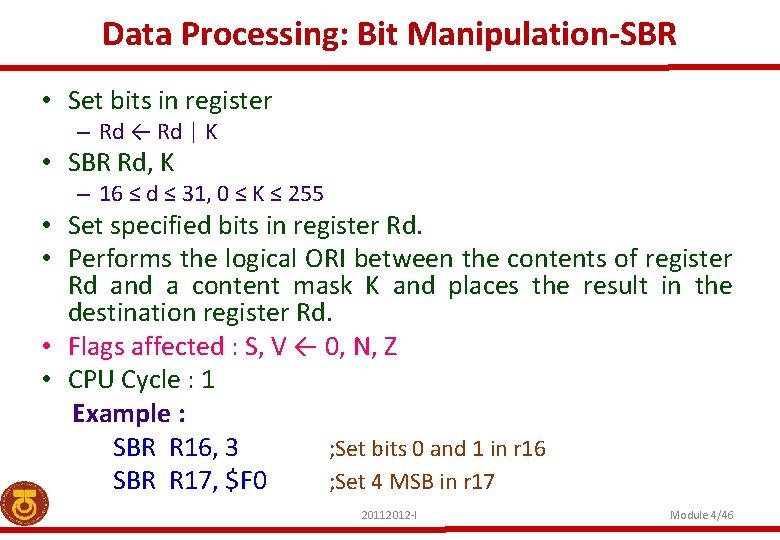

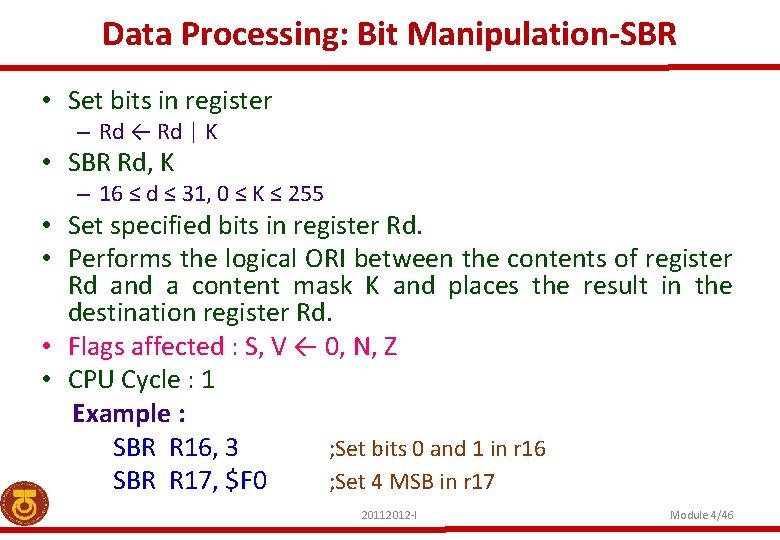

Data Processing: Bit Manipulation-SBR • Set bits in register – Rd ← Rd | K • SBR Rd, K – 16 ≤ d ≤ 31, 0 ≤ K ≤ 255 • Set specified bits in register Rd. • Performs the logical ORI between the contents of register Rd and a content mask K and places the result in the destination register Rd. • Flags affected : S, V ← 0, N, Z • CPU Cycle : 1 Example : SBR R 16, 3 ; Set bits 0 and 1 in r 16 SBR R 17, $F 0 ; Set 4 MSB in r 17 20112012 -I Module 4/46

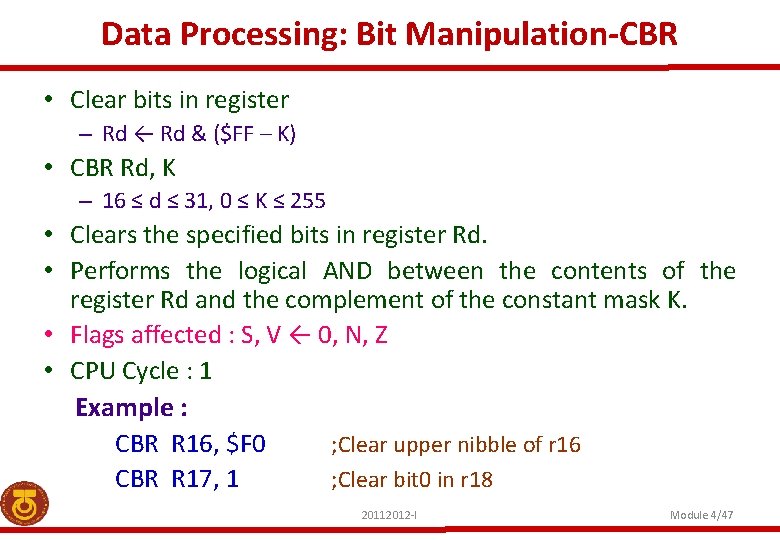

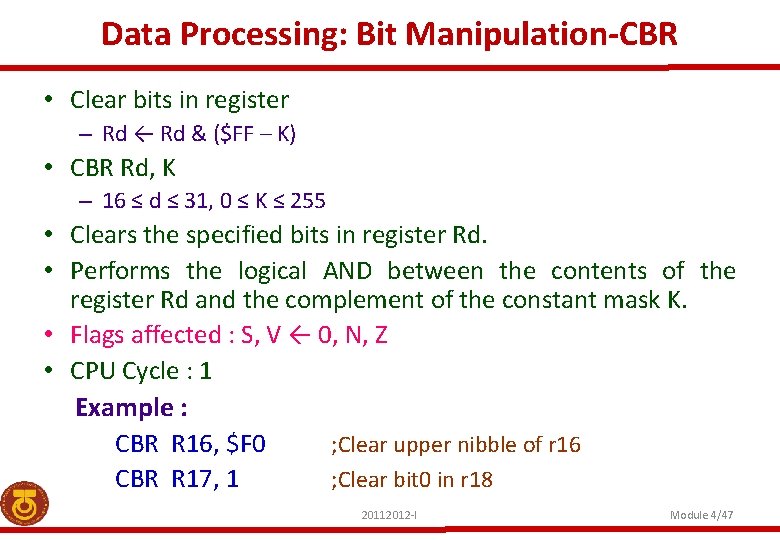

Data Processing: Bit Manipulation-CBR • Clear bits in register – Rd ← Rd & ($FF – K) • CBR Rd, K – 16 ≤ d ≤ 31, 0 ≤ K ≤ 255 • Clears the specified bits in register Rd. • Performs the logical AND between the contents of the register Rd and the complement of the constant mask K. • Flags affected : S, V ← 0, N, Z • CPU Cycle : 1 Example : CBR R 16, $F 0 ; Clear upper nibble of r 16 CBR R 17, 1 ; Clear bit 0 in r 18 20112012 -I Module 4/47

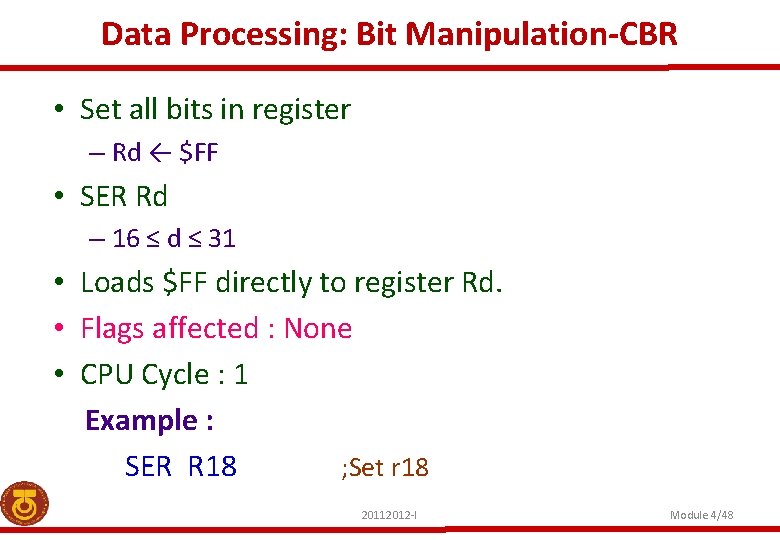

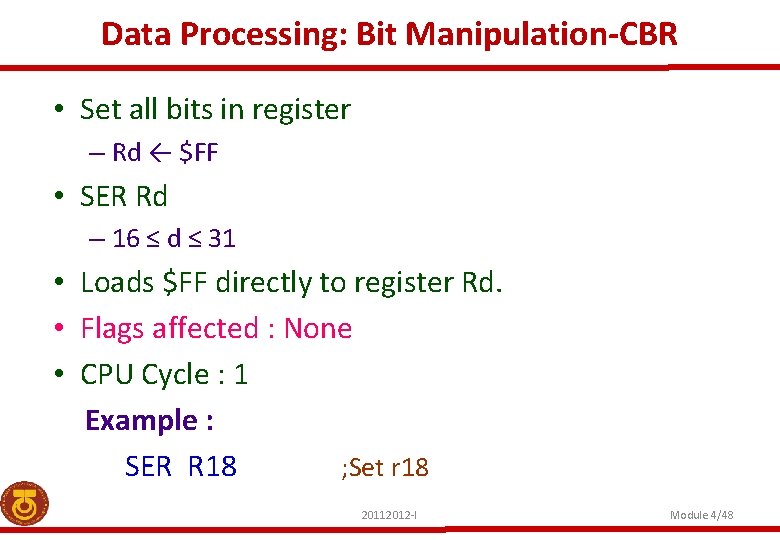

Data Processing: Bit Manipulation-CBR • Set all bits in register – Rd ← $FF • SER Rd – 16 ≤ d ≤ 31 • Loads $FF directly to register Rd. • Flags affected : None • CPU Cycle : 1 Example : SER R 18 ; Set r 18 20112012 -I Module 4/48

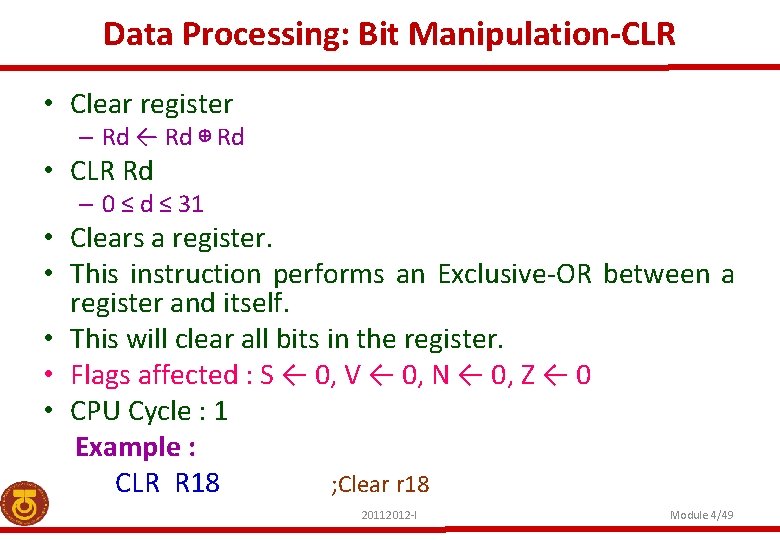

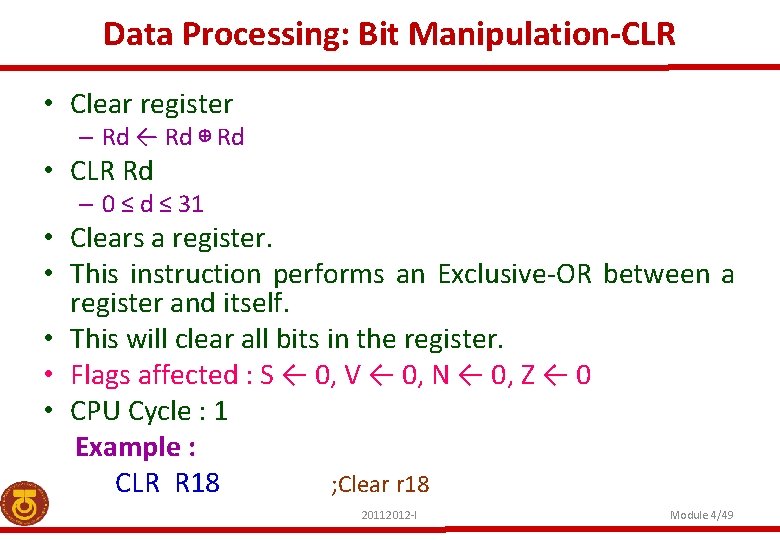

Data Processing: Bit Manipulation-CLR • Clear register – Rd ← Rd ⊕ Rd • CLR Rd – 0 ≤ d ≤ 31 • Clears a register. • This instruction performs an Exclusive-OR between a register and itself. • This will clear all bits in the register. • Flags affected : S ← 0, V ← 0, N ← 0, Z ← 0 • CPU Cycle : 1 Example : CLR R 18 ; Clear r 18 20112012 -I Module 4/49

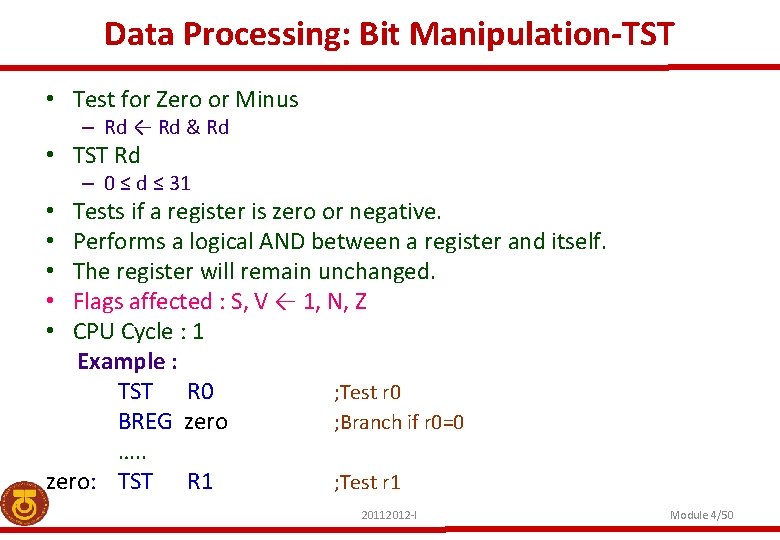

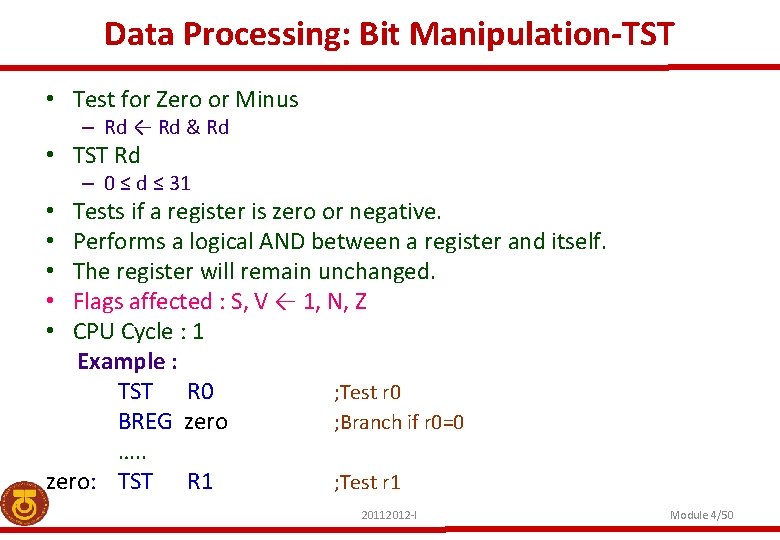

Data Processing: Bit Manipulation-TST • Test for Zero or Minus – Rd ← Rd & Rd • TST Rd – 0 ≤ d ≤ 31 Tests if a register is zero or negative. Performs a logical AND between a register and itself. The register will remain unchanged. Flags affected : S, V ← 1, N, Z CPU Cycle : 1 Example : TST R 0 ; Test r 0 BREG zero ; Branch if r 0=0 …. . zero: TST R 1 ; Test r 1 • • • 20112012 -I Module 4/50

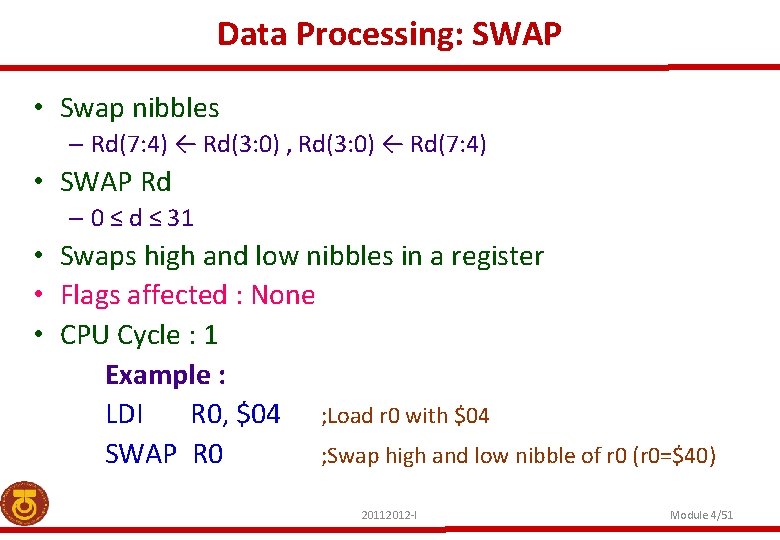

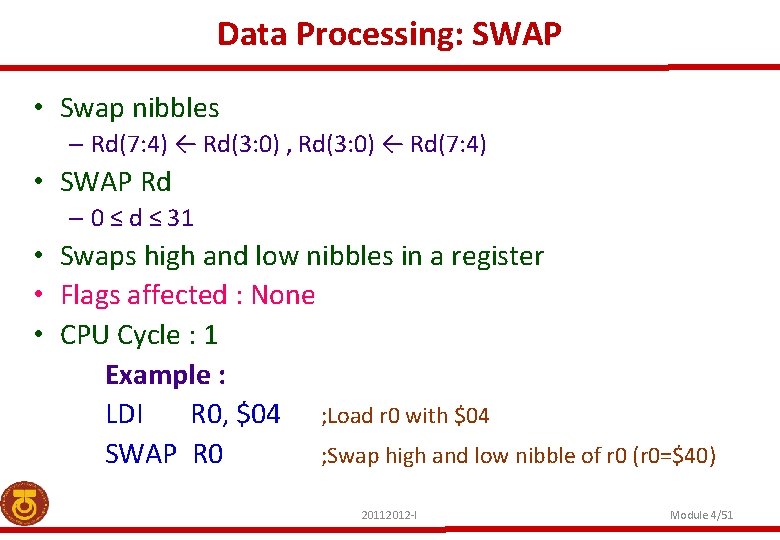

Data Processing: SWAP • Swap nibbles – Rd(7: 4) ← Rd(3: 0) , Rd(3: 0) ← Rd(7: 4) • SWAP Rd – 0 ≤ d ≤ 31 • Swaps high and low nibbles in a register • Flags affected : None • CPU Cycle : 1 Example : LDI R 0, $04 ; Load r 0 with $04 SWAP R 0 ; Swap high and low nibble of r 0 (r 0=$40) 20112012 -I Module 4/51

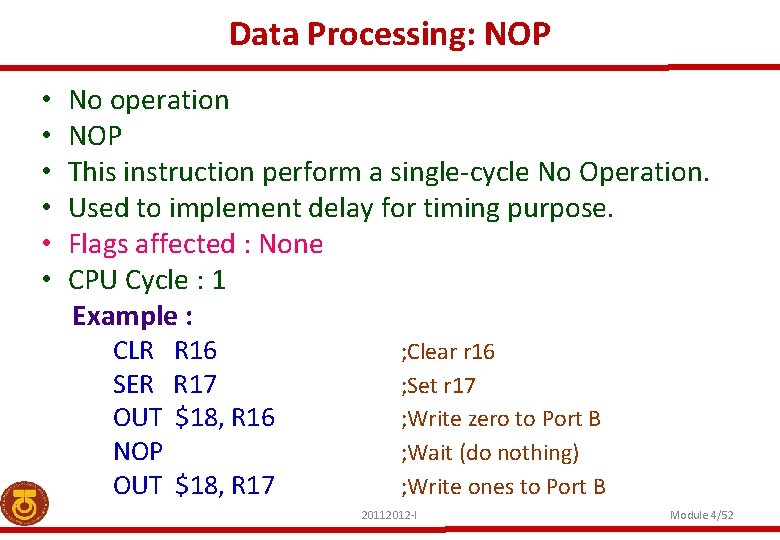

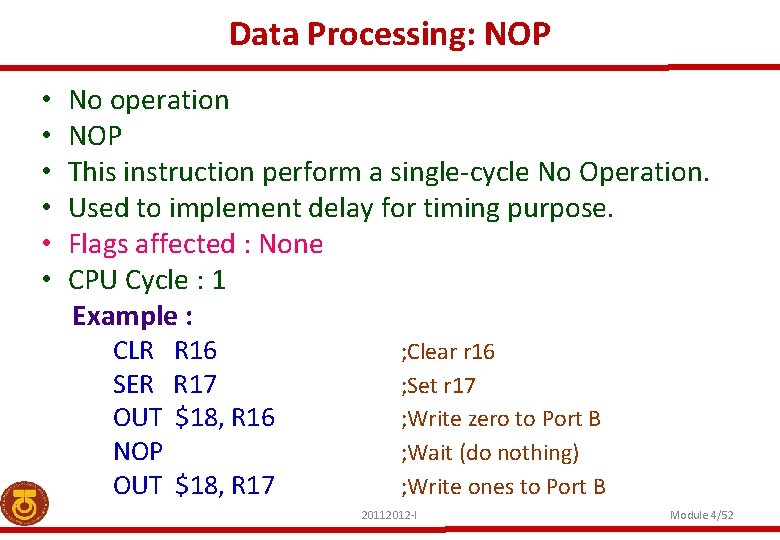

Data Processing: NOP • • • No operation NOP This instruction perform a single-cycle No Operation. Used to implement delay for timing purpose. Flags affected : None CPU Cycle : 1 Example : CLR SER OUT NOP OUT R 16 R 17 $18, R 16 $18, R 17 ; Clear r 16 ; Set r 17 ; Write zero to Port B ; Wait (do nothing) ; Write ones to Port B 20112012 -I Module 4/52