Modlisation et Simulation de Systmes sur Puce avec

- Slides: 24

Modélisation et Simulation de Systèmes sur Puce avec Soclib François Pêcheux Laboratoire LIP 6/ASIM francois. pecheux@lip 6. fr

Plan de la présentation Principes de So. CLib n Interfaces normalisées n Composants disponibles n Un exemple de plate-forme n Outils associés n Conclusion n

Soc. Lib, les principes n Résultat du travail collaboratif de 13 Laboratoires Nationaux et 6 partenaires industriels (dont ST et Thalès) Plate-forme labellisée par le CNRS en 2003 La coordination est assurée par le LIP 6 n Bibliothèque de modèles de composants n n ¨ ¨ n n n Ecrits en System. C Deux types de modèles (CABA et TLM/T) Interopérables (VCI) Performants (automates d’états synchrones) Open-source Conçue pour la modélisation et la simulation efficace de plateformes multiprocesseurs à espace mémoire partagé. Conçue pour l’exploration architecturale

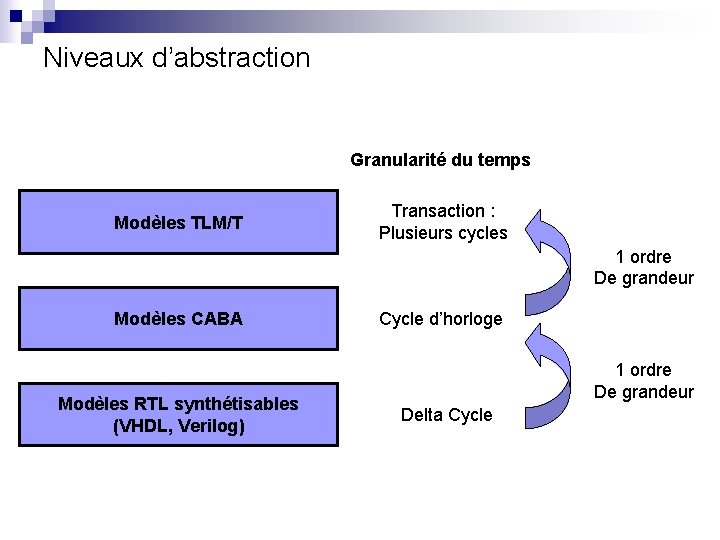

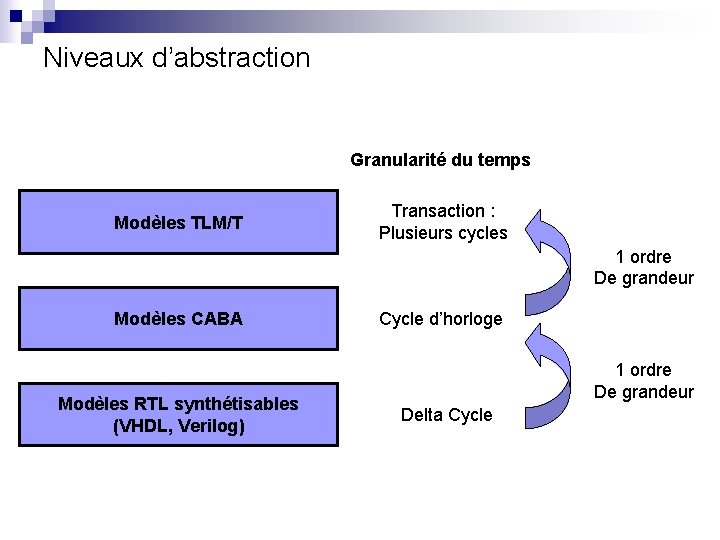

Niveaux d’abstraction Granularité du temps Modèles TLM/T Transaction : Plusieurs cycles 1 ordre De grandeur Modèles CABA Modèles RTL synthétisables (VHDL, Verilog) Cycle d’horloge 1 ordre De grandeur Delta Cycle

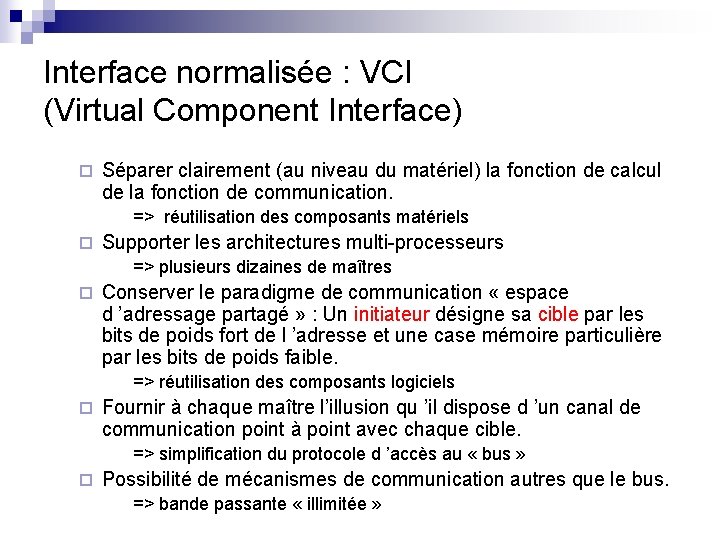

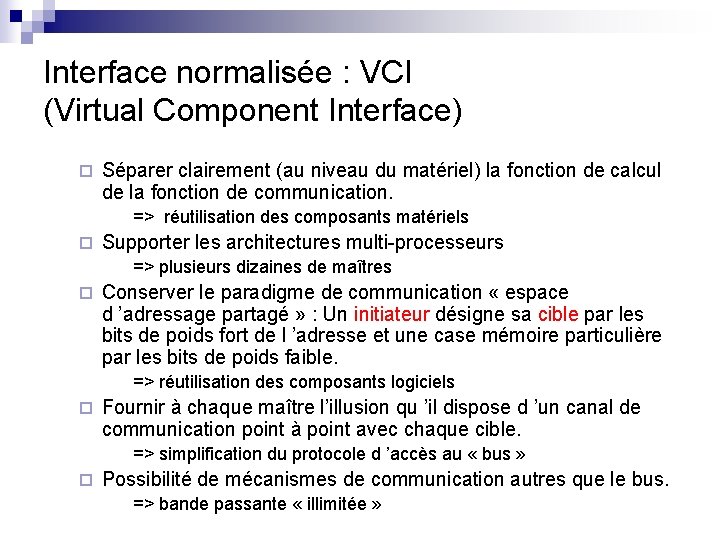

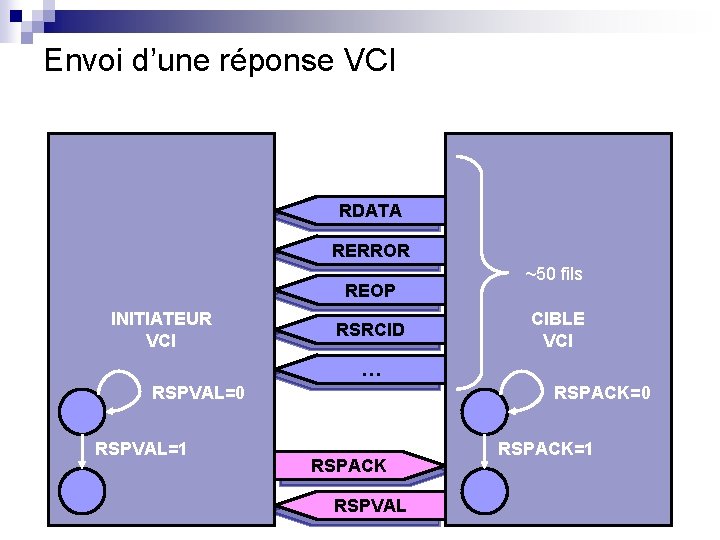

Interface normalisée : VCI (Virtual Component Interface) ¨ Séparer clairement (au niveau du matériel) la fonction de calcul de la fonction de communication. => réutilisation des composants matériels ¨ Supporter les architectures multi-processeurs => plusieurs dizaines de maîtres ¨ Conserver le paradigme de communication « espace d ’adressage partagé » : Un initiateur désigne sa cible par les bits de poids fort de l ’adresse et une case mémoire particulière par les bits de poids faible. => réutilisation des composants logiciels ¨ Fournir à chaque maître l’illusion qu ’il dispose d ’un canal de communication point à point avec chaque cible. => simplification du protocole d ’accès au « bus » ¨ Possibilité de mécanismes de communication autres que le bus. => bande passante « illimitée »

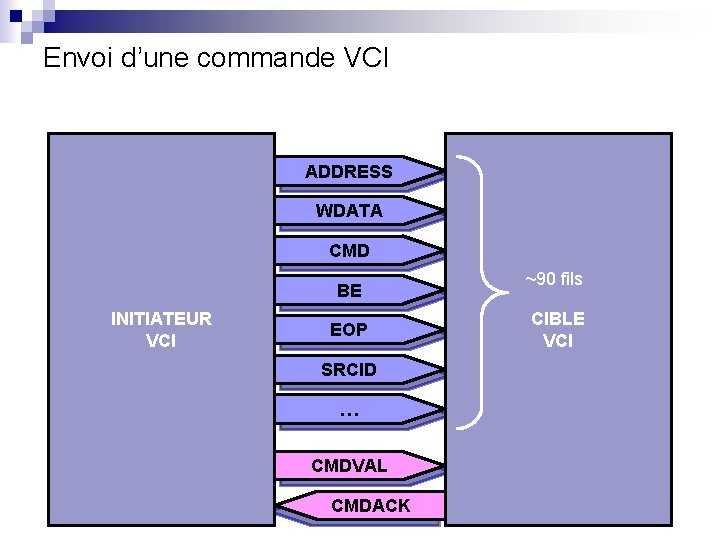

Envoi d’une commande VCI ADDRESS WDATA CMD BE INITIATEUR VCI EOP SRCID … CMDVAL CMDACK ~90 fils CIBLE VCI

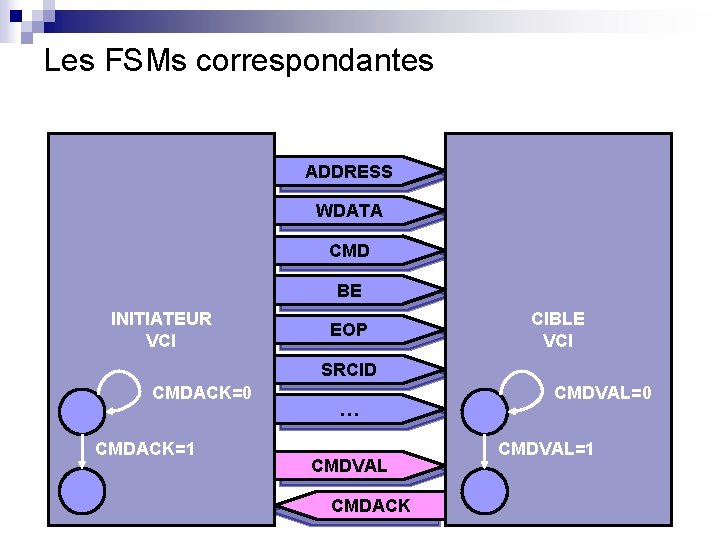

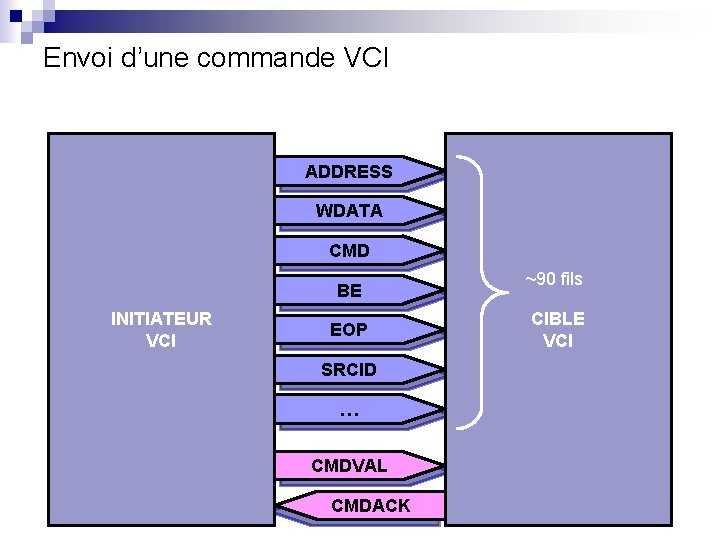

Les FSMs correspondantes ADDRESS WDATA CMD BE INITIATEUR VCI EOP CIBLE VCI SRCID CMDACK=0 CMDACK=1 … CMDVAL CMDACK CMDVAL=0 CMDVAL=1

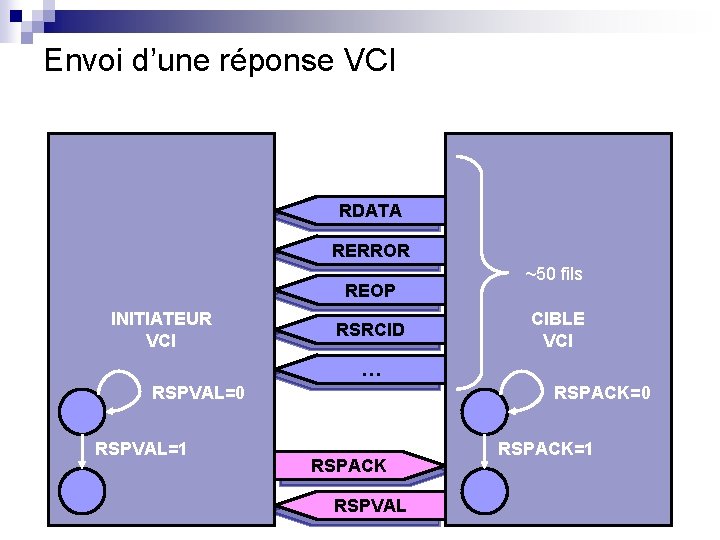

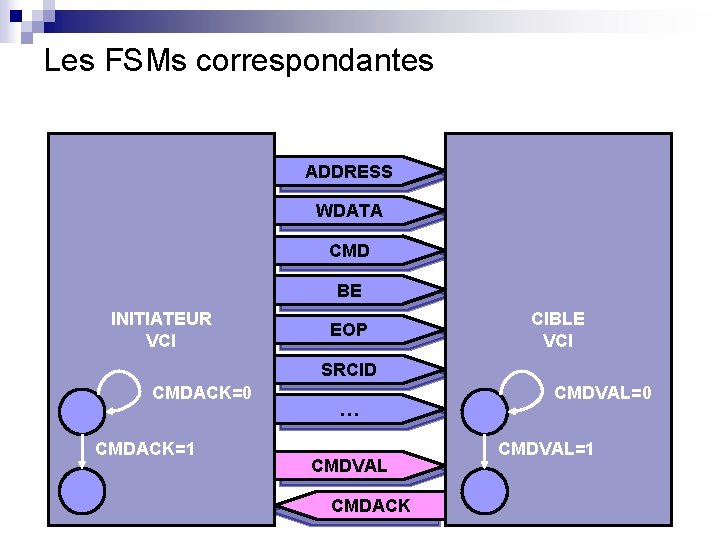

Envoi d’une réponse VCI RDATA RERROR REOP INITIATEUR VCI RSRCID ~50 fils CIBLE VCI … RSPVAL=0 RSPVAL=1 RSPACK=0 RSPACK RSPVAL RSPACK=1

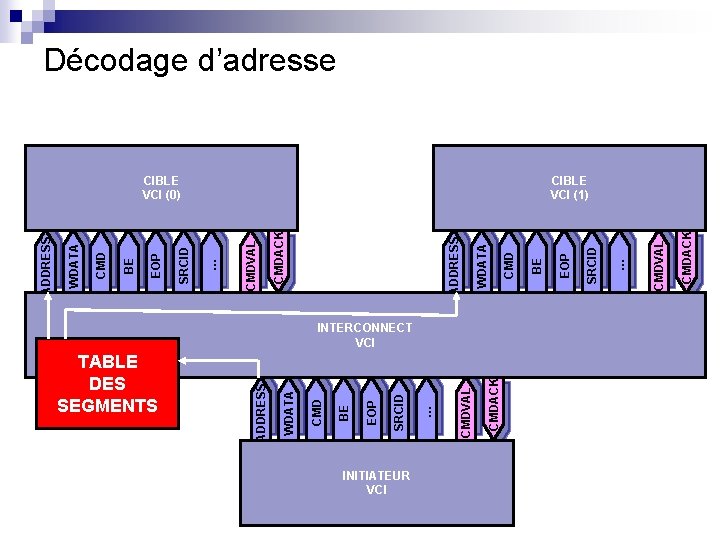

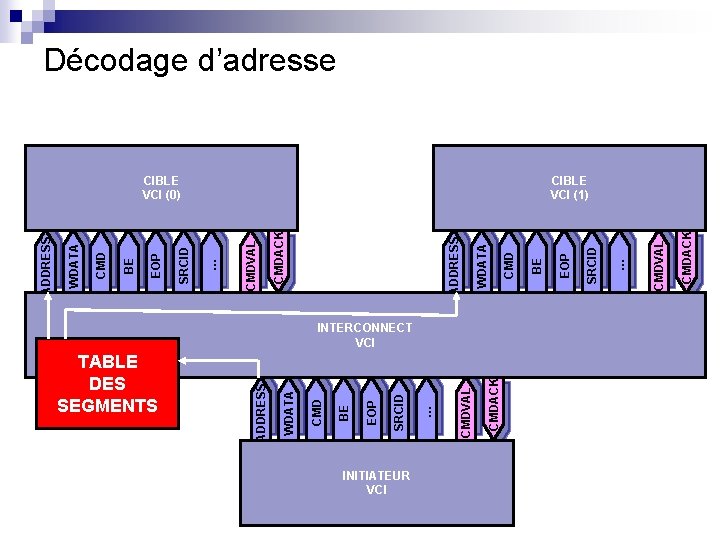

INITIATEUR VCI CMDACK CMDVAL … SRCID EOP BE CMD WDATA ADDRESS TABLE DES SEGMENTS INTERCONNECT VCI CMDACK CMDVAL … SRCID CIBLE VCI (0) EOP BE CMD WDATA ADDRESS CMDACK CMDVAL … SRCID EOP BE CMD WDATA ADDRESS Décodage d’adresse CIBLE VCI (1)

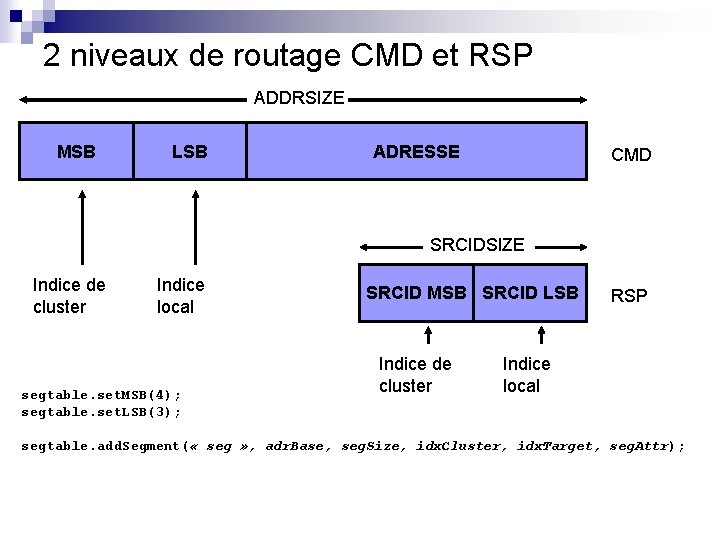

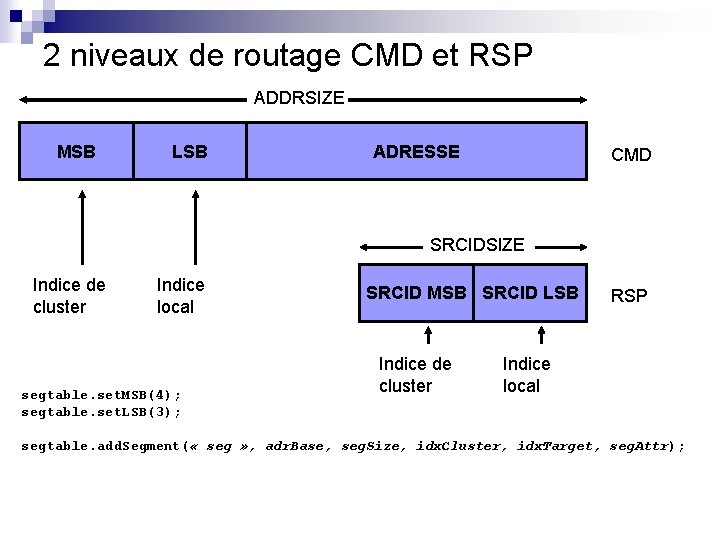

2 niveaux de routage CMD et RSP ADDRSIZE MSB LSB ADRESSE CMD SRCIDSIZE Indice de cluster Indice local segtable. set. MSB(4); segtable. set. LSB(3); SRCID MSB SRCID LSB Indice de cluster RSP Indice local segtable. add. Segment( « seg » , adr. Base, seg. Size, idx. Cluster, idx. Target, seg. Attr);

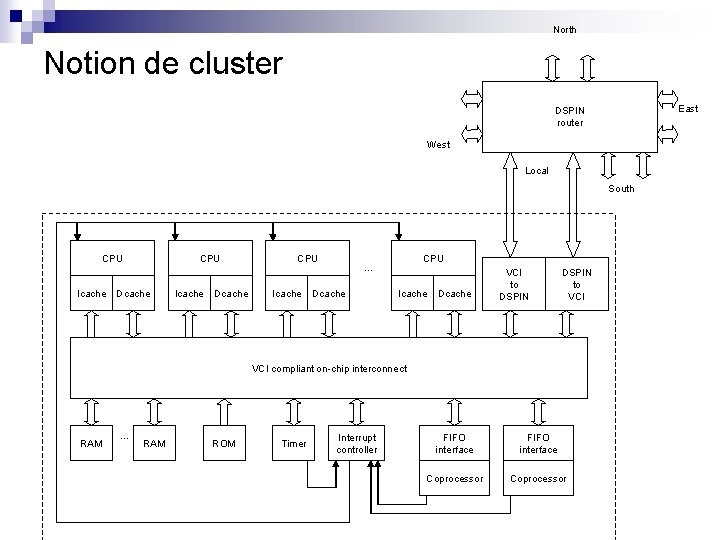

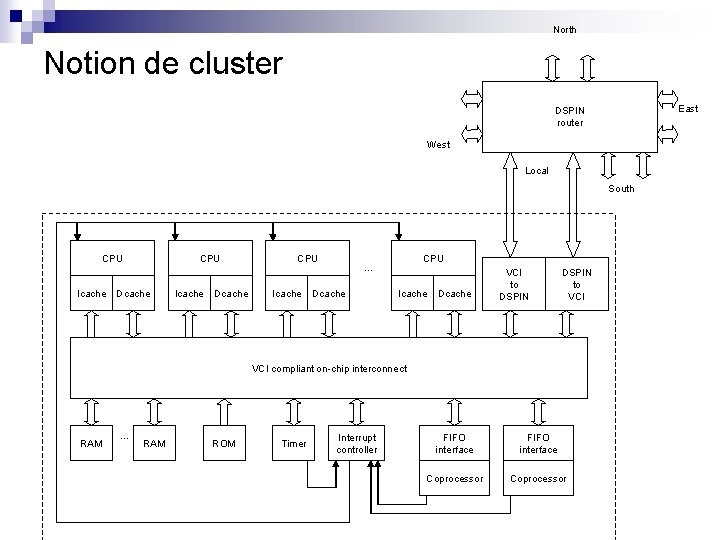

North Notion de cluster East DSPIN router West Local South CPU Icache CPU Dcache Icache Dcache CPU Icache CPU … Dcache Icache Dcache VCI to DSPIN to VCI compliant on-chip interconnect RAM … RAM ROM Timer Interrupt controller FIFO interface Coprocessor

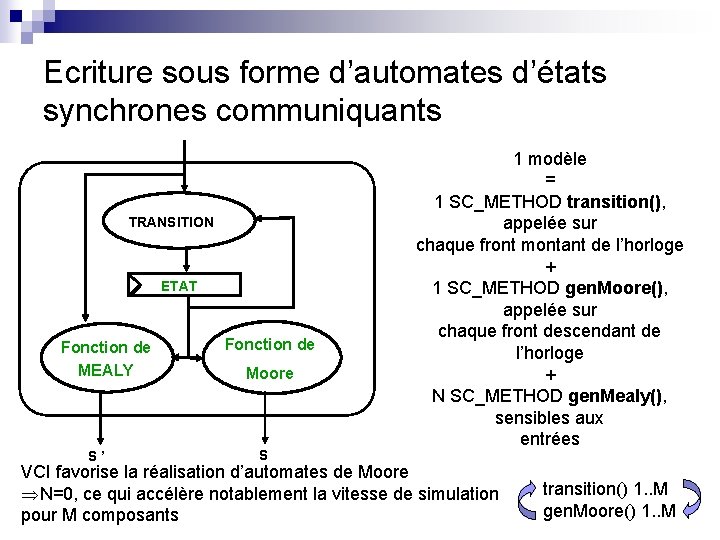

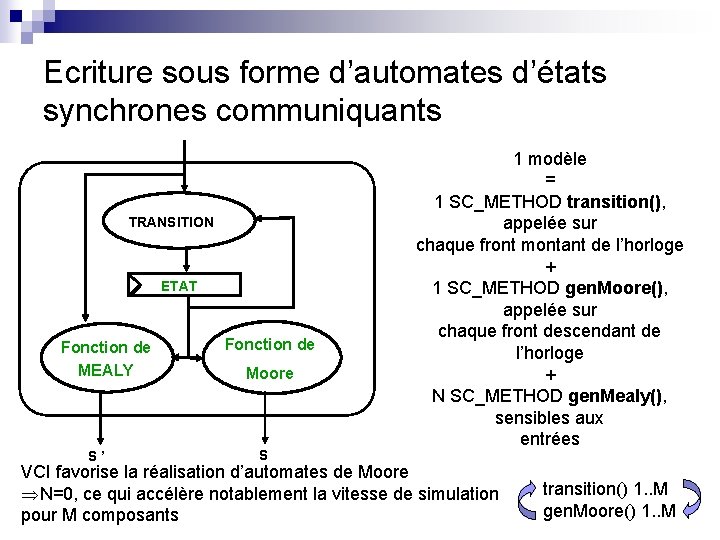

Ecriture sous forme d’automates d’états synchrones communiquants TRANSITION ETAT Fonction de MEALY S ’ Fonction de Moore S 1 modèle = 1 SC_METHOD transition(), appelée sur chaque front montant de l’horloge + 1 SC_METHOD gen. Moore(), appelée sur chaque front descendant de l’horloge + N SC_METHOD gen. Mealy(), sensibles aux entrées VCI favorise la réalisation d’automates de Moore ÞN=0, ce qui accélère notablement la vitesse de simulation pour M composants transition() 1. . M gen. Moore() 1. . M

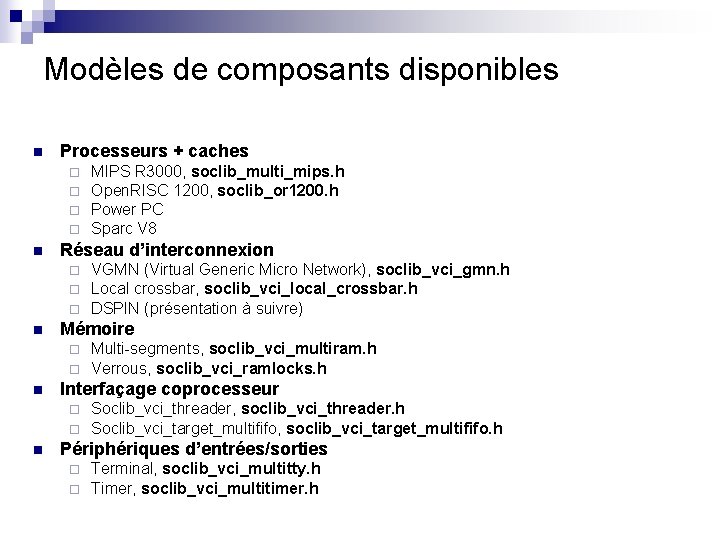

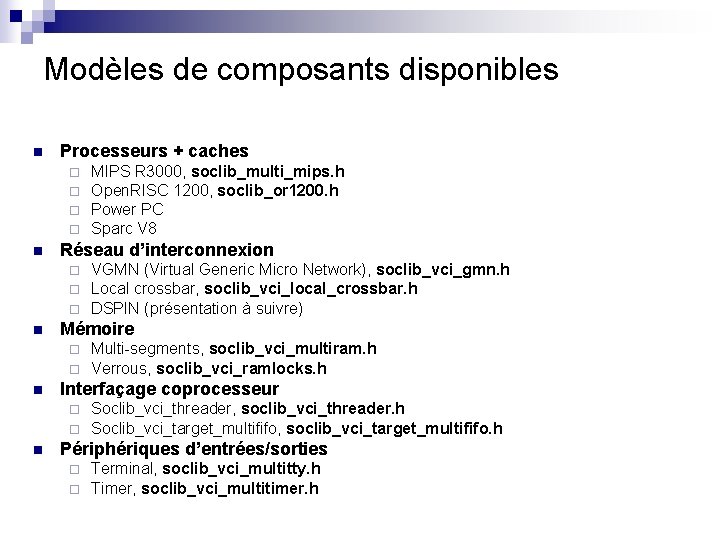

Modèles de composants disponibles n Processeurs + caches ¨ ¨ n Réseau d’interconnexion ¨ ¨ ¨ n Multi-segments, soclib_vci_multiram. h Verrous, soclib_vci_ramlocks. h Interfaçage coprocesseur ¨ ¨ n VGMN (Virtual Generic Micro Network), soclib_vci_gmn. h Local crossbar, soclib_vci_local_crossbar. h DSPIN (présentation à suivre) Mémoire ¨ ¨ n MIPS R 3000, soclib_multi_mips. h Open. RISC 1200, soclib_or 1200. h Power PC Sparc V 8 Soclib_vci_threader, soclib_vci_threader. h Soclib_vci_target_multififo, soclib_vci_target_multififo. h Périphériques d’entrées/sorties ¨ ¨ Terminal, soclib_vci_multitty. h Timer, soclib_vci_multitimer. h

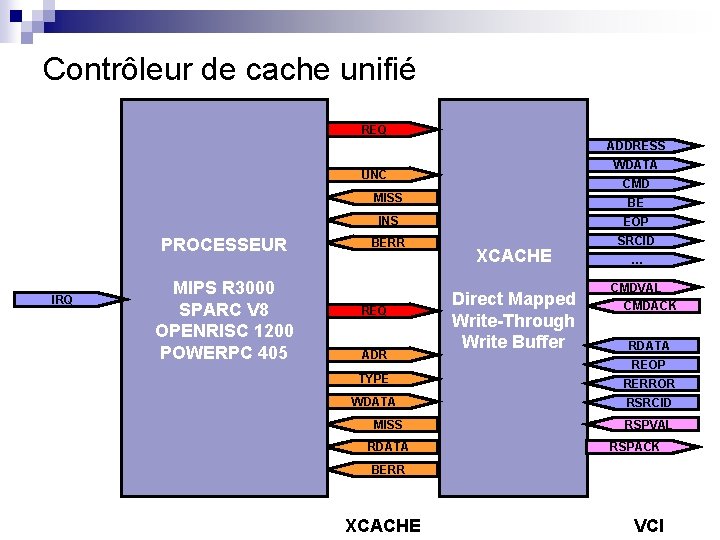

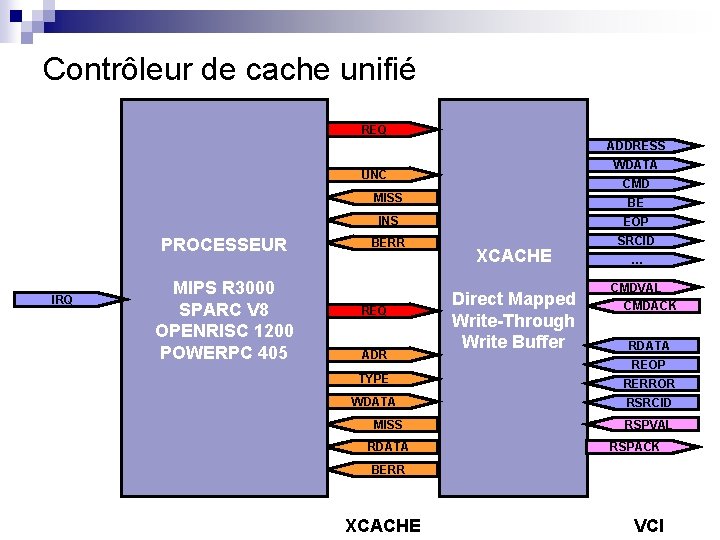

Contrôleur de cache unifié REQ ADDRESS WDATA UNC PROCESSEUR IRQ MIPS R 3000 SPARC V 8 OPENRISC 1200 POWERPC 405 CMD MISS BE INS EOP BERR SRCID REQ ADR XCACHE Direct Mapped Write-Through Write Buffer … CMDVAL CMDACK RDATA REOP TYPE RERROR WDATA RSRCID MISS RDATA RSPVAL RSPACK BERR XCACHE VCI

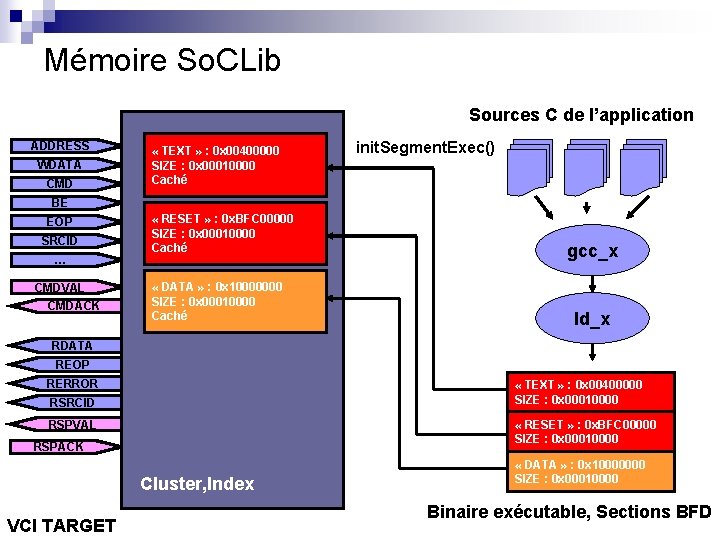

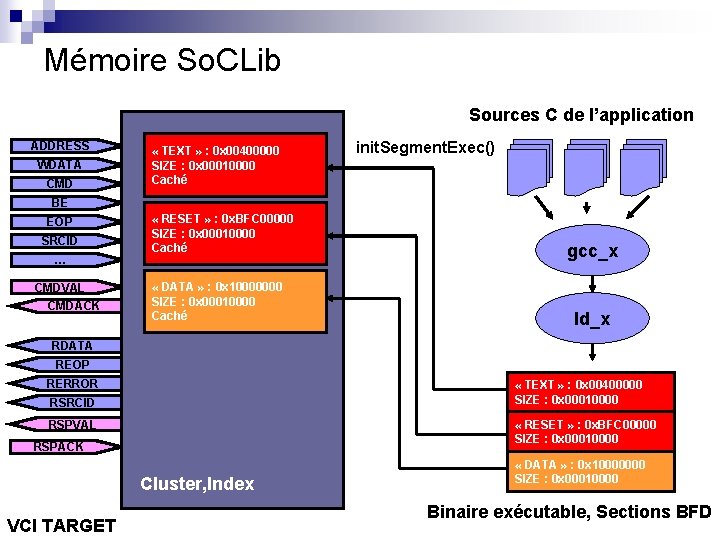

Mémoire So. CLib Sources C de l’application ADDRESS WDATA CMD « TEXT » : 0 x 00400000 SIZE : 0 x 00010000 Caché init. Segment. Exec() BE EOP SRCID … CMDVAL CMDACK « RESET » : 0 x. BFC 00000 SIZE : 0 x 00010000 Caché « DATA » : 0 x 10000000 SIZE : 0 x 00010000 Caché gcc_x ld_x RDATA REOP RERROR « TEXT » : 0 x 00400000 SIZE : 0 x 00010000 RSRCID RSPVAL « RESET » : 0 x. BFC 00000 SIZE : 0 x 00010000 RSPACK Cluster, Index VCI TARGET « DATA » : 0 x 10000000 SIZE : 0 x 00010000 Binaire exécutable, Sections BFD

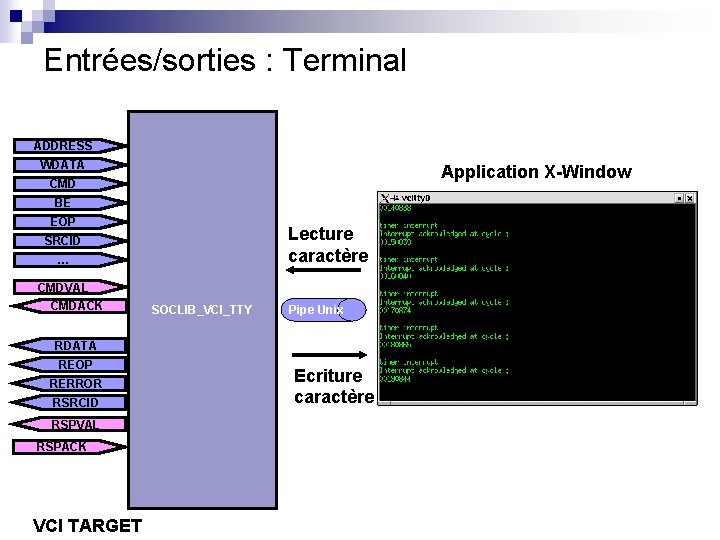

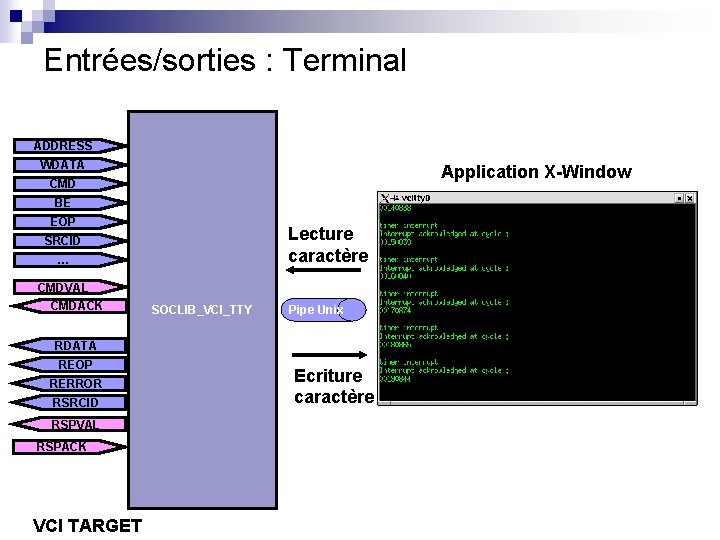

Entrées/sorties : Terminal ADDRESS WDATA Application X-Window CMD BE EOP Lecture caractère SRCID … CMDVAL CMDACK SOCLIB_VCI_TTY Pipe Unix RDATA REOP RERROR RSRCID RSPVAL RSPACK VCI TARGET Ecriture caractère

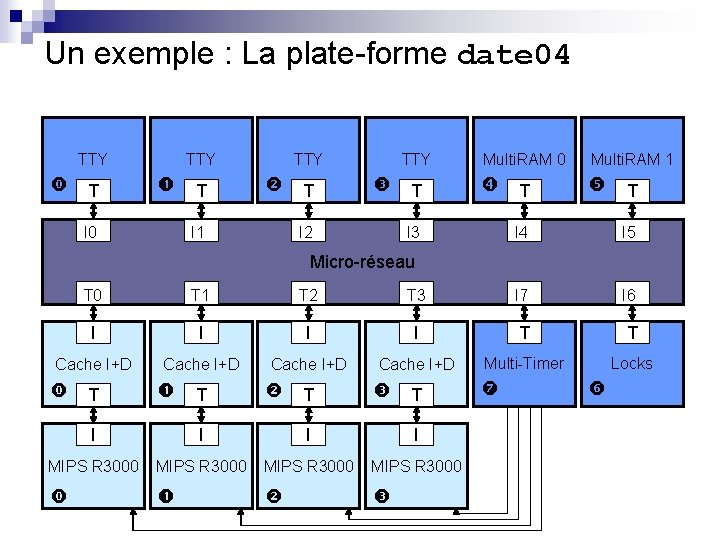

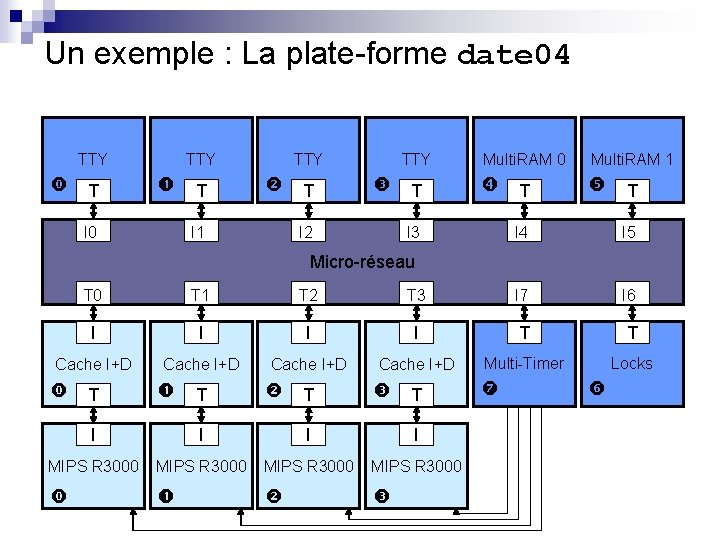

Un exemple : La plate-forme date 04 TTY T TTY I 1 I 0 T TTY I 2 T Multi. RAM 0 Multi. RAM 1 I 3 T T I 4 I 5 Micro-réseau T 0 T 1 T 2 T 3 I 7 I 6 I I T T Cache I+D Multi-Timer Locks T T I I MIPS R 3000

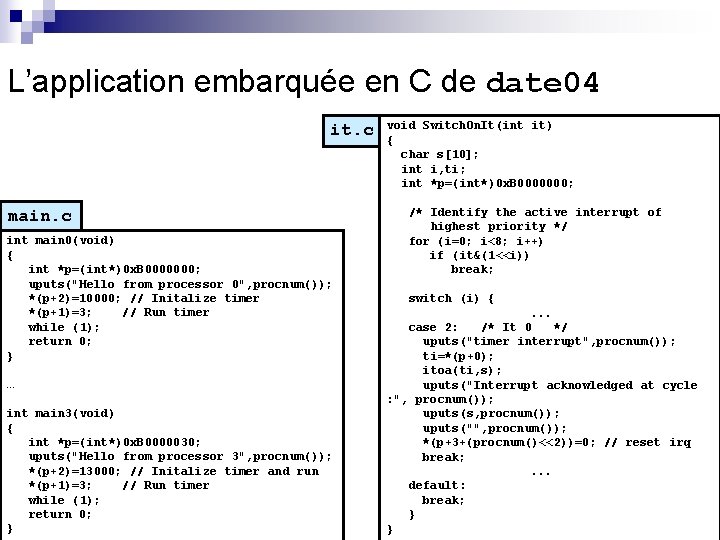

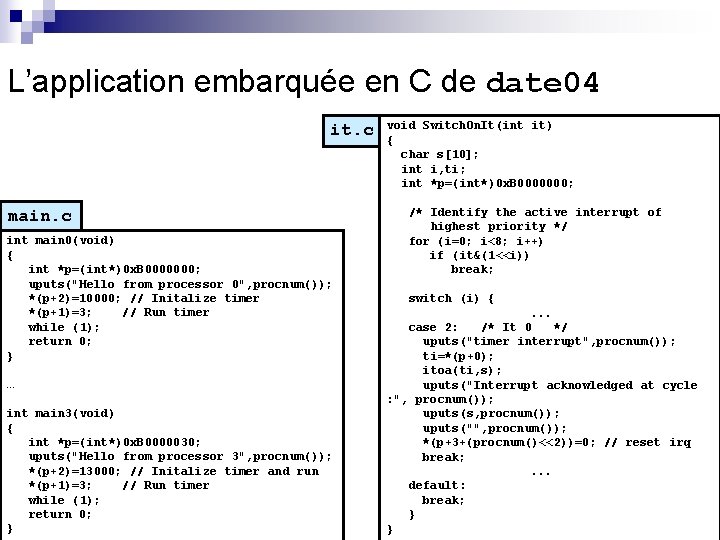

L’application embarquée en C de date 04 it. c main. c int main 0(void) { int *p=(int*)0 x. B 0000000; uputs("Hello from processor 0", procnum()); *(p+2)=10000; // Initalize timer *(p+1)=3; // Run timer while (1); return 0; } … int main 3(void) { int *p=(int*)0 x. B 0000030; uputs("Hello from processor 3", procnum()); *(p+2)=13000; // Initalize timer and run *(p+1)=3; // Run timer while (1); return 0; } void Switch. On. It(int it) { char s[10]; int i, ti; int *p=(int*)0 x. B 0000000; /* Identify the active interrupt of highest priority */ for (i=0; i<8; i++) if (it&(1<<i)) break; switch (i) {. . . case 2: /* It 0 */ uputs("timer interrupt", procnum()); ti=*(p+0); itoa(ti, s); uputs("Interrupt acknowledged at cycle : ", procnum()); uputs(s, procnum()); uputs("", procnum()); *(p+3+(procnum()<<2))=0; // reset irq break; . . . default: break; } }

Exécution de la simulation

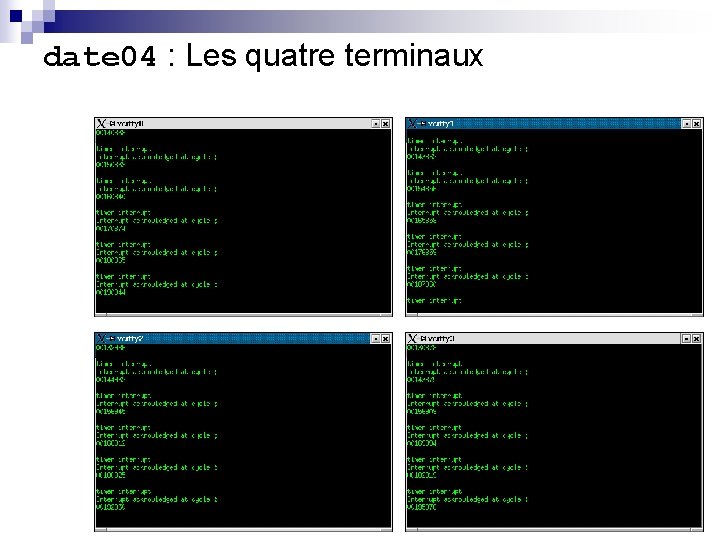

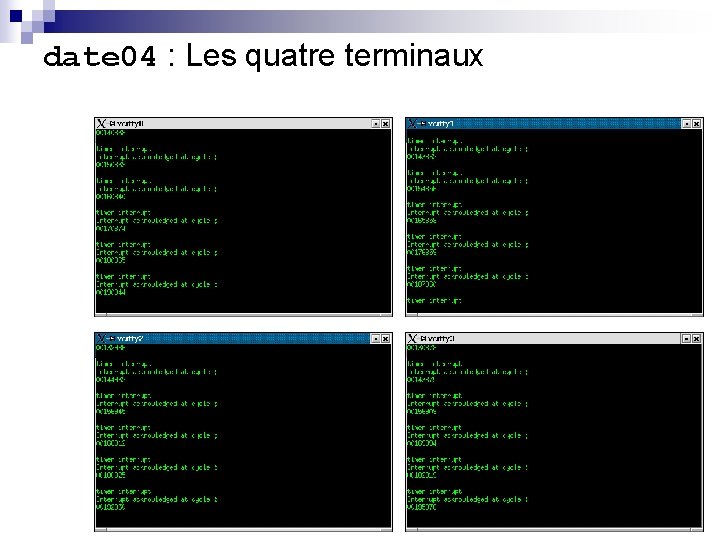

date 04 : Les quatre terminaux

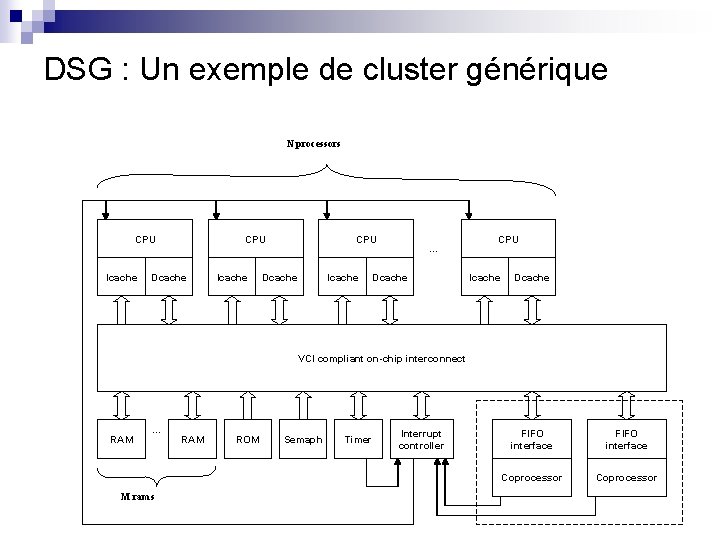

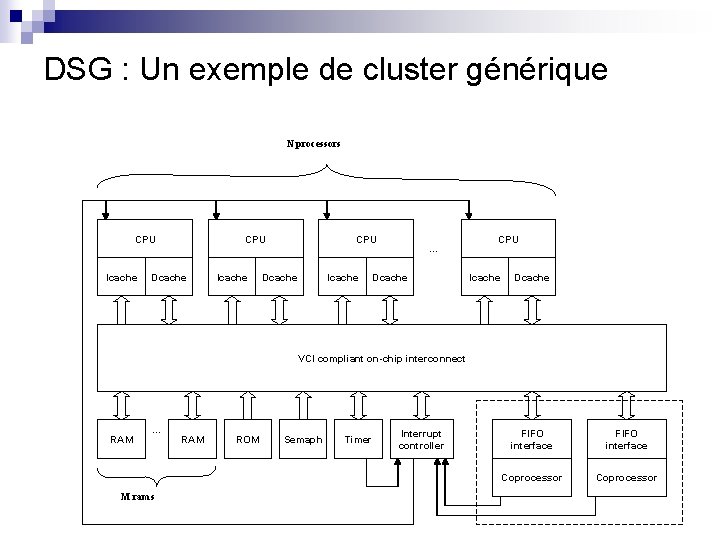

Outils associés n n System. Cass, Simulateur à ordonnancement statique, 7 fois plus rapide que System. C Soc. View, Outil de mise au point des modèles et des plates-formes DSG, outil de génération automatique de plate-forme et de déploiement de l’application multi-thread « Serendipity » , En cours de développement : Simulateur multi-niveaux d’abstraction : commutation «à chaud» entre simulation TLM/T et CABA.

DSG : Un exemple de cluster générique N processors CPU Icache CPU Dcache Icache … Dcache CPU Icache Dcache VCI compliant on-chip interconnect RAM … M rams RAM ROM Semaph Timer Interrupt controller FIFO interface Coprocessor

Conclusion n Bibliothèque opérationnelle de modèles de composants n Environnement, bibliothèque et outils disponibles sur http: //soclib. lip 6. fr n Méthode simplifiée de déploiement d’une application logicielle parallèle sur une plate-forme matérielle générique par l’emploi de générateurs de systèmes n Réalisation d’un CI système sur puce, Ao. C, s’appuyant sur les principes de So. CLib n Point chaud : La conception d’un système embarqué opérationnel revient à trouver un placement optimal pour ¨ ¨ ¨ les threads de l’application embarquée sur les processeurs les canaux de communicationsur les bancs mémoire physique les coprocesseurs matériels dans l’espace mémoire partagé

Contacts dans l’équipe So. CLib du LIP 6 n n n Direction du projet Soc. Lib, alain. greiner@lip 6. fr Coordination, francois. pecheux@lip 6. fr System. CASS, richard. buchmann@lip 6. fr MUTEK, franck. wajsburt@lip 6. fr, pascal. gomez@lip 6. fr Modélisation TLM/T, emmanuel. viaud@lip 6. fr Déploiement de plates-formes, So. CView, wahid. bahroun@lip 6. fr Processeur Réseau, daniela. genius@lip 6. fr, etienne. faure@lip 6. fr, Modèles Interconnect, herve. charlery@lip 6. fr, laurent. mortiez@lip 6. fr, Modèle Processeur Java, maxime. palus@lip 6. fr Modèle Processeur Mips, pirouz. bazargan@lip 6. fr, mathieu. rosiere@lip 6. fr Micro-réseau DSPIN alain. greiner@lip 6. fr, hamed. sheybanirad@lip 6. fr Modèle Processeur test mounir. benabdenbi@lip 6. fr, matthieu. tuna@lip 6. fr