Modeling with Constraint Logic Programming Ulf Nilsson Dept

![Examples: Cardinality ? - sat(A+B), sat(card ([1], [A, B])). sat(A== B) ? - sat(A=<B), Examples: Cardinality ? - sat(A+B), sat(card ([1], [A, B])). sat(A== B) ? - sat(A=<B),](https://slidetodoc.com/presentation_image/bb252ec89768ed3565fac6b29bceaeb5/image-10.jpg)

![Example ? - nswitch(S, D, G), labeling([S, D, G]). D = 0, G = Example ? - nswitch(S, D, G), labeling([S, D, G]). D = 0, G =](https://slidetodoc.com/presentation_image/bb252ec89768ed3565fac6b29bceaeb5/image-12.jpg)

- Slides: 16

Modeling with Constraint Logic Programming Ulf Nilsson Dept of Computer and Information Science Linköping University

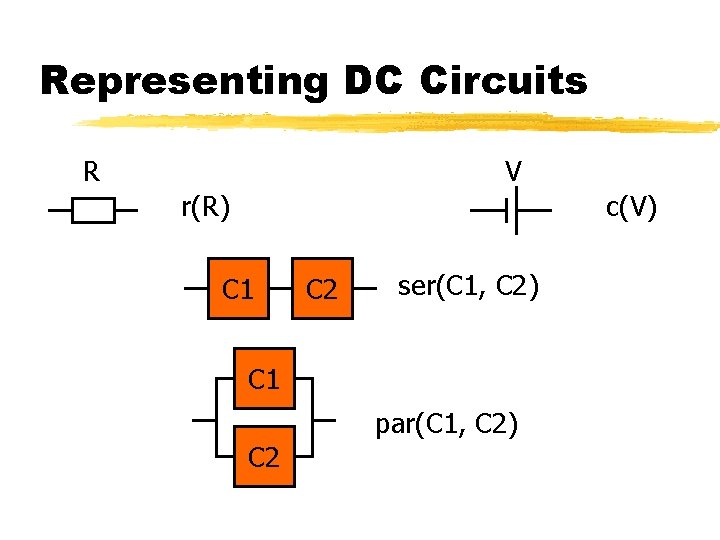

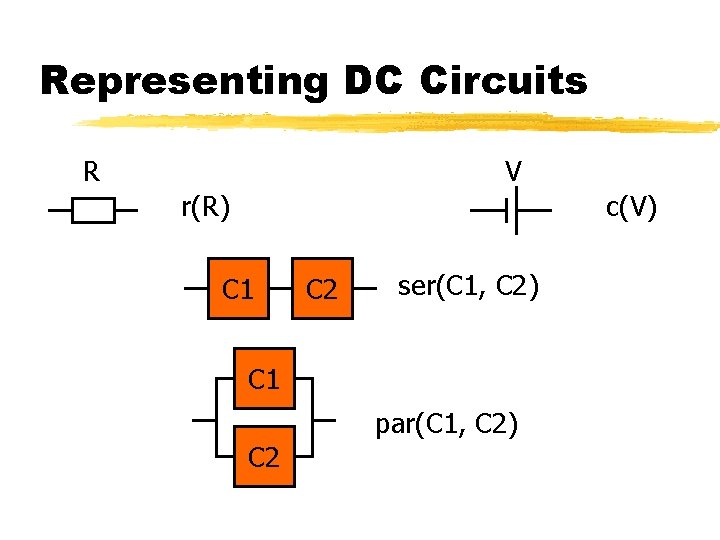

Representing DC Circuits R V r(R) c(V) C 1 C 2 ser(C 1, C 2) C 1 C 2 par(C 1, C 2)

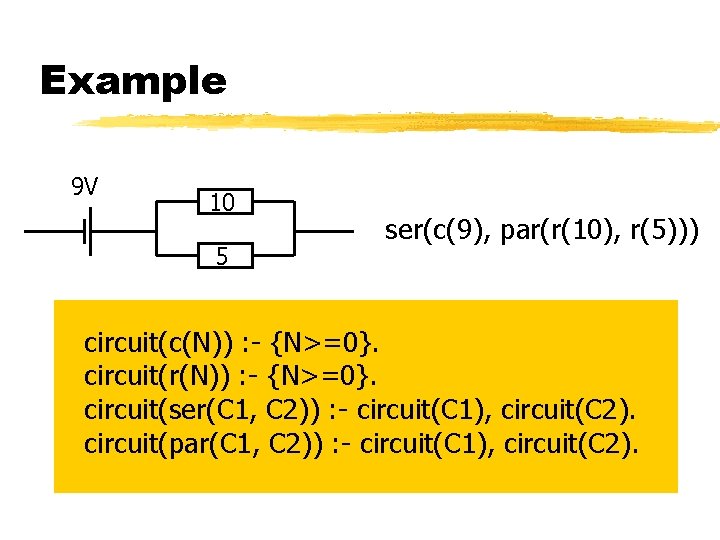

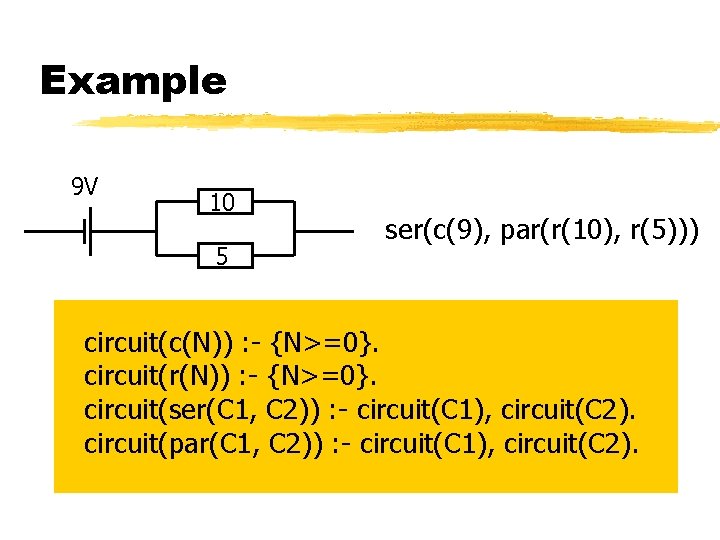

Example 9 V 10 5 ser(c(9), par(r(10), r(5))) circuit(c(N)) : - {N>=0}. circuit(r(N)) : - {N>=0}. circuit(ser(C 1, C 2)) : - circuit(C 1), circuit(C 2). circuit(par(C 1, C 2)) : - circuit(C 1), circuit(C 2).

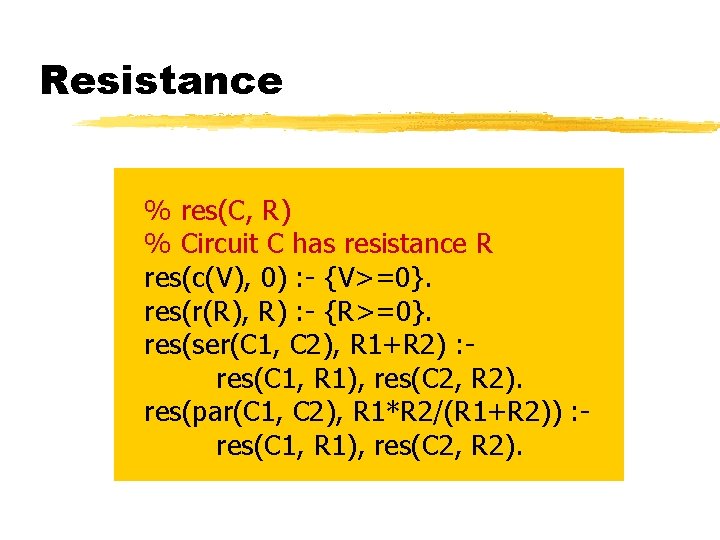

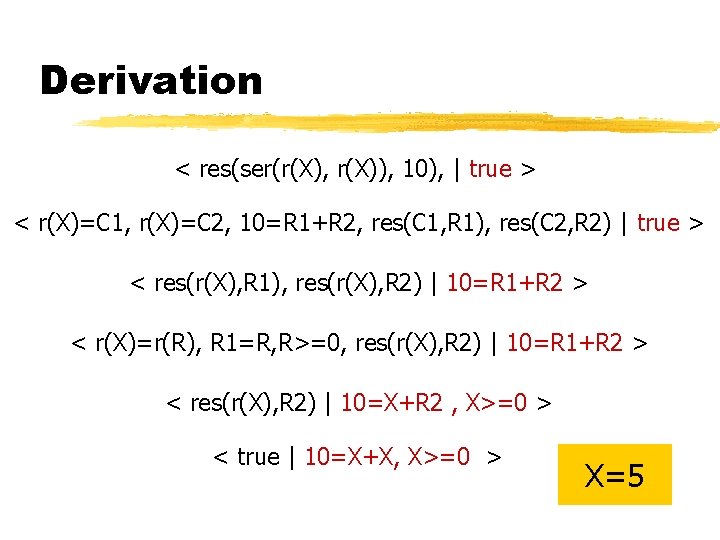

Resistance % res(C, R) % Circuit C has resistance R res(c(V), 0) : - {V>=0}. res(r(R), R) : - {R>=0}. res(ser(C 1, C 2), R 1+R 2) : res(C 1, R 1), res(C 2, R 2). res(par(C 1, C 2), R 1*R 2/(R 1+R 2)) : res(C 1, R 1), res(C 2, R 2).

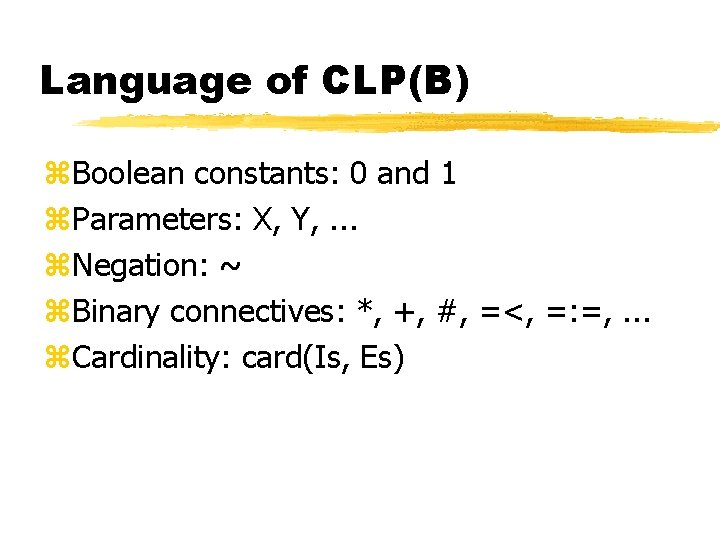

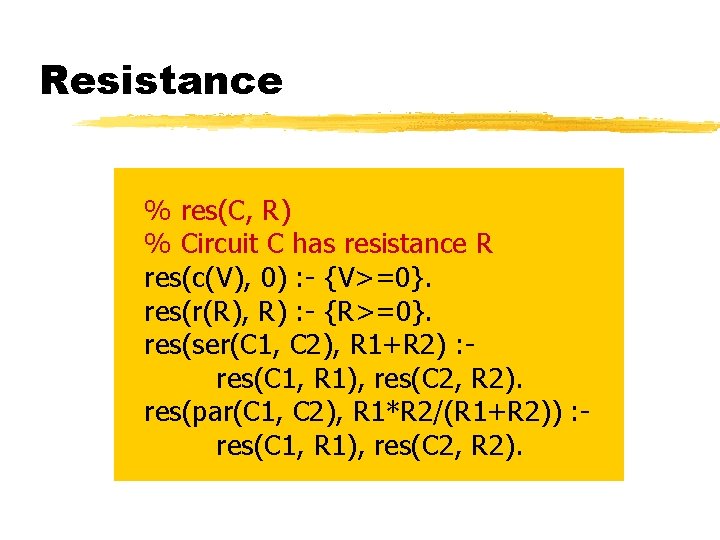

Derivation < res(ser(r(X), r(X)), 10), | true > < r(X)=C 1, r(X)=C 2, 10=R 1+R 2, res(C 1, R 1), res(C 2, R 2) | true > < res(r(X), R 1), res(r(X), R 2) | 10=R 1+R 2 > < r(X)=r(R), R 1=R, R>=0, res(r(X), R 2) | 10=R 1+R 2 > < res(r(X), R 2) | 10=X+R 2 , X>=0 > < true | 10=X+X, X>=0 > X=5

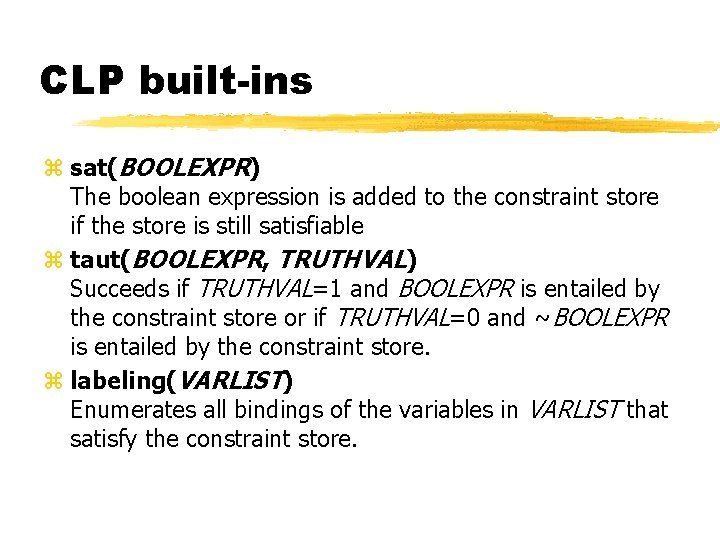

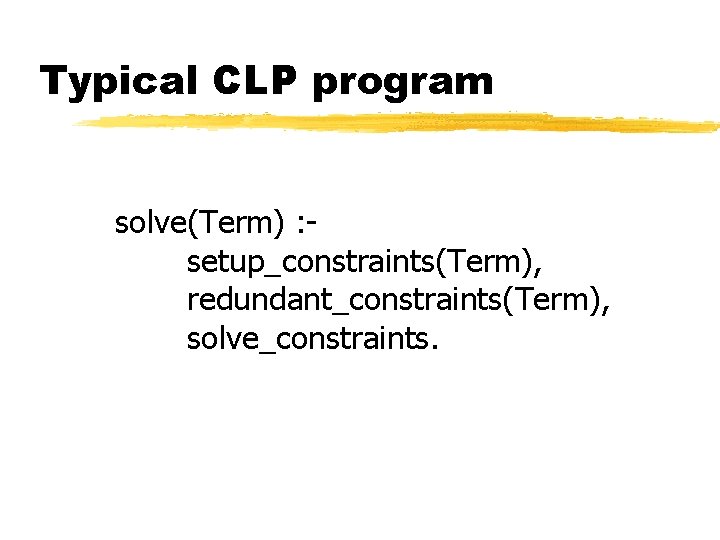

Typical CLP program solve(Term) : setup_constraints(Term), redundant_constraints(Term), solve_constraints.

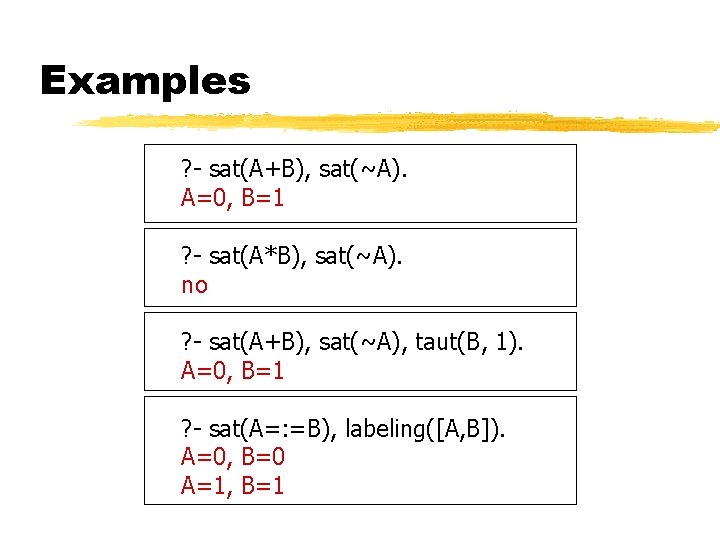

Language of CLP(B) z. Boolean constants: 0 and 1 z. Parameters: X, Y, . . . z. Negation: ~ z. Binary connectives: *, +, #, =<, =: =, . . . z. Cardinality: card(Is, Es)

CLP built-ins z sat(BOOLEXPR) The boolean expression is added to the constraint store if the store is still satisfiable z taut(BOOLEXPR, TRUTHVAL) Succeeds if TRUTHVAL=1 and BOOLEXPR is entailed by the constraint store or if TRUTHVAL=0 and ~BOOLEXPR is entailed by the constraint store. z labeling(VARLIST) Enumerates all bindings of the variables in VARLIST that satisfy the constraint store.

Examples ? - sat(A+B), sat(~A). A=0, B=1 ? - sat(A*B), sat(~A). no ? - sat(A+B), sat(~A), taut(B, 1). A=0, B=1 ? - sat(A=: =B), labeling([A, B]). A=0, B=0 A=1, B=1

![Examples Cardinality satAB satcard 1 A B satA B satAB Examples: Cardinality ? - sat(A+B), sat(card ([1], [A, B])). sat(A== B) ? - sat(A=<B),](https://slidetodoc.com/presentation_image/bb252ec89768ed3565fac6b29bceaeb5/image-10.jpg)

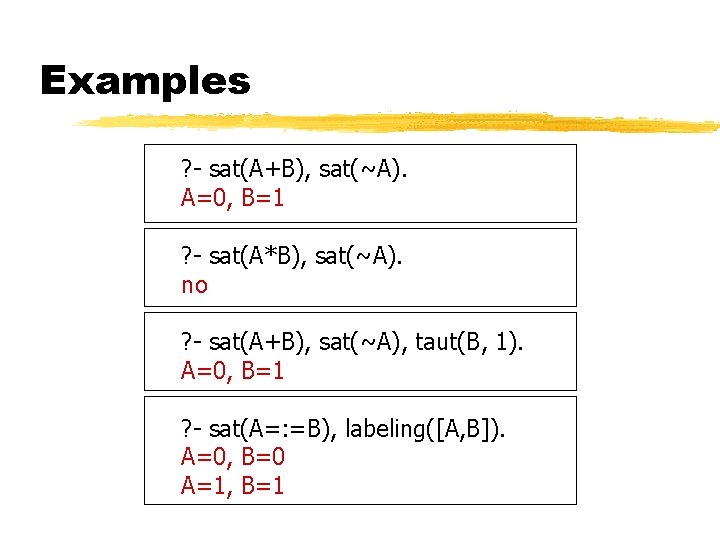

Examples: Cardinality ? - sat(A+B), sat(card ([1], [A, B])). sat(A== B) ? - sat(A=<B), sat(card([0 -1], [A, B])). A=0

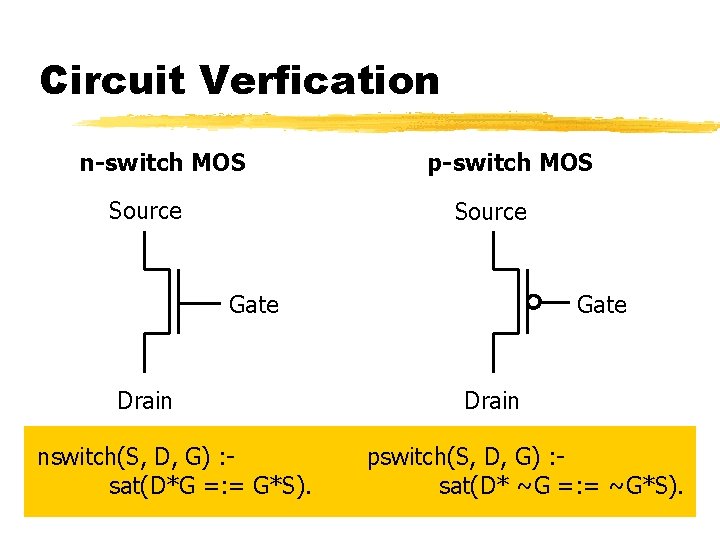

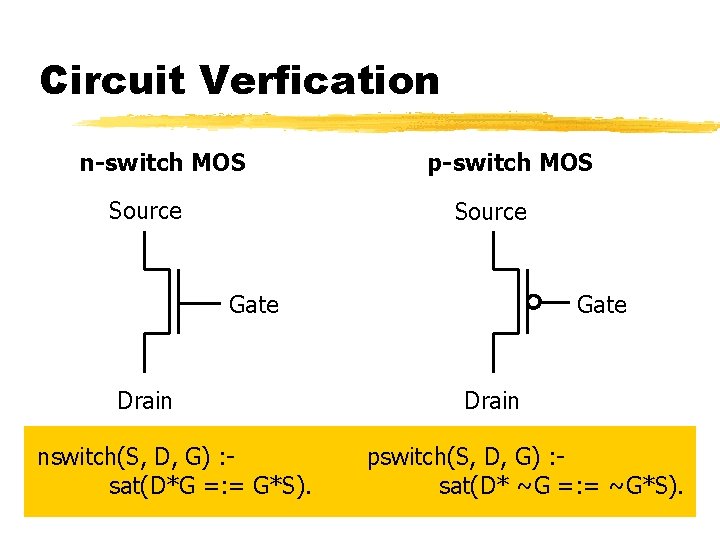

Circuit Verfication n-switch MOS Source p-switch MOS Source Gate Drain nswitch(S, D, G) : sat(D*G =: = G*S). Gate Drain pswitch(S, D, G) : sat(D* ~G =: = ~G*S).

![Example nswitchS D G labelingS D G D 0 G Example ? - nswitch(S, D, G), labeling([S, D, G]). D = 0, G =](https://slidetodoc.com/presentation_image/bb252ec89768ed3565fac6b29bceaeb5/image-12.jpg)

Example ? - nswitch(S, D, G), labeling([S, D, G]). D = 0, G = 0, S = 0 D = 1, G = 0, S = 0 D = 0, G = 1, S = 0 D = 0, G = 0, S = 1 D = 1, G = 1, S = 1

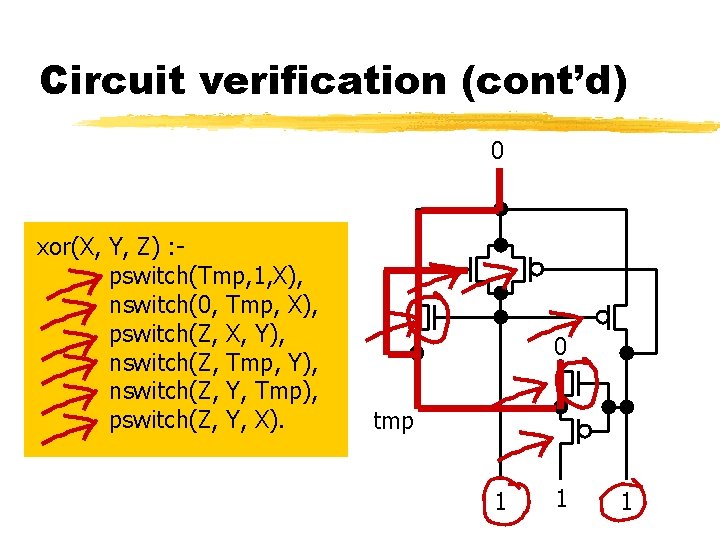

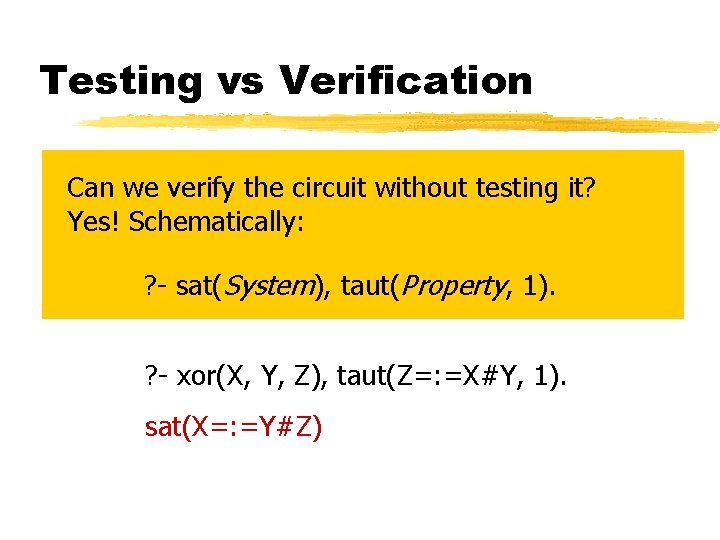

Circuit verification (cont’d) 0 z xor(X, Y, Z) : pswitch(Tmp, 1, X), nswitch(0, Tmp, X), pswitch(Z, X, Y), nswitch(Z, Tmp, Y), nswitch(Z, Y, Tmp), pswitch(Z, Y, X). 0 tmp 1 y 1 1 x

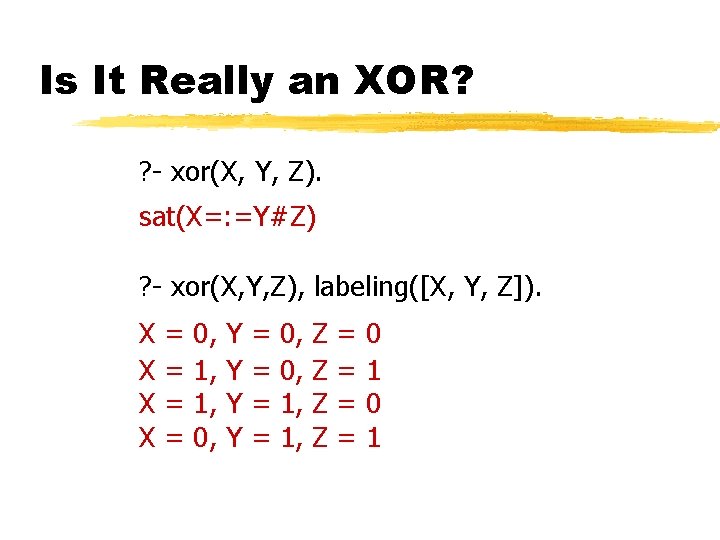

Is It Really an XOR? ? - xor(X, Y, Z). sat(X=: =Y#Z) ? - xor(X, Y, Z), labeling([X, Y, Z]). X X = = 0, 1, 1, 0, Y Y = = 0, 0, 1, 1, Z Z = = 0 1

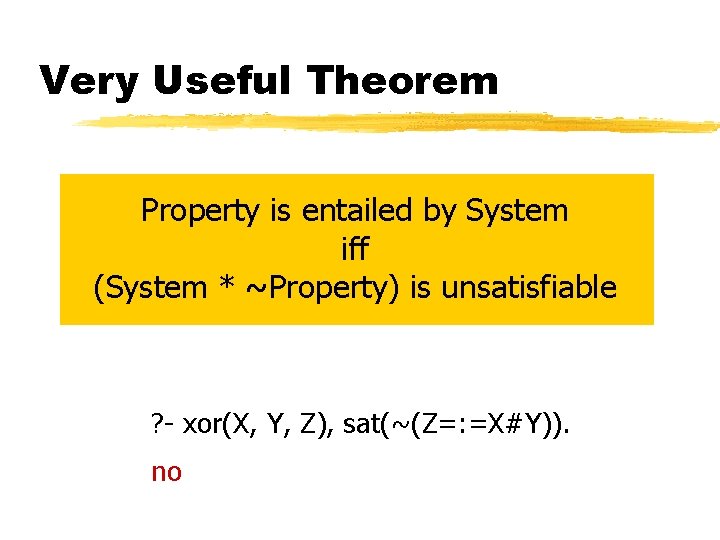

Testing vs Verification Can we verify the circuit without testing it? Yes! Schematically: ? - sat(System), taut(Property, 1). ? - xor(X, Y, Z), taut(Z=: =X#Y, 1). sat(X=: =Y#Z)

Very Useful Theorem Property is entailed by System iff (System * ~Property) is unsatisfiable ? - xor(X, Y, Z), sat(~(Z=: =X#Y)). no