Modeling Languages and Abstract Models Giovanni De Micheli

Modeling Languages and Abstract Models Giovanni De Micheli Integrated Systems Laboratory This presentation can be used for non-commercial purposes as long as this note and the copyright footers are not removed © Giovanni De Micheli – All rights reserved

Module 1 u Objective s Modeling requirements in systems s Modeling styles (c) Giovanni De Micheli 2

Electronic systems u A system is a combination of: s Hardware platform: t s Processors, memories, transducers Software : t Application and system software u Attributes: s Application domain t s Integration level t s Computing, communication, consumer Chip, board, distributed/networked Function t Autonomous, embedded (c) Giovanni De Micheli 3

Trends and challenges u Design increasingly more complex systems under higher time to market pressure s Raise level of abstraction u Design starts are mainly for embedded system applications u Use and re-use of high-level components s Processors, controllers, embedded memories u Support concurrent Hw/Sw development s System customization via embedded software u Support automated synthesis and verification (c) Giovanni De Micheli 4

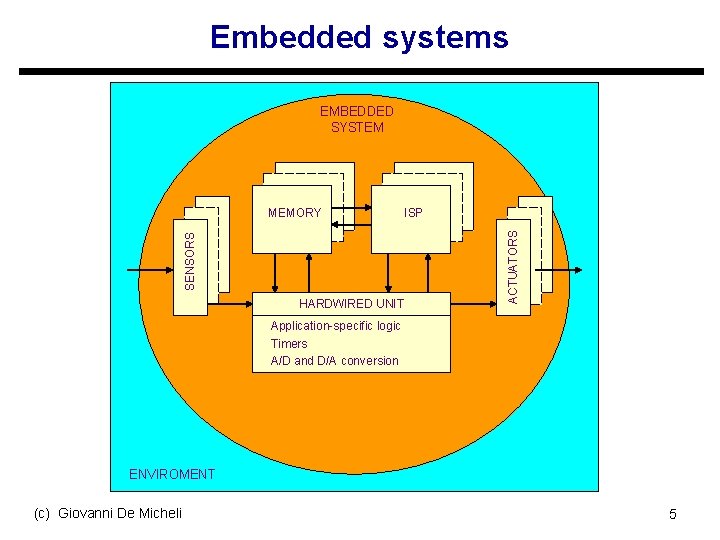

Embedded systems EMBEDDED SYSTEM HARDWIRED UNIT ISP ACTUATORS SENSORS MEMORY Application-specific logic Timers A/D and D/A conversion ENVIROMENT (c) Giovanni De Micheli 5

Embedded system requirements u Reactive systems: s The system never stops s The system responds to signals produced by the environment u Real-time systems: s Timing constraints on task execution s Hard and soft constraints (c) Giovanni De Micheli 6

System modeling u Represent system functions while abstracting away unnecessary details s Software programming languages s Hardware description languages s Flow and state-based diagrams s Schematics u No golden solution s System heterogeneity (c) Giovanni De Micheli 7

The limits of my language mean the limits of my world Wittgenstein (c) Giovanni De Micheli 8

Circuit Modeling u Formal methods: s Models in hardware languages s Flow and state diagrams s Schematics u Informal methods: s Principles of operations s Natural-language descriptions (c) Giovanni De Micheli 9

Hardware versus software models u Hardware: s Parallel execution s I/O ports, building blocks s Exact event timing is very important u Software: s Sequential execution (usually) s Structural information less important s Exact event timing is not important (c) Giovanni De Micheli 10

Hardware Description Languages u Specialized languages with hardware design support u Multi-level abstraction: s Behavior, RTL, structural u Support for simulation and synthesis s … but synthesis came in later (c) Giovanni De Micheli 11

Software programming languages u Software programming languages (C) can model functional behavior: s Example: processor models u Software language models support marginally design and synthesis: s s Unless extensions and overloading is used Example: System. C u Different paradigms for hardware and software u Strong trend in bridging the gap between software programming languages and HDLs (c) Giovanni De Micheli 12

Module 2 u Objectives s Language analysys s Procedural languages (Verilog) s Declarative languages (Silage) s Object-oriented languages (System. C) (c) Giovanni De Micheli 13

Language analysis u Syntax: s External look of a language s Specified by a grammar u Semantics: s Meaning of a language s Different ways of specifying it u Pragmatics: s Other aspects of the language s Implementation issues (c) Giovanni De Micheli 14

Language analysis u Procedural languages: s Specify the action by a sequence of steps s Examples: C, Pascal, VHDL, Verilog u Declarative languages: s Specify the problem by a set of declaration s Example: Prolog (c) Giovanni De Micheli 15

Language analysis u Imperative Semantics: s Dependence between the assignments and the values that variables can take s Examples C, Pascal u Applicative semantics: s Based on function invocation s Examples: Lisp, Silage (c) Giovanni De Micheli 16

Hardware languages and views u Physical view: s Physical layout languages s Declarative or procedural u Structural view: s Structural languages s Declarative (with some procedural features) u Behavioral view: s Behavioral languages s Mainly procedural (c) Giovanni De Micheli 17

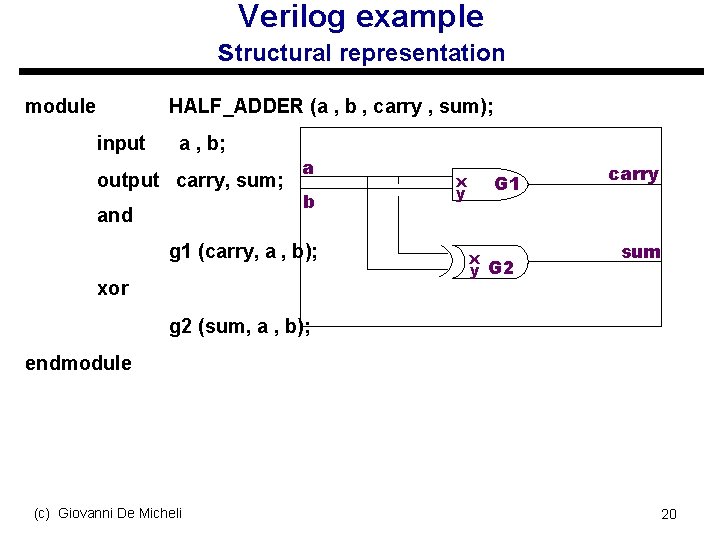

Structural view u Composition of blocks u Encoding of a schematic u Incidence structure u Hierarchy and instantiation u HDL examples: s VHDL, Verilog HDL, … (c) Giovanni De Micheli 18

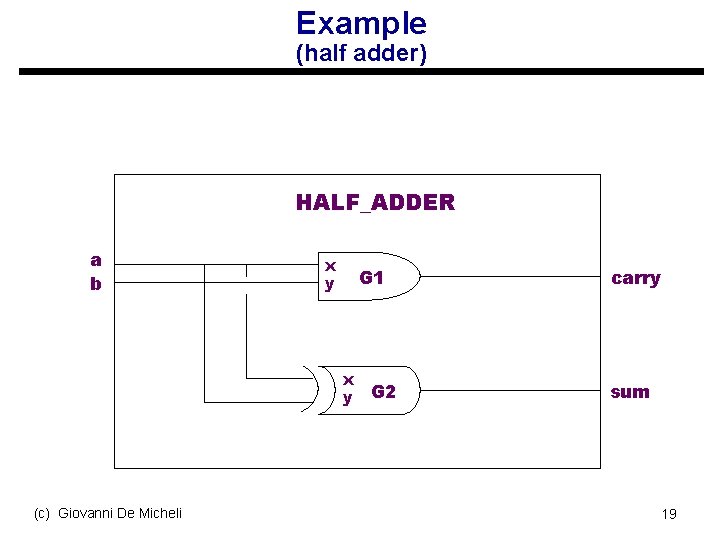

Example (half adder) HALF_ADDER a b x y G 1 x y (c) Giovanni De Micheli G 2 carry sum 19

Verilog example structural representation module HALF_ADDER (a , b , carry , sum); input a , b; output carry, sum; and a b g 1 (carry, a , b); xor x y G 1 x y G 2 carry sum g 2 (sum, a , b); endmodule (c) Giovanni De Micheli 20

Behavioral view procedural languages u Set of tasks with partial order: s Architectural-level: t s Tasks: generic operations. Logic-level: t Tasks: logic functions. u Independent of implementation choices u HDL examples: s VHDL, Verilog HDL, . . . (c) Giovanni De Micheli 21

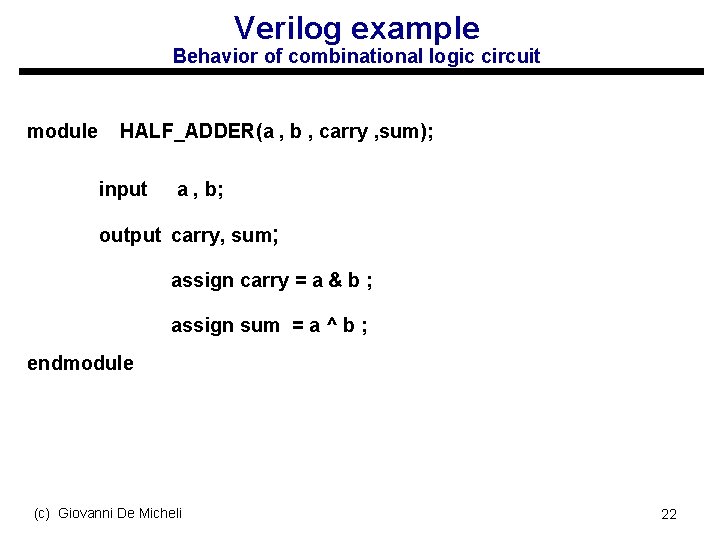

Verilog example Behavior of combinational logic circuit module HALF_ADDER(a , b , carry , sum); input a , b; output carry, sum; assign carry = a & b ; assign sum = a ^ b ; endmodule (c) Giovanni De Micheli 22

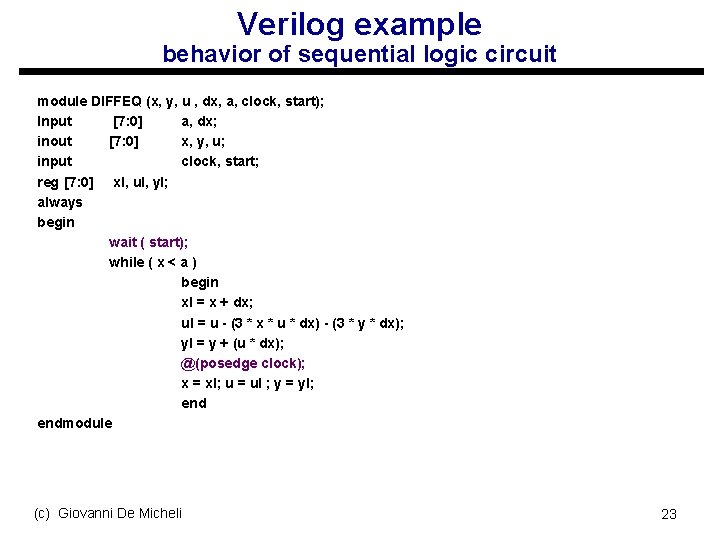

Verilog example behavior of sequential logic circuit module DIFFEQ (x, y, u , dx, a, clock, start); Input [7: 0] a, dx; inout [7: 0] x, y, u; input clock, start; reg [7: 0] xl, ul, yl; always begin wait ( start); while ( x < a ) begin xl = x + dx; ul = u - (3 * x * u * dx) - (3 * y * dx); yl = y + (u * dx); @(posedge clock); x = xl; u = ul ; y = yl; endmodule (c) Giovanni De Micheli 23

Timing interpretation for design u Operations are synchronized to a clock s By using a wait (or @) command u Wait and @ statements delimit clock boundaries u Clock is a parameter of the model: s Model is updated at each clock cycle (c) Giovanni De Micheli 24

Main languages at structural/behavioral level u Often called register-transfer level (RTL) languages u Verilog: s C-like, easy to write, harder to read s Motivated by high design productivity u VHDL s Verbose, longer to write, easy to read s Motivated by large system design (c) Giovanni De Micheli 25

Behavioral view declarative languages u Combinational circuits: s Set of untimed assignments. s Each assignment represents a virtual logic gate s Very similar to procedural models u Sequential circuits: s Use timing annotation for delayed signals s Set of assignments over (delayed) variables (c) Giovanni De Micheli 26

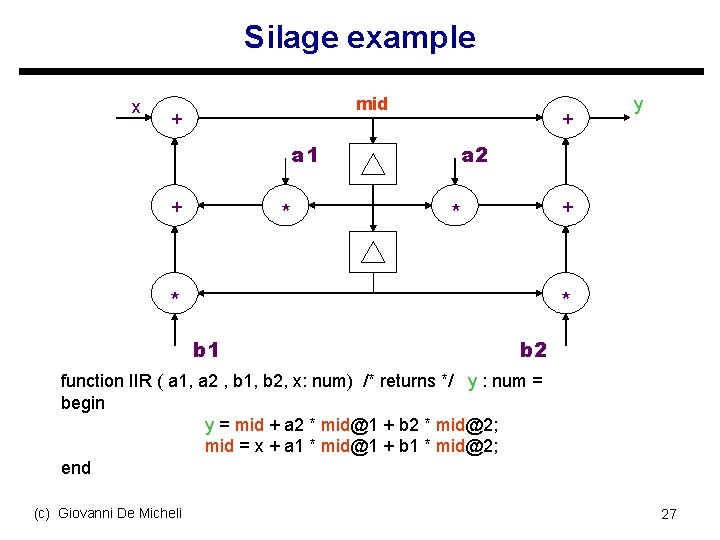

Silage example x mid + + a 1 + * y a 2 + * * * b 1 b 2 function IIR ( a 1, a 2 , b 1, b 2, x: num) /* returns */ y : num = begin y = mid + a 2 * mid@1 + b 2 * mid@2; mid = x + a 1 * mid@1 + b 1 * mid@2; end (c) Giovanni De Micheli 27

Hardware primitives u Hardware basic units: s Logic gates s Registers s Black-boxes t e. g. , Complex units, RAMs u Connections u Ports (c) Giovanni De Micheli 28

Semantics of variables u Variables are implemented in hardware by: s Registers s Wires u The hardware can store information or not u Two cases: s Combinational circuits t s Resolution policy for multiple assignment to a variable Sequential circuits t Variables keep values until reassigned (c) Giovanni De Micheli 29

Main languages at system level u System. C s Object-oriented C++ hardware library u System Verilog: s Extension of Verilog to system level s Support for system-level verification u Open. CL s Framework for heterogeneous system design s Interface to parallel computing (c) Giovanni De Micheli 30

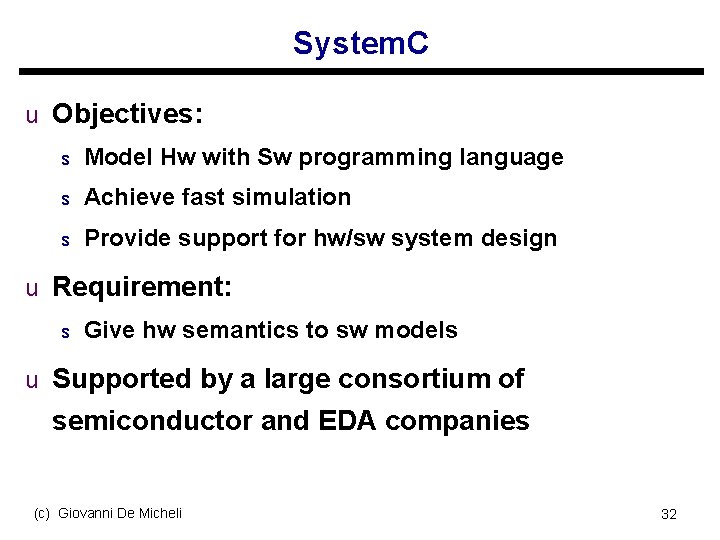

System. C u Objectives: s Model Hw with Sw programming language s Achieve fast simulation s Provide support for hw/sw system design u Requirement: s Give hw semantics to sw models u Supported by a large consortium of semiconductor and EDA companies (c) Giovanni De Micheli 32

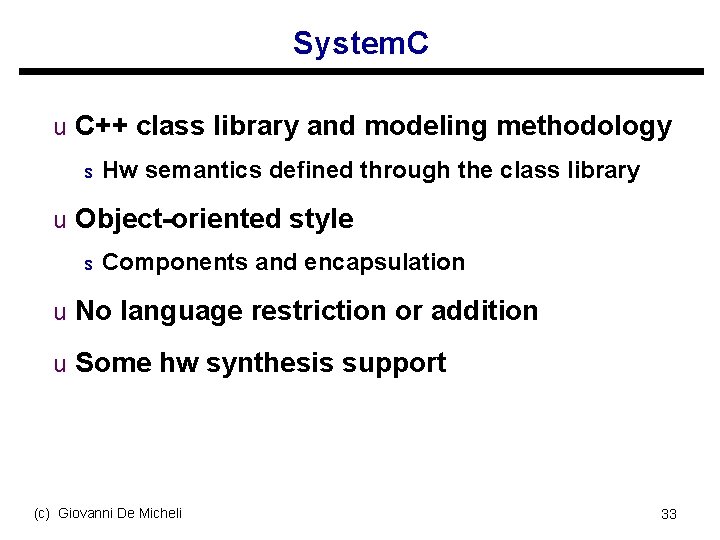

System. C u C++ class library and modeling methodology s Hw semantics defined through the class library u Object-oriented style s Components and encapsulation u No language restriction or addition u Some hw synthesis support (c) Giovanni De Micheli 33

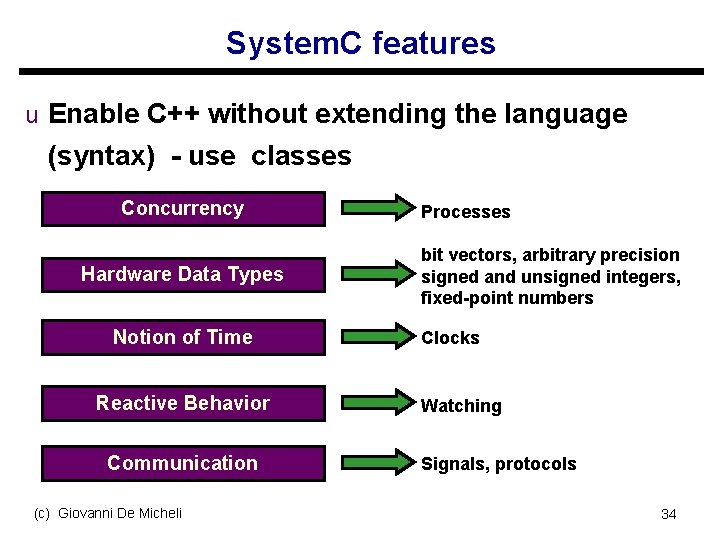

System. C features u Enable C++ without extending the language (syntax) - use classes Concurrency Hardware Data Types Notion of Time Reactive Behavior Communication (c) Giovanni De Micheli Processes bit vectors, arbitrary precision signed and unsigned integers, fixed-point numbers Clocks Watching Signals, protocols 34

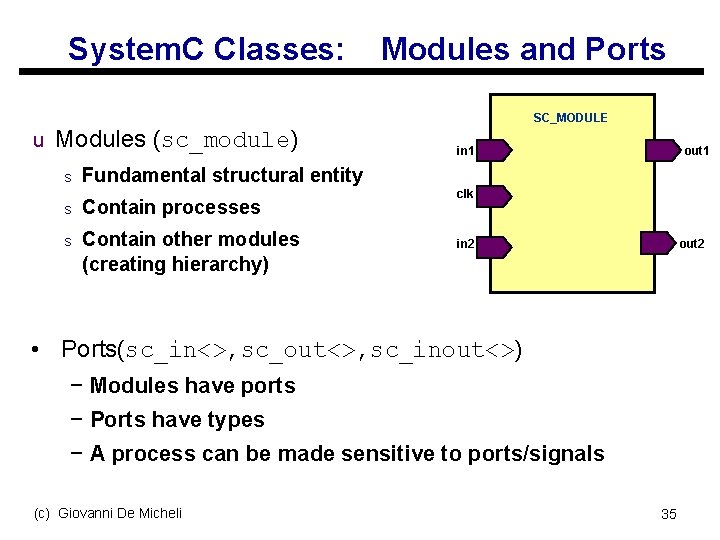

System. C Classes: Modules and Ports SC_MODULE u Modules (sc_module) s in 1 out 1 Fundamental structural entity s Contain processes s Contain other modules (creating hierarchy) clk in 2 out 2 • Ports(sc_in<>, sc_out<>, sc_inout<>) − Modules have ports − Ports have types − A process can be made sensitive to ports/signals (c) Giovanni De Micheli 35

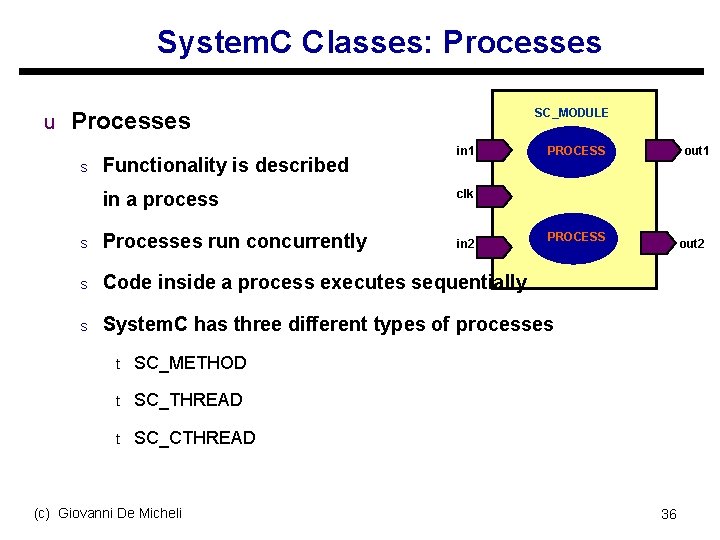

System. C Classes: Processes SC_MODULE u Processes s Functionality is described in 1 in a process clk s Processes run concurrently in 2 s Code inside a process executes sequentially s System. C has three different types of processes t SC_METHOD t SC_THREAD t SC_CTHREAD (c) Giovanni De Micheli out 1 PROCESS out 2 36

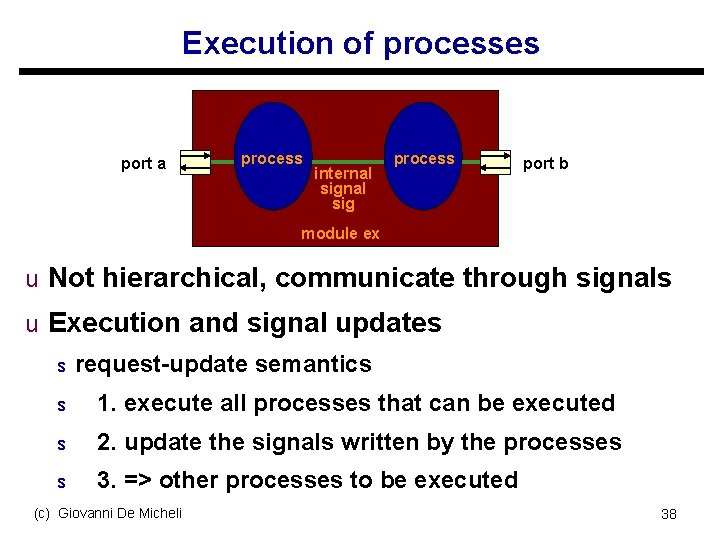

Execution of processes port a process internal sig process port b module ex u Not hierarchical, communicate through signals u Execution and signal updates s request-update semantics s 1. execute all processes that can be executed s 2. update the signals written by the processes s 3. => other processes to be executed (c) Giovanni De Micheli 38

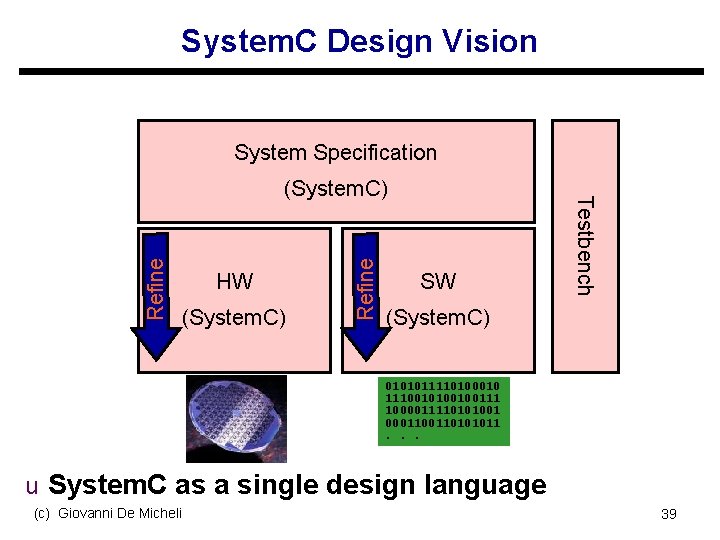

System. C Design Vision System Specification (System. C) Refine HW SW Testbench (System. C) 0101011110100010 11100100111 1000011110101001 000110101011. . . u System. C as a single design language (c) Giovanni De Micheli 39

Module 3 u Objectives s Abstract models s The sequencing graph abstraction and its properties (c) Giovanni De Micheli 40

Abstract models and intermediate formats u Abstract models: s Models based on graphs and discrete mathematics s Useful for problem formalization, algorithm development and reasoning about properties u Intermediate forms: s ASCII or binary representations of abstract models s Derived from language models by compilation (c) Giovanni De Micheli 41

Abstract models Examples u Netlists: s Structural views u Logic networks: s Mixed structural/behavioral views u State diagrams: s Behavioral views of sequential models u Dataflow and sequencing graphs: s Abstraction of behavioral models (c) Giovanni De Micheli 42

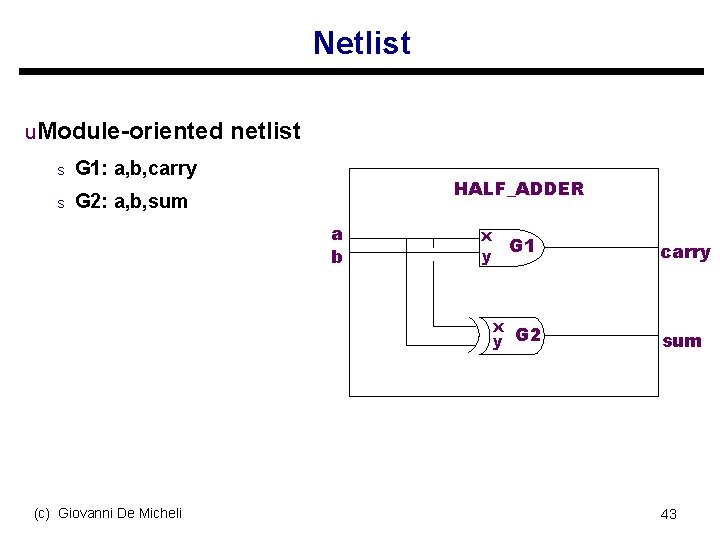

Netlist u. Module-oriented netlist s G 1: a, b, carry s G 2: a, b, sum HALF_ADDER a b (c) Giovanni De Micheli x y G 1 carry x y G 2 sum 43

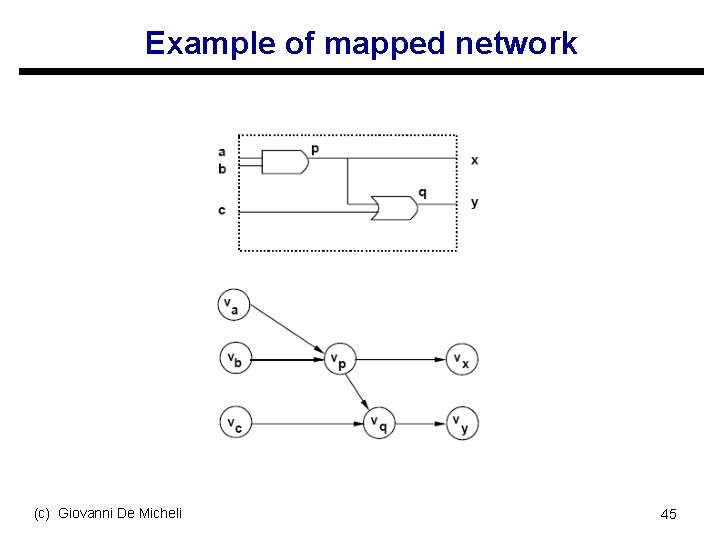

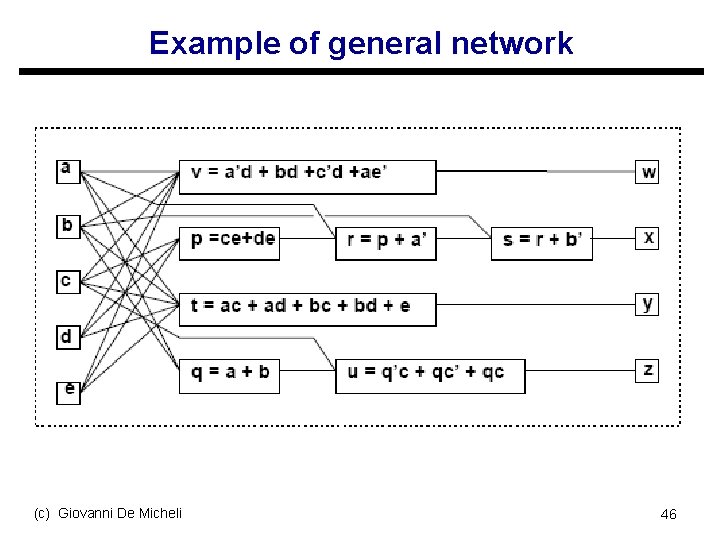

Logic network u Logic network s An interconnection of blocks t s Each block modeled by a Boolean function Usual restrictions: t t Acyclic and memoryless Single-output functions u The model has a structural/behavioral semantics s The structure is induced by the interconnection u Mapped network s Special case when the blocks correspond to library elements (c) Giovanni De Micheli 44

Example of mapped network (c) Giovanni De Micheli 45

Example of general network (c) Giovanni De Micheli 46

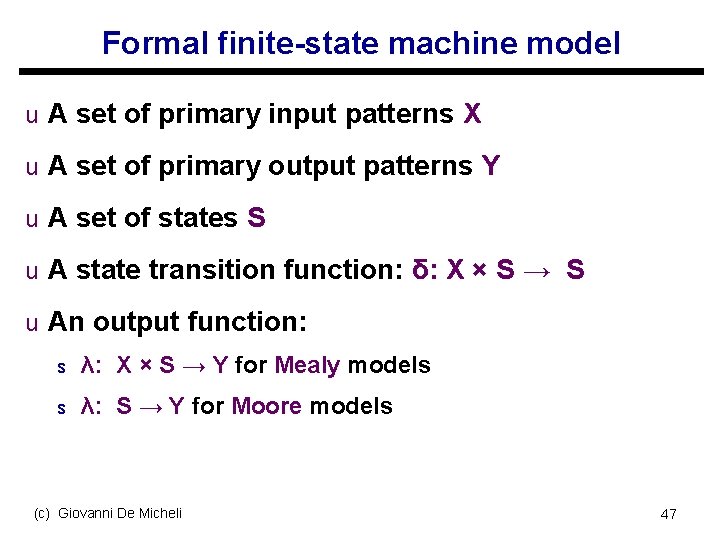

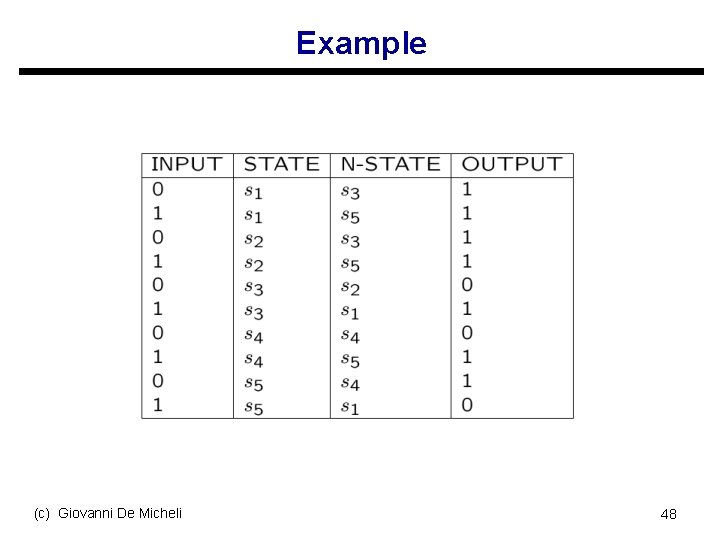

Formal finite-state machine model u A set of primary input patterns X u A set of primary output patterns Y u A set of states S u A state transition function: δ: X × S → S u An output function: s λ: X × S → Y for Mealy models s λ: S → Y for Moore models (c) Giovanni De Micheli 47

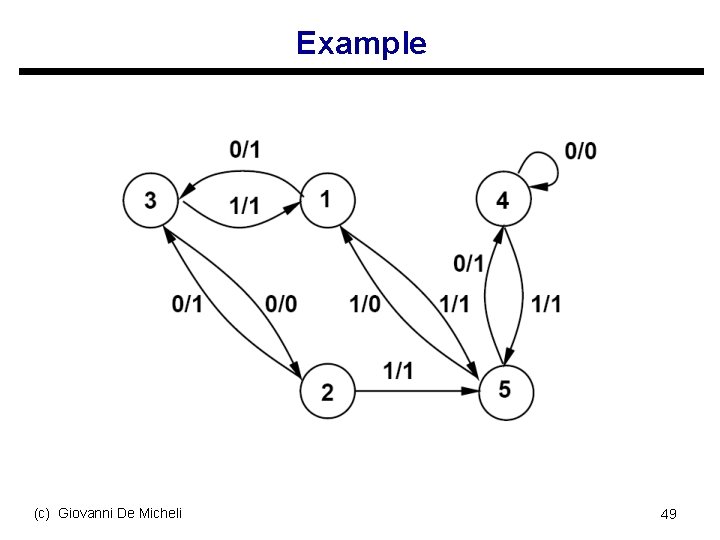

Example (c) Giovanni De Micheli 48

Example (c) Giovanni De Micheli 49

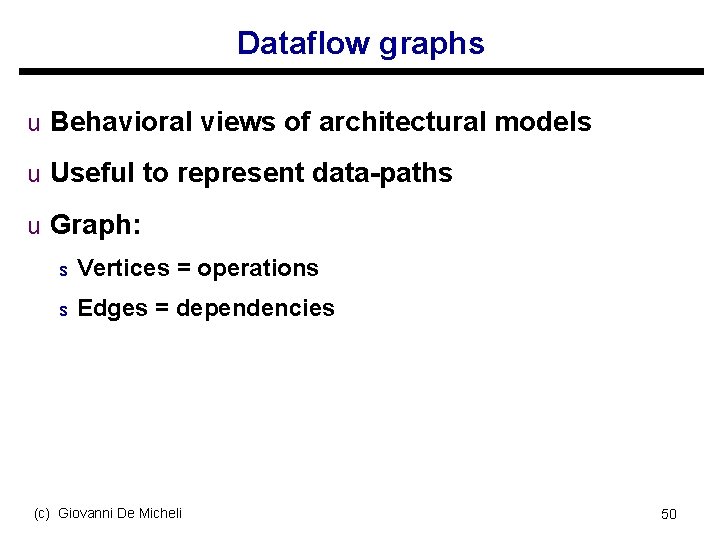

Dataflow graphs u Behavioral views of architectural models u Useful to represent data-paths u Graph: s Vertices = operations s Edges = dependencies (c) Giovanni De Micheli 50

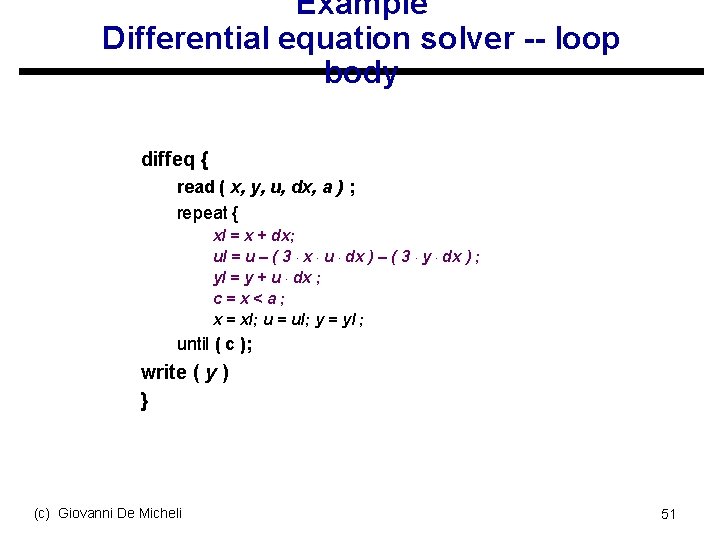

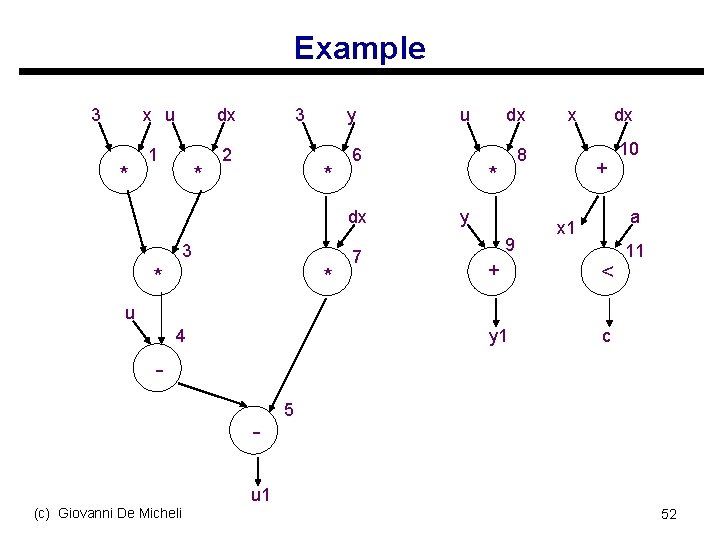

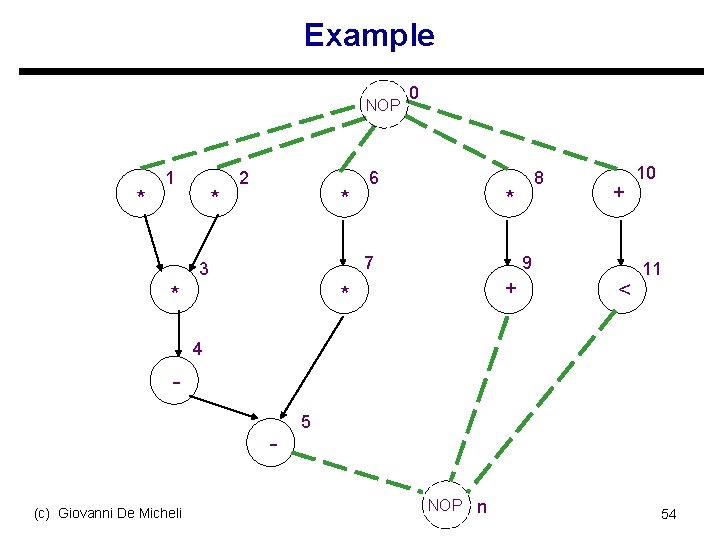

Example Differential equation solver -- loop body diffeq { read ( x, y, u, dx, a ) ; repeat { xl = x + dx; ul = u – ( 3. x. u. dx ) – ( 3. y. dx ) ; yl = y + u. dx ; c=x<a; x = xl; u = ul; y = yl ; until ( c ); write ( y ) } (c) Giovanni De Micheli 51

Example 3 * x u dx 1 2 * 3 y * 6 dx 3 * * u 7 dx x 8 * y 9 dx + 10 a x 1 + < y 1 c 11 u 4 - 5 u 1 (c) Giovanni De Micheli 52

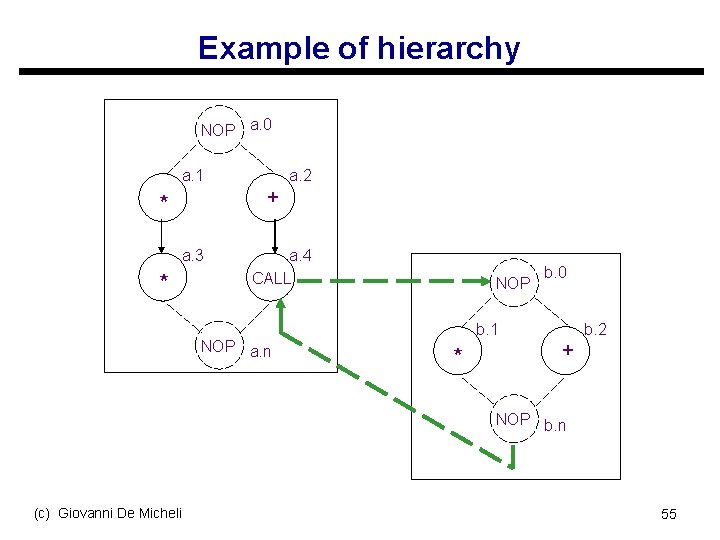

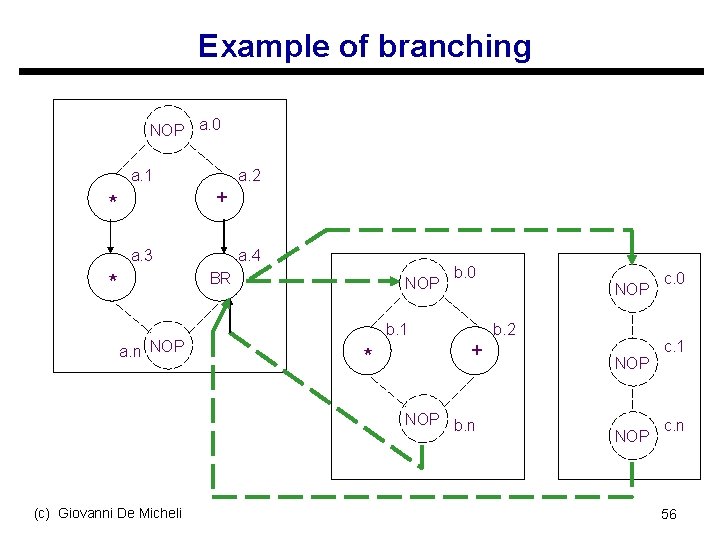

Sequencing graphs u Behavioral views of architectural models u Useful to represent data-path and control u Extended dataflow graphs: s Operation serialization s Hierarchy s Control-flow commands: t Branching and iteration. u Polar graphs: s Source and sink (c) Giovanni De Micheli 53

Example NOP * 1 * 2 * 0 6 * * + 9 7 3 8 + * < 10 11 4 (c) Giovanni De Micheli 5 NOP n 54

Example of hierarchy NOP a. 0 a. 1 * a. 3 * + a. 2 a. 4 CALL NOP a. n NOP b. 1 * b. 0 + b. 2 NOP b. n (c) Giovanni De Micheli 55

Example of branching NOP a. 0 a. 1 * + a. 3 a. 2 a. 4 BR * a. n NOP b. 1 * b. 0 + NOP b. n (c) Giovanni De Micheli NOP b. 2 NOP c. 0 c. 1 c. n 56

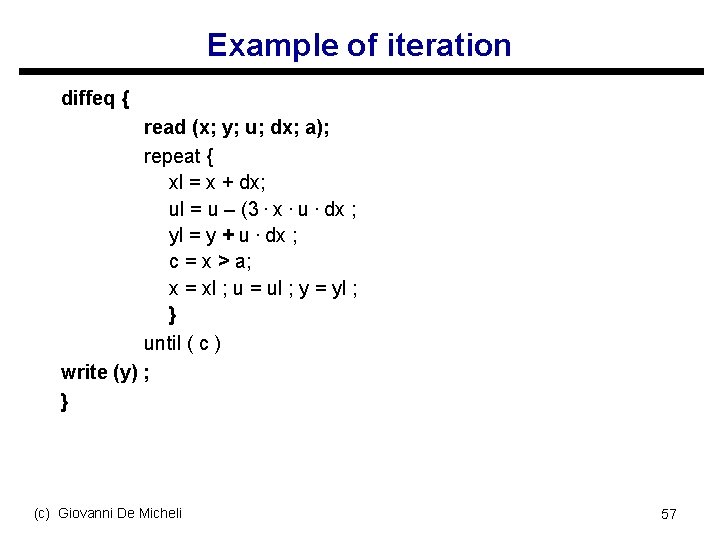

Example of iteration diffeq { read (x; y; u; dx; a); repeat { xl = x + dx; ul = u – (3. x. u. dx ; yl = y + u. dx ; c = x > a; x = xl ; u = ul ; y = yl ; } until ( c ) write (y) ; } (c) Giovanni De Micheli 57

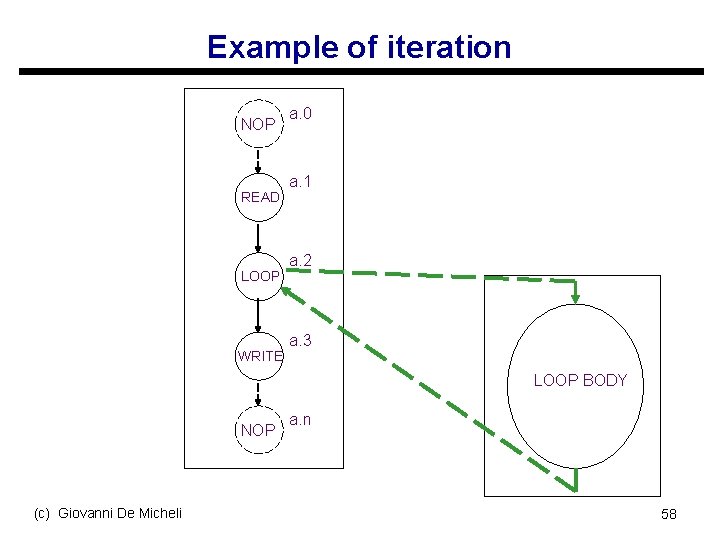

Example of iteration NOP READ LOOP WRITE a. 0 a. 1 a. 2 a. 3 LOOP BODY NOP (c) Giovanni De Micheli a. n 58

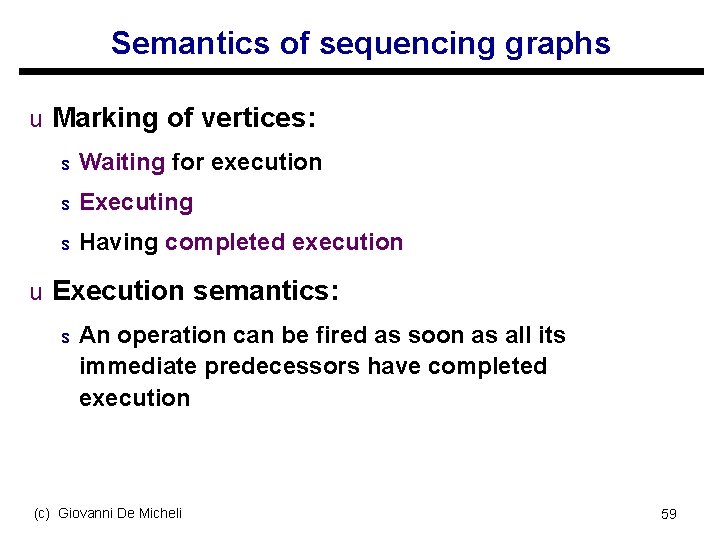

Semantics of sequencing graphs u Marking of vertices: s Waiting for execution s Executing s Having completed execution u Execution semantics: s An operation can be fired as soon as all its immediate predecessors have completed execution (c) Giovanni De Micheli 59

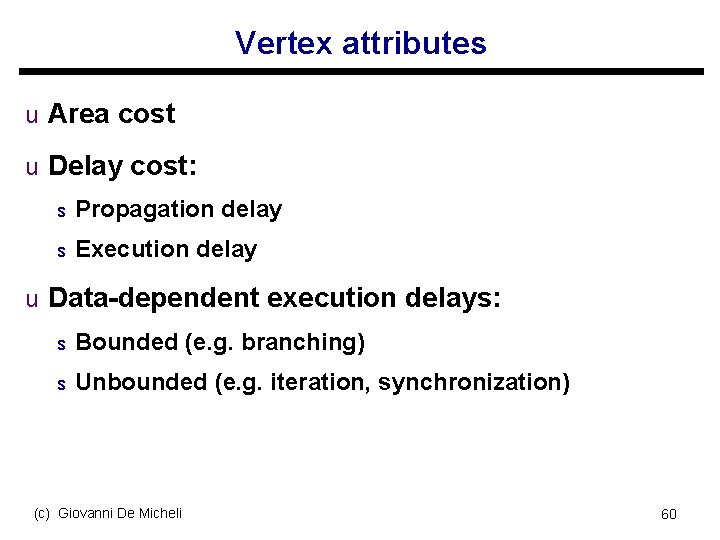

Vertex attributes u Area cost u Delay cost: s Propagation delay s Execution delay u Data-dependent execution delays: s Bounded (e. g. branching) s Unbounded (e. g. iteration, synchronization) (c) Giovanni De Micheli 60

Properties of sequencing graphs u Computed by visiting hierarchy bottom-up u Area estimate: s Sum of the area attributes of all vertices s Worst-case – no sharing u Delay estimate (latency): s Bounded-latency graphs s Length of longest path from source to sink (c) Giovanni De Micheli 61

Summary u Hardware synthesis requires specialized language support: s VHDL and Verilog HDL are mainly used today t t Similar features Simulation-oriented u Synthesis from programming languages is also possible: s Hardware and software models of computation are different s Appropriate hw semantics need to be associated with programming languages t System. C u Abstract models: s Capture essential information s Derivable from HDL models s Useful to prove properties and for algorithm development. (c) Giovanni De Micheli 62

- Slides: 60