Modeling and Simulating Wireless Systems Using MATLAB and

Modeling and Simulating Wireless Systems Using MATLAB® and Simulink® 2010 Technology Roadshow © 2010 Altera Corporation—Public

Agenda n Introduction - Challenges of wireless system modeling and simulation - Introduction to MATLAB, Simulink, and blocksets n Models and demonstrations - n System-level wireless system model RF receiver front-end design Fixed-point design HDL co-simulation Next steps - FPGA implementation © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 2

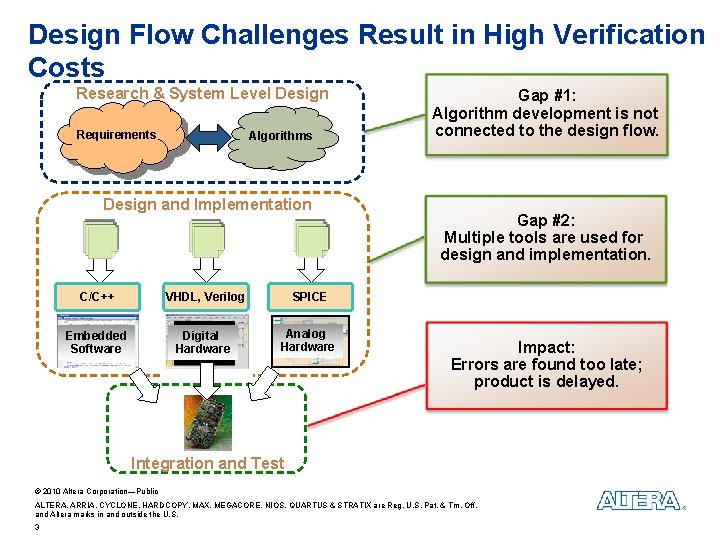

Design Flow Challenges Result in High Verification Costs Research & System Level Design Requirements Algorithms Design and Implementation C/C++ VHDL, Verilog SPICE Embedded Software Digital Hardware Analog Hardware Gap #1: Algorithm development is not connected to the design flow. Gap #2: Multiple tools are used for design and implementation. Impact: Errors are found too late; product is delayed. Integration and Test © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 3

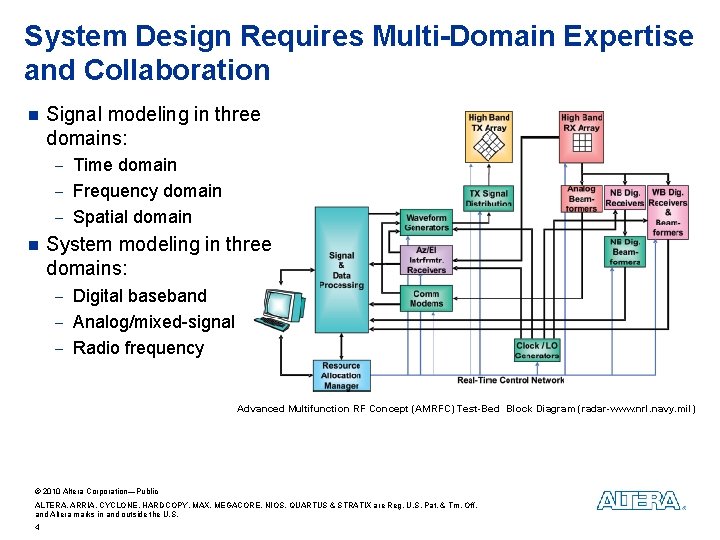

System Design Requires Multi-Domain Expertise and Collaboration n Signal modeling in three domains: - Time domain - Frequency domain - Spatial domain n System modeling in three domains: - Digital baseband - Analog/mixed-signal - Radio frequency Advanced Multifunction RF Concept (AMRFC) Test-Bed Block Diagram (radar-www. nrl. navy. mil) © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 4

Solution: Multi-domain Modeling and Simulation Unify algorithm research, design, & testing Requirements 1. Design Environment Models 2. Timing and Control Logic Analog/RF Models Digital Models 3. Generate Algorithms Implementation 4. C, C++ VHDL, Verilog SPICE Embedded Software Digital Hardware Analog Hardware 5. Prototype Integration and Test Model the system and requirements in the same industry-standard environment. Model different subsystem domains in one integrated environment. Re-use this model as a testbench throughout the design process Verify implementation details using system testbench and cosimulation with your chosen design tools. Leverage the environment all the way to integration and test. Test Environments © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 5

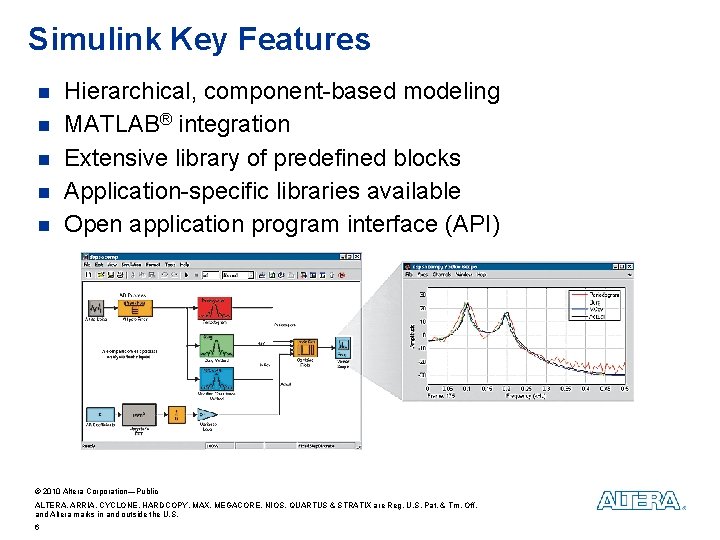

Simulink Key Features n n n Hierarchical, component-based modeling MATLAB® integration Extensive library of predefined blocks Application-specific libraries available Open application program interface (API) © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 6

Key Features – Signal Processing Blockset n Waveform coding n Matched filter detectors n Adaptive beamforming or detection (STAP) n DOA, target detection n Beamforming n Tracking n N-dimensional signals © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 7

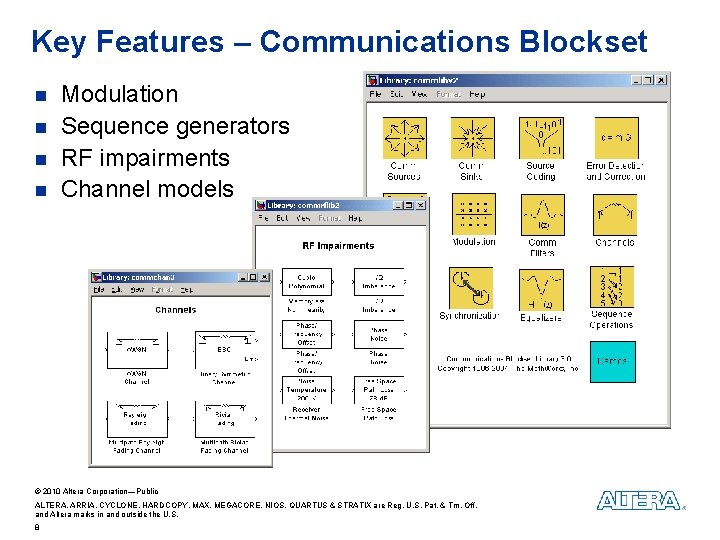

Key Features – Communications Blockset n n Modulation Sequence generators RF impairments Channel models © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 8

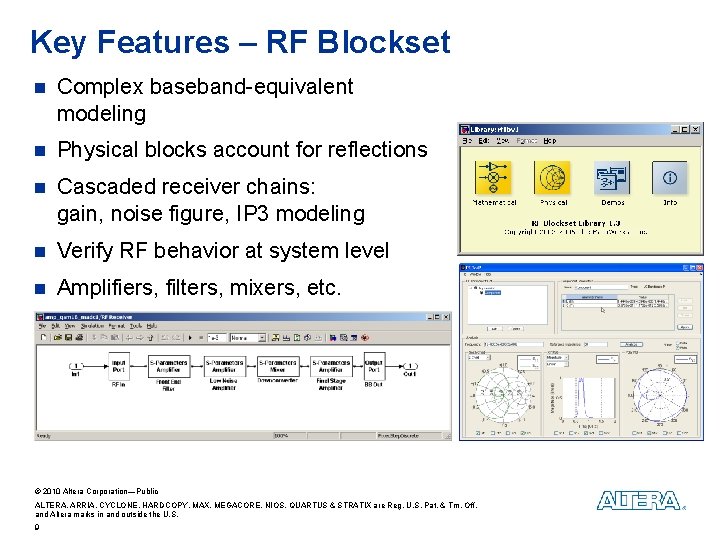

Key Features – RF Blockset n Complex baseband-equivalent modeling n Physical blocks account for reflections n Cascaded receiver chains: gain, noise figure, IP 3 modeling n Verify RF behavior at system level n Amplifiers, filters, mixers, etc. © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 9

Demonstrations © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 10

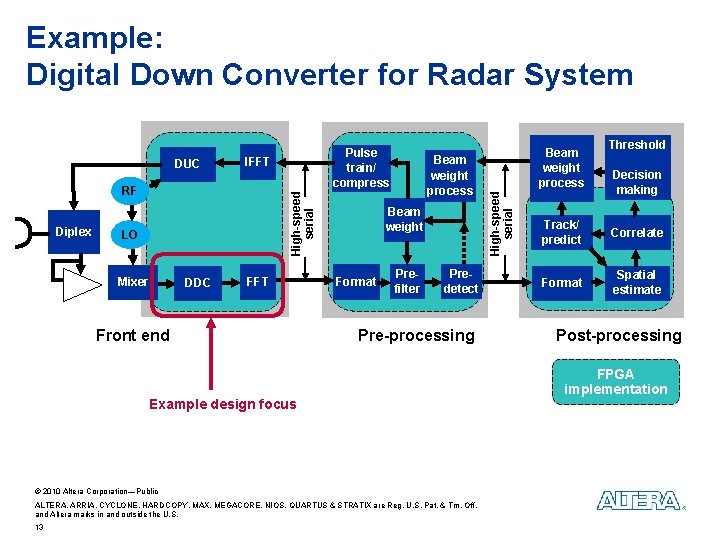

Example: Digital Down Converter for Radar System IFFT Diplex High-speed serial RF LO Mixer DDC FFT Front end Beam weight process Beam weight Format Prefilter Predetect Pre-processing Example design focus © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 13 Beam weight process High-speed serial DUC Pulse train/ compress Threshold Decision making Track/ predict Correlate Format Spatial estimate Post-processing FPGA implementation

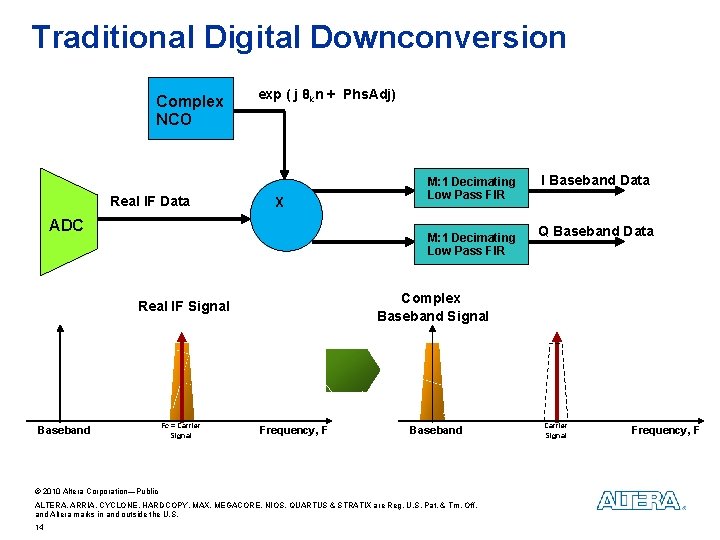

Traditional Digital Downconversion Complex NCO Real IF Data exp ( j θkn + Phs. Adj) X ADC M: 1 Decimating Low Pass FIR Fc = Carrier Signal Frequency, F Baseband © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 14 Q Baseband Data Complex Baseband Signal Real IF Signal Baseband I Baseband Data Carrier Signal Frequency, F

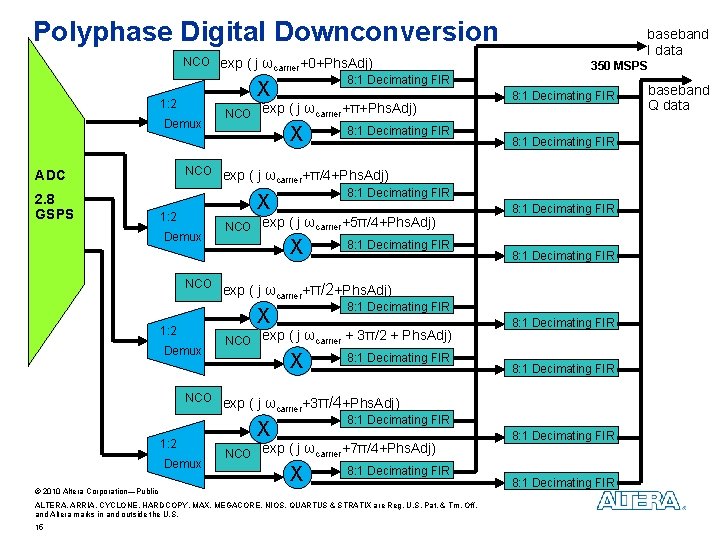

Polyphase Digital Downconversion NCO exp ( j ωcarrier+0+Phs. Adj) 8: 1 Decimating FIR X 1: 2 Demux X X 1: 2 Demux NCO exp ( j ωcarrier+5π/4+Phs. Adj) X 8: 1 Decimating FIR Demux NCO 1: 2 Demux 8: 1 Decimating FIR exp ( j ωcarrier+π/2+Phs. Adj) 8: 1 Decimating FIR X 1: 2 NCO exp ( j ωcarrier + 3π/2 + Phs. Adj) 8: 1 Decimating FIR X 8: 1 Decimating FIR exp ( j ωcarrier+3π/4+Phs. Adj) 8: 1 Decimating FIR X NCO exp ( j ωcarrier+7π/4+Phs. Adj) X 8: 1 Decimating FIR © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 15 350 MSPS NCO exp ( j ω carrier+π/4+Phs. Adj) 8: 1 Decimating FIR ADC 2. 8 GSPS NCO exp ( j ωcarrier+π+Phs. Adj) 8: 1 Decimating FIR baseband I data 8: 1 Decimating FIR baseband Q data

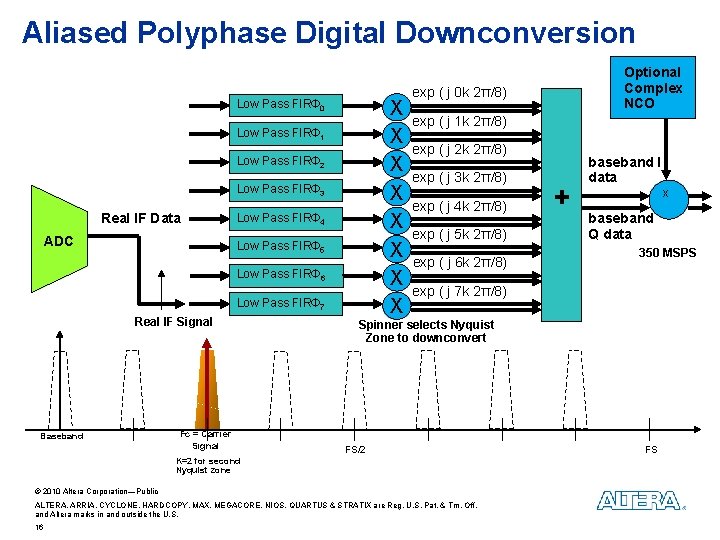

Aliased Polyphase Digital Downconversion X X X X Low Pass FIRФ 0 Low Pass FIRФ 1 Low Pass FIRФ 2 Low Pass FIRФ 3 Real IF Data ADC Low Pass FIRФ 4 Low Pass FIRФ 5 Low Pass FIRФ 6 Low Pass FIRФ 7 Real IF Signal Baseband Fc = Carrier Signal exp ( j 0 k 2π/8) exp ( j 1 k 2π/8) exp ( j 2 k 2π/8) exp ( j 3 k 2π/8) exp ( j 4 k 2π/8) exp ( j 5 k 2π/8) exp ( j 6 k 2π/8) + baseband I data X baseband Q data 350 MSPS exp ( j 7 k 2π/8) Spinner selects Nyquist Zone to downconvert FS/2 K=2 for second Nyquist zone © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 16 Optional Complex NCO FS

What We Used n Simulink n Embedded MATLAB RF Blockset Signal Processing Blockset Fixed-Point Tool EDA Simulator Links Masked subsystems and libraries n n n © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 17

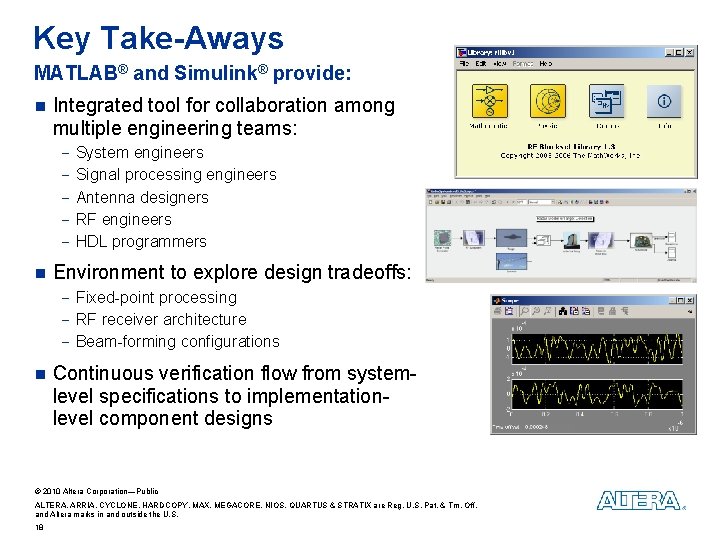

Key Take-Aways MATLAB® and Simulink® provide: n Integrated tool for collaboration among multiple engineering teams: - n System engineers Signal processing engineers Antenna designers RF engineers HDL programmers Environment to explore design tradeoffs: - Fixed-point processing - RF receiver architecture - Beam-forming configurations n Continuous verification flow from systemlevel specifications to implementationlevel component designs © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 18

Next steps: FPGA implementation n The original Simulink floating-point model and the elaborated fixed-point models are re-used as a system level verification test bench n Verification “deltas” resulting from device-specific behavior are evaluated using system level metrics (BER, Pd, etc. ) n Altera® Advanced DSP Builder blocks enable system level verification by maintaining the connection between high level model and FPGA hardware © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 19

For More Information about MATLAB Products or Services, Please Contact: n Mainland, China Non-military Industry and Education Users: The Math. Works China Website: www. mathworks. cn Tel: 86 -10 -5982 -7000 Military Industry Users: Hi. Rain Technologies Website: www. hirain. com Tel: 86 -10 -6484 -0606 n Hong Kong/ Macau World Express Computer Systems Ltd. Tel: 852 -2893 -3262 n Taiwan Tera. Soft Inc. Website: www. terasoft. com. tw Tel: 886 -2 -2788 -9300 n US Headquarters: The Math. Works, Inc Website: www. mathworks. com Tel: 10 -508 -647 -7000 © 2010 Altera Corporation—Public ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS & STRATIX are Reg. U. S. Pat. & Tm. Off. and Altera marks in and outside the U. S. 20

Thank You! For more information visit: www. altera. com © 2010 Altera Corporation—Public

- Slides: 19