Mixed PLB and Interconnect BIST for FPGAs Without

Mixed PLB and Interconnect BIST for FPGAs Without Fault-Free Assumptions Vishal Suthar and Shantanu Dutt Electrical and Computer Engineering University of Illinois at Chicago.

Outline The problem of fault-free assumptions & other stories Iterative Bootstrapping (IB) – A general solution Mixed BIST: Combining PLB & interconnect testing with IB—no fault-free assumptions – Recent work in PLB BIST (HD-BIST) – Recent work in interconnect BIST (I-BIST) Simulation Results Conclusions

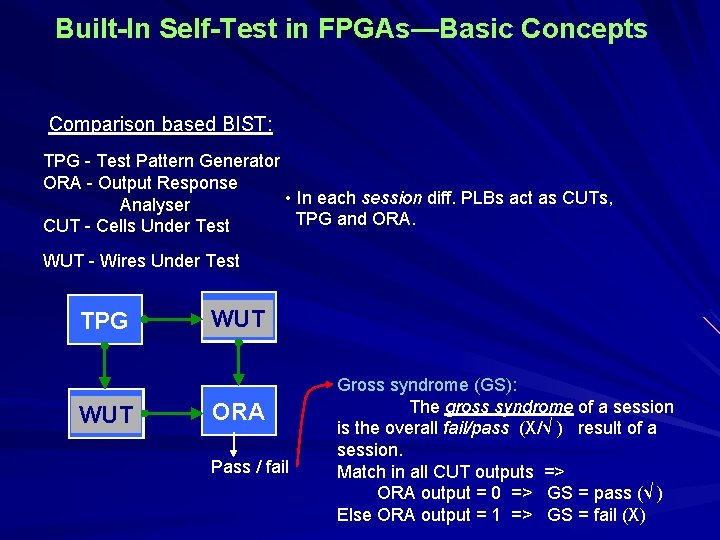

Built-In Self-Test in FPGAs—Basic Concepts Comparison based BIST: TPG - Test Pattern Generator ORA - Output Response • In each session diff. PLBs act as CUTs, Analyser TPG and ORA. CUT - Cells Under Test WUT - Wires Under Test TPG CUT WUT ORA Pass / fail Gross syndrome (GS): The gross syndrome of a session is the overall fail/pass (X/√ ) result of a session. Match in all CUT outputs => ORA output = 0 => GS = pass (√ ) Else ORA output = 1 => GS = fail (X)

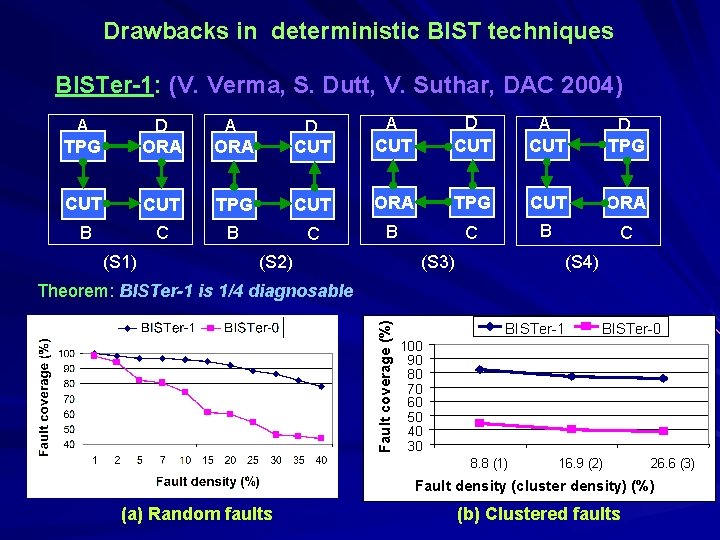

Drawbacks in deterministic BIST techniques BISTer-1: (V. Verma, S. Dutt, V. Suthar, DAC 2004) A TPG D ORA A ORA D CUT A CUT D TPG CUT ORA B C B C (S 1) (S 2) (S 3) (S 4) Fault coverage (%) Theorem: BISTer-1 is 1/4 diagnosable BISTer-1 BISTer-0 100 90 80 70 60 50 40 30 8. 8 (1) 16. 9 (2) 26. 6 (3) Fault density (cluster density) (%) (a) Random faults (b) Clustered faults

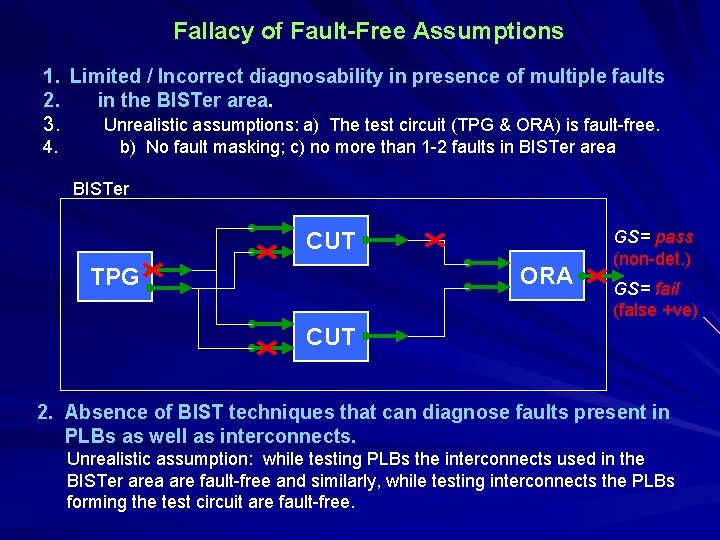

Fallacy of Fault-Free Assumptions 1. Limited / Incorrect diagnosability in presence of multiple faults 2. in the BISTer area. 3. Unrealistic assumptions: a) The test circuit (TPG & ORA) is fault-free. 4. b) No fault masking; c) no more than 1 -2 faults in BISTer area BISTer CUT ORA TPG GS= pass (non-det. ) GS= fail (false +ve) CUT 2. Absence of BIST techniques that can diagnose faults present in PLBs as well as interconnects. Unrealistic assumption: while testing PLBs the interconnects used in the BISTer area are fault-free and similarly, while testing interconnects the PLBs forming the test circuit are fault-free.

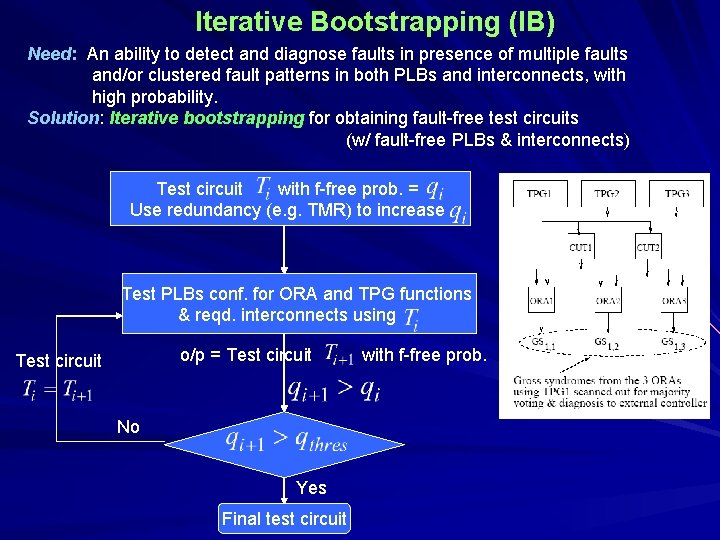

Iterative Bootstrapping (IB) Need: An ability to detect and diagnose faults in presence of multiple faults and/or clustered fault patterns in both PLBs and interconnects, with high probability. Solution: Iterative bootstrapping for obtaining fault-free test circuits (w/ fault-free PLBs & interconnects) Test circuit with f-free prob. = Use redundancy (e. g. TMR) to increase Test PLBs conf. for ORA and TPG functions & reqd. interconnects using o/p = Test circuit No Yes Final test circuit with f-free prob.

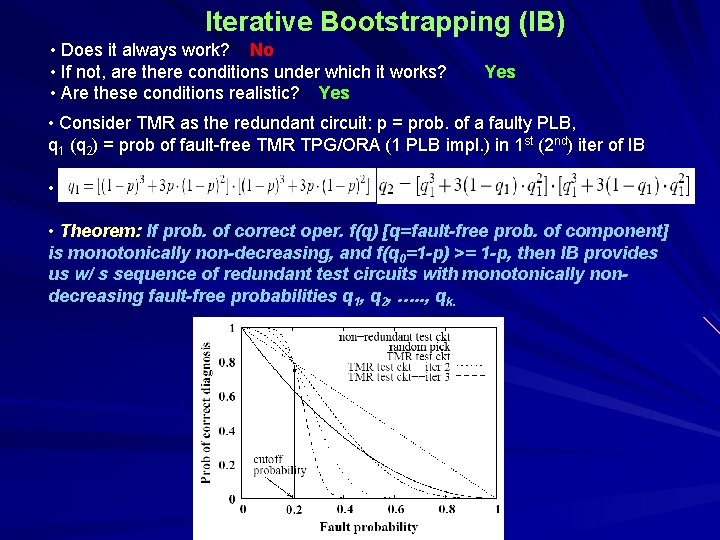

Iterative Bootstrapping (IB) • Does it always work? No • If not, are there conditions under which it works? • Are these conditions realistic? Yes • Consider TMR as the redundant circuit: p = prob. of a faulty PLB, q 1 (q 2) = prob of fault-free TMR TPG/ORA (1 PLB impl. ) in 1 st (2 nd) iter of IB • • Theorem: If prob. of correct oper. f(q) [q=fault-free prob. of component] is monotonically non-decreasing, and f(q 0=1 -p) >= 1 -p, then IB provides us w/ s sequence of redundant test circuits with monotonically nondecreasing fault-free probabilities q 1, q 2, …. . , qk.

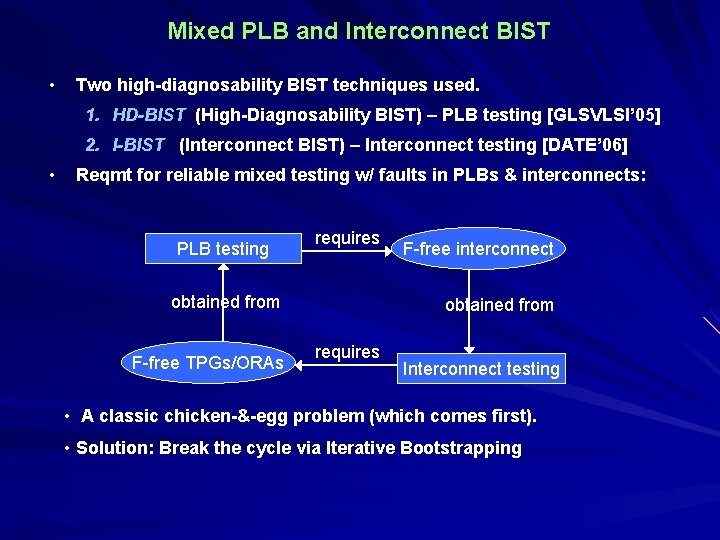

Mixed PLB and Interconnect BIST • Two high-diagnosability BIST techniques used. 1. HD-BIST (High-Diagnosability BIST) – PLB testing [GLSVLSI’ 05] 2. I-BIST (Interconnect BIST) – Interconnect testing [DATE’ 06] • Reqmt for reliable mixed testing w/ faults in PLBs & interconnects: PLB testing requires obtained from F-free TPGs/ORAs F-free interconnect obtained from requires Interconnect testing • A classic chicken-&-egg problem (which comes first). • Solution: Break the cycle via Iterative Bootstrapping

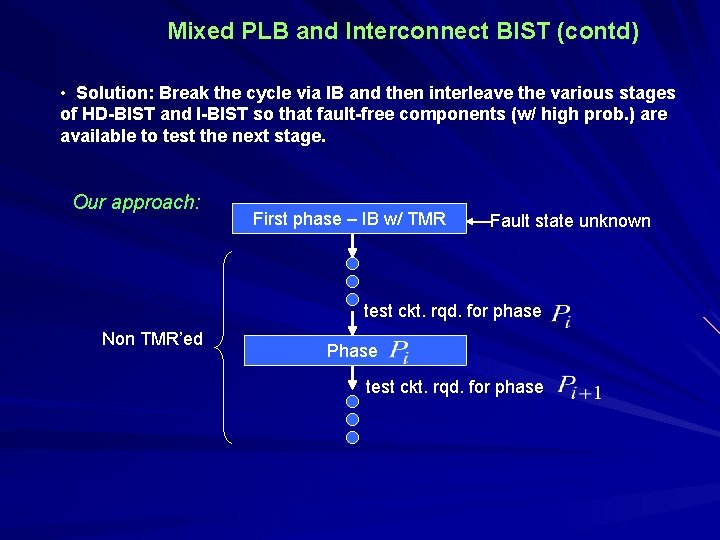

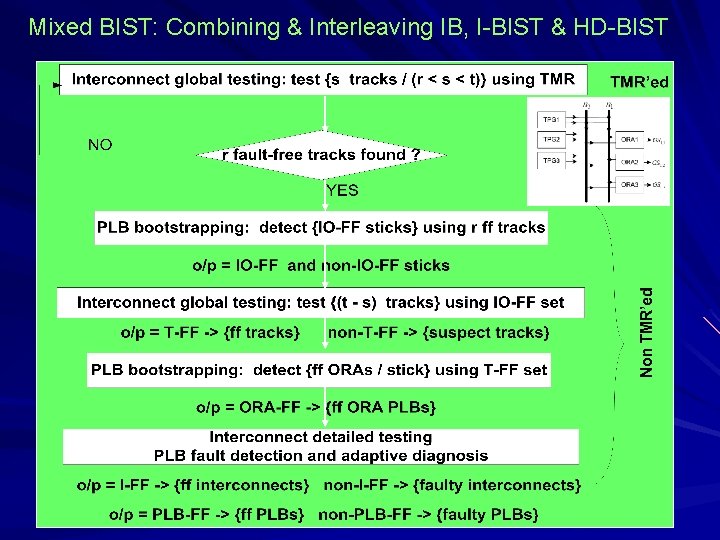

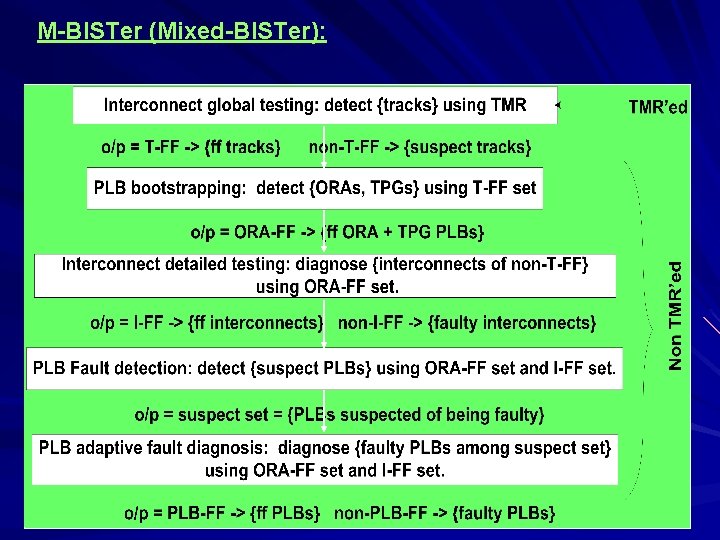

Mixed PLB and Interconnect BIST (contd) • Solution: Break the cycle via IB and then interleave the various stages of HD-BIST and I-BIST so that fault-free components (w/ high prob. ) are available to test the next stage. Our approach: First phase – IB w/ TMR Fault state unknown test ckt. rqd. for phase Non TMR’ed Phase test ckt. rqd. for phase

![Mixed-BIST: PLB BIST Stages HD-BIST [Suthar & Dutt, GLSVLSI’ 05] START Tester Stick TPGORATPG Mixed-BIST: PLB BIST Stages HD-BIST [Suthar & Dutt, GLSVLSI’ 05] START Tester Stick TPGORATPG](http://slidetodoc.com/presentation_image/e4e722cbf9cf4c854ef832d776fdb018/image-10.jpg)

Mixed-BIST: PLB BIST Stages HD-BIST [Suthar & Dutt, GLSVLSI’ 05] START Tester Stick TPGORATPG D E F TPG ORATPG D E F CUT TPG A B C TPG CUT A B C CUT TPG CUT A B C Testee Stick TPG shuffling scheme (instead of TMR) to reduce test vector skipping probability Theorem: = prob. of shuffled TPG skipping a test vector. = prob. of normal TPG skipping a test vector. p = prob. of a PLB being faulty. Bootstrapping phases (2) o/p = fault-free ORA / stick (if exists) Global testing – Fault detection & gross diagnosis phase o/p = suspect PLBs & fault-free sticks Detailed testing: Adaptive diagnosis phase o/p = faulty PLBs END

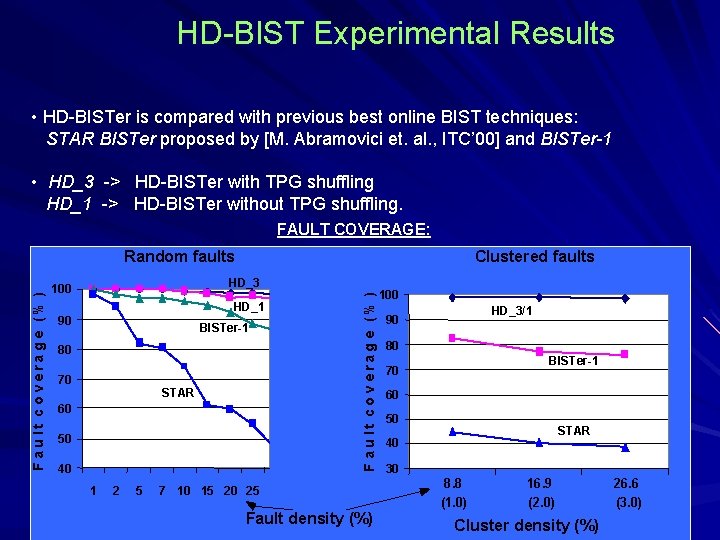

HD-BIST Experimental Results • HD-BISTer is compared with previous best online BIST techniques: STAR BISTer proposed by [M. Abramovici et. al. , ITC’ 00] and BISTer-1 • HD_3 -> HD-BISTer with TPG shuffling HD_1 -> HD-BISTer without TPG shuffling. FAULT COVERAGE: Clustered faults HD_3 100 HD_1 90 BISTer-1 80 70 STAR 60 50 40 1 2 5 F a u lt c o v e ra g e (% ) F a u lt c o v e r a g e (% ) Random faults 7 10 15 20 25 Fault density (%) 100 HD_3/1 90 80 BISTer-1 70 60 50 STAR 40 30 8. 8 (1. 0) 16. 9 (2. 0) Cluster density (%) 26. 6 (3. 0)

![Mixed-BIST: Interconnect BIST Stages I-BIST [Suthar & Dutt, DATE’ 06] Approach: 1. Global Testing: Mixed-BIST: Interconnect BIST Stages I-BIST [Suthar & Dutt, DATE’ 06] Approach: 1. Global Testing:](http://slidetodoc.com/presentation_image/e4e722cbf9cf4c854ef832d776fdb018/image-12.jpg)

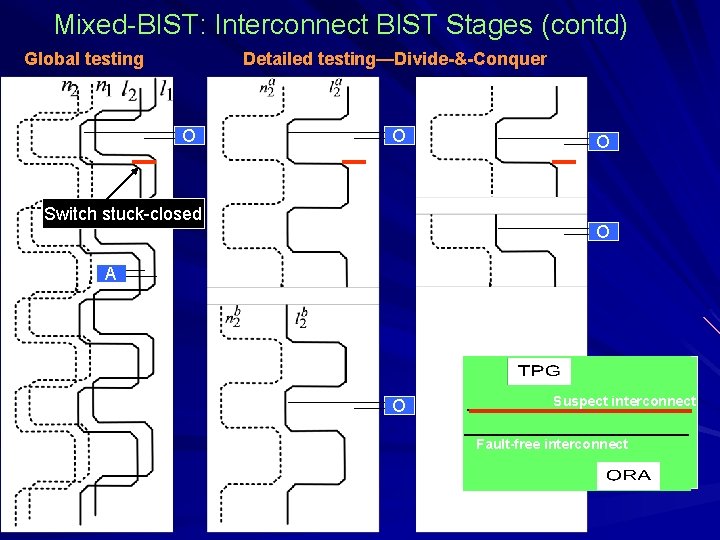

Mixed-BIST: Interconnect BIST Stages I-BIST [Suthar & Dutt, DATE’ 06] Approach: 1. Global Testing: First isolate the possible fault locations to a small set of interconnects in very few configurations -> Suspect Set 2. Detailed Testing: Then diagnose interconnects of suspect set for faults using divide-&-conquer and in the final iteration by comparison to known faultfree interconnects Global Testing (1/5 configs)

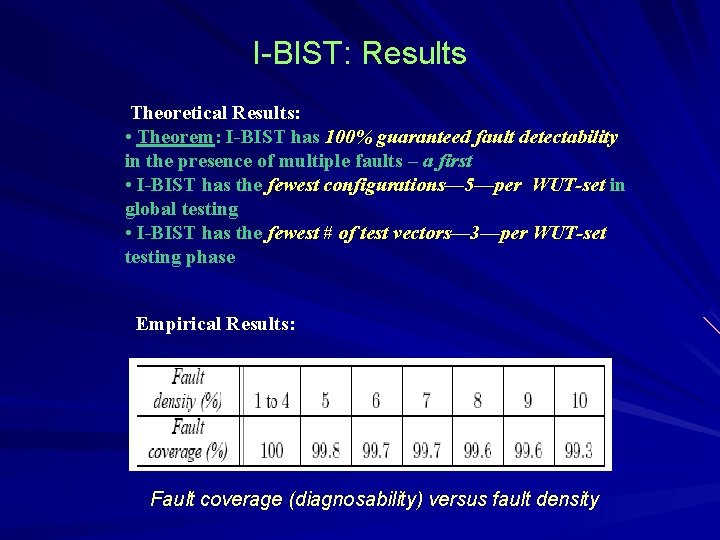

I-BIST: Results Theoretical Results: • Theorem: I-BIST has 100% guaranteed fault detectability in the presence of multiple faults – a first • I-BIST has the fewest configurations— 5—per WUT-set in global testing • I-BIST has the fewest # of test vectors— 3—per WUT-set testing phase Empirical Results: Fault coverage (diagnosability) versus fault density

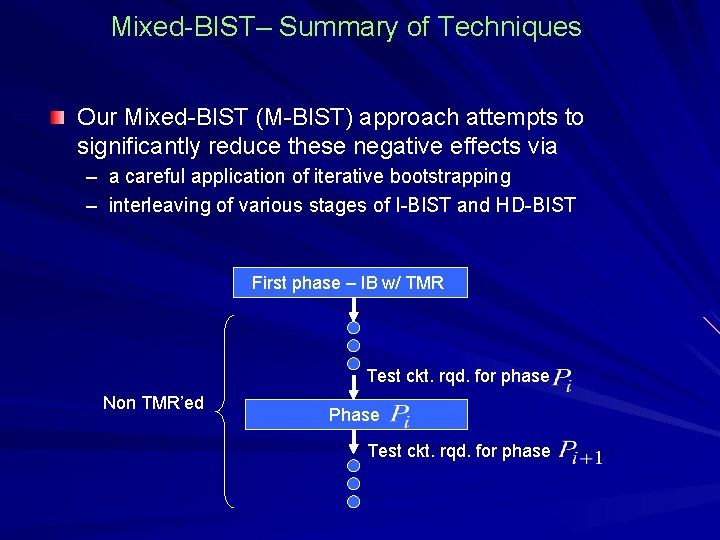

Mixed-BIST– Summary of Techniques Our Mixed-BIST (M-BIST) approach attempts to significantly reduce these negative effects via – a careful application of iterative bootstrapping – interleaving of various stages of I-BIST and HD-BIST First phase – IB w/ TMR Test ckt. rqd. for phase Non TMR’ed Phase Test ckt. rqd. for phase

Mixed BIST: Combining & Interleaving IB, I-BIST & HD-BIST

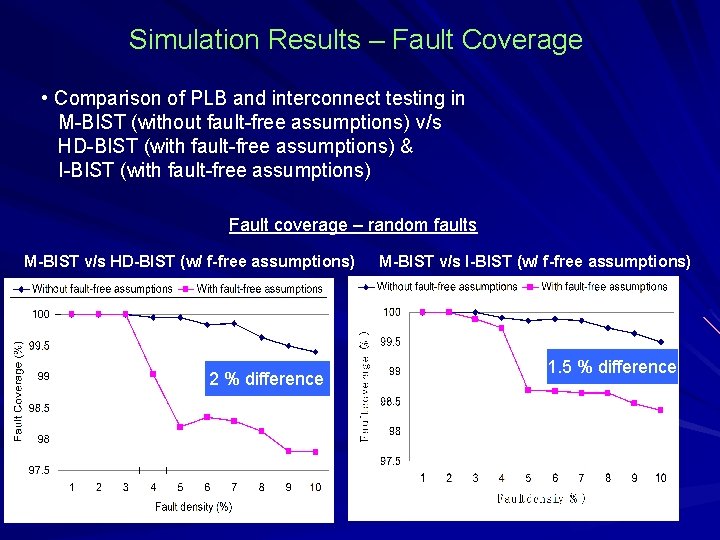

Simulation Results – Fault Coverage • Comparison of PLB and interconnect testing in M-BIST (without fault-free assumptions) v/s HD-BIST (with fault-free assumptions) & I-BIST (with fault-free assumptions) Fault coverage – random faults M-BIST v/s HD-BIST (w/ f-free assumptions) 2 % difference M-BIST v/s I-BIST (w/ f-free assumptions) 1. 5 % difference

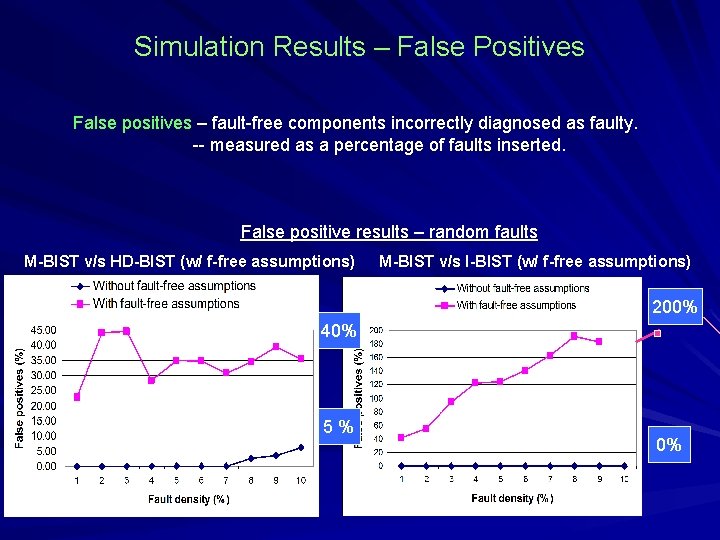

Simulation Results – False Positives False positives – fault-free components incorrectly diagnosed as faulty. -- measured as a percentage of faults inserted. False positive results – random faults M-BIST v/s HD-BIST (w/ f-free assumptions) M-BIST v/s I-BIST (w/ f-free assumptions) 200% 40% 5% 0%

Conclusions Goal: Mixed PLB and Interconnect BIST that does not require any fault-free assumptions in order to: – improve diagnosability and reduce false positives – in the presence of clustered and high density faults in both PLBs and interconnects Introduced the novel concept of general iterative bootstrapping for this purpose that can be used in different test and fault tolerance domains Analyzed the mathematical conditions for improved diagnosis using iterative bootstrapping Applied iterative bootstrapping in novel ways (TMR, shuffled TPGs, TPGs w/o i/o faults) to develop a Mixed BISTer M-BIST sans fault-free assumptions Achieved our aim of accurate PLB and interconnect diagnosis Future Work: Built-in controller for diagnosis and reconfiguration

THANK YOU

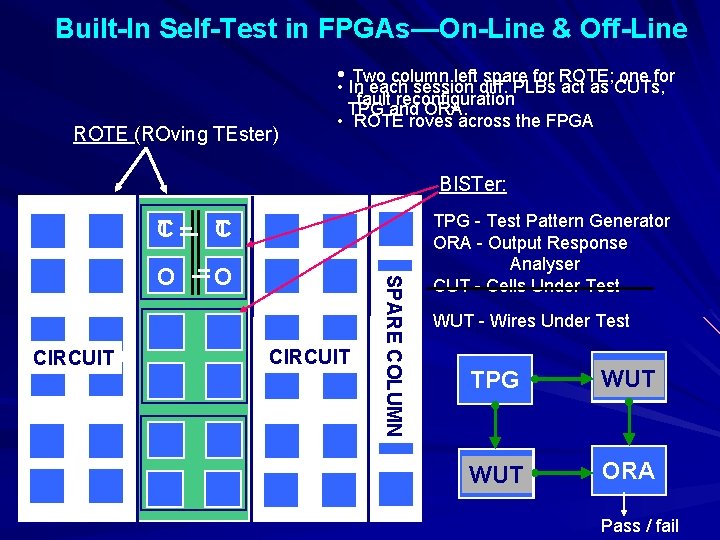

Built-In Self-Test in FPGAs—On-Line & Off-Line • • In. Two column left spare for ROTE; one for each session diff. PLBs act as CUTs, ROTE (ROving TEster) fault reconfiguration TPG and ORA. • ROTE roves across the FPGA BISTer: C T C O O C CIRCUIT SPARE COLUMN CIRCUIT C T TPG - Test Pattern Generator ORA - Output Response Analyser CUT - Cells Under Test WUT - Wires Under Test TPG CUT WUT ORA Pass / fail

Mixed-BIST: Interconnect BIST Stages (contd) Global testing Detailed testing—Divide-&-Conquer O O Switch stuck-closed O O A O Suspect interconnect Fault-free interconnect

M-BISTer (Mixed-BISTer):

- Slides: 22