Mitglied der HelmholtzGemeinschaft The Jlich Digital Readout System

- Slides: 13

Mitglied der Helmholtz-Gemeinschaft The Jülich Digital Readout System for PANDA Developments 3. Dec 2012 | Simone Esch s. esch@fz-juelich. de

Outline § § § Mitglied der Helmholtz-Gemeinschaft § § § The PANDA experiment The Micro Vertex Detector The Jülich Digital Readout System : • Software • Hardware • Firmware UDP implementation GBT implementation Summary 3. December 2012 2

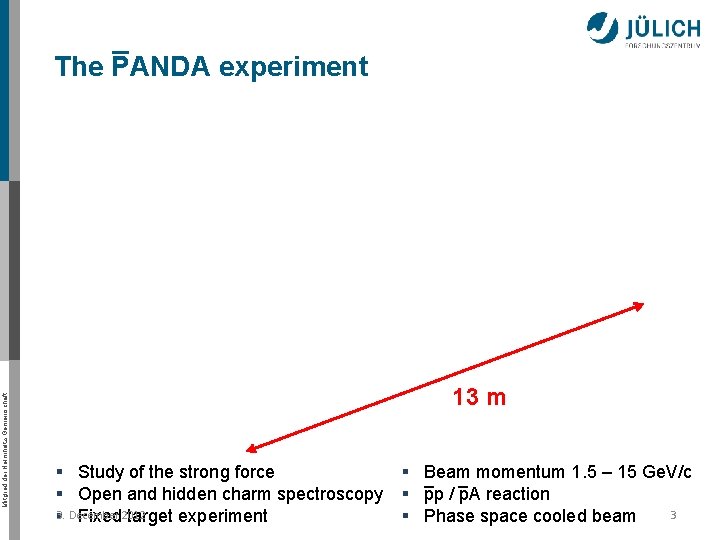

Mitglied der Helmholtz-Gemeinschaft _ The PANDA experiment 13 m § Study of the strong force § Beam _ _ momentum 1. 5 – 15 Ge. V/c § Open and hidden charm spectroscopy § pp / p. A reaction 3 § 3. December Fixed 2012 target experiment § Phase space cooled beam

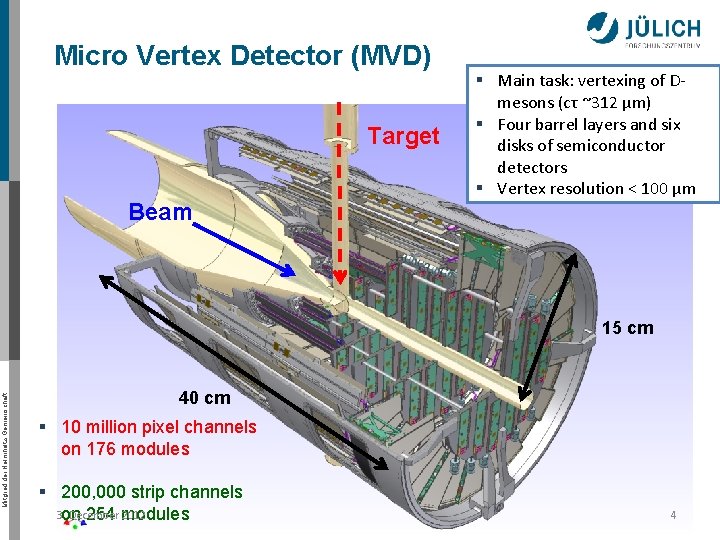

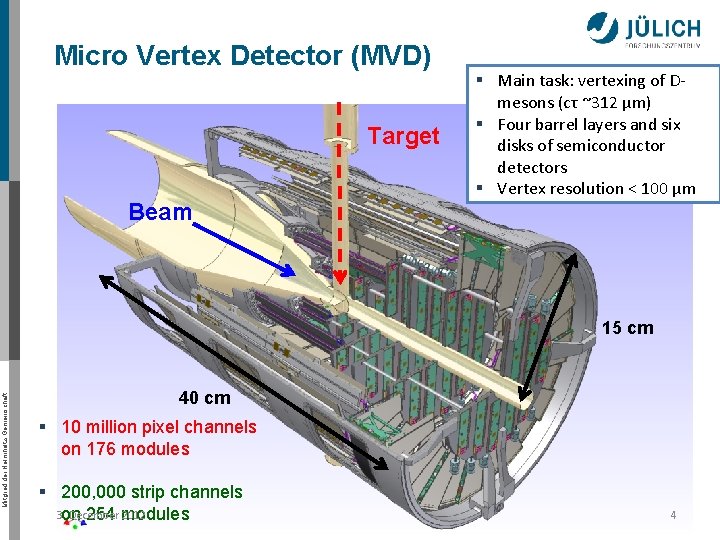

Micro Vertex Detector (MVD) Target Beam § Main task: vertexing of Dmesons (cτ ~312 μm) § Four barrel layers and six disks of semiconductor detectors § Vertex resolution < 100 μm Mitglied der Helmholtz-Gemeinschaft 15 cm 40 cm § 10 million pixel channels on 176 modules § 200, 000 strip channels 3. on December 2012 254 modules 4

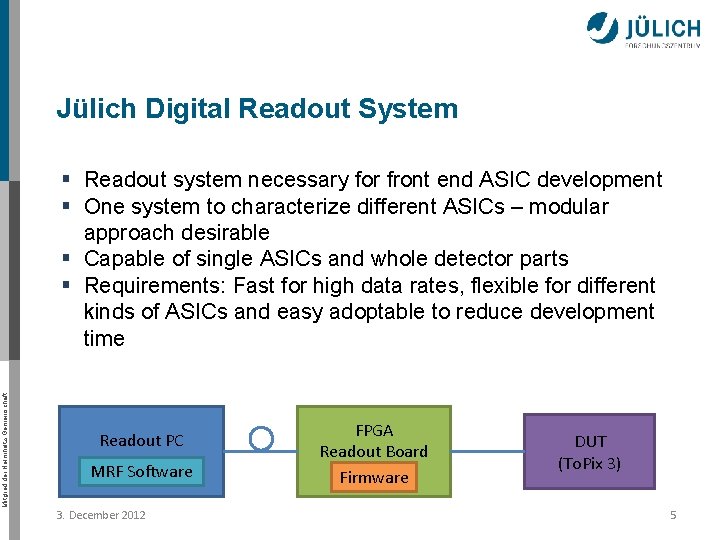

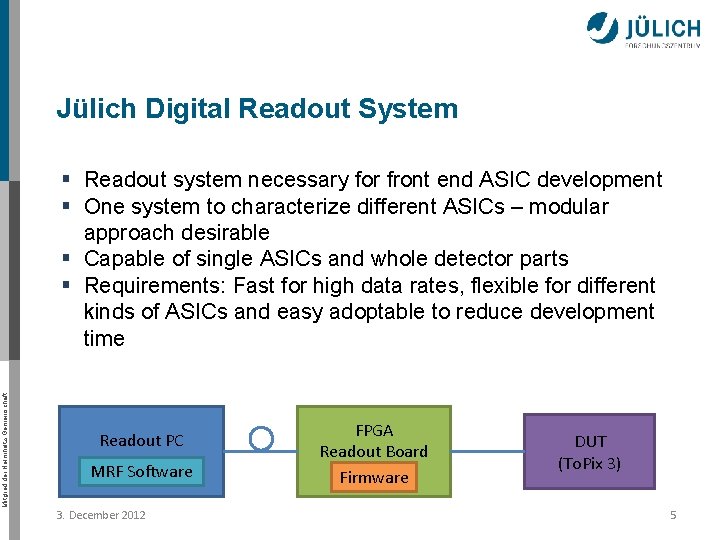

Jülich Digital Readout System Mitglied der Helmholtz-Gemeinschaft § Readout system necessary for front end ASIC development § One system to characterize different ASICs – modular approach desirable § Capable of single ASICs and whole detector parts § Requirements: Fast for high data rates, flexible for different kinds of ASICs and easy adoptable to reduce development time Readout PC MRF Software 3. December 2012 FPGA Readout Board Firmware DUT (To. Pix 3) 5

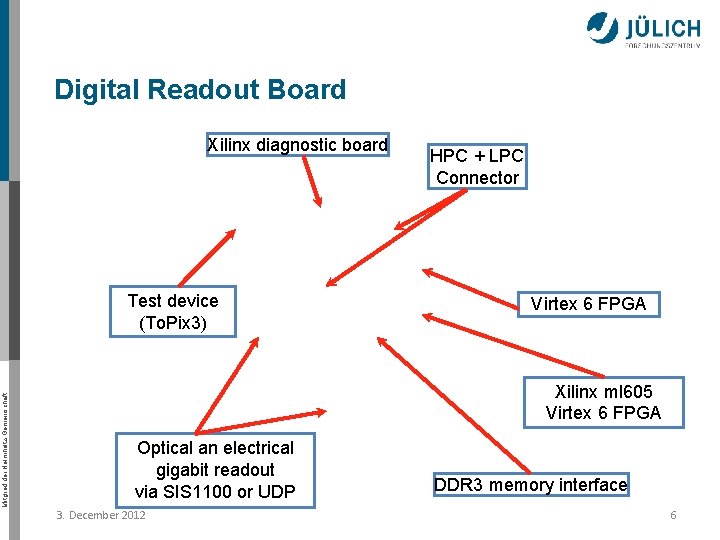

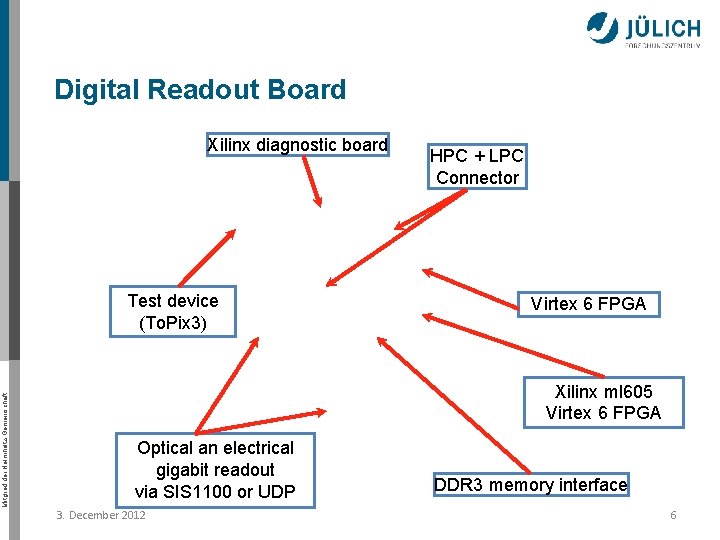

Digital Readout Board Xilinx diagnostic board Mitglied der Helmholtz-Gemeinschaft Test device (To. Pix 3) HPC + LPC Connector Virtex 6 FPGA Xilinx ml 605 Virtex 6 FPGA Optical an electrical gigabit readout via SIS 1100 or UDP 3. December 2012 DDR 3 memory interface 6

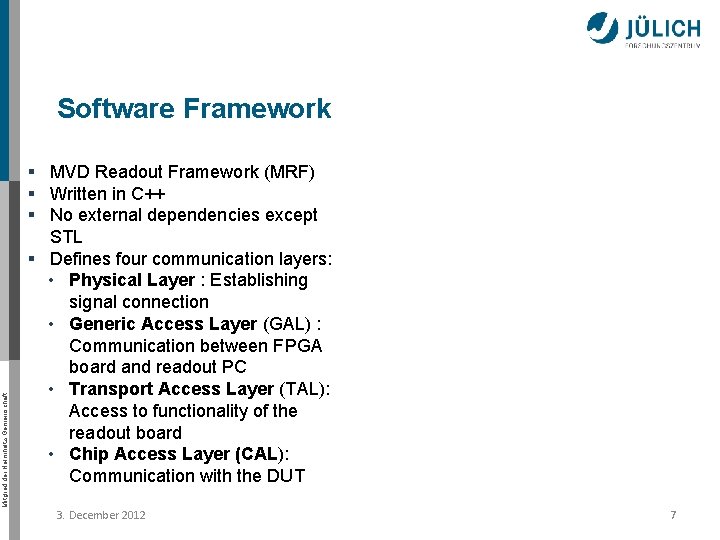

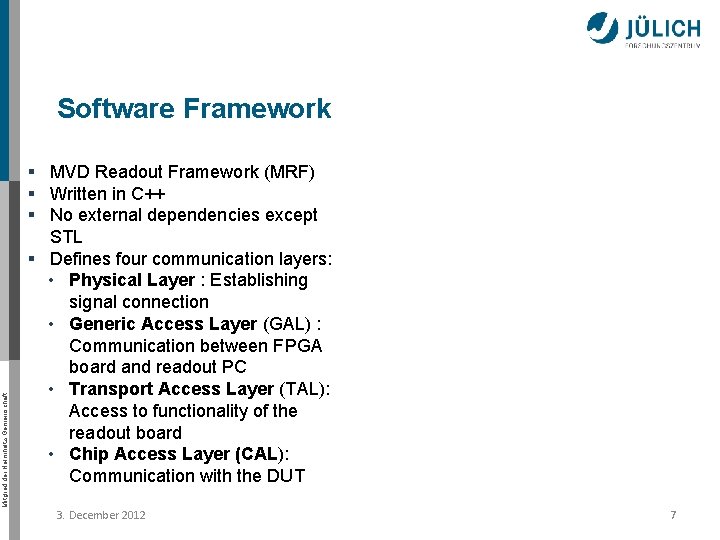

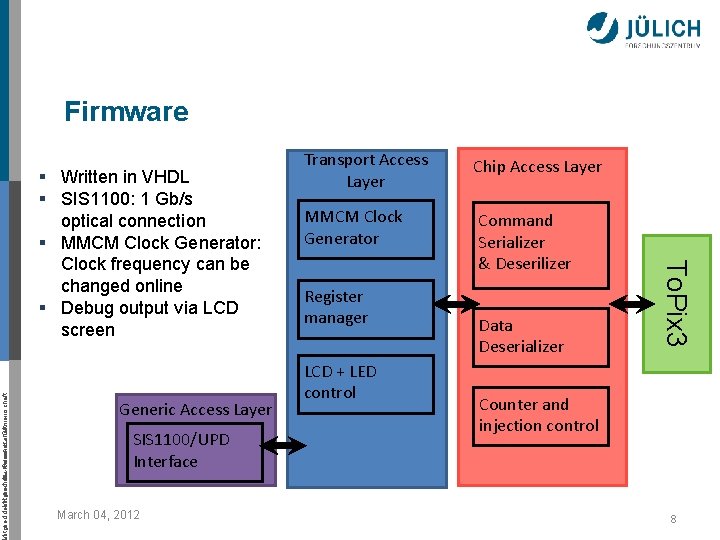

Mitglied der Helmholtz-Gemeinschaft Software Framework § MVD Readout Framework (MRF) § Written in C++ § No external dependencies except STL § Defines four communication layers: • Physical Layer : Establishing signal connection • Generic Access Layer (GAL) : Communication between FPGA board and readout PC • Transport Access Layer (TAL): Access to functionality of the readout board • Chip Access Layer (CAL): Communication with the DUT 3. December 2012 7

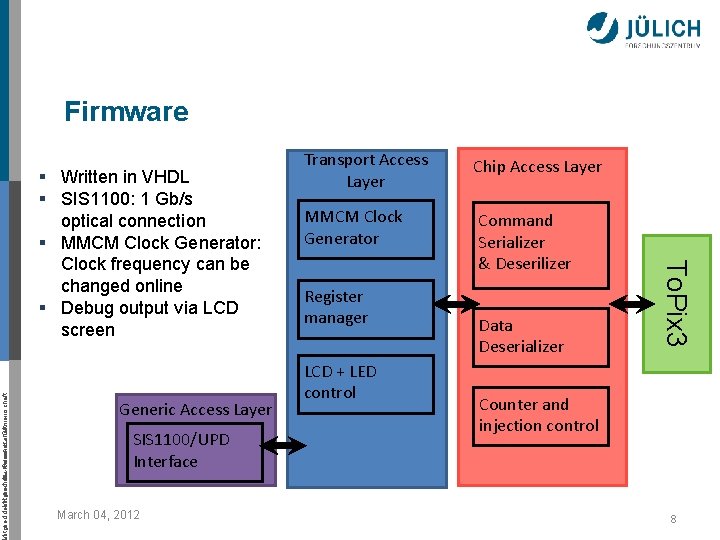

Firmware itglied der. Mitglied Helmholtz-Gemeinschaft der Helmholtz-Gemeinschaft Generic Access Layer SIS 1100/UPD Interface March 04, 2012 Chip Access Layer MMCM Clock Generator Command Serializer & Deserilizer Register manager LCD + LED control Data Deserializer To. Pix 3 § Written in VHDL § SIS 1100: 1 Gb/s optical connection § MMCM Clock Generator: Clock frequency can be changed online § Debug output via LCD screen Transport Access Layer Counter and injection control 8

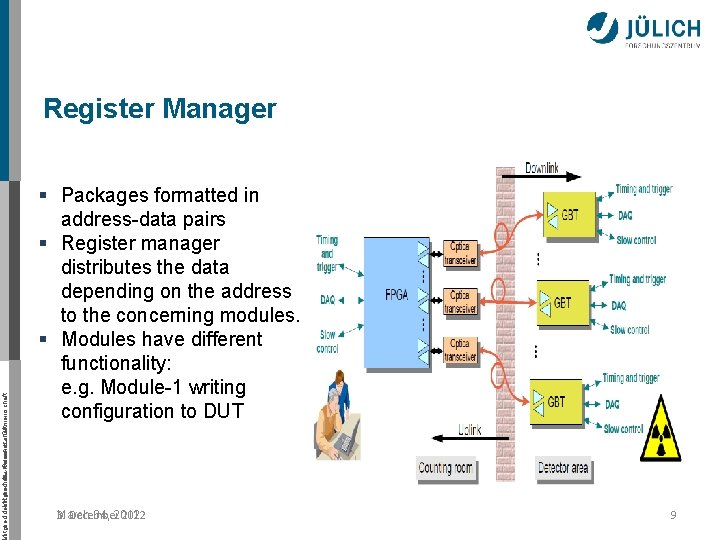

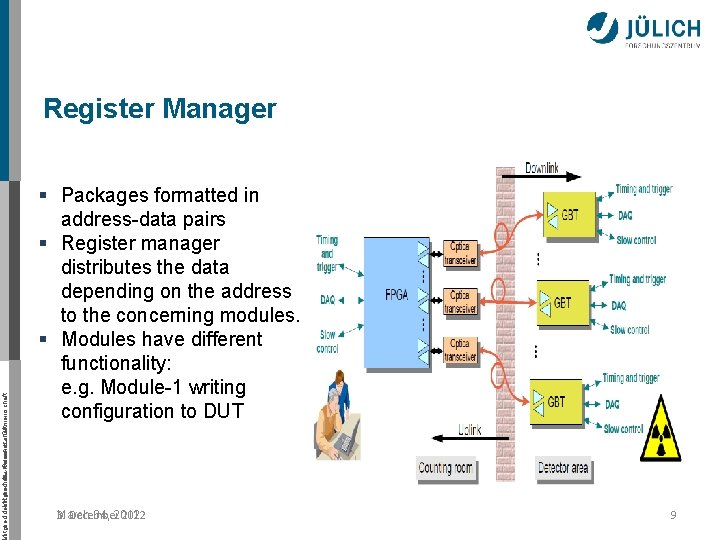

itglied der. Mitglied Helmholtz-Gemeinschaft der Helmholtz-Gemeinschaft Register Manager § Packages formatted in address-data pairs § Register manager distributes the data depending on the address to the concerning modules. § Modules have different functionality: e. g. Module-1 writing configuration to DUT 3. December 2012 March 04, 2012 9

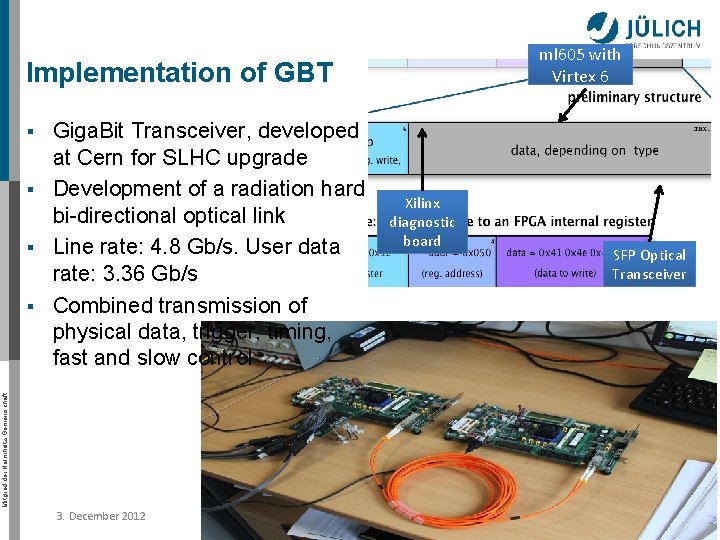

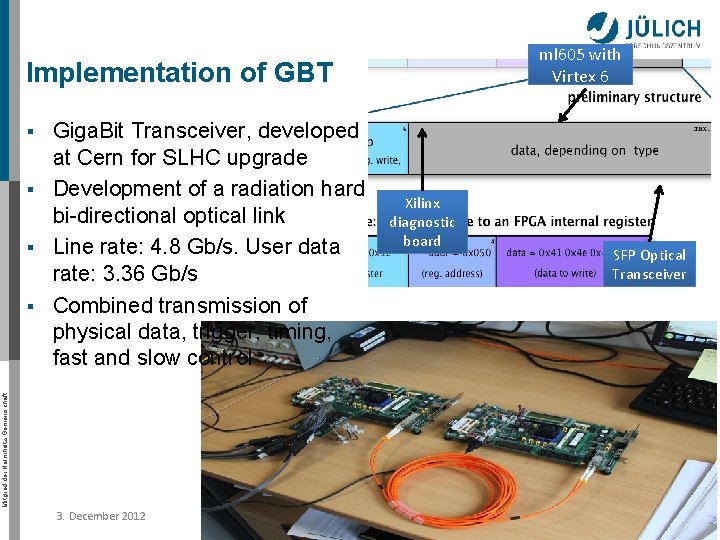

ml 605 with Virtex 6 Implementation of GBT Giga. Bit Transceiver, developed at Cern for SLHC upgrade § Development of a radiation hard bi-directional optical link § Line rate: 4. 8 Gb/s. User data rate: 3. 36 Gb/s § Combined transmission of physical data, trigger, timing, fast and slow control Mitglied der Helmholtz-Gemeinschaft § 3. December 2012 Xilinx diagnostic board SFP Optical Transceiver 10

Implementation of UDP link Mitglied der Helmholtz-Gemeinschaft § Ongoing development: Implementation of communication via UDP § Additional communication link § Standard hardware can be used 3. December 2012 11

Summary • • Mitglied der Helmholtz-Gemeinschaft • • • The Jülich Digital Readout System has been developed to characterize different ASICs for the development of the PANDA detector. The system includes hardware, firmware and software developed with a modular approach for easy adaption to new interfaces. The Readout System is successfully working with the MVD Pixel front end prototype To. Pix 2 and To. Pix 3 A UDP link implementation is under development A GBT link implementation into readout system is under development to interface the next prototype To. Pix 4 3. December 2012 12

Dankeschön Mitglied der Helmholtz-Gemeinschaft Thank you for your attention 3. December 2012 13