Mismatch Modeling of MOS Transistors for Deep Submicron

Mismatch Modeling of MOS Transistors for Deep Sub-micron Technologies Rasit Onur Topaloglu rtopalog@cse. ucsd. edu University of California at San Diego Computer Science and Engineering Department La Jolla, CA, 92093, USA

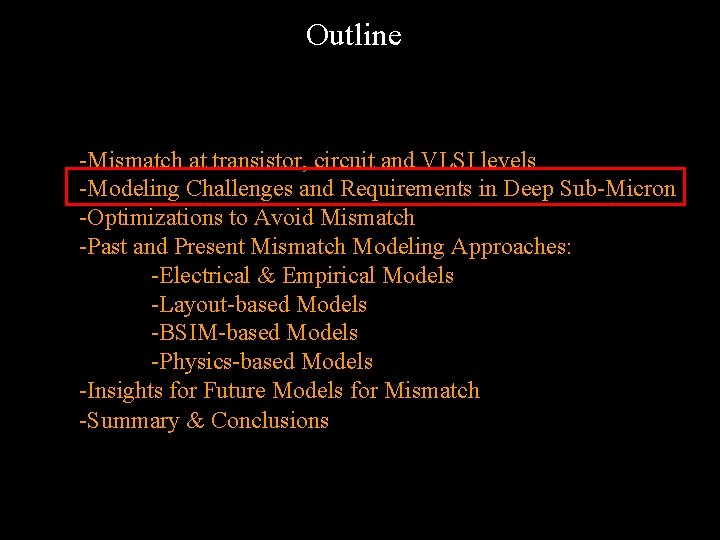

Outline -Mismatch at transistor, circuit and VLSI levels -Modeling Challenges and Requirements in Deep Sub-Micron -Optimizations to Avoid Mismatch -Past and Present Mismatch Modeling Approaches: -Electrical & Empirical Models -Layout-based Models -BSIM-based Models -Physics-based Models -Insights for Future Models for Mismatch -Summary & Conclusions

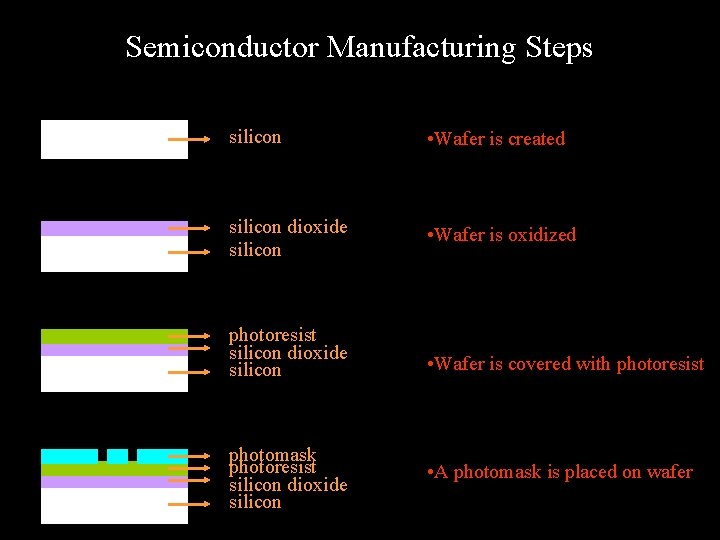

Semiconductor Manufacturing Steps silicon • Wafer is created silicon dioxide silicon • Wafer is oxidized photoresist silicon dioxide silicon photomask photoresist silicon dioxide silicon • Wafer is covered with photoresist • A photomask is placed on wafer

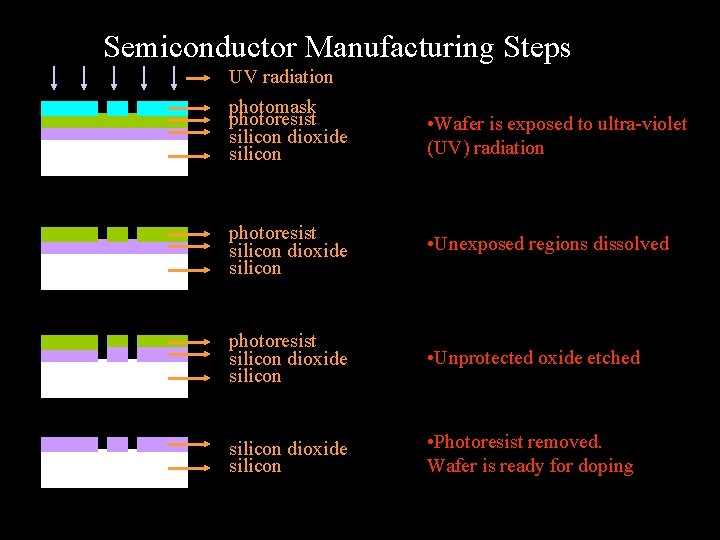

Semiconductor Manufacturing Steps UV radiation photomask photoresist silicon dioxide silicon • Wafer is exposed to ultra-violet (UV) radiation photoresist silicon dioxide silicon • Unexposed regions dissolved photoresist silicon dioxide silicon • Unprotected oxide etched silicon dioxide silicon • Photoresist removed. Wafer is ready for doping

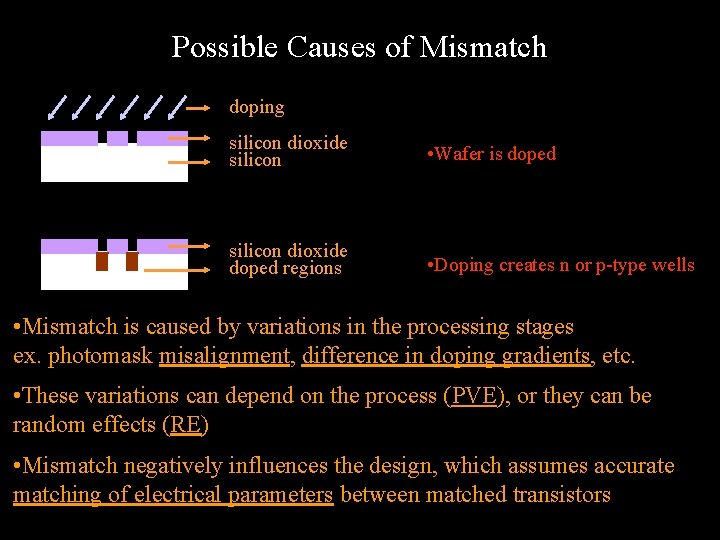

Possible Causes of Mismatch doping silicon dioxide silicon • Wafer is doped silicon dioxide doped regions • Doping creates n or p-type wells • Mismatch is caused by variations in the processing stages ex. photomask misalignment, difference in doping gradients, etc. • These variations can depend on the process (PVE), or they can be random effects (RE) • Mismatch negatively influences the design, which assumes accurate matching of electrical parameters between matched transistors

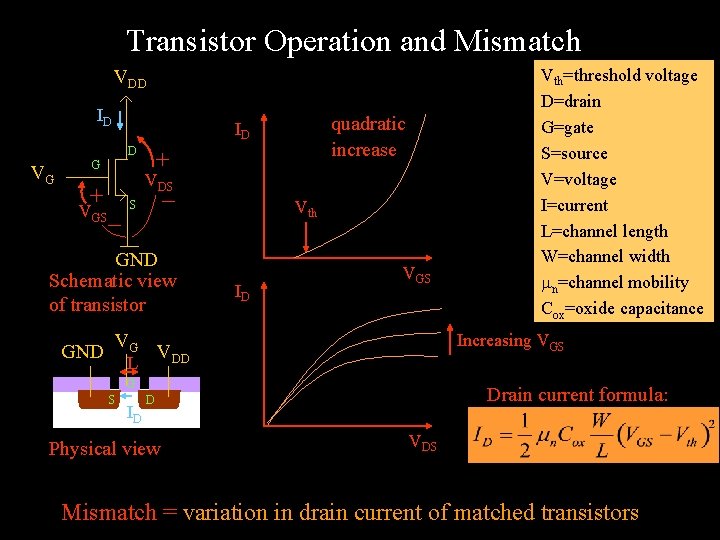

Transistor Operation and Mismatch VDD ID quadratic increase ID D VG G VDS Vth S VGS GND Schematic view of transistor GND VG ID VGS Increasing VGS VDD L G S ID Drain current formula: D Physical view Vth=threshold voltage D=drain G=gate S=source V=voltage I=current L=channel length W=channel width n=channel mobility Cox=oxide capacitance VDS Mismatch = variation in drain current of matched transistors

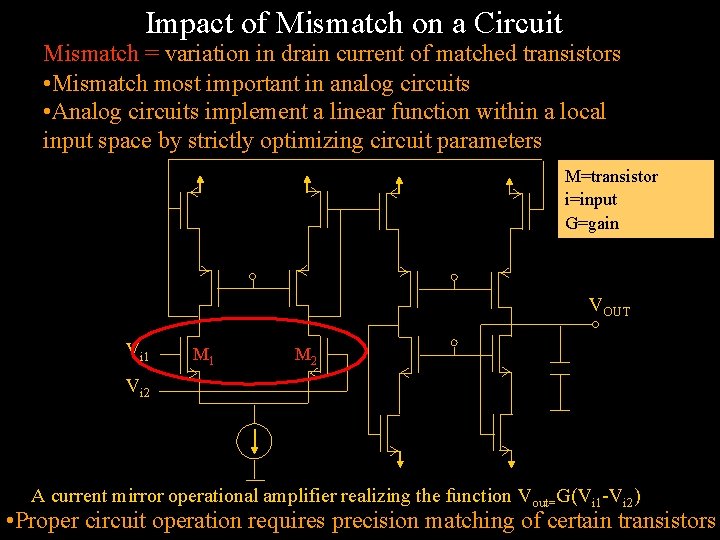

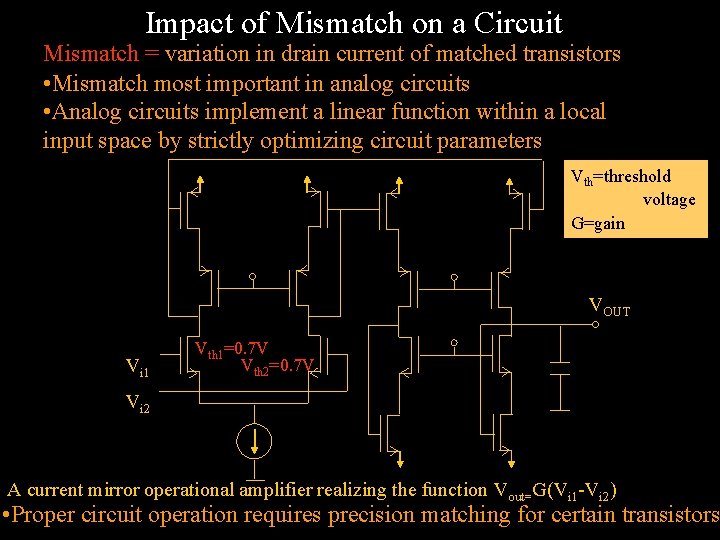

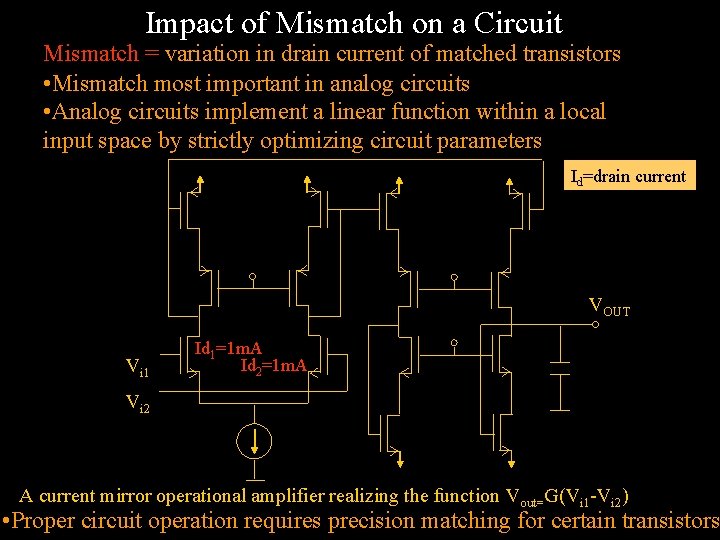

Impact of Mismatch on a Circuit Mismatch = variation in drain current of matched transistors • Mismatch most important in analog circuits • Analog circuits implement a linear function within a local input space by strictly optimizing circuit parameters M=transistor i=input G=gain VOUT Vi 1 M 2 Vi 2 A current mirror operational amplifier realizing the function Vout=G(Vi 1 -Vi 2) • Proper circuit operation requires precision matching of certain transistors

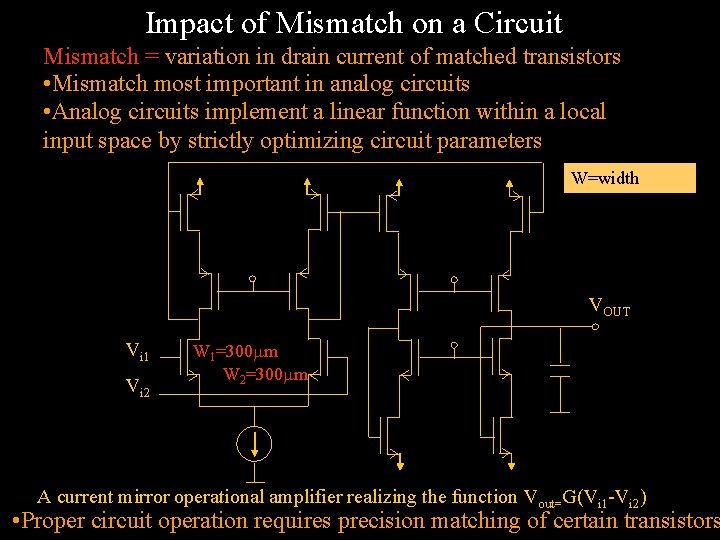

Impact of Mismatch on a Circuit Mismatch = variation in drain current of matched transistors • Mismatch most important in analog circuits • Analog circuits implement a linear function within a local input space by strictly optimizing circuit parameters W=width VOUT Vi 1 Vi 2 W 1=300 m W 2=300 m A current mirror operational amplifier realizing the function Vout=G(Vi 1 -Vi 2) • Proper circuit operation requires precision matching of certain transistors

Impact of Mismatch on a Circuit Mismatch = variation in drain current of matched transistors • Mismatch most important in analog circuits • Analog circuits implement a linear function within a local input space by strictly optimizing circuit parameters Vth=threshold voltage G=gain VOUT Vi 1 Vth 1=0. 7 V Vth 2=0. 7 V Vi 2 A current mirror operational amplifier realizing the function Vout=G(Vi 1 -Vi 2) • Proper circuit operation requires precision matching for certain transistors

Impact of Mismatch on a Circuit Mismatch = variation in drain current of matched transistors • Mismatch most important in analog circuits • Analog circuits implement a linear function within a local input space by strictly optimizing circuit parameters Id=drain current VOUT Vi 1 Id 1=1 m. A Id 2=1 m. A Vi 2 A current mirror operational amplifier realizing the function Vout=G(Vi 1 -Vi 2) • Proper circuit operation requires precision matching for certain transistors

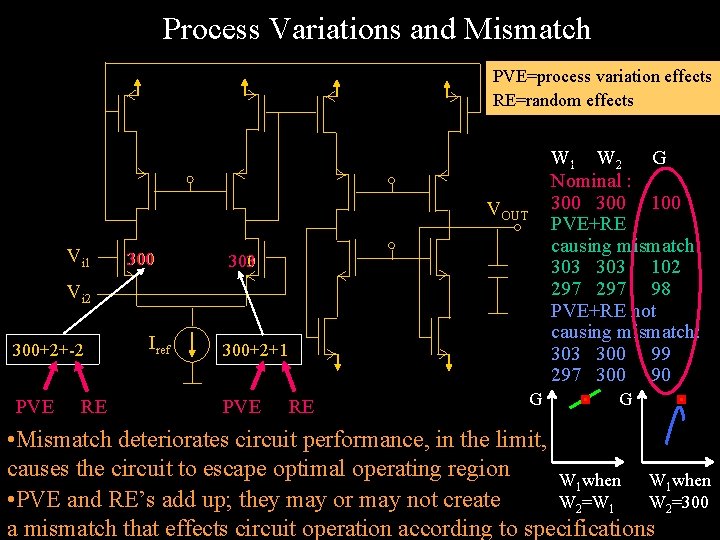

Process Variations and Mismatch PVE=process variation effects RE=random effects W 1 W 2 G Nominal : 300 100 PVE+RE causing mismatch: 303 102 297 98 PVE+RE not causing mismatch: 303 300 99 297 300 90 VOUT Vi 1 300 303 Vi 2 300+2+-2 PVE RE Iref 300+2+1 PVE RE G G • Mismatch deteriorates circuit performance, in the limit, causes the circuit to escape optimal operating region W 1 when • PVE and RE’s add up; they may or may not create W 2=W 1 W 2=300 a mismatch that effects circuit operation according to specifications

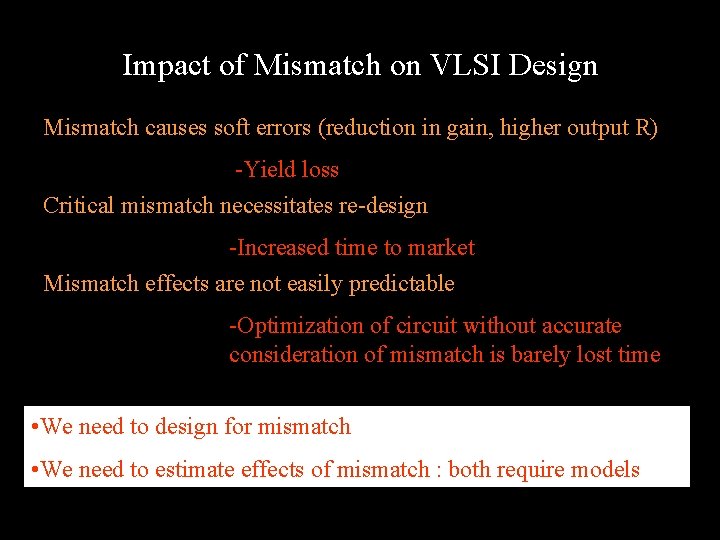

Impact of Mismatch on VLSI Design Mismatch causes soft errors (reduction in gain, higher output R) -Yield loss Critical mismatch necessitates re-design -Increased time to market Mismatch effects are not easily predictable -Optimization of circuit without accurate consideration of mismatch is barely lost time • We need to design for mismatch • We need to estimate effects of mismatch : both require models

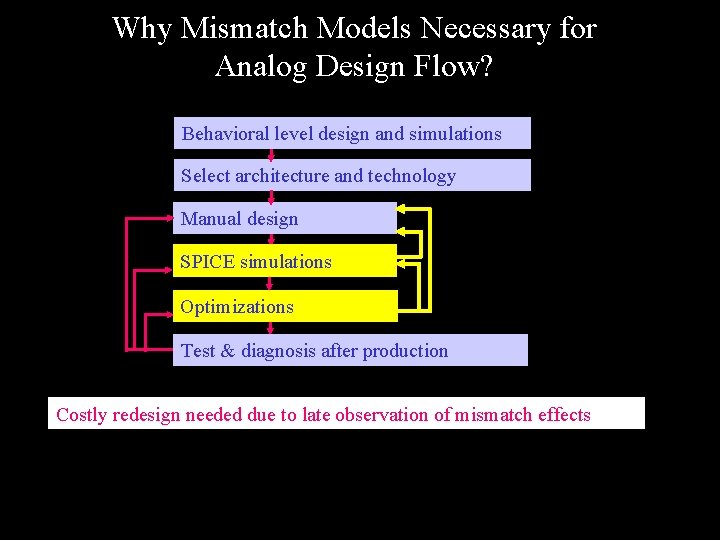

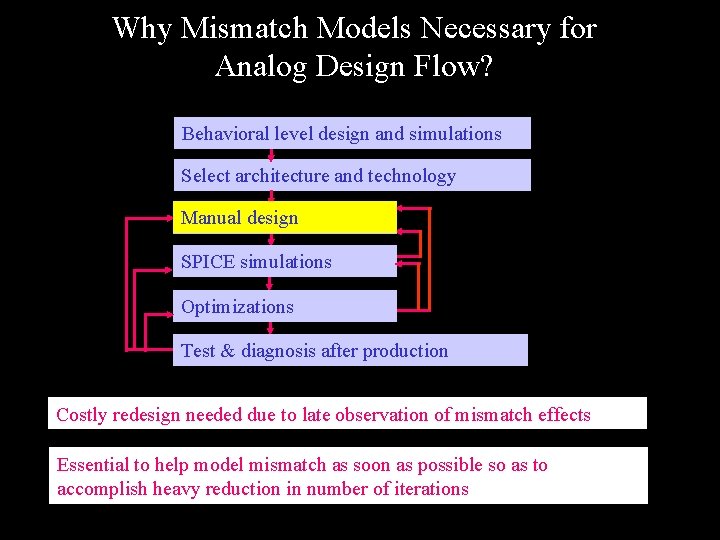

Why Mismatch Models Necessary for Analog Design Flow? Behavioral level design and simulations Select architecture and technology Manual design SPICE simulations Optimizations Test & diagnosis after production Costly redesign needed due to late observation of mismatch effects

Why Mismatch Models Necessary for Analog Design Flow? Behavioral level design and simulations Select architecture and technology Manual design SPICE simulations Optimizations Test & diagnosis after production Costly redesign needed due to late observation of mismatch effects Essential to help model mismatch as soon as possible so as to accomplish heavy reduction in number of iterations

Outline -Mismatch at transistor, circuit and VLSI levels -Modeling Challenges and Requirements in Deep Sub-Micron -Optimizations to Avoid Mismatch -Past and Present Mismatch Modeling Approaches: -Electrical & Empirical Models -Layout-based Models -BSIM-based Models -Physics-based Models -Insights for Future Models for Mismatch -Summary & Conclusions

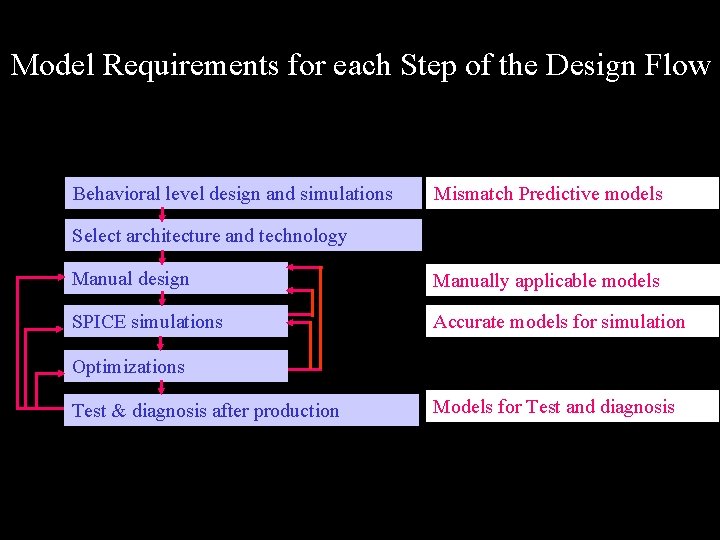

Model Requirements for each Step of the Design Flow Behavioral level design and simulations Mismatch Predictive models Select architecture and technology Manual design Manually applicable models SPICE simulations Accurate models for simulation Optimizations Test & diagnosis after production Models for Test and diagnosis

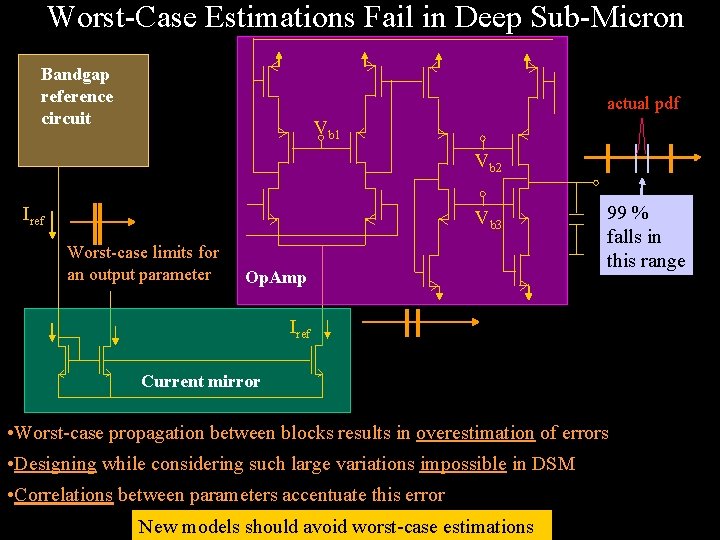

Worst-Case Estimations Fail in Deep Sub-Micron Bandgap reference circuit actual pdf Vb 1 Vb 2 Iref Vb 3 Worst-case limits for an output parameter Op. Amp 99 % falls in this range Iref Current mirror • Worst-case propagation between blocks results in overestimation of errors • Designing while considering such large variations impossible in DSM • Correlations between parameters accentuate this error New models should avoid worst-case estimations

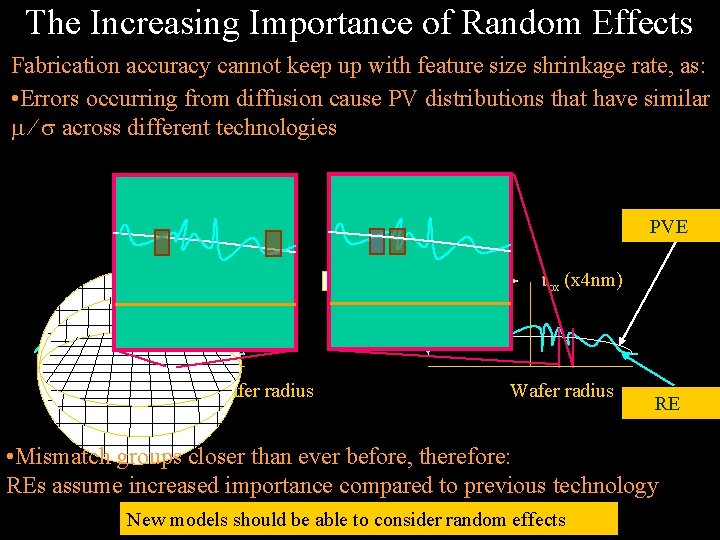

The Increasing Importance of Random Effects Fabrication accuracy cannot keep up with feature size shrinkage rate, as: • Errors occurring from diffusion cause PV distributions that have similar across different technologies PVE tox (x 40 nm) Wafer radius newer technology tox (x 4 nm) Wafer radius RE • Mismatch groups closer than ever before, therefore: REs assume increased importance compared to previous technology New models should be able to consider random effects

Outline -Mismatch at transistor, circuit and VLSI levels -Modeling Challenges and Requirements in Deep Sub-Micron -Optimizations to Avoid Mismatch -Past and Present Mismatch Modeling Approaches: -Electrical & Empirical Models -Layout-based Models -BSIM-based Models -Physics-based Models -Insights for Future Models for Mismatch -Summary & Conclusions

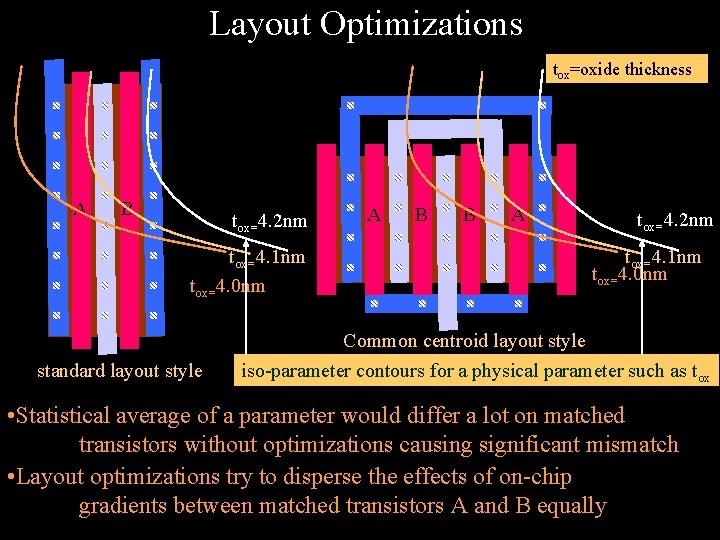

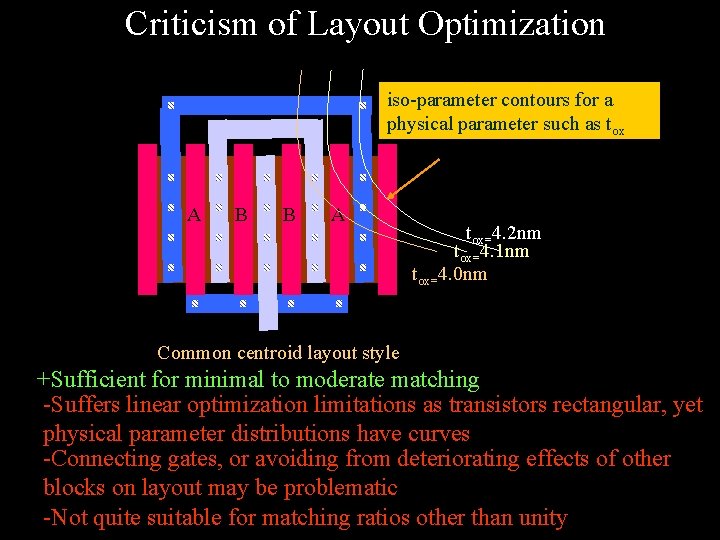

Layout Optimizations tox=oxide thickness A B tox=4. 2 nm tox=4. 1 nm tox=4. 0 nm standard layout style A B B A tox=4. 2 nm tox=4. 1 nm tox=4. 0 nm Common centroid layout style iso-parameter contours for a physical parameter such as tox • Statistical average of a parameter would differ a lot on matched transistors without optimizations causing significant mismatch • Layout optimizations try to disperse the effects of on-chip gradients between matched transistors A and B equally

Criticism of Layout Optimization iso-parameter contours for a physical parameter such as tox A B B A tox=4. 2 nm tox=4. 1 nm tox=4. 0 nm Common centroid layout style +Sufficient for minimal to moderate matching -Suffers linear optimization limitations as transistors rectangular, yet physical parameter distributions have curves -Connecting gates, or avoiding from deteriorating effects of other blocks on layout may be problematic -Not quite suitable for matching ratios other than unity

![Circuit Optimizations PSD=power spectral density DAC=digital to analog converter x[n] b Thermometer Encoder A Circuit Optimizations PSD=power spectral density DAC=digital to analog converter x[n] b Thermometer Encoder A](http://slidetodoc.com/presentation_image_h/750026c64f070bcc812cc339308fd8cc/image-22.jpg)

Circuit Optimizations PSD=power spectral density DAC=digital to analog converter x[n] b Thermometer Encoder A Digital-to-Analog Converter (DAC) x 1[n] . . y [n] 1 -Bit 1 DAC 1 -Bit y 2[n] DAC . . y[n] 1 -Bit x 2 b[n] DAC y 2 b [n] • The circuit implements an ideal staircase transfer function between input and output PSD • Mismatch within DAC’s cause a related performance parameter, PSD, to fail specifications x[n] frequency I. Galton and P. Carbone, “A Rigorous Error Analysis of D/A Conversion with Dynamic Element Matching, ” IEEE TCAS-II, 1995

![Circuit Optimizations b x 1[n] . . Scrambler x[n] Thermometer Encoder A Low Harmonic Circuit Optimizations b x 1[n] . . Scrambler x[n] Thermometer Encoder A Low Harmonic](http://slidetodoc.com/presentation_image_h/750026c64f070bcc812cc339308fd8cc/image-23.jpg)

Circuit Optimizations b x 1[n] . . Scrambler x[n] Thermometer Encoder A Low Harmonic DAC . . PSD y [n] 1 -Bit 1 DAC 1 -Bit y 2[n] DAC . . y[n] frequency 1 -Bit x 2 b[n] DAC y 2 b [n] • Scrambler randomly selects 1 -Bit DACs to be used in computation I. Galton and P. Carbone, “A Rigorous Error Analysis of D/A Conversion with Dynamic Element Matching, ” IEEE TCAS-II, 1995

![Circuit Optimizations b x 1[n]. . Scrambler x[n] Thermometer Encoder A Low Harmonic DAC Circuit Optimizations b x 1[n]. . Scrambler x[n] Thermometer Encoder A Low Harmonic DAC](http://slidetodoc.com/presentation_image_h/750026c64f070bcc812cc339308fd8cc/image-24.jpg)

Circuit Optimizations b x 1[n]. . Scrambler x[n] Thermometer Encoder A Low Harmonic DAC . . PSD y 1[n] 1 -Bit DAC 1 -Bit y 2[n] DAC . . y[n] frequency 1 -Bit x 2 b[n] DAC y 2 b [n] • Scrambler randomly selects 1 -Bit DACs to be used in computation • Mismatch in 1 -Bit DAC blocks averaged, compensating deteriorating effects of mismatch on distortion I. Galton and P. Carbone, “A Rigorous Error Analysis of D/A Conversion with Dynamic Element Matching, ” IEEE TCAS-II, 1995

![Criticism of Circuit Optimizations b x 1[n]. . Scrambler x[n] Thermometer Encoder A Low Criticism of Circuit Optimizations b x 1[n]. . Scrambler x[n] Thermometer Encoder A Low](http://slidetodoc.com/presentation_image_h/750026c64f070bcc812cc339308fd8cc/image-25.jpg)

Criticism of Circuit Optimizations b x 1[n]. . Scrambler x[n] Thermometer Encoder A Low Harmonic DAC . . y [n] 1 -Bit 1 DAC 1 -Bit y 2[n] DAC . . y[n] 1 -Bit x 2 b[n] DAC y 2 b [n] +May be the best way to optimize for a single parameter -Architecture specific, hence requires design time -It is usually necessary to optimize a circuit for more than one parameter

Outline -Mismatch at transistor, circuit and VLSI levels -Modeling Challenges and Requirements in Deep Sub-Micron -Optimizations to Avoid Mismatch -Past and Present Mismatch Modeling Approaches: -Electrical & Empirical Models -Layout-based Models -BSIM-based Models -Physics-based Models -Insights for Future Models for Mismatch -Summary & Conclusions

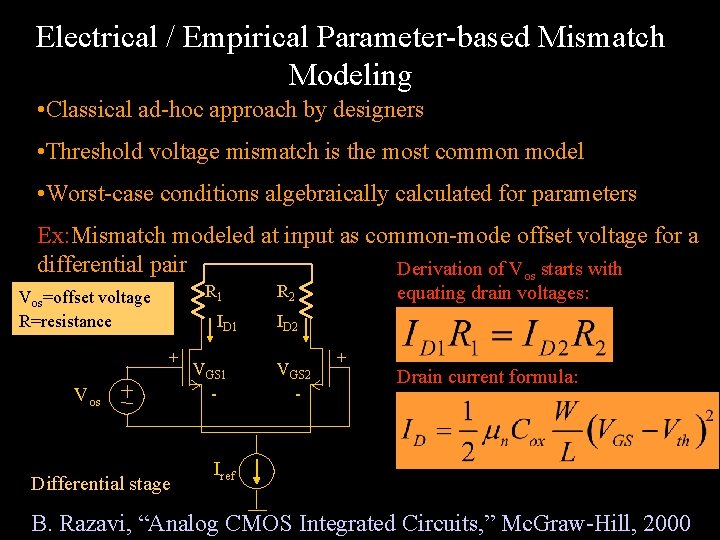

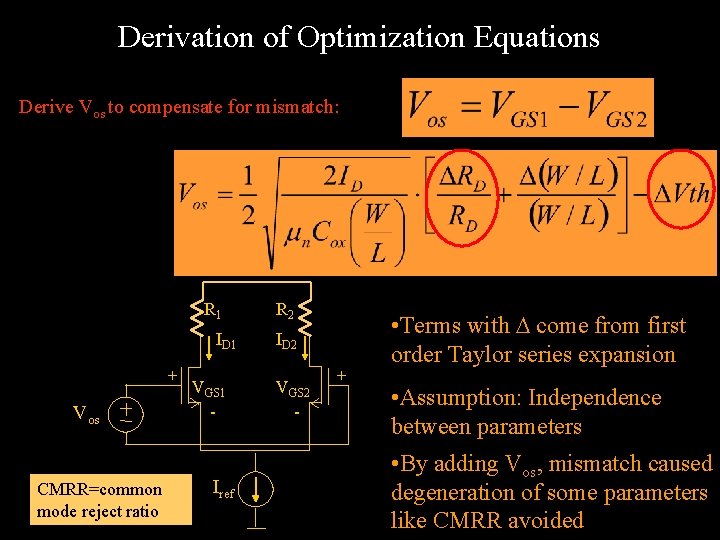

Electrical / Empirical Parameter-based Mismatch Modeling • Classical ad-hoc approach by designers • Threshold voltage mismatch is the most common model • Worst-case conditions algebraically calculated for parameters Ex: Mismatch modeled at input as common-mode offset voltage for a differential pair Derivation of Vos starts with R 1 Vos=offset voltage R=resistance ID 1 + Vos Differential stage VGS 1 - R 2 equating drain voltages: ID 2 VGS 2 - + Drain current formula: Iref B. Razavi, “Analog CMOS Integrated Circuits, ” Mc. Graw-Hill, 2000

Derivation of Optimization Equations Derive Vos to compensate for mismatch: R 1 ID 1 + Vos CMRR=common mode reject ratio VGS 1 - Iref R 2 ID 2 VGS 2 - + • Terms with come from first order Taylor series expansion • Assumption: Independence between parameters • By adding Vos, mismatch caused degeneration of some parameters like CMRR avoided

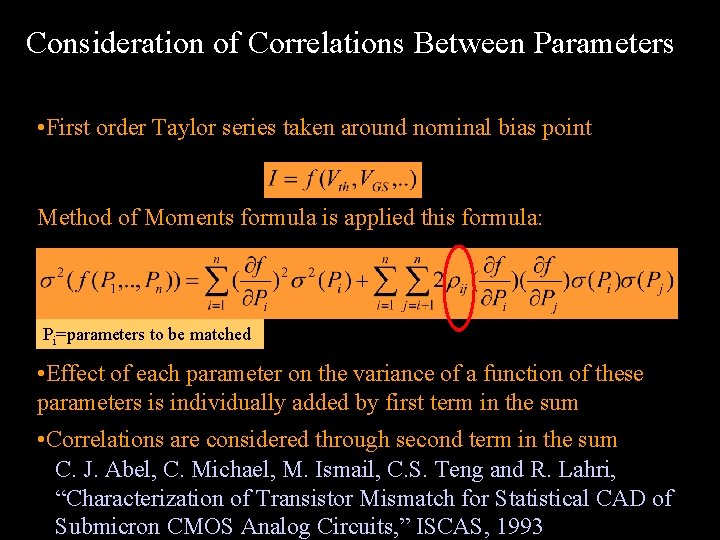

Consideration of Correlations Between Parameters • First order Taylor series taken around nominal bias point Method of Moments formula is applied this formula: Pi=parameters to be matched • Effect of each parameter on the variance of a function of these parameters is individually added by first term in the sum • Correlations are considered through second term in the sum C. J. Abel, C. Michael, M. Ismail, C. S. Teng and R. Lahri, “Characterization of Transistor Mismatch for Statistical CAD of Submicron CMOS Analog Circuits, ” ISCAS, 1993

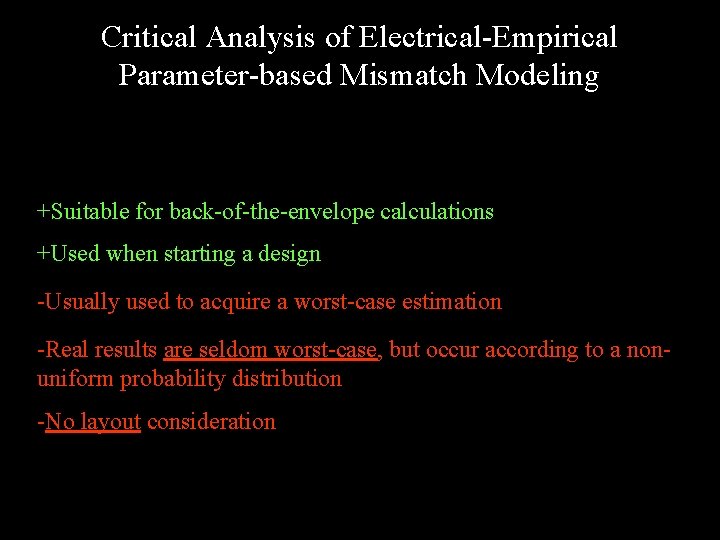

Critical Analysis of Electrical-Empirical Parameter-based Mismatch Modeling +Suitable for back-of-the-envelope calculations +Used when starting a design -Usually used to acquire a worst-case estimation -Real results are seldom worst-case, but occur according to a nonuniform probability distribution -No layout consideration

Outline -Mismatch at transistor, circuit and VLSI levels -Modeling Challenges and Requirements in Deep Sub-Micron -Optimizations to Avoid Mismatch -Past and Present Mismatch Modeling Approaches: -Electrical & Empirical Models -Layout-based Models -BSIM-based Models -Physics-based Models -Insights for Future Models for Mismatch -Summary & Conclusions

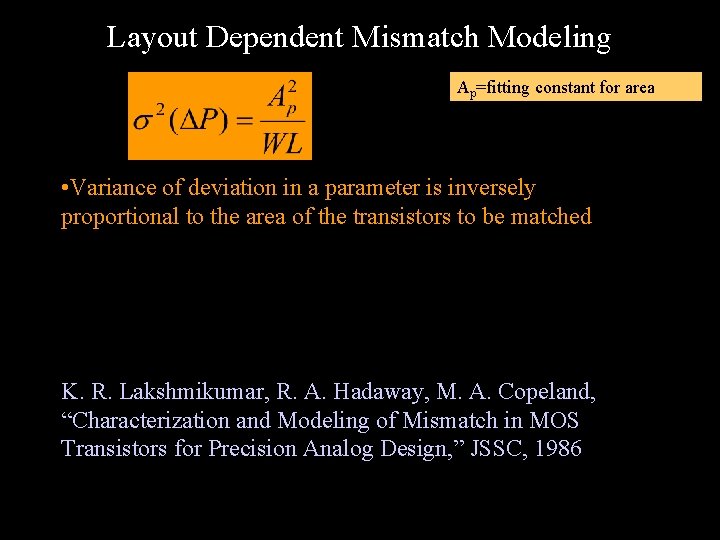

Layout Dependent Mismatch Modeling Ap=fitting constant for area • Variance of deviation in a parameter is inversely proportional to the area of the transistors to be matched K. R. Lakshmikumar, R. A. Hadaway, M. A. Copeland, “Characterization and Modeling of Mismatch in MOS Transistors for Precision Analog Design, ” JSSC, 1986

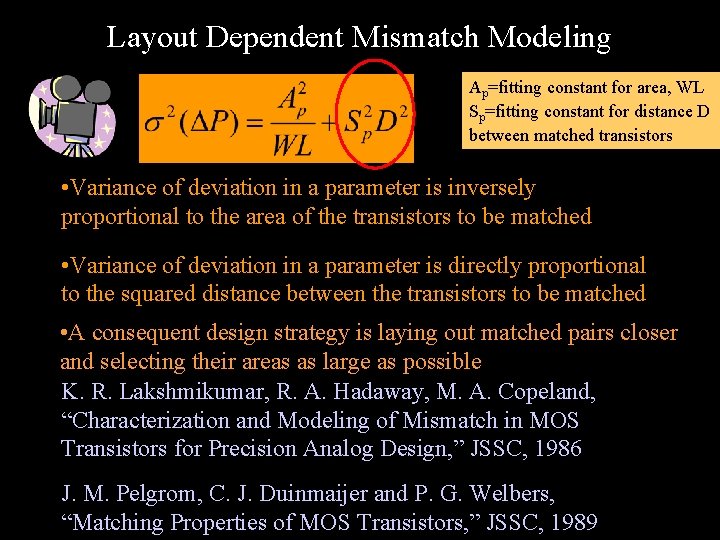

Layout Dependent Mismatch Modeling Ap=fitting constant for area, WL Sp=fitting constant for distance D between matched transistors • Variance of deviation in a parameter is inversely proportional to the area of the transistors to be matched • Variance of deviation in a parameter is directly proportional to the squared distance between the transistors to be matched • A consequent design strategy is laying out matched pairs closer and selecting their areas as large as possible K. R. Lakshmikumar, R. A. Hadaway, M. A. Copeland, “Characterization and Modeling of Mismatch in MOS Transistors for Precision Analog Design, ” JSSC, 1986 J. M. Pelgrom, C. J. Duinmaijer and P. G. Welbers, “Matching Properties of MOS Transistors, ” JSSC, 1989

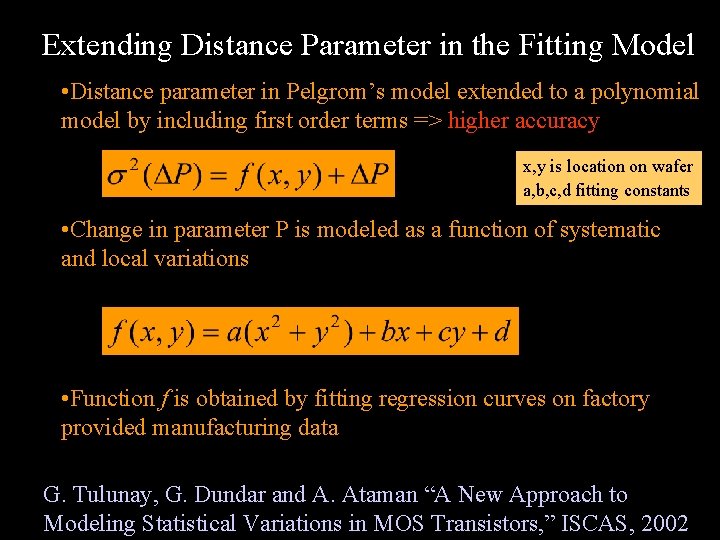

Extending Distance Parameter in the Fitting Model • Distance parameter in Pelgrom’s model extended to a polynomial model by including first order terms => higher accuracy x, y is location on wafer a, b, c, d fitting constants • Change in parameter P is modeled as a function of systematic and local variations • Function f is obtained by fitting regression curves on factory provided manufacturing data G. Tulunay, G. Dundar and A. Ataman “A New Approach to Modeling Statistical Variations in MOS Transistors, ” ISCAS, 2002

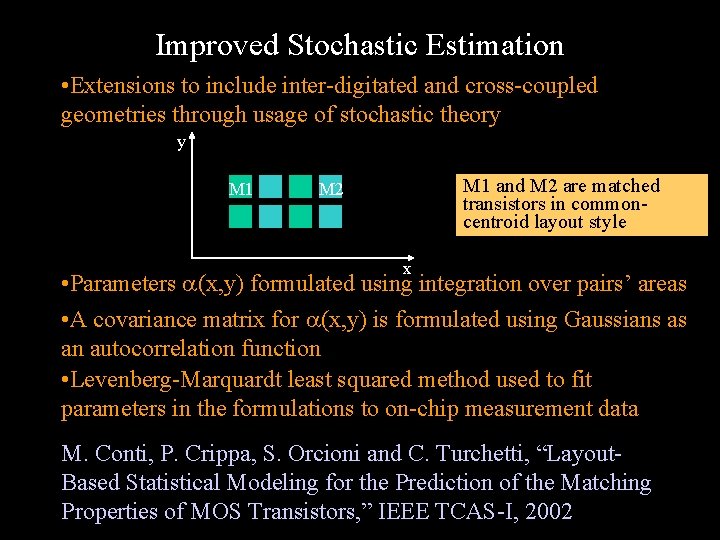

Improved Stochastic Estimation • Extensions to include inter-digitated and cross-coupled geometries through usage of stochastic theory y M 1 and M 2 are matched transistors in commoncentroid layout style M 2 x • Parameters (x, y) formulated using integration over pairs’ areas • A covariance matrix for (x, y) is formulated using Gaussians as an autocorrelation function • Levenberg-Marquardt least squared method used to fit parameters in the formulations to on-chip measurement data M. Conti, P. Crippa, S. Orcioni and C. Turchetti, “Layout. Based Statistical Modeling for the Prediction of the Matching Properties of MOS Transistors, ” IEEE TCAS-I, 2002

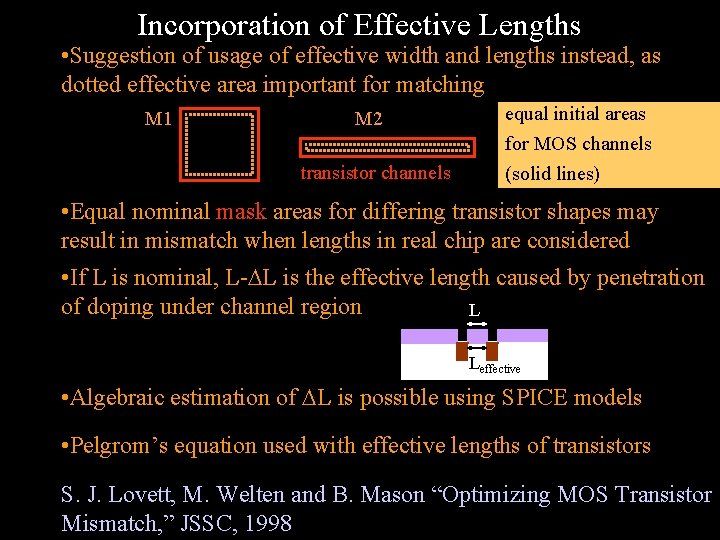

Incorporation of Effective Lengths • Suggestion of usage of effective width and lengths instead, as dotted effective area important for matching M 1 M 2 equal initial areas for MOS channels transistor channels (solid lines) • Equal nominal mask areas for differing transistor shapes may result in mismatch when lengths in real chip are considered • If L is nominal, L- L is the effective length caused by penetration of doping under channel region L Leffective • Algebraic estimation of L is possible using SPICE models • Pelgrom’s equation used with effective lengths of transistors S. J. Lovett, M. Welten and B. Mason “Optimizing MOS Transistor Mismatch, ” JSSC, 1998

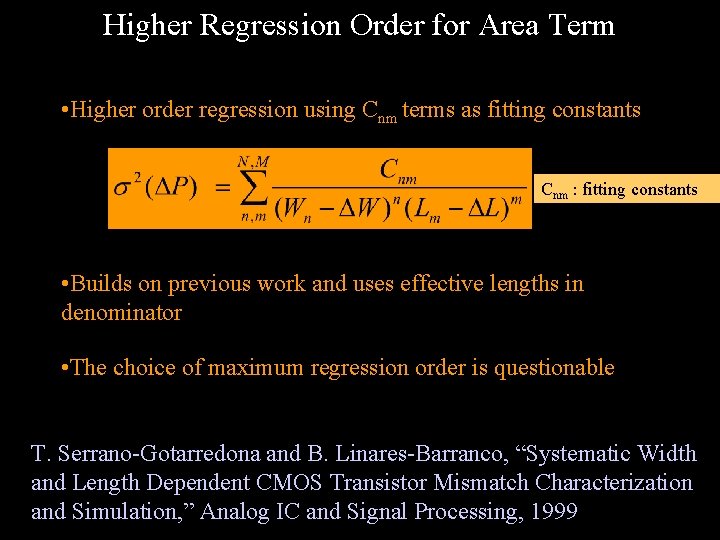

Higher Regression Order for Area Term • Higher order regression using Cnm terms as fitting constants Cnm : fitting constants • Builds on previous work and uses effective lengths in denominator • The choice of maximum regression order is questionable T. Serrano-Gotarredona and B. Linares-Barranco, “Systematic Width and Length Dependent CMOS Transistor Mismatch Characterization and Simulation, ” Analog IC and Signal Processing, 1999

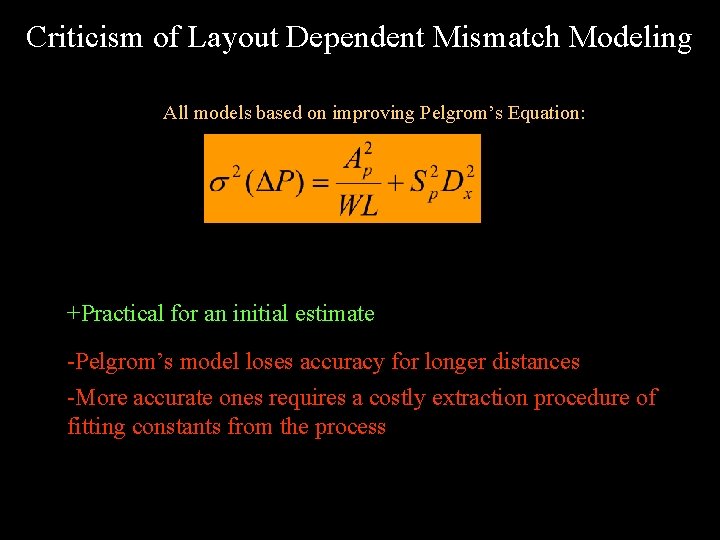

Criticism of Layout Dependent Mismatch Modeling All models based on improving Pelgrom’s Equation: +Practical for an initial estimate -Pelgrom’s model loses accuracy for longer distances -More accurate ones requires a costly extraction procedure of fitting constants from the process

Outline -Mismatch at transistor, circuit and VLSI levels -Modeling Challenges and Requirements in Deep Sub-Micron -Optimizations to Avoid Mismatch -Past and Present Mismatch Modeling Approaches: -Electrical & Empirical Models -Layout-based Models -BSIM-based Models -Physics-based Models -Insights for Future Models for Mismatch -Summary & Conclusions

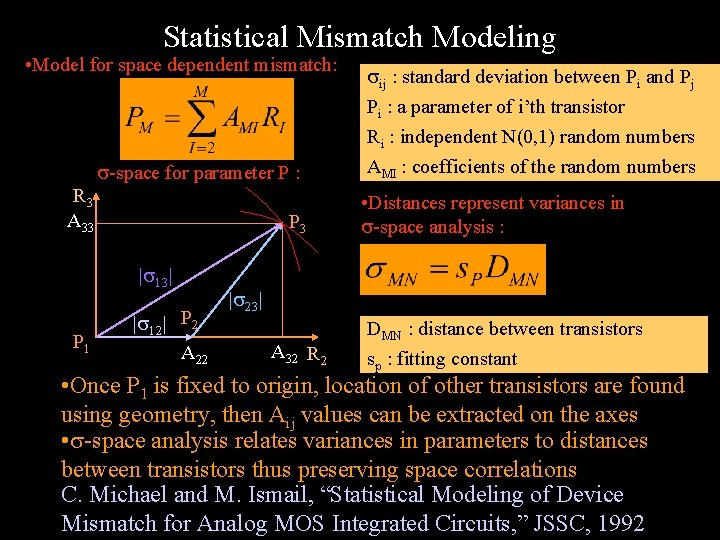

Statistical Mismatch Modeling • Model for space dependent mismatch: ij : standard deviation between Pi and Pj Pi : a parameter of i’th transistor -space for parameter P : R 3 A 33 P 3 | 13| P 1 | 12| P 2 A 22 Ri : independent N(0, 1) random numbers AMI : coefficients of the random numbers • Distances represent variances in -space analysis : | 23| A 32 R 2 DMN : distance between transistors sp : fitting constant • Once P 1 is fixed to origin, location of other transistors are found using geometry, then Aij values can be extracted on the axes • -space analysis relates variances in parameters to distances between transistors thus preserving space correlations C. Michael and M. Ismail, “Statistical Modeling of Device Mismatch for Analog MOS Integrated Circuits, ” JSSC, 1992

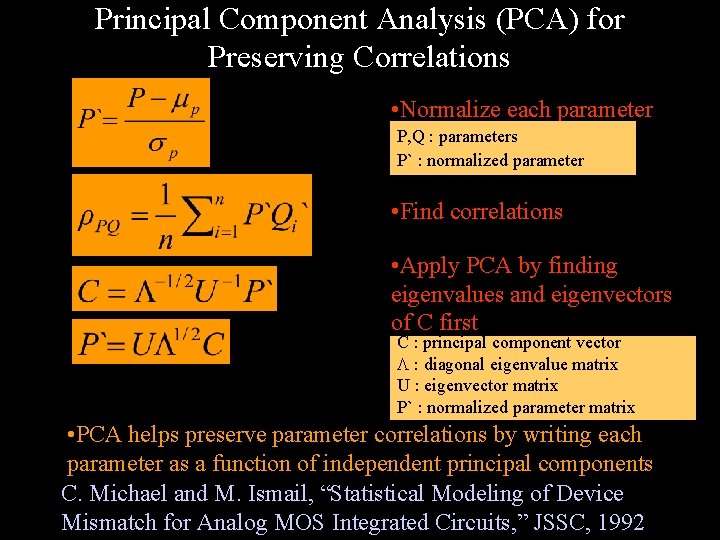

Principal Component Analysis (PCA) for Preserving Correlations • Normalize each parameter P, Q : parameters P` : normalized parameter • Find correlations • Apply PCA by finding eigenvalues and eigenvectors of C first C : principal component vector : diagonal eigenvalue matrix U : eigenvector matrix P` : normalized parameter matrix • PCA helps preserve parameter correlations by writing each parameter as a function of independent principal components C. Michael and M. Ismail, “Statistical Modeling of Device Mismatch for Analog MOS Integrated Circuits, ” JSSC, 1992

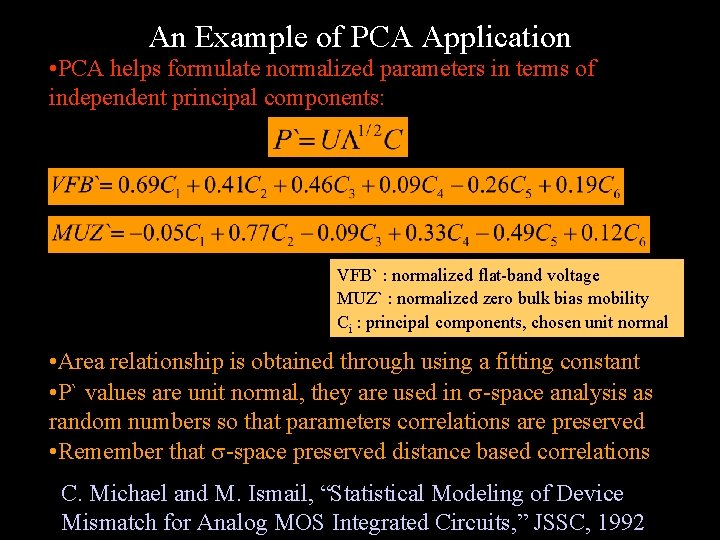

An Example of PCA Application • PCA helps formulate normalized parameters in terms of independent principal components: VFB` : normalized flat-band voltage MUZ` : normalized zero bulk bias mobility Ci : principal components, chosen unit normal • Area relationship is obtained through using a fitting constant • P` values are unit normal, they are used in -space analysis as random numbers so that parameters correlations are preserved • Remember that -space preserved distance based correlations C. Michael and M. Ismail, “Statistical Modeling of Device Mismatch for Analog MOS Integrated Circuits, ” JSSC, 1992

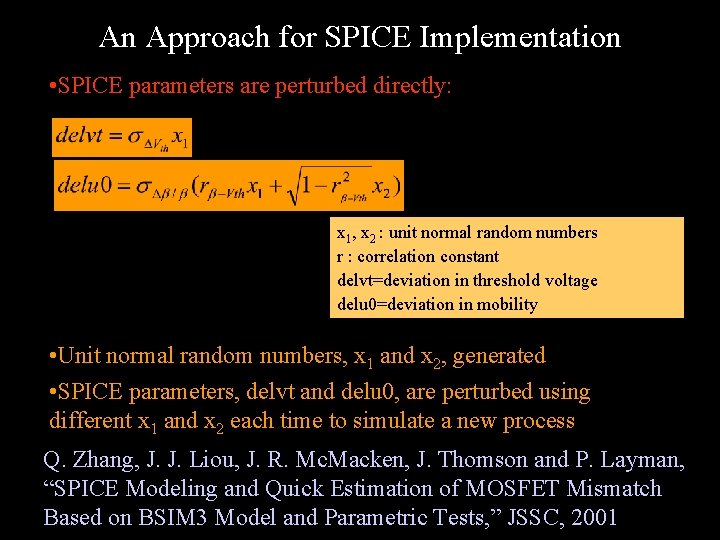

An Approach for SPICE Implementation • SPICE parameters are perturbed directly: x 1, x 2 : unit normal random numbers r : correlation constant delvt=deviation in threshold voltage delu 0=deviation in mobility • Unit normal random numbers, x 1 and x 2, generated • SPICE parameters, delvt and delu 0, are perturbed using different x 1 and x 2 each time to simulate a new process Q. Zhang, J. J. Liou, J. R. Mc. Macken, J. Thomson and P. Layman, “SPICE Modeling and Quick Estimation of MOSFET Mismatch Based on BSIM 3 Model and Parametric Tests, ” JSSC, 2001

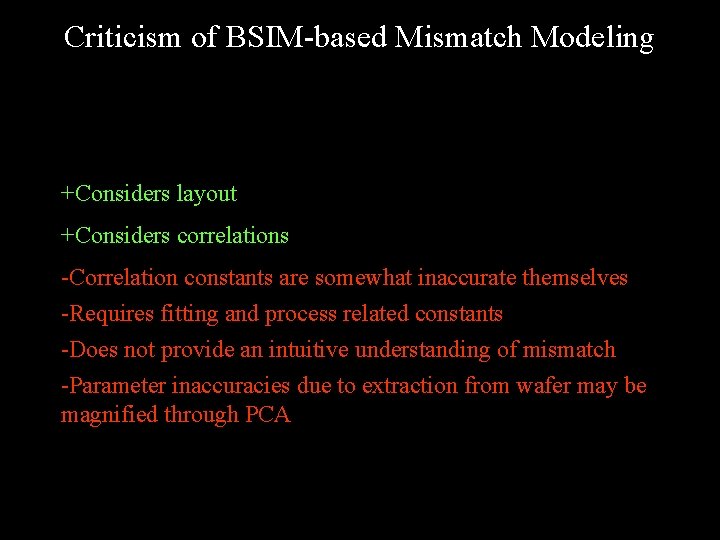

Criticism of BSIM-based Mismatch Modeling +Considers layout +Considers correlations -Correlation constants are somewhat inaccurate themselves -Requires fitting and process related constants -Does not provide an intuitive understanding of mismatch -Parameter inaccuracies due to extraction from wafer may be magnified through PCA

Outline -Mismatch at transistor, circuit and VLSI levels -Modeling Challenges and Requirements in Deep Sub-Micron -Optimizations to Avoid Mismatch -Past and Present Mismatch Modeling Approaches: -Electrical & Empirical Models -Layout-based Models -BSIM-based Models -Physics-based Models -Insights for Future Models for Mismatch -Summary & Conclusions

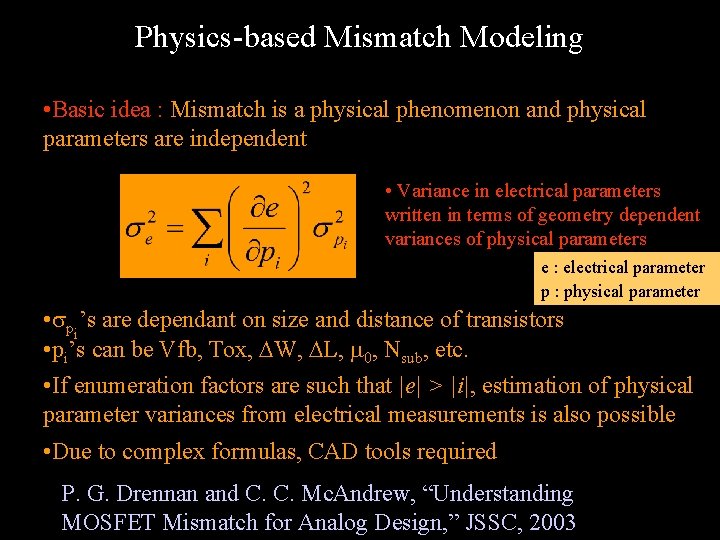

Physics-based Mismatch Modeling • Basic idea : Mismatch is a physical phenomenon and physical parameters are independent • Variance in electrical parameters written in terms of geometry dependent variances of physical parameters e : electrical parameter p : physical parameter • pi’s are dependant on size and distance of transistors • pi’s can be Vfb, Tox, W, L, 0, Nsub, etc. • If enumeration factors are such that |e| > |i|, estimation of physical parameter variances from electrical measurements is also possible • Due to complex formulas, CAD tools required P. G. Drennan and C. C. Mc. Andrew, “Understanding MOSFET Mismatch for Analog Design, ” JSSC, 2003

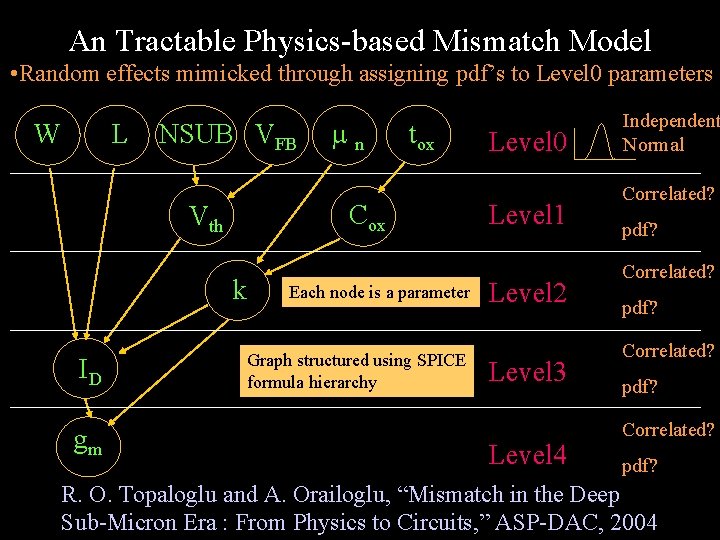

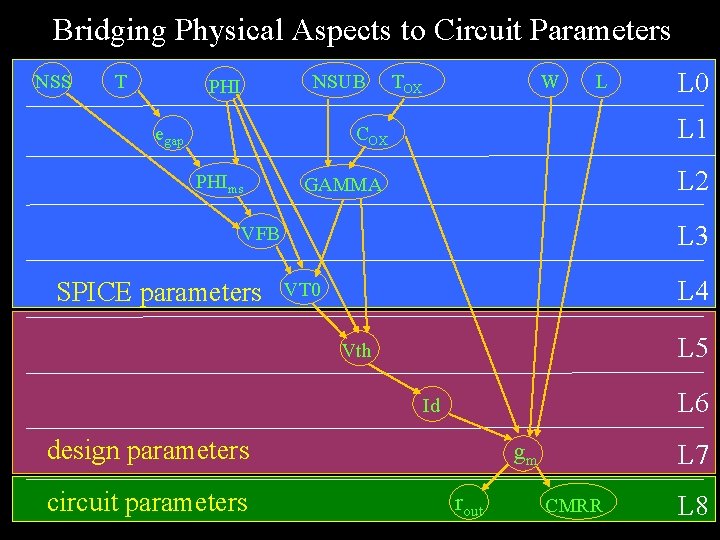

An Tractable Physics-based Mismatch Model • Random effects mimicked through assigning pdf’s to Level 0 parameters W L NSUB VFB k gm tox Cox Vth ID n Each node is a parameter Graph structured using SPICE formula hierarchy Level 0 Level 1 Level 2 Level 3 Level 4 Independent Normal Correlated? pdf? R. O. Topaloglu and A. Orailoglu, “Mismatch in the Deep Sub-Micron Era : From Physics to Circuits, ” ASP-DAC, 2004

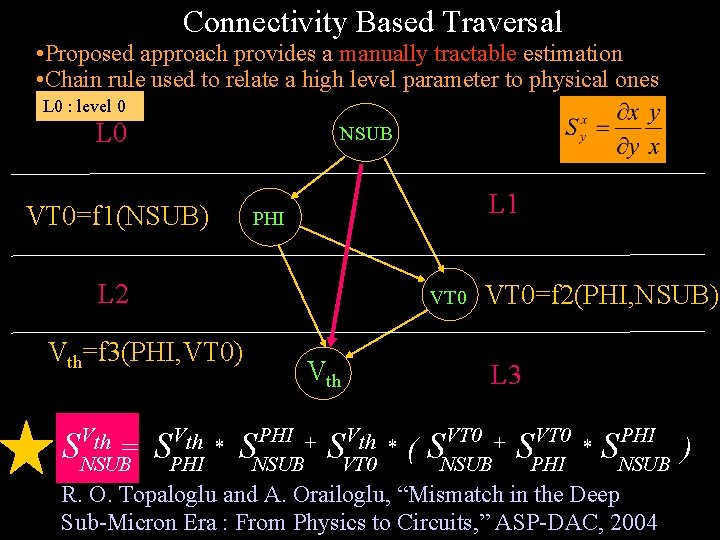

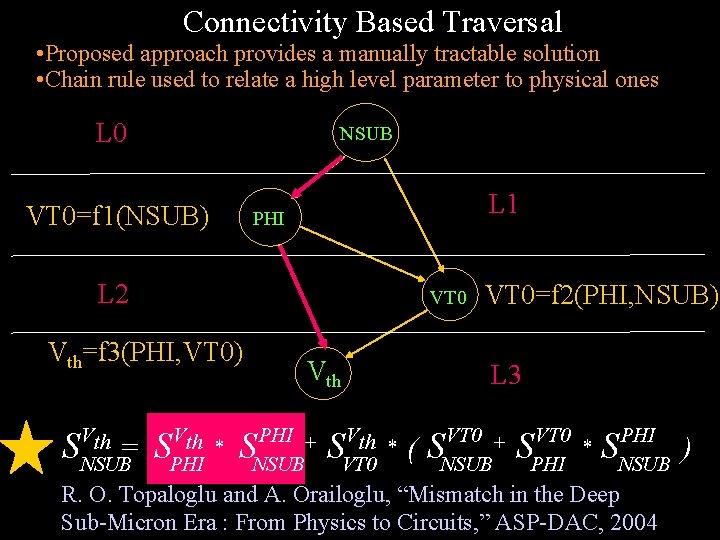

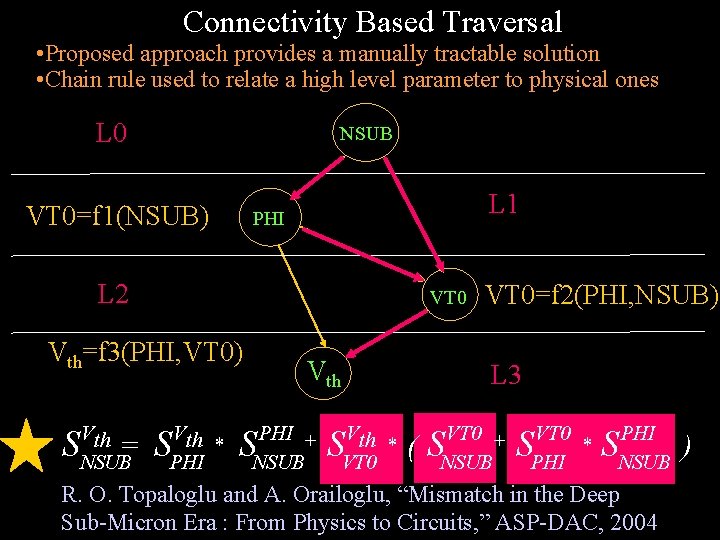

Connectivity Based Traversal • Proposed approach provides a manually tractable estimation • Chain rule used to relate a high level parameter to physical ones L 0 : level 0 L 0 NSUB VT 0=f 1(NSUB) L 1 PHI L 2 VT 0 Vth=f 3(PHI, VT 0) Vth = NSUB S Vth * PHI S Vth PHI + NSUB S VT 0=f 2(PHI, NSUB) L 3 Vth * VT 0 S VT 0 + NSUB (S VT 0 * PHI S PHI NSUB S R. O. Topaloglu and A. Orailoglu, “Mismatch in the Deep Sub-Micron Era : From Physics to Circuits, ” ASP-DAC, 2004 )

Connectivity Based Traversal • Proposed approach provides a manually tractable solution • Chain rule used to relate a high level parameter to physical ones L 0 NSUB VT 0=f 1(NSUB) L 1 PHI L 2 VT 0 Vth=f 3(PHI, VT 0) Vth = NSUB S Vth * PHI S Vth PHI + NSUB S VT 0=f 2(PHI, NSUB) L 3 Vth * VT 0 S VT 0 + NSUB (S VT 0 * PHI S PHI NSUB S R. O. Topaloglu and A. Orailoglu, “Mismatch in the Deep Sub-Micron Era : From Physics to Circuits, ” ASP-DAC, 2004 )

Connectivity Based Traversal • Proposed approach provides a manually tractable solution • Chain rule used to relate a high level parameter to physical ones L 0 NSUB VT 0=f 1(NSUB) L 1 PHI L 2 VT 0 Vth=f 3(PHI, VT 0) Vth = NSUB S Vth * PHI S Vth PHI + NSUB S VT 0=f 2(PHI, NSUB) L 3 Vth * VT 0 S VT 0 + NSUB (S VT 0 * PHI S PHI NSUB S R. O. Topaloglu and A. Orailoglu, “Mismatch in the Deep Sub-Micron Era : From Physics to Circuits, ” ASP-DAC, 2004 )

Bridging Physical Aspects to Circuit Parameters NSS T NSUB PHI W L L 1 GAMMA L 2 L 3 VFB SPICE parameters L 4 VT 0 L 5 Vth L 6 Id design parameters circuit parameters L 0 COX egap PHIms TOX gm rout L 7 CMRR L 8

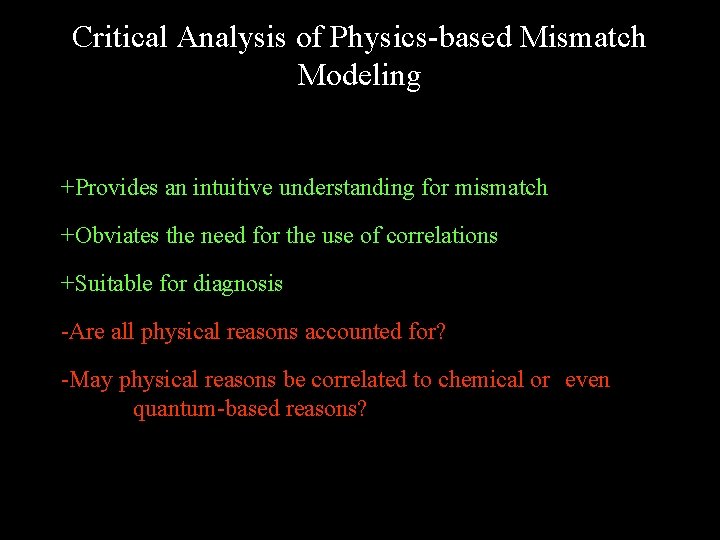

Critical Analysis of Physics-based Mismatch Modeling +Provides an intuitive understanding for mismatch +Obviates the need for the use of correlations +Suitable for diagnosis -Are all physical reasons accounted for? -May physical reasons be correlated to chemical or even quantum-based reasons?

Outline -Mismatch at transistor, circuit and VLSI levels -Modeling Challenges and Requirements in Deep Sub-Micron -Optimizations to Avoid Mismatch -Past and Present Mismatch Modeling Approaches: -Electrical & Empirical Models -Layout-based Models -BSIM-based Models -Physics-based Models -Insights for Future Models for Mismatch -Summary & Conclusions

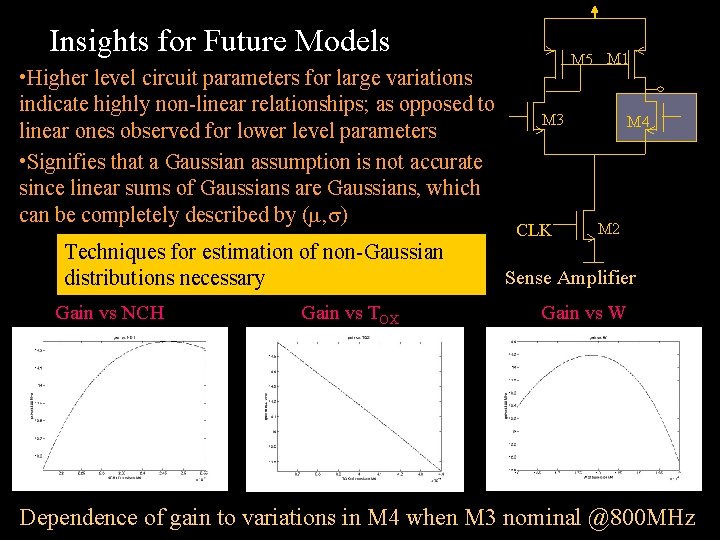

Insights for Future Models • Higher level circuit parameters for large variations indicate highly non-linear relationships; as opposed to linear ones observed for lower level parameters • Signifies that a Gaussian assumption is not accurate since linear sums of Gaussians are Gaussians, which can be completely described by ( , ) Techniques for estimation of non-Gaussian distributions necessary Gain vs NCH Gain vs TOX M 5 M 1 M 3 CLK M 4 M 2 Sense Amplifier Gain vs W Dependence of gain to variations in M 4 when M 3 nominal @800 MHz

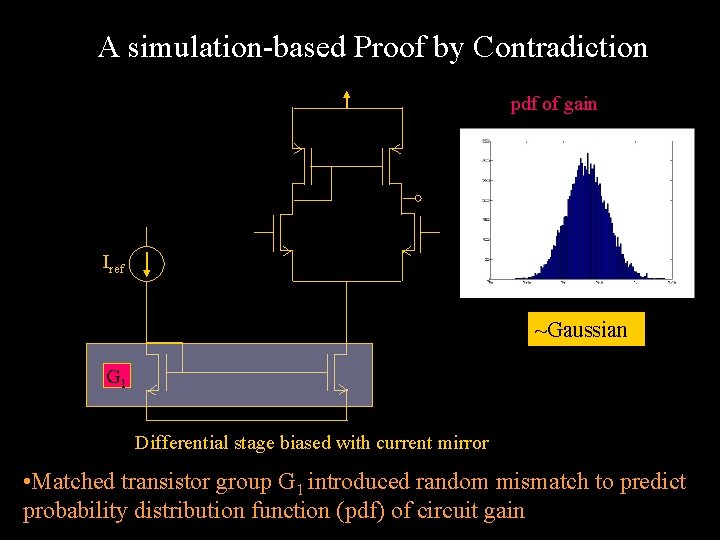

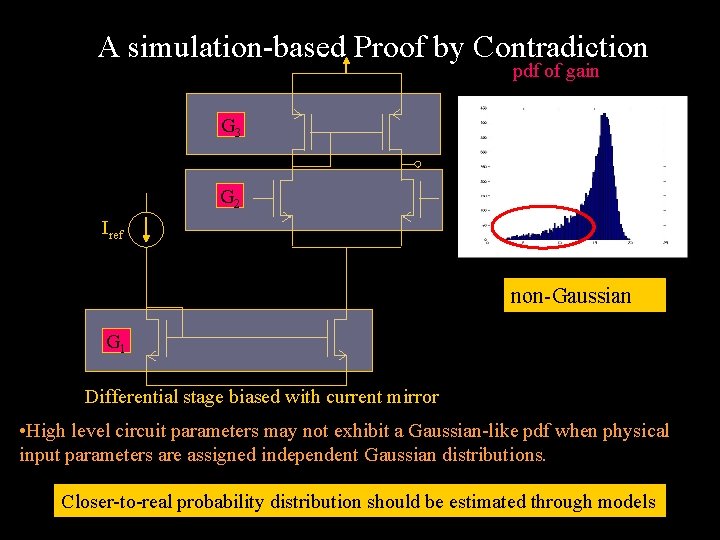

A simulation-based Proof by Contradiction pdf of gain Iref ~Gaussian G 1 Differential stage biased with current mirror • Matched transistor group G 1 introduced random mismatch to predict probability distribution function (pdf) of circuit gain

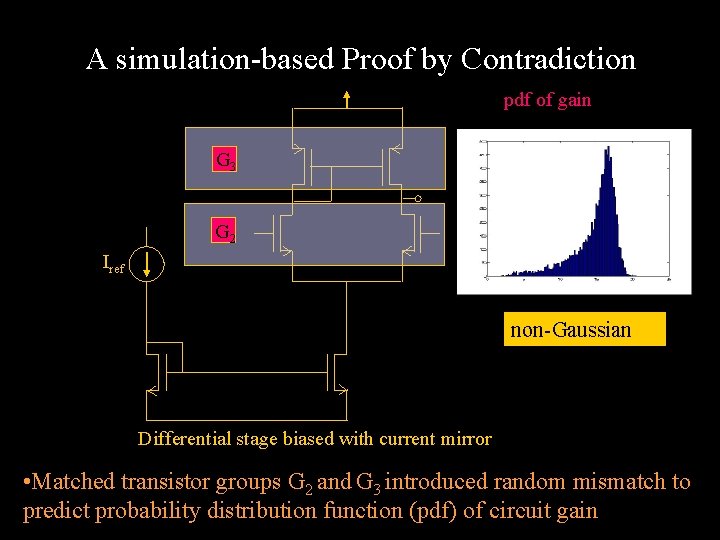

A simulation-based Proof by Contradiction pdf of gain G 3 G 2 Iref non-Gaussian Differential stage biased with current mirror • Matched transistor groups G 2 and G 3 introduced random mismatch to predict probability distribution function (pdf) of circuit gain

A simulation-based Proof by Contradiction pdf of gain G 3 G 2 Iref non-Gaussian G 1 Differential stage biased with current mirror • High level circuit parameters may not exhibit a Gaussian-like pdf when physical input parameters are assigned independent Gaussian distributions. Closer-to-real probability distribution should be estimated through models

Summary: • Circuit optimizations : remedy for a single circuit parameter • Layout optimizations : used whenever possible yet insufficient • Electrical / Empirical models : used when starting a design • Layout-based models : Pelgrom’s Equation used to incorporate layout information • BSIM-based models : used for direct SPICE implementation • Physics-based models : used for better intuition and accuracy

Conclusions • A spectrum of mismatch models has been presented • Deep sub-micron modeling needs has been identified as avoiding worst-case limits, consideration of random effects and an early estimation of mismatch • Future models should target to obtain closer-to-real probability distribution functions of performance parameters

- Slides: 59