MIPS Assembly Arithmetic Instructions MIPS Assembly 1 All

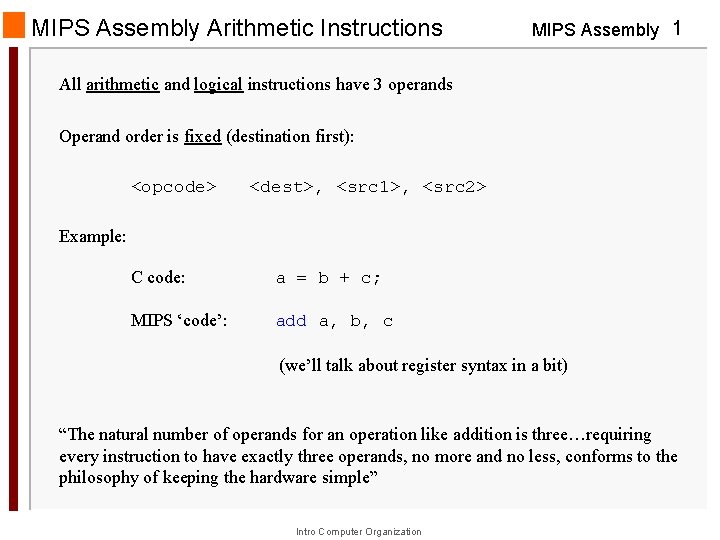

MIPS Assembly Arithmetic Instructions MIPS Assembly 1 All arithmetic and logical instructions have 3 operands Operand order is fixed (destination first): <opcode> <dest>, <src 1>, <src 2> Example: C code: a = b + c; MIPS ‘code’: add a, b, c (we’ll talk about register syntax in a bit) “The natural number of operands for an operation like addition is three…requiring every instruction to have exactly three operands, no more and no less, conforms to the philosophy of keeping the hardware simple” Intro Computer Organization

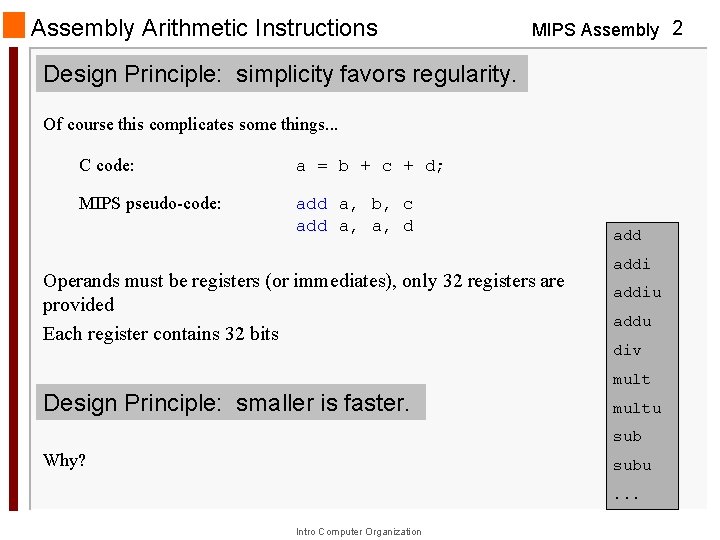

Assembly Arithmetic Instructions MIPS Assembly 2 Design Principle: simplicity favors regularity. Of course this complicates some things. . . C code: a = b + c + d; MIPS pseudo-code: add a, b, c add a, a, d Operands must be registers (or immediates), only 32 registers are provided Each register contains 32 bits addiu addu div mult Design Principle: smaller is faster. multu sub Why? subu. . . Intro Computer Organization

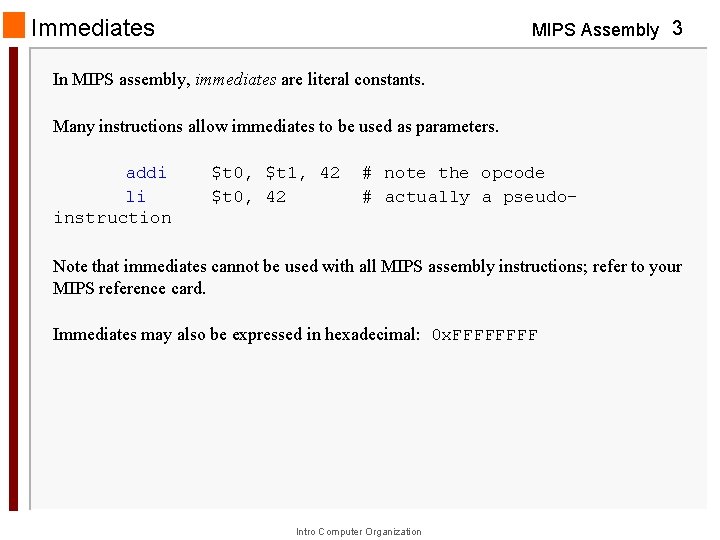

Immediates MIPS Assembly 3 In MIPS assembly, immediates are literal constants. Many instructions allow immediates to be used as parameters. addi li instruction $t 0, $t 1, 42 $t 0, 42 # note the opcode # actually a pseudo- Note that immediates cannot be used with all MIPS assembly instructions; refer to your MIPS reference card. Immediates may also be expressed in hexadecimal: 0 x. FFFF Intro Computer Organization

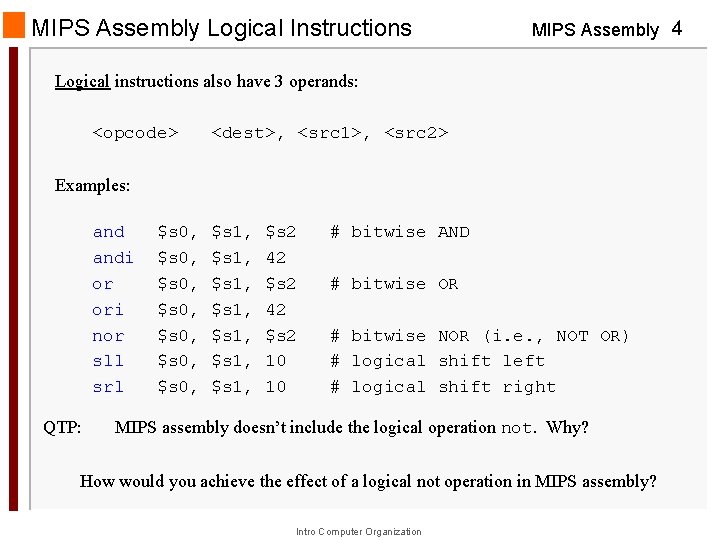

MIPS Assembly Logical Instructions MIPS Assembly 4 Logical instructions also have 3 operands: <opcode> <dest>, <src 1>, <src 2> Examples: andi or ori nor sll srl QTP: $s 0, $s 0, $s 1, $s 1, $s 2 42 $s 2 10 10 # bitwise AND # bitwise OR # bitwise NOR (i. e. , NOT OR) # logical shift left # logical shift right MIPS assembly doesn’t include the logical operation not. Why? How would you achieve the effect of a logical not operation in MIPS assembly? Intro Computer Organization

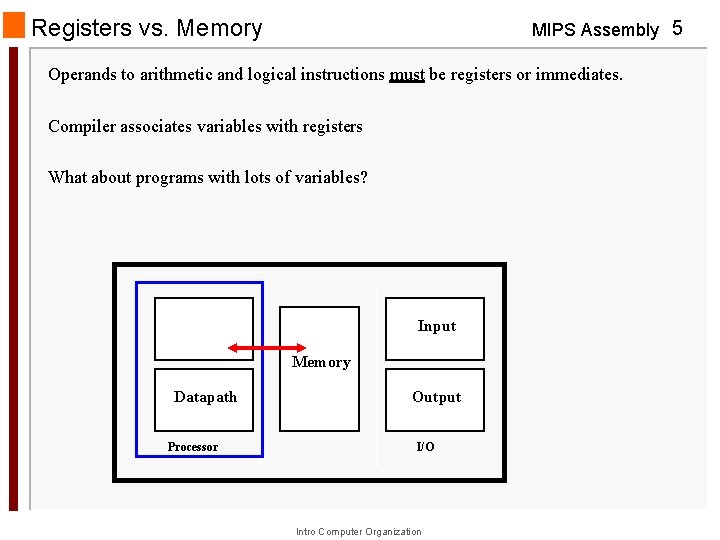

Registers vs. Memory MIPS Assembly 5 Operands to arithmetic and logical instructions must be registers or immediates. Compiler associates variables with registers What about programs with lots of variables? Input Control Memory Datapath Processor Output I/O Intro Computer Organization

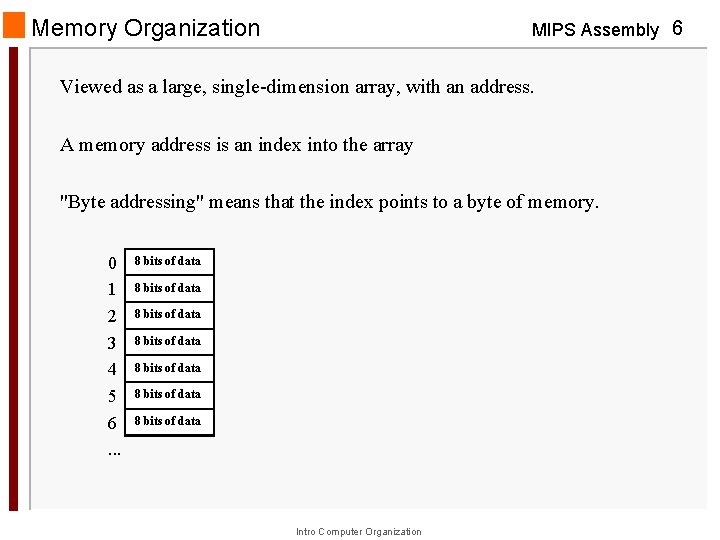

Memory Organization MIPS Assembly 6 Viewed as a large, single-dimension array, with an address. A memory address is an index into the array "Byte addressing" means that the index points to a byte of memory. 0 1 2 3 4 5 6. . . 8 bits of data 8 bits of data Intro Computer Organization

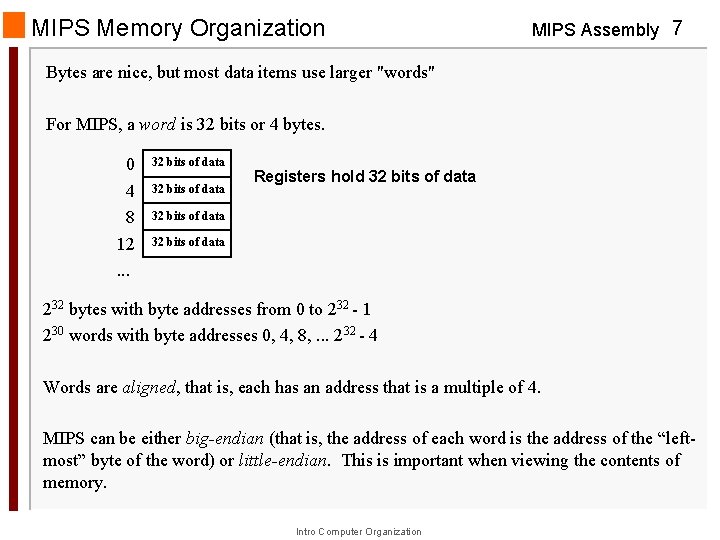

MIPS Memory Organization MIPS Assembly 7 Bytes are nice, but most data items use larger "words" For MIPS, a word is 32 bits or 4 bytes. 0 4 8 12. . . 32 bits of data Registers hold 32 bits of data 232 bytes with byte addresses from 0 to 232 - 1 230 words with byte addresses 0, 4, 8, . . . 232 - 4 Words are aligned, that is, each has an address that is a multiple of 4. MIPS can be either big-endian (that is, the address of each word is the address of the “leftmost” byte of the word) or little-endian. This is important when viewing the contents of memory. Intro Computer Organization

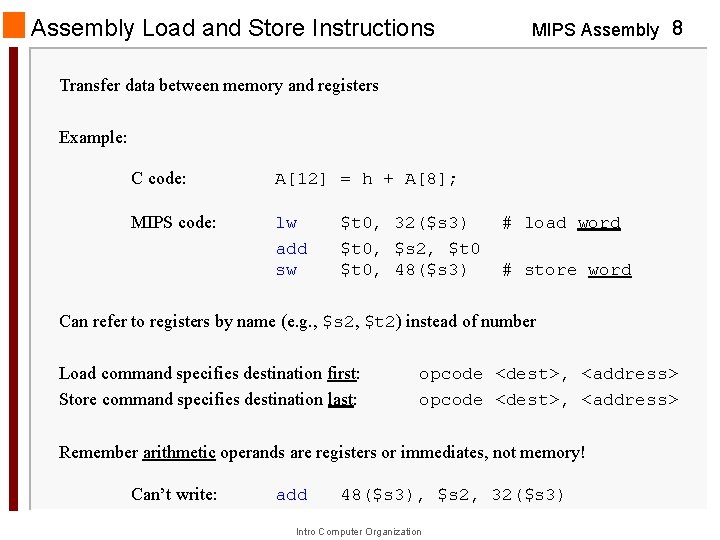

Assembly Load and Store Instructions MIPS Assembly 8 Transfer data between memory and registers Example: C code: A[12] = h + A[8]; MIPS code: lw add sw $t 0, 32($s 3) $t 0, $s 2, $t 0, 48($s 3) # load word # store word Can refer to registers by name (e. g. , $s 2, $t 2) instead of number Load command specifies destination first: Store command specifies destination last: opcode <dest>, <address> Remember arithmetic operands are registers or immediates, not memory! Can’t write: add 48($s 3), $s 2, 32($s 3) Intro Computer Organization

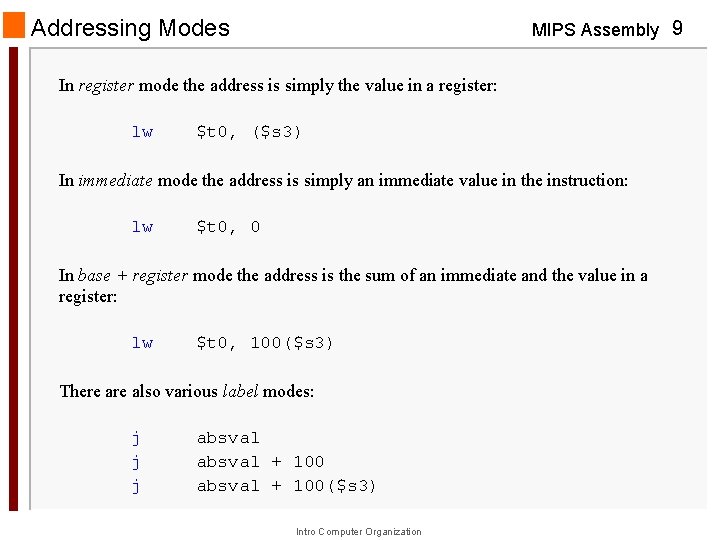

Addressing Modes MIPS Assembly 9 In register mode the address is simply the value in a register: lw $t 0, ($s 3) In immediate mode the address is simply an immediate value in the instruction: lw $t 0, 0 In base + register mode the address is the sum of an immediate and the value in a register: lw $t 0, 100($s 3) There also various label modes: j j j absval + 100($s 3) Intro Computer Organization

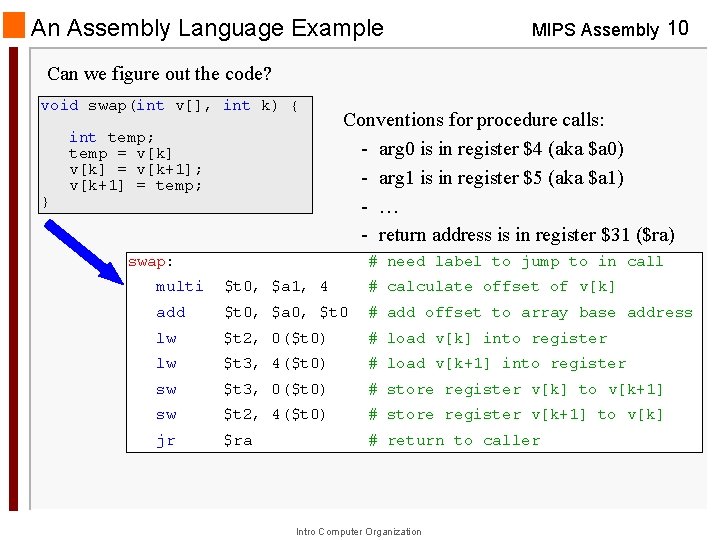

An Assembly Language Example MIPS Assembly 10 Can we figure out the code? void swap(int v[], int k) { } int temp; temp = v[k] = v[k+1]; v[k+1] = temp; Conventions for procedure calls: - arg 0 is in register $4 (aka $a 0) - arg 1 is in register $5 (aka $a 1) - … - return address is in register $31 ($ra) swap: # need label to jump to in call multi $t 0, $a 1, 4 # calculate offset of v[k] add $t 0, $a 0, $t 0 # add offset to array base address lw $t 2, 0($t 0) # load v[k] into register lw $t 3, 4($t 0) # load v[k+1] into register sw $t 3, 0($t 0) # store register v[k] to v[k+1] sw $t 2, 4($t 0) # store register v[k+1] to v[k] jr $ra # return to caller Intro Computer Organization

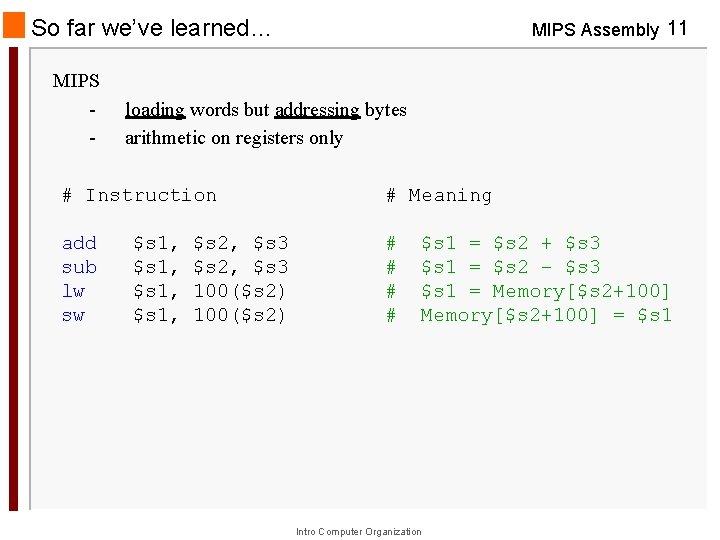

So far we’ve learned… MIPS - MIPS Assembly 11 loading words but addressing bytes arithmetic on registers only # Instruction # Meaning add sub lw sw # # $s 1, $s 2, $s 3 100($s 2) $s 1 = $s 2 + $s 3 $s 1 = $s 2 – $s 3 $s 1 = Memory[$s 2+100] = $s 1 Intro Computer Organization

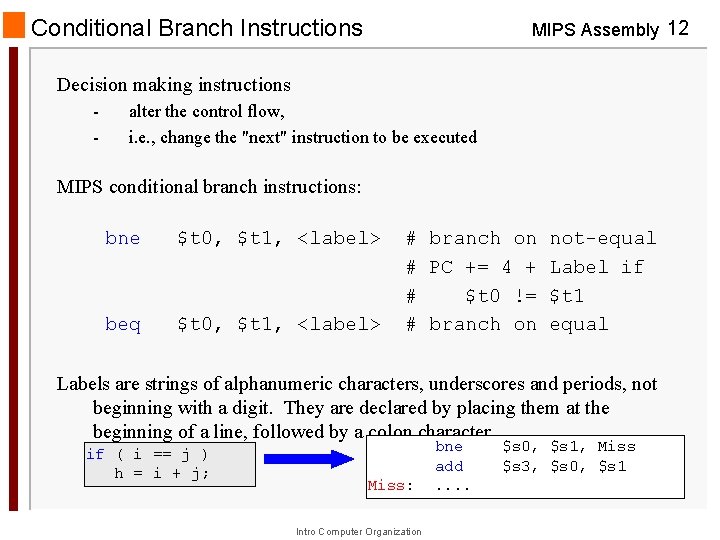

Conditional Branch Instructions MIPS Assembly 12 Decision making instructions - alter the control flow, i. e. , change the "next" instruction to be executed MIPS conditional branch instructions: bne $t 0, $t 1, <label> beq $t 0, $t 1, <label> # branch on not-equal # PC += 4 + Label if # $t 0 != $t 1 # branch on equal Labels are strings of alphanumeric characters, underscores and periods, not beginning with a digit. They are declared by placing them at the beginning of a line, followed by a colon character. if ( i == j ) h = i + j; Miss: Intro Computer Organization bne add. . $s 0, $s 1, Miss $s 3, $s 0, $s 1

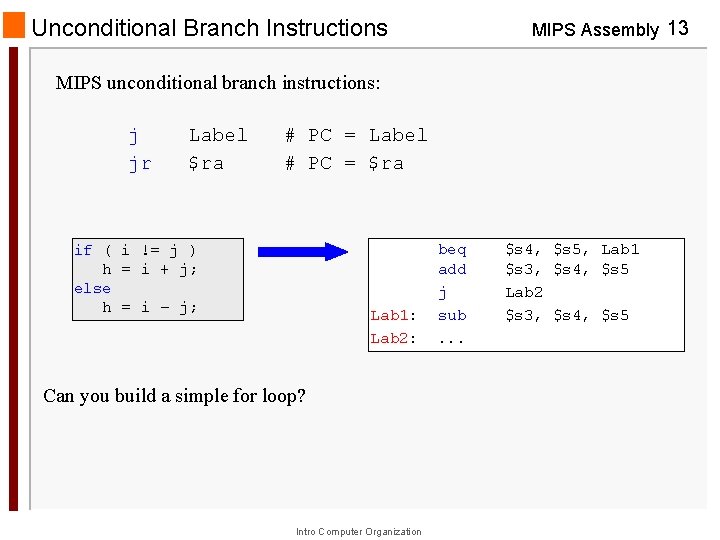

Unconditional Branch Instructions MIPS Assembly 13 MIPS unconditional branch instructions: j jr Label $ra # PC = Label # PC = $ra if ( i != j ) h = i + j; else h = i – j; Lab 1: Lab 2: Can you build a simple for loop? Intro Computer Organization beq add j sub. . . $s 4, $s 5, Lab 1 $s 3, $s 4, $s 5 Lab 2 $s 3, $s 4, $s 5

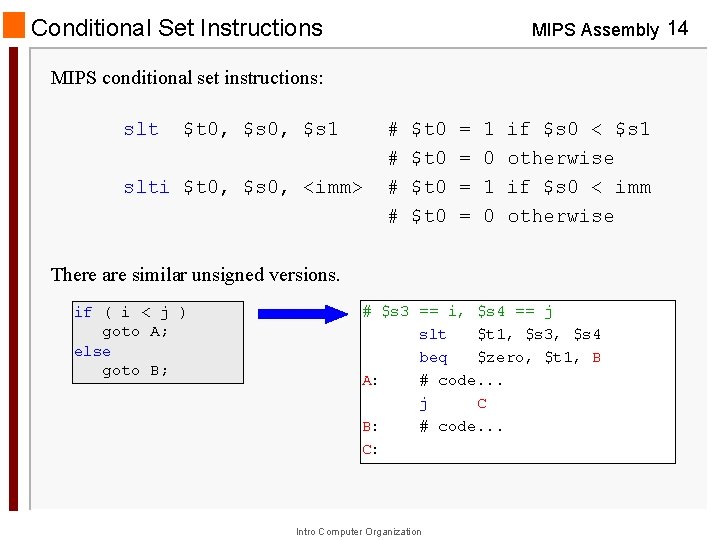

Conditional Set Instructions MIPS Assembly 14 MIPS conditional set instructions: slt $t 0, $s 1 slti $t 0, $s 0, <imm> # # $t 0 = = 1 0 if $s 0 < $s 1 otherwise if $s 0 < imm otherwise There are similar unsigned versions. if ( i < j ) goto A; else goto B; # $s 3 == i, $s 4 == j slt $t 1, $s 3, $s 4 beq $zero, $t 1, B A: # code. . . j C B: # code. . . C: Intro Computer Organization

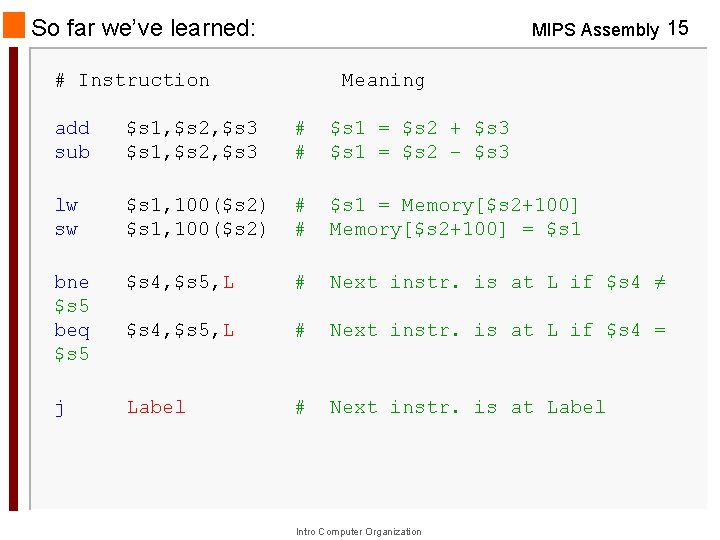

So far we’ve learned: MIPS Assembly 15 # Instruction Meaning add sub $s 1, $s 2, $s 3 # # $s 1 = $s 2 + $s 3 $s 1 = $s 2 – $s 3 lw sw $s 1, 100($s 2) # # $s 1 = Memory[$s 2+100] = $s 1 bne $s 5 beq $s 5 $s 4, $s 5, L # Next instr. is at L if $s 4 ≠ $s 4, $s 5, L # Next instr. is at L if $s 4 = j Label # Next instr. is at Label Intro Computer Organization

- Slides: 15