MIPS Architecture CPSC 321 Computer Architecture Andreas Klappenecker

- Slides: 16

MIPS Architecture CPSC 321 Computer Architecture Andreas Klappenecker

MIPS Design Paradigms n Simplicity favors regularity n n Smaller is faster n n 32 registers Make good compromises n n all instructions single size three register operands in arithmetic instr. keep register fields in the same place large addresses and constants versus unique instruction length Make the common case fast n PC-relative addressing for conditional branches

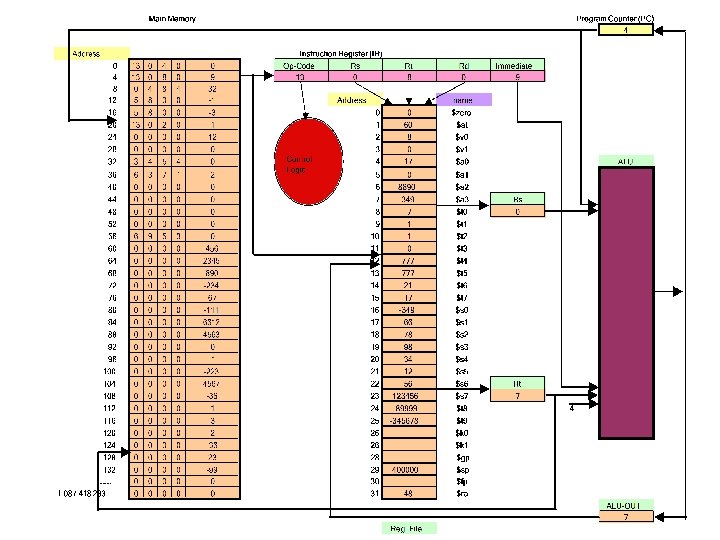

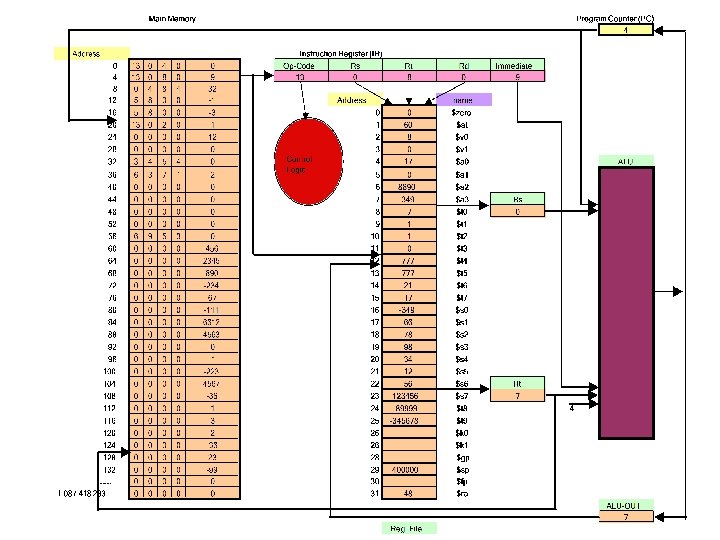

Basic Functional Components n n n Control unit Register file Arithmetic logic unit (ALU) Program counter (PC) Memory Instruction register (IR)

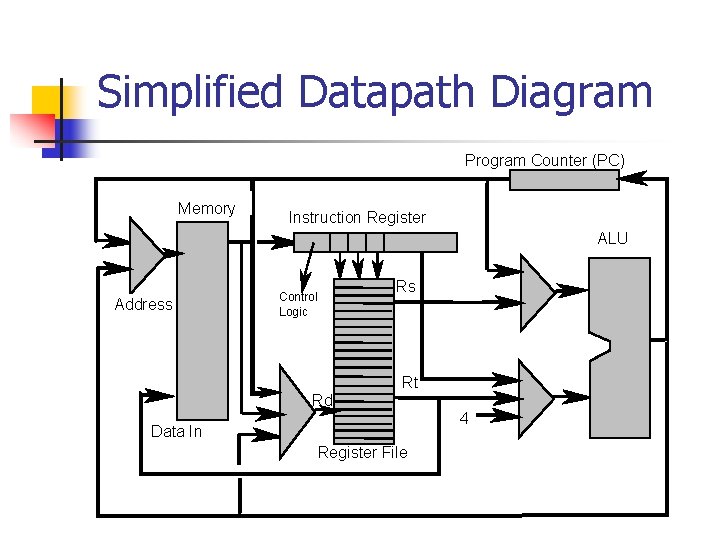

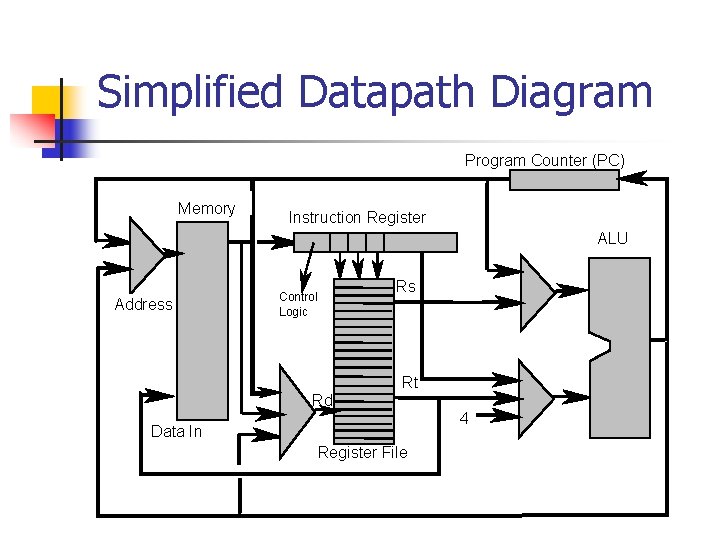

Simplified Datapath Diagram Program Counter (PC) Memory Instruction Register ALU Address Rs Control Logic Rt Rd 4 Data In Register File

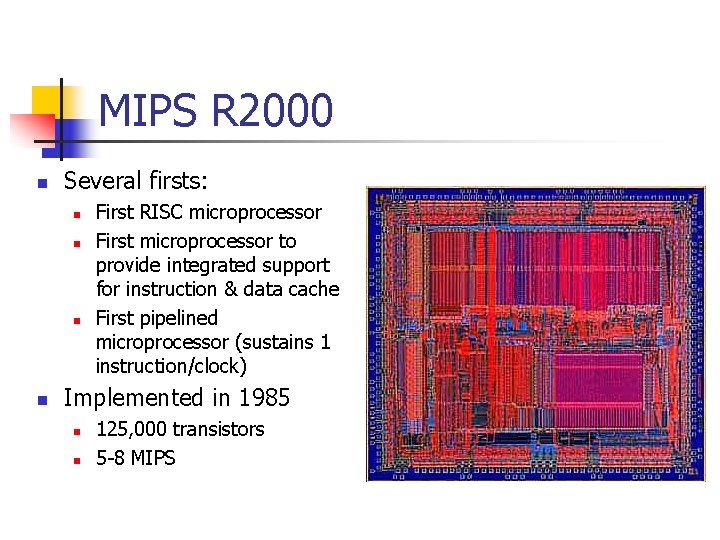

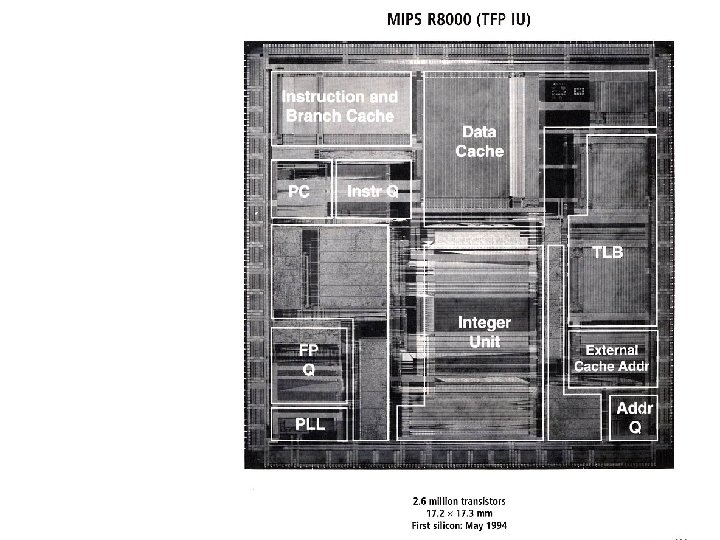

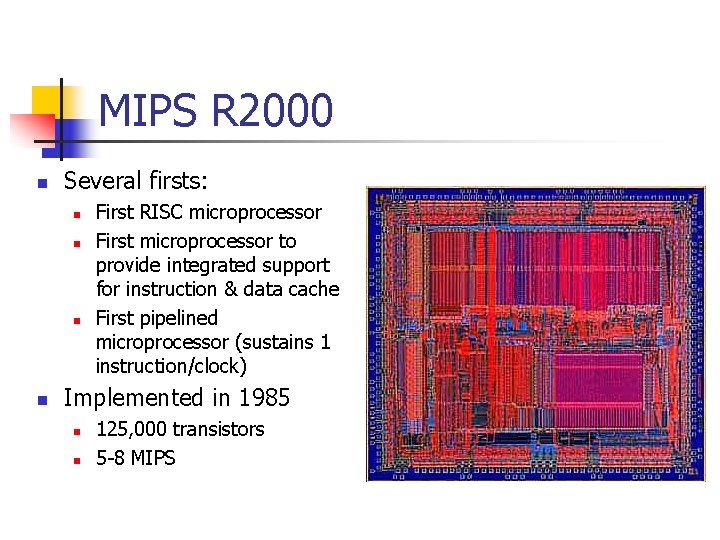

MIPS R 2000 n Several firsts: n n First RISC microprocessor First microprocessor to provide integrated support for instruction & data cache First pipelined microprocessor (sustains 1 instruction/clock) Implemented in 1985 n n 125, 000 transistors 5 -8 MIPS

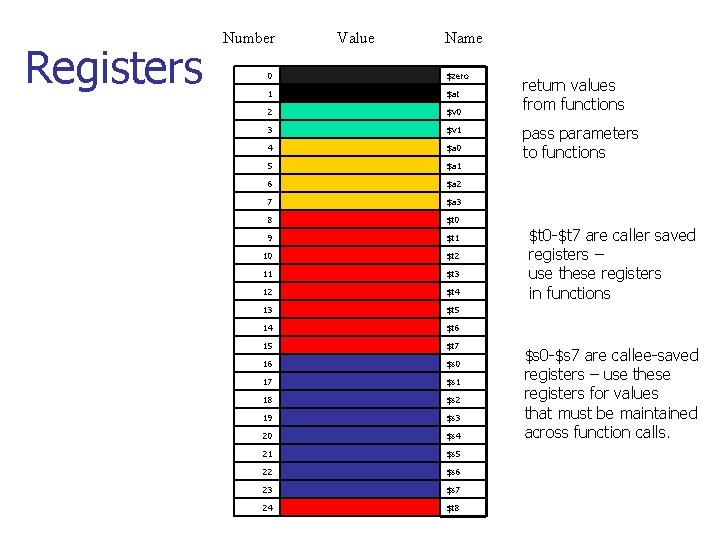

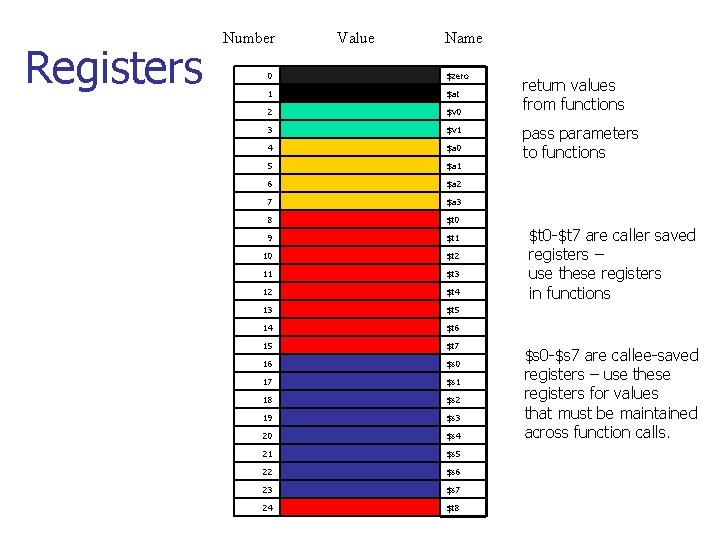

Registers Number Value Name 0 $zero 1 $at 2 $v 0 3 $v 1 4 $a 0 5 $a 1 6 $a 2 7 $a 3 8 $t 0 9 $t 1 10 $t 2 11 $t 3 12 $t 4 13 $t 5 14 $t 6 15 $t 7 16 $s 0 17 $s 1 18 $s 2 19 $s 3 20 $s 4 21 $s 5 22 $s 6 23 $s 7 24 $t 8 return values from functions pass parameters to functions $t 0 -$t 7 are caller saved registers – use these registers in functions $s 0 -$s 7 are callee-saved registers – use these registers for values that must be maintained across function calls.

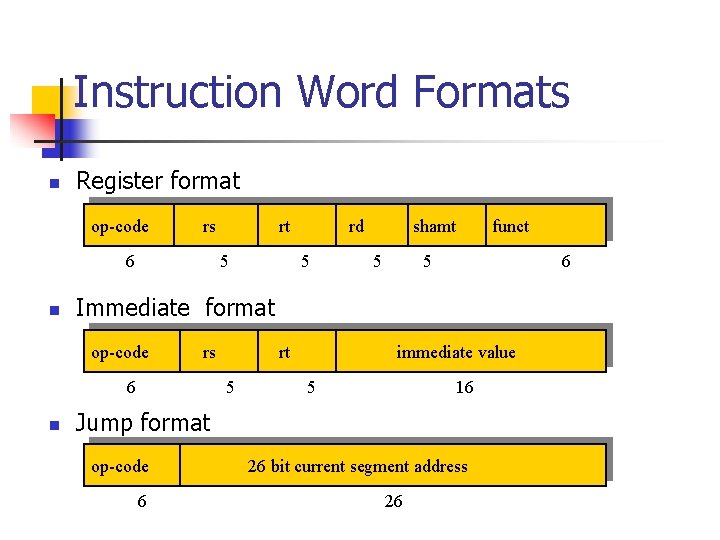

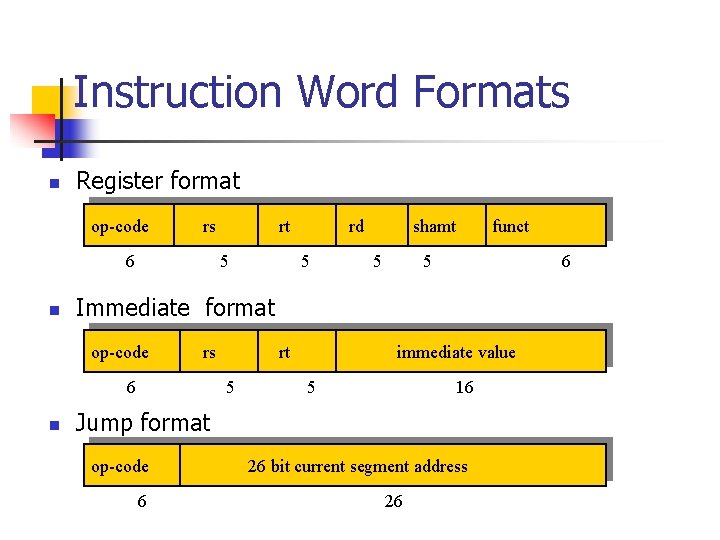

Instruction Word Formats n Register format op-code rs 6 n 5 rd 5 shamt 5 funct 5 6 Immediate format op-code rs 6 n rt rt 5 immediate value 5 16 Jump format op-code 6 26 bit current segment address 26

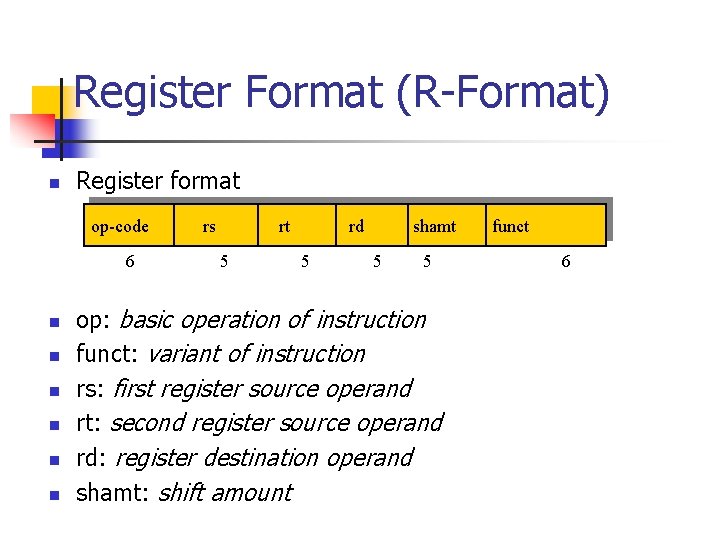

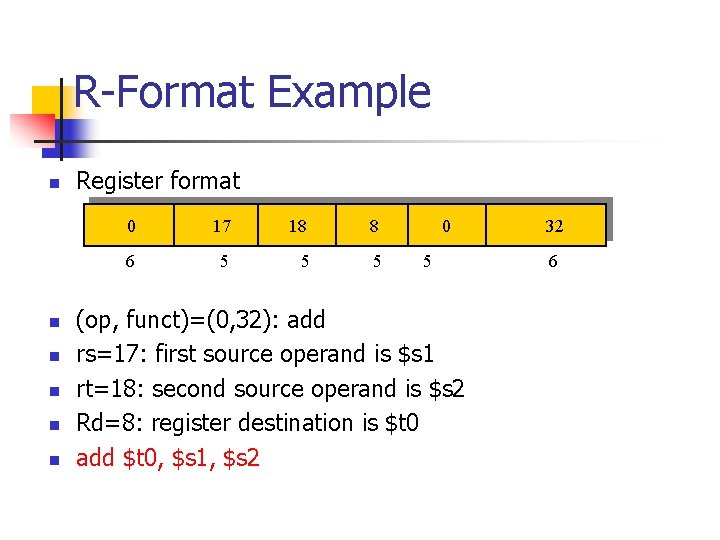

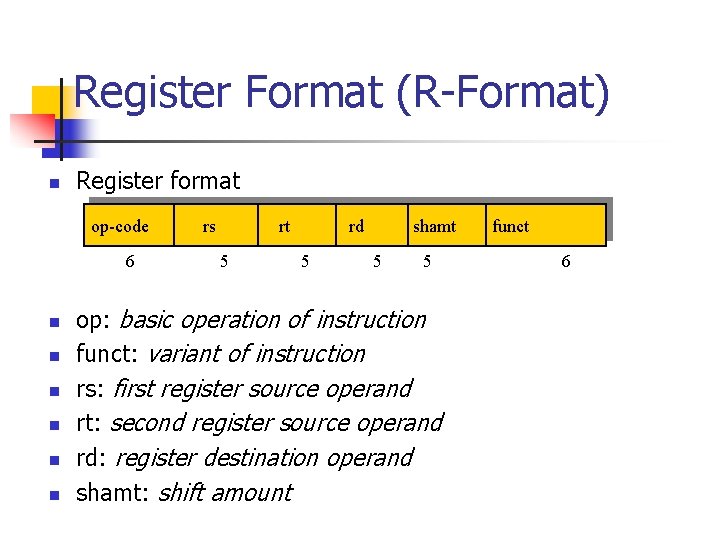

Register Format (R-Format) n Register format op-code 6 n n n rs rt 5 rd 5 shamt 5 5 op: basic operation of instruction funct: variant of instruction rs: first register source operand rt: second register source operand rd: register destination operand shamt: shift amount funct 6

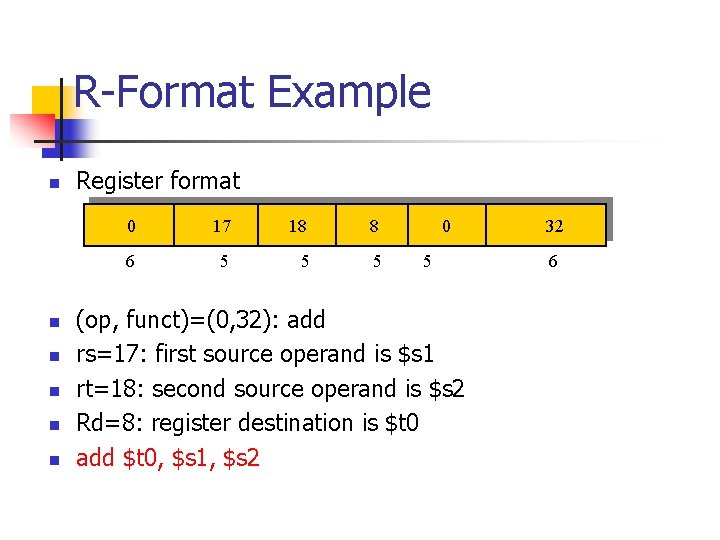

R-Format Example n n n Register format 0 17 18 8 6 5 5 5 0 5 (op, funct)=(0, 32): add rs=17: first source operand is $s 1 rt=18: second source operand is $s 2 Rd=8: register destination is $t 0 add $t 0, $s 1, $s 2 32 6

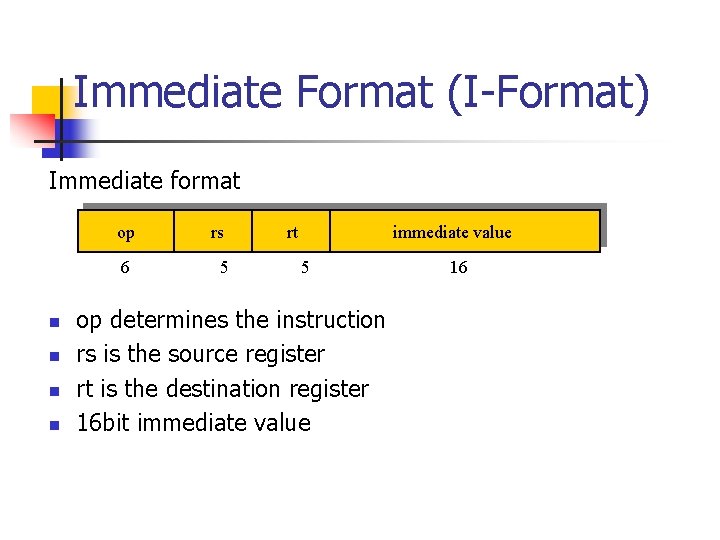

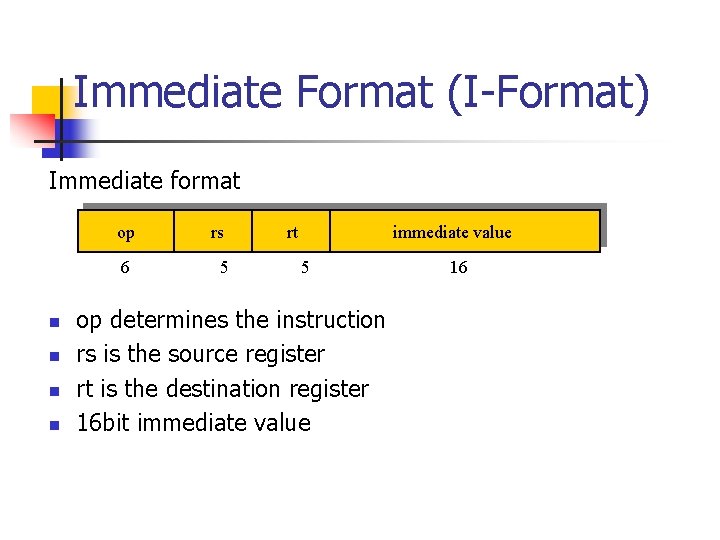

Immediate Format (I-Format) Immediate format n n op rs 6 5 rt immediate value 5 op determines the instruction rs is the source register rt is the destination register 16 bit immediate value 16

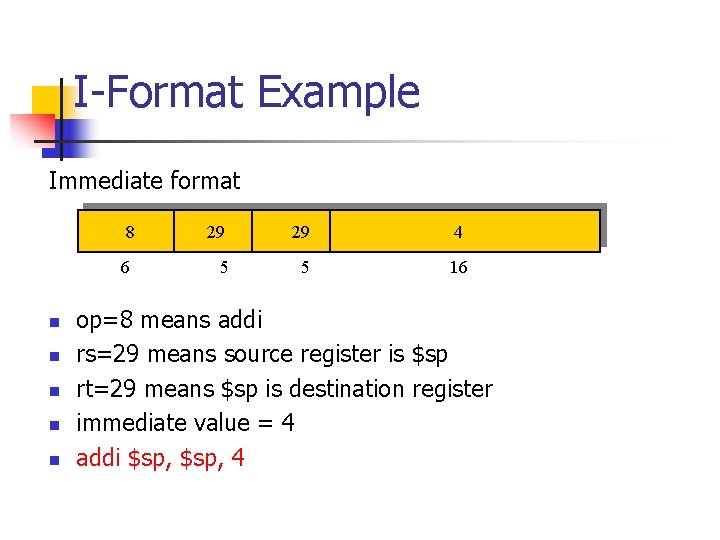

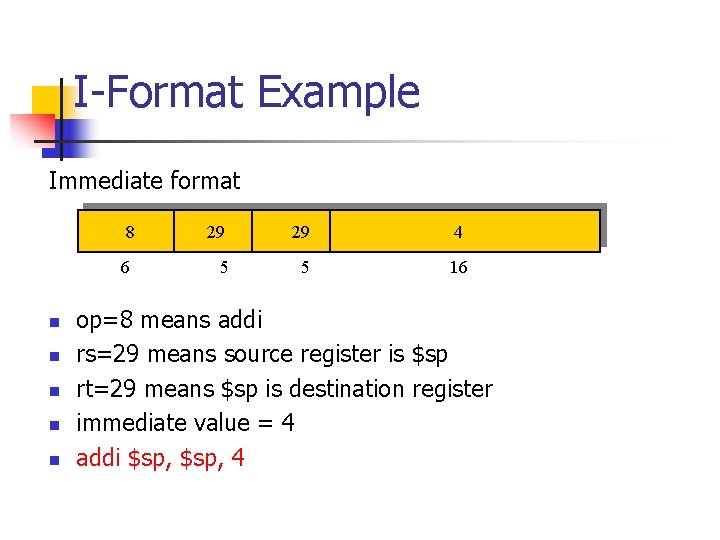

I-Format Example Immediate format n n n 8 29 29 4 6 5 5 16 op=8 means addi rs=29 means source register is $sp rt=29 means $sp is destination register immediate value = 4 addi $sp, 4

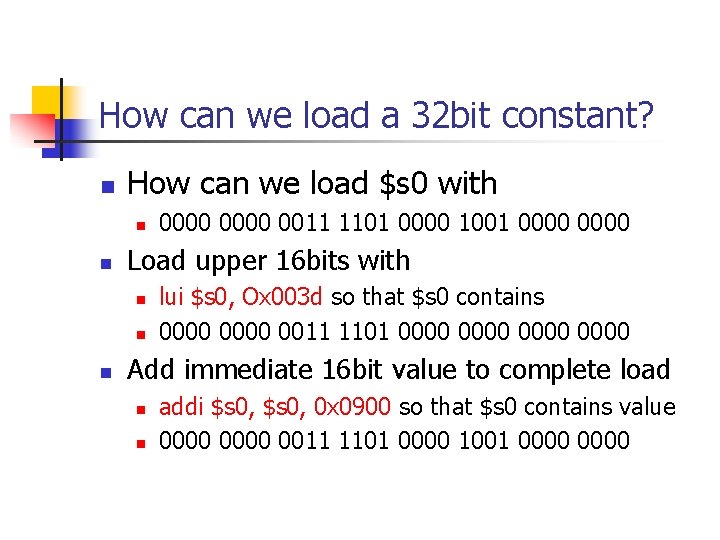

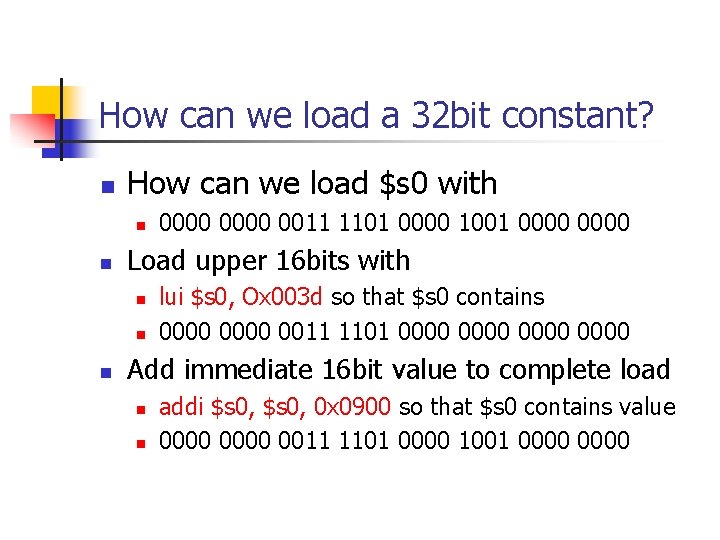

How can we load a 32 bit constant? n How can we load $s 0 with n n Load upper 16 bits with n n n 0000 0011 1101 0000 1001 0000 lui $s 0, Ox 003 d so that $s 0 contains 0000 0011 1101 0000 Add immediate 16 bit value to complete load n n addi $s 0, 0 x 0900 so that $s 0 contains value 0000 0011 1101 0000 1001 0000

MIPS Addressing Modes n n Register addressing Base displacement addressing Immediate addressing PC-relative addressing n n address is the sum of the PC and a constant in the instruction Pseudo-direct addressing n jump address is 26 bits of instruction concatenated with upper bits of PC

What next? n Details of the arithmetic logic unit n n n Details of datapath and control n n Chapter 4 Project: Build your own ALU Chapter 5 Project: Build your own CPU Pipelining Caching