Minnen w Innehll n l l l n

- Slides: 26

Minnen w Innehåll n l l l n n Minneselement Låskrets (eng. latch) Vippa (eng. Flip-flop) Register Random-Access Memory (RAM) Read-Only Memory (ROM) Copyright Bengt Oelmann 2002 1

Minneselement w Tillåter lagring av binära variabler för framtida beräkningar n Latch l l l n Vippa (eng. Flip-flop) l l l n Dess värde ändras vid klocksignalens aktiva nivå (t. ex C=1) Grundläggande bistabilt minneselement Lagrar 1 bit Dess värde ändras endast vid klocksignalens flank Lagrar 1 bit Används t. ex i tillståndsmaskiner och register Register l l En grupp vippor som klockas med samma klocka Lagrar en binär variabel som består av flera bitar Copyright Bengt Oelmann 2002 2

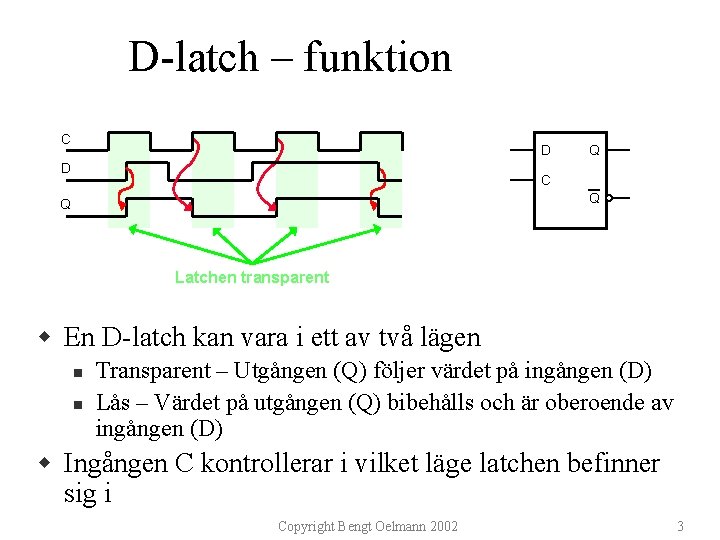

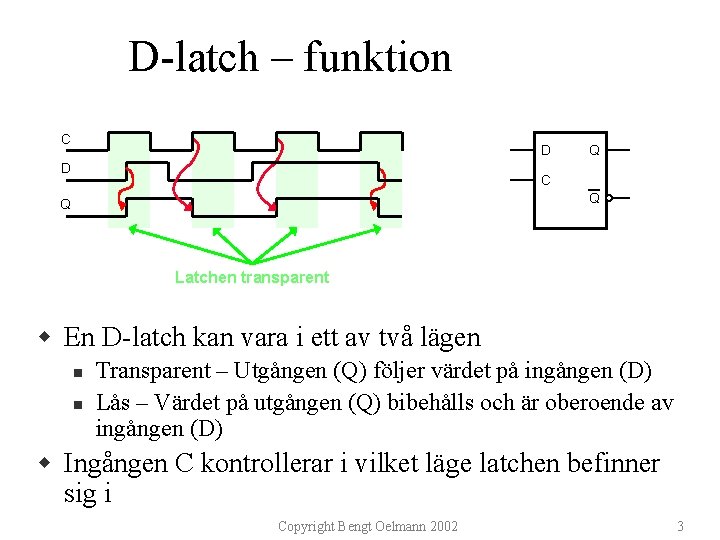

D-latch – funktion C D D Q C Q Q Latchen transparent w En D-latch kan vara i ett av två lägen n n Transparent – Utgången (Q) följer värdet på ingången (D) Lås – Värdet på utgången (Q) bibehålls och är oberoende av ingången (D) w Ingången C kontrollerar i vilket läge latchen befinner sig i Copyright Bengt Oelmann 2002 3

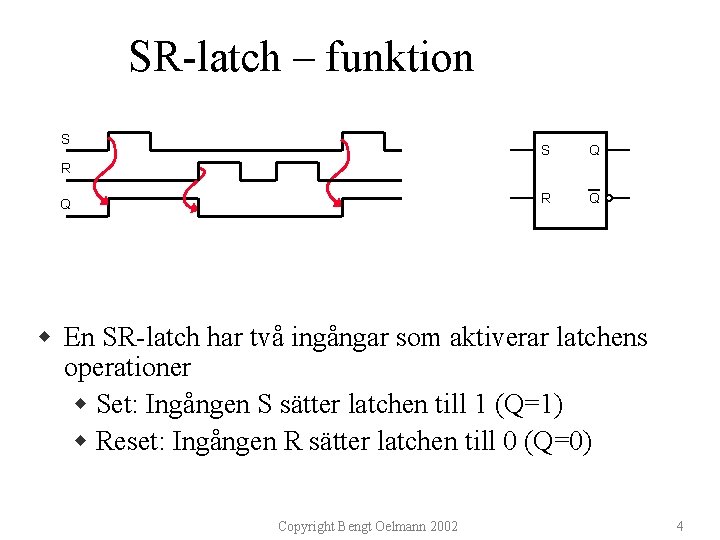

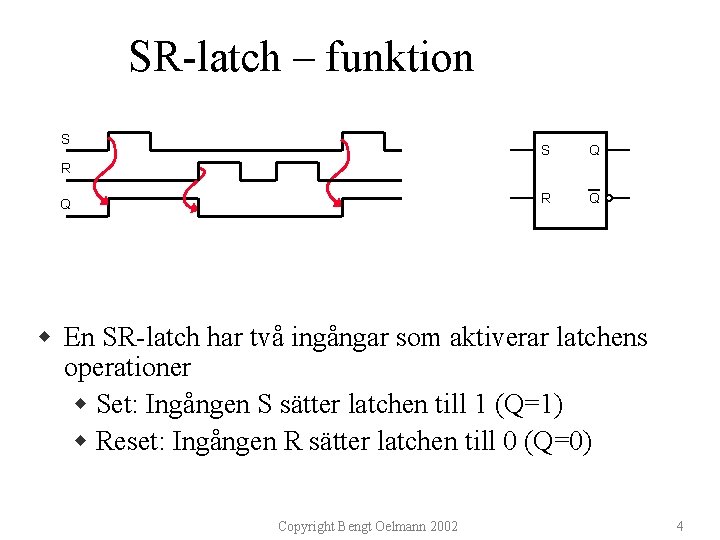

SR-latch – funktion S S Q R Q w En SR-latch har två ingångar som aktiverar latchens operationer w Set: Ingången S sätter latchen till 1 (Q=1) w Reset: Ingången R sätter latchen till 0 (Q=0) Copyright Bengt Oelmann 2002 4

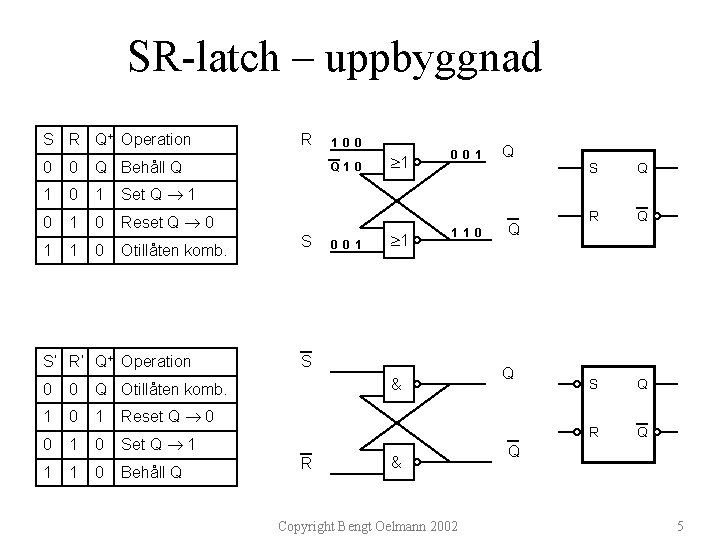

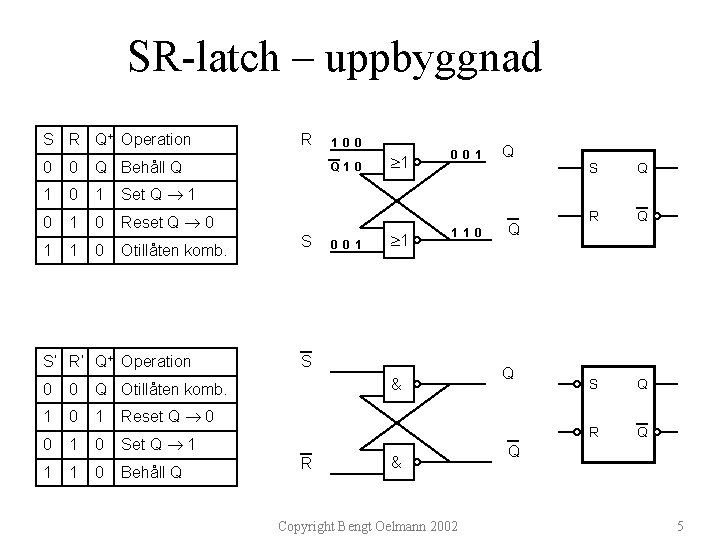

SR-latch – uppbyggnad S R Q+ Operation 0 0 Q Behåll Q 1 0 1 Set Q 1 0 Reset Q 0 1 1 0 Otillåten komb. S’ R’ Q+ Operation 0 0 Q Otillåten komb. 1 0 1 Reset Q 0 0 1 0 Set Q 1 1 1 0 Behåll Q R 1 0 0 Q 1 0 S 0 0 1 1 1 0 0 1 1 1 0 S & R & Copyright Bengt Oelmann 2002 Q Q Q S Q R Q Q 5

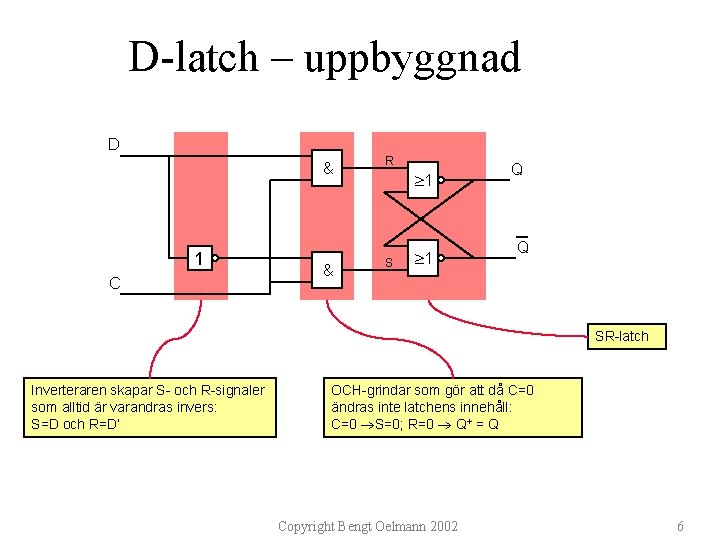

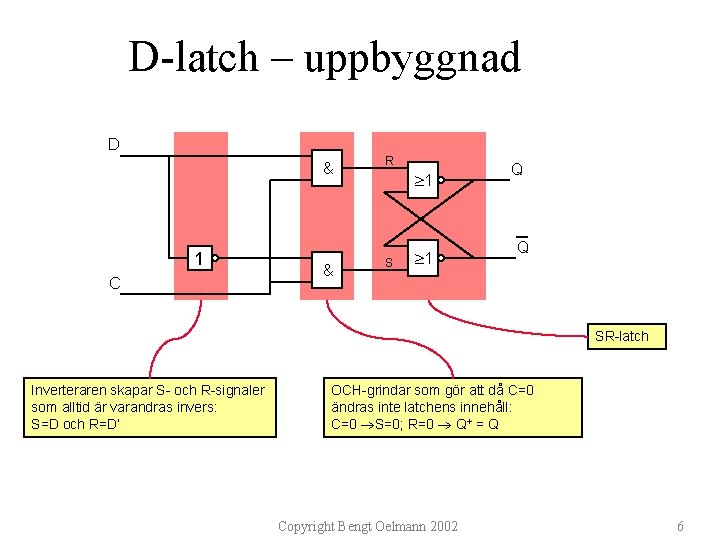

D-latch – uppbyggnad D 1 C & R & S 1 1 Q Q SR-latch Inverteraren skapar S- och R-signaler som alltid är varandras invers: S=D och R=D’ OCH-grindar som gör att då C=0 ändras inte latchens innehåll: C=0 S=0; R=0 Q+ = Q Copyright Bengt Oelmann 2002 6

D-vippa – funktion C D D Q C Q Q Positiv flank D-vippan ”samplar” värdet på D-ingången vid klocksignalens flank C D D Q C Q Q Negativ flank Copyright Bengt Oelmann 2002 7

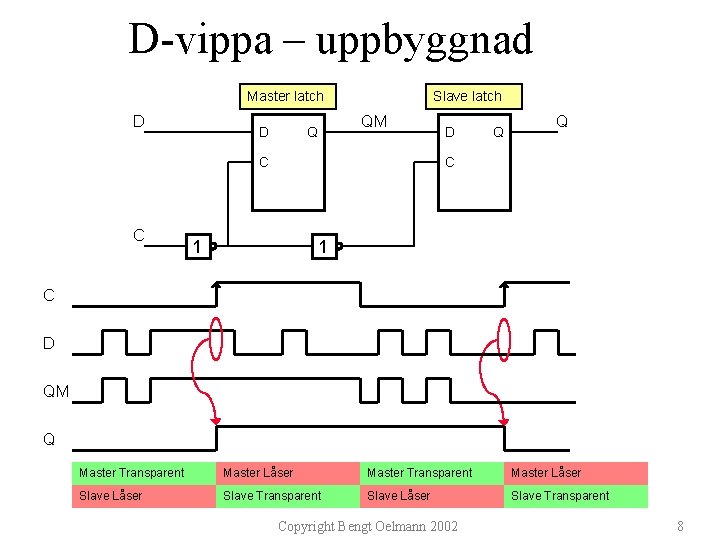

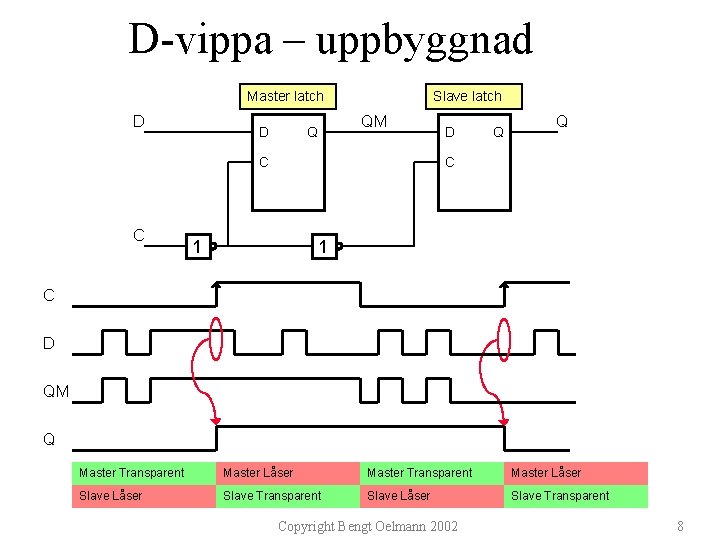

D-vippa – uppbyggnad Master latch D D Slave latch QM Q C C D Q Q C 1 1 C D QM Q Master Transparent Master Låser Slave Transparent Copyright Bengt Oelmann 2002 8

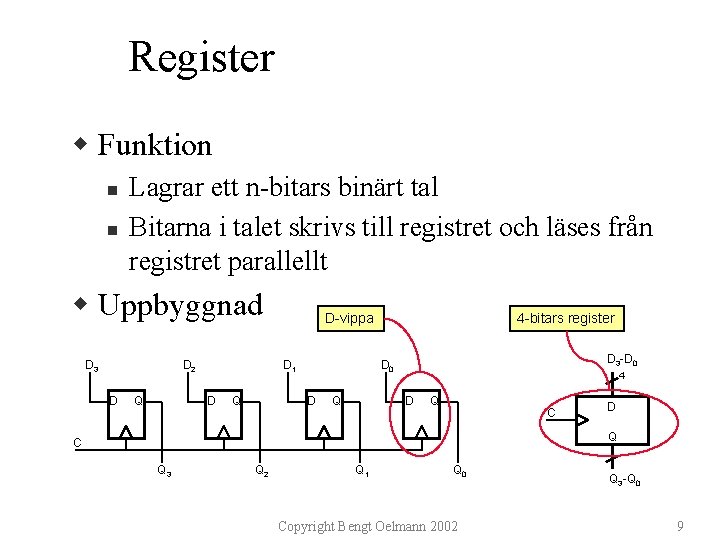

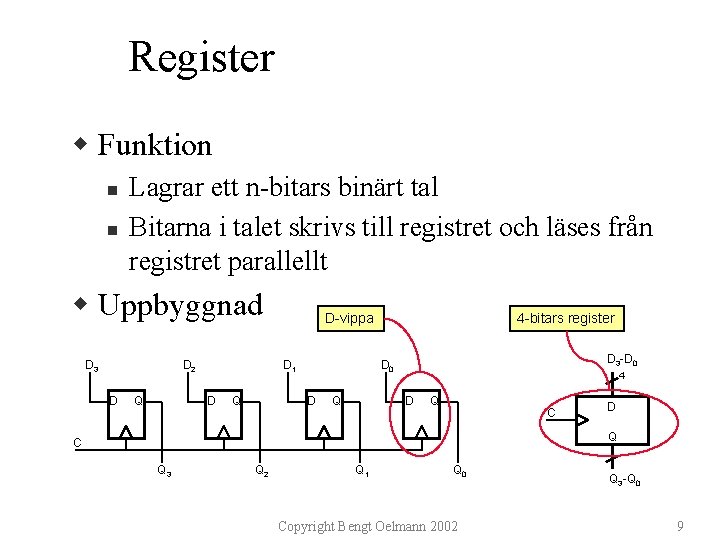

Register w Funktion n n Lagrar ett n-bitars binärt tal Bitarna i talet skrivs till registret och läses från registret parallellt w Uppbyggnad D 3 D 2 D Q D-vippa D 1 D Q 4 -bitars register D 3 -D 0 D Q 4 D Q C Q 3 Q 2 Q 1 Q 0 Copyright Bengt Oelmann 2002 Q 3 -Q 0 9

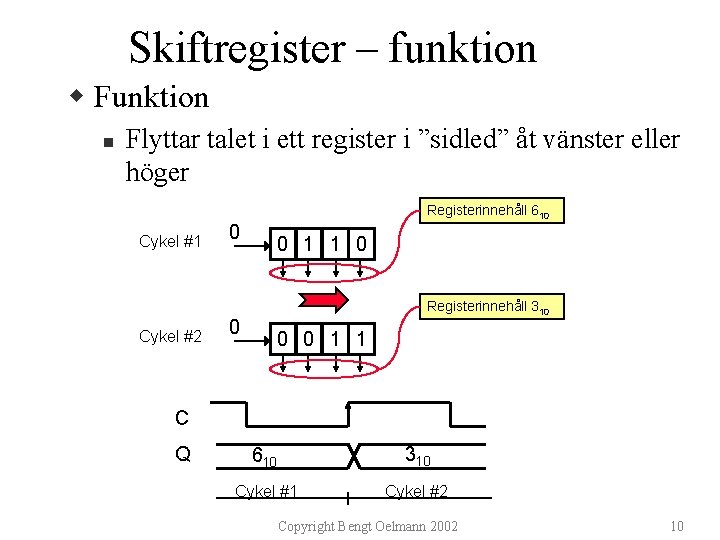

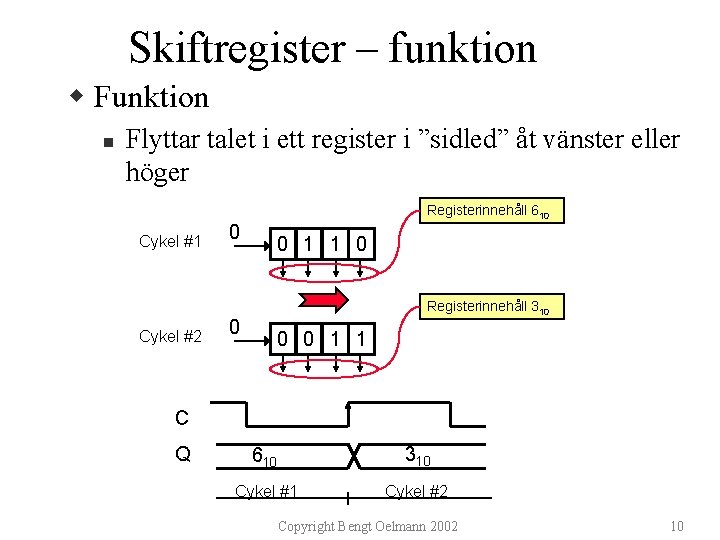

Skiftregister – funktion w Funktion n Flyttar talet i ett register i ”sidled” åt vänster eller höger Registerinnehåll 610 Cykel #1 Cykel #2 0 0 0 1 1 0 Registerinnehåll 310 0 0 1 1 C Q 610 310 Cykel #1 Cykel #2 Copyright Bengt Oelmann 2002 10

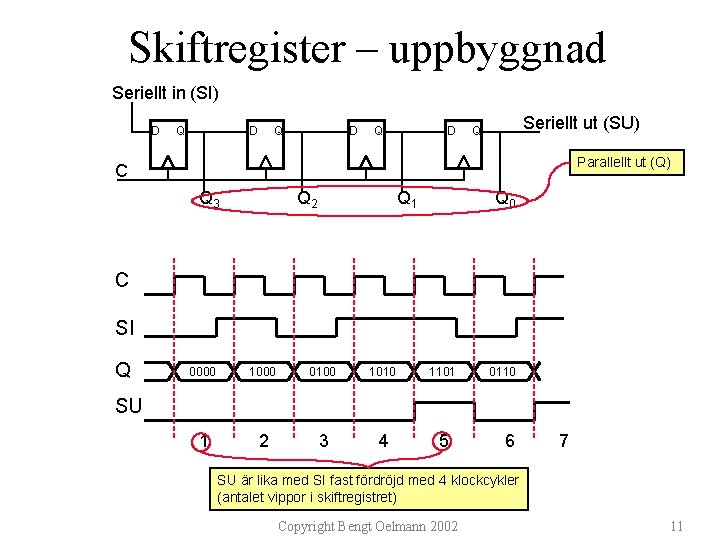

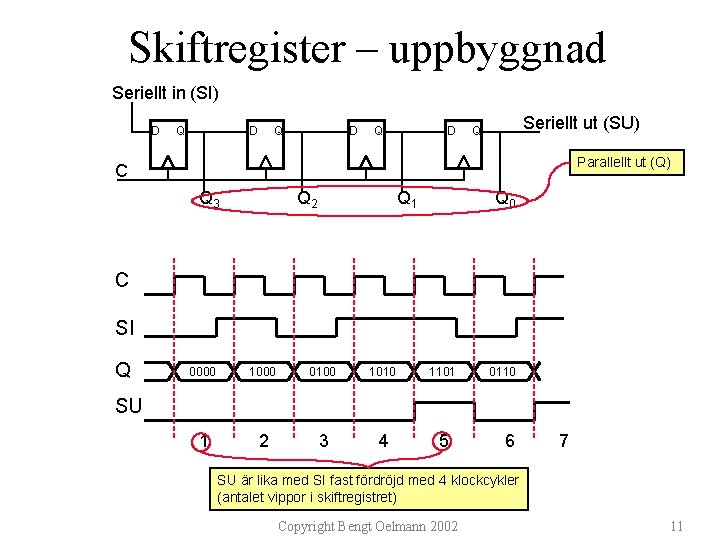

Skiftregister – uppbyggnad Seriellt in (SI) D Q D Q D Seriellt ut (SU) Q Parallellt ut (Q) C Q 3 Q 2 Q 1 Q 0 C SI Q 0000 1000 0100 1010 1101 1 2 3 4 5 0110 SU 6 7 SU är lika med SI fast fördröjd med 4 klockcykler (antalet vippor i skiftregistret) Copyright Bengt Oelmann 2002 11

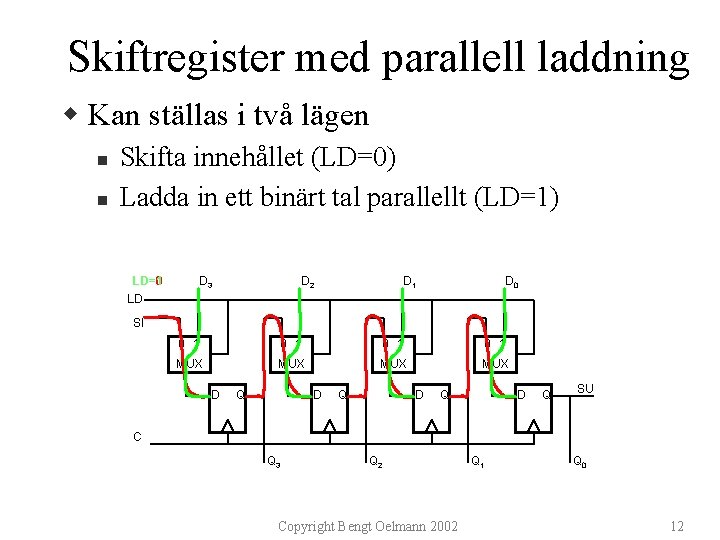

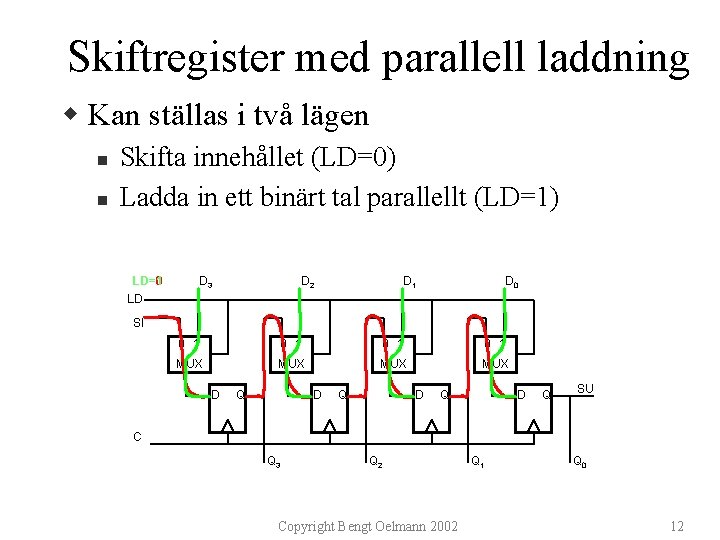

Skiftregister med parallell laddning w Kan ställas i två lägen n n Skifta innehållet (LD=0) Ladda in ett binärt tal parallellt (LD=1) LD=0 LD=1 LD D 3 D 2 D 1 D 0 SI 0 1 0 1 MUX MUX D Q D Q SU C Q 3 Q 2 Copyright Bengt Oelmann 2002 Q 1 Q 0 12

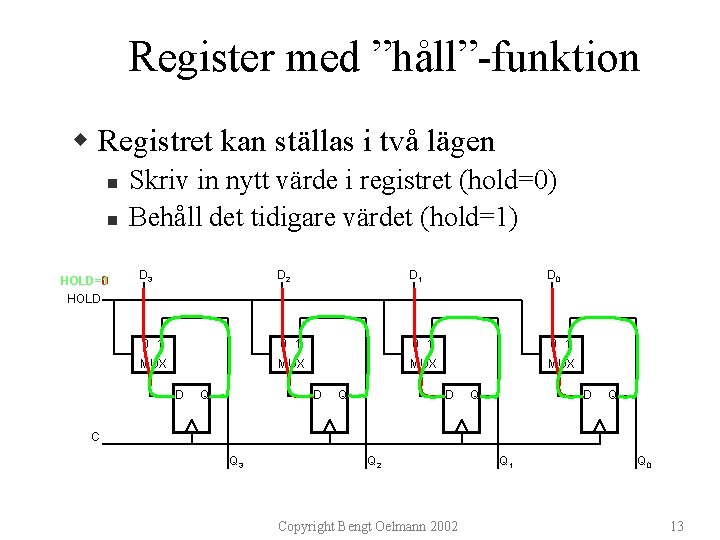

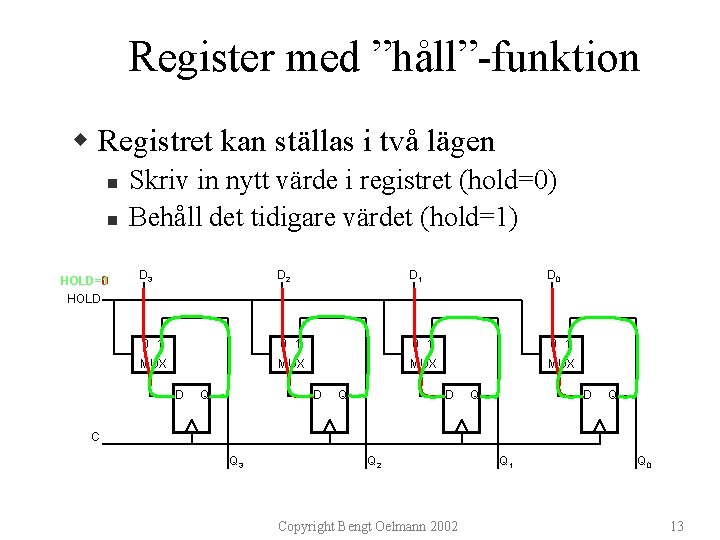

Register med ”håll”-funktion w Registret kan ställas i två lägen n n HOLD=0 HOLD=1 HOLD Skriv in nytt värde i registret (hold=0) Behåll det tidigare värdet (hold=1) D 3 D 2 D 1 D 0 0 1 0 1 MUX MUX D Q D Q C Q 3 Q 2 Copyright Bengt Oelmann 2002 Q 1 Q 0 13

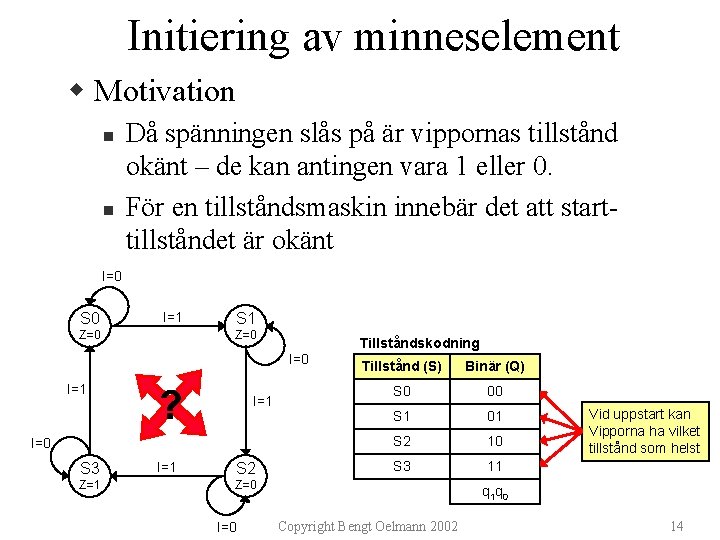

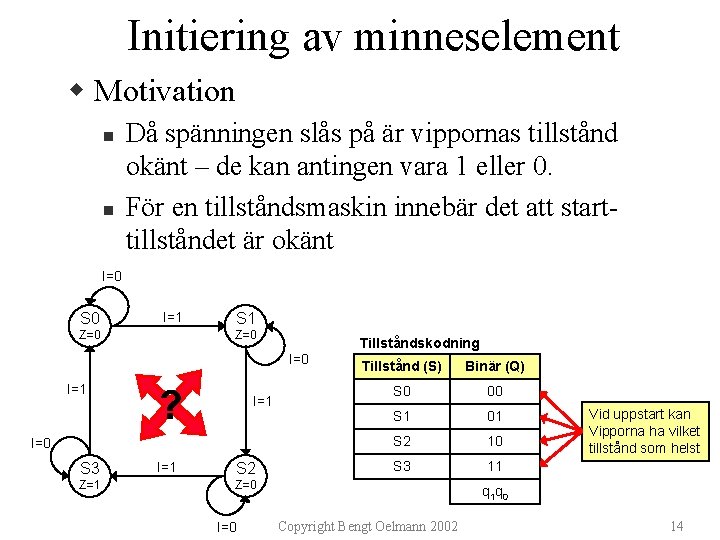

Initiering av minneselement w Motivation n n Då spänningen slås på är vippornas tillstånd okänt – de kan antingen vara 1 eller 0. För en tillståndsmaskin innebär det att starttillståndet är okänt I=0 S 0 I=1 Z=0 S 1 Z=0 Tillståndskodning I=0 I=1 ? I=1 I=0 S 3 Z=1 I=1 S 2 Tillstånd (S) Binär (Q) S 0 00 S 1 01 S 2 10 S 3 11 Z=0 I=0 Vid uppstart kan Vipporna ha vilket tillstånd som helst q 1 q 0 Copyright Bengt Oelmann 2002 14

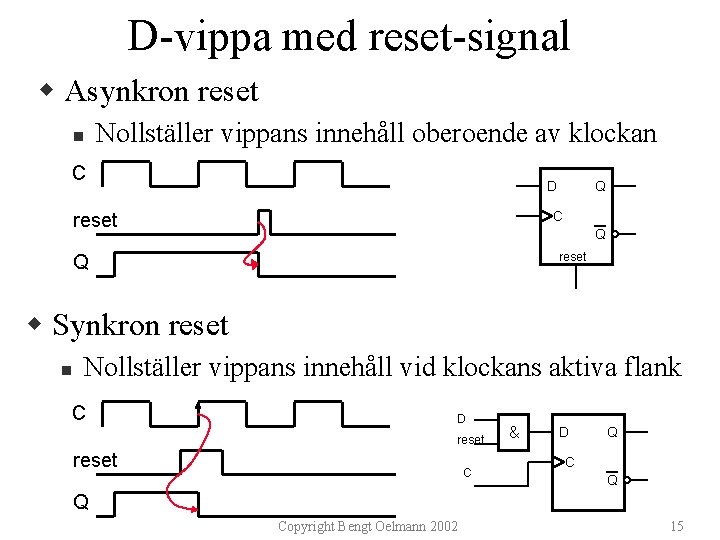

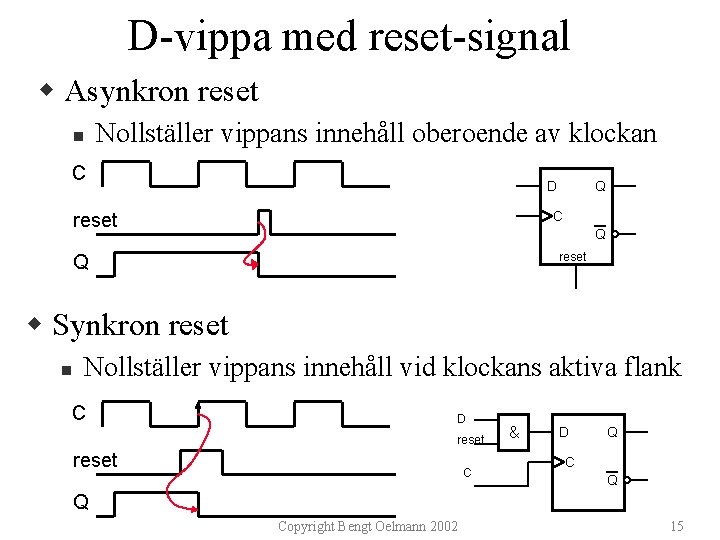

D-vippa med reset-signal w Asynkron reset n Nollställer vippans innehåll oberoende av klockan C D Q C reset Q w Synkron reset n Nollställer vippans innehåll vid klockans aktiva flank C D reset C & D Q C Q Q Copyright Bengt Oelmann 2002 15

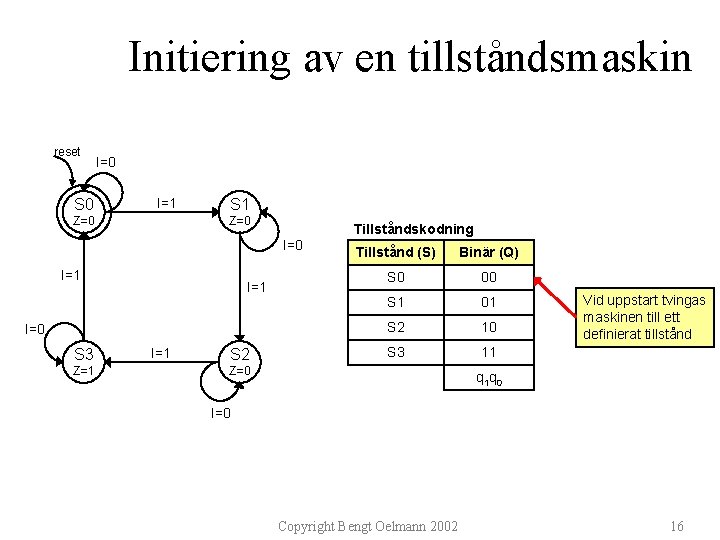

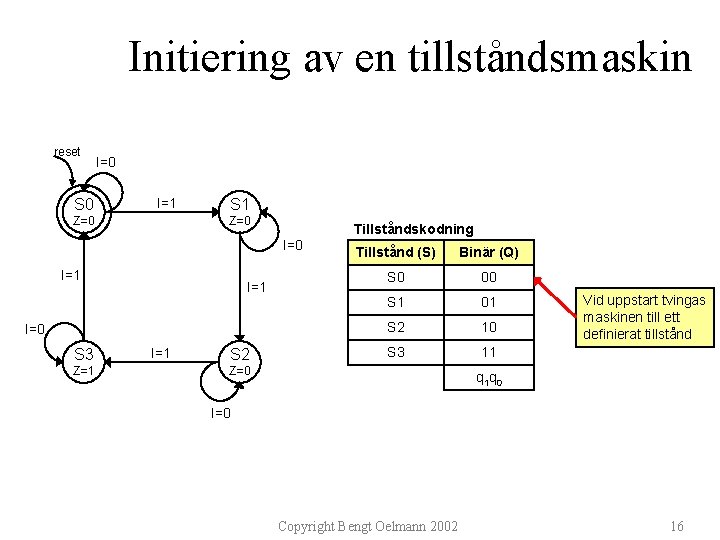

Initiering av en tillståndsmaskin reset S 0 I=1 Z=0 S 1 Z=0 Tillståndskodning I=0 I=1 I=0 S 3 Z=1 I=1 S 2 Tillstånd (S) Binär (Q) S 0 00 S 1 01 S 2 10 S 3 11 Z=0 Vid uppstart tvingas maskinen till ett definierat tillstånd q 1 q 0 I=0 Copyright Bengt Oelmann 2002 16

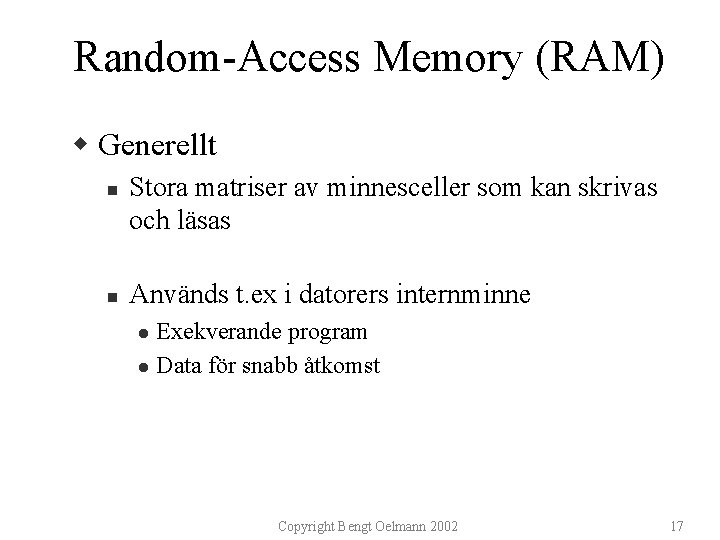

Random-Access Memory (RAM) w Generellt n n Stora matriser av minnesceller som kan skrivas och läsas Används t. ex i datorers internminne Exekverande program l Data för snabb åtkomst l Copyright Bengt Oelmann 2002 17

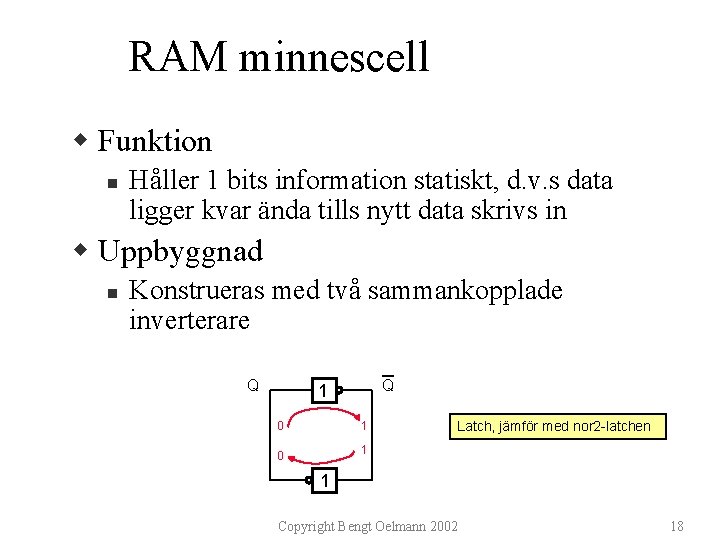

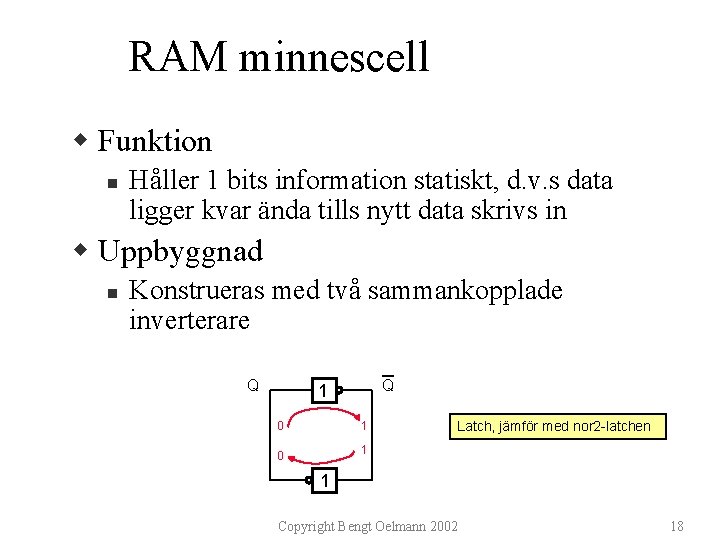

RAM minnescell w Funktion n Håller 1 bits information statiskt, d. v. s data ligger kvar ända tills nytt data skrivs in w Uppbyggnad n Konstrueras med två sammankopplade inverterare Q Q 1 0 1 Latch, jämför med nor 2 -latchen 1 0 1 Copyright Bengt Oelmann 2002 18

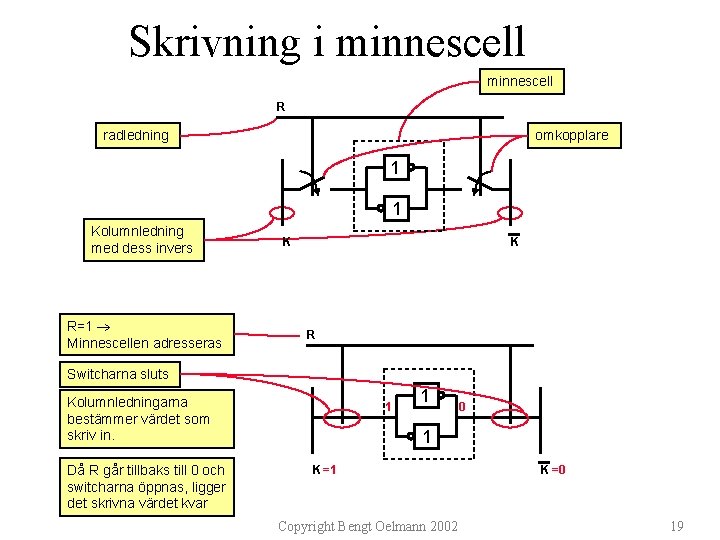

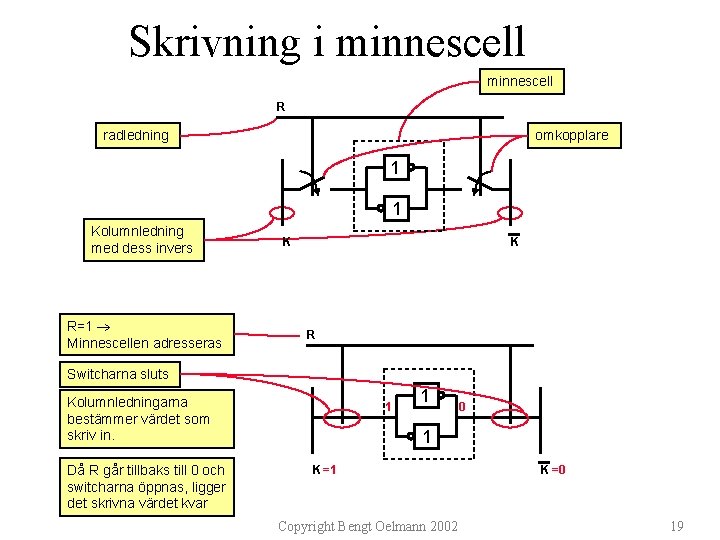

Skrivning i minnescell R radledning omkopplare 1 1 Kolumnledning med dess invers R=1 Minnescellen adresseras K K R Switcharna sluts Kolumnledningarna bestämmer värdet som skriv in. Då R går tillbaks till 0 och switcharna öppnas, ligger det skrivna värdet kvar 1 1 0 1 K =1 Copyright Bengt Oelmann 2002 K =0 19

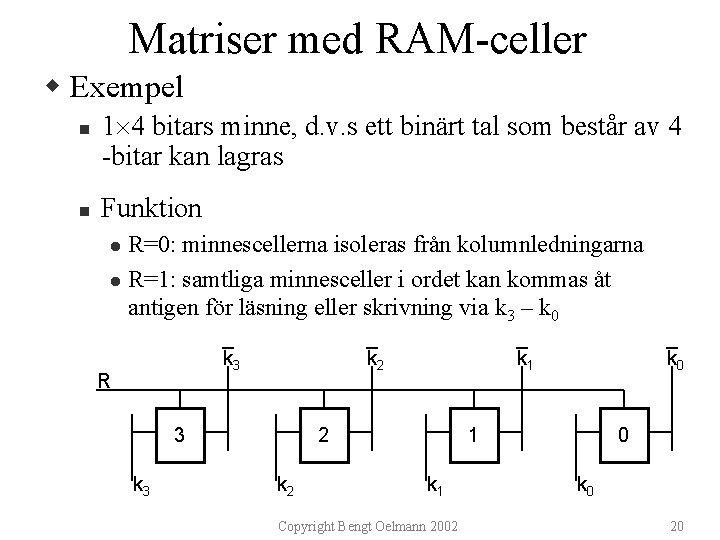

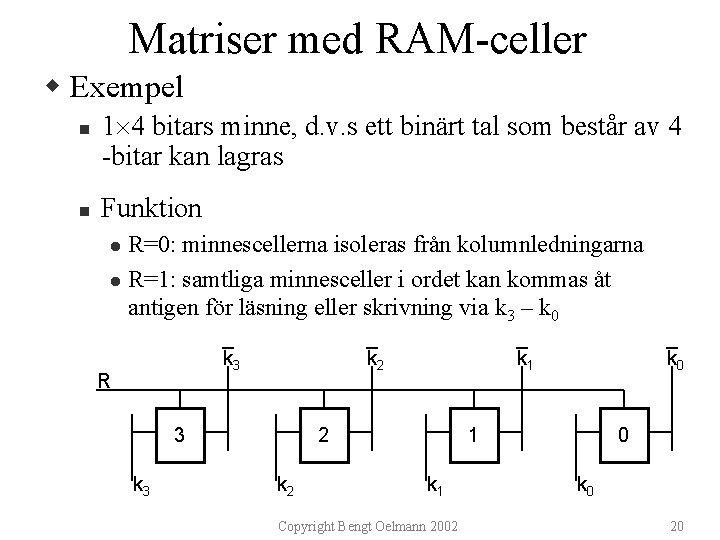

Matriser med RAM-celler w Exempel n n 1 4 bitars minne, d. v. s ett binärt tal som består av 4 -bitar kan lagras Funktion R=0: minnescellerna isoleras från kolumnledningarna l R=1: samtliga minnesceller i ordet kan kommas åt antigen för läsning eller skrivning via k 3 – k 0 l k 3 R k 2 3 k 1 2 k 0 1 k 1 Copyright Bengt Oelmann 2002 0 k 0 20

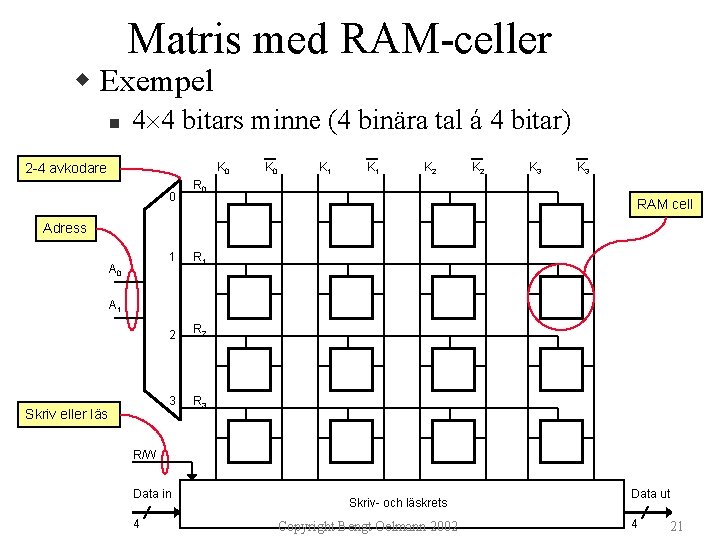

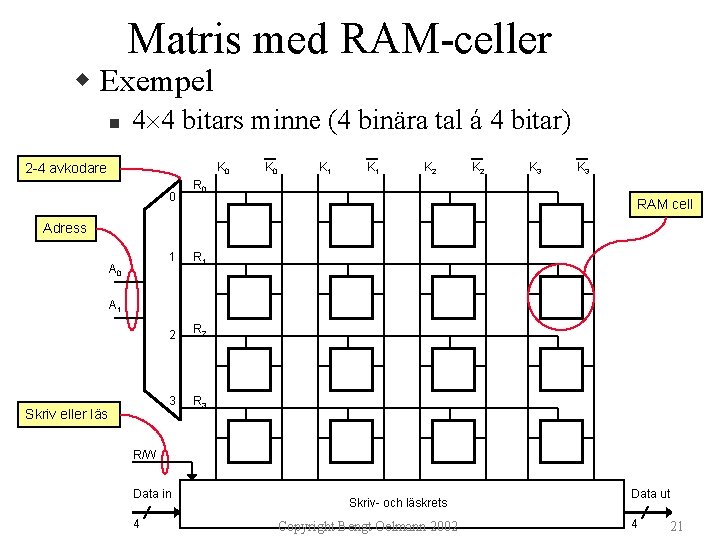

Matris med RAM-celler w Exempel n 4 4 bitars minne (4 binära tal á 4 bitar) K 0 2 -4 avkodare 0 K 1 K 2 K 3 K 3 R 0 RAM cell Adress A 0 1 R 1 2 R 2 3 R 3 A 1 Skriv eller läs R/W Data in 4 Skriv- och läskrets Copyright Bengt Oelmann 2002 Data ut 4 21

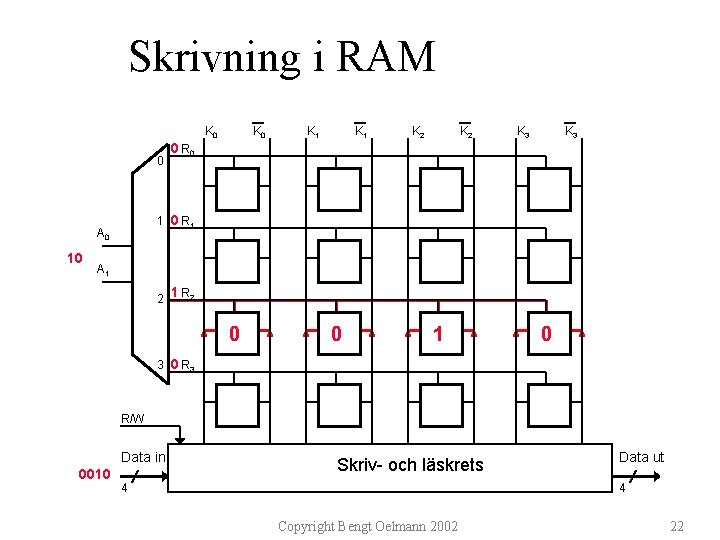

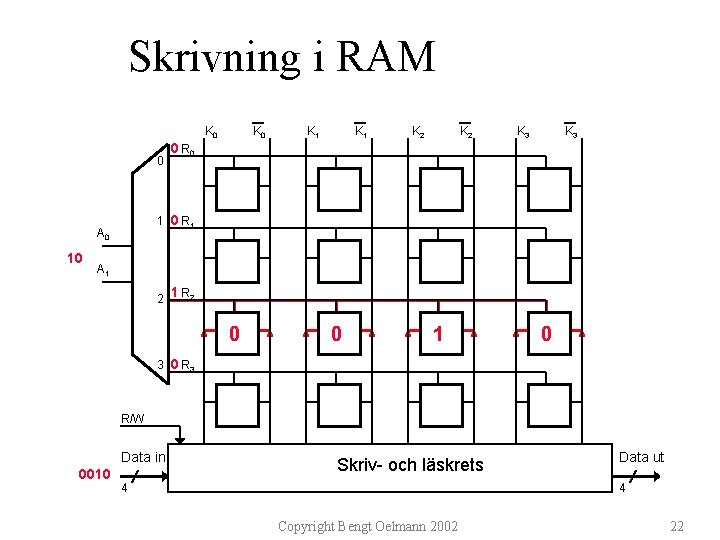

Skrivning i RAM K 0 0 K 1 K 2 K 3 0 R 0 1 0 R 1 A 0 10 K 0 A 1 2 1 R 2 0 0 1 0 3 0 R 3 R/W Data in 0010 Skriv- och läskrets 4 Data ut 4 Copyright Bengt Oelmann 2002 22

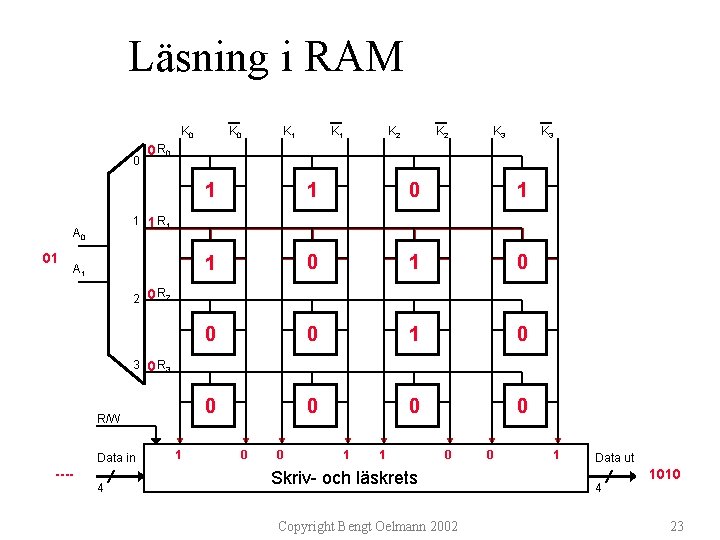

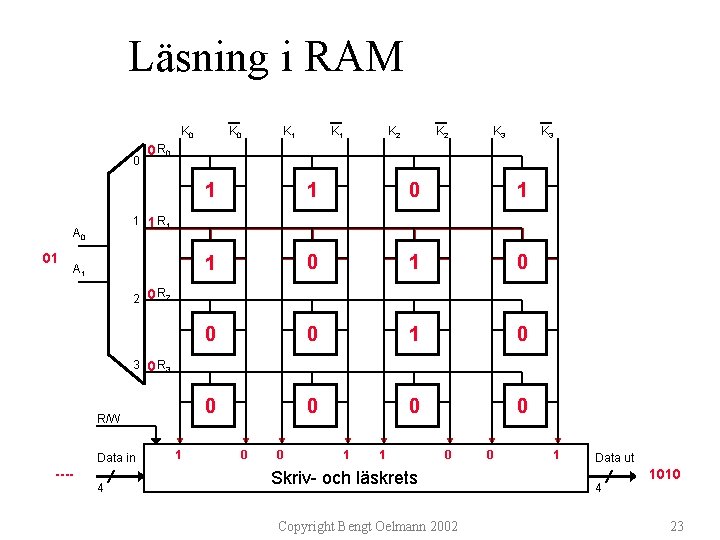

Läsning i RAM K 0 0 K 1 K 2 K 3 0 R 0 1 1 0 1 0 0 0 0 0 1 1 R 1 A 0 01 K 0 A 1 2 0 R 2 3 0 R 3 R/W Data in ---- 4 1 0 0 1 1 0 Skriv- och läskrets Copyright Bengt Oelmann 2002 0 1 Data ut 4 1010 23

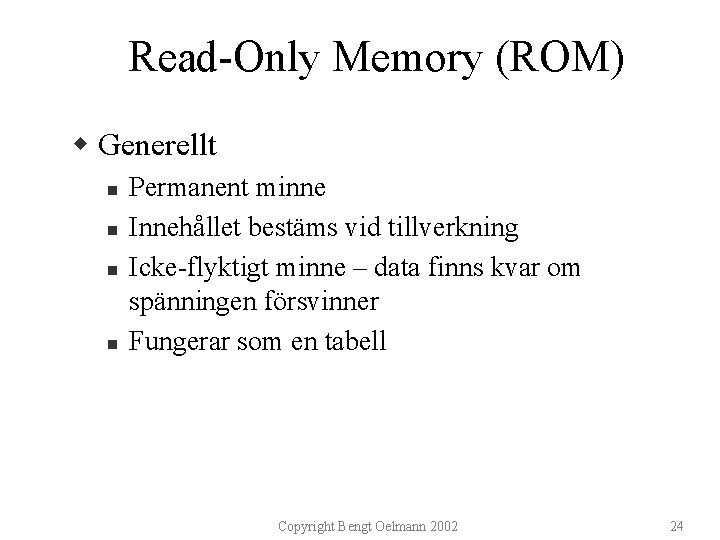

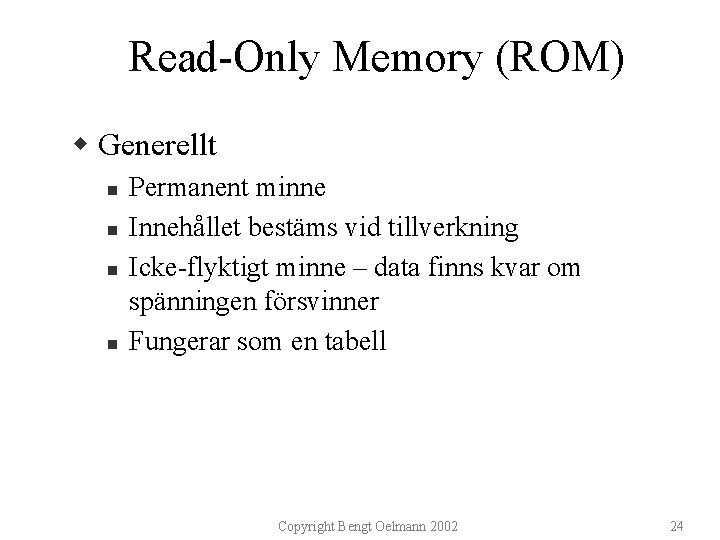

Read-Only Memory (ROM) w Generellt n n Permanent minne Innehållet bestäms vid tillverkning Icke-flyktigt minne – data finns kvar om spänningen försvinner Fungerar som en tabell Copyright Bengt Oelmann 2002 24

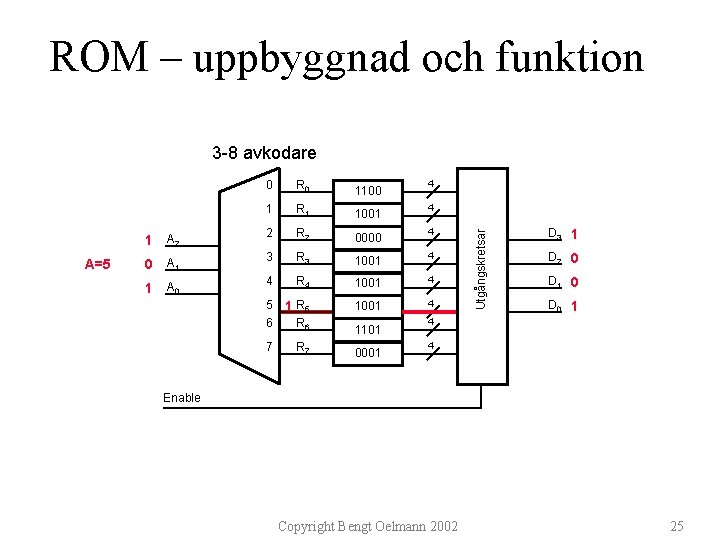

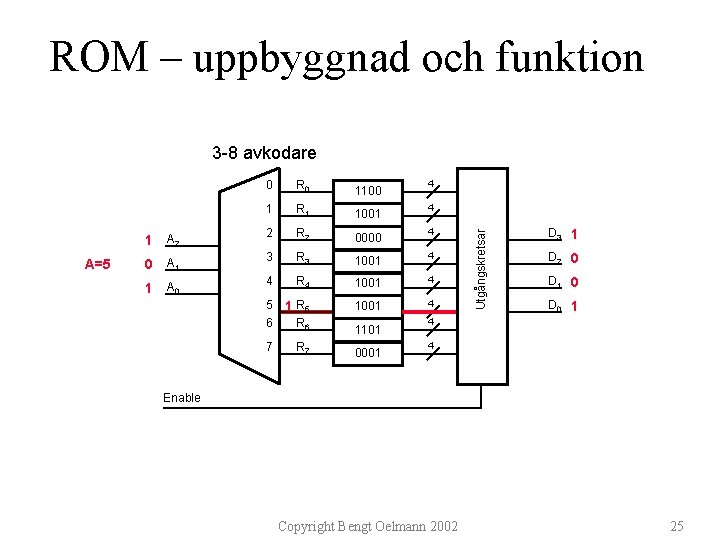

ROM – uppbyggnad och funktion 3 -8 avkodare R 0 1100 1 R 1 1001 4 4 1 A 2 2 R 2 0000 4 0 A 1 3 R 3 1001 4 1 A 0 4 R 4 1001 4 5 1 R 5 1001 4 6 R 6 1101 7 R 7 0001 Utgångskretsar A=5 0 D 3 1 D 2 0 D 1 0 D 0 1 4 4 Enable Copyright Bengt Oelmann 2002 25

SLUT på Föreläsning 6. 1 w Innehåll n Minneselement Låskrets (eng latch) l Vippa (eng. Flip-flop) l Register l n n Random-Access Memory (RAM) Read-Only Memory (ROM) Copyright Bengt Oelmann 2002 26