Mikroszmtgpek I 8085 processzor I 8085 rszei Regiszter

- Slides: 42

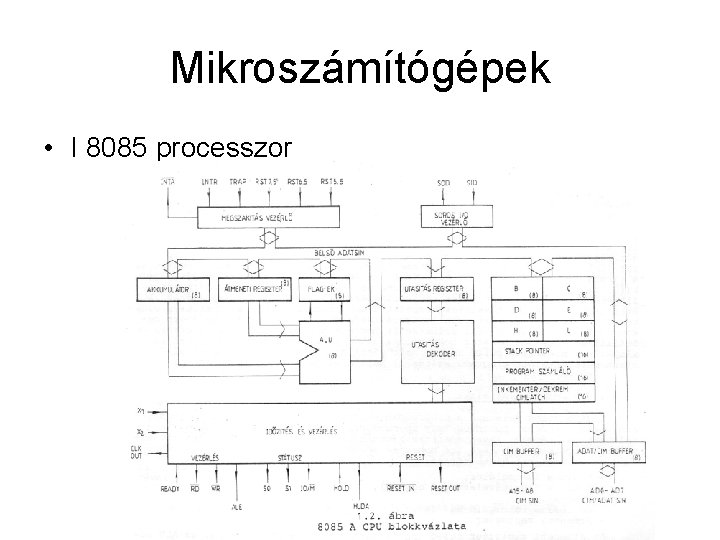

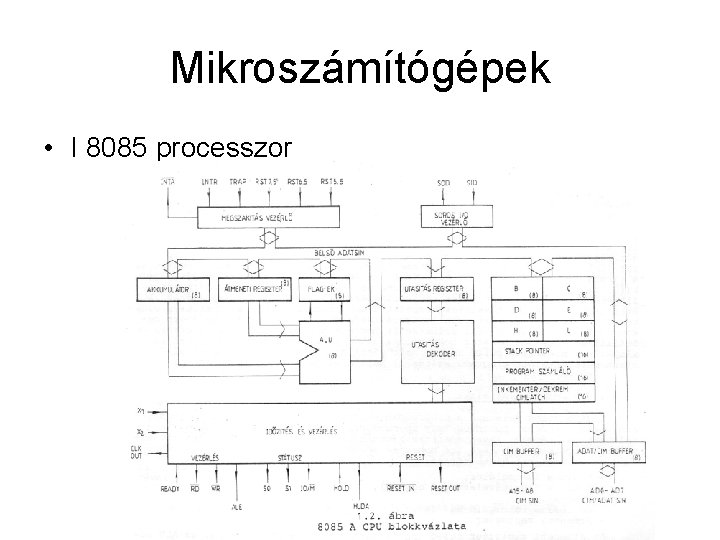

Mikroszámítógépek • I 8085 processzor

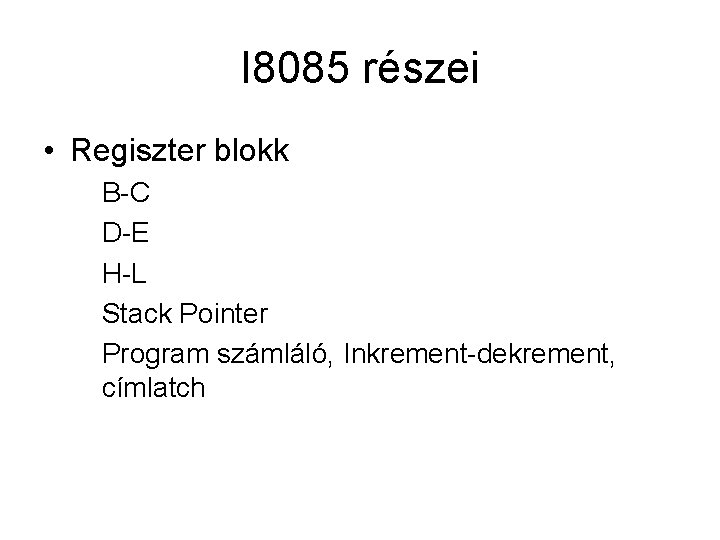

I 8085 részei • Regiszter blokk B-C D-E H-L Stack Pointer Program számláló, Inkrement-dekrement, címlatch

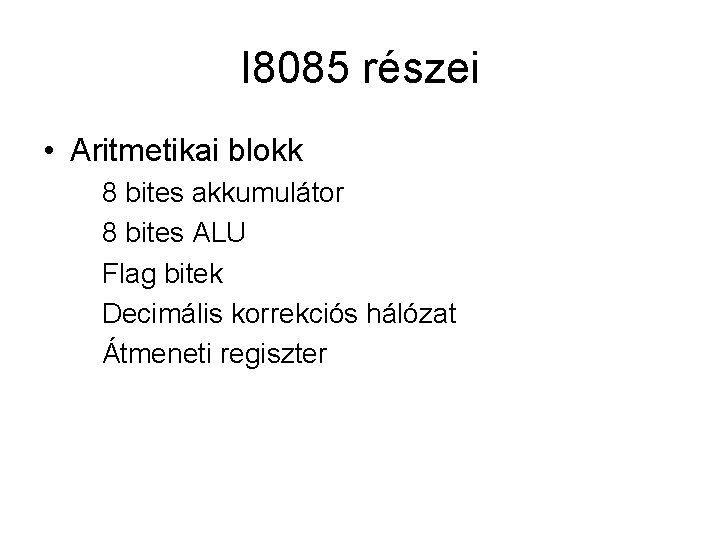

I 8085 részei • Aritmetikai blokk 8 bites akkumulátor 8 bites ALU Flag bitek Decimális korrekciós hálózat Átmeneti regiszter

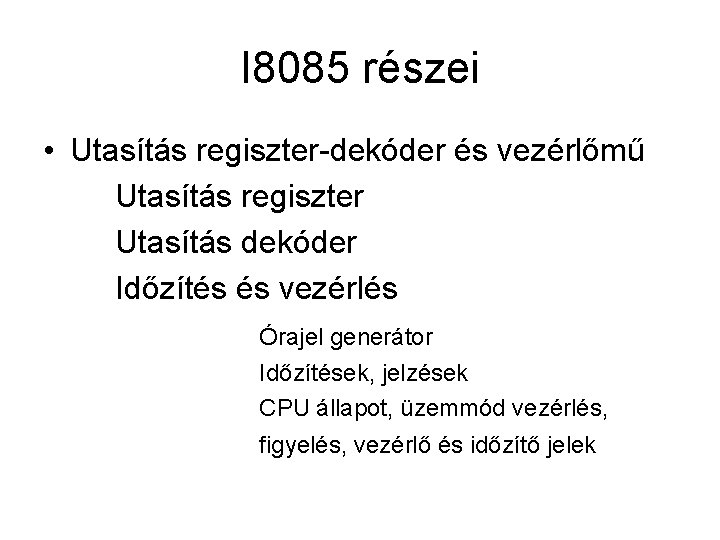

I 8085 részei • Utasítás regiszter-dekóder és vezérlőmű Utasítás regiszter Utasítás dekóder Időzítés és vezérlés Órajel generátor Időzítések, jelzések CPU állapot, üzemmód vezérlés, figyelés, vezérlő és időzítő jelek

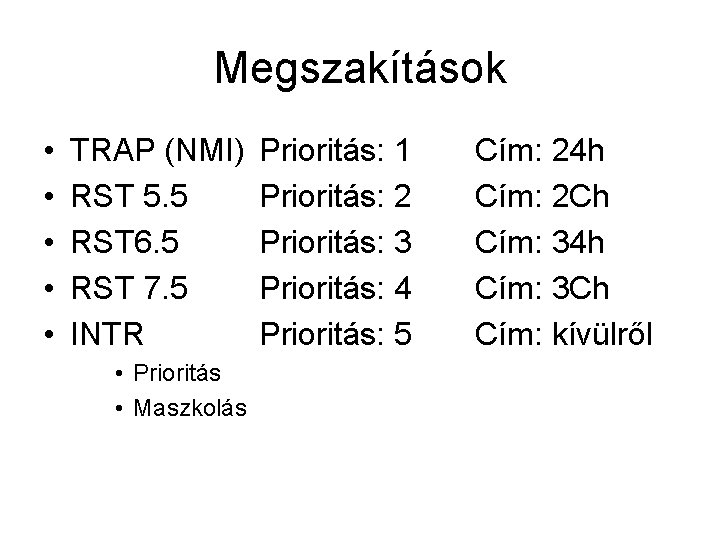

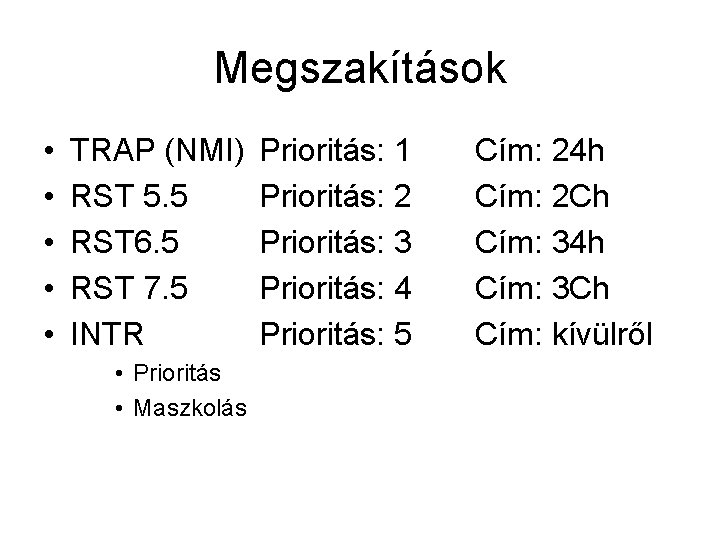

Megszakítások • • • TRAP (NMI) RST 5. 5 RST 6. 5 RST 7. 5 INTR • Prioritás • Maszkolás Prioritás: 1 Prioritás: 2 Prioritás: 3 Prioritás: 4 Prioritás: 5 Cím: 24 h Cím: 2 Ch Cím: 34 h Cím: 3 Ch Cím: kívülről

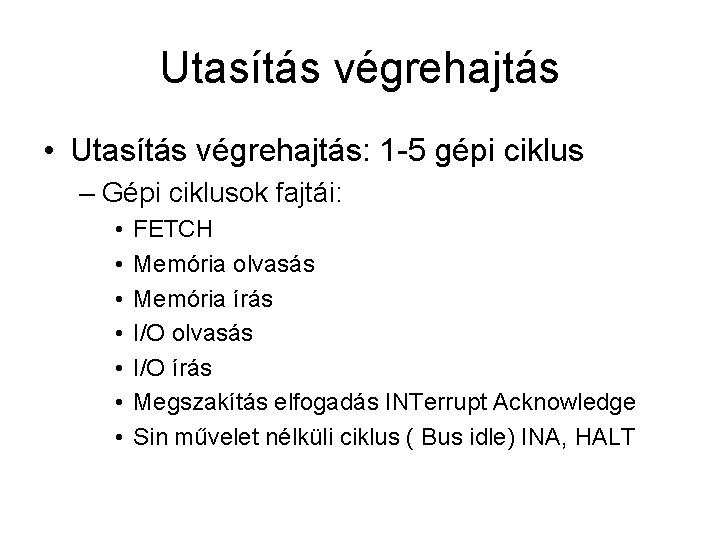

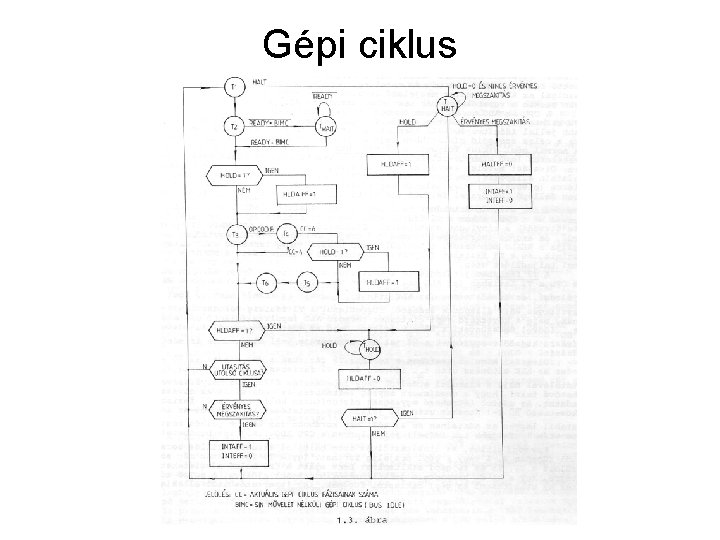

Utasítás végrehajtás • Utasítás végrehajtás: 1 -5 gépi ciklus – Gépi ciklusok fajtái: • • FETCH Memória olvasás Memória írás I/O olvasás I/O írás Megszakítás elfogadás INTerrupt Acknowledge Sin művelet nélküli ciklus ( Bus idle) INA, HALT

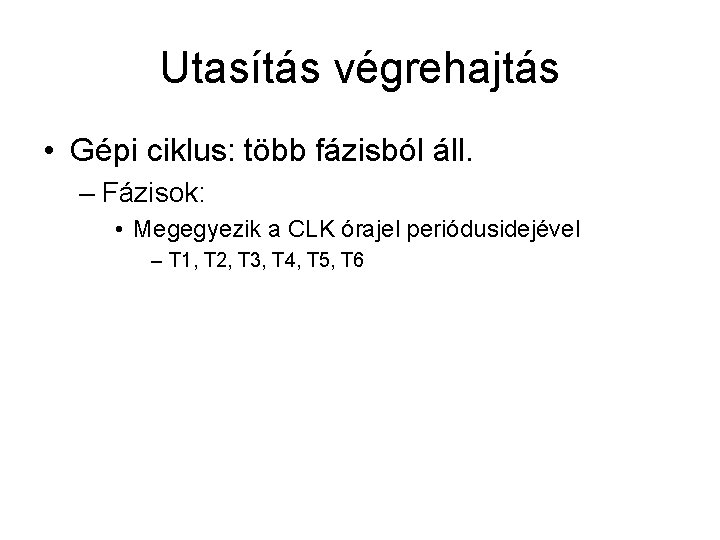

Utasítás végrehajtás • Gépi ciklus: több fázisból áll. – Fázisok: • Megegyezik a CLK órajel periódusidejével – T 1, T 2, T 3, T 4, T 5, T 6

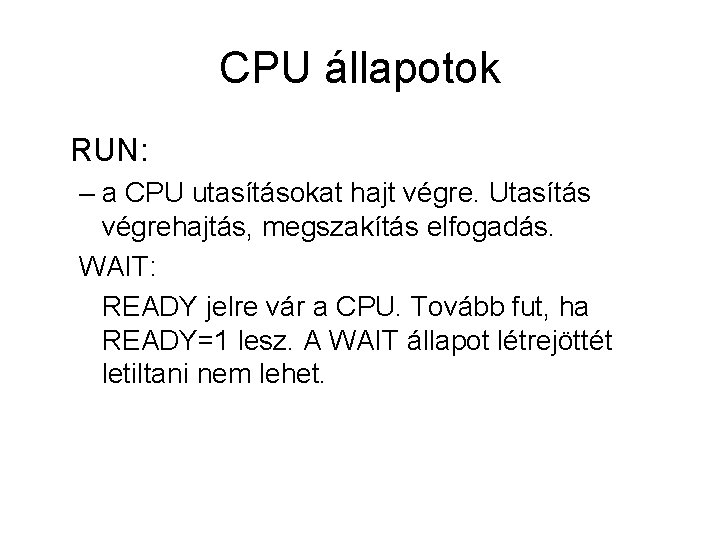

CPU állapotok RUN: – a CPU utasításokat hajt végre. Utasítás végrehajtás, megszakítás elfogadás. WAIT: READY jelre vár a CPU. Tovább fut, ha READY=1 lesz. A WAIT állapot létrejöttét letiltani nem lehet.

• HALT: – HLT utasítás hatására – Megszakítás hatására fut tovább – Halt állapotban HOLD kérelmet elfogad HOLD: CPU kimenetei nagy impedanciás állapotba kerülnek. HOLD jel megszüntéig áll fenn. (DMA) HLDA: nyugtázó jel.

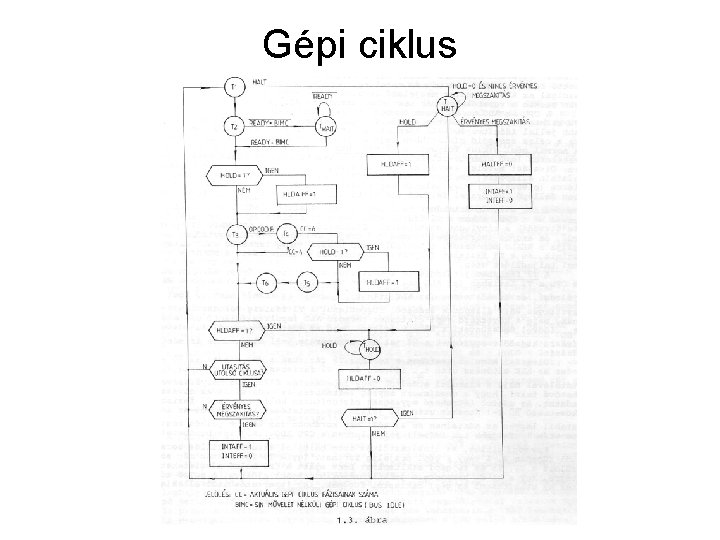

Gépi ciklus

Normál gépi ciklus • Program végrehajtás, Memóriából vagy I/O egységből olvasás, vagy Memóriába vagy I/O egységbe írás történik. 1 Byte adat mozgatása. T 1 -T 3 alatt adat mozgatás T 4 -T 6 alatt CPU- belüli műveletek

HALT típusú gépi ciklus HLT utasítás hatására jön létre. – Utasítás számlálót nem növeli – T 1 után nem jön T 2, hanem HALT állapot – Adat és cím busz, valamint az IO/M, RD, WR vezérlő jelek nagy impedanciás állapotba kerülnek HALT megszüntetése: HOLD kérelem, RESET, Külső megszakítás

HOLD állapot • T 3 fázis előtt mintavételezi a HOLD jelet. – A CPU HOLD állapotba kerül és kiadja a HLDA jelet – AD 0 -AD 7, A 8 -A 15, RD, WR, IO/M nagy impedanciás állapotba kerül. – HOLD jel megszünte után visszatés normál állapotba.

Megszakítás kezelés • Az utasítás végrehajtás utolsó ciklusában fogad el megszakítást. – Megszakítás elfogadás után INterrupt Acknowledge ( INA) ciklus jön létre. – INTA által ütemezve CALL utasítás kódot, majd két cím byte-ot vesz át a CPU a megszakító egységtől. – TRAP. RST 5. 5, RST 6. 5 és RST 7. 5 fix címekkel rendelkezik. – TRAP: nem tiltható le.

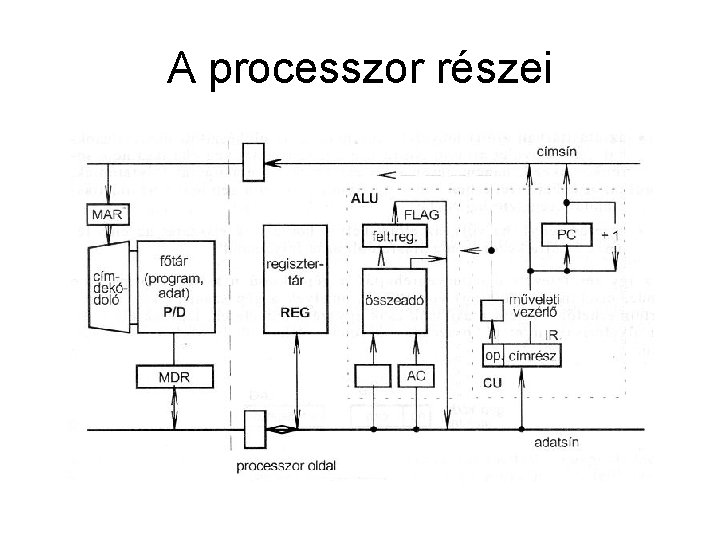

A processzor részei Vezérlő egység: Control Unit: A műveleti kód vagy megszakítások alapján a CPU vezérlése a feladata Aritmetikai-Logikai egység: Aritmetikai és logikai műveletek végrehajtása Regiszterek: Utasítás számláló Utasítás regiszter

A processzor részei Regiszterek: Utasítás számláló Utasítás regiszter Bázis cím regiszter Index regiszter Állapot/vezérlő regiszter Stack pointer Puffer regiszterek: Belső és külső busz szétválasztása.

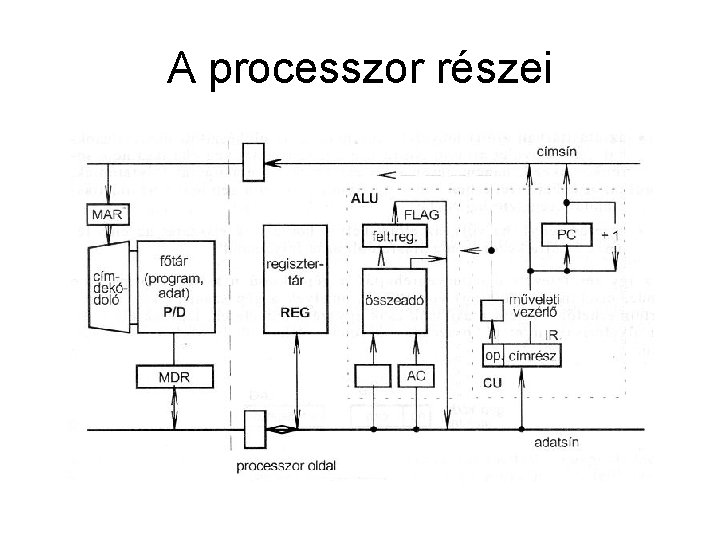

A processzor részei

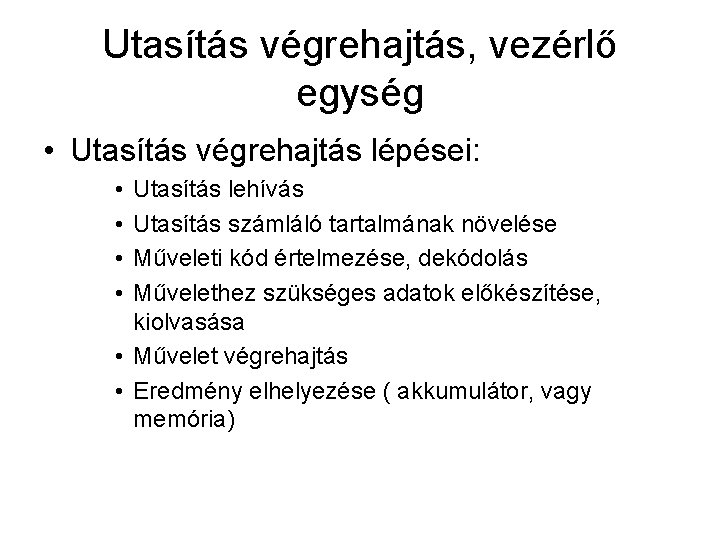

Utasítás végrehajtás, vezérlő egység • Utasítás végrehajtás lépései: • • Utasítás lehívás Utasítás számláló tartalmának növelése Műveleti kód értelmezése, dekódolás Művelethez szükséges adatok előkészítése, kiolvasása • Művelet végrehajtás • Eredmény elhelyezése ( akkumulátor, vagy memória)

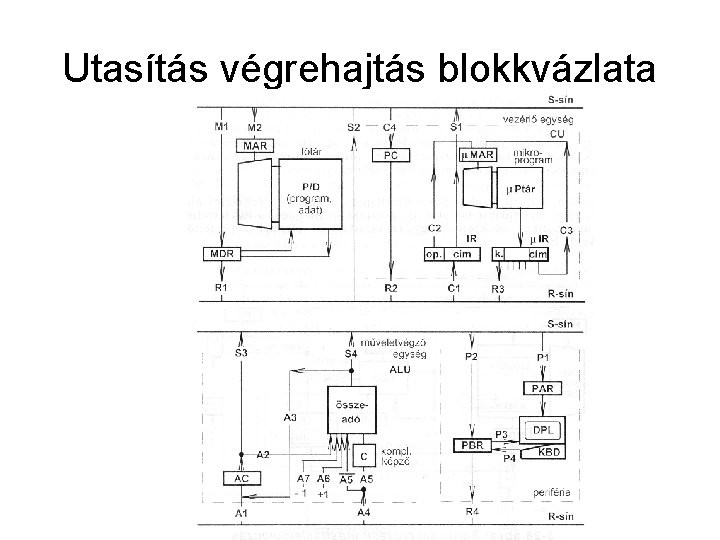

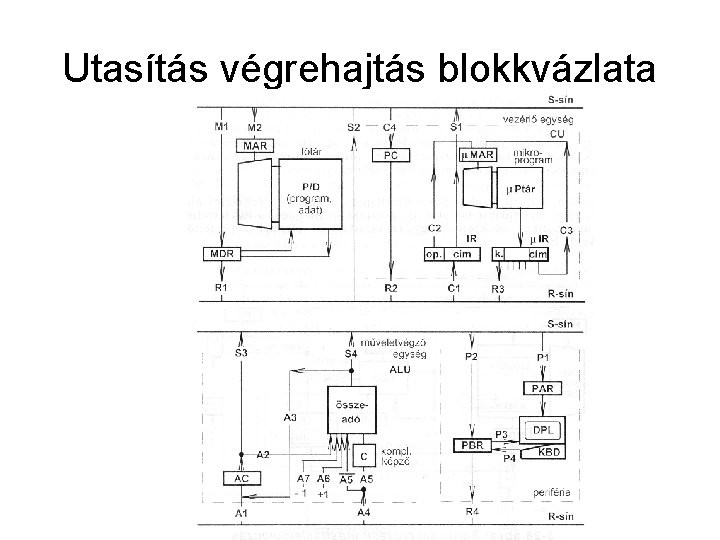

Utasítás végrehajtás blokkvázlata

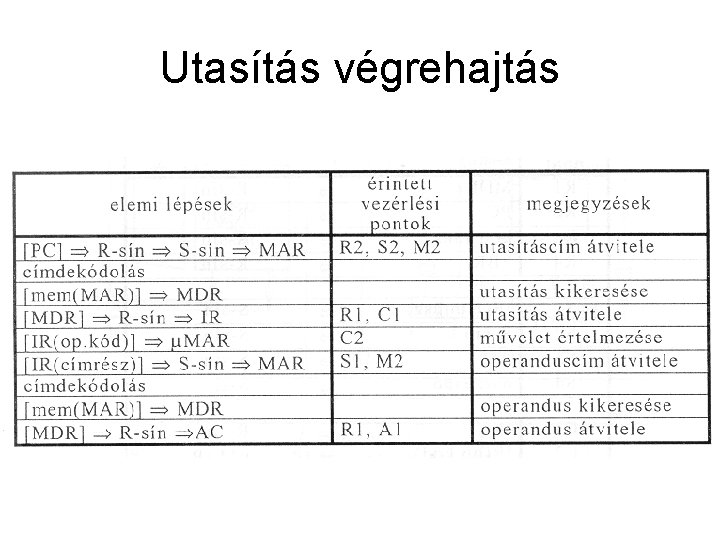

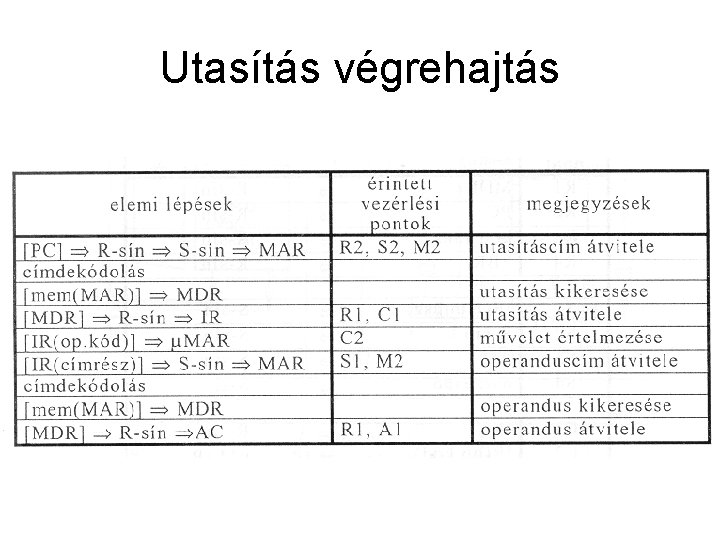

Utasítás végrehajtás

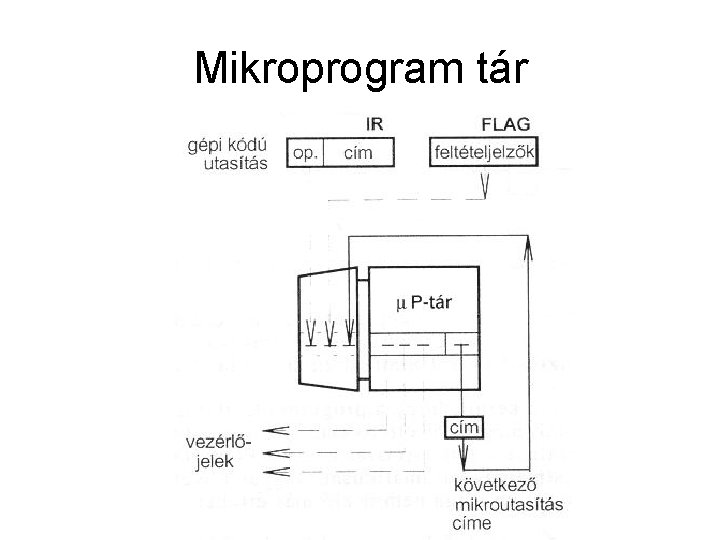

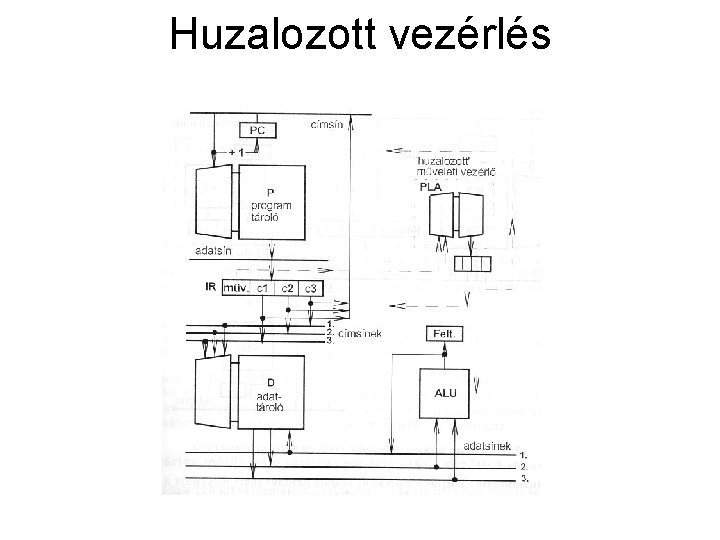

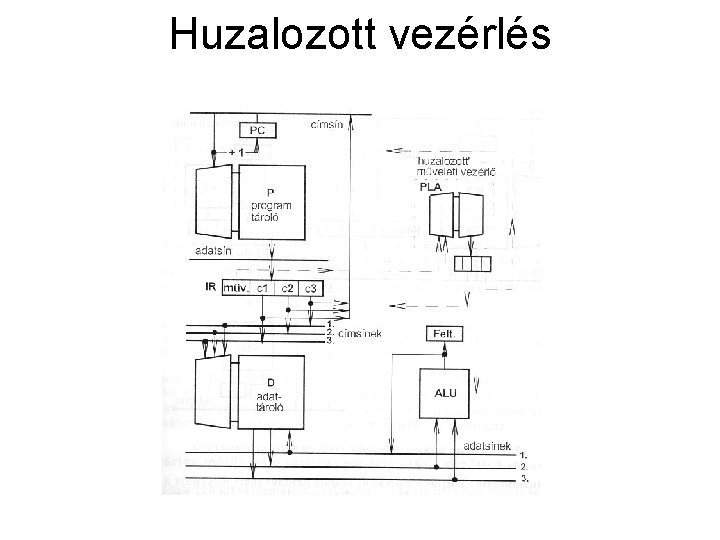

Műveleti vezérlés módjai Huzalozott A művelet végrehajtáshoz szükséges elemi tevékenységek sorrendjének vezérlését sorrendi, és kombinációs hálózatok vezérlik. ( PLA) Mikroprogramozott A végrehajtás lépéseit a mikroprogram tárban tárolt utasítások vezérlik

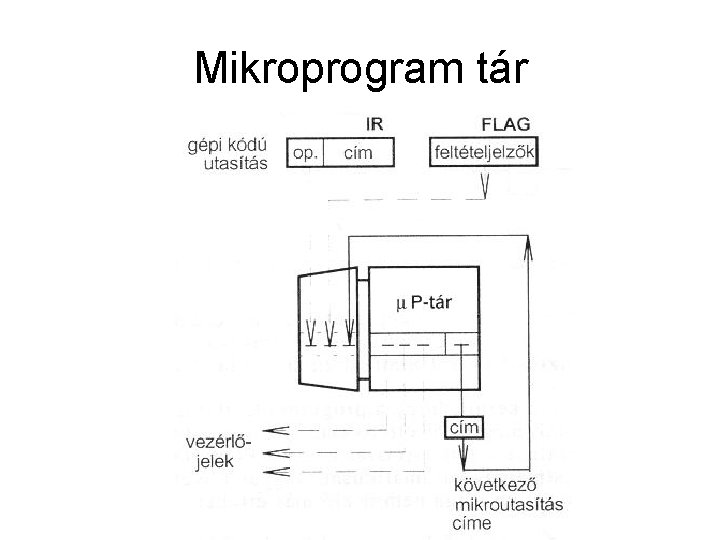

Mikroprogram tár

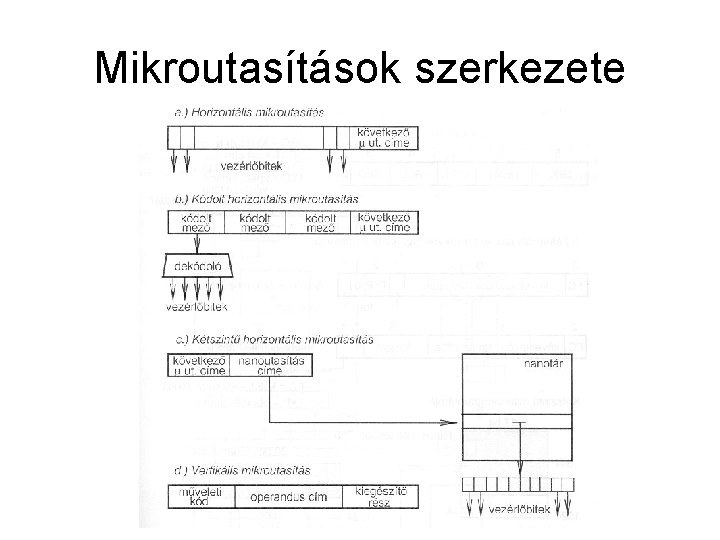

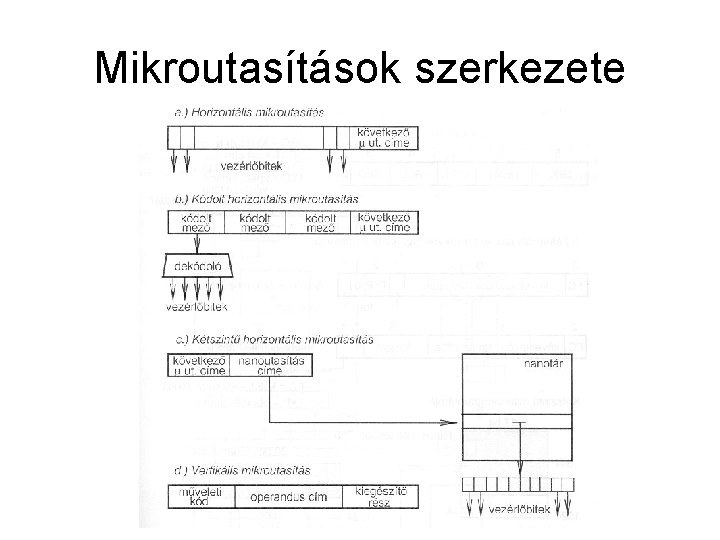

Mikroutasítások szerkezete

Huzalozott vezérlés

Mikroprogramozott vezérlés:

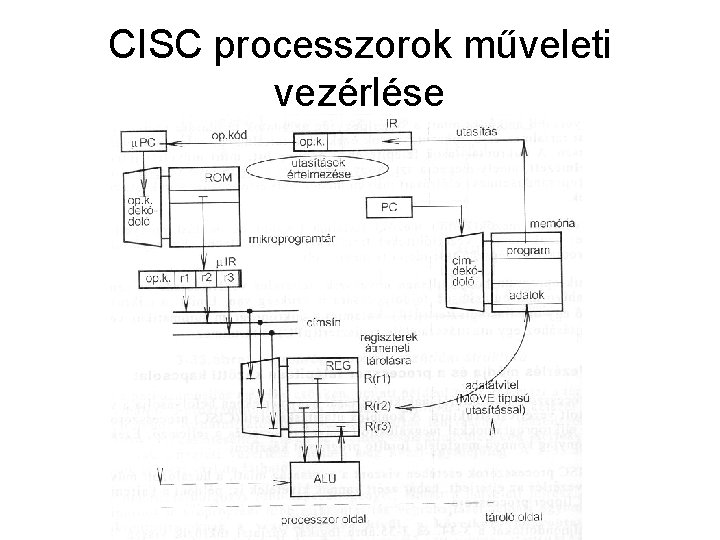

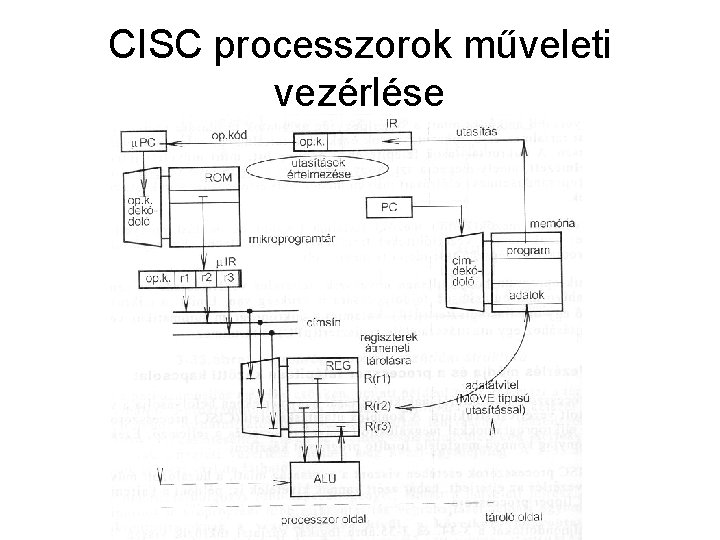

CISC processzorok műveleti vezérlése • CISC processzorok: – Sok, bonyolult utasítás: mikroprogramozott vezérléssel a legegyszerűbb megvalósítani. – Adat mozgás művelet végrehajtás közben főleg a memória és a regiszterek között zajlik.

CISC processzorok műveleti vezérlése

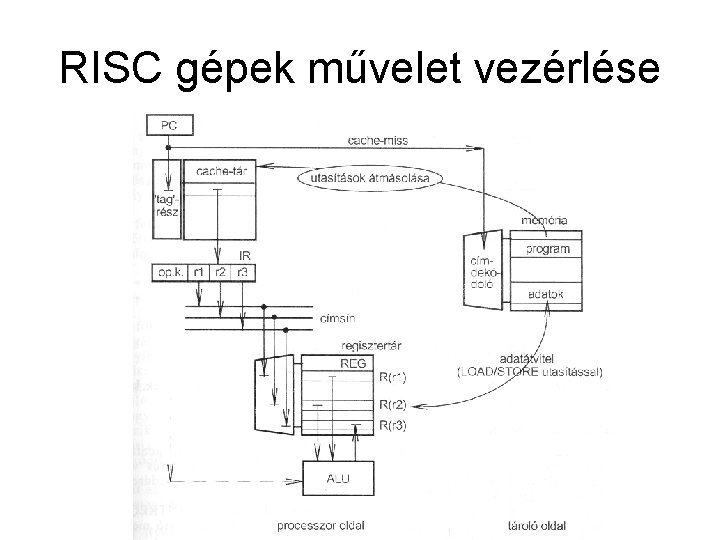

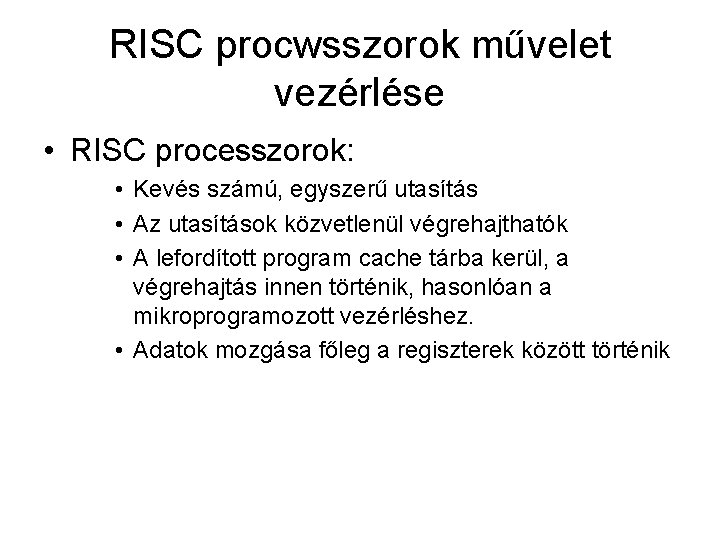

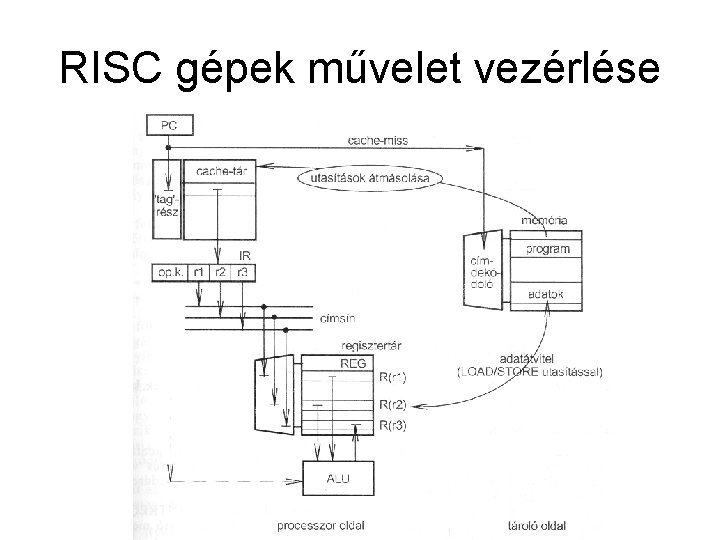

RISC procwsszorok művelet vezérlése • RISC processzorok: • Kevés számú, egyszerű utasítás • Az utasítások közvetlenül végrehajthatók • A lefordított program cache tárba kerül, a végrehajtás innen történik, hasonlóan a mikroprogramozott vezérléshez. • Adatok mozgása főleg a regiszterek között történik

RISC gépek művelet vezérlése

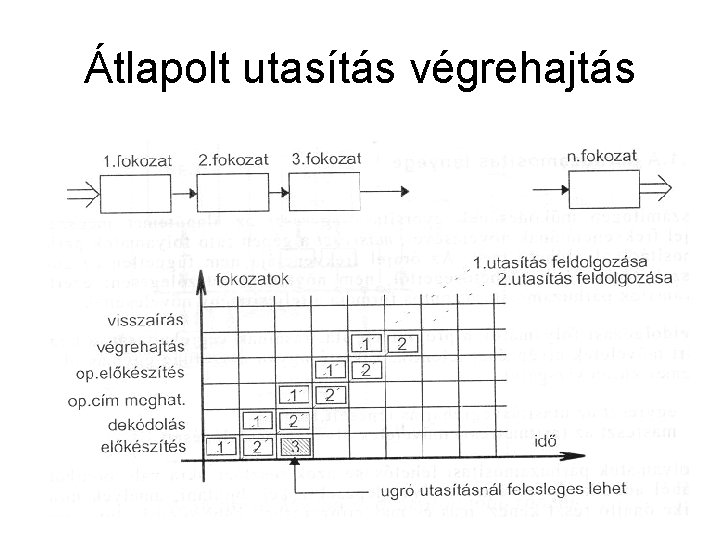

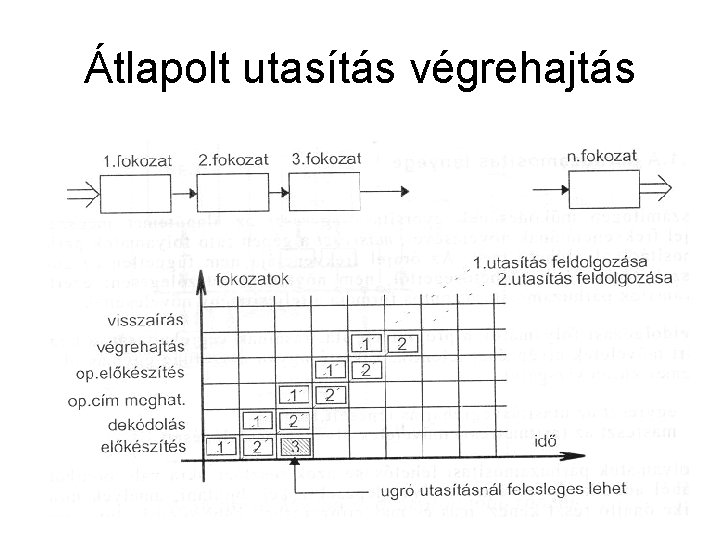

Átlapolt utasítás végrehajtás

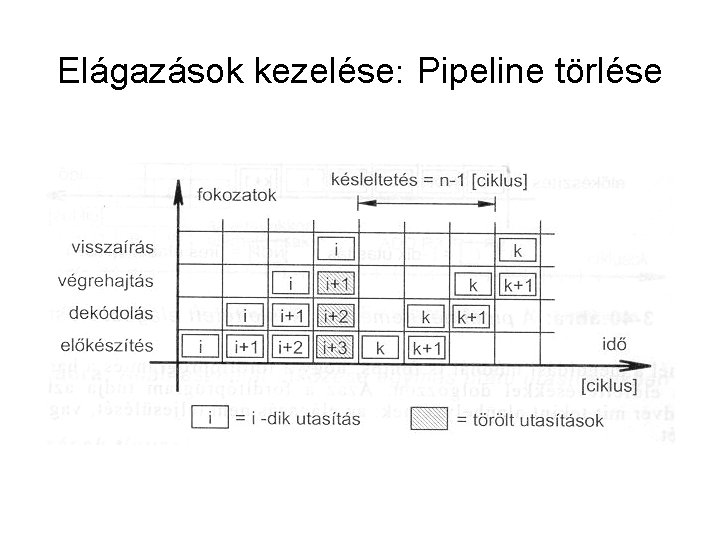

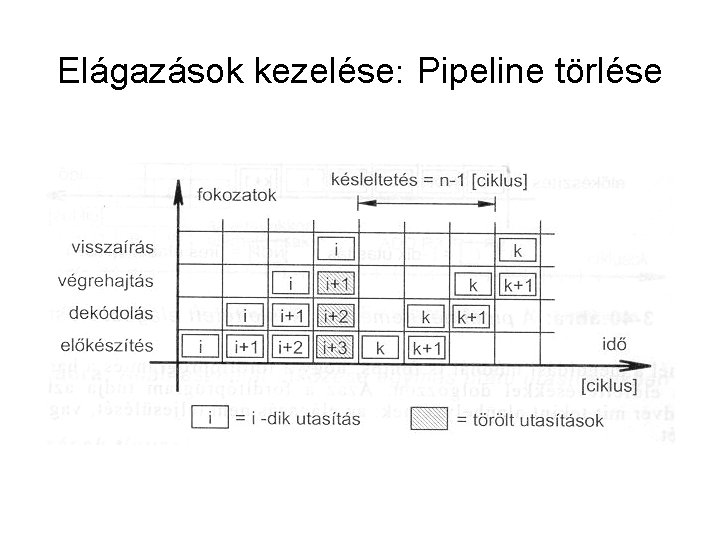

Elágazások kezelése: Pipeline törlése

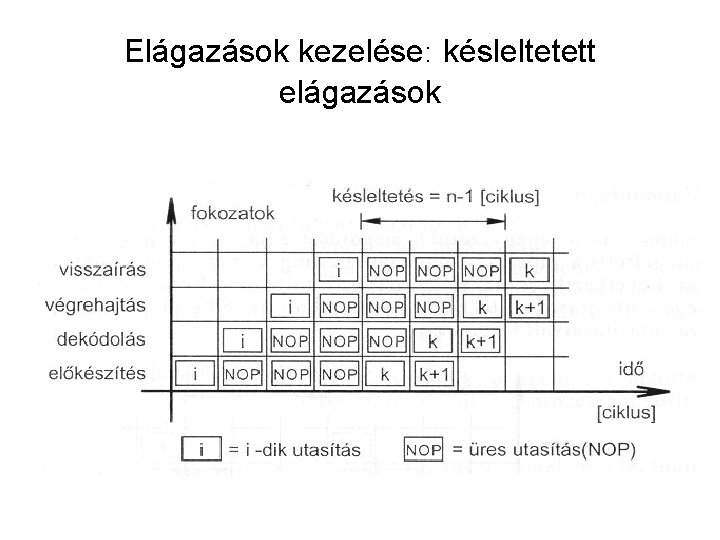

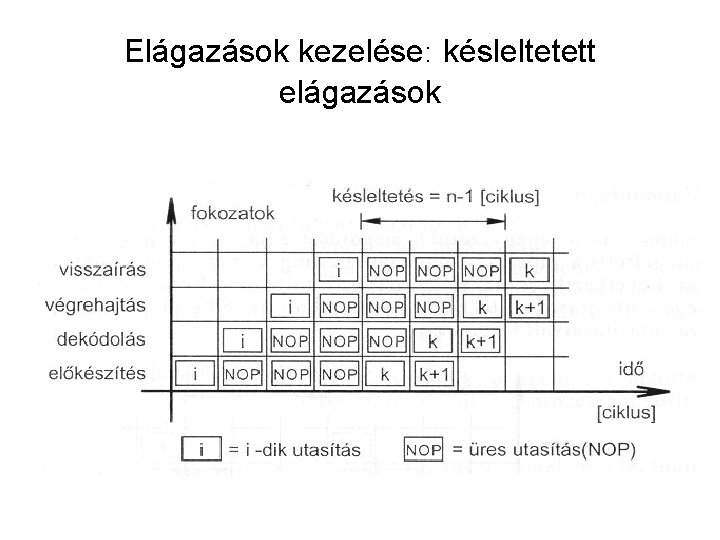

Elágazások kezelése: késleltetett elágazások

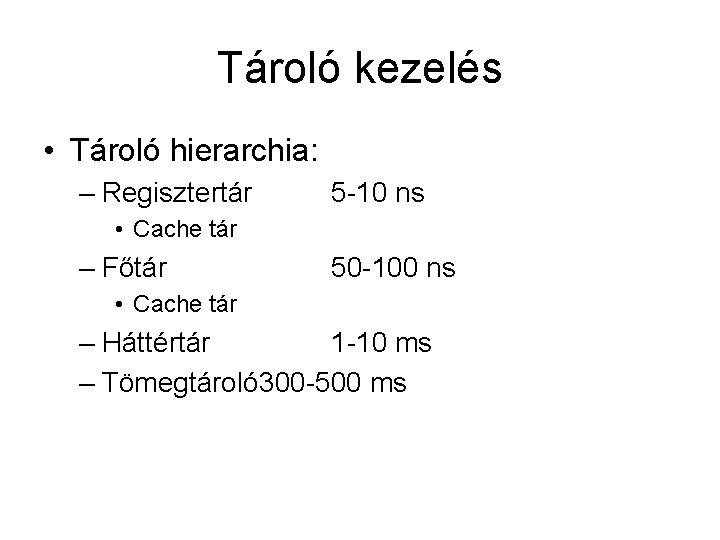

Tároló kezelés • Tároló hierarchia: – Regisztertár 5 -10 ns • Cache tár – Főtár 50 -100 ns • Cache tár – Háttértár 1 -10 ms – Tömegtároló 300 -500 ms

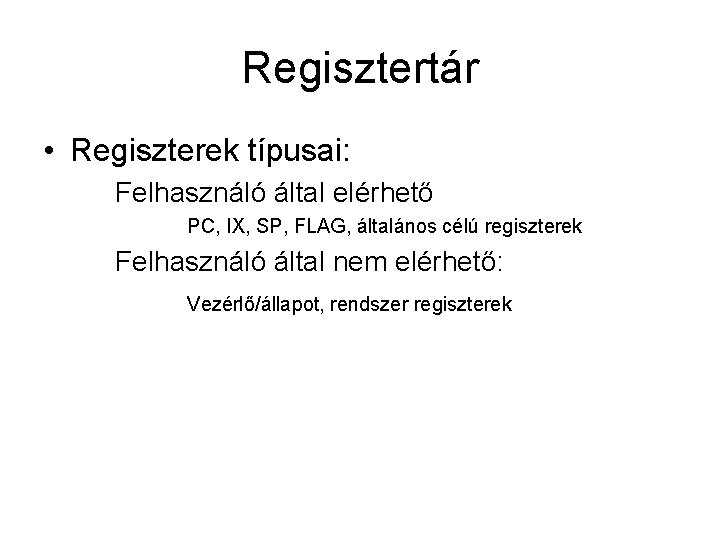

Regisztertár • Regiszterek típusai: Felhasználó által elérhető PC, IX, SP, FLAG, általános célú regiszterek Felhasználó által nem elérhető: Vezérlő/állapot, rendszer regiszterek

Regisztertárakkal szemben támasztott kövelelmények • Adatforgalom csökkentése a memória és a processzor között • Nagy méret ( 32, 64, 128. . Db) • 3 címes elérés ( 2 operandus + eredmény) • Általános felhasználású legyen

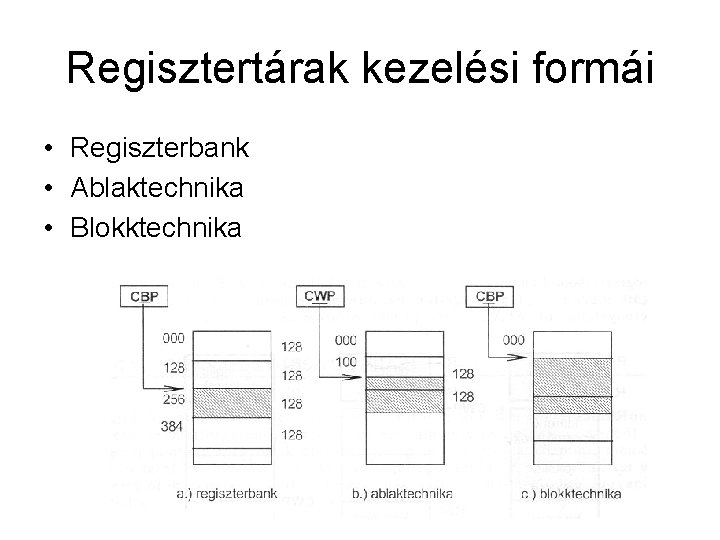

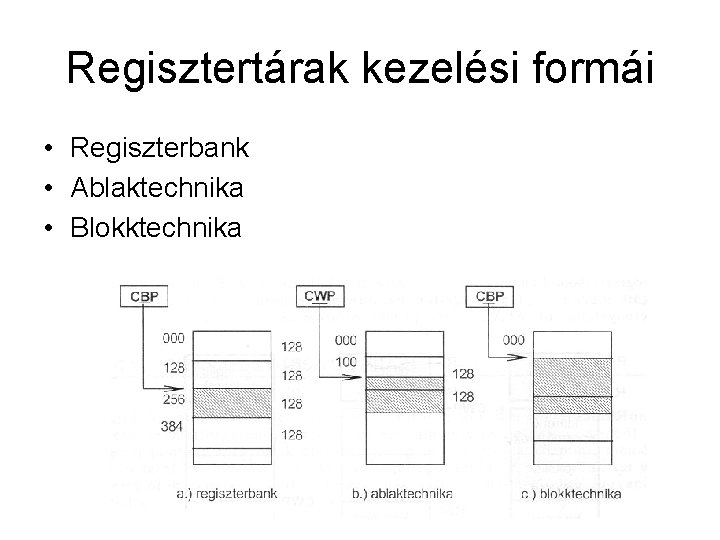

Regisztertárak kezelési formái • Regiszterbank • Ablaktechnika • Blokktechnika

Cache tárak jellemzői • ON-CHIP ( 8 -32 k. B) vagy OFF CHIP 64 -256 k. B ( processzorban vagy kívül) • Adatátvitel a cache és a memória között blokkos • Utasítás, adat illetve vegyes cache tárolók lehetnek • Általában tartalom szerinti visszakereséssel működnek ( asszociatív) cache tár • Tartalom cseréjéhez hatékony stratégia kell • CPU és cache sebessége legyen azonos

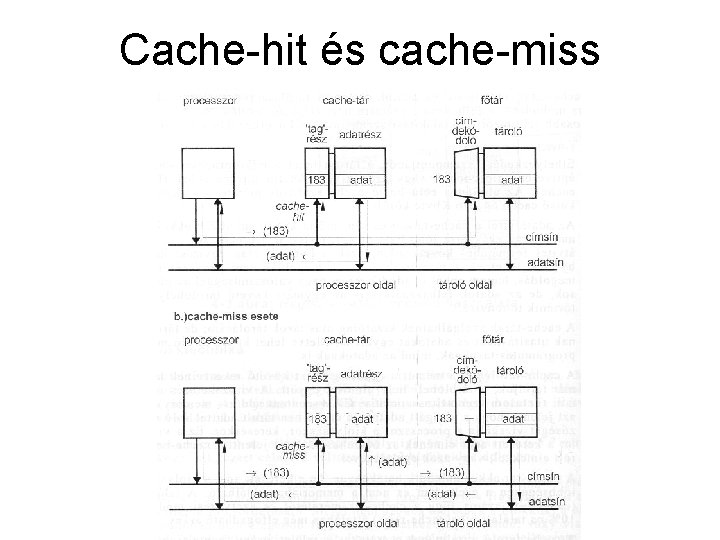

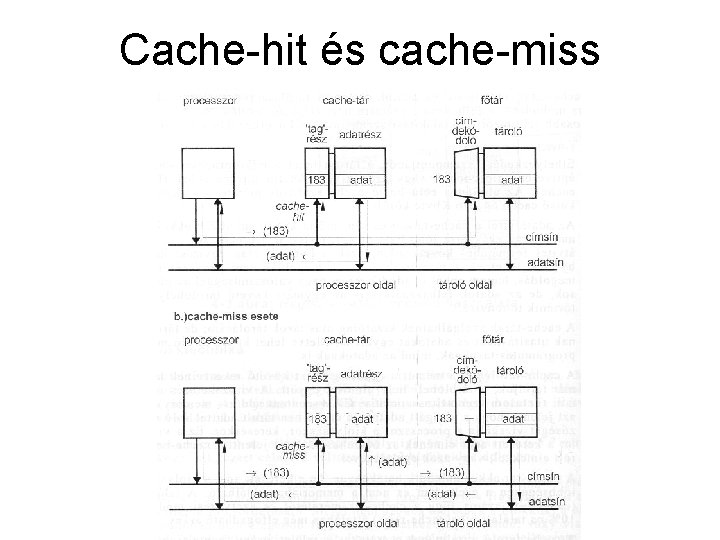

Cache-hit és cache-miss

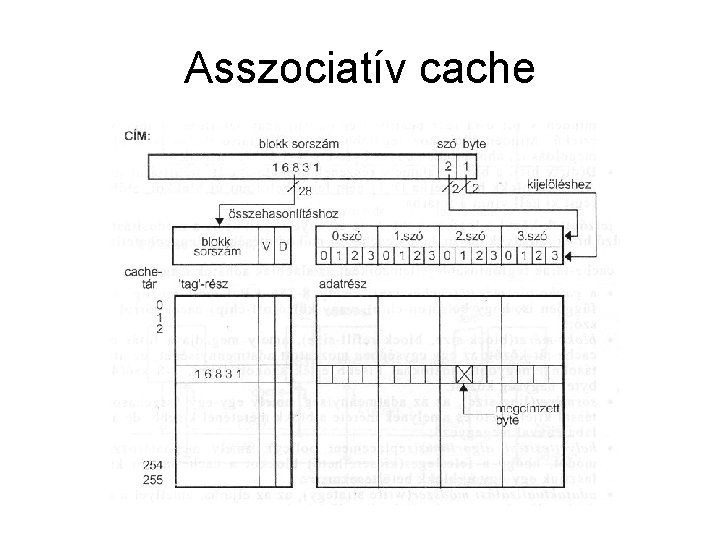

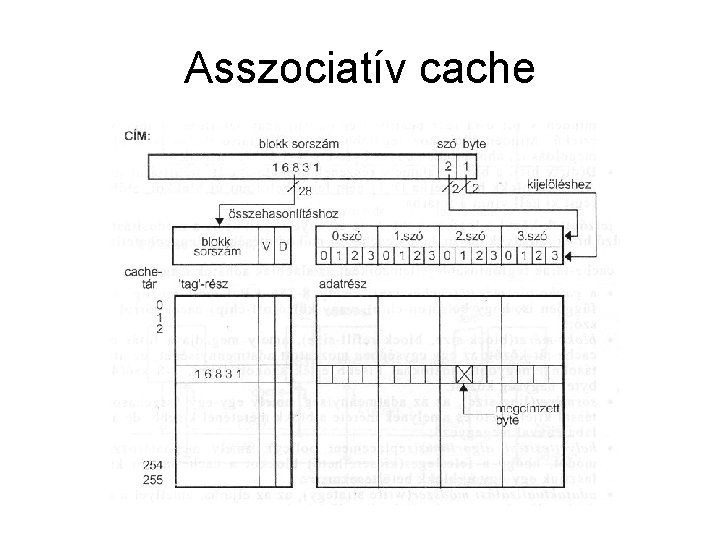

Asszociatív cache

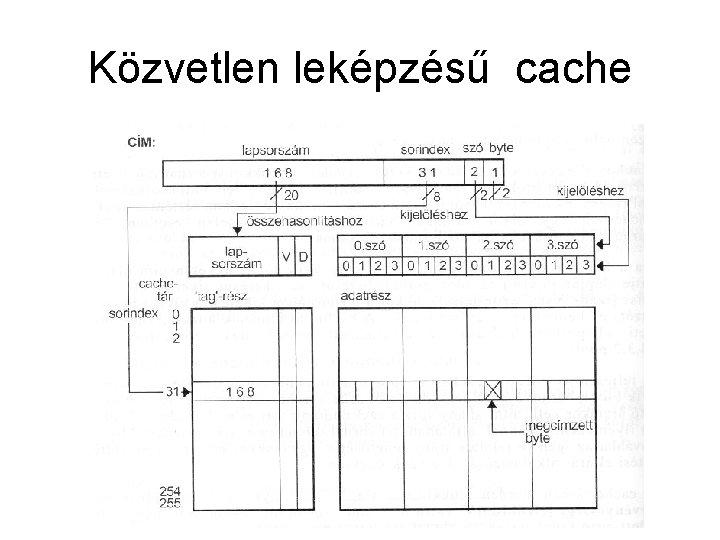

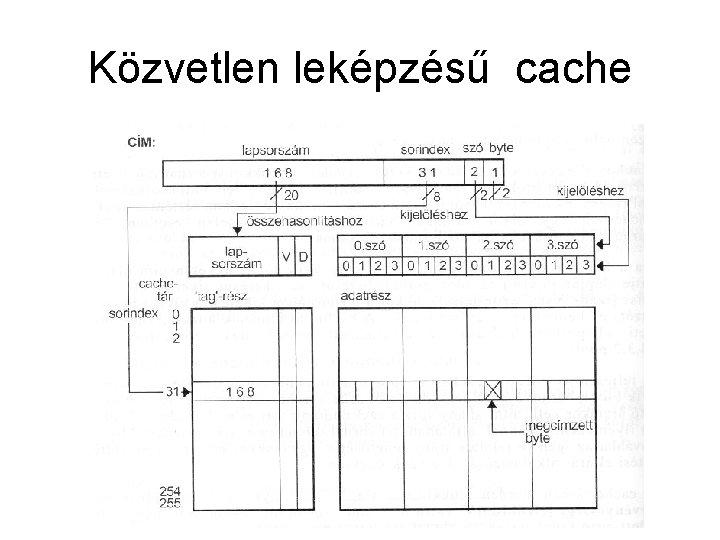

Közvetlen leképzésű cache

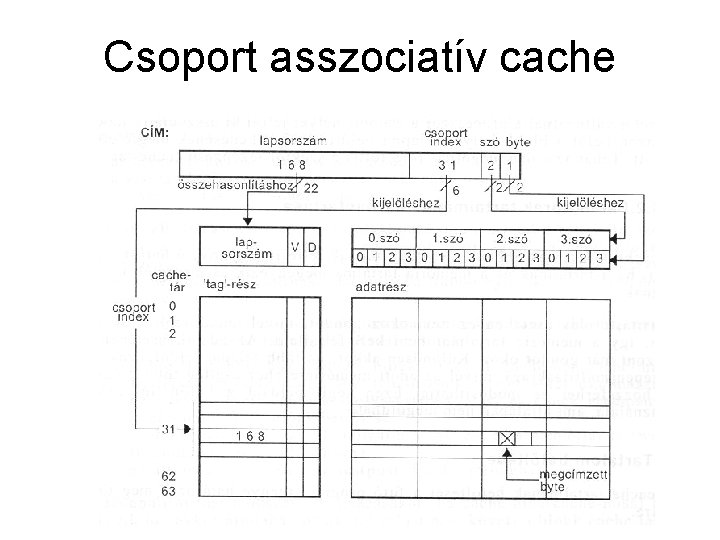

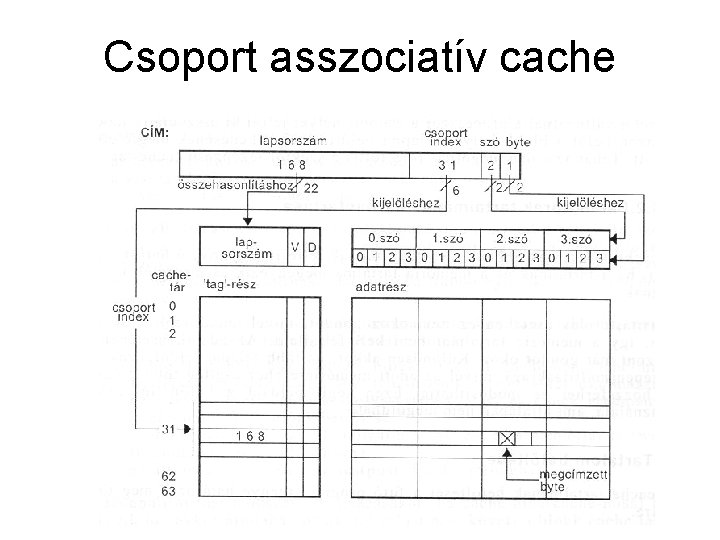

Csoport asszociatív cache