Microwave Oscillator By Professor Syed Idris Syed Hassan

Microwave Oscillator By Professor Syed Idris Syed Hassan Sch of Elect. & Electron Engineering Campus USM Nibong Tebal 14300 SPS Penang

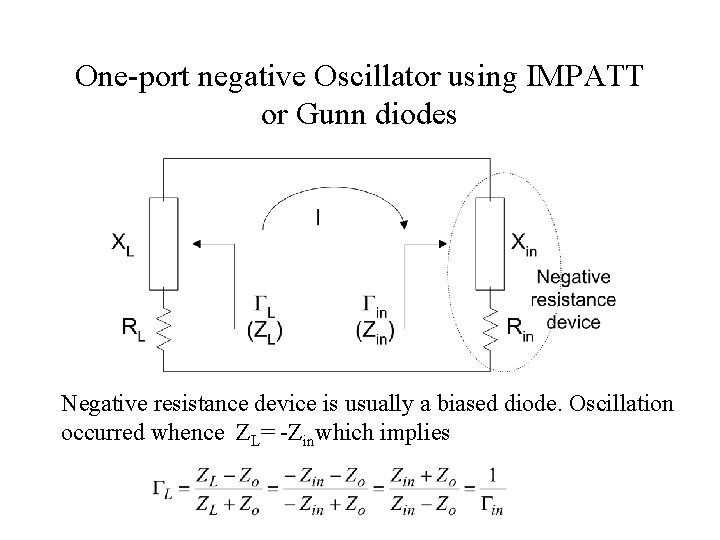

One-port negative Oscillator using IMPATT or Gunn diodes Negative resistance device is usually a biased diode. Oscillation occurred whence ZL= -Zinwhich implies

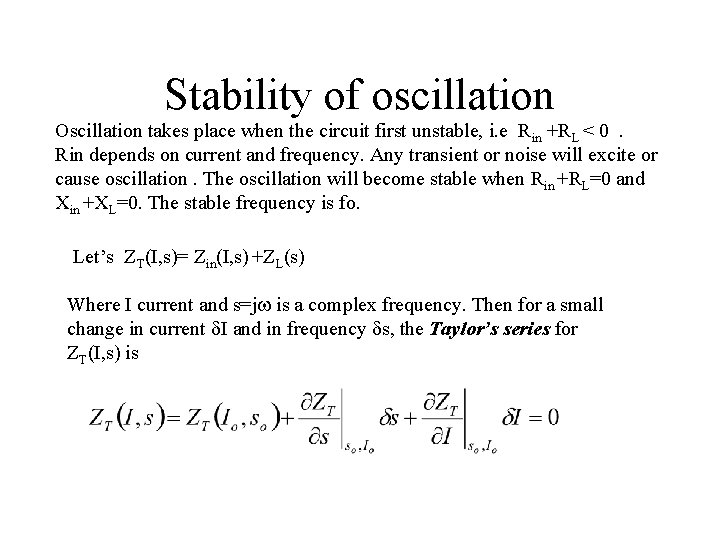

Stability of oscillation Oscillation takes place when the circuit first unstable, i. e Rin +RL < 0. Rin depends on current and frequency. Any transient or noise will excite or cause oscillation. The oscillation will become stable when Rin +RL=0 and Xin +XL=0. The stable frequency is fo. Let’s ZT(I, s)= Zin(I, s) +ZL(s) Where I current and s=jw is a complex frequency. Then for a small change in current d. I and in frequency ds, the Taylor’s series for ZT(I, s) is

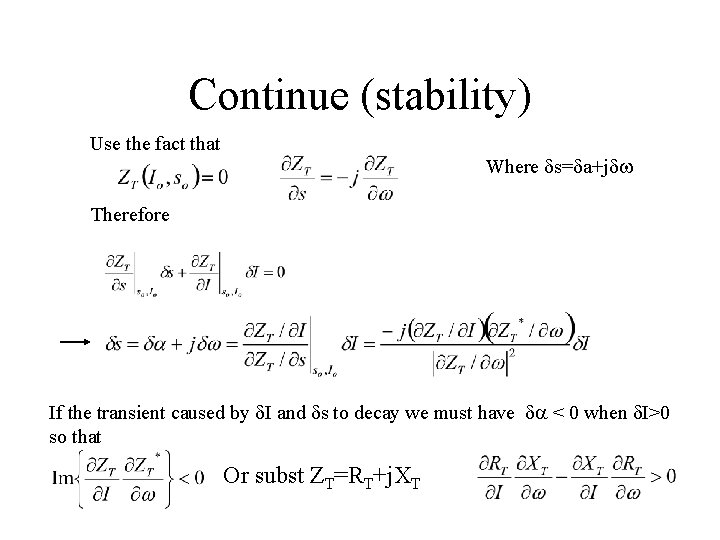

Continue (stability) Use the fact that Where ds=da+jdw Therefore If the transient caused by d. I and ds to decay we must have da < 0 when d. I>0 so that Or subst ZT=RT+j. XT

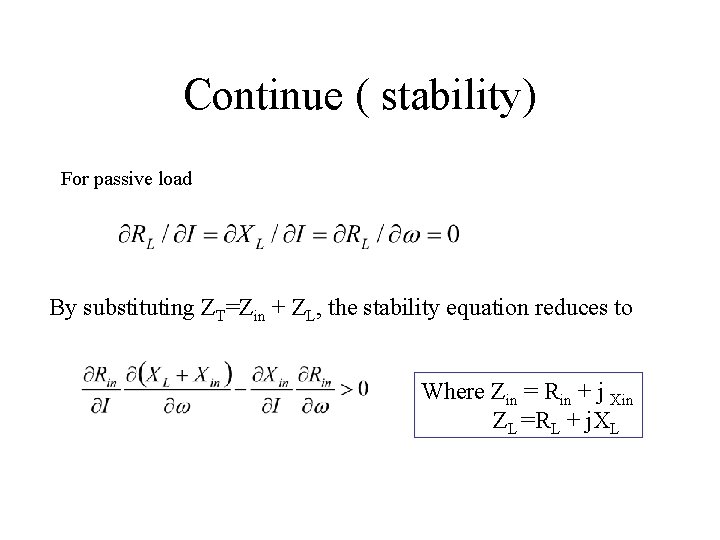

Continue ( stability) For passive load By substituting ZT=Zin + ZL, the stability equation reduces to Where Zin = Rin + j Xin ZL =RL + j. XL

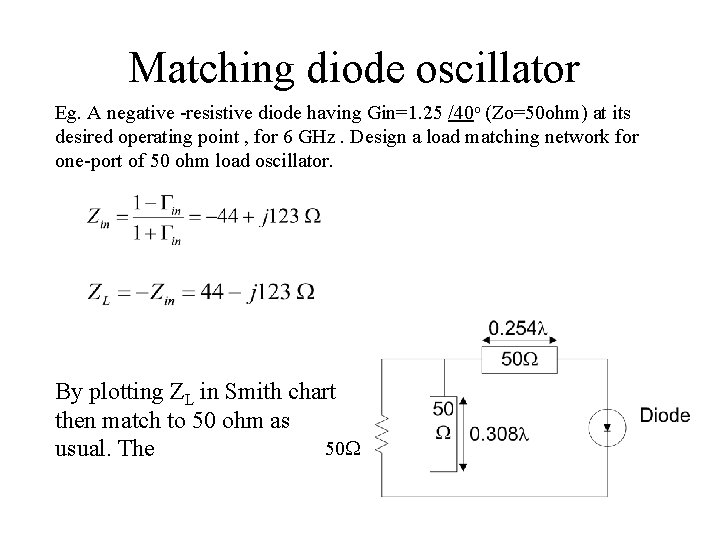

Matching diode oscillator Eg. A negative -resistive diode having Gin=1. 25 /40 o (Zo=50 ohm) at its desired operating point , for 6 GHz. Design a load matching network for one-port of 50 ohm load oscillator. By plotting ZL in Smith chart then match to 50 ohm as 50 W usual. The

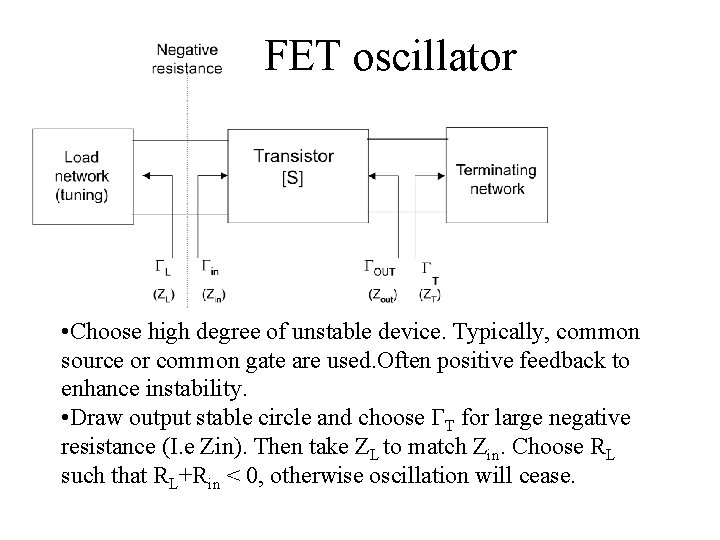

FET oscillator • Choose high degree of unstable device. Typically, common source or common gate are used. Often positive feedback to enhance instability. • Draw output stable circle and choose GT for large negative resistance (I. e Zin). Then take ZL to match Zin. Choose RL such that RL+Rin < 0, otherwise oscillation will cease.

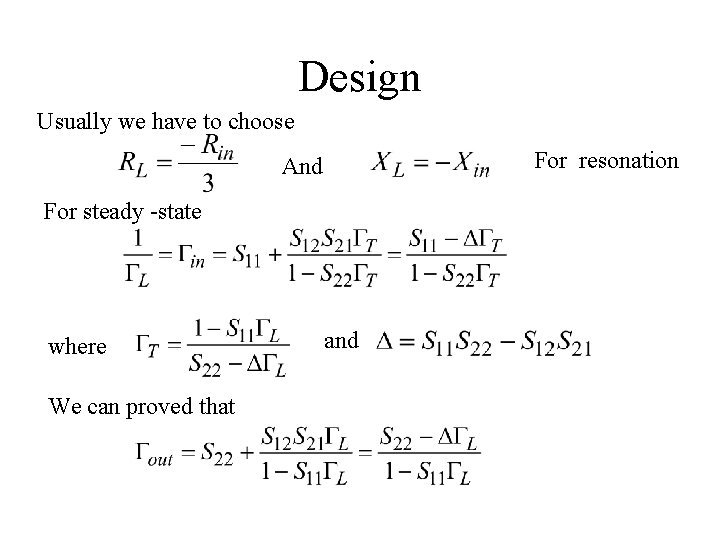

Design Usually we have to choose For resonation And For steady -state where We can proved that and

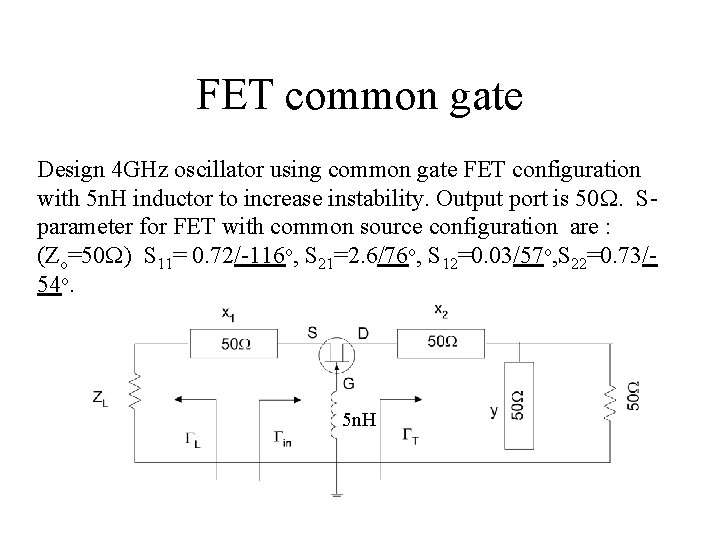

FET common gate Design 4 GHz oscillator using common gate FET configuration with 5 n. H inductor to increase instability. Output port is 50 W. Sparameter for FET with common source configuration are : (Zo=50 W) S 11= 0. 72/-116 o, S 21=2. 6/76 o, S 12=0. 03/57 o, S 22=0. 73/54 o. 5 n. H

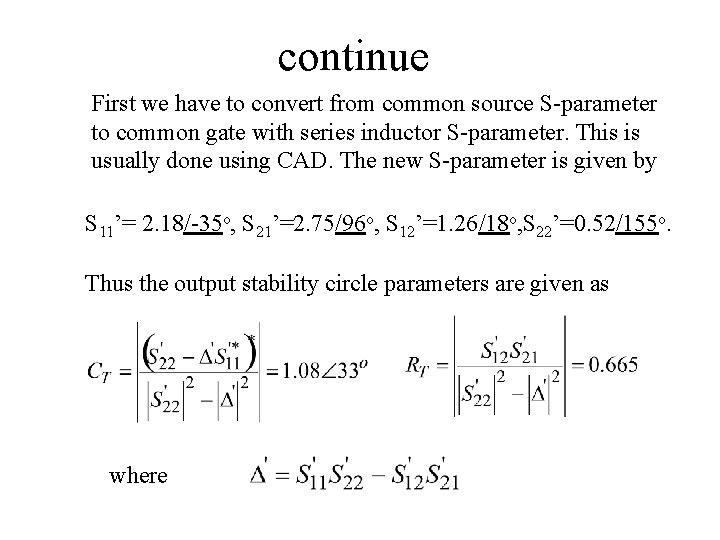

continue First we have to convert from common source S-parameter to common gate with series inductor S-parameter. This is usually done using CAD. The new S-parameter is given by S 11’= 2. 18/-35 o, S 21’=2. 75/96 o, S 12’=1. 26/18 o, S 22’=0. 52/155 o. Thus the output stability circle parameters are given as where

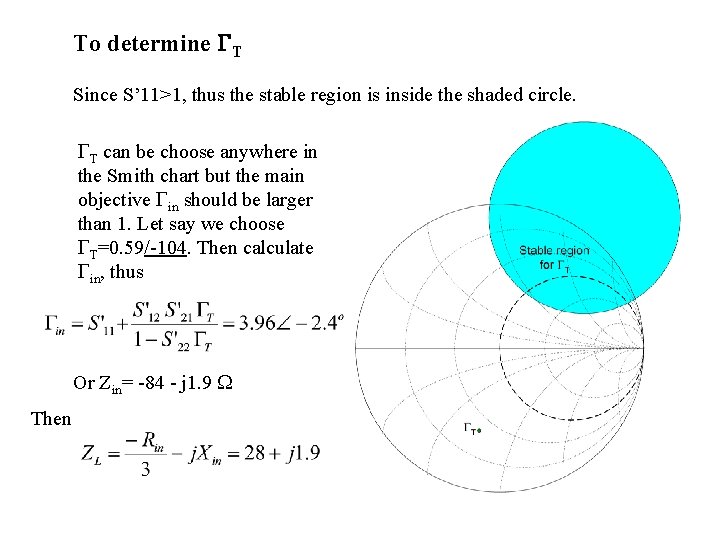

To determine GT Since S’ 11>1, thus the stable region is inside the shaded circle. GT can be choose anywhere in the Smith chart but the main objective Gin should be larger than 1. Let say we choose GT=0. 59/-104. Then calculate Gin, thus Or Zin= -84 - j 1. 9 W Then

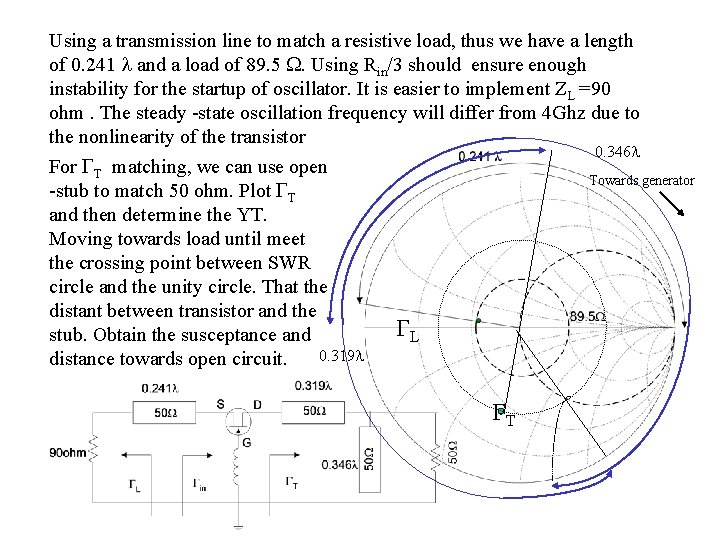

Using a transmission line to match a resistive load, thus we have a length of 0. 241 l and a load of 89. 5 W. Using Rin/3 should ensure enough instability for the startup of oscillator. It is easier to implement ZL =90 ohm. The steady -state oscillation frequency will differ from 4 Ghz due to the nonlinearity of the transistor For GT matching, we can use open -stub to match 50 ohm. Plot GT and then determine the YT. Moving towards load until meet the crossing point between SWR circle and the unity circle. That the distant between transistor and the stub. Obtain the susceptance and 0. 319 l distance towards open circuit. 0. 346 l Towards generator GL GT

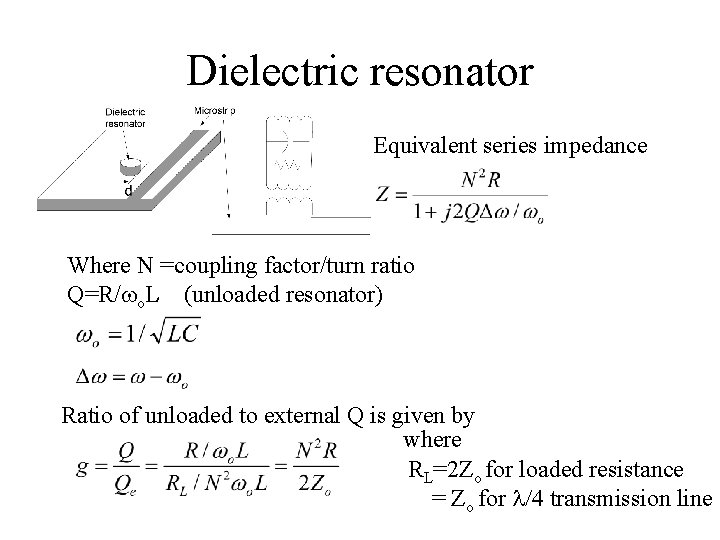

Dielectric resonator Equivalent series impedance Where N =coupling factor/turn ratio Q=R/wo. L (unloaded resonator) Ratio of unloaded to external Q is given by where RL=2 Zo for loaded resistance = Zo for l/4 transmission line

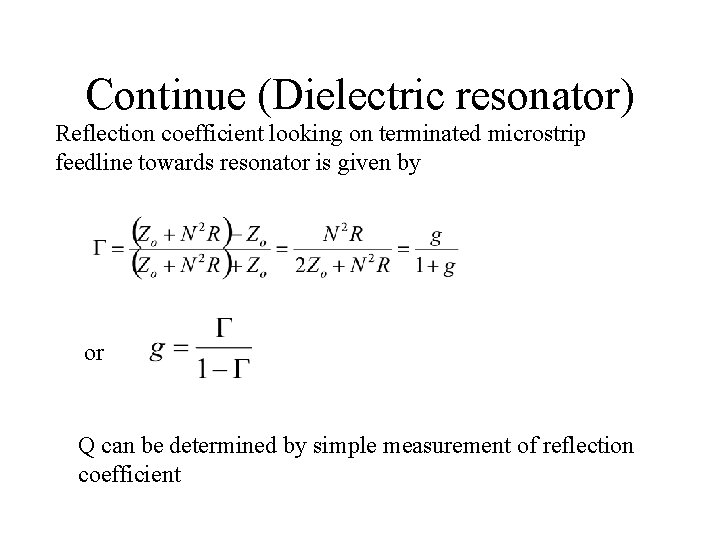

Continue (Dielectric resonator) Reflection coefficient looking on terminated microstrip feedline towards resonator is given by or Q can be determined by simple measurement of reflection coefficient

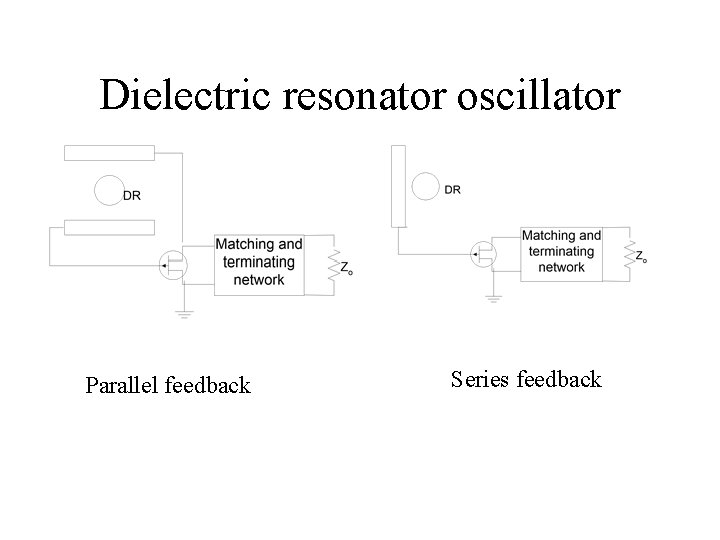

Dielectric resonator oscillator Parallel feedback Series feedback

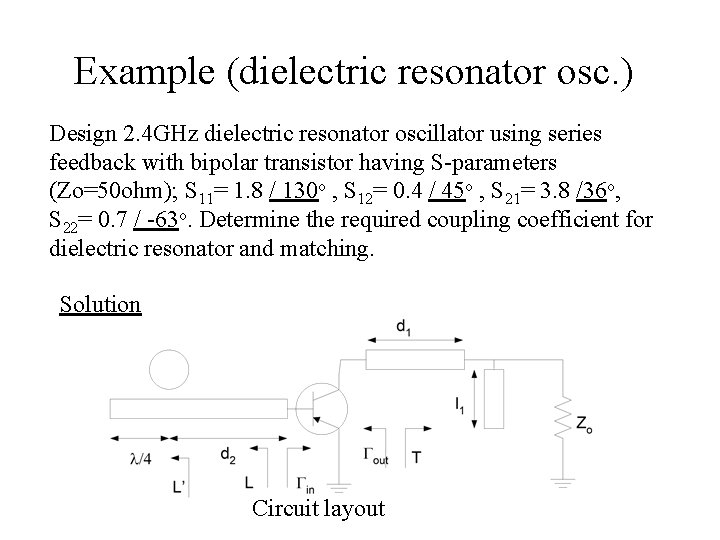

Example (dielectric resonator osc. ) Design 2. 4 GHz dielectric resonator oscillator using series feedback with bipolar transistor having S-parameters (Zo=50 ohm); S 11= 1. 8 / 130 o , S 12= 0. 4 / 45 o , S 21= 3. 8 /36 o, S 22= 0. 7 / -63 o. Determine the required coupling coefficient for dielectric resonator and matching. Solution Circuit layout

continue Procedures 1. Plot the stability circles 2. Choose a point Gin Inside the instability area

continue Calculate the Gout and Gin = GL using this formula We obtain Gout = 10. 7/132 o. This corresponding to Then

Continue (output matching) X So we have d 1=0. 034 l l 1=0. 193 l Or d 1=0. 429 l l 1=0. 307 l

Network at resonator Resonator should be placed at zero or 180 o of phase from the transistor. So we have either 0. 181 l (zero phase) or 0. 431 l (180 o phase) d 2= 0. 181 l Or = 0. 431 l

Noise in oscillator • Amplitude noise • Phase noise • Flicker noise Phase noise-may be due to variation of device capacitance with variation of voltage. This is usually happened in amplifier. Amplitude noise may be converted to phase noise if the amplifier is present. Noises cause frequency instability in oscillator.

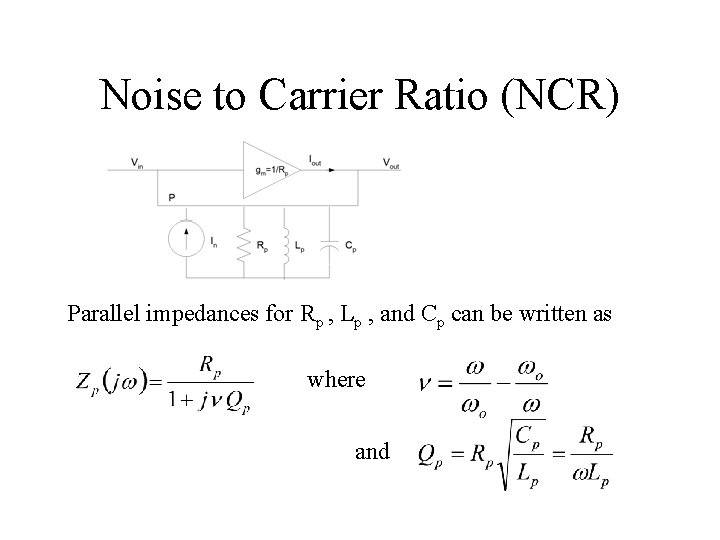

Noise to Carrier Ratio (NCR) Parallel impedances for Rp , Lp , and Cp can be written as where and

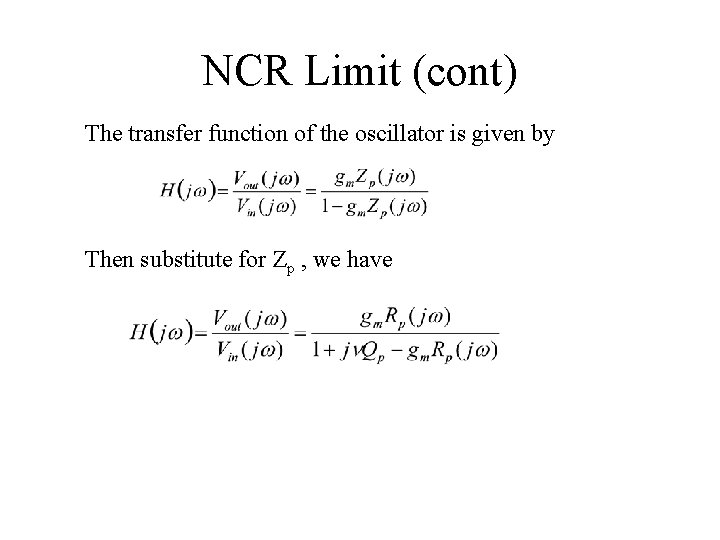

NCR Limit (cont) The transfer function of the oscillator is given by Then substitute for Zp , we have

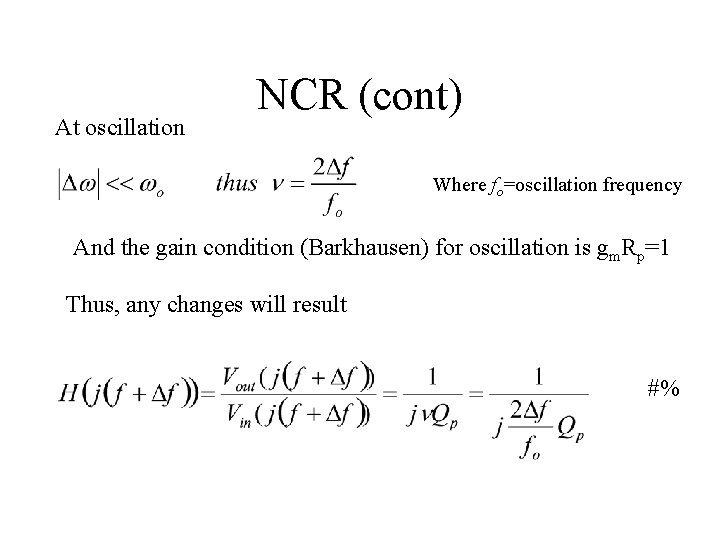

At oscillation NCR (cont) Where fo=oscillation frequency And the gain condition (Barkhausen) for oscillation is gm. Rp=1 Thus, any changes will result #%

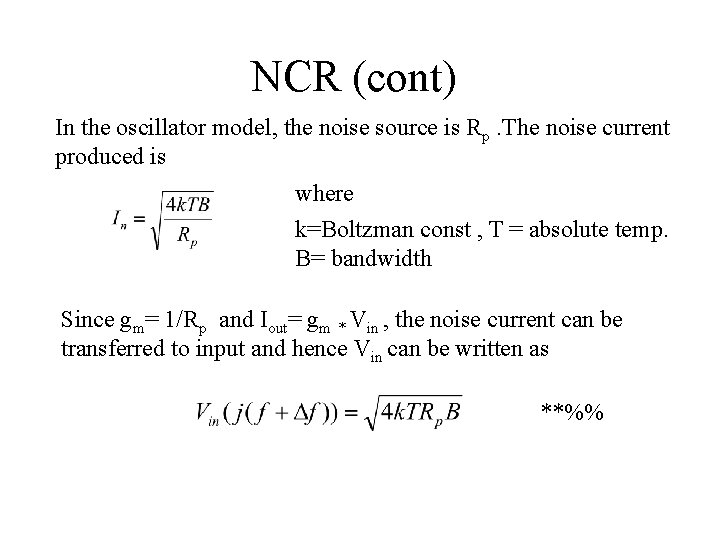

NCR (cont) In the oscillator model, the noise source is Rp. The noise current produced is where k=Boltzman const , T = absolute temp. B= bandwidth Since gm= 1/Rp and Iout= gm * Vin , the noise current can be transferred to input and hence Vin can be written as **%%

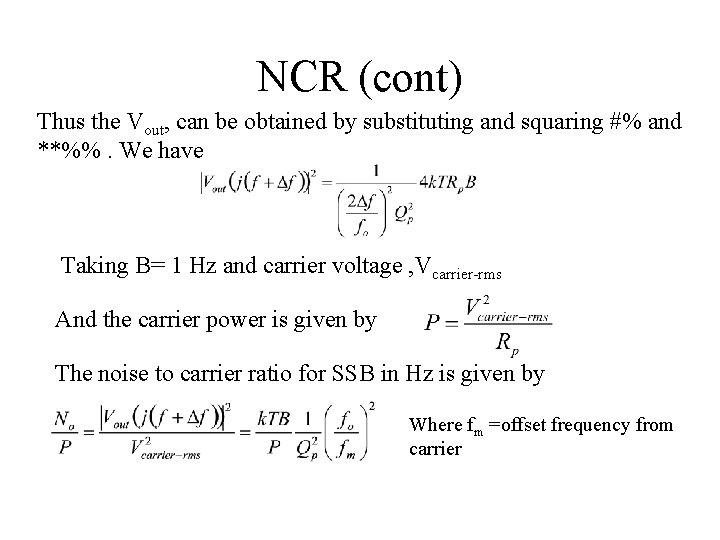

NCR (cont) Thus the Vout, can be obtained by substituting and squaring #% and **%%. We have Taking B= 1 Hz and carrier voltage , Vcarrier-rms And the carrier power is given by The noise to carrier ratio for SSB in Hz is given by Where fm =offset frequency from carrier

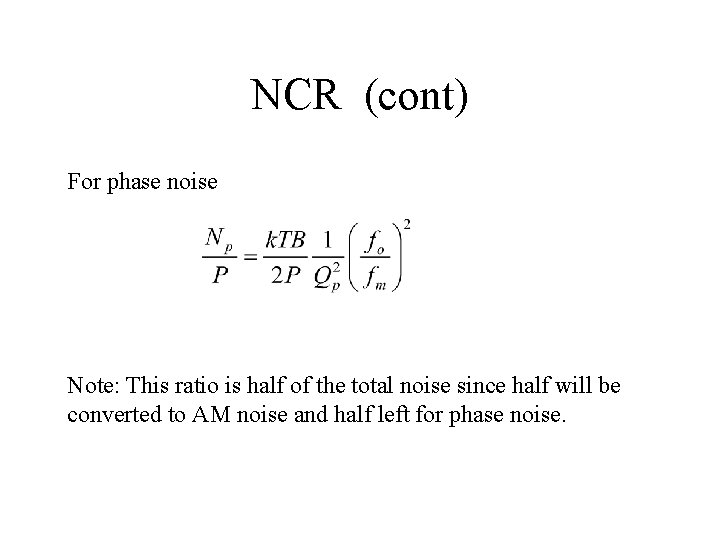

NCR (cont) For phase noise Note: This ratio is half of the total noise since half will be converted to AM noise and half left for phase noise.

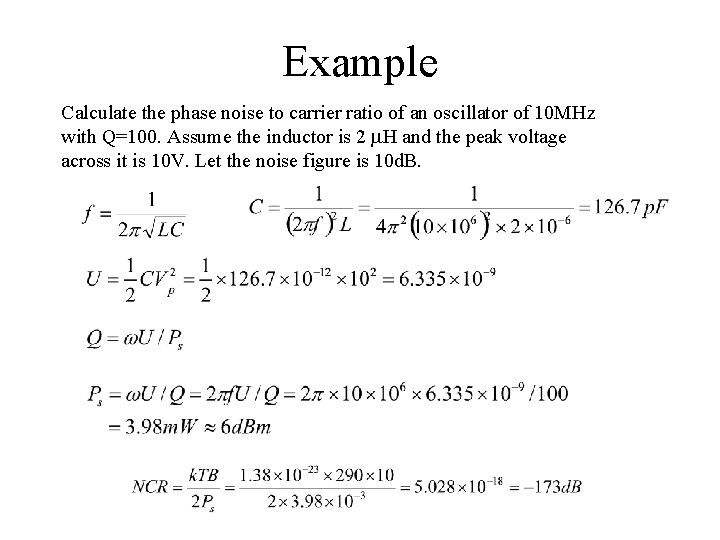

Example Calculate the phase noise to carrier ratio of an oscillator of 10 MHz with Q=100. Assume the inductor is 2 m. H and the peak voltage across it is 10 V. Let the noise figure is 10 d. B.

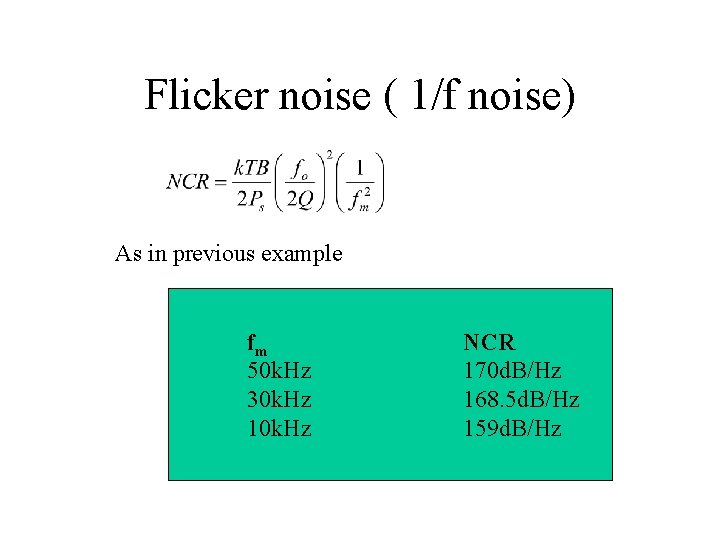

Flicker noise ( 1/f noise) As in previous example fm 50 k. Hz 30 k. Hz 10 k. Hz NCR 170 d. B/Hz 168. 5 d. B/Hz 159 d. B/Hz

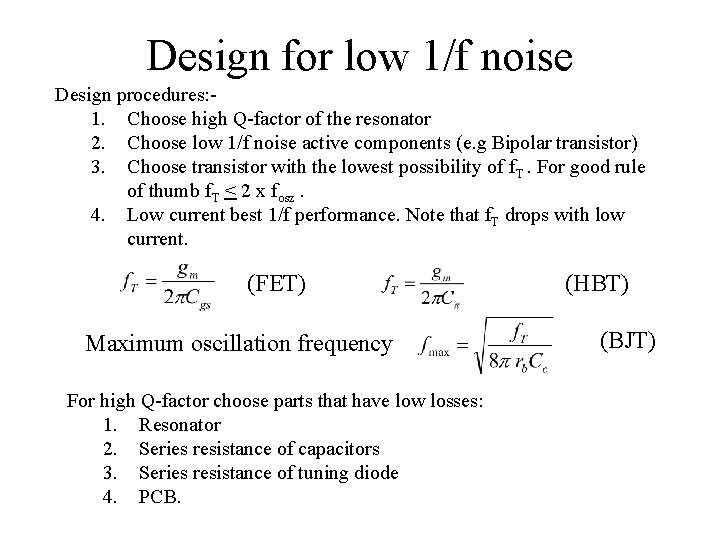

Design for low 1/f noise Design procedures: 1. Choose high Q-factor of the resonator 2. Choose low 1/f noise active components (e. g Bipolar transistor) 3. Choose transistor with the lowest possibility of f. T. For good rule of thumb f. T < 2 x fosz. 4. Low current best 1/f performance. Note that f. T drops with low current. (FET) Maximum oscillation frequency For high Q-factor choose parts that have low losses: 1. Resonator 2. Series resistance of capacitors 3. Series resistance of tuning diode 4. PCB. (HBT) (BJT)

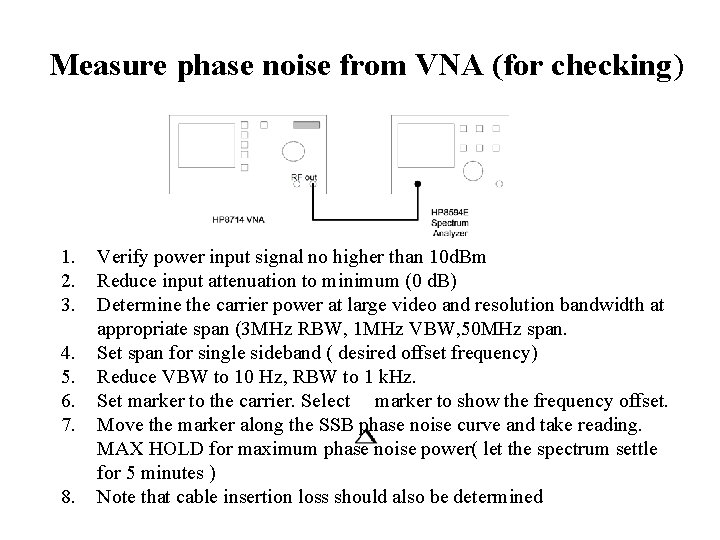

Measure phase noise from VNA (for checking) 1. 2. 3. 4. 5. 6. 7. 8. Verify power input signal no higher than 10 d. Bm Reduce input attenuation to minimum (0 d. B) Determine the carrier power at large video and resolution bandwidth at appropriate span (3 MHz RBW, 1 MHz VBW, 50 MHz span. Set span for single sideband ( desired offset frequency) Reduce VBW to 10 Hz, RBW to 1 k. Hz. Set marker to the carrier. Select marker to show the frequency offset. Move the marker along the SSB phase noise curve and take reading. MAX HOLD for maximum phase noise power( let the spectrum settle for 5 minutes ) Note that cable insertion loss should also be determined

Measure phase noise from VCO

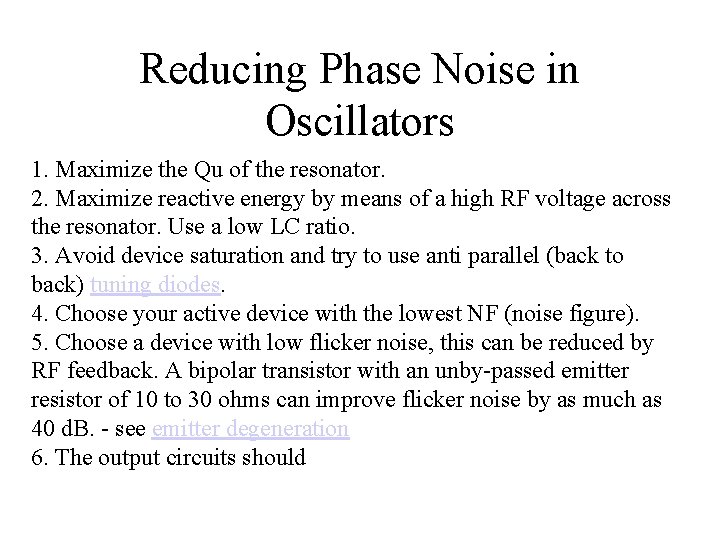

Reducing Phase Noise in Oscillators 1. Maximize the Qu of the resonator. 2. Maximize reactive energy by means of a high RF voltage across the resonator. Use a low LC ratio. 3. Avoid device saturation and try to use anti parallel (back to back) tuning diodes. 4. Choose your active device with the lowest NF (noise figure). 5. Choose a device with low flicker noise, this can be reduced by RF feedback. A bipolar transistor with an unby-passed emitter resistor of 10 to 30 ohms can improve flicker noise by as much as 40 d. B. - see emitter degeneration 6. The output circuits should

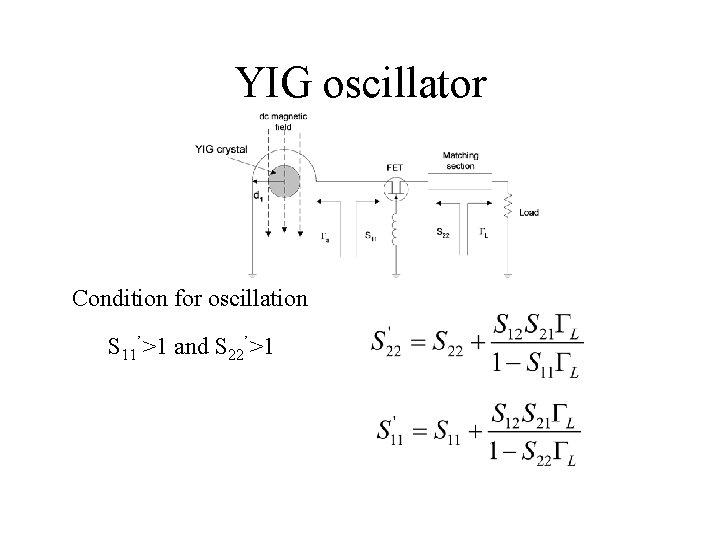

YIG oscillator Condition for oscillation S 11’>1 and S 22’>1

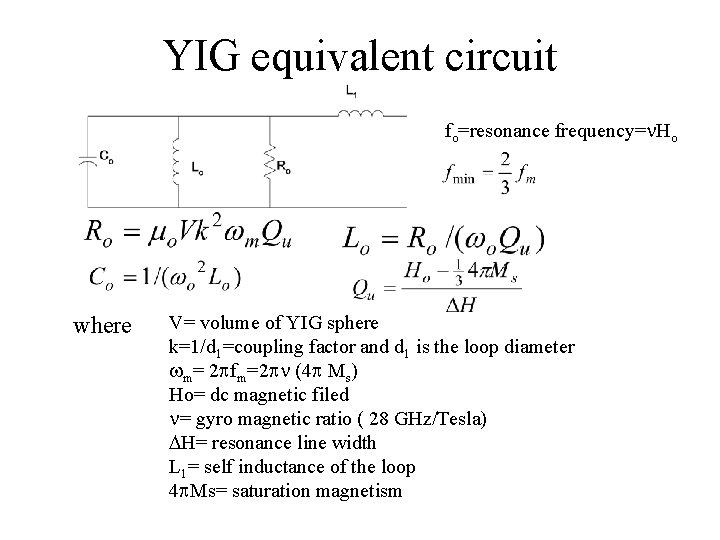

YIG equivalent circuit fo=resonance frequency=n. Ho where V= volume of YIG sphere k=1/d 1=coupling factor and d 1 is the loop diameter wm= 2 pfm=2 pn (4 p Ms) Ho= dc magnetic filed n= gyro magnetic ratio ( 28 GHz/Tesla) DH= resonance line width L 1= self inductance of the loop 4 p. Ms= saturation magnetism

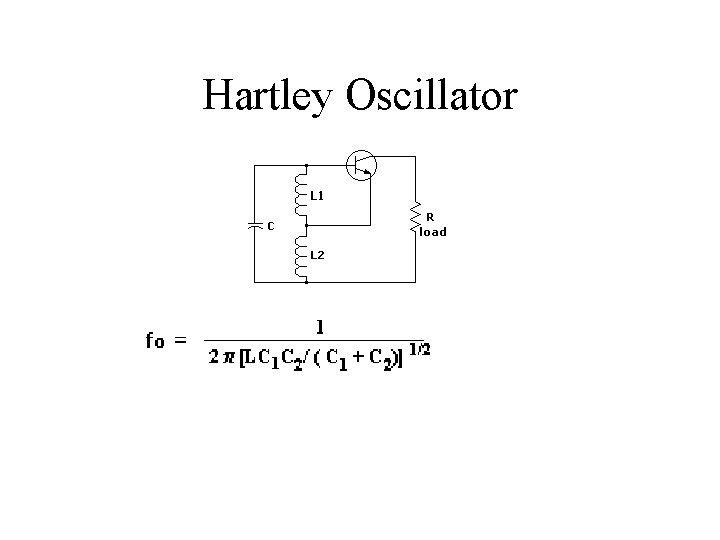

Hartley Oscillator

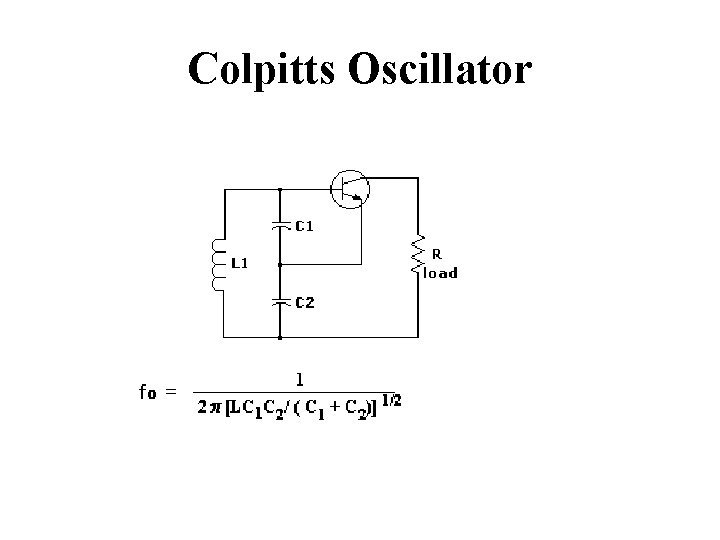

Colpitts Oscillator

Effects of ambient changes on stability in oscillators A frequency change of a few tens of hertz back and forth over a couple of minutes would mean nothing to an entertainment receiver designed for the FM Radio band. Such a drift in an otherwise contest grade receiver designed to receive CW (morse code) would be intolerable. It's a question of relativity.

- Slides: 38