Microwave Devices Microwave Semiconductor Devices 4 2008 1

![Microwave FETs [ Device Structures ] l l l MESFET ; Schottky-FET Heterostructure FET Microwave FETs [ Device Structures ] l l l MESFET ; Schottky-FET Heterostructure FET](https://slidetodoc.com/presentation_image_h2/febed4e0cb68e1234abf26a9db49b51e/image-7.jpg)

- Slides: 34

Microwave Devices - Microwave Semiconductor Devices - 4 2008 / 1 학기 서광석 • S. N. U. EE Microwave Devices 2008

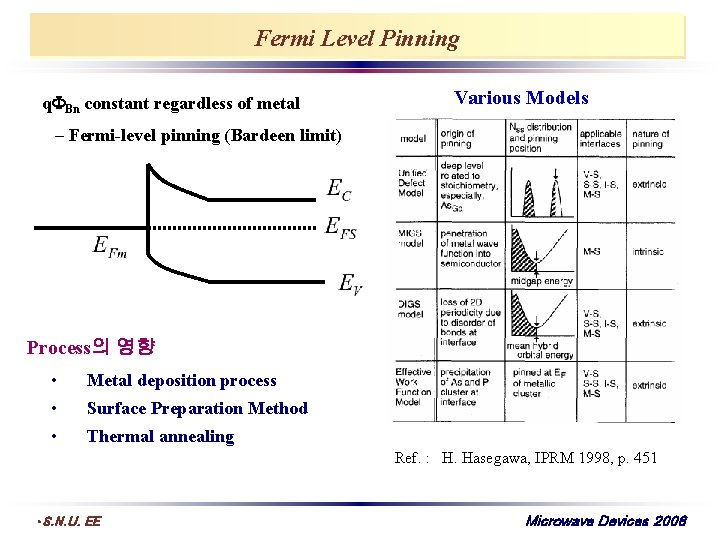

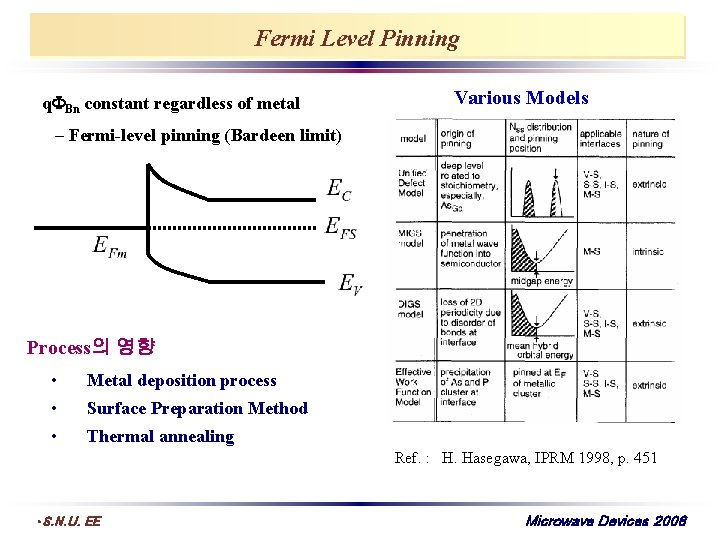

Fermi Level Pinning q Bn constant regardless of metal Various Models – Fermi-level pinning (Bardeen limit) Process의 영향 • Metal deposition process • Surface Preparation Method • Thermal annealing Ref. : H. Hasegawa, IPRM 1998, p. 451 • S. N. U. EE Microwave Devices 2008

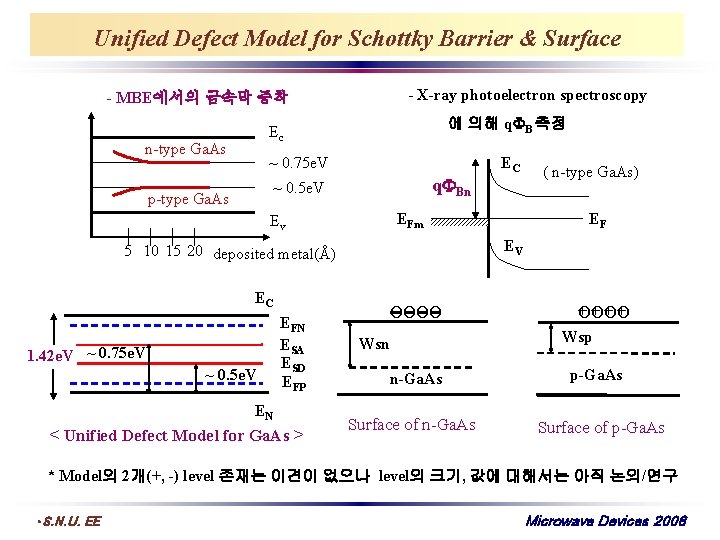

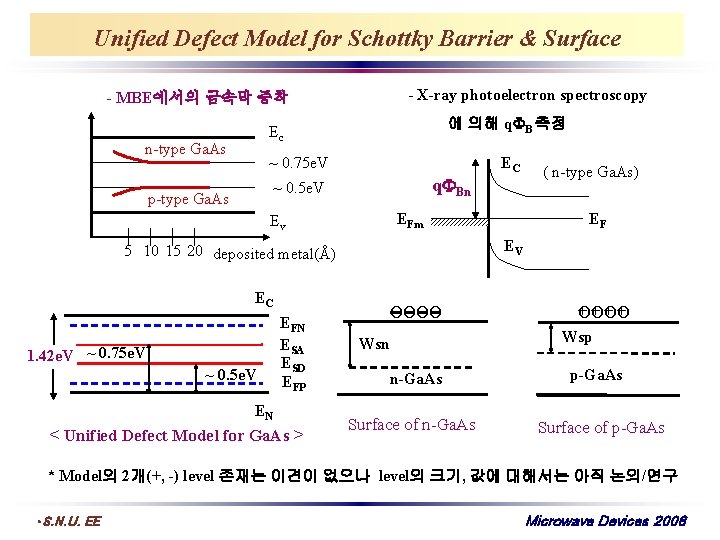

Unified Defect Model for Schottky Barrier & Surface - X-ray photoelectron spectroscopy - MBE에서의 금속막 증착 에 의해 q B 측정 Ec n-type Ga. As EC ~ 0. 75 e. V q Bn ~ 0. 5 e. V p-type Ga. As EFm Ev 1. 42 e. V ~ 0. 75 e. V ~ 0. 5 e. V EFN ESA ESD EFP EN < Unified Defect Model for Ga. As > EF EV 5 10 15 20 deposited metal(Å) EC ( n-type Ga. As) OOOO ---Wsn n-Ga. As Surface of n-Ga. As ++++ OOOO Wsp p-Ga. As Surface of p-Ga. As * Model의 2개(+, -) level 존재는 이견이 없으나 level의 크기, 값에 대해서는 아직 논의/연구 • S. N. U. EE Microwave Devices 2008

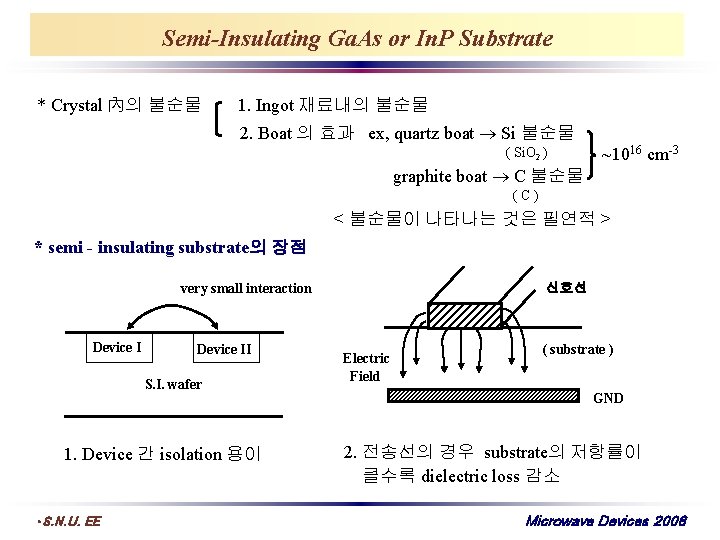

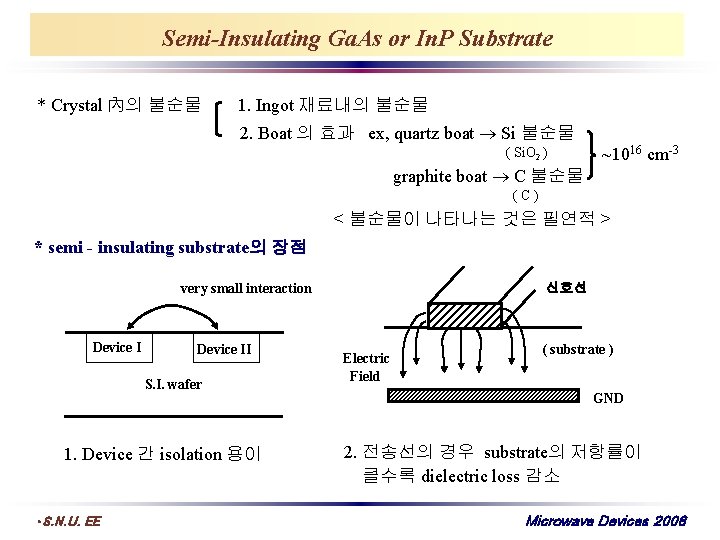

Semi-Insulating Ga. As or In. P Substrate * Crystal 內의 불순물 1. Ingot 재료내의 불순물 2. Boat 의 효과 ex, quartz boat Si 불순물 ( Si. O 2 ) ~1016 cm-3 graphite boat C 불순물 (C) < 불순물이 나타나는 것은 필연적 > * semi - insulating substrate의 장점 신호선 very small interaction Device II S. I. wafer 1. Device 간 isolation 용이 • S. N. U. EE Electric Field ( substrate ) GND 2. 전송선의 경우 substrate의 저항률이 클수록 dielectric loss 감소 Microwave Devices 2008

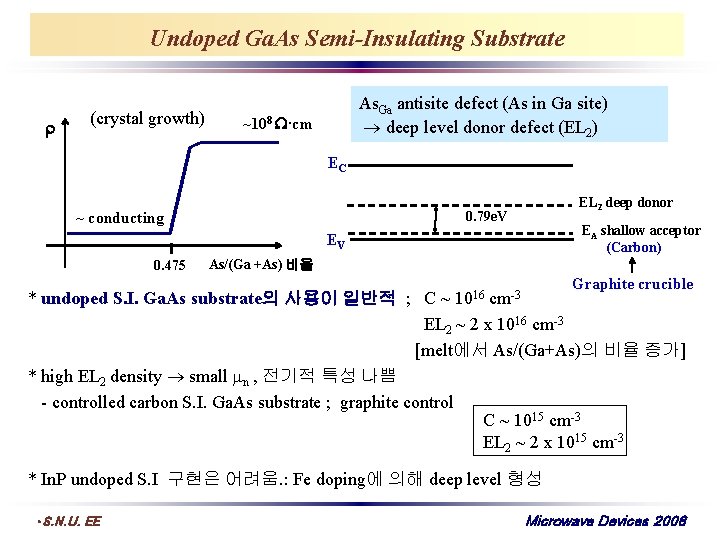

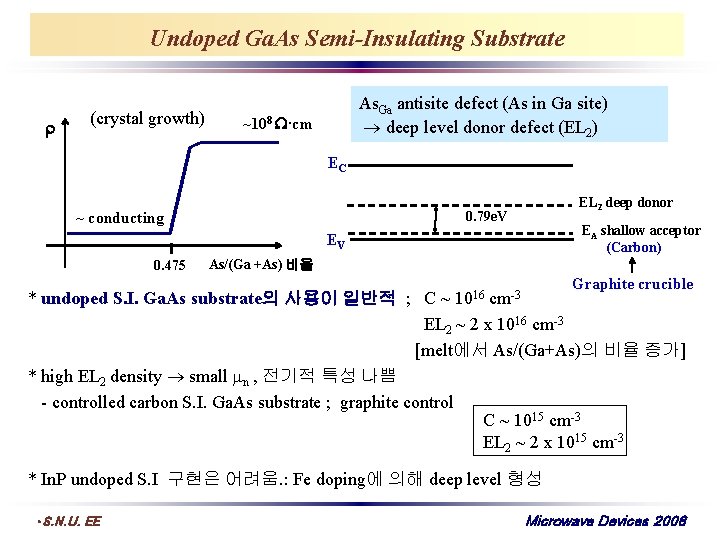

Undoped Ga. As Semi-Insulating Substrate (crystal growth) As. Ga antisite defect (As in Ga site) deep level donor defect (EL 2) ~108 ·cm EC ~ conducting EL 2 deep donor 0. 79 e. V EA shallow acceptor (Carbon) EV 0. 475 As/(Ga +As) 비율 1016 Graphite crucible cm-3 * undoped S. I. Ga. As substrate의 사용이 일반적 ; C ~ EL 2 ~ 2 x 1016 cm-3 [melt에서 As/(Ga+As)의 비율 증가] * high EL 2 density small n , 전기적 특성 나쁨 - controlled carbon S. I. Ga. As substrate ; graphite control C ~ 1015 cm-3 EL 2 ~ 2 x 1015 cm-3 * In. P undoped S. I 구현은 어려움. : Fe doping에 의해 deep level 형성 • S. N. U. EE Microwave Devices 2008

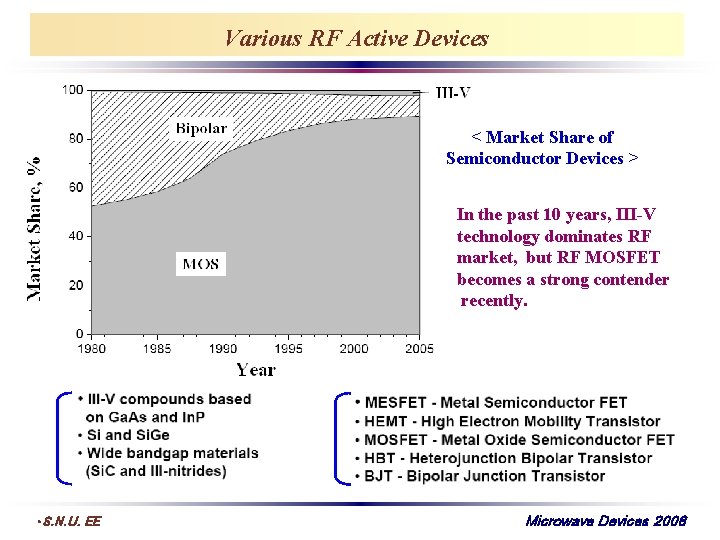

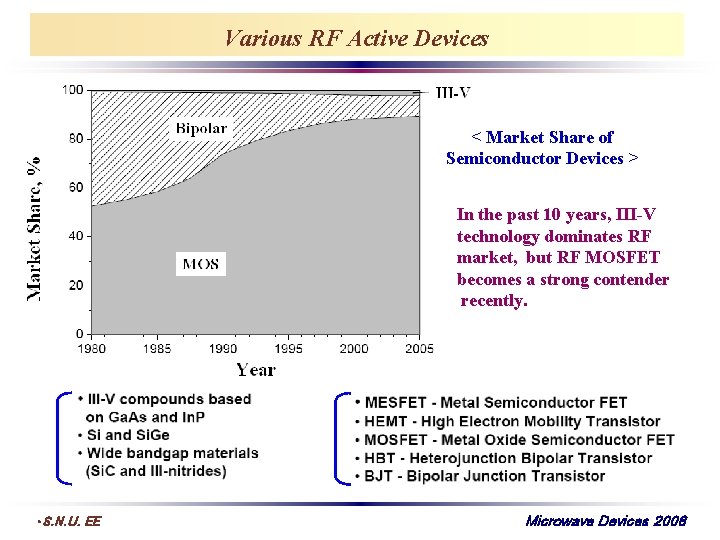

Various RF Active Devices < Market Share of Semiconductor Devices > In the past 10 years, III-V technology dominates RF market, but RF MOSFET becomes a strong contender recently. • S. N. U. EE Microwave Devices 2008

![Microwave FETs Device Structures l l l MESFET SchottkyFET Heterostructure FET Microwave FETs [ Device Structures ] l l l MESFET ; Schottky-FET Heterostructure FET](https://slidetodoc.com/presentation_image_h2/febed4e0cb68e1234abf26a9db49b51e/image-7.jpg)

Microwave FETs [ Device Structures ] l l l MESFET ; Schottky-FET Heterostructure FET (HFET) n Doped Channel HFET n High Electron Mobility Transistor (HEMT) Modulation Doped FET (MODFET) MOSFET or MISFET [ Material Related Classification ] l l l Ga. As MESFET In. Ga. As/Al. Ga. As HFET In. Ga. As/In. Al. As HFET Si MOSFET/Si. Ge HFET, Si LDMOS In. P MISFET, Ga. N/Al. Ga. N HMISFET • S. N. U. EE Microwave Devices 2008

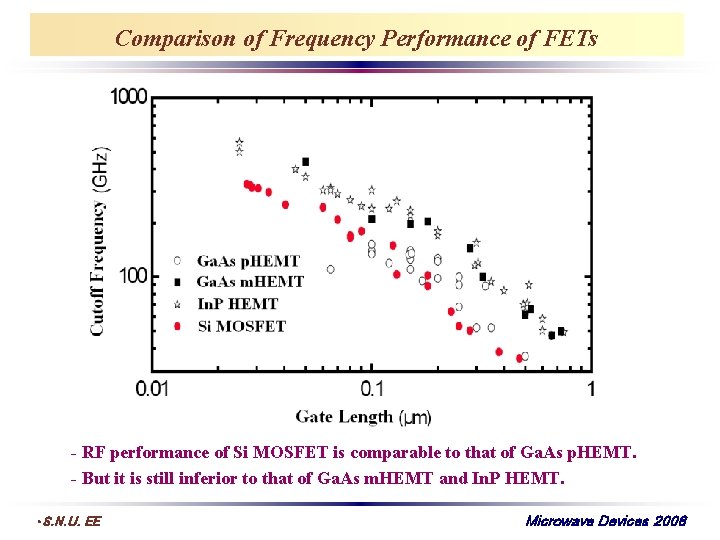

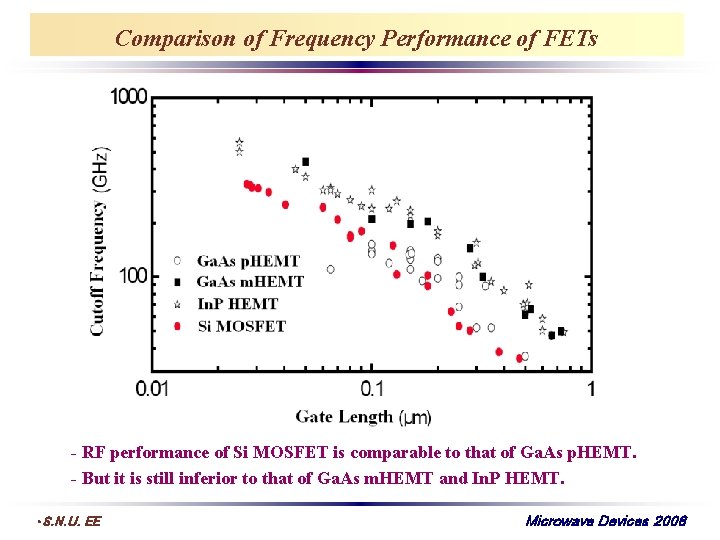

Comparison of Frequency Performance of FETs - RF performance of Si MOSFET is comparable to that of Ga. As p. HEMT. - But it is still inferior to that of Ga. As m. HEMT and In. P HEMT. • S. N. U. EE Microwave Devices 2008

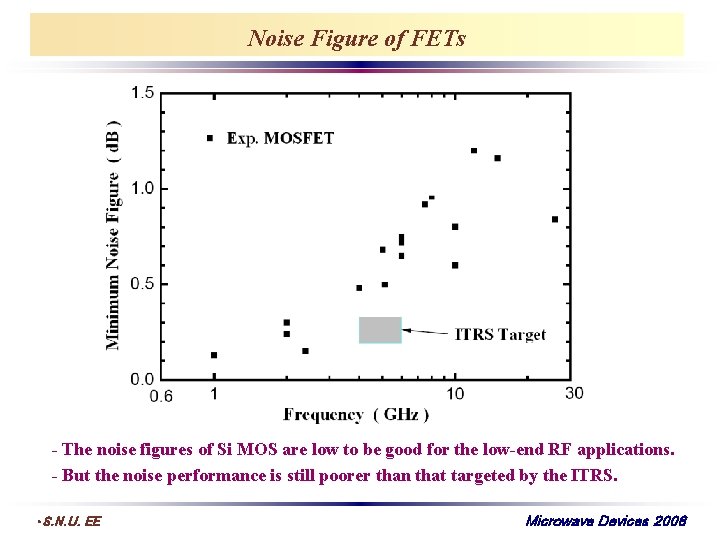

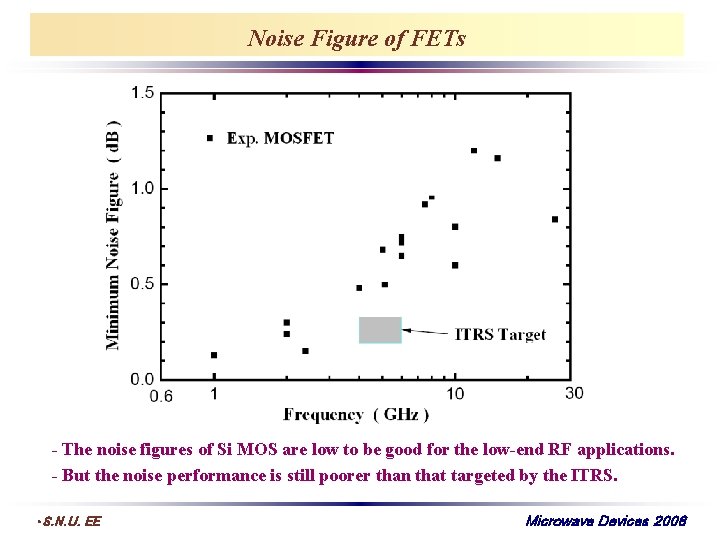

Noise Figure of FETs - The noise figures of Si MOS are low to be good for the low-end RF applications. - But the noise performance is still poorer than that targeted by the ITRS. • S. N. U. EE Microwave Devices 2008

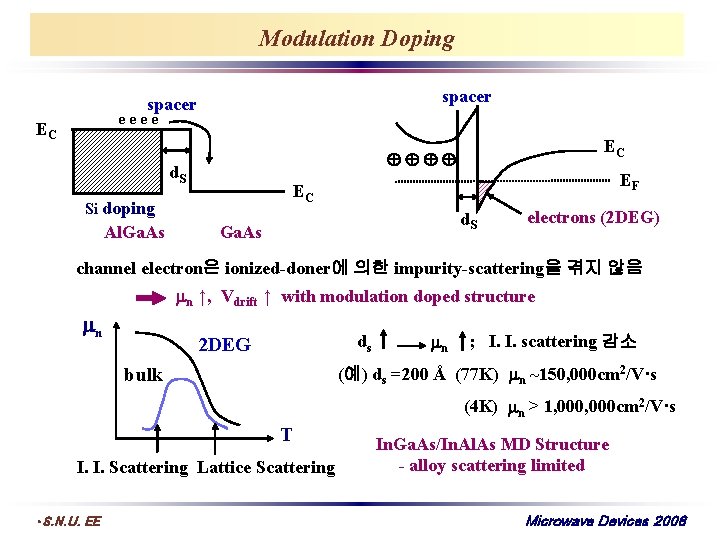

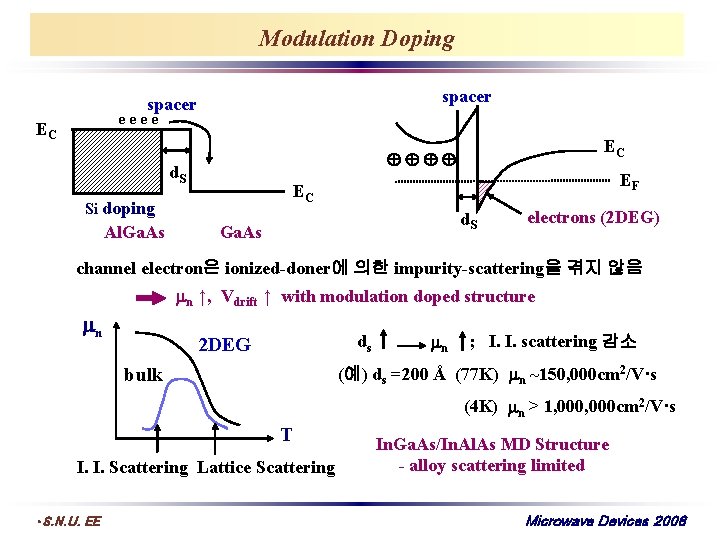

Modulation Doping spacer eeee EC d. S EF EC Si doping Al. Ga. As EC d. S Ga. As electrons (2 DEG) channel electron은 ionized-doner에 의한 impurity-scattering을 겪지 않음 n ↑, Vdrift ↑ with modulation doped structure n ds 2 DEG n ; I. I. scattering 감소 (예) ds =200 Å (77 K) n ~150, 000 cm 2/V·s bulk (4 K) n > 1, 000 cm 2/V·s T I. I. Scattering Lattice Scattering • S. N. U. EE In. Ga. As/In. Al. As MD Structure - alloy scattering limited Microwave Devices 2008

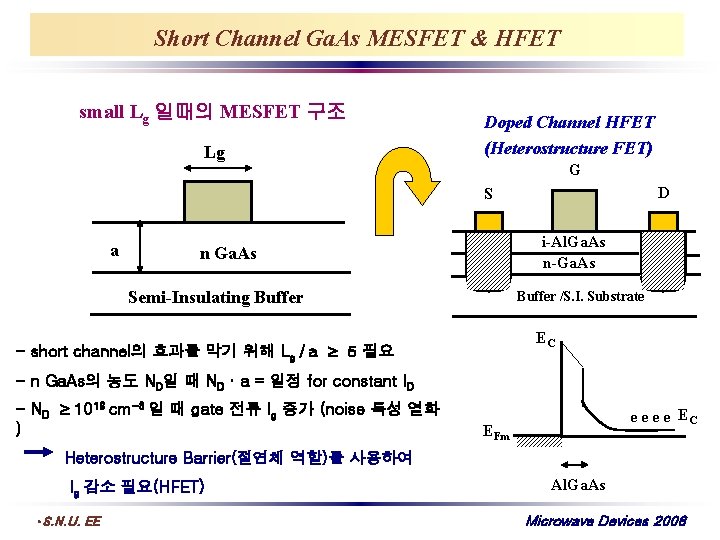

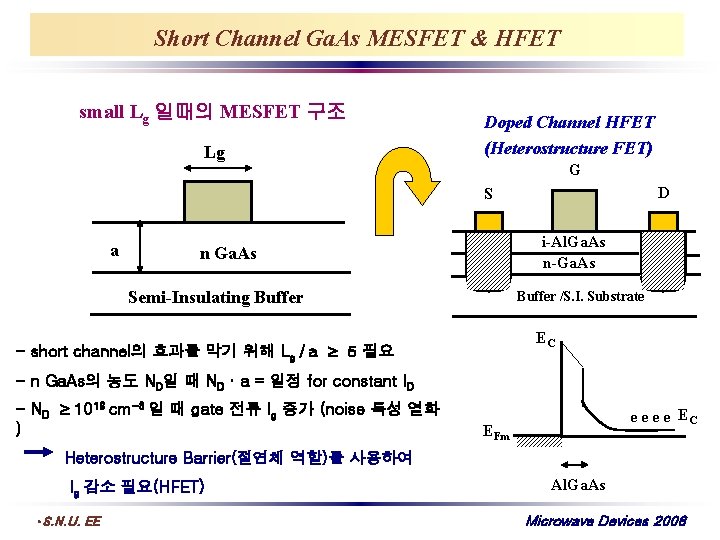

Short Channel Ga. As MESFET & HFET small Lg 일때의 MESFET 구조 Lg Doped Channel HFET (Heterostructure FET) G D S a i-Al. Ga. As n-Ga. As n Ga. As Semi-Insulating Buffer /S. I. Substrate EC - short channel의 효과를 막기 위해 Lg / a 5 필요 - n Ga. As의 농도 ND일 때 ND · a = 일정 for constant ID - ND 1018 cm-3 일 때 gate 전류 Ig 증가 (noise 특성 열화 ) e e EC EFm Heterostructure Barrier(절연체 역할)를 사용하여 Ig 감소 필요(HFET) • S. N. U. EE Al. Ga. As Microwave Devices 2008

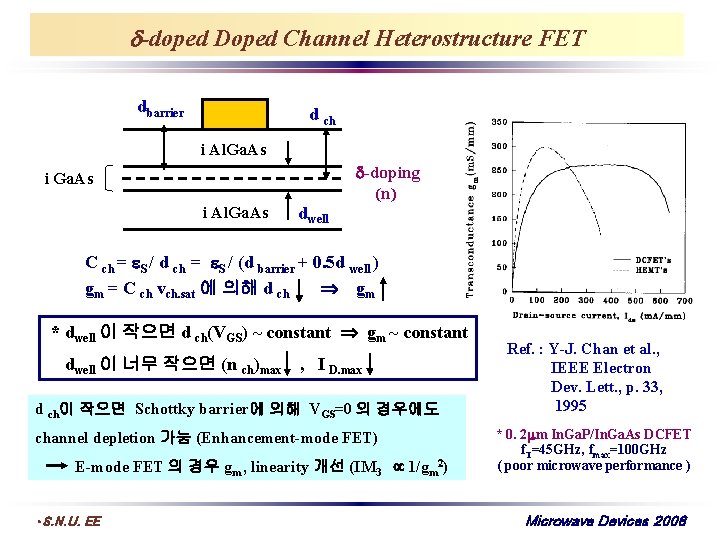

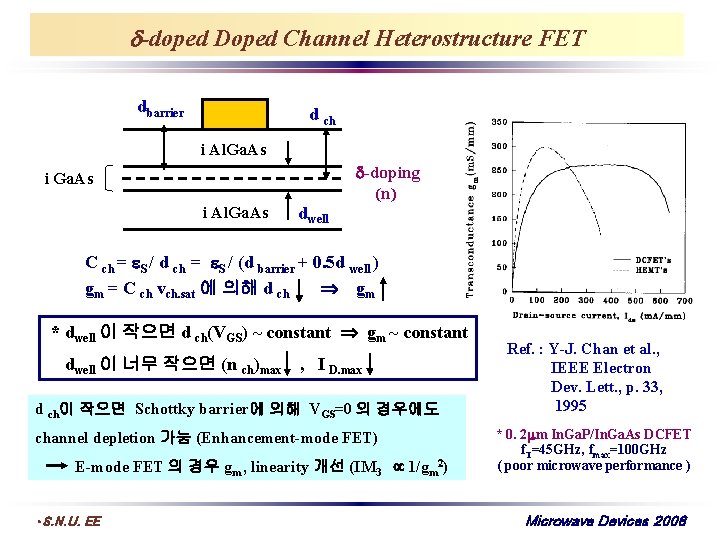

-doped Doped Channel Heterostructure FET dbarrier d ch i Al. Ga. As -doping (n) i Ga. As i Al. Ga. As dwell C ch = S / d ch = S / (d barrier + 0. 5 d well ) gm = C ch vch. sat 에 의해 d ch gm * dwell 이 작으면 d ch(VGS) ~ constant gm ~ constant dwell 이 너무 작으면 (n ch)max , I D. max d ch이 작으면 Schottky barrier에 의해 VGS=0 의 경우에도 channel depletion 가능 (Enhancement-mode FET) E-mode FET 의 경우 gm , linearity 개선 (IM 3 1/gm 2) • S. N. U. EE Ref. : Y-J. Chan et al. , IEEE Electron Dev. Lett. , p. 33, 1995 * 0. 2 m In. Ga. P/In. Ga. As DCFET f. T=45 GHz, fmax=100 GHz ( poor microwave performance ) Microwave Devices 2008

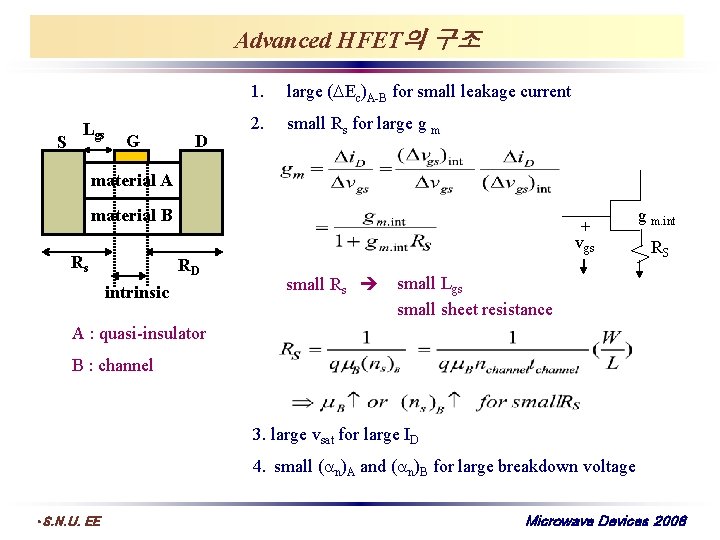

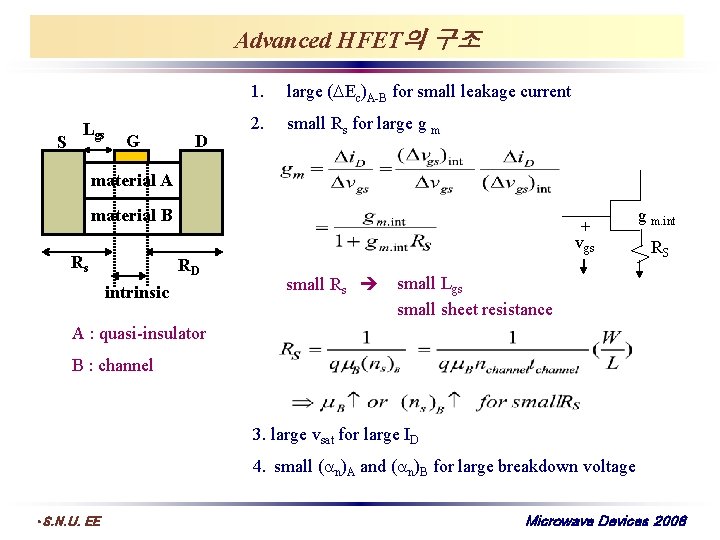

Advanced HFET의 구조 S Lgs G D 1. large ( Ec)A-B for small leakage current 2. small Rs for large g m material A material B Rs RD intrinsic + vgs small Rs g m. int RS small Lgs small sheet resistance A : quasi-insulator B : channel 3. large vsat for large ID 4. small ( n)A and ( n)B for large breakdown voltage • S. N. U. EE Microwave Devices 2008

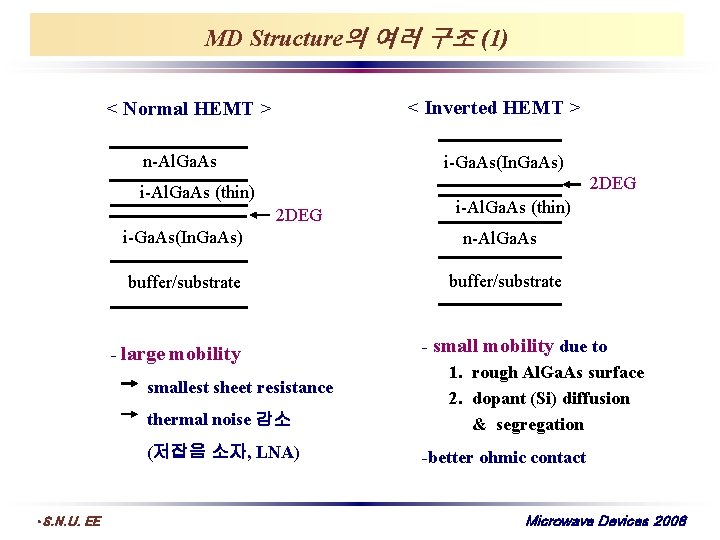

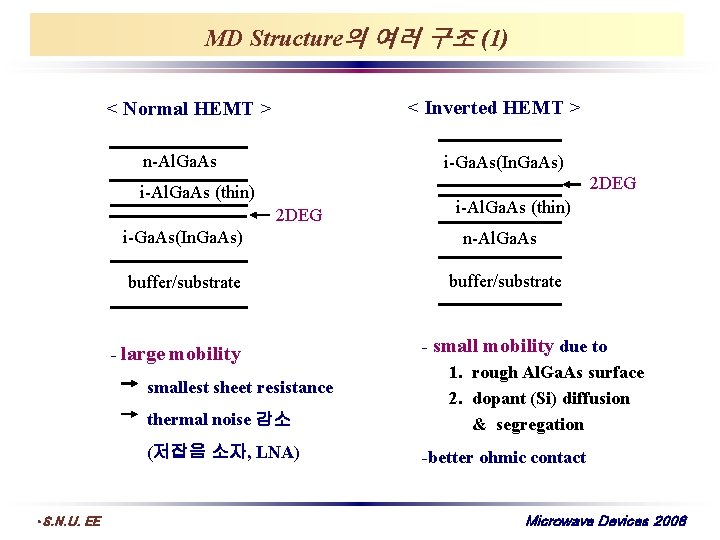

MD Structure의 여러 구조 (1) < Inverted HEMT > < Normal HEMT > n-Al. Ga. As i-Ga. As(In. Ga. As) 2 DEG i-Al. Ga. As (thin) 2 DEG i-Ga. As(In. Ga. As) buffer/substrate n-Al. Ga. As buffer/substrate thermal noise 감소 - small mobility due to 1. rough Al. Ga. As surface 2. dopant (Si) diffusion & segregation (저잡음 소자, LNA) -better ohmic contact - large mobility smallest sheet resistance • S. N. U. EE i-Al. Ga. As (thin) Microwave Devices 2008

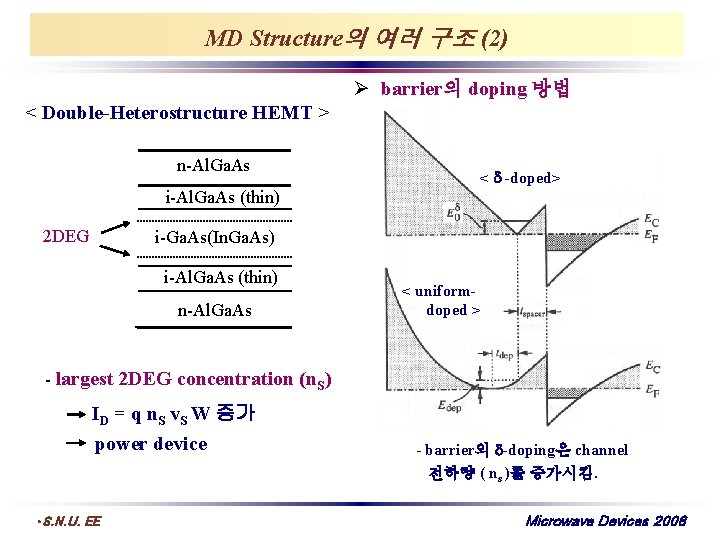

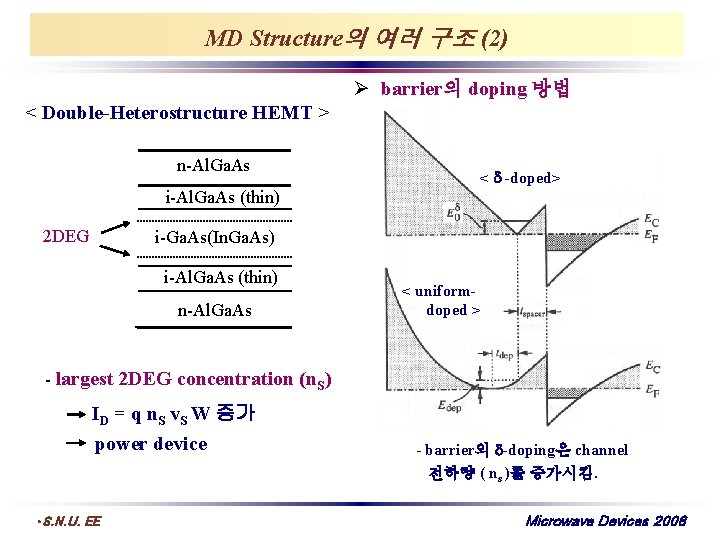

MD Structure의 여러 구조 (2) Ø barrier의 doping 방법 < Double-Heterostructure HEMT > n-Al. Ga. As < -doped> i-Al. Ga. As (thin) 2 DEG i-Ga. As(In. Ga. As) i-Al. Ga. As (thin) n-Al. Ga. As < uniformdoped > - largest 2 DEG concentration (n. S) ID = q n. S v. S W 증가 power device • S. N. U. EE - barrier의 -doping은 channel 전하량 ( ns )를 증가시킴. Microwave Devices 2008

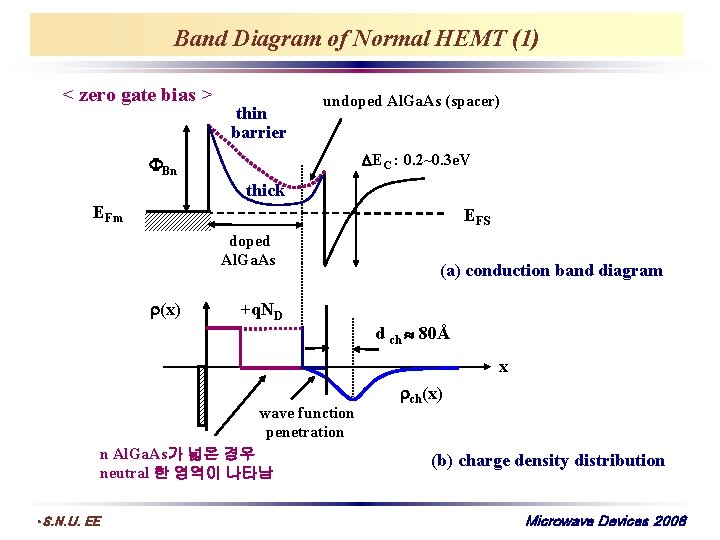

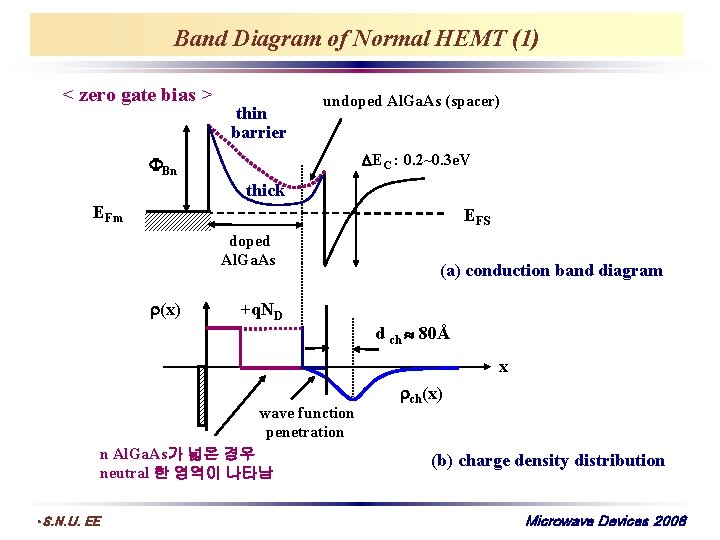

Band Diagram of Normal HEMT (1) < zero gate bias > thin barrier undoped Al. Ga. As (spacer) EC : 0. 2~0. 3 e. V Bn thick EFm EFS doped Al. Ga. As (x) +q. ND (a) conduction band diagram d ch 80Å x wave function penetration n Al. Ga. As가 넓은 경우 neutral 한 영역이 나타남 • S. N. U. EE ch(x) (b) charge density distribution Microwave Devices 2008

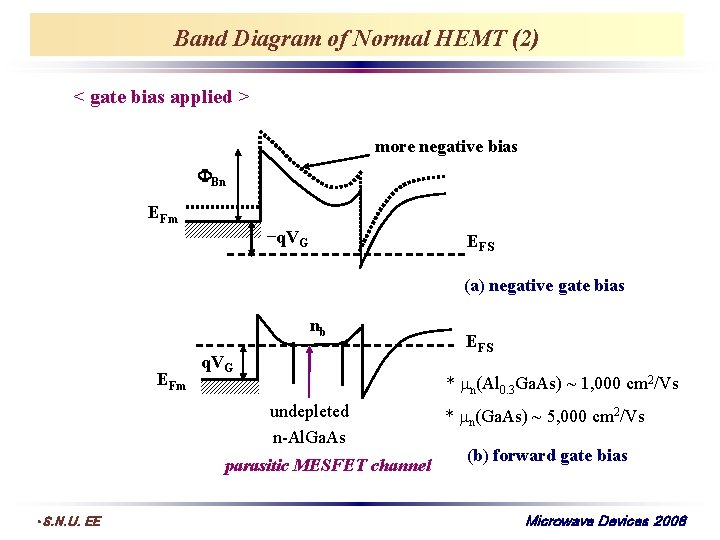

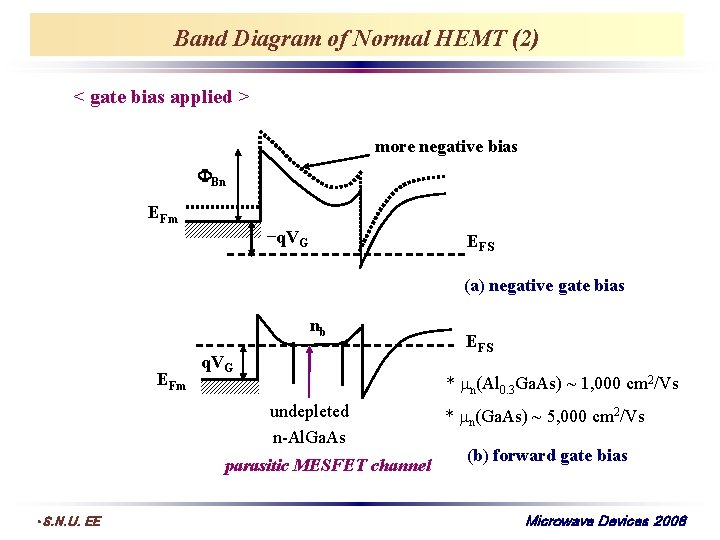

Band Diagram of Normal HEMT (2) < gate bias applied > more negative bias Bn EFm –q. VG EFS (a) negative gate bias nb EFm q. VG * n(Al 0. 3 Ga. As) ~ 1, 000 cm 2/Vs undepleted n-Al. Ga. As parasitic MESFET channel • S. N. U. EE EFS * n(Ga. As) ~ 5, 000 cm 2/Vs (b) forward gate bias Microwave Devices 2008

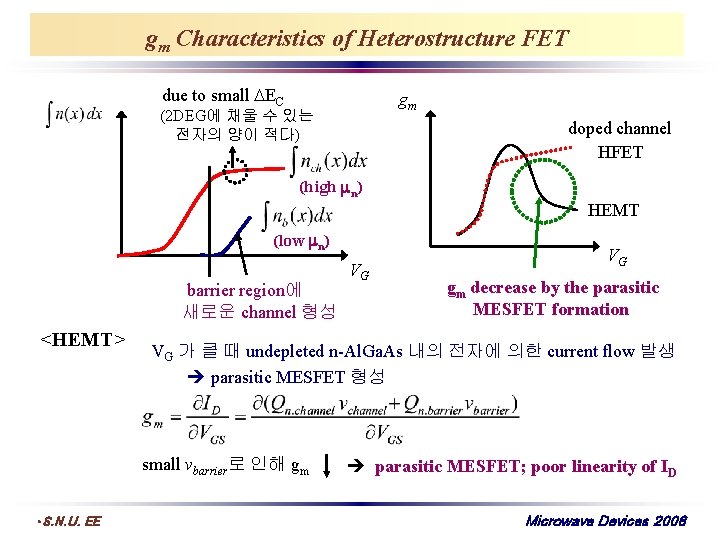

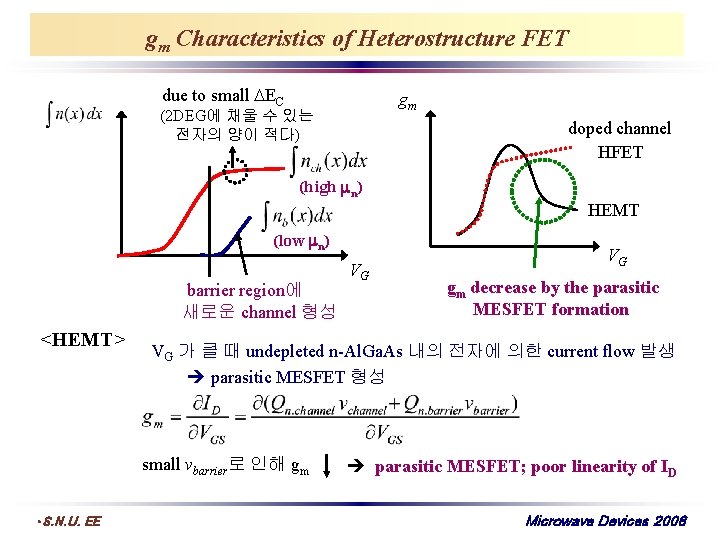

gm Characteristics of Heterostructure FET due to small EC gm (2 DEG에 채울 수 있는 전자의 양이 적다) doped channel HFET (high n) HEMT (low n) barrier region에 새로운 channel 형성 <HEMT> VG gm decrease by the parasitic MESFET formation VG 가 클 때 undepleted n-Al. Ga. As 내의 전자에 의한 current flow 발생 parasitic MESFET 형성 small vbarrier로 인해 gm • S. N. U. EE VG parasitic MESFET; poor linearity of ID Microwave Devices 2008

Charge-Voltage Characteristics of HEMT Structure (1) - Ga. As/Al. Ga. As interface의 Al. Ga. As 쪽에서의 전기장 Fi 2 - Poisson equation in the barrier By solving Poisson equation, From the band diagram, , where • S. N. U. EE Microwave Devices 2008

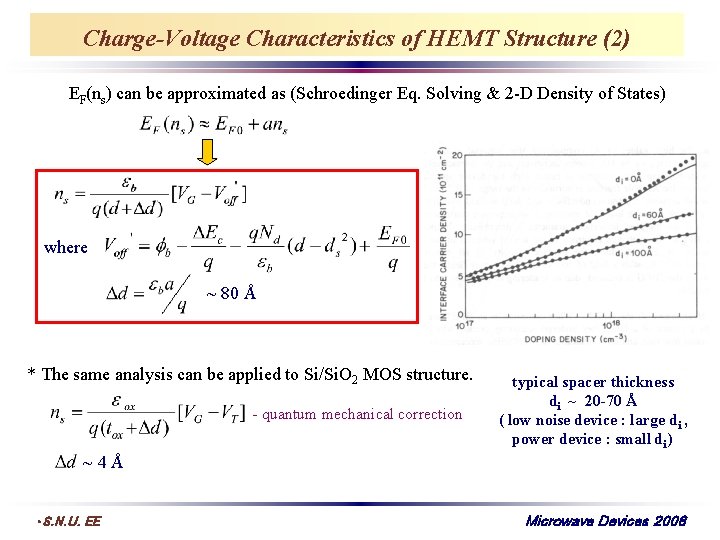

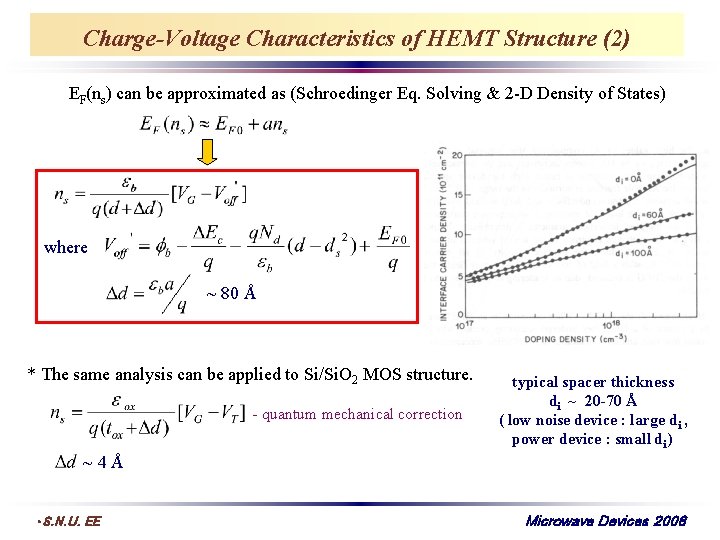

Charge-Voltage Characteristics of HEMT Structure (2) EF(ns) can be approximated as (Schroedinger Eq. Solving & 2 -D Density of States) where ~ 80 Å * The same analysis can be applied to Si/Si. O 2 MOS structure. - quantum mechanical correction typical spacer thickness di ~ 20 -70 Å ( low noise device : large di , power device : small di ) ~4Å • S. N. U. EE Microwave Devices 2008

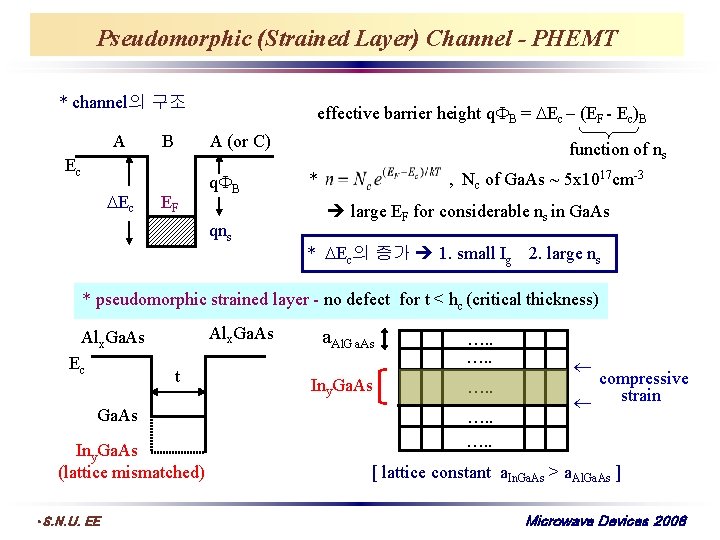

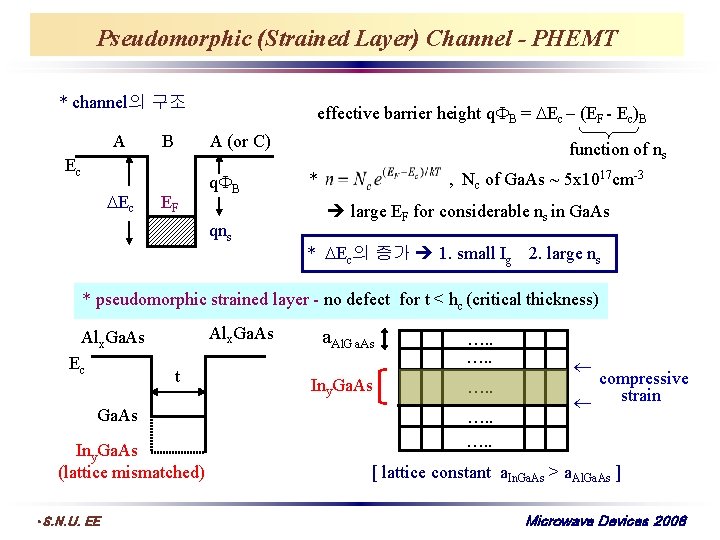

Pseudomorphic (Strained Layer) Channel - PHEMT * channel의 구조 A B A (or C) Ec Ec effective barrier height q B = Ec – (EF - Ec)B EF q B qns function of ns * , Nc of Ga. As ~ 5 x 1017 cm-3 large EF for considerable ns in Ga. As * Ec의 증가 1. small Ig 2. large ns * pseudomorphic strained layer - no defect for t < hc (critical thickness) Alx. Ga. As Ec t Ga. As Iny. Ga. As (lattice mismatched) • S. N. U. EE a. Al. Ga. As Iny. Ga. As …. . compressive strain [ lattice constant a. In. Ga. As > a. Al. Ga. As ] Microwave Devices 2008

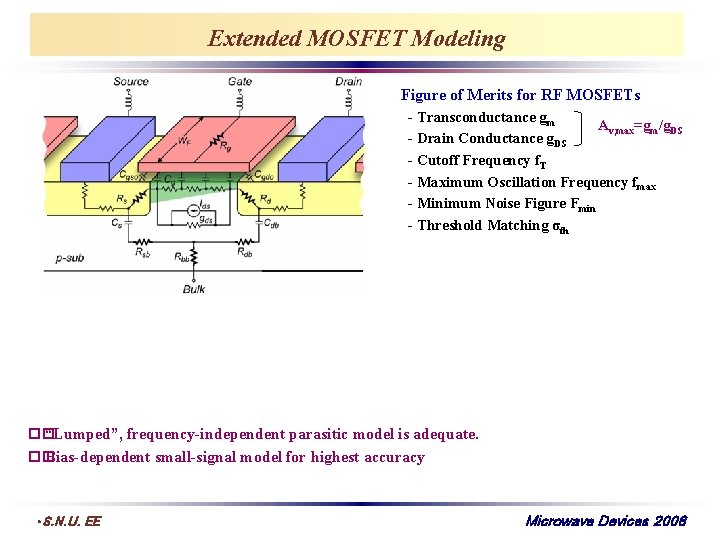

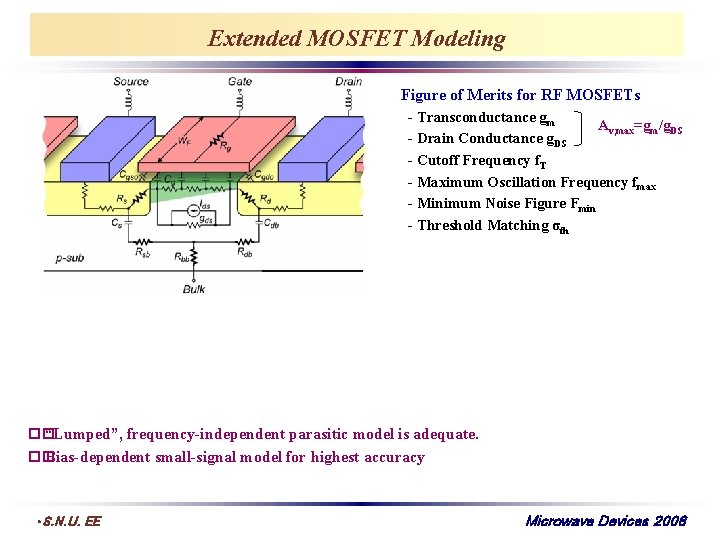

Extended MOSFET Modeling Figure of Merits for RF MOSFETs - Transconductance gm Av, max=gm/g. DS - Drain Conductance g. DS - Cutoff Frequency f. T - Maximum Oscillation Frequency fmax - Minimum Noise Figure Fmin - Threshold Matching σth �� “Lumped”, frequency-independent parasitic model is adequate. �� Bias-dependent small-signal model for highest accuracy • S. N. U. EE Microwave Devices 2008

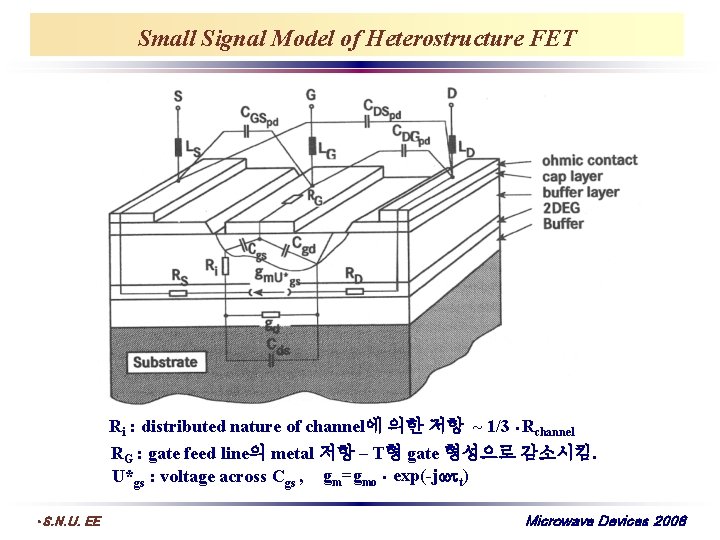

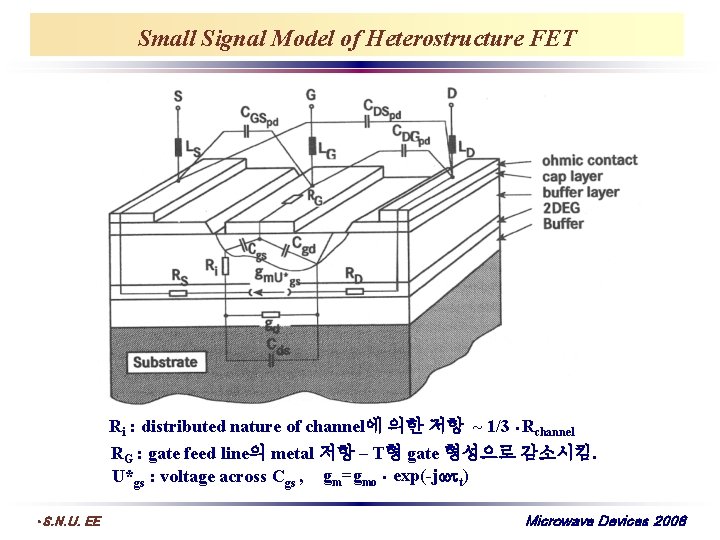

Small Signal Model of Heterostructure FET Ri : distributed nature of channel에 의한 저항 ~ 1/3 • Rchannel RG : gate feed line의 metal 저항 – T형 gate 형성으로 감소시킴. U*gs : voltage across Cgs , gm=gmo • exp(-j t) • S. N. U. EE Microwave Devices 2008

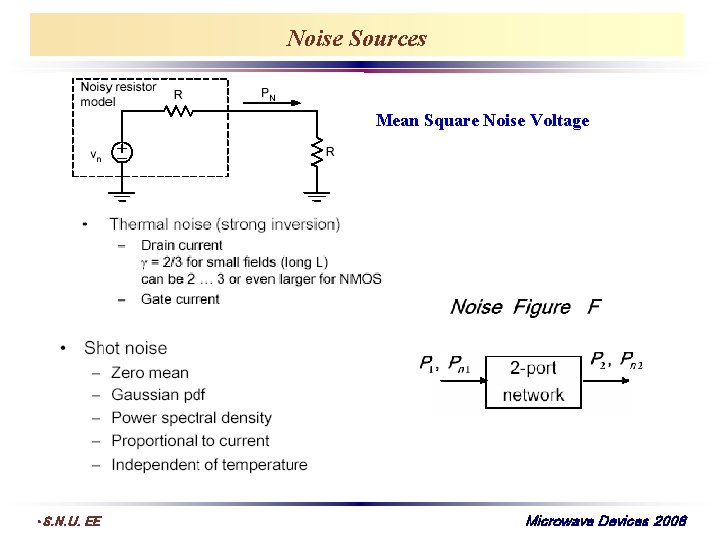

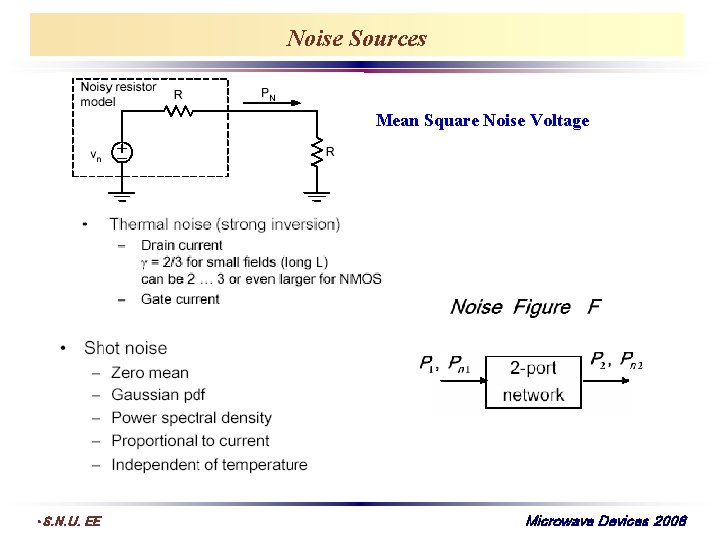

Noise Sources Mean Square Noise Voltage • S. N. U. EE Microwave Devices 2008

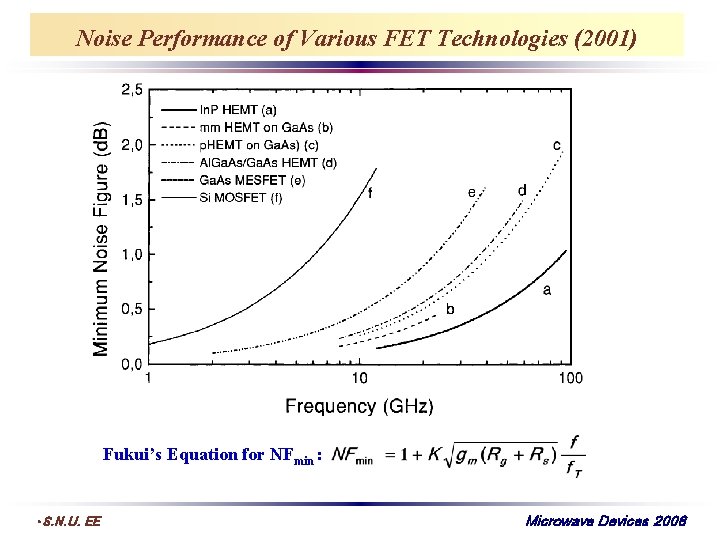

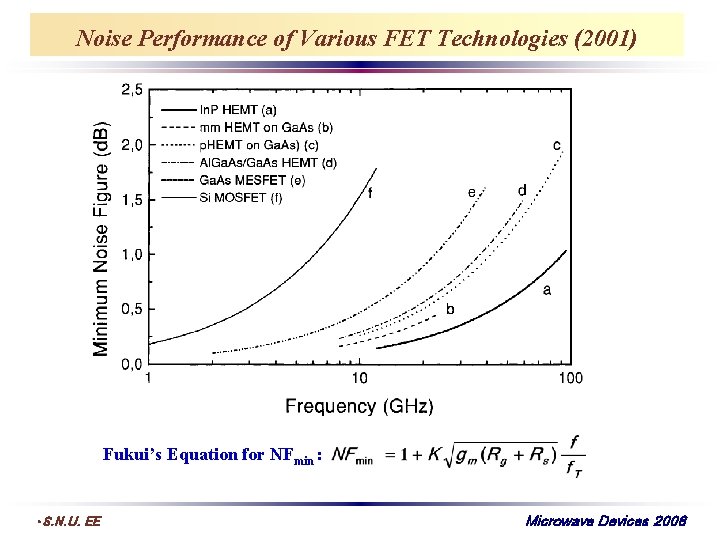

Noise Performance of Various FET Technologies (2001) Fukui’s Equation for NFmin : • S. N. U. EE Microwave Devices 2008

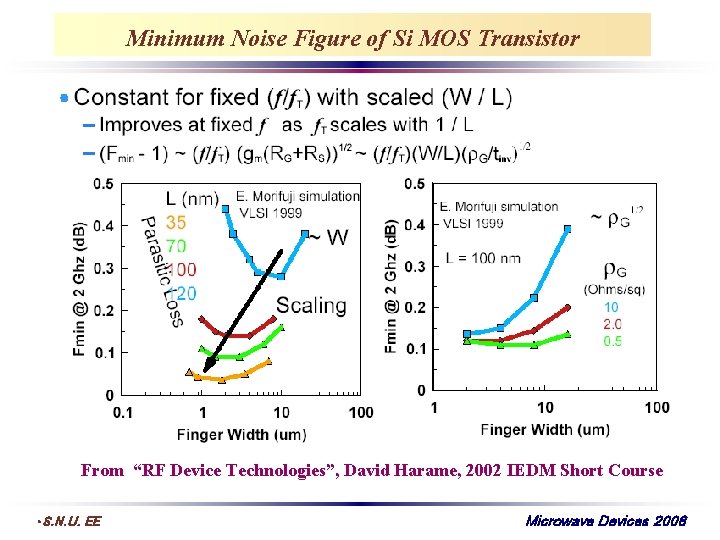

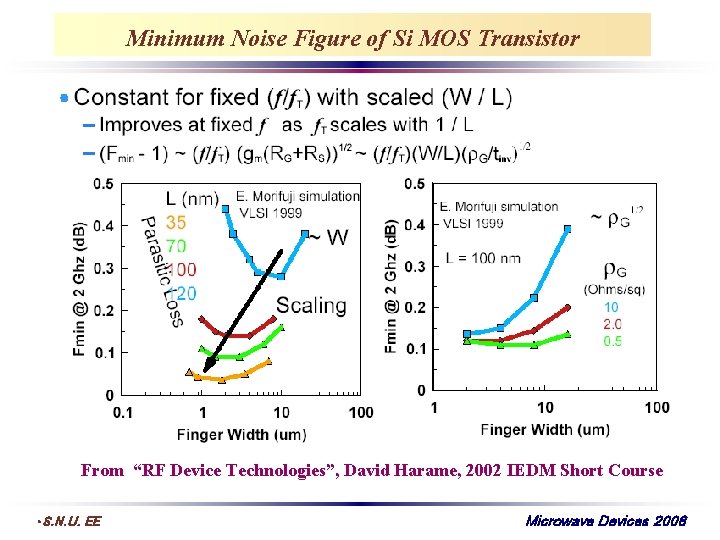

Minimum Noise Figure of Si MOS Transistor From “RF Device Technologies”, David Harame, 2002 IEDM Short Course • S. N. U. EE Microwave Devices 2008

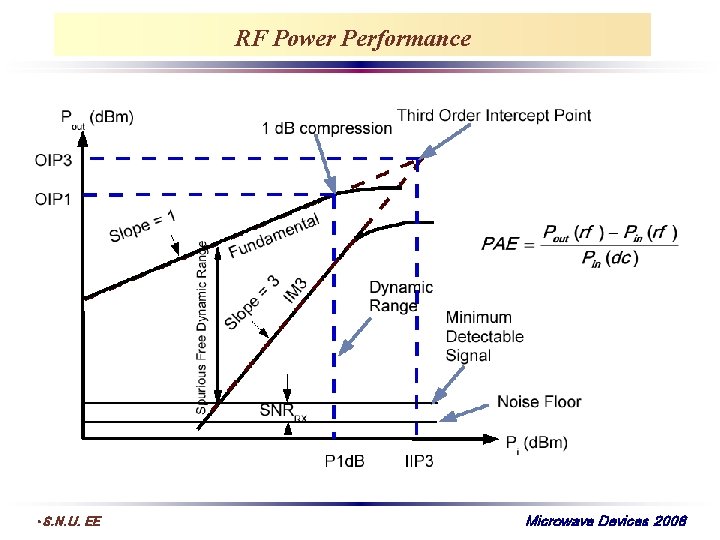

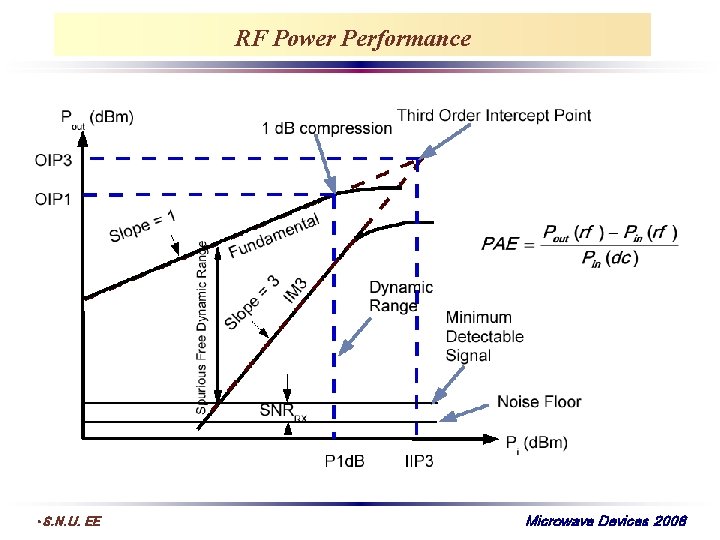

RF Power Performance • S. N. U. EE Microwave Devices 2008

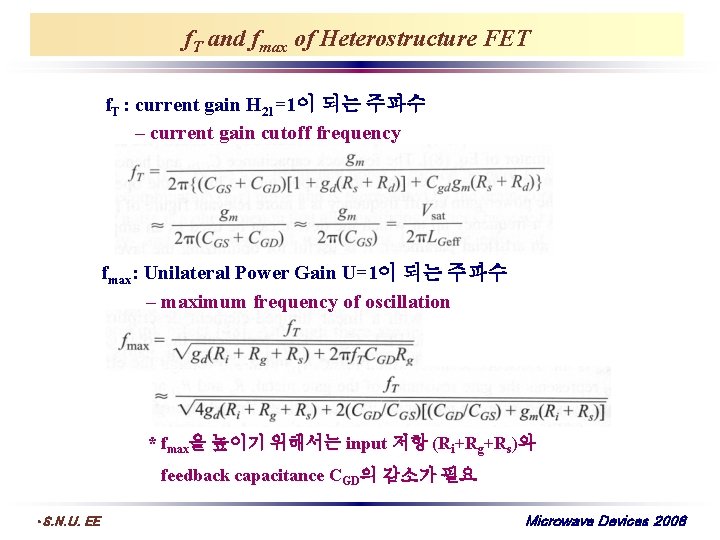

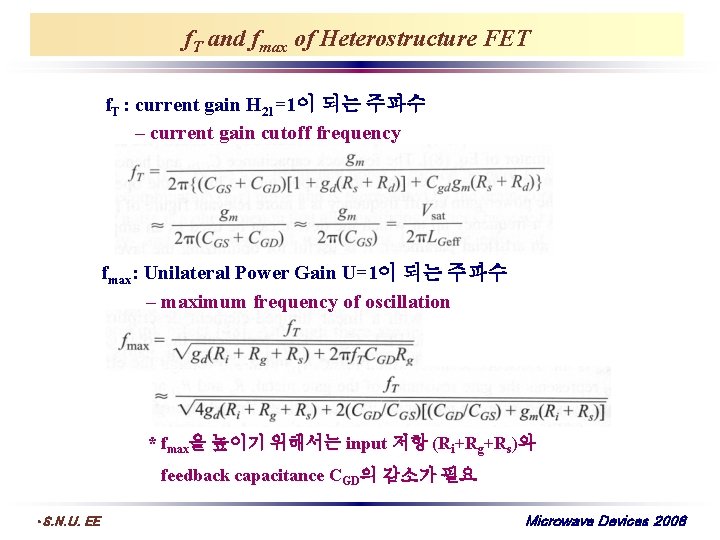

f. T and fmax of Heterostructure FET f. T : current gain H 21=1이 되는 주파수 – current gain cutoff frequency fmax: Unilateral Power Gain U=1이 되는 주파수 – maximum frequency of oscillation * fmax을 높이기 위해서는 input 저항 (Ri+Rg+Rs)와 feedback capacitance CGD의 감소가 필요 • S. N. U. EE Microwave Devices 2008

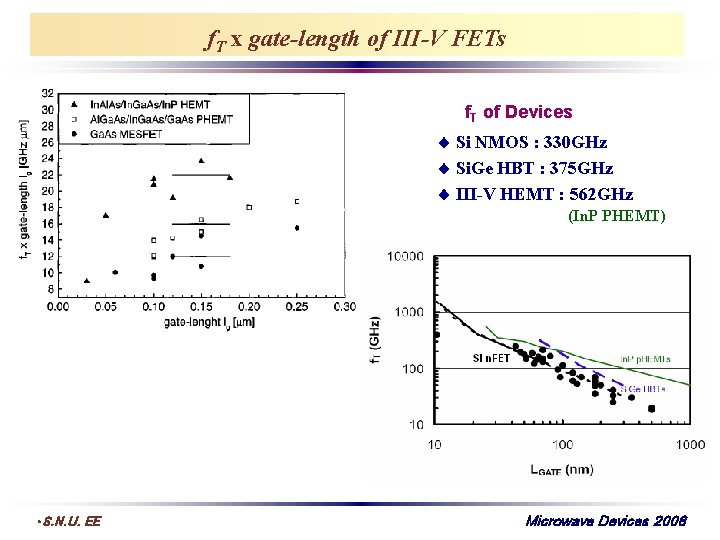

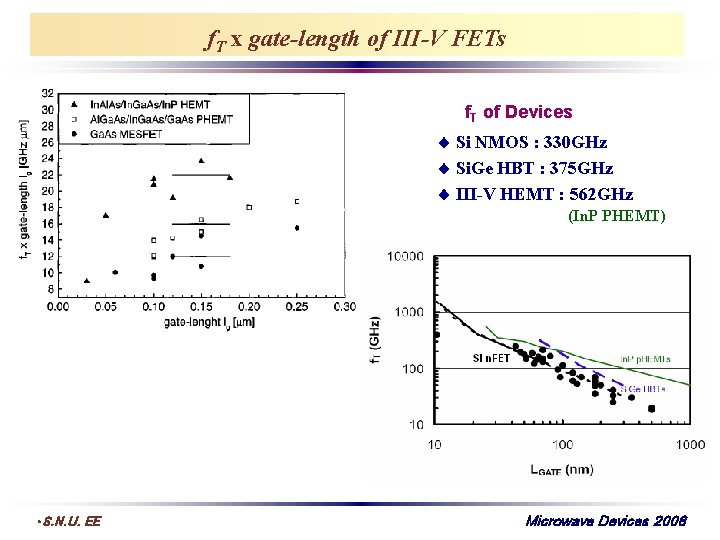

f. T x gate-length of III-V FETs f. T of Devices Si NMOS : 330 GHz Si. Ge HBT : 375 GHz III-V HEMT : 562 GHz (In. P PHEMT) • S. N. U. EE Microwave Devices 2008

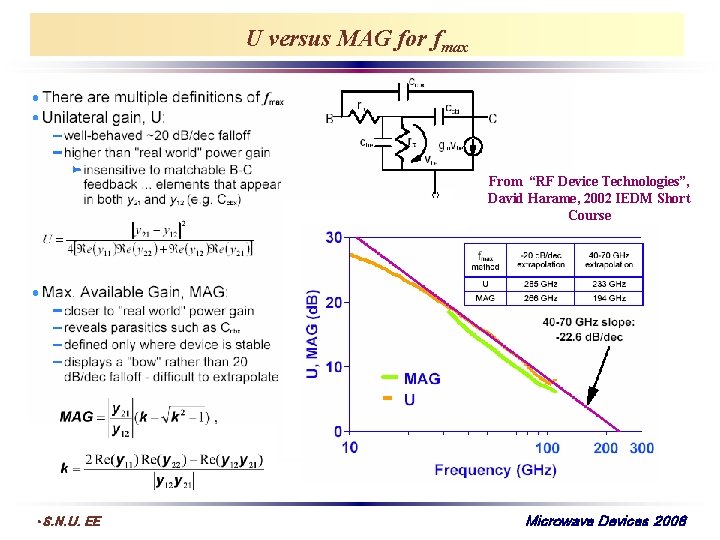

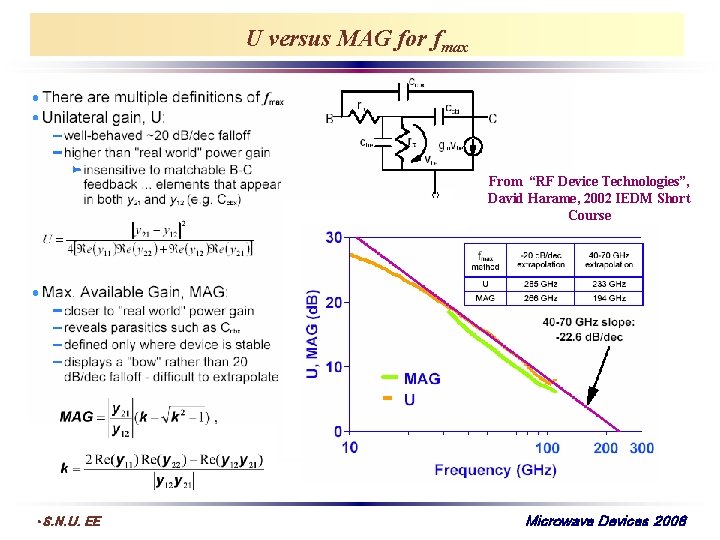

U versus MAG for fmax From “RF Device Technologies”, David Harame, 2002 IEDM Short Course • S. N. U. EE Microwave Devices 2008

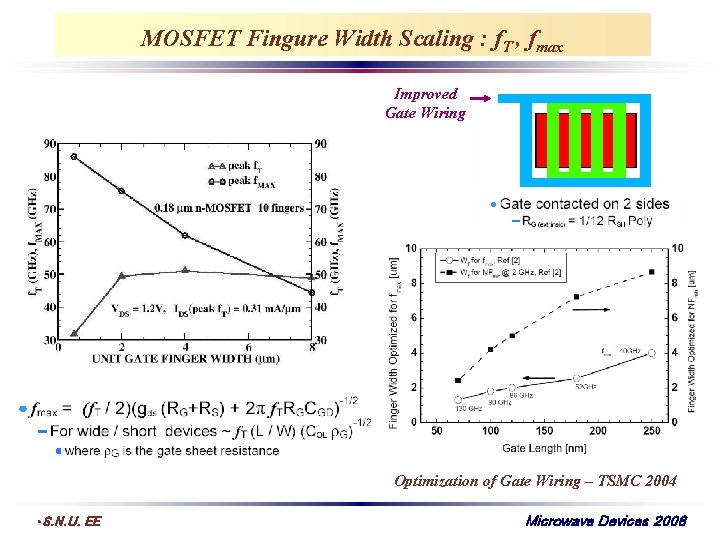

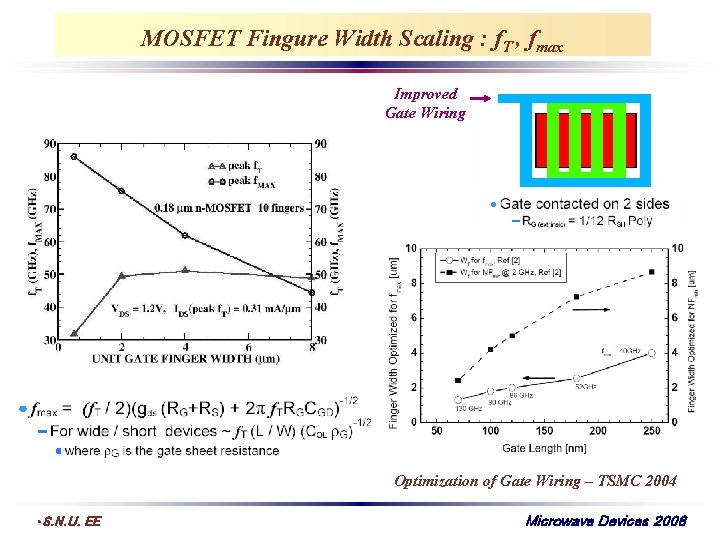

MOSFET Fingure Width Scaling : f. T , fmax Improved Gate Wiring Optimization of Gate Wiring – TSMC 2004 • S. N. U. EE Microwave Devices 2008

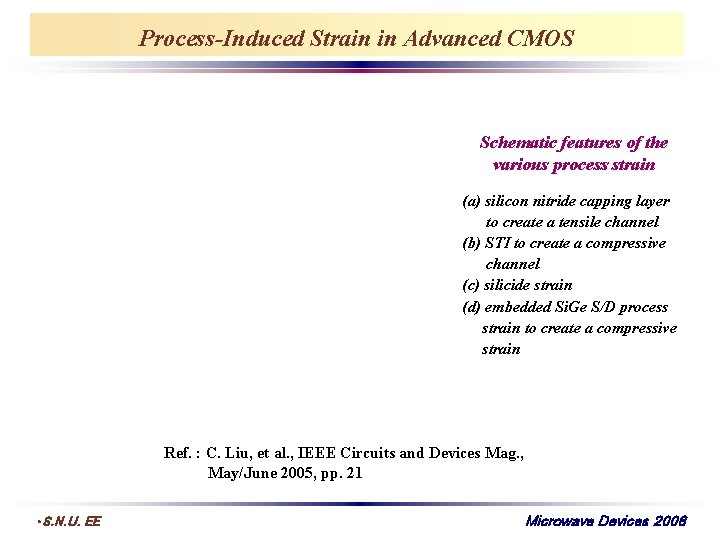

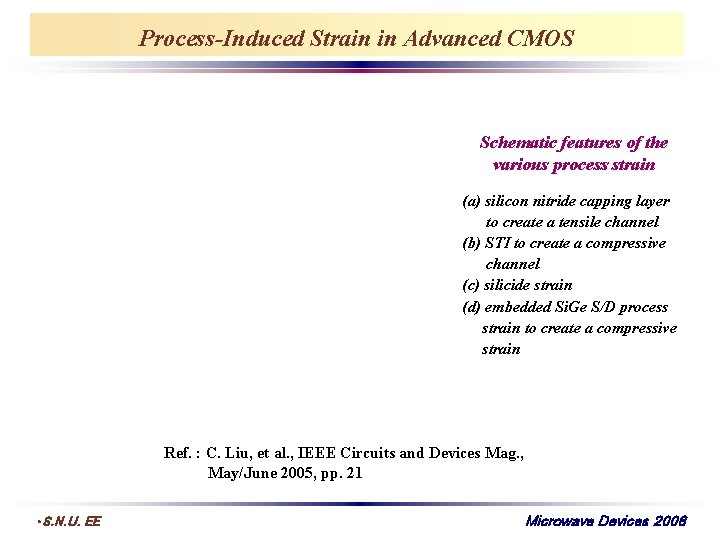

Process-Induced Strain in Advanced CMOS Schematic features of the various process strain (a) silicon nitride capping layer to create a tensile channel (b) STI to create a compressive channel (c) silicide strain (d) embedded Si. Ge S/D process strain to create a compressive strain Ref. : C. Liu, et al. , IEEE Circuits and Devices Mag. , May/June 2005, pp. 21 • S. N. U. EE Microwave Devices 2008

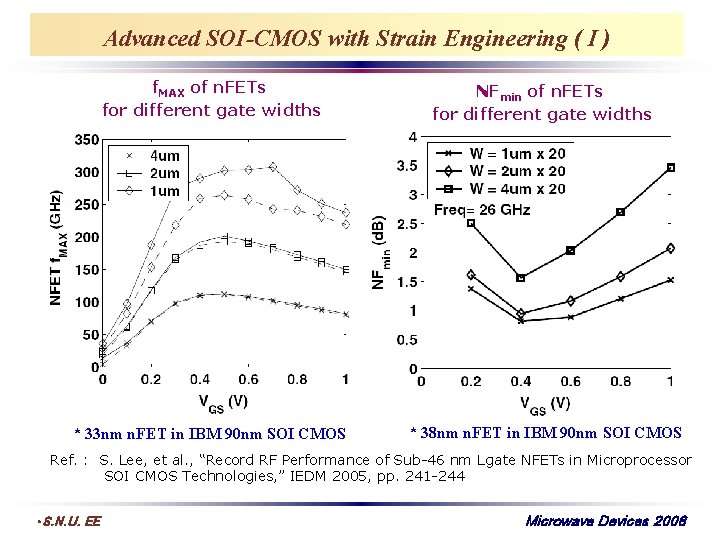

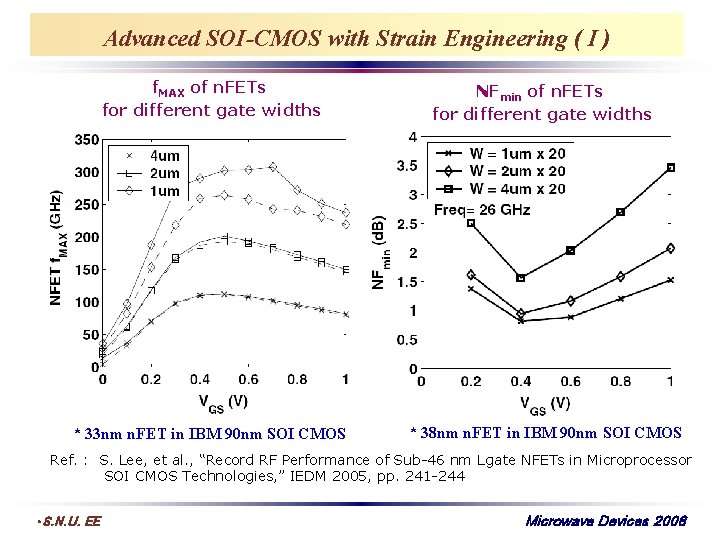

Advanced SOI-CMOS with Strain Engineering ( I ) f. MAX of n. FETs for different gate widths NFmin of n. FETs for different gate widths * 33 nm n. FET in IBM 90 nm SOI CMOS * 38 nm n. FET in IBM 90 nm SOI CMOS Ref. : S. Lee, et al. , “Record RF Performance of Sub-46 nm Lgate NFETs in Microprocessor SOI CMOS Technologies, ” IEDM 2005, pp. 241 -244 • S. N. U. EE Microwave Devices 2008

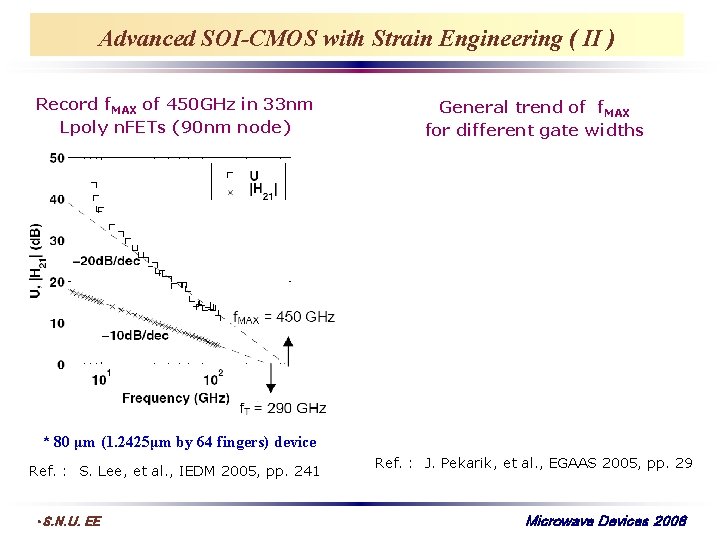

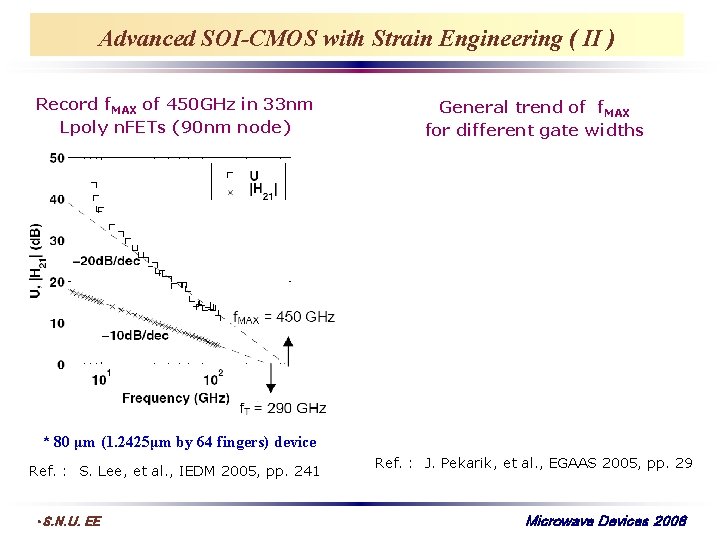

Advanced SOI-CMOS with Strain Engineering ( II ) Record f. MAX of 450 GHz in 33 nm Lpoly n. FETs (90 nm node) General trend of f. MAX for different gate widths * 80 μm (1. 2425μm by 64 fingers) device Ref. : S. Lee, et al. , IEDM 2005, pp. 241 • S. N. U. EE Ref. : J. Pekarik, et al. , EGAAS 2005, pp. 29 Microwave Devices 2008