Microprogramming A Case Study ITSIAC Accumulator register ACC

- Slides: 19

Microprogramming A Case Study

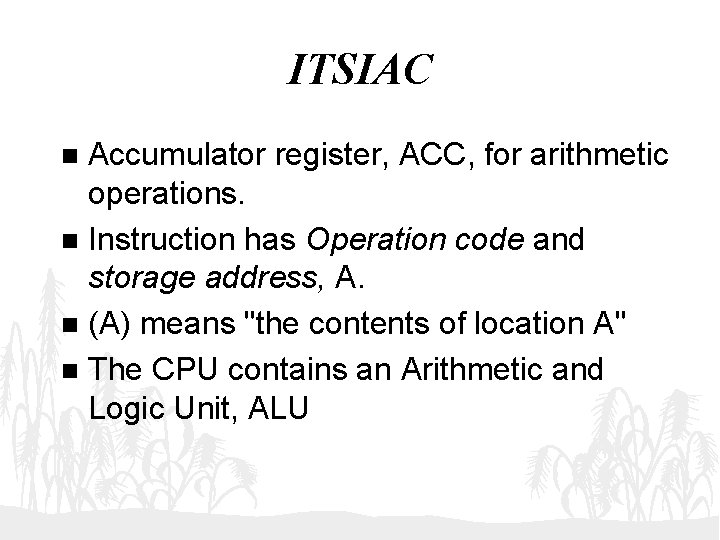

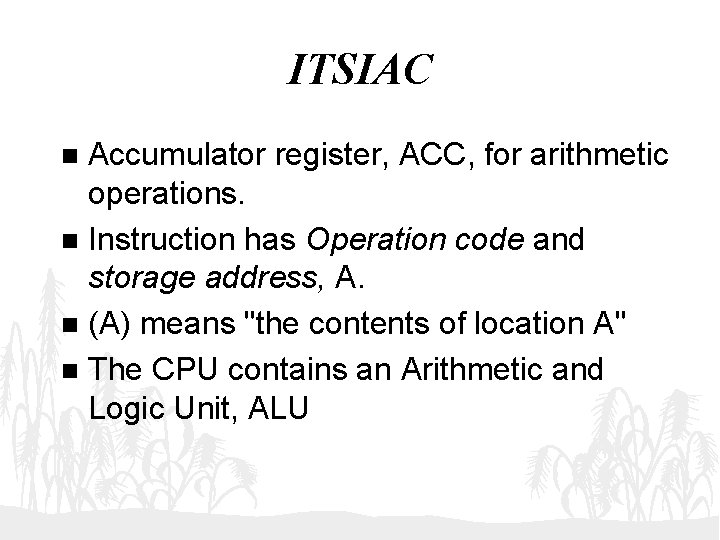

ITSIAC Accumulator register, ACC, for arithmetic operations. n Instruction has Operation code and storage address, A. n (A) means "the contents of location A" n The CPU contains an Arithmetic and Logic Unit, ALU n

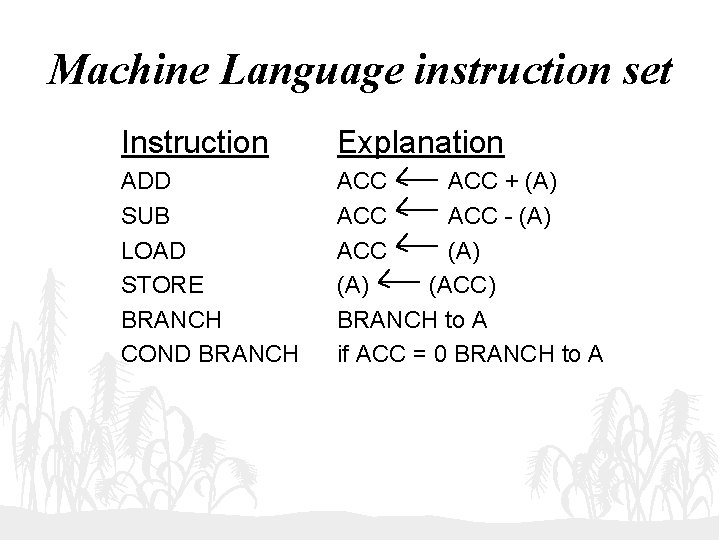

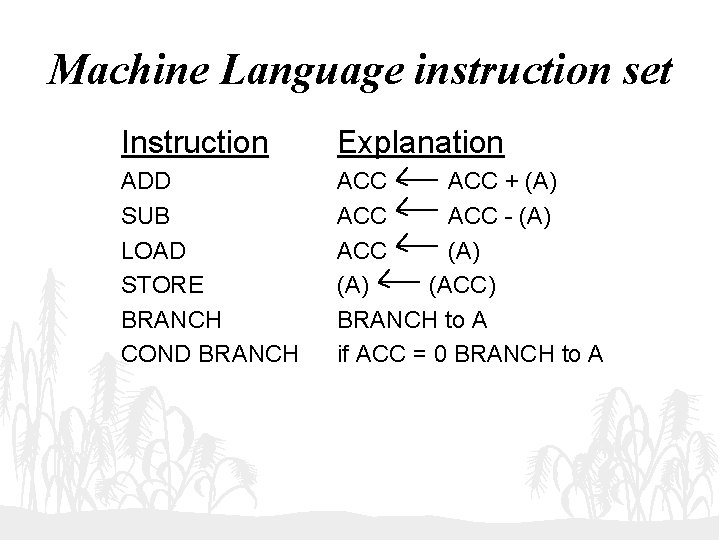

Machine Language instruction set Instruction Explanation ADD SUB LOAD STORE BRANCH COND BRANCH ACC + (A) ACC - (A) ACC (A) (ACC) BRANCH to A if ACC = 0 BRANCH to A

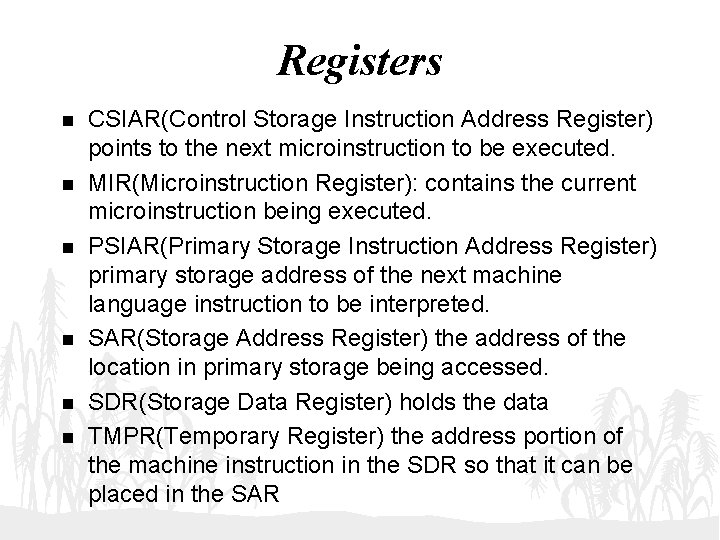

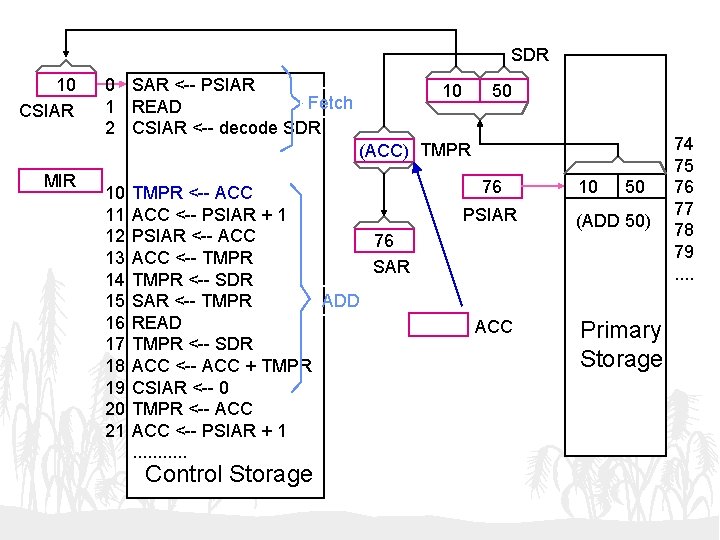

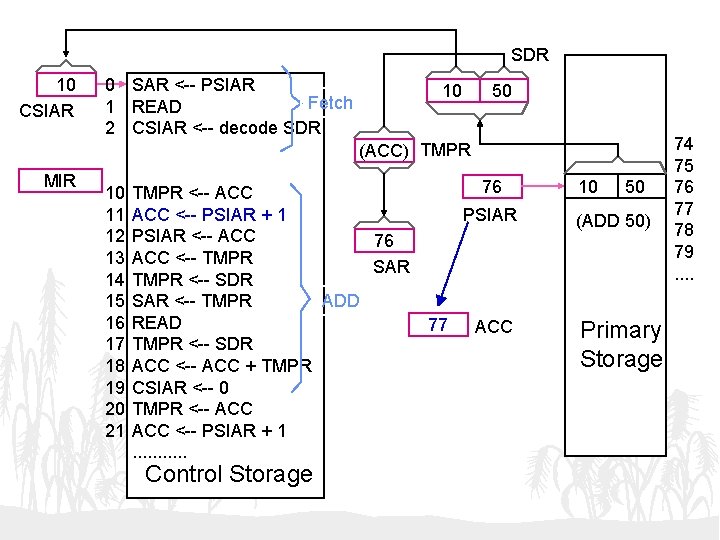

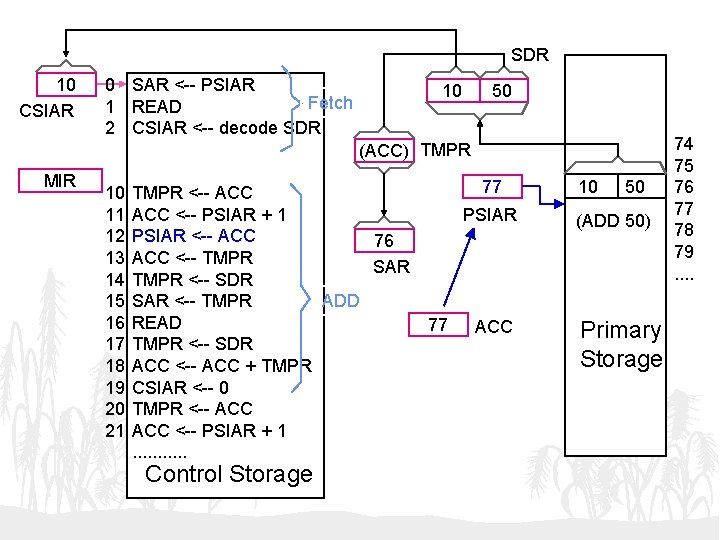

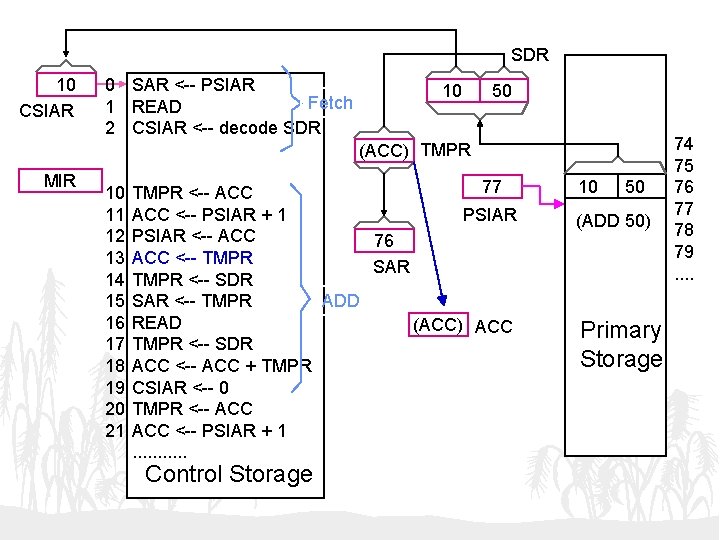

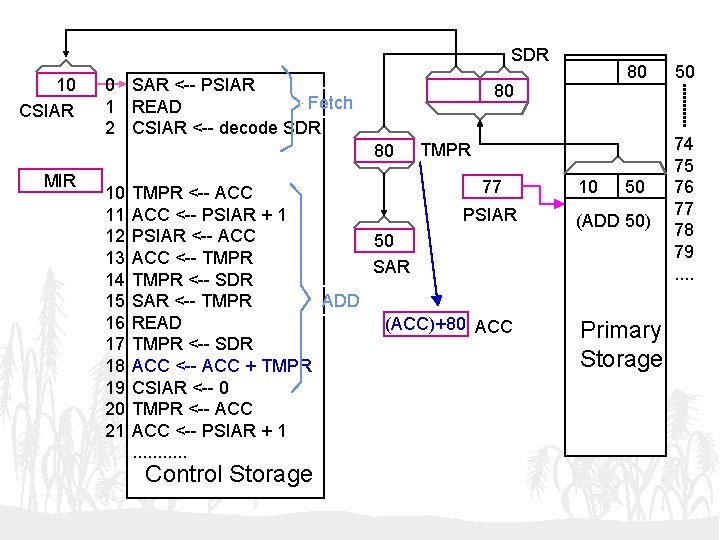

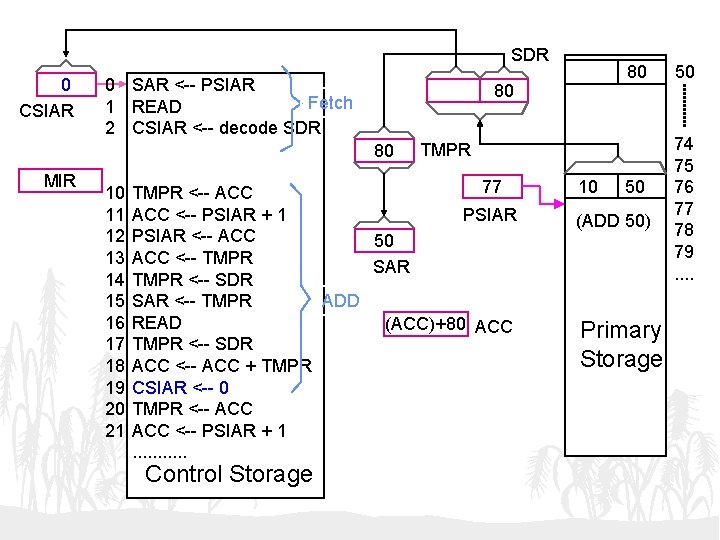

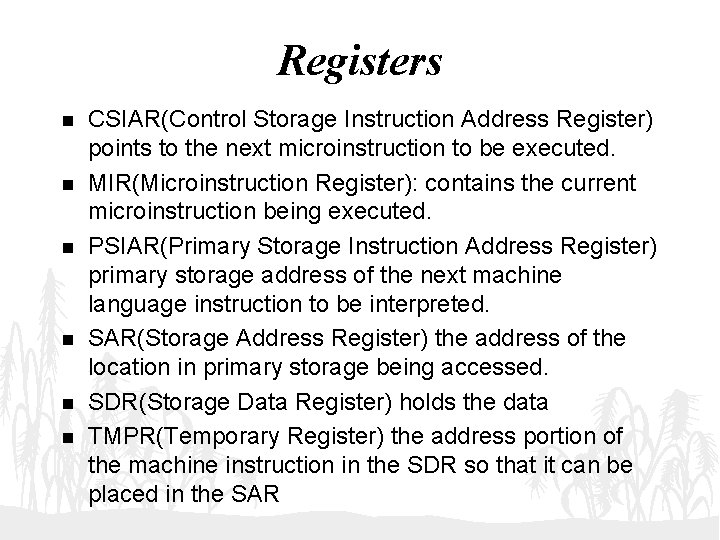

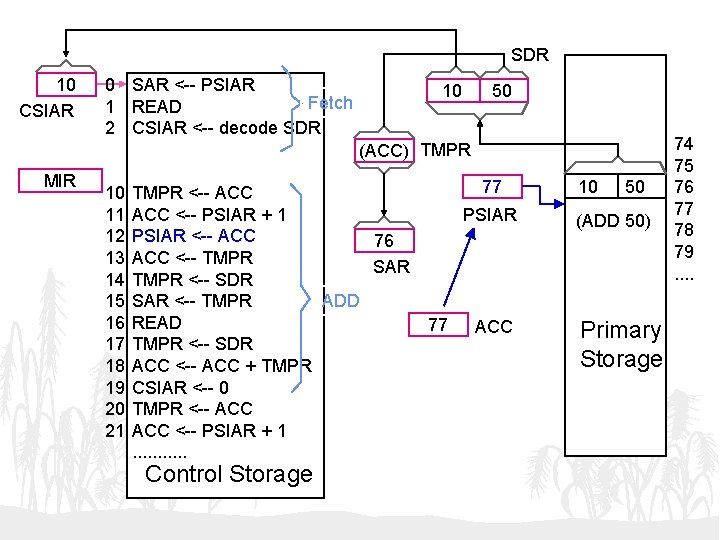

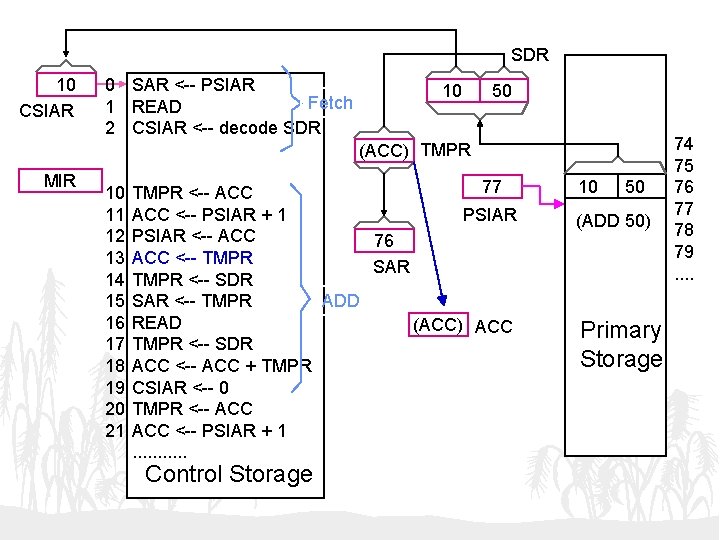

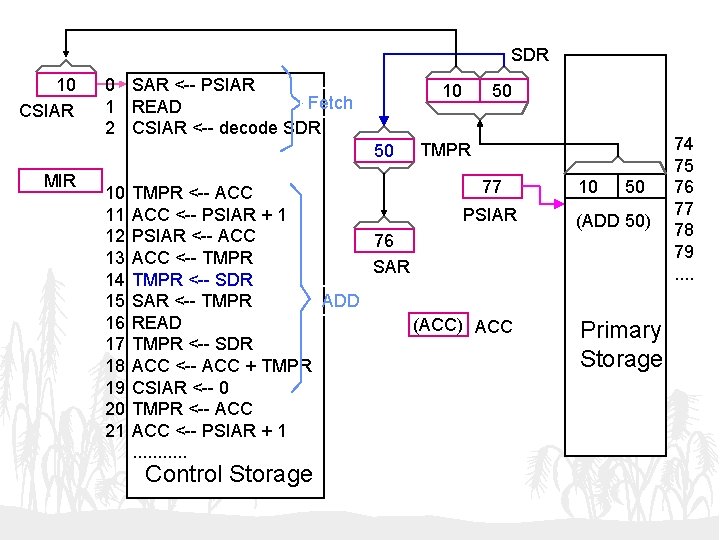

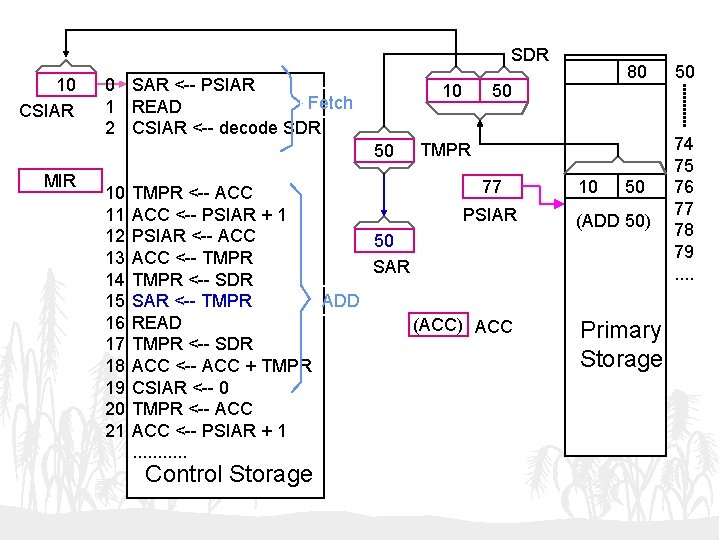

Registers n n n CSIAR(Control Storage Instruction Address Register) points to the next microinstruction to be executed. MIR(Microinstruction Register): contains the current microinstruction being executed. PSIAR(Primary Storage Instruction Address Register) primary storage address of the next machine language instruction to be interpreted. SAR(Storage Address Register) the address of the location in primary storage being accessed. SDR(Storage Data Register) holds the data TMPR(Temporary Register) the address portion of the machine instruction in the SDR so that it can be placed in the SAR

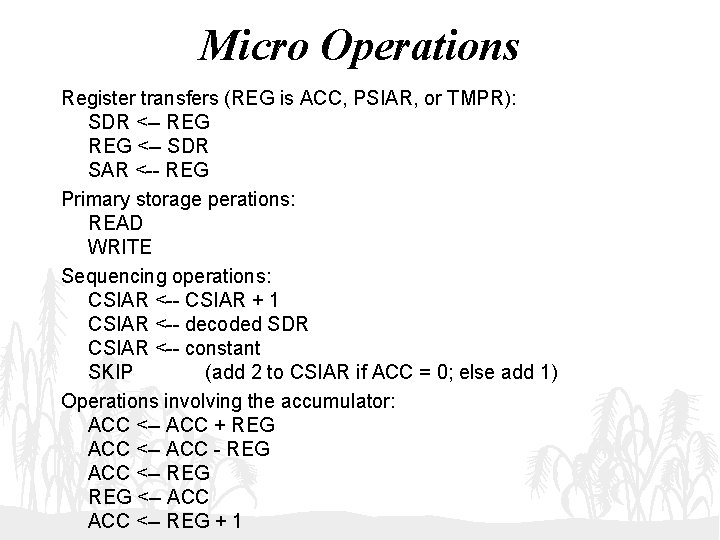

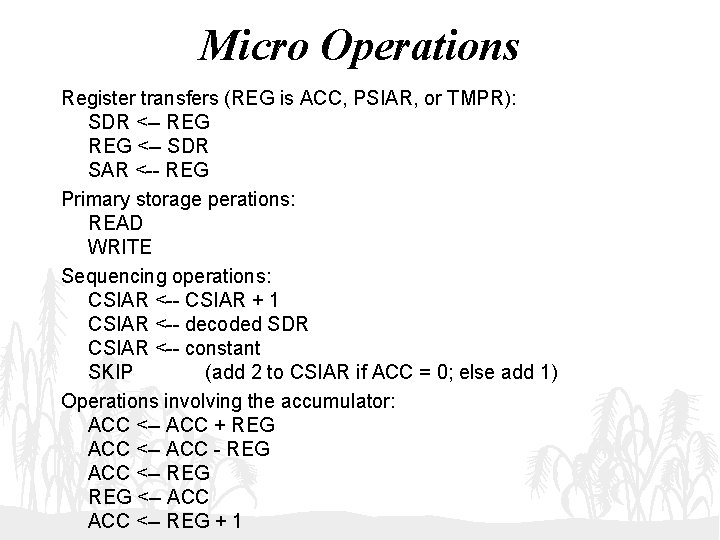

Micro Operations Register transfers (REG is ACC, PSIAR, or TMPR): SDR <-- REG <-- SDR SAR <-- REG Primary storage perations: READ WRITE Sequencing operations: CSIAR <-- CSIAR + 1 CSIAR <-- decoded SDR CSIAR <-- constant SKIP (add 2 to CSIAR if ACC = 0; else add 1) Operations involving the accumulator: ACC <-- ACC + REG ACC <-- ACC - REG ACC <-- REG <-- ACC <-- REG + 1

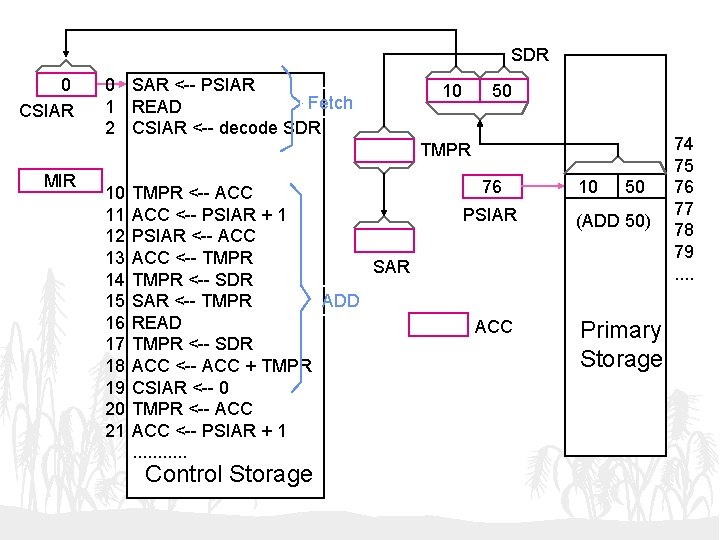

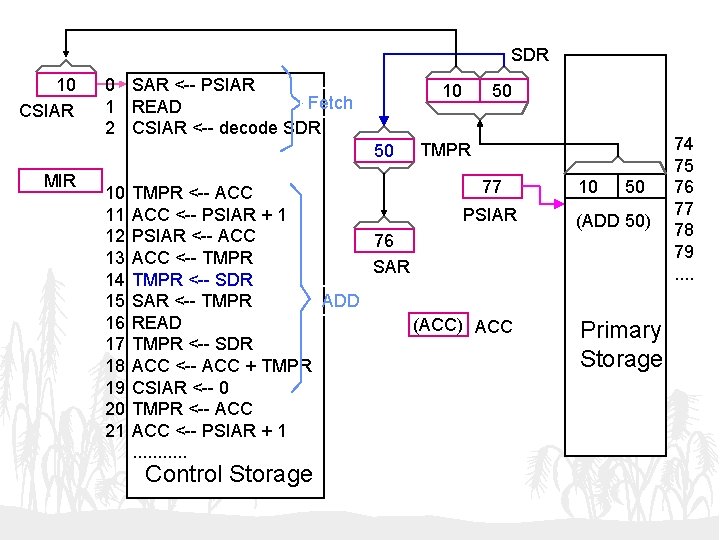

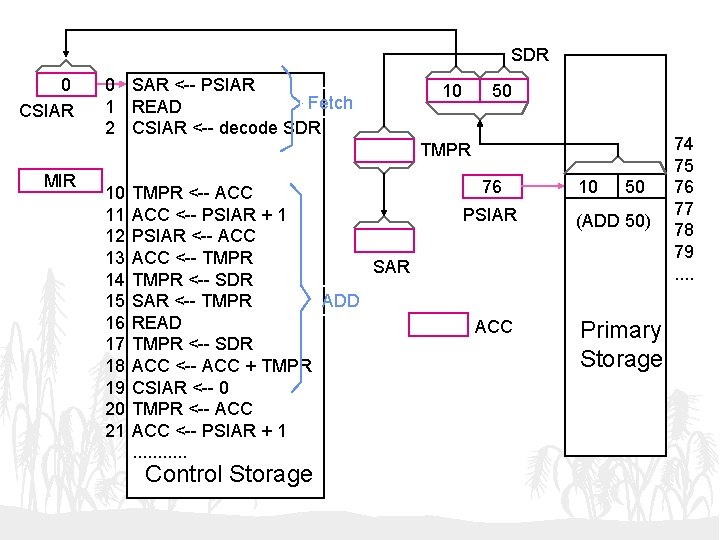

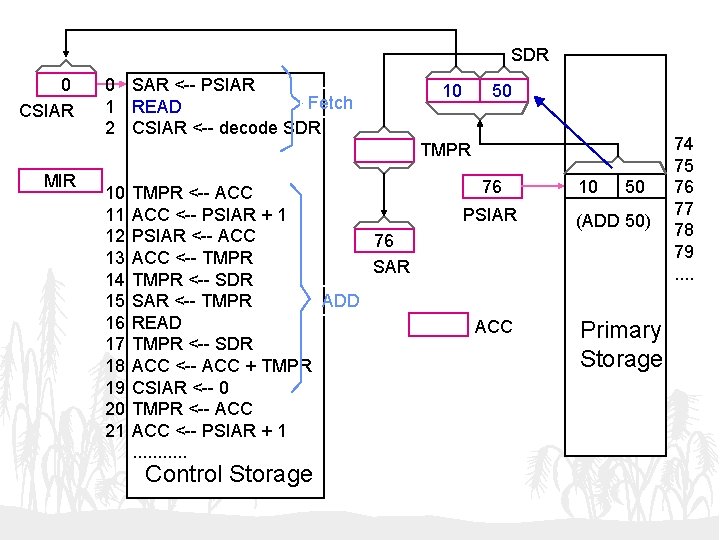

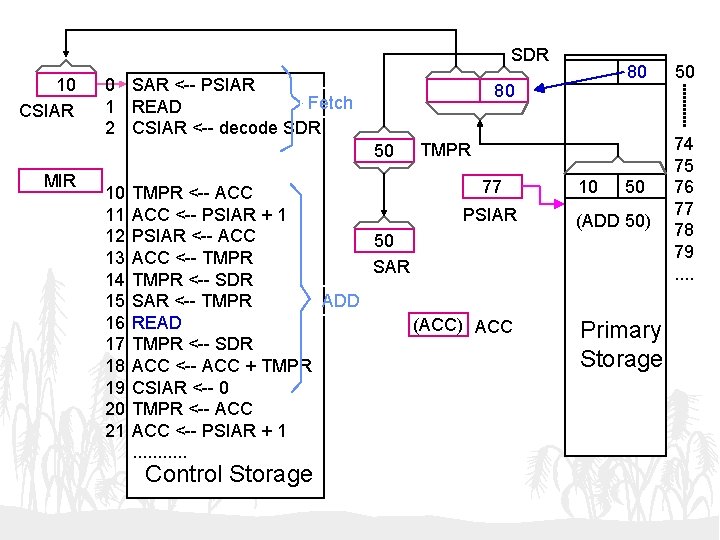

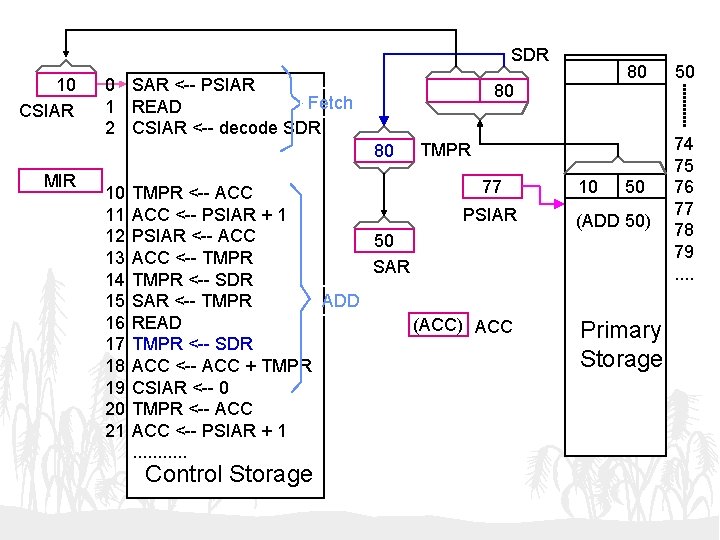

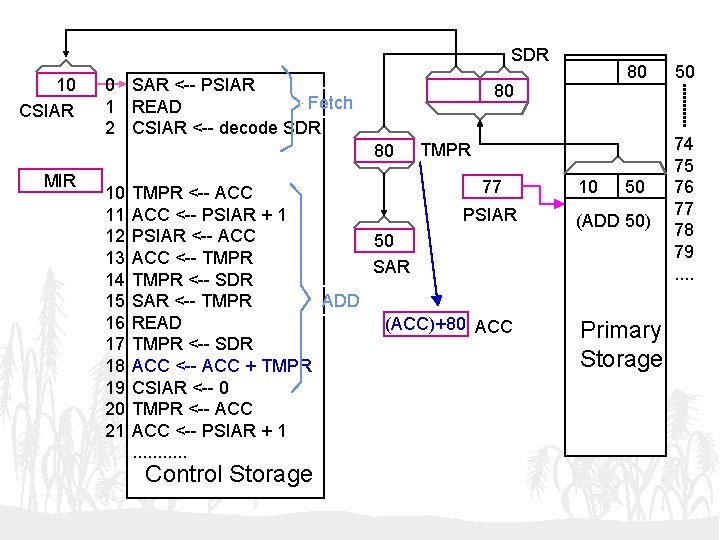

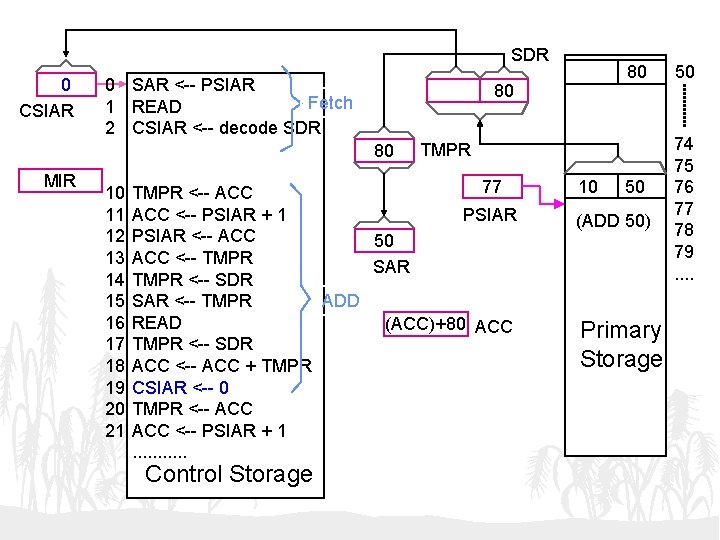

SDR 0 CSIAR 0 SAR <-- PSIAR Fetch 1 READ 2 CSIAR <-- decode SDR 10 50 TMPR MIR 10 11 12 13 14 15 16 17 18 19 20 21 TMPR <-- ACC <-- PSIAR + 1 PSIAR <-- ACC <-- TMPR SAR TMPR <-- SDR ADD SAR <-- TMPR READ TMPR <-- SDR ACC <-- ACC + TMPR CSIAR <-- 0 TMPR <-- ACC <-- PSIAR + 1. . . Control Storage 76 PSIAR ACC 10 50 (ADD 50) Primary Storage 74 75 76 77 78 79. .

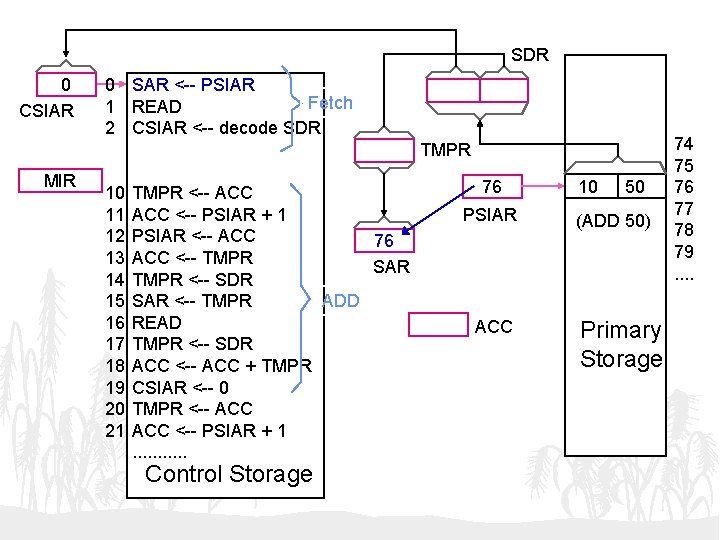

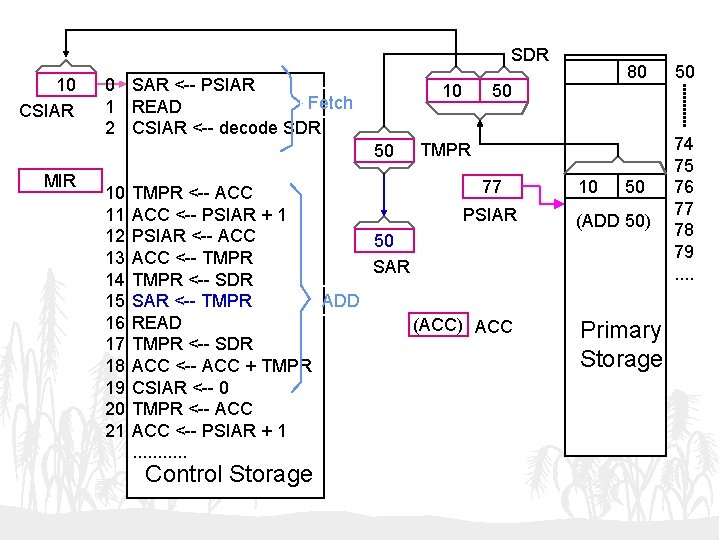

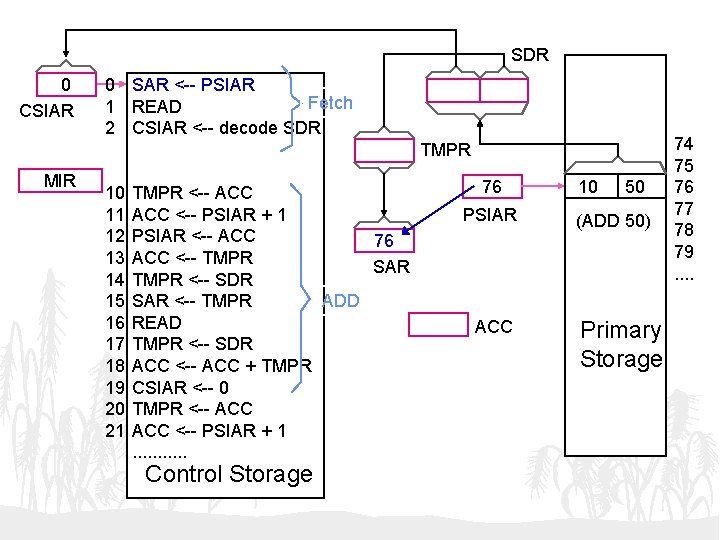

SDR 0 CSIAR 0 SAR <-- PSIAR Fetch 1 READ 2 CSIAR <-- decode SDR TMPR MIR 10 11 12 13 14 15 16 17 18 19 20 21 TMPR <-- ACC <-- PSIAR + 1 PSIAR <-- ACC 76 ACC <-- TMPR SAR TMPR <-- SDR ADD SAR <-- TMPR READ TMPR <-- SDR ACC <-- ACC + TMPR CSIAR <-- 0 TMPR <-- ACC <-- PSIAR + 1. . . Control Storage 76 PSIAR ACC 10 50 (ADD 50) Primary Storage 74 75 76 77 78 79. .

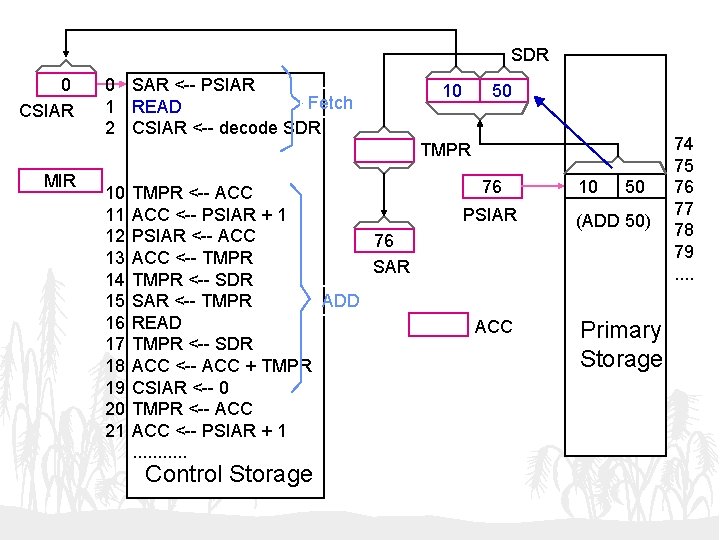

SDR 0 CSIAR 0 SAR <-- PSIAR Fetch 1 READ 2 CSIAR <-- decode SDR 10 50 TMPR MIR 10 11 12 13 14 15 16 17 18 19 20 21 TMPR <-- ACC <-- PSIAR + 1 PSIAR <-- ACC 76 ACC <-- TMPR SAR TMPR <-- SDR ADD SAR <-- TMPR READ TMPR <-- SDR ACC <-- ACC + TMPR CSIAR <-- 0 TMPR <-- ACC <-- PSIAR + 1. . . Control Storage 76 PSIAR ACC 10 50 (ADD 50) Primary Storage 74 75 76 77 78 79. .

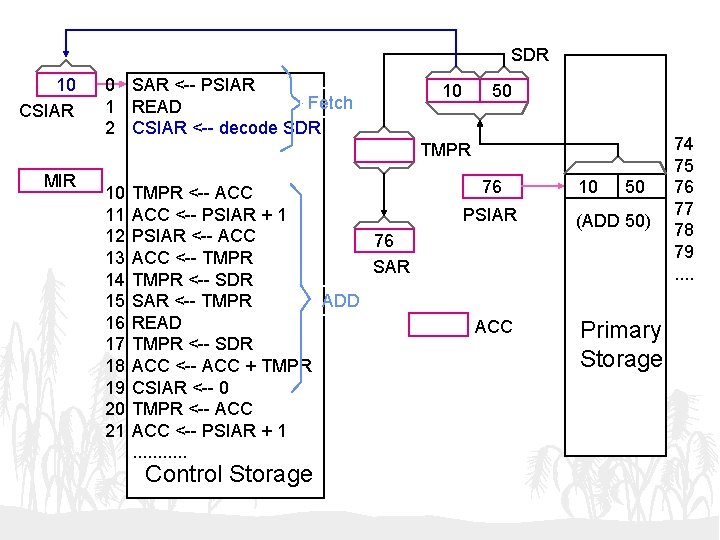

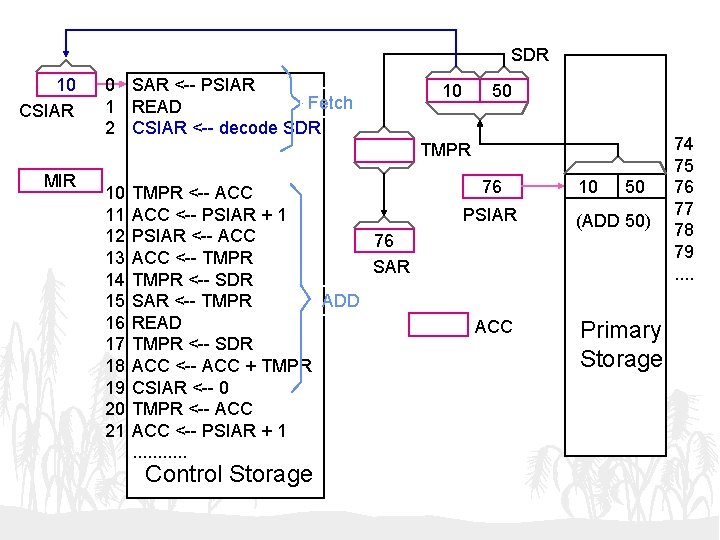

SDR 10 CSIAR 0 SAR <-- PSIAR Fetch 1 READ 2 CSIAR <-- decode SDR 10 50 TMPR MIR 10 11 12 13 14 15 16 17 18 19 20 21 TMPR <-- ACC <-- PSIAR + 1 PSIAR <-- ACC 76 ACC <-- TMPR SAR TMPR <-- SDR ADD SAR <-- TMPR READ TMPR <-- SDR ACC <-- ACC + TMPR CSIAR <-- 0 TMPR <-- ACC <-- PSIAR + 1. . . Control Storage 76 PSIAR ACC 10 50 (ADD 50) Primary Storage 74 75 76 77 78 79. .

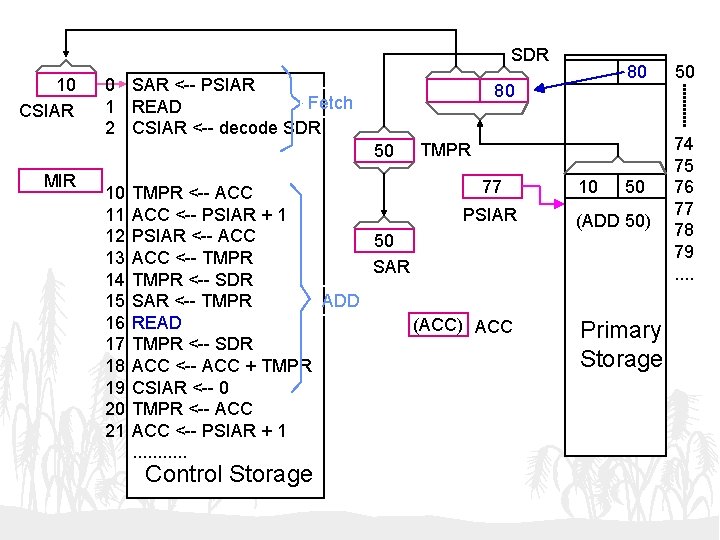

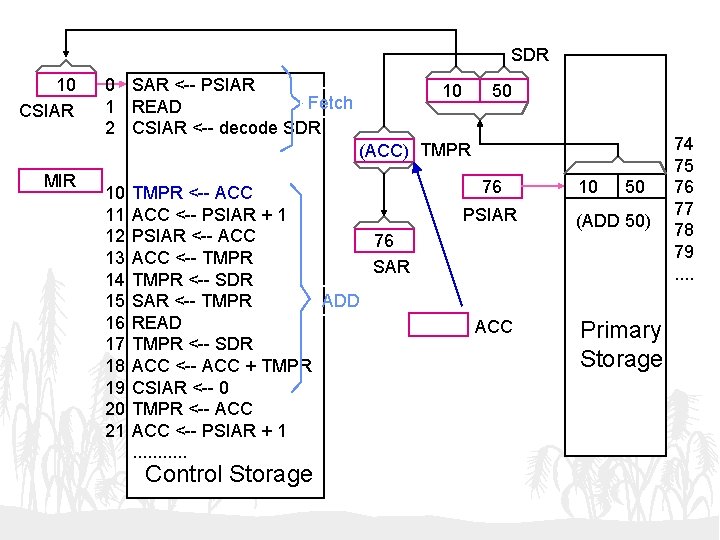

SDR 10 CSIAR 0 SAR <-- PSIAR Fetch 1 READ 2 CSIAR <-- decode SDR 10 50 (ACC) TMPR MIR 10 11 12 13 14 15 16 17 18 19 20 21 TMPR <-- ACC <-- PSIAR + 1 PSIAR <-- ACC 76 ACC <-- TMPR SAR TMPR <-- SDR ADD SAR <-- TMPR READ TMPR <-- SDR ACC <-- ACC + TMPR CSIAR <-- 0 TMPR <-- ACC <-- PSIAR + 1. . . Control Storage 76 PSIAR ACC 10 50 (ADD 50) Primary Storage 74 75 76 77 78 79. .

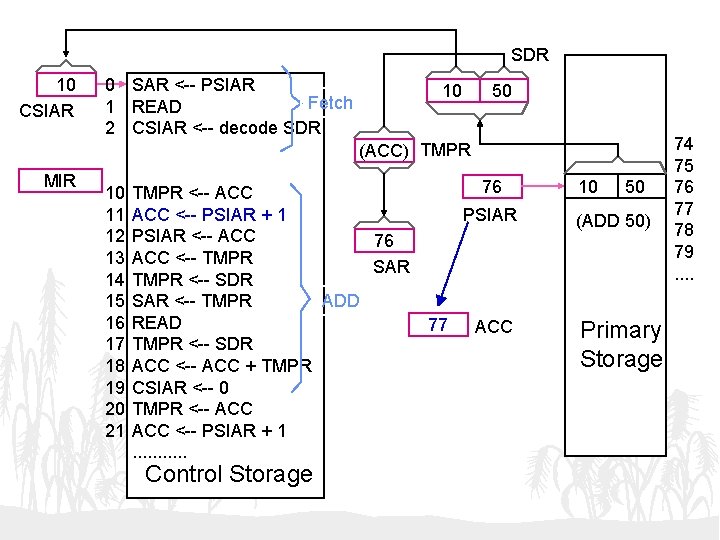

SDR 10 CSIAR 0 SAR <-- PSIAR Fetch 1 READ 2 CSIAR <-- decode SDR 10 50 (ACC) TMPR MIR 10 11 12 13 14 15 16 17 18 19 20 21 76 TMPR <-- ACC <-- PSIAR + 1 PSIAR <-- ACC 76 ACC <-- TMPR SAR TMPR <-- SDR ADD SAR <-- TMPR READ 77 ACC TMPR <-- SDR ACC <-- ACC + TMPR CSIAR <-- 0 TMPR <-- ACC <-- PSIAR + 1. . . Control Storage 10 50 (ADD 50) Primary Storage 74 75 76 77 78 79. .

SDR 10 CSIAR 0 SAR <-- PSIAR Fetch 1 READ 2 CSIAR <-- decode SDR 10 50 (ACC) TMPR MIR 10 11 12 13 14 15 16 17 18 19 20 21 77 TMPR <-- ACC <-- PSIAR + 1 PSIAR <-- ACC 76 ACC <-- TMPR SAR TMPR <-- SDR ADD SAR <-- TMPR READ 77 ACC TMPR <-- SDR ACC <-- ACC + TMPR CSIAR <-- 0 TMPR <-- ACC <-- PSIAR + 1. . . Control Storage 10 50 (ADD 50) Primary Storage 74 75 76 77 78 79. .

SDR 10 CSIAR 0 SAR <-- PSIAR Fetch 1 READ 2 CSIAR <-- decode SDR 10 50 (ACC) TMPR MIR 10 11 12 13 14 15 16 17 18 19 20 21 77 TMPR <-- ACC <-- PSIAR + 1 PSIAR <-- ACC 76 ACC <-- TMPR SAR TMPR <-- SDR ADD SAR <-- TMPR READ (ACC) ACC TMPR <-- SDR ACC <-- ACC + TMPR CSIAR <-- 0 TMPR <-- ACC <-- PSIAR + 1. . . Control Storage 10 50 (ADD 50) Primary Storage 74 75 76 77 78 79. .

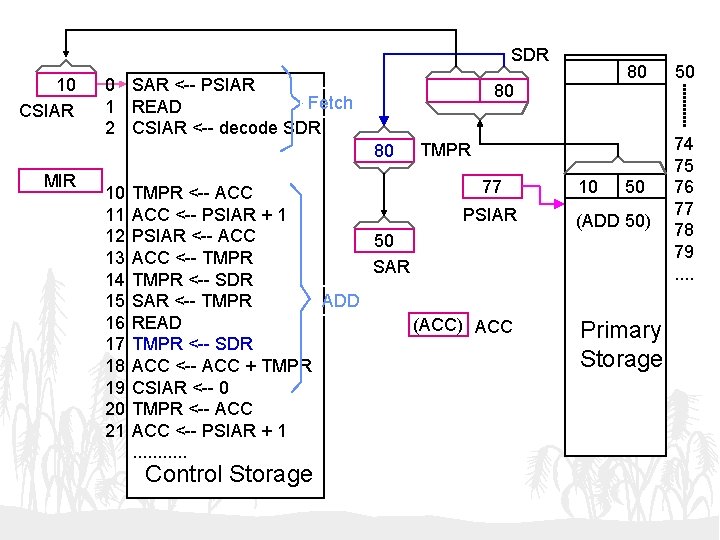

SDR 10 CSIAR 0 SAR <-- PSIAR Fetch 1 READ 2 CSIAR <-- decode SDR 10 50 MIR 10 11 12 13 14 15 16 17 18 19 20 21 50 TMPR 77 TMPR <-- ACC <-- PSIAR + 1 PSIAR <-- ACC 76 ACC <-- TMPR SAR TMPR <-- SDR ADD SAR <-- TMPR READ (ACC) ACC TMPR <-- SDR ACC <-- ACC + TMPR CSIAR <-- 0 TMPR <-- ACC <-- PSIAR + 1. . . Control Storage 10 50 (ADD 50) Primary Storage 74 75 76 77 78 79. .

SDR 10 CSIAR 0 SAR <-- PSIAR Fetch 1 READ 2 CSIAR <-- decode SDR 10 50 MIR 10 11 12 13 14 15 16 17 18 19 20 21 50 TMPR 77 TMPR <-- ACC <-- PSIAR + 1 PSIAR <-- ACC 50 ACC <-- TMPR SAR TMPR <-- SDR ADD SAR <-- TMPR READ (ACC) ACC TMPR <-- SDR ACC <-- ACC + TMPR CSIAR <-- 0 TMPR <-- ACC <-- PSIAR + 1. . . Control Storage 80 10 50 (ADD 50) Primary Storage 50 74 75 76 77 78 79. .

SDR 10 CSIAR 0 SAR <-- PSIAR Fetch 1 READ 2 CSIAR <-- decode SDR 80 50 MIR 10 11 12 13 14 15 16 17 18 19 20 21 TMPR 77 TMPR <-- ACC <-- PSIAR + 1 PSIAR <-- ACC 50 ACC <-- TMPR SAR TMPR <-- SDR ADD SAR <-- TMPR READ (ACC) ACC TMPR <-- SDR ACC <-- ACC + TMPR CSIAR <-- 0 TMPR <-- ACC <-- PSIAR + 1. . . Control Storage 80 10 50 (ADD 50) Primary Storage 50 74 75 76 77 78 79. .

SDR 10 CSIAR 0 SAR <-- PSIAR Fetch 1 READ 2 CSIAR <-- decode SDR 80 80 MIR 10 11 12 13 14 15 16 17 18 19 20 21 TMPR 77 TMPR <-- ACC <-- PSIAR + 1 PSIAR <-- ACC 50 ACC <-- TMPR SAR TMPR <-- SDR ADD SAR <-- TMPR READ (ACC) ACC TMPR <-- SDR ACC <-- ACC + TMPR CSIAR <-- 0 TMPR <-- ACC <-- PSIAR + 1. . . Control Storage 80 10 50 (ADD 50) Primary Storage 50 74 75 76 77 78 79. .

SDR 10 CSIAR 0 SAR <-- PSIAR Fetch 1 READ 2 CSIAR <-- decode SDR 80 80 MIR 10 11 12 13 14 15 16 17 18 19 20 21 TMPR 77 TMPR <-- ACC <-- PSIAR + 1 PSIAR <-- ACC 50 ACC <-- TMPR SAR TMPR <-- SDR ADD SAR <-- TMPR READ (ACC)+80 ACC TMPR <-- SDR ACC <-- ACC + TMPR CSIAR <-- 0 TMPR <-- ACC <-- PSIAR + 1. . . Control Storage 80 10 50 (ADD 50) Primary Storage 50 74 75 76 77 78 79. .

SDR 0 CSIAR 0 SAR <-- PSIAR Fetch 1 READ 2 CSIAR <-- decode SDR 80 80 MIR 10 11 12 13 14 15 16 17 18 19 20 21 TMPR 77 TMPR <-- ACC <-- PSIAR + 1 PSIAR <-- ACC 50 ACC <-- TMPR SAR TMPR <-- SDR ADD SAR <-- TMPR READ (ACC)+80 ACC TMPR <-- SDR ACC <-- ACC + TMPR CSIAR <-- 0 TMPR <-- ACC <-- PSIAR + 1. . . Control Storage 80 10 50 (ADD 50) Primary Storage 50 74 75 76 77 78 79. .