Microprogramao Vamos ento construir o controlador microprogramado do

- Slides: 46

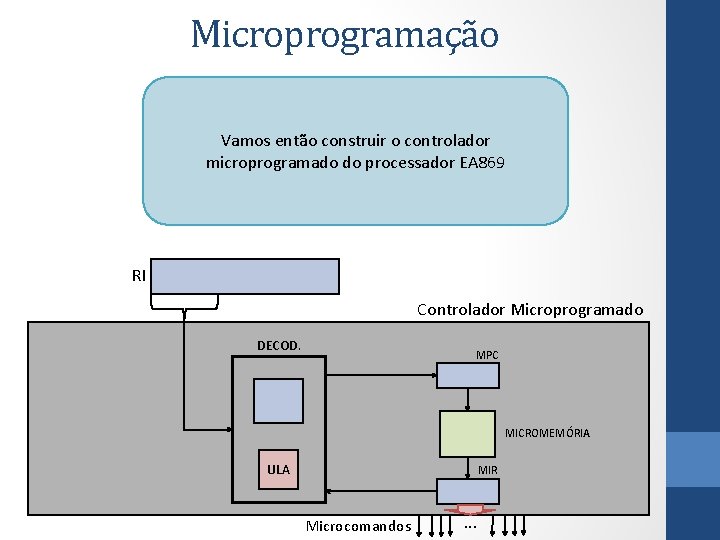

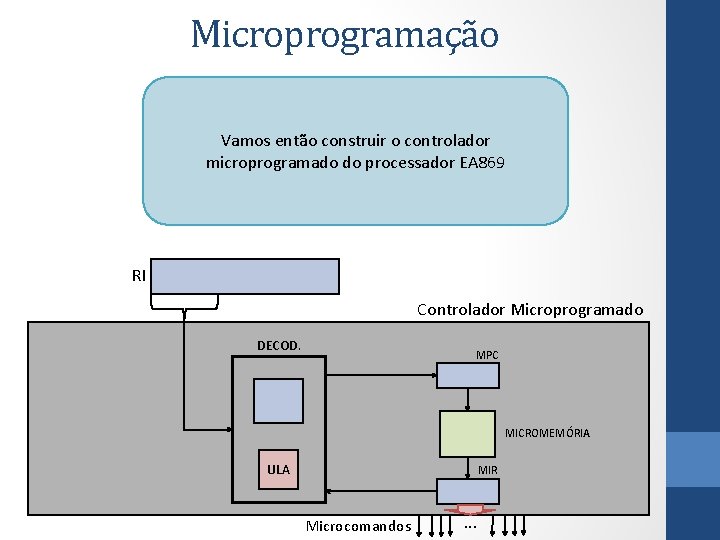

Microprogramação Vamos então construir o controlador microprogramado do processador EA 869 RI Controlador Microprogramado DECOD. MPC MICROMEMÓRIA ULA MIR Microcomandos . . .

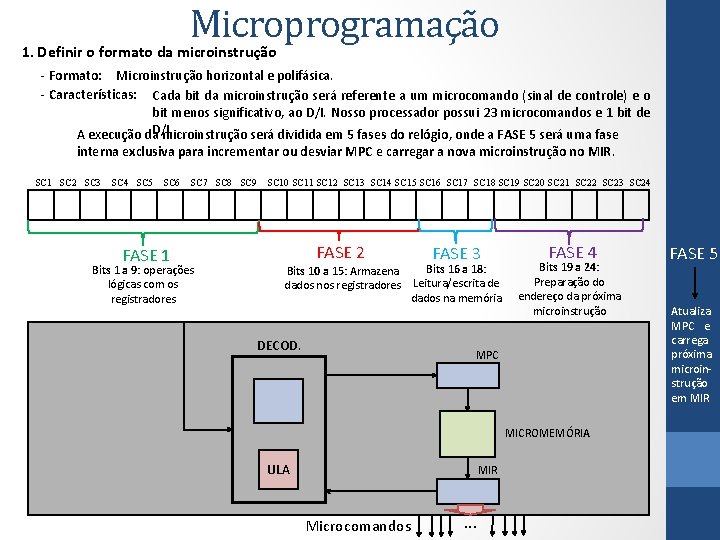

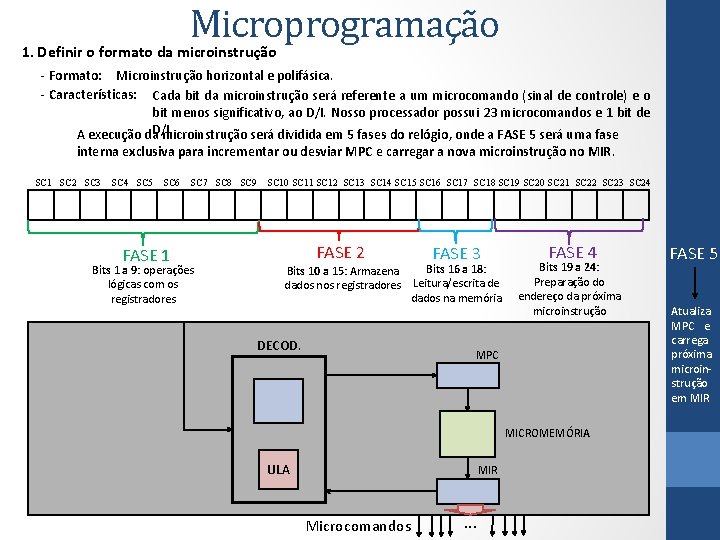

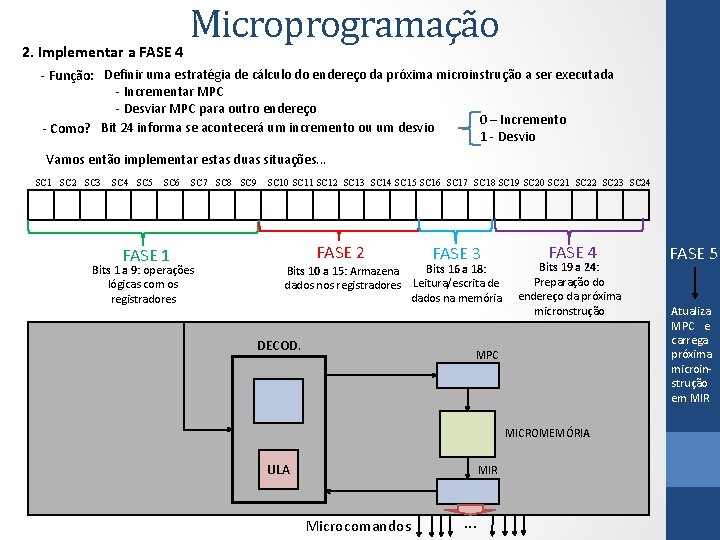

Microprogramação 1. Definir o formato da microinstrução - Formato: Microinstrução horizontal e polifásica. - Características: Cada bit da microinstrução será referente a um microcomando (sinal de controle) e o bit menos significativo, ao D/I. Nosso processador possui 23 microcomandos e 1 bit de D/I. A execução da microinstrução será dividida em 5 fases do relógio, onde a FASE 5 será uma fase interna exclusiva para incrementar ou desviar MPC e carregar a nova microinstrução no MIR. SC 1 SC 2 SC 3 SC 4 SC 5 SC 6 FASE 1 SC 7 SC 8 SC 9 Bits 1 a 9: operações lógicas com os registradores SC 10 SC 11 SC 12 SC 13 SC 14 SC 15 SC 16 SC 17 SC 18 SC 19 SC 20 SC 21 SC 22 SC 23 SC 24 FASE 2 FASE 3 Bits 16 a 18: Bits 10 a 15: Armazena Leitura/escrita de dados nos registradores dados na memória DECOD. FASE 4 Bits 19 a 24: Preparação do endereço da próxima microinstrução MPC MICROMEMÓRIA ULA MIR Microcomandos . . . FASE 5 Atualiza MPC e carrega próxima microinstrução em MIR

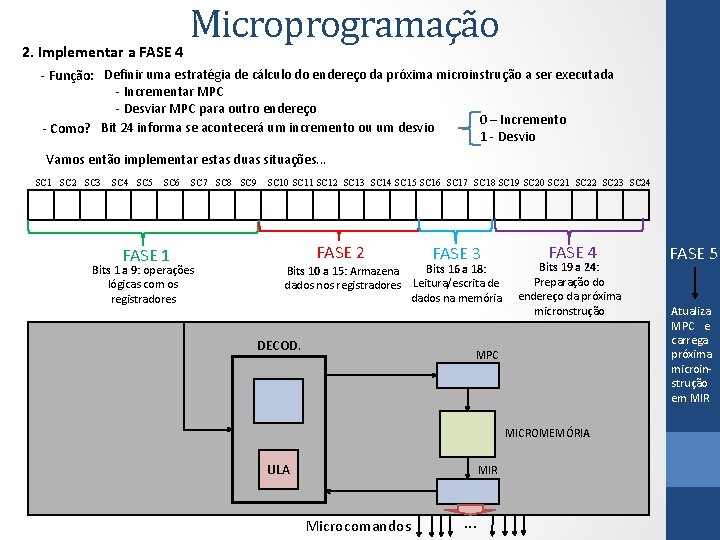

2. Implementar a FASE 4 Microprogramação - Função: Definir uma estratégia de cálculo do endereço da próxima microinstrução a ser executada - Incrementar MPC - Desviar MPC para outro endereço 0 – Incremento - Como? Bit 24 informa se acontecerá um incremento ou um desvio 1 - Desvio Vamos então implementar estas duas situações. . . SC 1 SC 2 SC 3 SC 4 SC 5 SC 6 FASE 1 SC 7 SC 8 SC 9 Bits 1 a 9: operações lógicas com os registradores SC 10 SC 11 SC 12 SC 13 SC 14 SC 15 SC 16 SC 17 SC 18 SC 19 SC 20 SC 21 SC 22 SC 23 SC 24 FASE 2 FASE 3 Bits 16 a 18: Bits 10 a 15: Armazena Leitura/escrita de dados nos registradores dados na memória DECOD. FASE 4 Bits 19 a 24: Preparação do endereço da próxima micronstrução MPC MICROMEMÓRIA ULA MIR Microcomandos . . . FASE 5 Atualiza MPC e carrega próxima microinstrução em MIR

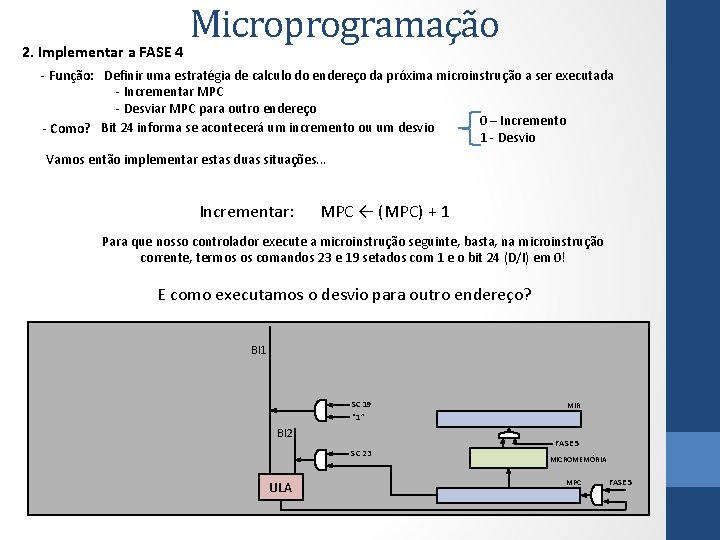

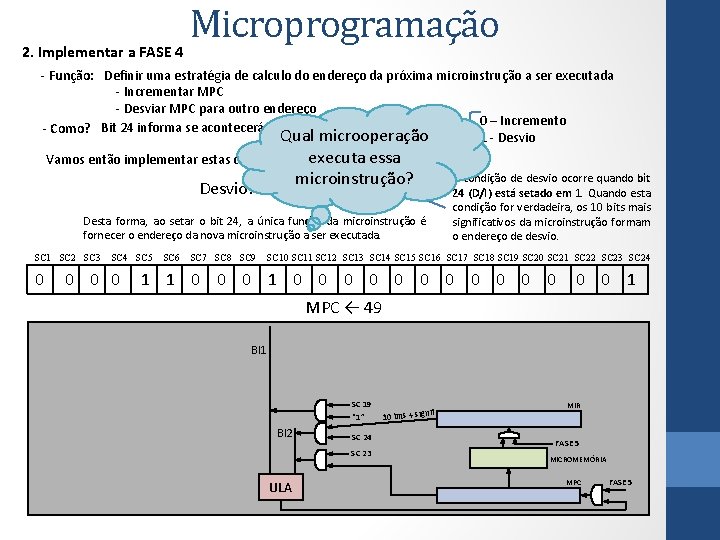

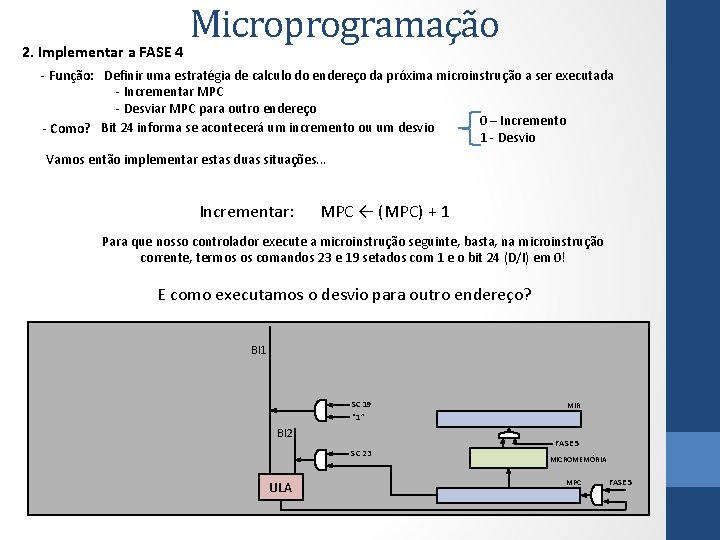

2. Implementar a FASE 4 Microprogramação - Função: Definir uma estratégia de calculo do endereço da próxima microinstrução a ser executada - Incrementar MPC - Desviar MPC para outro endereço 0 – Incremento - Como? Bit 24 informa se acontecerá um incremento ou um desvio 1 - Desvio Vamos então implementar estas duas situações. . . Incrementar: MPC ← (MPC) + 1 Para que nosso controlador execute a microinstrução seguinte, basta, na microinstrução corrente, termos os comandos 23 e 19 setados com 1 e o bit 24 (D/I) em 0! E como executamos o desvio para outro endereço? BI 1 SC 19 “ 1” BI 2 SC 23 ULA MIR FASE 5 MICROMEMÓRIA MPC FASE 5

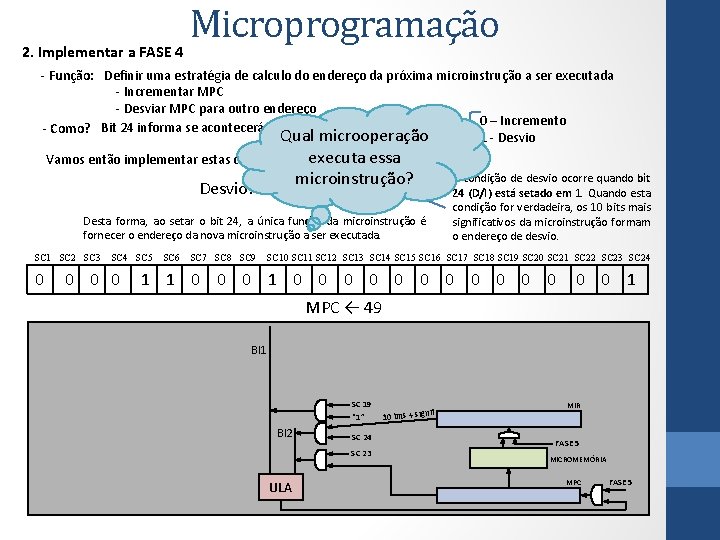

2. Implementar a FASE 4 Microprogramação - Função: Definir uma estratégia de calculo do endereço da próxima microinstrução a ser executada - Incrementar MPC - Desviar MPC para outro endereço 0 – Incremento - Como? Bit 24 informa se acontecerá um incremento ou um desvio! Qual microoperação 1 - Desvio executa essa Vamos então implementar estas duas situações. . . microinstrução? MPC ← end Desvio: A condição de desvio ocorre quando bit 24 (D/I) está setado em 1. Quando esta condição for verdadeira, os 10 bits mais significativos da microinstrução formam o endereço de desvio. Desta forma, ao setar o bit 24, a única função da microinstrução é fornecer o endereço da nova microinstrução a ser executada. SC 1 SC 2 SC 3 SC 4 SC 5 SC 6 SC 7 SC 8 SC 9 SC 10 SC 11 SC 12 SC 13 SC 14 SC 15 SC 16 SC 17 SC 18 SC 19 SC 20 SC 21 SC 22 SC 23 SC 24 0 0 0 0 1 1 0 0 0 0 0 0 1 MPC ← 49 BI 1 SC 19 “ 1” BI 2 SC 24 SC 23 ULA . if 10 bits + sign MIR FASE 5 MICROMEMÓRIA MPC FASE 5

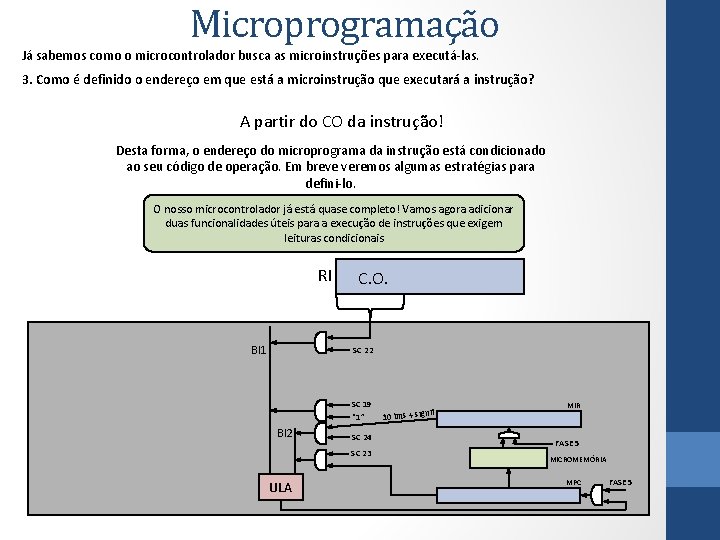

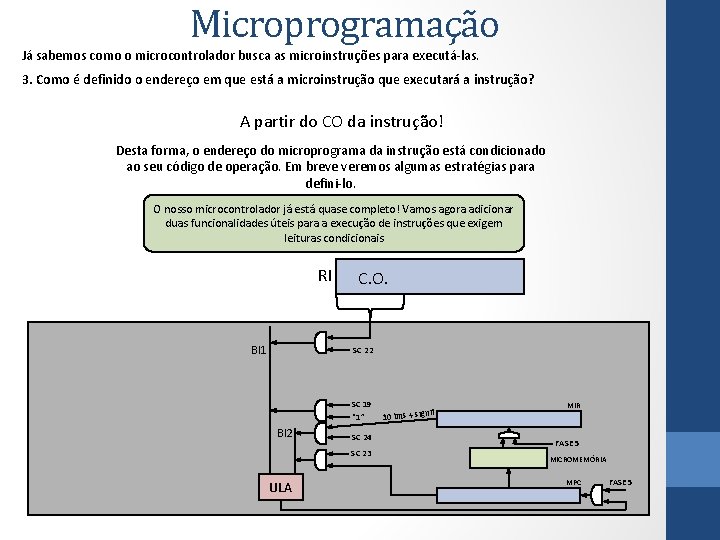

Microprogramação Já sabemos como o microcontrolador busca as microinstruções para executá-las. 3. Como é definido o endereço em que está a microinstrução que executará a instrução? A partir do CO da instrução! Desta forma, o endereço do microprograma da instrução está condicionado ao seu código de operação. Em breve veremos algumas estratégias para defini-lo. O nosso microcontrolador já está quase completo! Vamos agora adicionar duas funcionalidades úteis para a execução de instruções que exigem leituras condicionais RI BI 1 C. O. SC 22 SC 19 “ 1” BI 2 SC 24 SC 23 ULA . if 10 bits + sign MIR FASE 5 MICROMEMÓRIA MPC FASE 5

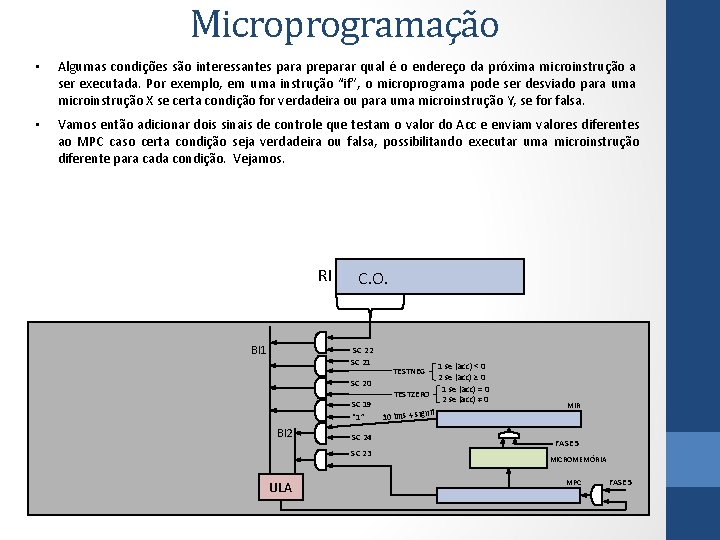

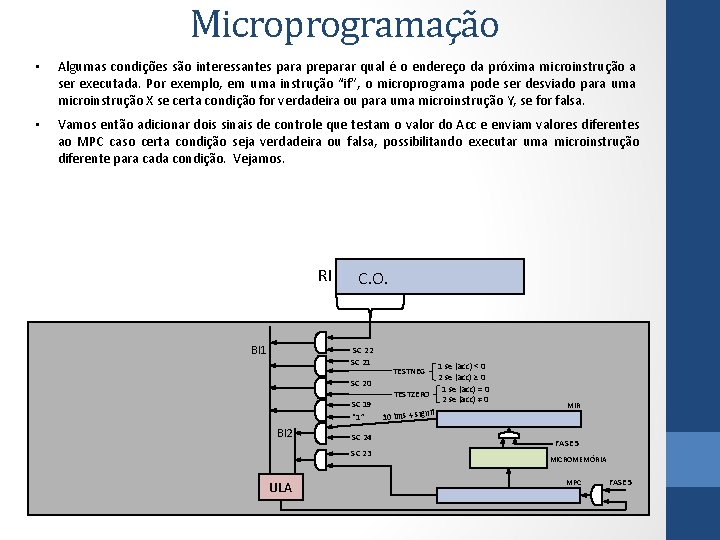

Microprogramação • Algumas condições são interessantes para preparar qual é o endereço da próxima microinstrução a ser executada. Por exemplo, em uma instrução “if”, o microprograma pode ser desviado para uma microinstrução X se certa condição for verdadeira ou para uma microinstrução Y, se for falsa. • Vamos então adicionar dois sinais de controle que testam o valor do Acc e enviam valores diferentes ao MPC caso certa condição seja verdadeira ou falsa, possibilitando executar uma microinstrução diferente para cada condição. Vejamos. RI BI 1 C. O. SC 22 SC 21 SC 20 SC 19 “ 1” BI 2 SC 24 SC 23 ULA 1 se (acc) < 0 2 se (acc) ≥ 0 1 se (acc) = 0 TESTZERO 2 se (acc) ≠ 0. if 10 bits + sign TESTNEG MIR FASE 5 MICROMEMÓRIA MPC FASE 5

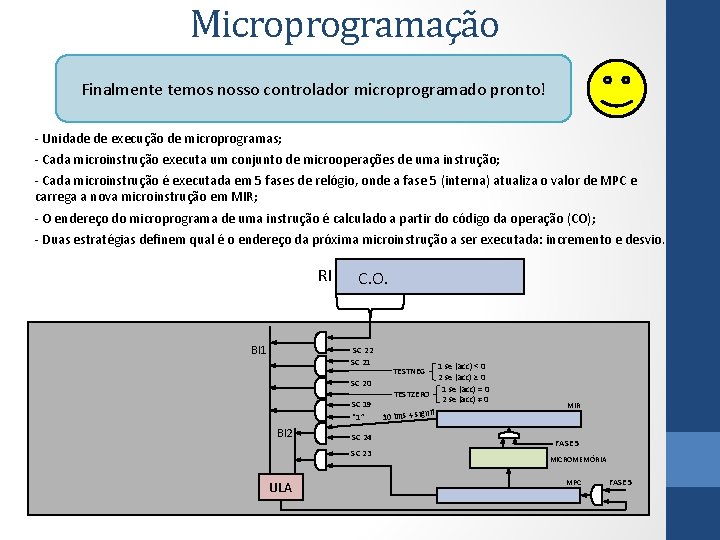

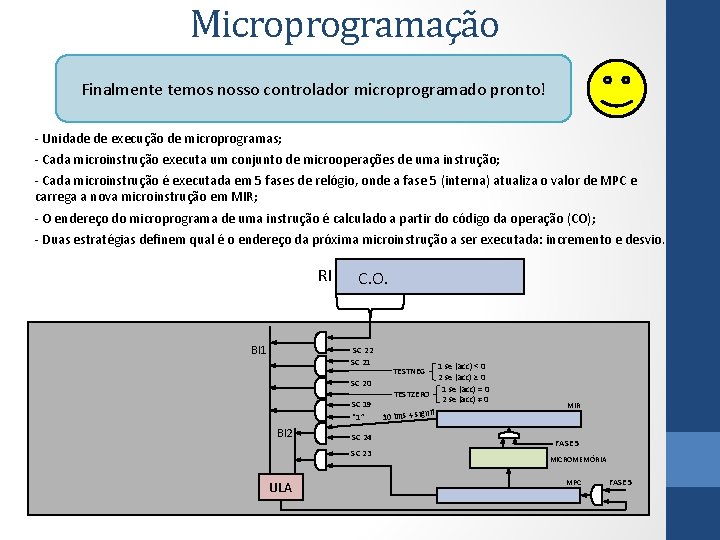

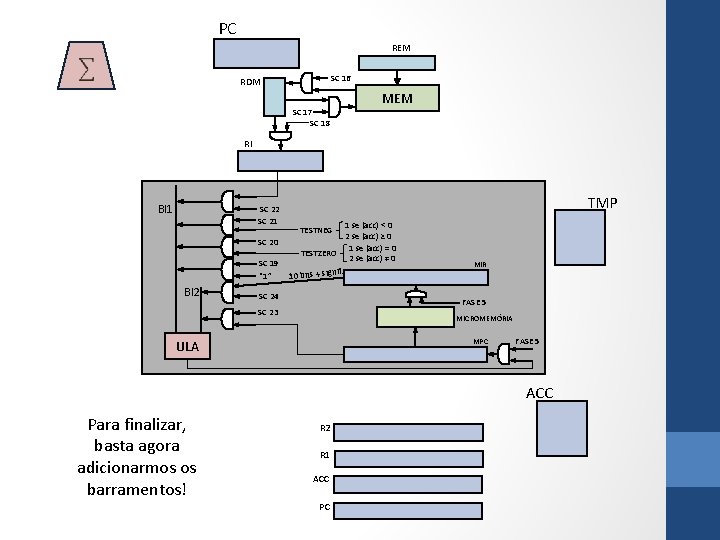

Microprogramação Finalmente temos nosso controlador microprogramado pronto! - Unidade de execução de microprogramas; - Cada microinstrução executa um conjunto de microoperações de uma instrução; - Cada microinstrução é executada em 5 fases de relógio, onde a fase 5 (interna) atualiza o valor de MPC e carrega a nova microinstrução em MIR; - O endereço do microprograma de uma instrução é calculado a partir do código da operação (CO); - Duas estratégias definem qual é o endereço da próxima microinstrução a ser executada: incremento e desvio. RI BI 1 C. O. SC 22 SC 21 SC 20 SC 19 “ 1” BI 2 SC 24 SC 23 ULA 1 se (acc) < 0 2 se (acc) ≥ 0 1 se (acc) = 0 TESTZERO 2 se (acc) ≠ 0. if 10 bits + sign TESTNEG MIR FASE 5 MICROMEMÓRIA MPC FASE 5

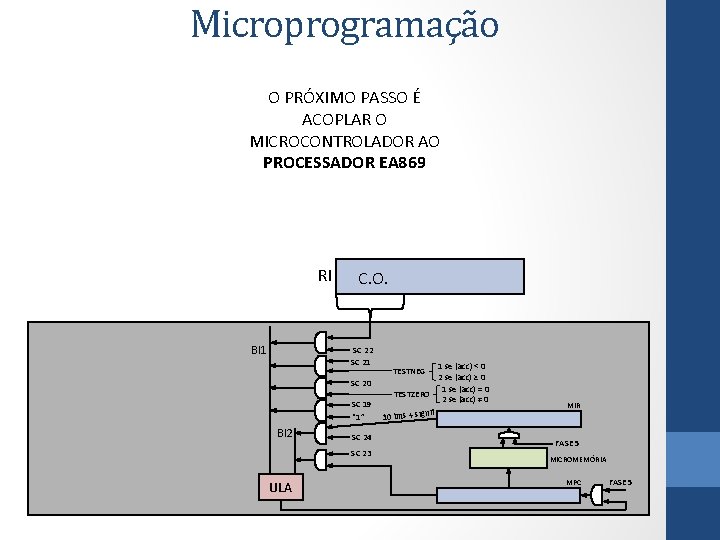

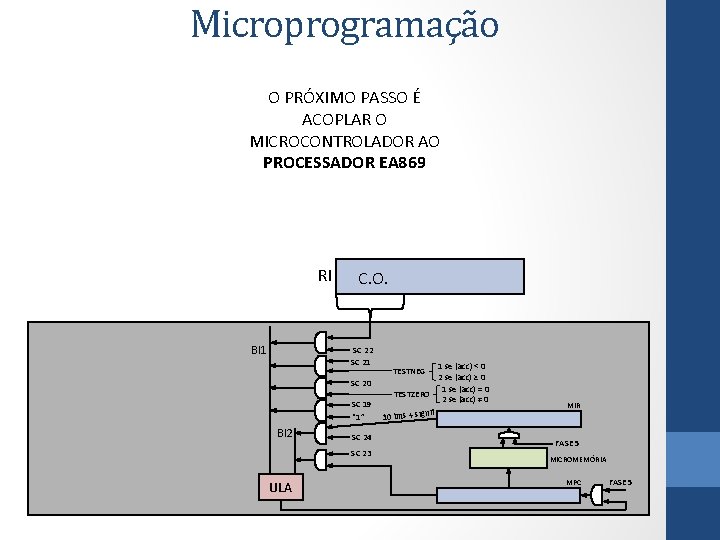

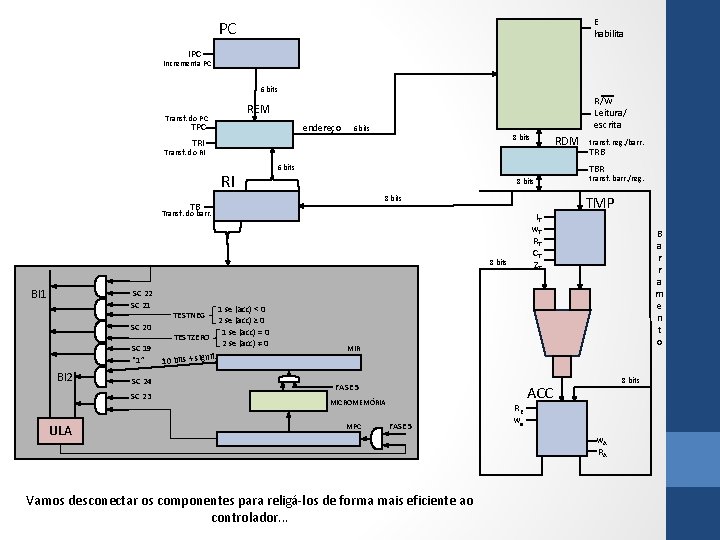

Microprogramação O PRÓXIMO PASSO É ACOPLAR O MICROCONTROLADOR AO PROCESSADOR EA 869 RI BI 1 C. O. SC 22 SC 21 SC 20 SC 19 “ 1” BI 2 SC 24 SC 23 ULA 1 se (acc) < 0 2 se (acc) ≥ 0 1 se (acc) = 0 TESTZERO 2 se (acc) ≠ 0. if 10 bits + sign TESTNEG MIR FASE 5 MICROMEMÓRIA MPC FASE 5

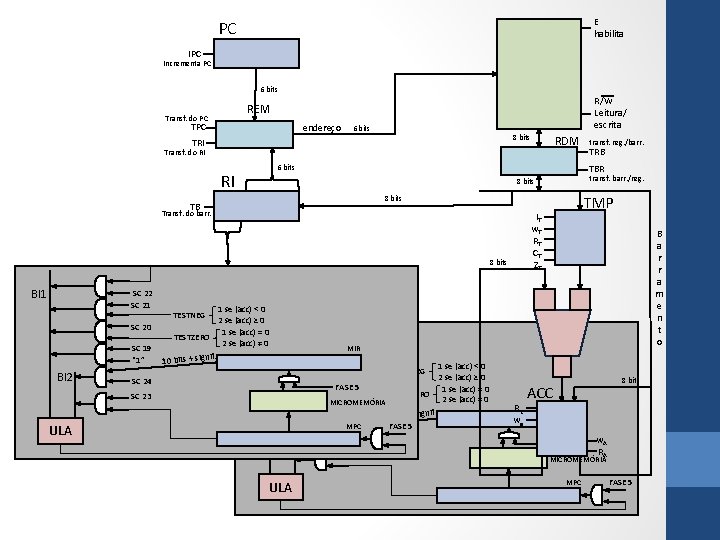

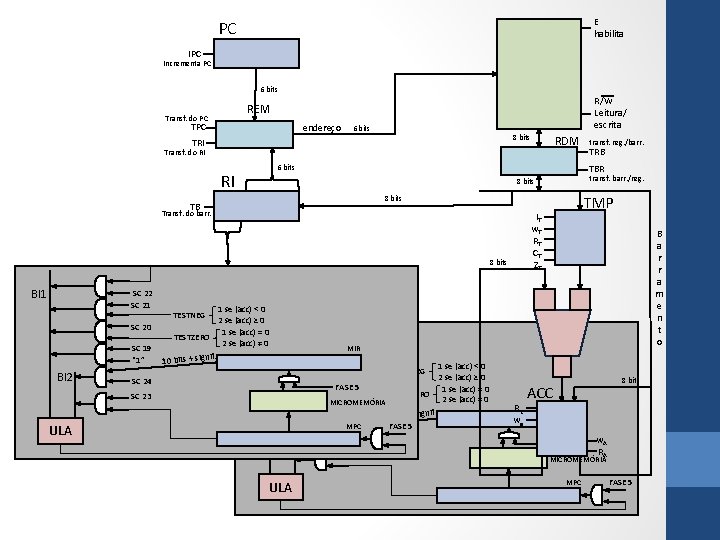

E habilita PC Incrementa PC 6 bits R/W Leitura/ escrita REM Transf. do PC TPC endereço 6 bits 8 bits TRI RDM Transf. do RI RI 6 bits SC 19 “ 1” BI 2 IT w. T RT CT ZT 1 se (acc) < 0 2 se (acc) ≥ 0 1 se (acc) = 0 TESTZERO 2 se (acc) ≠ 0 BI 1. if 10 bits + sign B a r r a m e n t o TESTNEG MIR SC 22 SC 21 SC 24 SC 23 ULA TMP 8 bits SC 20 transf. barr. /reg. 8 bits Transf. do barr. SC 22 SC 21 TRB TBR TB BI 1 transf. reg. /barr. BI 2 1 se (acc) < 0 2 se (acc) ≥ 0 SC 20 FASE 5 1 se (acc) = 0 TESTZERO 2 se (acc) ≠ 0 MICROMEMÓRIA SC 19. if “ 1” 10 bits + sign FASE 5 MPC SC 24 SC 23 ULA TESTNEG RE we ACC 8 bits MIR FASE 5 w. A RA MICROMEMÓRIA MPC FASE 5

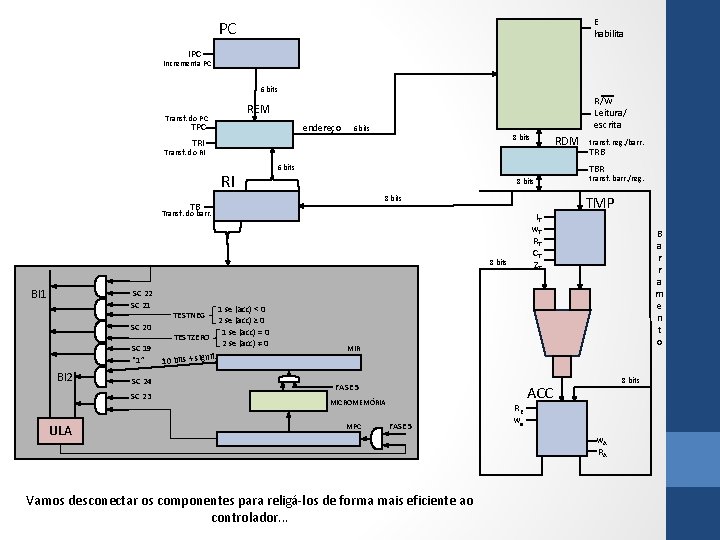

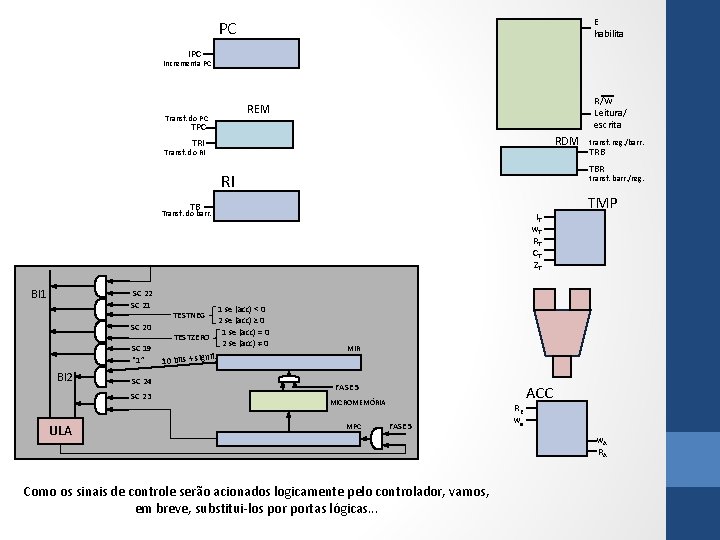

E habilita PC Incrementa PC 6 bits R/W Leitura/ escrita REM Transf. do PC TPC endereço 6 bits 8 bits TRI RDM Transf. do RI RI 6 bits 8 bits Transf. do barr. IT w. T RT CT ZT 8 bits SC 22 SC 21 SC 20 SC 19 “ 1” BI 2 SC 24 SC 23 ULA 1 se (acc) < 0 2 se (acc) ≥ 0 1 se (acc) = 0 TESTZERO 2 se (acc) ≠ 0. if 10 bits + sign TRB TBR TB BI 1 transf. reg. /barr. transf. barr. /reg. TMP B a r r a m e n t o TESTNEG MIR FASE 5 MICROMEMÓRIA MPC FASE 5 Vamos desconectar os componentes para religá-los de forma mais eficiente ao controlador. . . RE we 8 bits ACC w. A RA

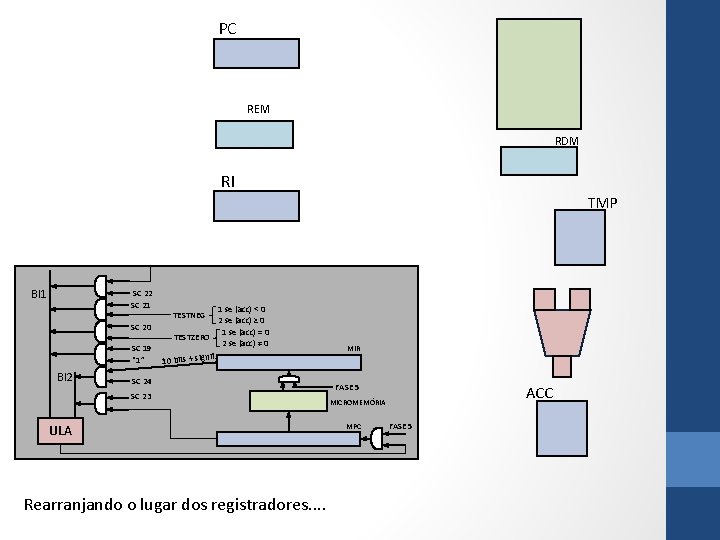

E habilita PC Incrementa PC R/W Leitura/ escrita REM Transf. do PC TPC RDM TRI Transf. do RI transf. barr. /reg. TB Transf. do barr. SC 22 SC 21 SC 20 SC 19 “ 1” BI 2 SC 24 SC 23 ULA 1 se (acc) < 0 2 se (acc) ≥ 0 1 se (acc) = 0 TESTZERO 2 se (acc) ≠ 0. if 10 bits + sign TRB TBR RI BI 1 transf. reg. /barr. IT w. T RT CT ZT TMP TESTNEG MIR FASE 5 MICROMEMÓRIA MPC FASE 5 Como os sinais de controle serão acionados logicamente pelo controlador, vamos, em breve, substitui-los portas lógicas. . . RE we ACC w. A RA

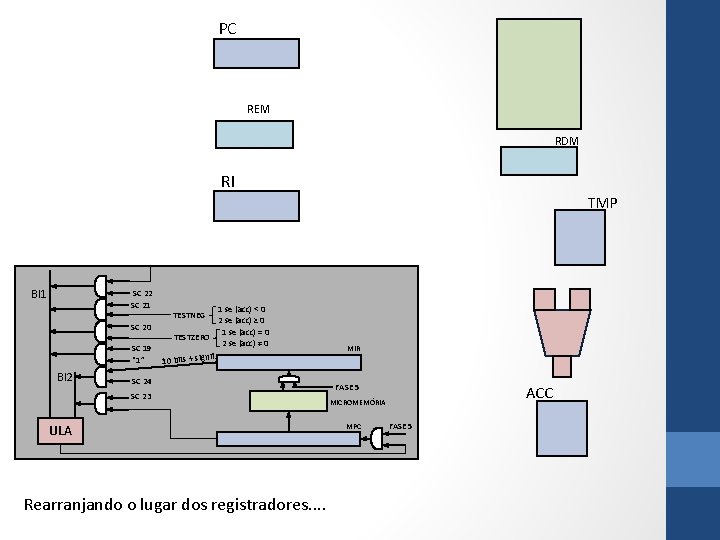

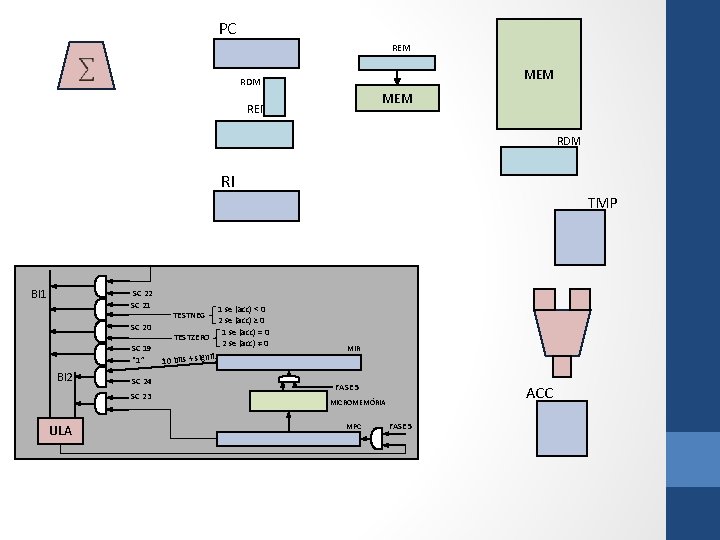

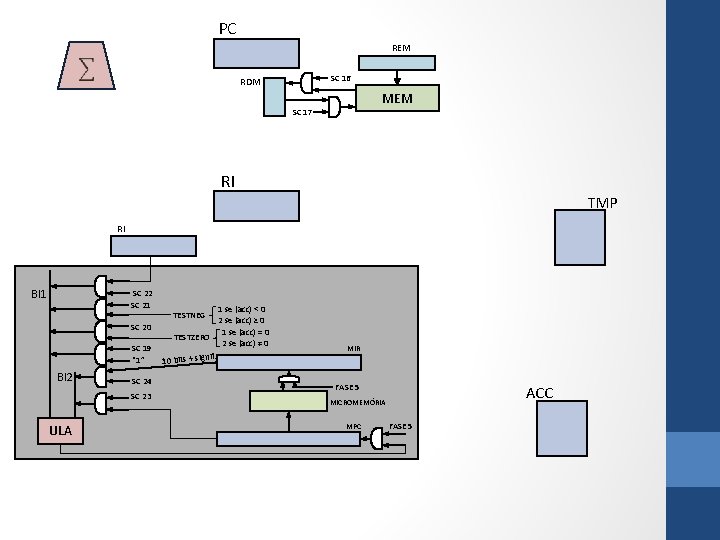

PC REM RDM RI TMP BI 1 SC 22 SC 21 SC 20 SC 19 “ 1” BI 2 1 se (acc) < 0 2 se (acc) ≥ 0 1 se (acc) = 0 TESTZERO 2 se (acc) ≠ 0. if 10 bits + sign TESTNEG SC 24 SC 23 ULA Rearranjando o lugar dos registradores. . MIR FASE 5 ACC MICROMEMÓRIA MPC FASE 5

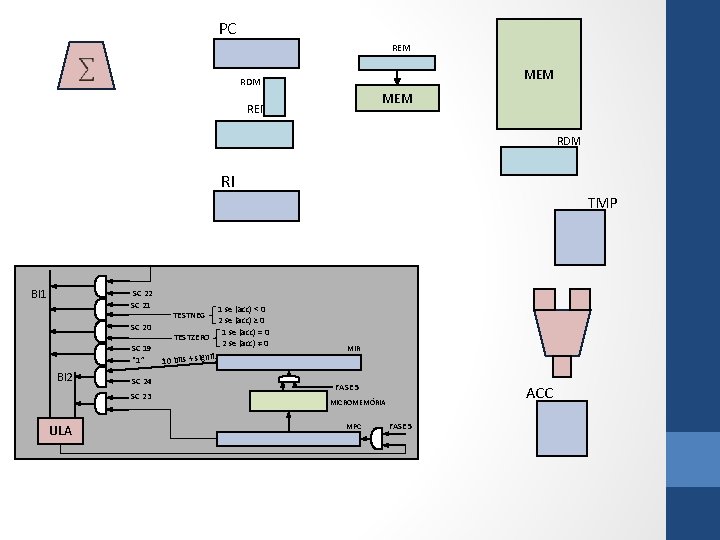

PC REM MEM RDM RI TMP BI 1 SC 22 SC 21 SC 20 SC 19 “ 1” BI 2 SC 24 SC 23 ULA 1 se (acc) < 0 2 se (acc) ≥ 0 1 se (acc) = 0 TESTZERO 2 se (acc) ≠ 0. if 10 bits + sign TESTNEG MIR FASE 5 ACC MICROMEMÓRIA MPC FASE 5

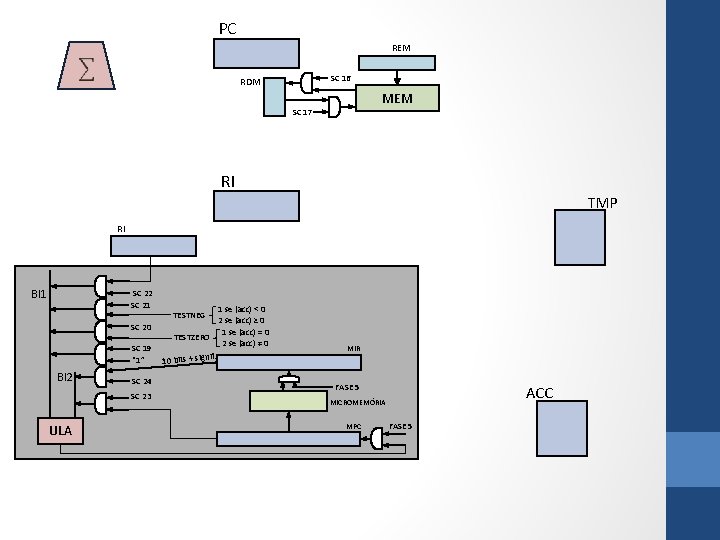

PC REM SC 16 RDM MEM SC 17 RI TMP RI BI 1 SC 22 SC 21 SC 20 SC 19 “ 1” BI 2 SC 24 SC 23 ULA 1 se (acc) < 0 2 se (acc) ≥ 0 1 se (acc) = 0 TESTZERO 2 se (acc) ≠ 0. if 10 bits + sign TESTNEG MIR FASE 5 ACC MICROMEMÓRIA MPC FASE 5

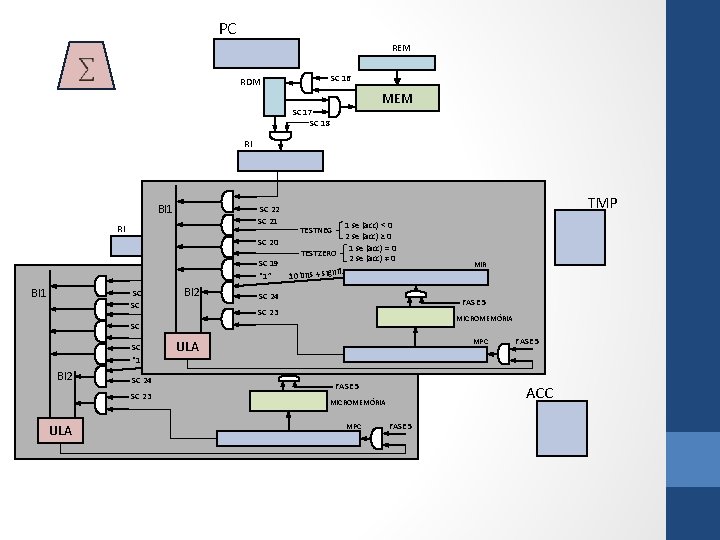

PC REM SC 16 RDM MEM SC 17 SC 18 RI BI 1 SC 22 SC 21 RI SC 20 SC 19 “ 1” BI 1 SC 22 SC 21 SC 20 SC 19 “ 1” BI 2 SC 24 SC 23 ULA TMP 1 se (acc) < 0 2 se (acc) ≥ 0 1 se (acc) = 0 TESTZERO 2 se (acc) ≠ 0. if gn si 10 bits + TESTNEG BI 2 SC 24 1 se (acc) < 0 SC 23 TESTNEG 2 se (acc) ≥ 0 1 se (acc) = 0 TESTZERO 2 se (acc) ≠ 0 ULA. if gn 10 bits + si MIR FASE 5 MICROMEMÓRIA MPC MIR FASE 5 ACC MICROMEMÓRIA MPC FASE 5

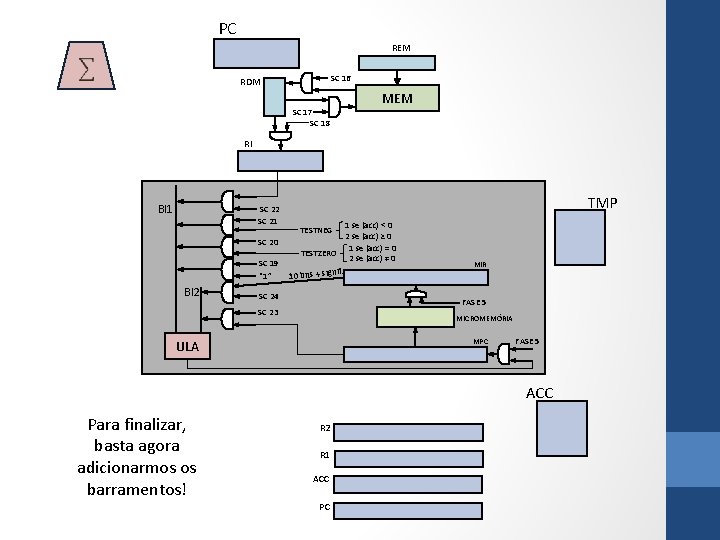

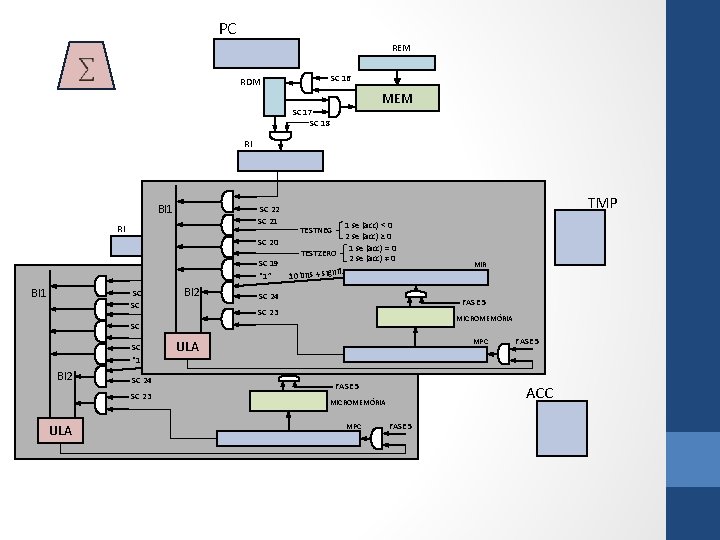

PC REM SC 16 RDM SC 17 SC 18 MEM RI BI 1 SC 22 SC 21 SC 20 SC 19 “ 1” BI 2 TMP 1 se (acc) < 0 2 se (acc) ≥ 0 1 se (acc) = 0 TESTZERO 2 se (acc) ≠ 0. if gn si 10 bits + TESTNEG SC 24 MIR FASE 5 SC 23 MICROMEMÓRIA MPC ULA FASE 5 ACC Para finalizar, basta agora adicionarmos os barramentos! R 2 R 1 ACC PC

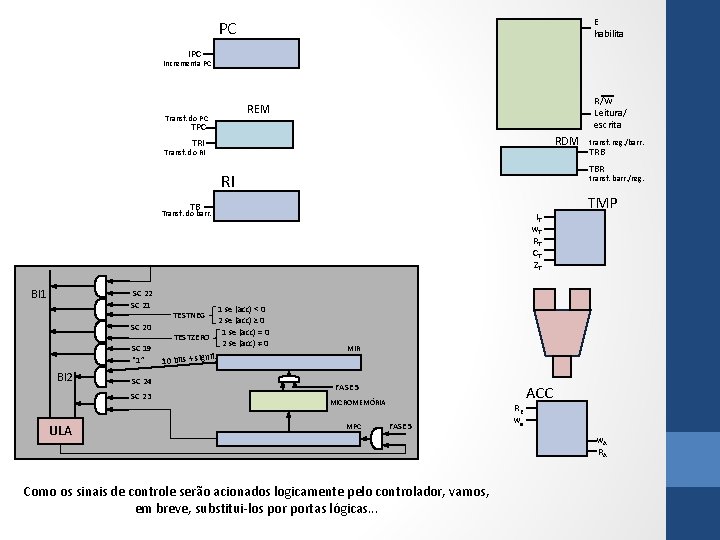

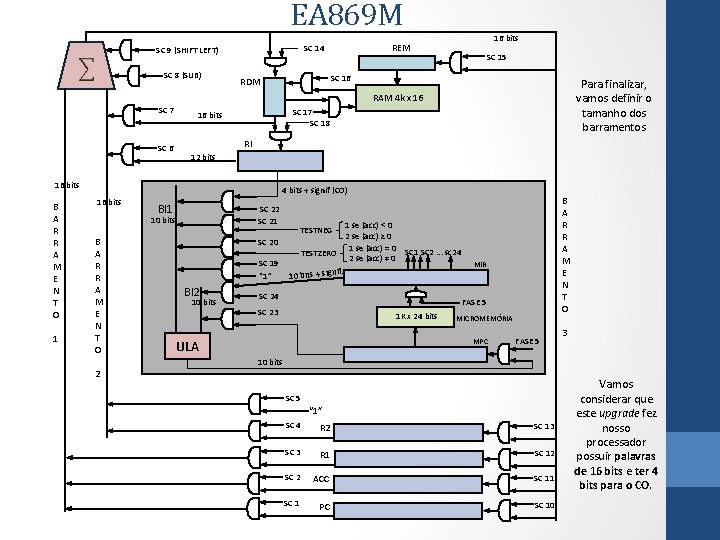

EA 869 M SC 8 (SUB) SC 7 SC 6 SC 15 SC 16 RDM Para finalizar, vamos definir o tamanho dos barramentos RAM 4 k x 16 SC 17 SC 18 16 bits RI 12 bits 16 bits B A R R A M E N T O 1 16 bits REM SC 14 SC 9 (SHIFT LEFT) 4 bits + signif (CO) 16 bits BI 1 SC 22 SC 21 10 bits B A R R A M E N T O 2 SC 20 SC 19 “ 1” BI 2 10 bits 1 se (acc) < 0 2 se (acc) ≥ 0 1 se (acc) = 0 SC 1 SC 2. . . sc 24 TESTZERO 2 se (acc) ≠ 0. if gn si 10 bits + TESTNEG SC 24 MIR FASE 5 SC 23 1 K x 24 bits MICROMEMÓRIA MPC ULA FASE 5 B A R R A M E N T O 3 10 bits SC 5 “ 1” SC 4 R 2 SC 13 SC 3 R 1 SC 12 SC 2 ACC SC 11 SC 1 PC SC 10 Vamos considerar que este upgrade fez nosso processador possuir palavras de 16 bits e ter 4 bits para o CO.

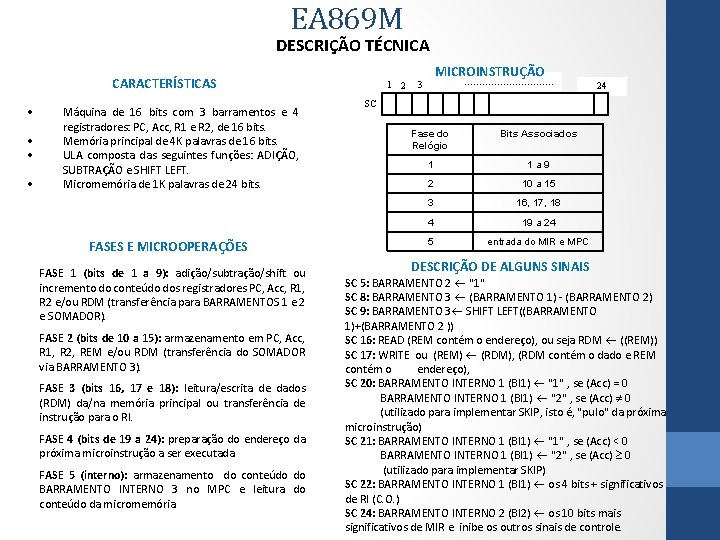

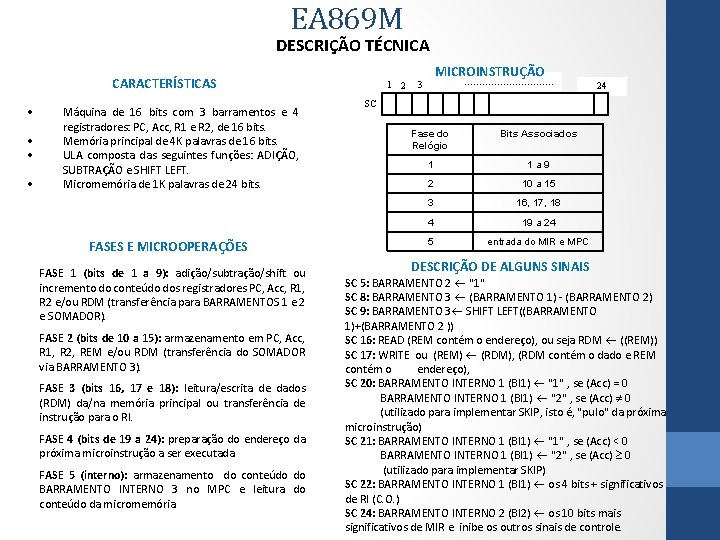

EA 869 M DESCRIÇÃO TÉCNICA CARACTERÍSTICAS • • Máquina de 16 bits com 3 barramentos e 4 registradores: PC, Acc, R 1 e R 2, de 16 bits. Memória principal de 4 K palavras de 16 bits. ULA composta das seguintes funções: ADIÇÃO, SUBTRAÇÃO e SHIFT LEFT. Micromemória de 1 K palavras de 24 bits. FASES E MICROOPERAÇÕES FASE 1 (bits de 1 a 9): adição/subtração/shift ou incremento do conteúdo dos registradores PC, Acc, R 1, R 2 e/ou RDM (transferência para BARRAMENTOS 1 e 2 e SOMADOR). FASE 2 (bits de 10 a 15): armazenamento em PC, Acc, R 1, R 2, REM e/ou RDM (transferência do SOMADOR via BARRAMENTO 3). FASE 3 (bits 16, 17 e 18): leitura/escrita de dados (RDM) da/na memória principal ou transferência de instrução para o RI. FASE 4 (bits de 19 a 24): preparação do endereço da próxima microinstrução a ser executada. FASE 5 (interno): armazenamento do conteúdo do BARRAMENTO INTERNO 3 no MPC e leitura do conteúdo da micromemória. 1 2 MICROINSTRUÇÃO . . . . 3 24 SC Fase do Relógio Bits Associados 1 1 a 9 2 10 a 15 3 16, 17, 18 4 19 a 24 5 entrada do MIR e MPC DESCRIÇÃO DE ALGUNS SINAIS SC 5: BARRAMENTO 2 "1" SC 8: BARRAMENTO 3 (BARRAMENTO 1) - (BARRAMENTO 2) SC 9: BARRAMENTO 3 SHIFT LEFT((BARRAMENTO 1)+(BARRAMENTO 2 )) SC 16: READ (REM contém o endereço), ou seja RDM ((REM)) SC 17: WRITE ou (REM) (RDM), (RDM contém o dado e REM contém o endereço), SC 20: BARRAMENTO INTERNO 1 (BI 1) "1" , se (Acc) = 0 BARRAMENTO INTERNO 1 (BI 1) "2" , se (Acc) 0 (utilizado para implementar SKIP, isto é, "pulo" da próxima microinstrução) SC 21: BARRAMENTO INTERNO 1 (BI 1) "1" , se (Acc) < 0 BARRAMENTO INTERNO 1 (BI 1) "2" , se (Acc) 0 (utilizado para implementar SKIP) SC 22: BARRAMENTO INTERNO 1 (BI 1) os 4 bits + significativos de RI (C. O. ) SC 24: BARRAMENTO INTERNO 2 (BI 2) os 10 bits mais significativos de MIR e inibe os outros sinais de controle.

EA 869 M Agora que projetamos uma arquitetura de um computador microcontrolado, falta conhecermos seu funcionamento. O que este computador precisa para funcionar adequadamente? Ter um microprograma na micromemória que faça adequadamente todas as tarefas de um computador: busca e execução das instruções. Vamos aprender como se programa a micromemória! Qual linguagem utilizaremos? Linguagem de Máquina

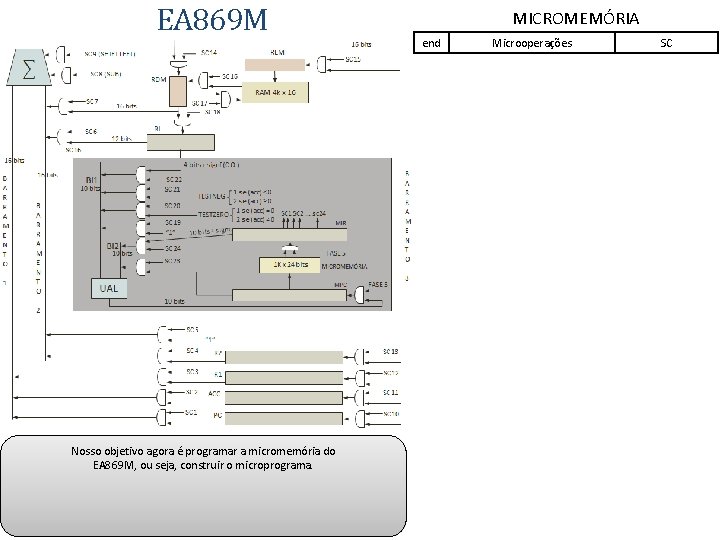

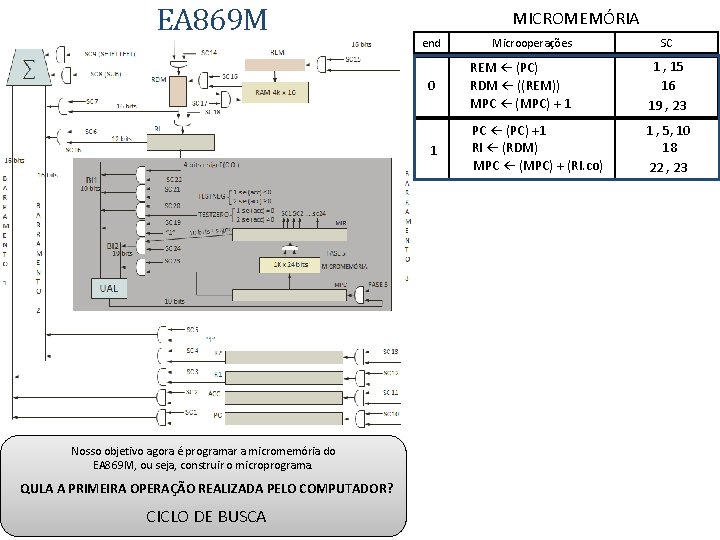

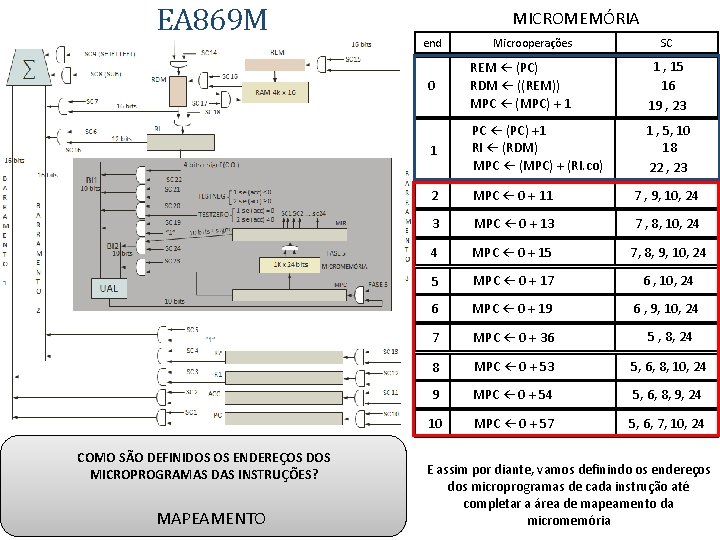

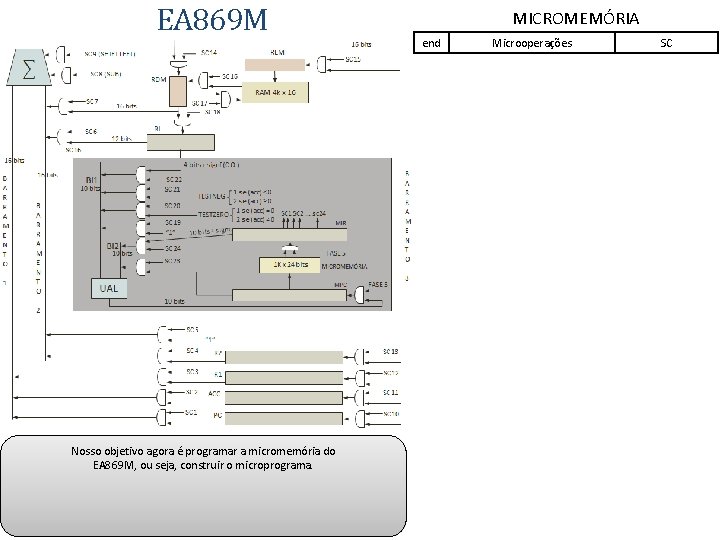

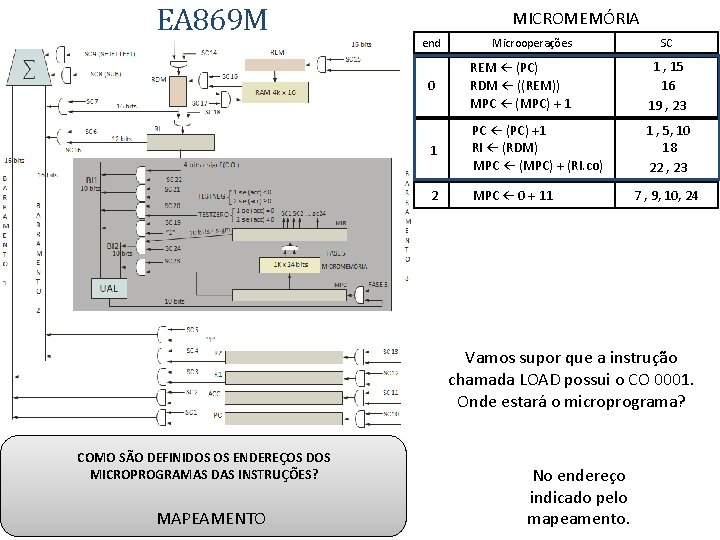

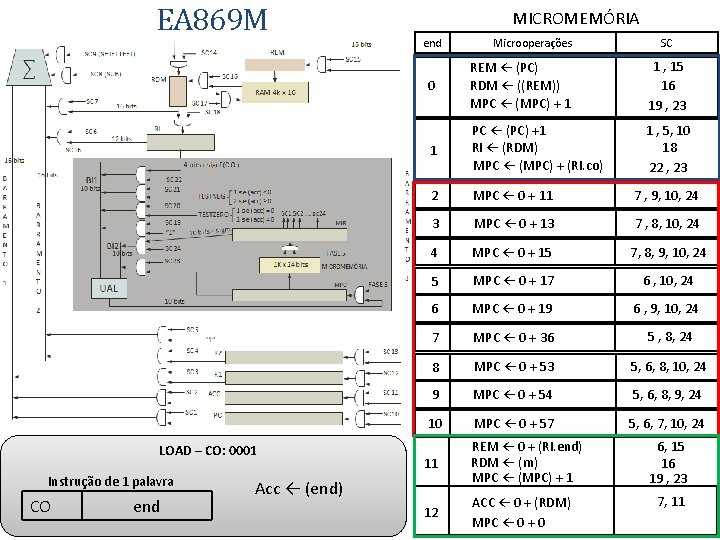

EA 869 M Nosso objetivo agora é programar a micromemória do EA 869 M, ou seja, construir o microprograma. MICROMEMÓRIA end Microoperações SC

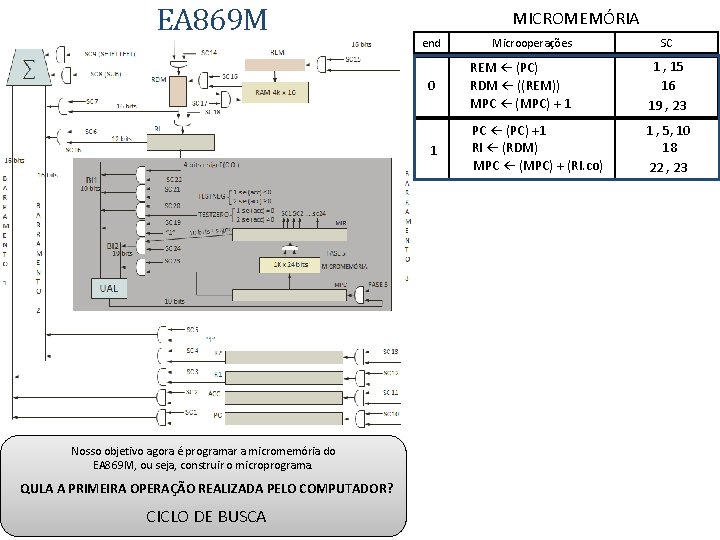

EA 869 M Nosso objetivo agora é programar a micromemória do EA 869 M, ou seja, construir o microprograma. QULA A PRIMEIRA OPERAÇÃO REALIZADA PELO COMPUTADOR? CICLO DE BUSCA MICROMEMÓRIA end Microoperações SC 0 REM ← (PC) RDM ← ((REM)) MPC ← (MPC) + 1 1 , 15 16 19 , 23 1 PC ← (PC) +1 RI ← (RDM) MPC ← (MPC) + (RI. co) 1 , 5, 10 18 22 , 23

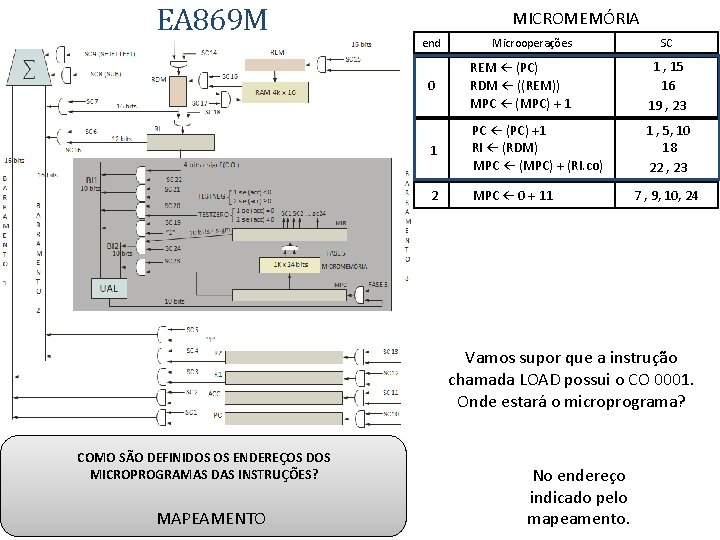

EA 869 M MICROMEMÓRIA end Microoperações SC 0 REM ← (PC) RDM ← ((REM)) MPC ← (MPC) + 1 1 , 15 16 19 , 23 1 PC ← (PC) +1 RI ← (RDM) MPC ← (MPC) + (RI. co) 1 , 5, 10 18 22 , 23 2 MPC ← 0 + 11 7 , 9, 10, 24 Vamos supor que a instrução chamada LOAD possui o CO 0001. Onde estará o microprograma? COMO SÃO DEFINIDOS OS ENDEREÇOS DOS MICROPROGRAMAS DAS INSTRUÇÕES? MAPEAMENTO No endereço indicado pelo mapeamento.

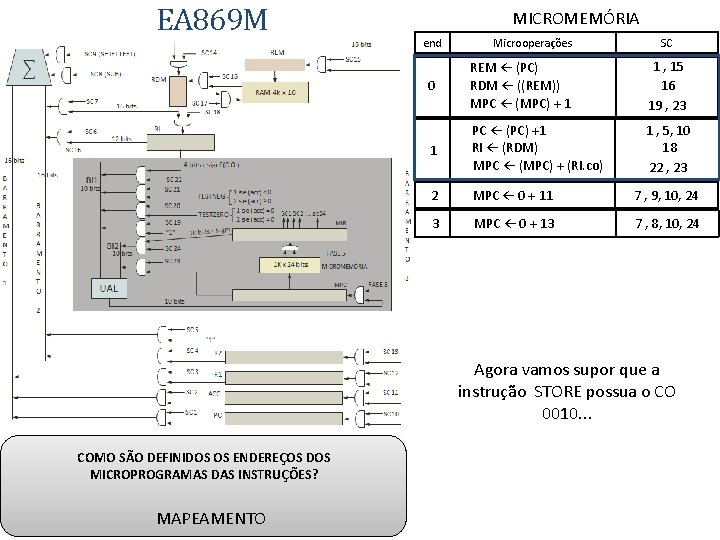

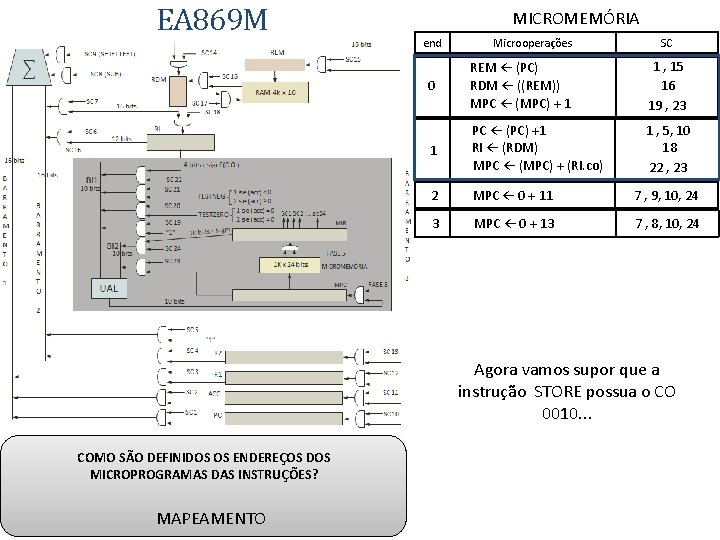

EA 869 M MICROMEMÓRIA end Microoperações SC 0 REM ← (PC) RDM ← ((REM)) MPC ← (MPC) + 1 1 , 15 16 19 , 23 1 PC ← (PC) +1 RI ← (RDM) MPC ← (MPC) + (RI. co) 1 , 5, 10 18 22 , 23 2 MPC ← 0 + 11 7 , 9, 10, 24 3 MPC ← 0 + 13 7 , 8, 10, 24 Agora vamos supor que a instrução STORE possua o CO 0010. . . COMO SÃO DEFINIDOS OS ENDEREÇOS DOS MICROPROGRAMAS DAS INSTRUÇÕES? MAPEAMENTO

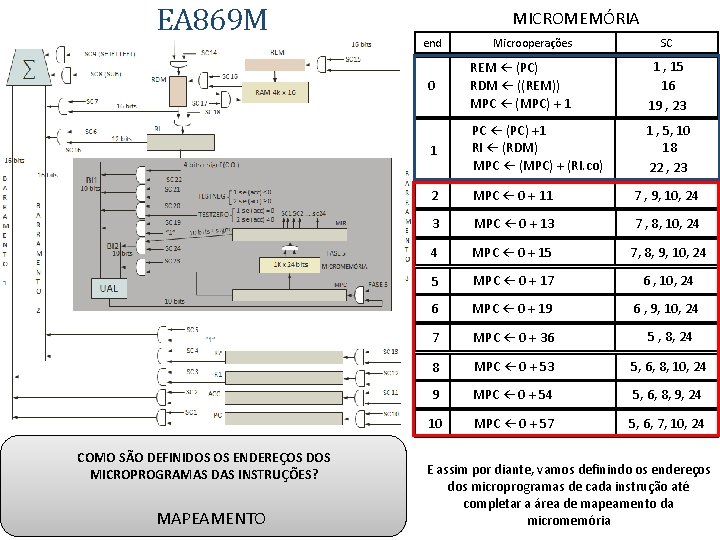

EA 869 M COMO SÃO DEFINIDOS OS ENDEREÇOS DOS MICROPROGRAMAS DAS INSTRUÇÕES? MAPEAMENTO MICROMEMÓRIA end Microoperações SC 0 REM ← (PC) RDM ← ((REM)) MPC ← (MPC) + 1 1 , 15 16 19 , 23 1 PC ← (PC) +1 RI ← (RDM) MPC ← (MPC) + (RI. co) 1 , 5, 10 18 22 , 23 2 MPC ← 0 + 11 7 , 9, 10, 24 3 MPC ← 0 + 13 7 , 8, 10, 24 4 MPC ← 0 + 15 7, 8, 9, 10, 24 5 MPC ← 0 + 17 6 , 10, 24 6 MPC ← 0 + 19 6 , 9, 10, 24 7 MPC ← 0 + 36 5 , 8, 24 8 MPC ← 0 + 53 5, 6, 8, 10, 24 9 MPC ← 0 + 54 5, 6, 8, 9, 24 10 MPC ← 0 + 57 5, 6, 7, 10, 24 E assim por diante, vamos definindo os endereços dos microprogramas de cada instrução até completar a área de mapeamento da micromemória

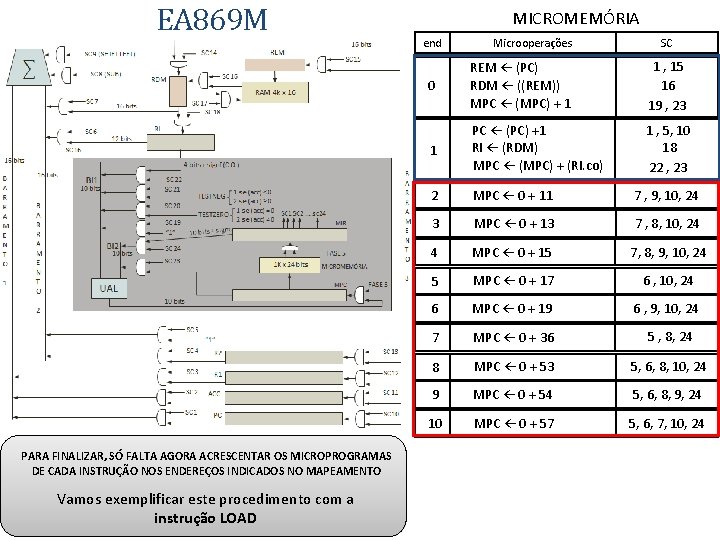

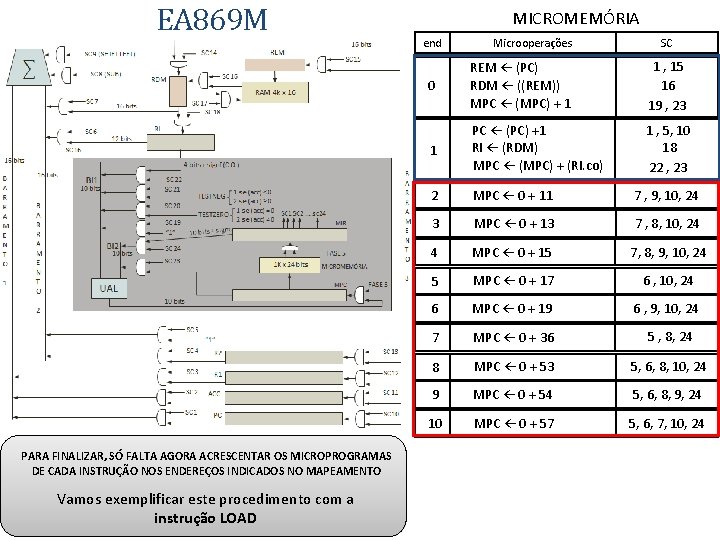

EA 869 M PARA FINALIZAR, SÓ FALTA AGORA ACRESCENTAR OS MICROPROGRAMAS DE CADA INSTRUÇÃO NOS ENDEREÇOS INDICADOS NO MAPEAMENTO Vamos exemplificar este procedimento com a instrução LOAD MICROMEMÓRIA end Microoperações SC 0 REM ← (PC) RDM ← ((REM)) MPC ← (MPC) + 1 1 , 15 16 19 , 23 1 PC ← (PC) +1 RI ← (RDM) MPC ← (MPC) + (RI. co) 1 , 5, 10 18 22 , 23 2 MPC ← 0 + 11 7 , 9, 10, 24 3 MPC ← 0 + 13 7 , 8, 10, 24 4 MPC ← 0 + 15 7, 8, 9, 10, 24 5 MPC ← 0 + 17 6 , 10, 24 6 MPC ← 0 + 19 6 , 9, 10, 24 7 MPC ← 0 + 36 5 , 8, 24 8 MPC ← 0 + 53 5, 6, 8, 10, 24 9 MPC ← 0 + 54 5, 6, 8, 9, 24 10 MPC ← 0 + 57 5, 6, 7, 10, 24

EA 869 M LOAD – CO: 0001 Instrução de 1 palavra CO end MICROMEMÓRIA end Microoperações SC 0 REM ← (PC) RDM ← ((REM)) MPC ← (MPC) + 1 1 , 15 16 19 , 23 1 PC ← (PC) +1 RI ← (RDM) MPC ← (MPC) + (RI. co) 1 , 5, 10 18 22 , 23 2 MPC ← 0 + 11 7 , 9, 10, 24 3 MPC ← 0 + 13 7 , 8, 10, 24 4 MPC ← 0 + 15 7, 8, 9, 10, 24 5 MPC ← 0 + 17 6 , 10, 24 6 MPC ← 0 + 19 6 , 9, 10, 24 7 MPC ← 0 + 36 5 , 8, 24 8 MPC ← 0 + 53 5, 6, 8, 10, 24 9 MPC ← 0 + 54 5, 6, 8, 9, 24 10 MPC ← 0 + 57 5, 6, 7, 10, 24 11 REM ← 0 + (RI. end) RDM ← (m) MPC ← (MPC) + 1 12 ACC ← 0 + (RDM) MPC ← 0 + 0 Acc ← (end) 6, 15 16 19 , 23 7, 11

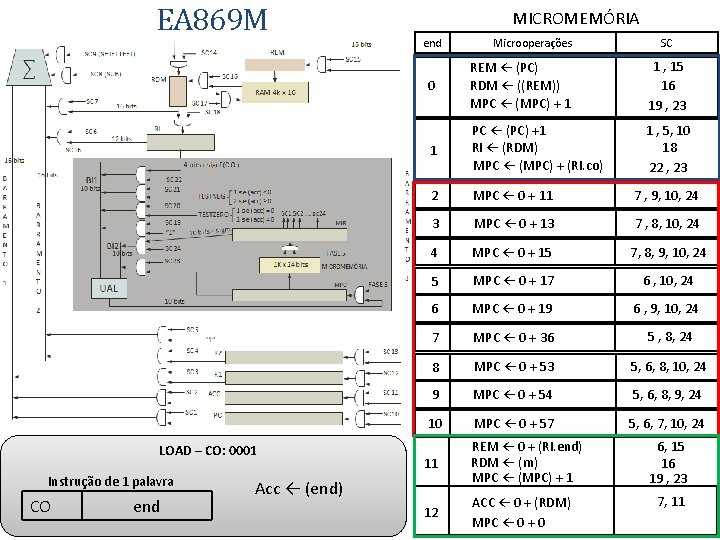

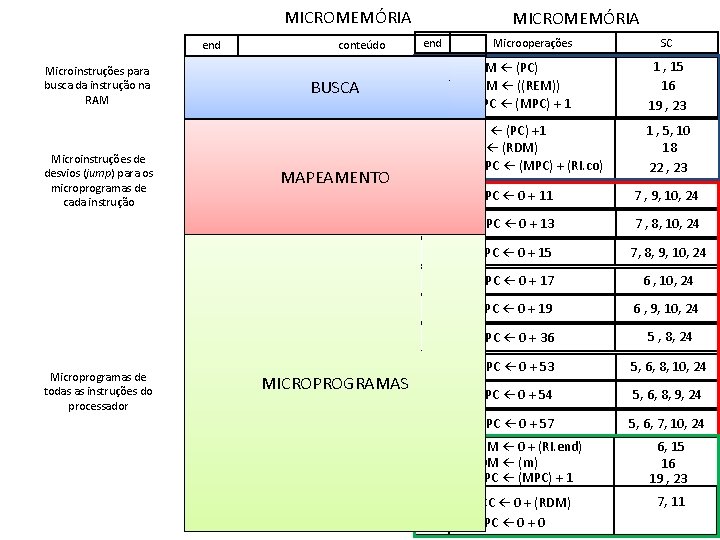

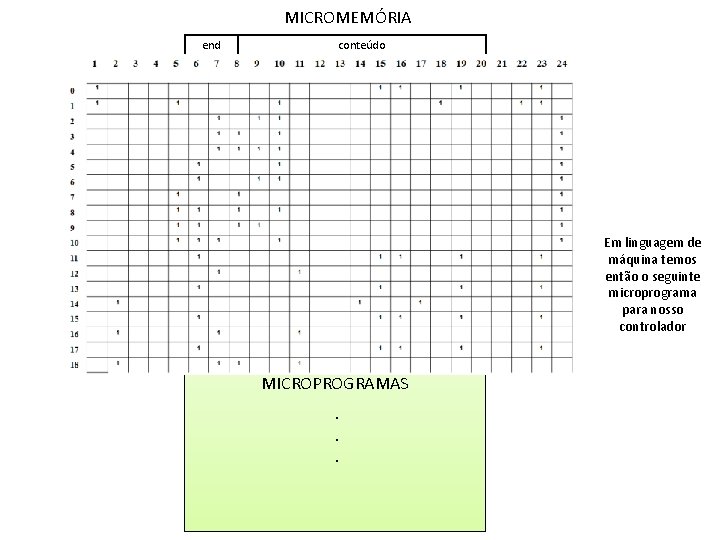

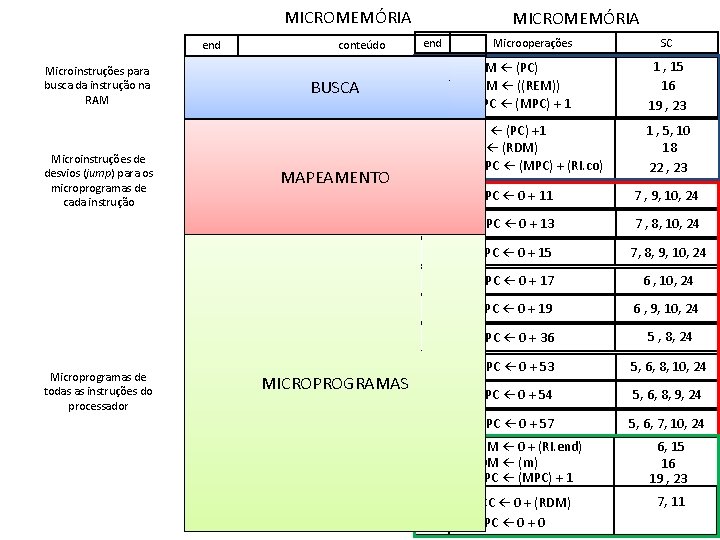

MICROMEMÓRIA end Microinstruções para busca da instrução na RAM Microinstruções de desvios (jump) para os microprogramas de cada instrução Microprogramas de todas as instruções do processador conteúdo BUSCA MAPEAMENTO MICROPROGRAMAS MICROMEMÓRIA end Microoperações SC 0 REM ← (PC) RDM ← ((REM)) MPC ← (MPC) + 1 1 , 15 16 19 , 23 1 PC ← (PC) +1 RI ← (RDM) MPC ← (MPC) + (RI. co) 1 , 5, 10 18 22 , 23 2 MPC ← 0 + 11 7 , 9, 10, 24 3 MPC ← 0 + 13 7 , 8, 10, 24 4 MPC ← 0 + 15 7, 8, 9, 10, 24 5 MPC ← 0 + 17 6 , 10, 24 6 MPC ← 0 + 19 6 , 9, 10, 24 7 MPC ← 0 + 36 5 , 8, 24 8 MPC ← 0 + 53 5, 6, 8, 10, 24 9 MPC ← 0 + 54 5, 6, 8, 9, 24 10 MPC ← 0 + 57 5, 6, 7, 10, 24 11 REM ← 0 + (RI. end) RDM ← (m) MPC ← (MPC) + 1 12 ACC ← 0 + (RDM) MPC ← 0 + 0 6, 15 16 19 , 23 7, 11

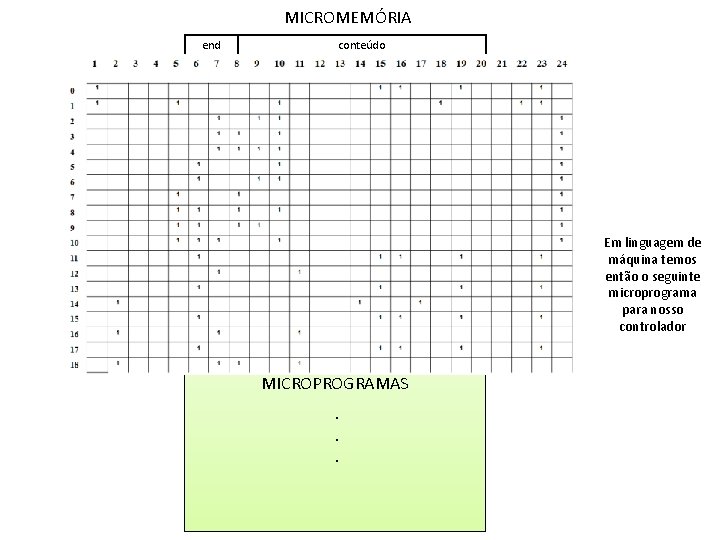

MICROMEMÓRIA end conteúdo BUSCA MAPEAMENTO Em linguagem de máquina temos então o seguinte microprograma para nosso controlador MICROPROGRAMAS. . .

Conclusões • A microprogramação nada mais é do que uma técnica de implementação do controlador de um processador. • Esta técnica consiste em replicar a ideia de programa armazenado, mas agora no nível do controlador. • Desta forma, o controle das microoperações ficará a cargo de um microprograma, alocado na micromemória. • Um microprograma é composto por microinstruções, as quais podem ser classificadas como horizontais (os bits representam os sinais de controle) e polifásicas (uma microinstrução é executada em diversas fases do relógio). • Um microprograma completo possui três áreas: busca (microinstruções para leitura da instrução), mapeamento (microinstruções de desvio para o endereço do microprograma da instrução) e os microprogramas de cada instrução. • A vantagem do uso da microprogramação é a economia de memória RAM (já que pode possuir mais instruções complexas) e a flexibilidade de criar instruções. • Já as desvantagens são as possíveis perdas de velocidade, o fato de ser antieconômico para sistemas simples e a dificuldade de achar erros nos microprogramas. “Lembro do exato momento em que me dei conta de que boa parte de minha vida foi dedicada a localizar erros em meus próprios programas. ” Maurice V. Wilkes, criador da microprogramação

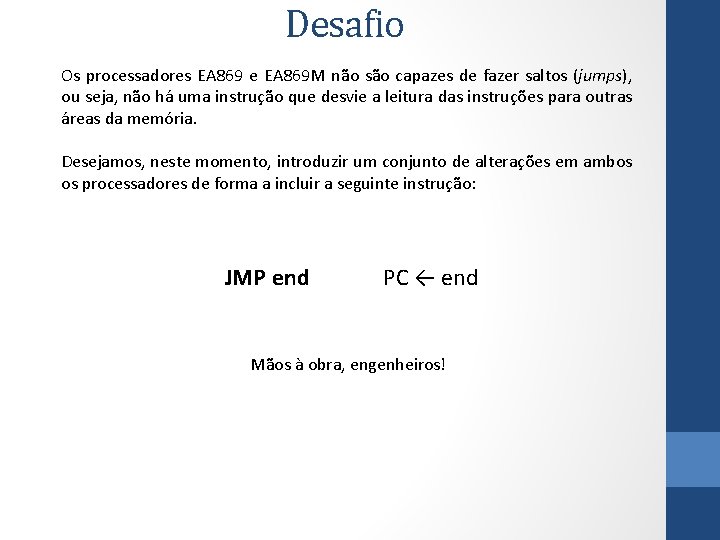

Desafio Os processadores EA 869 e EA 869 M não são capazes de fazer saltos (jumps), ou seja, não há uma instrução que desvie a leitura das instruções para outras áreas da memória. Desejamos, neste momento, introduzir um conjunto de alterações em ambos os processadores de forma a incluir a seguinte instrução: JMP end PC ← end Mãos à obra, engenheiros!

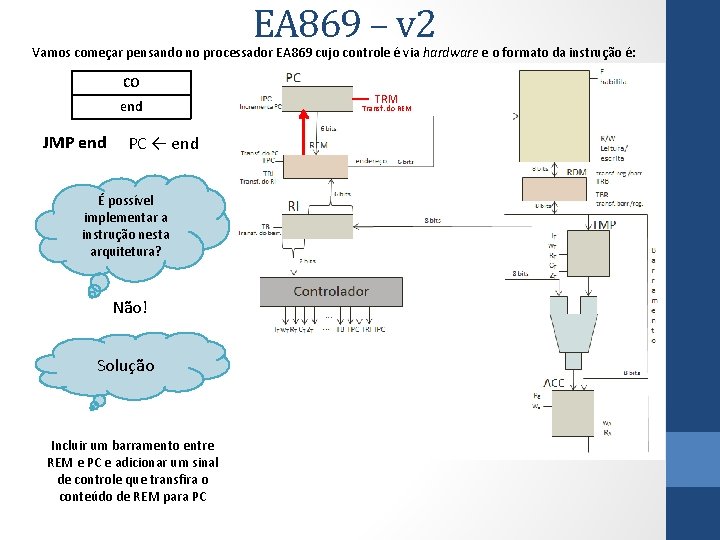

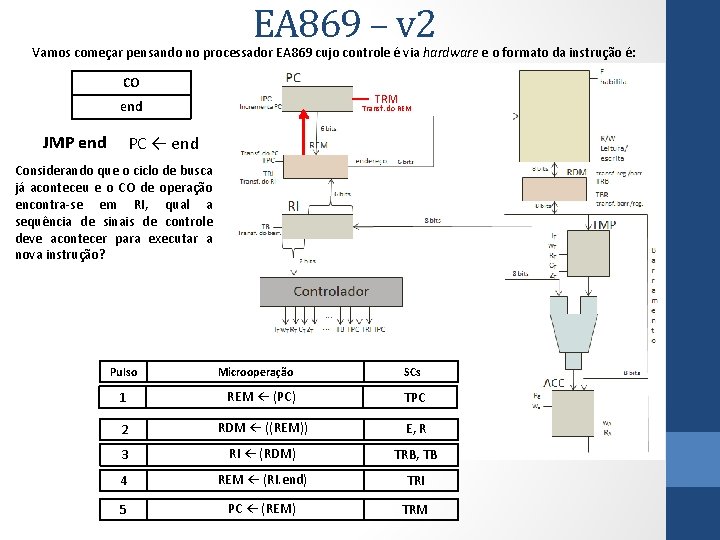

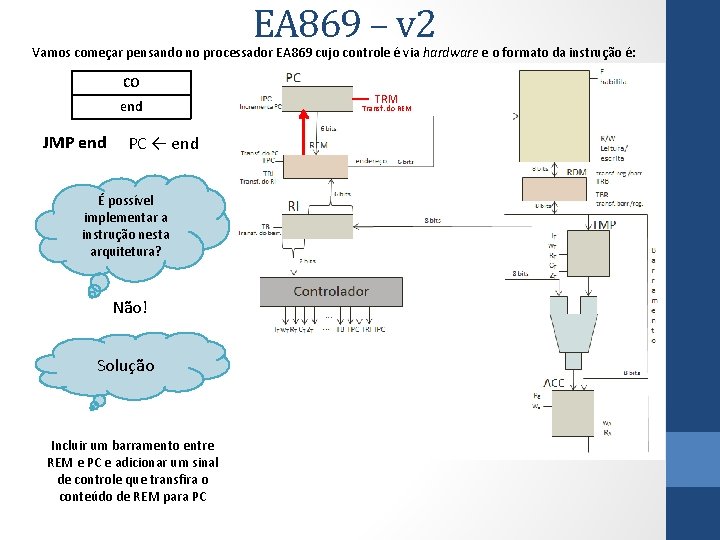

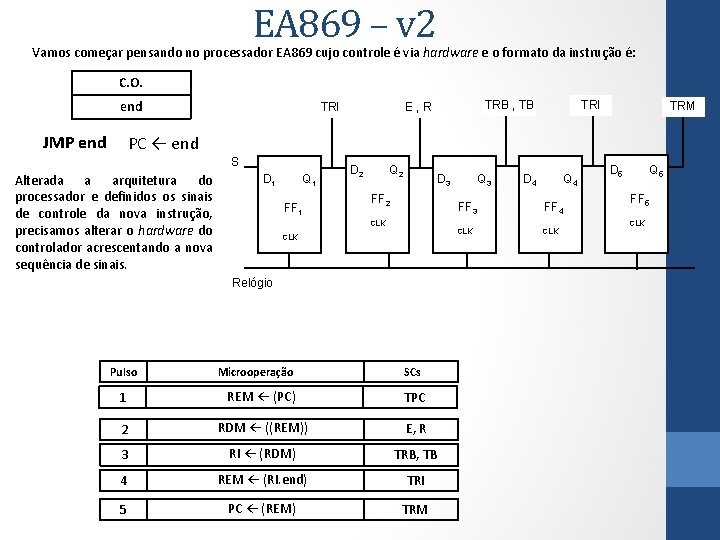

EA 869 – v 2 Vamos começar pensando no processador EA 869 cujo controle é via hardware e o formato da instrução é: CO end JMP end PC ← end É possível implementar a instrução nesta arquitetura? Não! Solução Incluir um barramento entre REM e PC e adicionar um sinal de controle que transfira o conteúdo de REM para PC TRM Transf. do REM

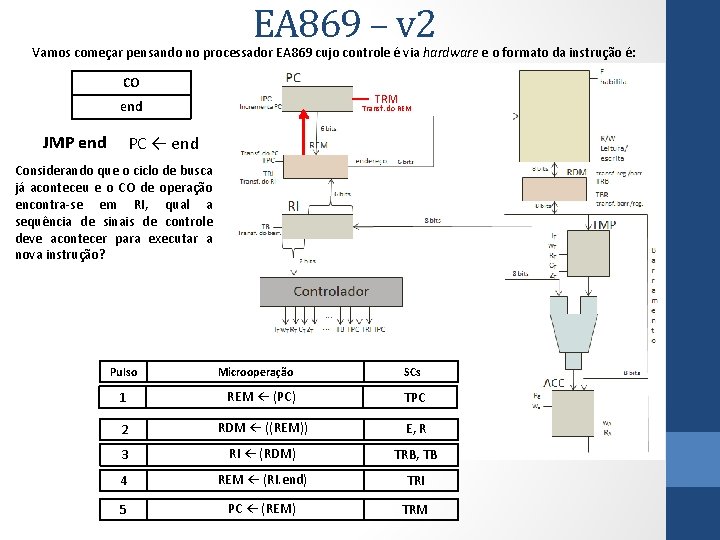

EA 869 – v 2 Vamos começar pensando no processador EA 869 cujo controle é via hardware e o formato da instrução é: CO TRM end JMP end Transf. do REM PC ← end Considerando que o ciclo de busca já aconteceu e o CO de operação encontra-se em RI, qual a sequência de sinais de controle deve acontecer para executar a nova instrução? Pulso Microoperação SCs 1 REM ← (PC) 2 RDM ← ((REM)) E, R 3 RI ← (RDM) TRB, TB 4 REM ← (RI. end) TRI 5 PC ← (REM) TRM TPC

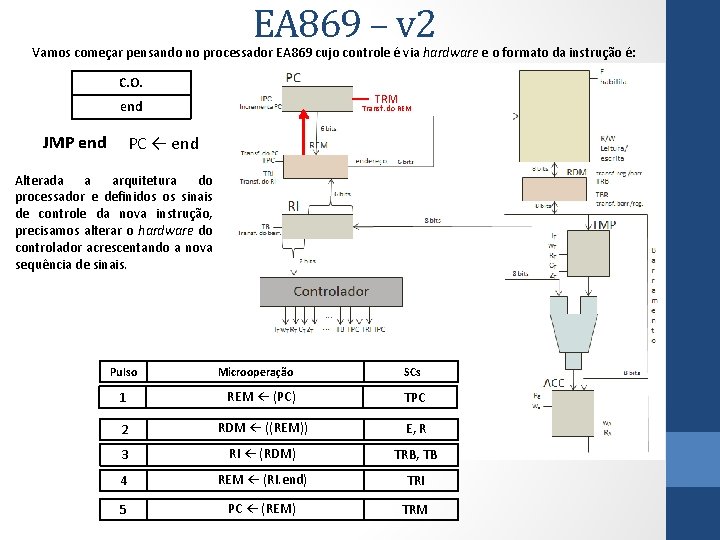

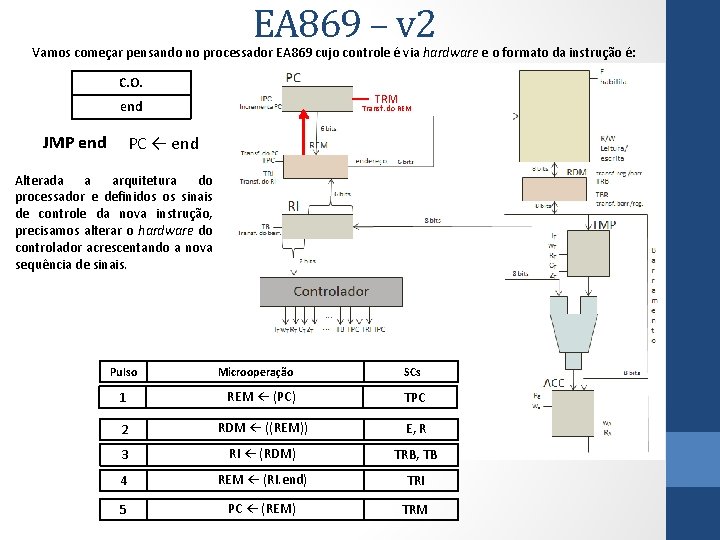

EA 869 – v 2 Vamos começar pensando no processador EA 869 cujo controle é via hardware e o formato da instrução é: C. O. TRM end JMP end Transf. do REM PC ← end Alterada a arquitetura do processador e definidos os sinais de controle da nova instrução, precisamos alterar o hardware do controlador acrescentando a nova sequência de sinais. Pulso Microoperação SCs 1 REM ← (PC) 2 RDM ← ((REM)) E, R 3 RI ← (RDM) TRB, TB 4 REM ← (RI. end) TRI 5 PC ← (REM) TRM TPC

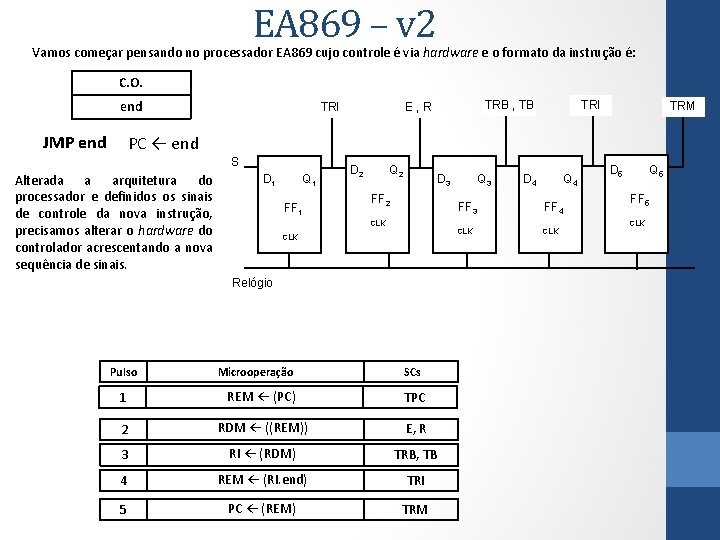

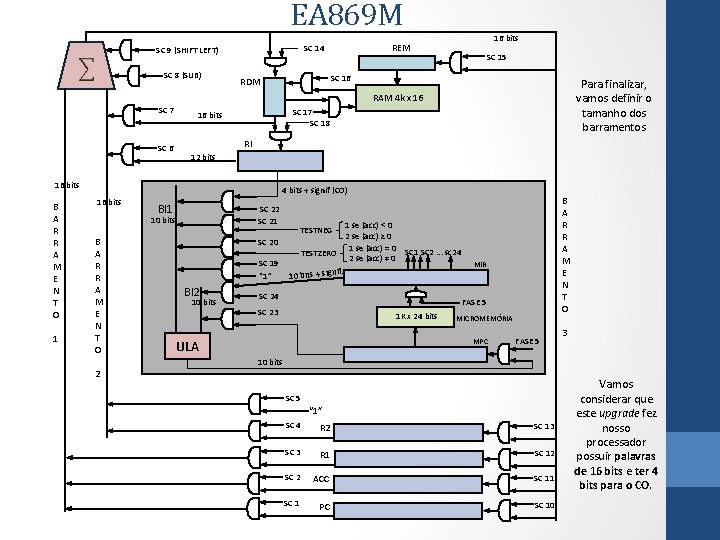

EA 869 – v 2 Vamos começar pensando no processador EA 869 cujo controle é via hardware e o formato da instrução é: C. O. end JMP end TRI TRB , TB E, R TRI TRM PC ← end S Alterada a arquitetura do processador e definidos os sinais de controle da nova instrução, precisamos alterar o hardware do controlador acrescentando a nova sequência de sinais. D 1 Q 1 FF 1 D 2 Q 2 D 3 FF 2 CLK Relógio Pulso Microoperação SCs 1 REM ← (PC) 2 RDM ← ((REM)) E, R 3 RI ← (RDM) TRB, TB 4 REM ← (RI. end) TRI 5 PC ← (REM) TRM TPC Q 3 D 4 Q 4 FF 3 FF 4 CLK D 5 Q 5 FF 5 CLK

Resolvido o problema da versão original do processador EA 869, vamos agora analisar a versão microprogramada!

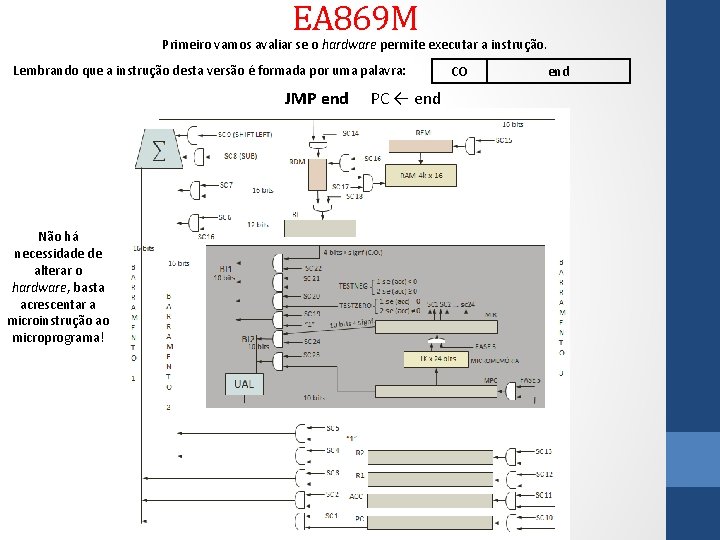

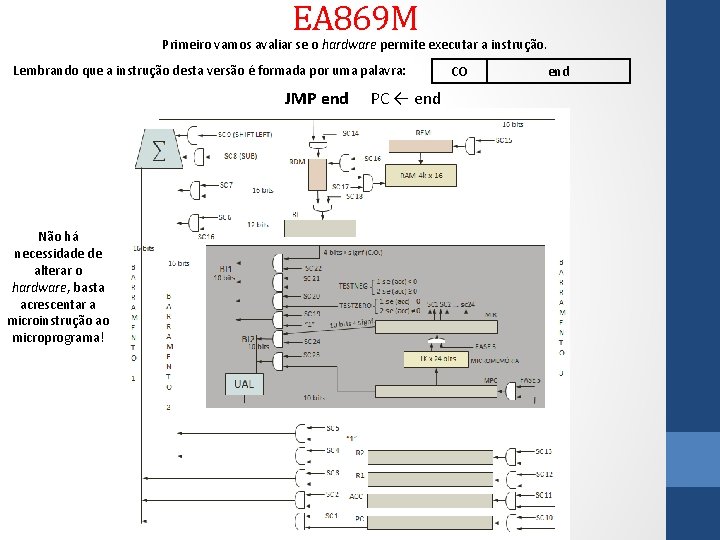

EA 869 M Primeiro vamos avaliar se o hardware permite executar a instrução. Lembrando que a instrução desta versão é formada por uma palavra: JMP end Não há necessidade de alterar o hardware, basta acrescentar a microinstrução ao microprograma! PC ← end CO end

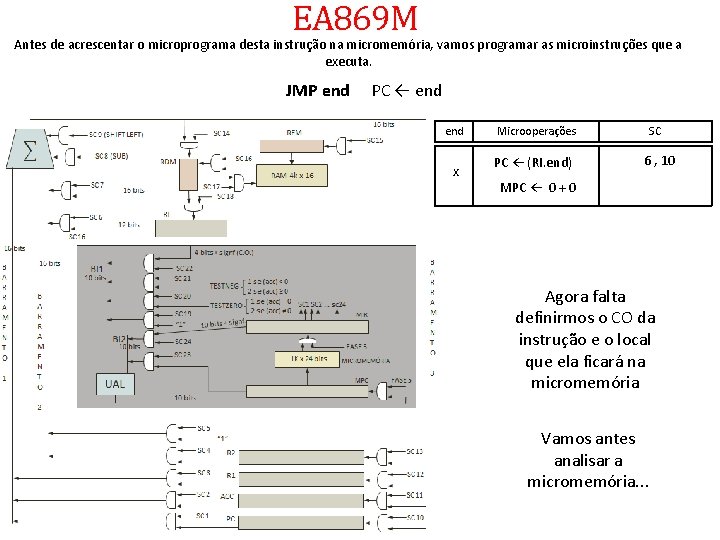

EA 869 M Antes de acrescentar o microprograma desta instrução na micromemória, vamos programar as microinstruções que a executa. JMP end PC ← end x Microoperações PC ← (RI. end) SC 6 , 10 MPC ← 0 + 0 Agora falta definirmos o CO da instrução e o local que ela ficará na micromemória Vamos antes analisar a micromemória. . .

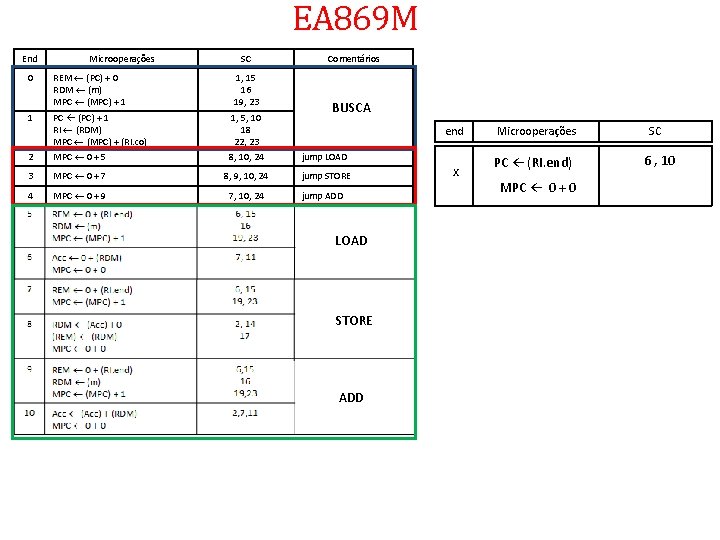

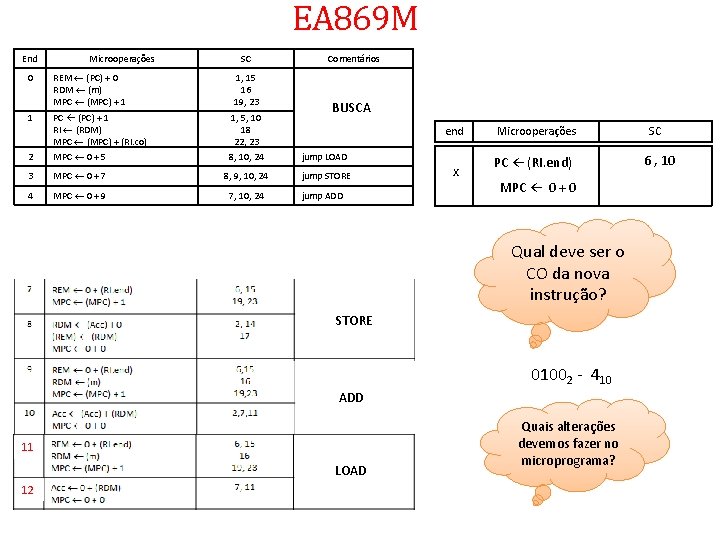

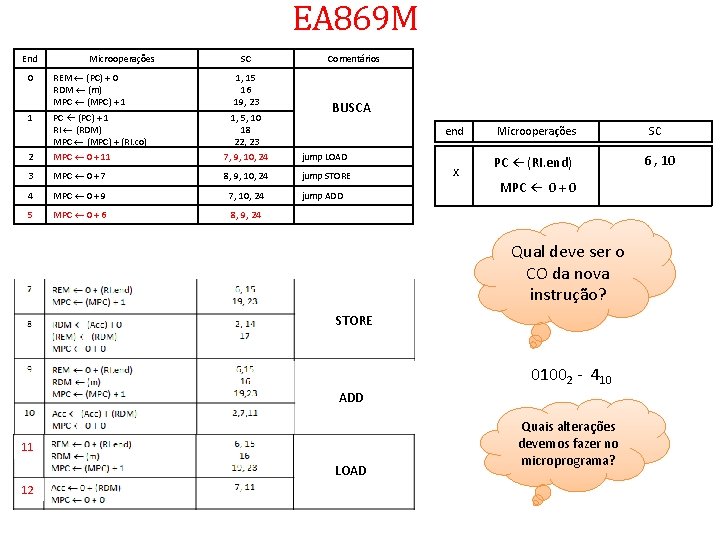

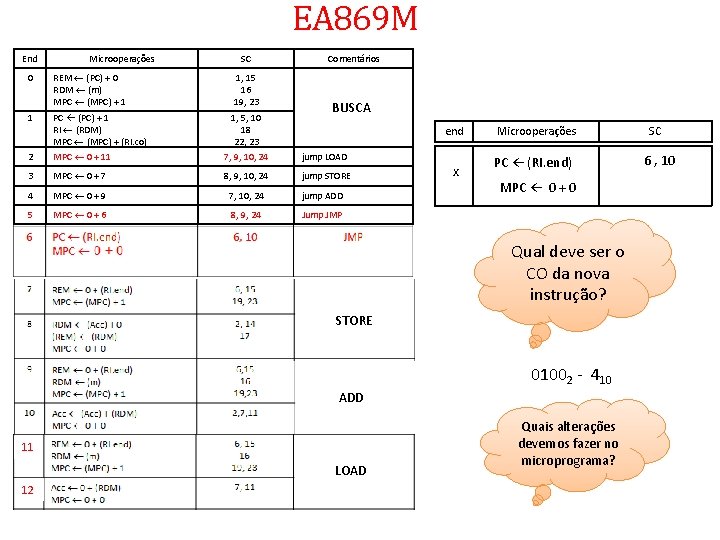

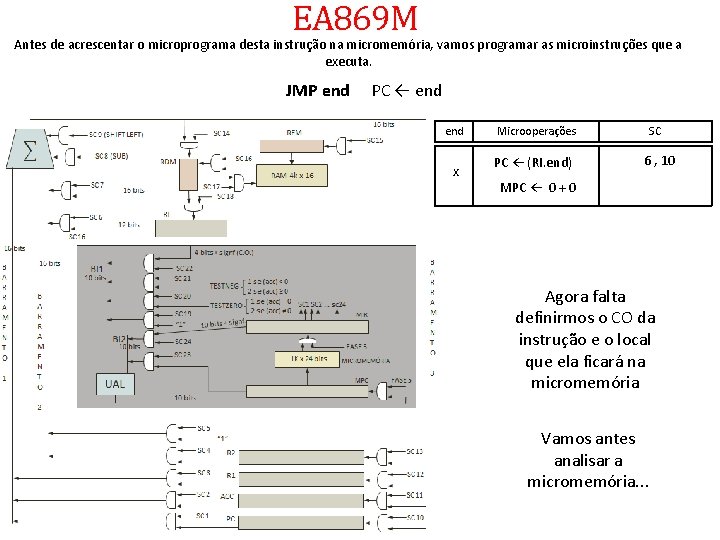

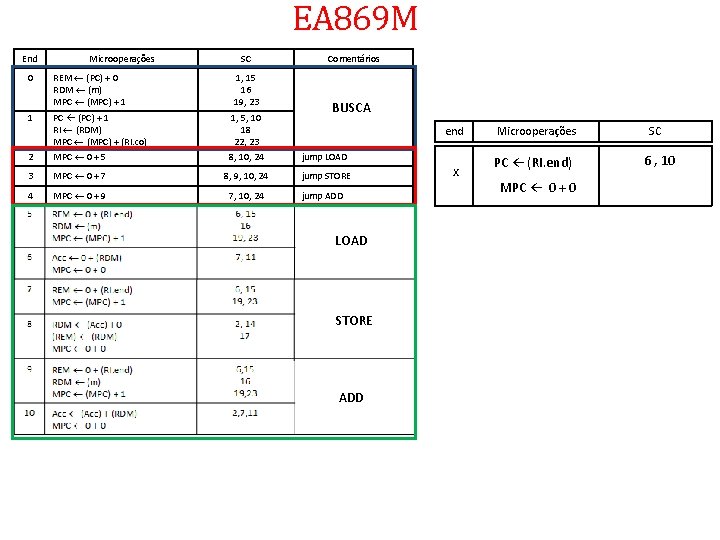

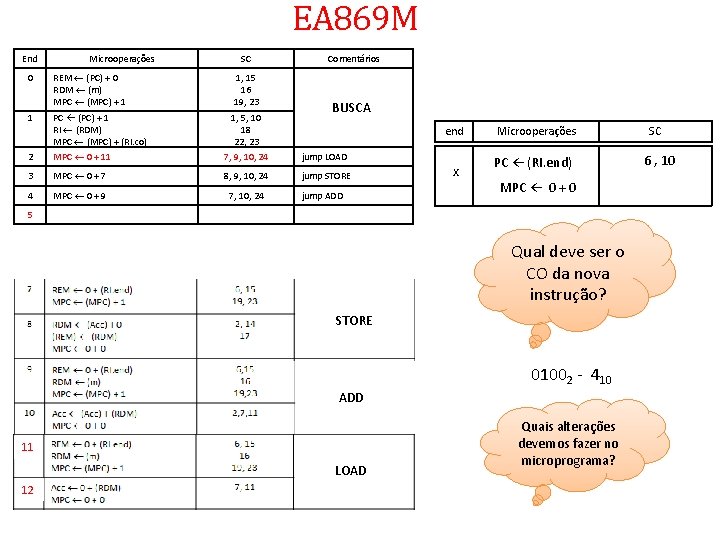

EA 869 M End Microoperações SC Comentários 0 REM (PC) + 0 RDM (m) MPC (MPC) + 1 1, 15 16 19, 23 1 PC (PC) + 1 RI (RDM) MPC (MPC) + (RI. co) 1, 5, 10 18 22, 23 2 MPC 0 + 5 8, 10, 24 jump LOAD 3 MPC 0 + 7 8, 9, 10, 24 jump STORE 4 MPC 0 + 9 7, 10, 24 BUSCA end jump ADD LOAD STORE ADD x Microoperações PC ← (RI. end) MPC ← 0 + 0 SC 6 , 10

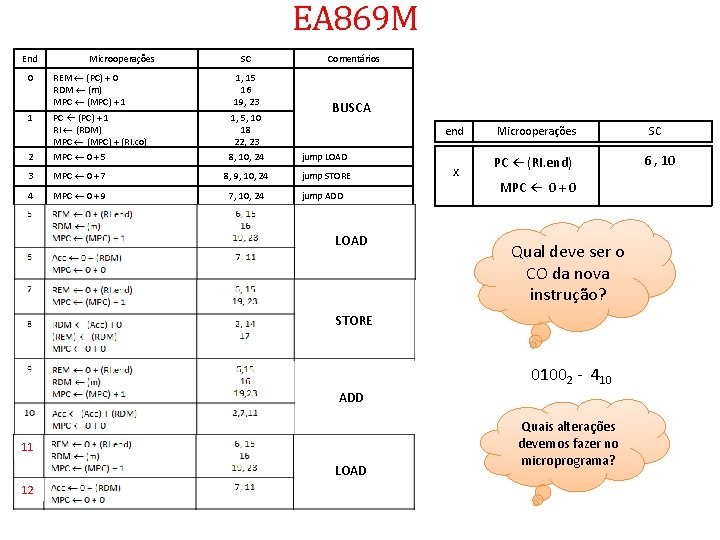

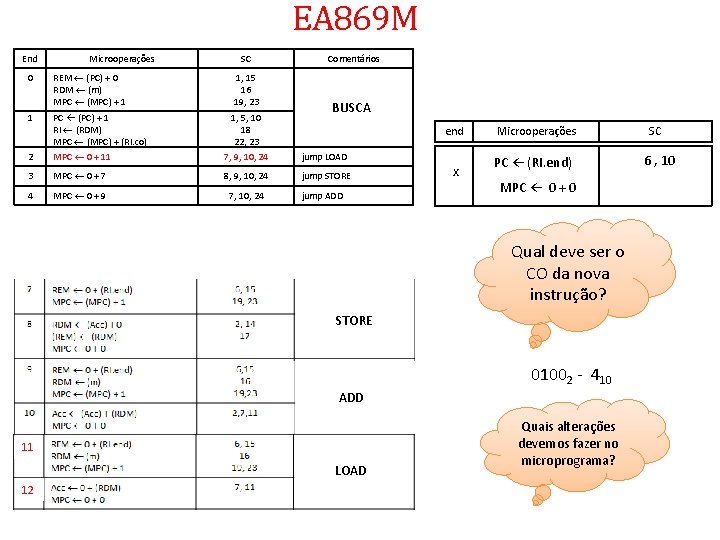

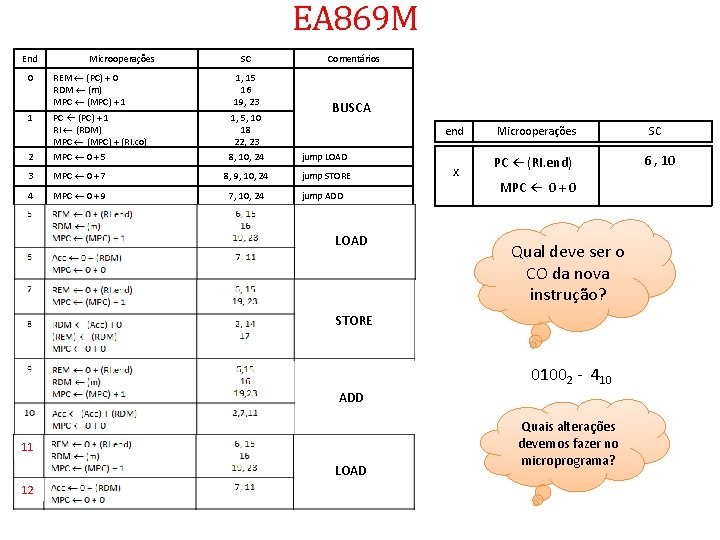

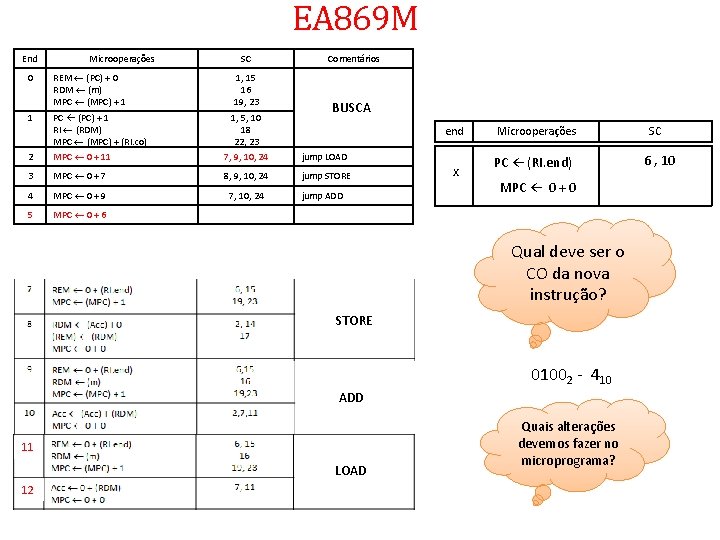

EA 869 M End Microoperações SC Comentários 0 REM (PC) + 0 RDM (m) MPC (MPC) + 1 1, 15 16 19, 23 1 PC (PC) + 1 RI (RDM) MPC (MPC) + (RI. co) 1, 5, 10 18 22, 23 2 MPC 0 + 5 8, 10, 24 jump LOAD 3 MPC 0 + 7 8, 9, 10, 24 jump STORE 4 MPC 0 + 9 7, 10, 24 BUSCA end jump ADD LOAD x Microoperações PC ← (RI. end) MPC ← 0 + 0 Qual deve ser o CO da nova instrução? STORE 01002 - 410 ADD 11 LOAD 12 Quais alterações devemos fazer no microprograma? SC 6 , 10

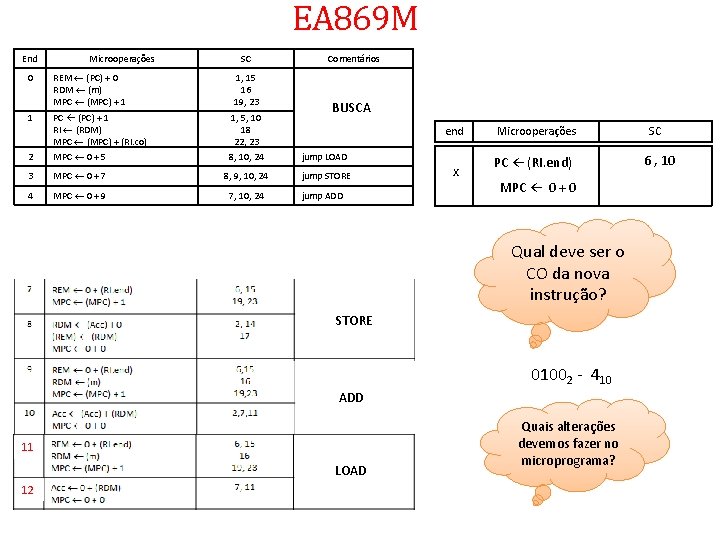

EA 869 M End Microoperações SC Comentários 0 REM (PC) + 0 RDM (m) MPC (MPC) + 1 1, 15 16 19, 23 1 PC (PC) + 1 RI (RDM) MPC (MPC) + (RI. co) 1, 5, 10 18 22, 23 2 MPC 0 + 5 8, 10, 24 jump LOAD 3 MPC 0 + 7 8, 9, 10, 24 jump STORE 4 MPC 0 + 9 7, 10, 24 BUSCA end jump ADD x Microoperações PC ← (RI. end) MPC ← 0 + 0 Qual deve ser o CO da nova instrução? STORE 01002 - 410 ADD 11 LOAD 12 Quais alterações devemos fazer no microprograma? SC 6 , 10

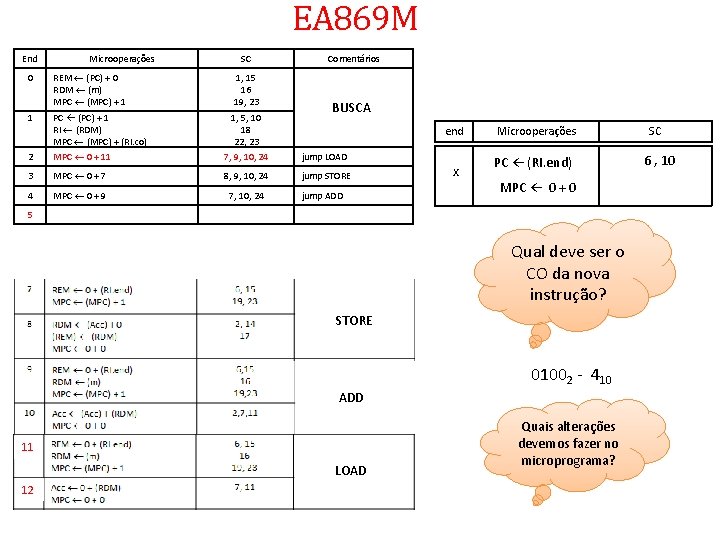

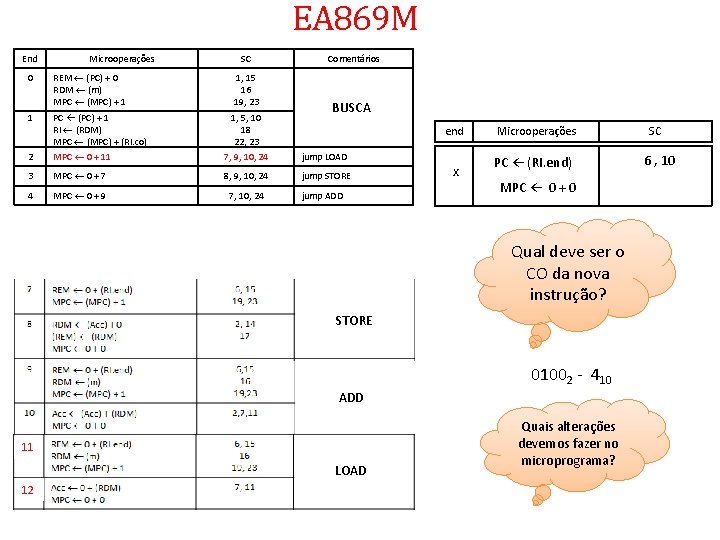

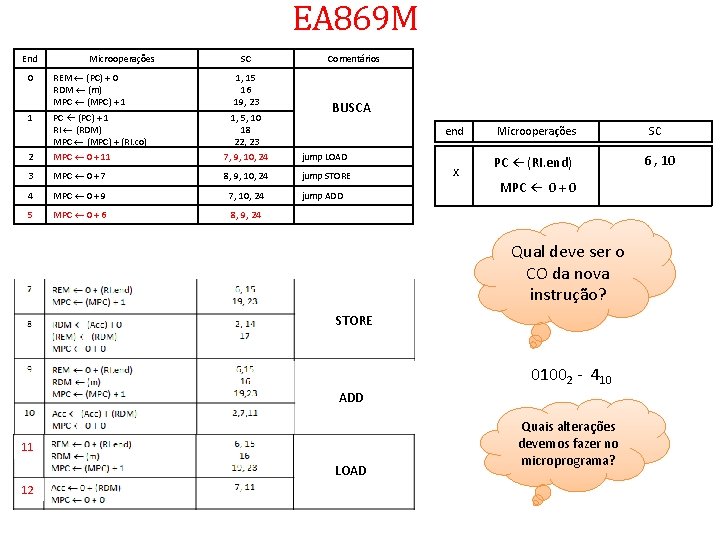

EA 869 M End Microoperações SC 0 REM (PC) + 0 RDM (m) MPC (MPC) + 1 1, 15 16 19, 23 1 PC (PC) + 1 RI (RDM) MPC (MPC) + (RI. co) 1, 5, 10 18 22, 23 Comentários BUSCA end 2 MPC 0 + 11 7, 9, 10, 24 jump LOAD 3 MPC 0 + 7 8, 9, 10, 24 jump STORE 4 MPC 0 + 9 7, 10, 24 jump ADD x Microoperações PC ← (RI. end) MPC ← 0 + 0 Qual deve ser o CO da nova instrução? STORE 01002 - 410 ADD 11 LOAD 12 Quais alterações devemos fazer no microprograma? SC 6 , 10

EA 869 M End Microoperações SC 0 REM (PC) + 0 RDM (m) MPC (MPC) + 1 1, 15 16 19, 23 1 PC (PC) + 1 RI (RDM) MPC (MPC) + (RI. co) 1, 5, 10 18 22, 23 Comentários BUSCA end 2 MPC 0 + 11 7, 9, 10, 24 jump LOAD 3 MPC 0 + 7 8, 9, 10, 24 jump STORE 4 MPC 0 + 9 7, 10, 24 jump ADD x Microoperações PC ← (RI. end) MPC ← 0 + 0 5 Qual deve ser o CO da nova instrução? STORE 01002 - 410 ADD 11 LOAD 12 Quais alterações devemos fazer no microprograma? SC 6 , 10

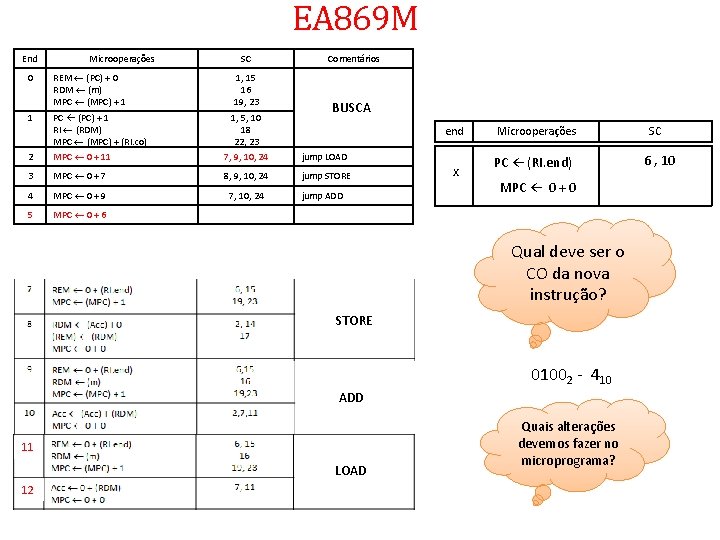

EA 869 M End Microoperações SC 0 REM (PC) + 0 RDM (m) MPC (MPC) + 1 1, 15 16 19, 23 1 PC (PC) + 1 RI (RDM) MPC (MPC) + (RI. co) 1, 5, 10 18 22, 23 Comentários BUSCA end 2 MPC 0 + 11 7, 9, 10, 24 jump LOAD 3 MPC 0 + 7 8, 9, 10, 24 jump STORE 4 MPC 0 + 9 7, 10, 24 5 MPC 0 + 6 jump ADD x Microoperações PC ← (RI. end) MPC ← 0 + 0 Qual deve ser o CO da nova instrução? STORE 01002 - 410 ADD 11 LOAD 12 Quais alterações devemos fazer no microprograma? SC 6 , 10

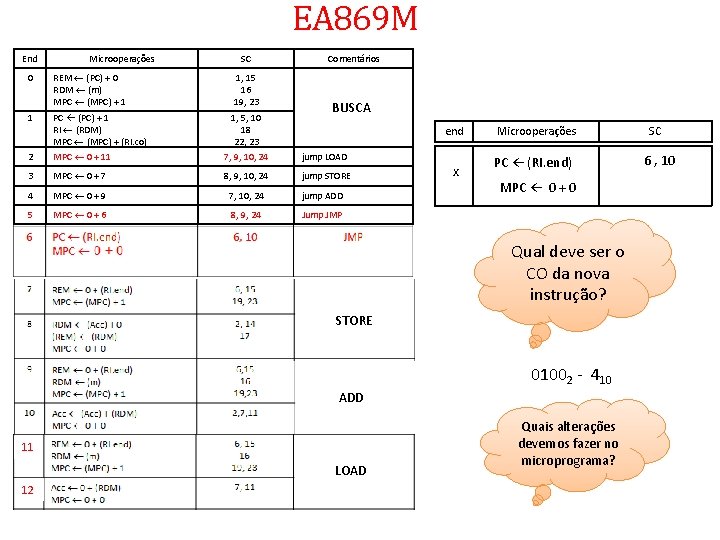

EA 869 M End Microoperações SC 0 REM (PC) + 0 RDM (m) MPC (MPC) + 1 1, 15 16 19, 23 1 PC (PC) + 1 RI (RDM) MPC (MPC) + (RI. co) 1, 5, 10 18 22, 23 Comentários BUSCA end 2 MPC 0 + 11 7, 9, 10, 24 jump LOAD 3 MPC 0 + 7 8, 9, 10, 24 jump STORE 4 MPC 0 + 9 7, 10, 24 5 MPC 0 + 6 8, 9, 24 jump ADD x Microoperações PC ← (RI. end) MPC ← 0 + 0 Qual deve ser o CO da nova instrução? STORE 01002 - 410 ADD 11 LOAD 12 Quais alterações devemos fazer no microprograma? SC 6 , 10

EA 869 M End Microoperações SC 0 REM (PC) + 0 RDM (m) MPC (MPC) + 1 1, 15 16 19, 23 1 PC (PC) + 1 RI (RDM) MPC (MPC) + (RI. co) 1, 5, 10 18 22, 23 Comentários BUSCA end 2 MPC 0 + 11 7, 9, 10, 24 jump LOAD 3 MPC 0 + 7 8, 9, 10, 24 jump STORE 4 MPC 0 + 9 7, 10, 24 jump ADD 5 MPC 0 + 6 8, 9, 24 Jump JMP x Microoperações PC ← (RI. end) MPC ← 0 + 0 Qual deve ser o CO da nova instrução? STORE 01002 - 410 ADD 11 LOAD 12 Quais alterações devemos fazer no microprograma? SC 6 , 10