Microprocessorbased systems Course 6 Memory design 1 Memory

Microprocessor-based systems Course 6 Memory design 1

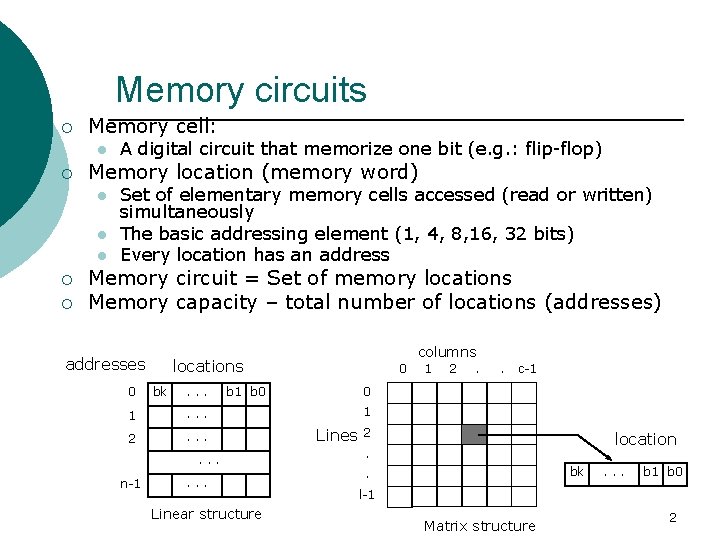

Memory circuits ¡ Memory cell: l ¡ Memory location (memory word) l l l ¡ ¡ A digital circuit that memorize one bit (e. g. : flip-flop) Set of elementary memory cells accessed (read or written) simultaneously The basic addressing element (1, 4, 8, 16, 32 bits) Every location has an address Memory circuit = Set of memory locations Memory capacity – total number of locations (addresses) addresses 0 bk . . . 1 . . . 2 . . . 0 b 1 b 0 . . . n-1 columns locations . . . Linear structure 1 2 . . c-1 0 1 Lines 2 location . bk . . b 1 b 0 l-1 Matrix structure 2

Characteristics of a memory circuit ¡ Geometry of internal organization: l ¡ Memory capacity, l l ¡ The length of the memory word, organization and addressing. Expressed in number of memory locations or in bytes For example: 32 kbytes, 64 k. B, 256 MB, 1 GB. Volatility: loss of data l ROM memory (Read Only Memories) – keeps/stores the data even when the power supply is switched off ¡ l ROM, PROM, EEPROM, Flash RAM memory (Random Access Memories): it looses its content if the power supply is switched off ¡ Static RAM (SRAM) l ¡ High speed, low capacity Dynamic RAM (DRAM): it looses its memory in time l Medium speed, very high capacity 3

Characteristics of a memory circuit ¡ Memory technologies: l l ¡ Time features: l l l ¡ bipolar (TTL, TTL Shottky, ECL) – fast but low integration ratio, high power consumption MOS, CMOS – high integration ratio, high capacity, average speed, small power consumption Access time: the time needed to read or write a memory location; expressed in nanoseconds [ns]. The duration of a read or write cycle The memory’s speed determined by its access time or transfer cycle Power consumption, expressed in w/bit. l l Bipolar memories have higher power consumption; it depends on the capacity MOS memories have very low power consumption; it depends on the access frequency 4

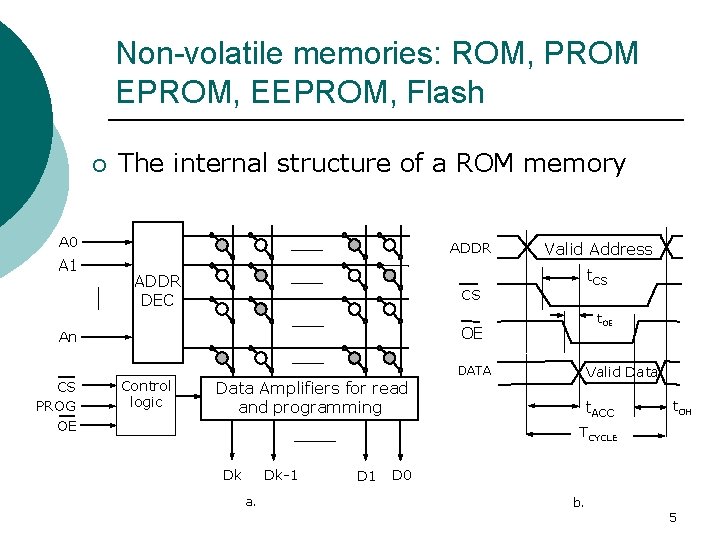

Non-volatile memories: ROM, PROM EPROM, EEPROM, Flash ¡ The internal structure of a ROM memory A 0 A 1 ADDR DEC t. CS CS t. OE OE An CS PROG OE Valid Address Control logic Valid Data DATA Data Amplifiers for read and programming t. ACC t. OH TCYCLE Dk Dk-1 a. D 1 D 0 b. 5

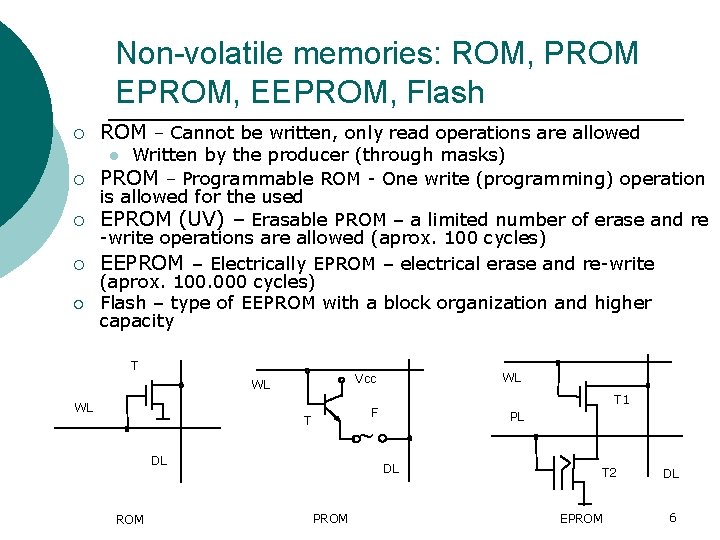

Non-volatile memories: ROM, PROM EPROM, EEPROM, Flash ¡ ROM – Cannot be written, only read operations are allowed Written by the producer (through masks) ¡ PROM – Programmable ROM - One write (programming) operation is allowed for the used ¡ EPROM (UV) – Erasable PROM – a limited number of erase and re -write operations are allowed (aprox. 100 cycles) ¡ EEPROM – Electrically EPROM – electrical erase and re-write (aprox. 100. 000 cycles) ¡ Flash – type of EEPROM with a block organization and higher capacity l T WL T 1 F T PL DL ROM WL Vcc WL DL PROM T 2 EPROM DL 6

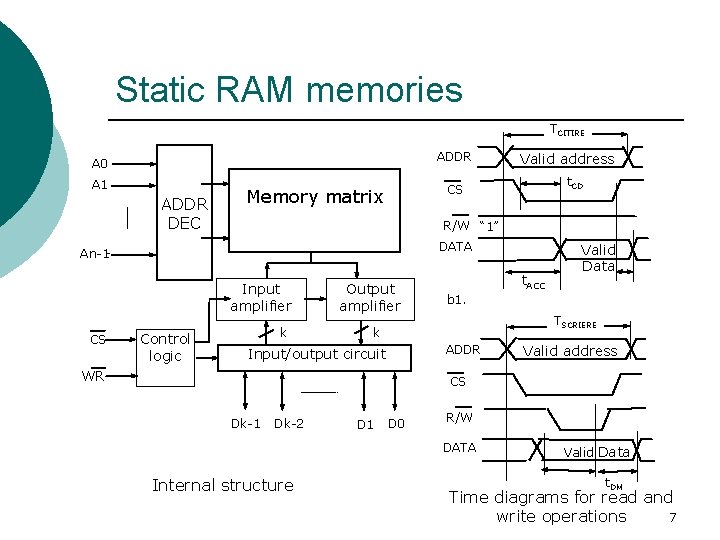

Static RAM memories TCITIRE ADDR A 0 A 1 ADDR DEC t. CD CS Memory matrix R/W “ 1” DATA An-1 Input amplifier CS Valid address Control logic k Output amplifier t. ACC b 1. TSCRIERE k ADDR Input/output circuit WR Valid Data Valid address CS Dk-1 Dk-2 D 1 D 0 R/W DATA Internal structure Valid Data t. DM Time diagrams for read and 7 write operations

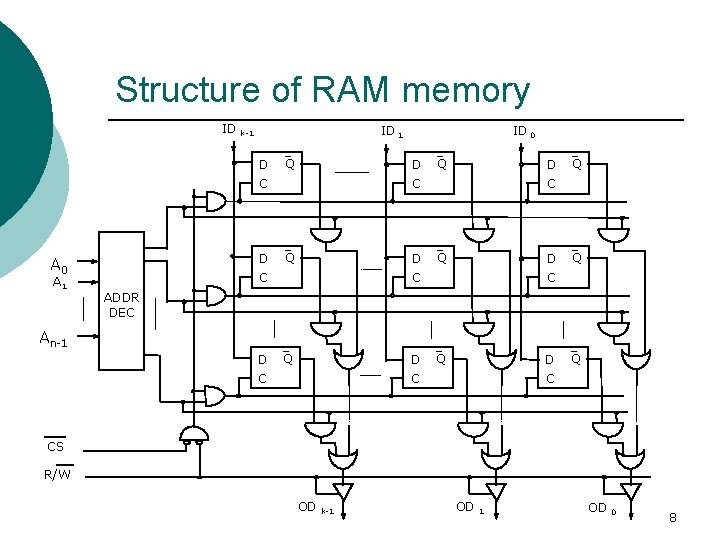

Structure of RAM memory ID A 0 A 1 ID 1 k-1 ID 0 D Q D Q D Q C C C ADDR DEC An-1 CS R/W OD k-1 OD 0 8

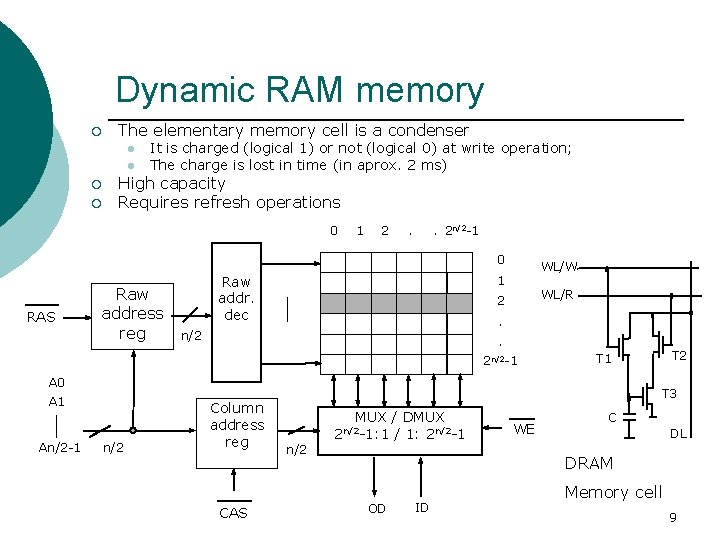

Dynamic RAM memory ¡ The elementary memory cell is a condenser l l ¡ ¡ It is charged (logical 1) or not (logical 0) at write operation; The charge is lost in time (in aprox. 2 ms) High capacity Requires refresh operations 0 1 2 . . 2 n/2 -1 0 RAS Raw address reg Raw addr. dec WL/W 1 WL/R 2. n/2 . 2 n/2 -1 A 0 A 1 An/2 -1 n/2 Column address reg CAS T 2 T 1 T 3 MUX / DMUX / 1: 2 n/2 -1: 1 n/2 WE C DL DRAM OD ID Memory cell 9

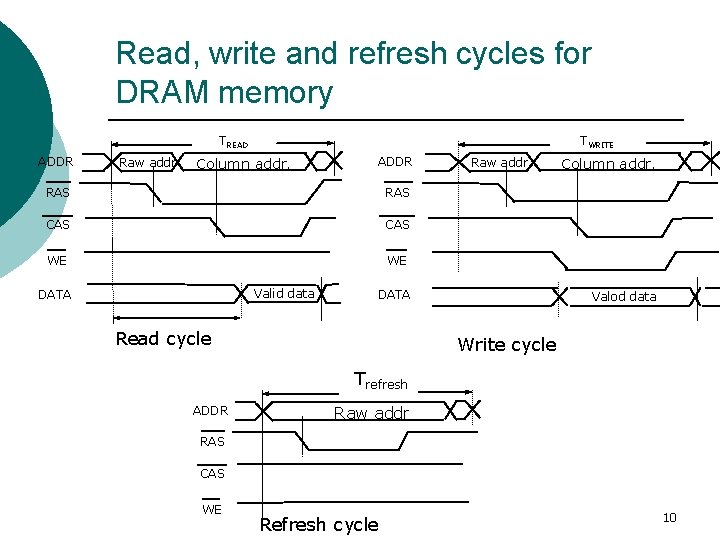

Read, write and refresh cycles for DRAM memory TREAD ADDR Raw addr TWRITE Column addr. ADDR RAS CAS WE WE Valid data DATA Raw addr DATA Read cycle Column addr. Valod data Write cycle Trefresh ADDR Raw addr RAS CAS WE Refresh cycle 10

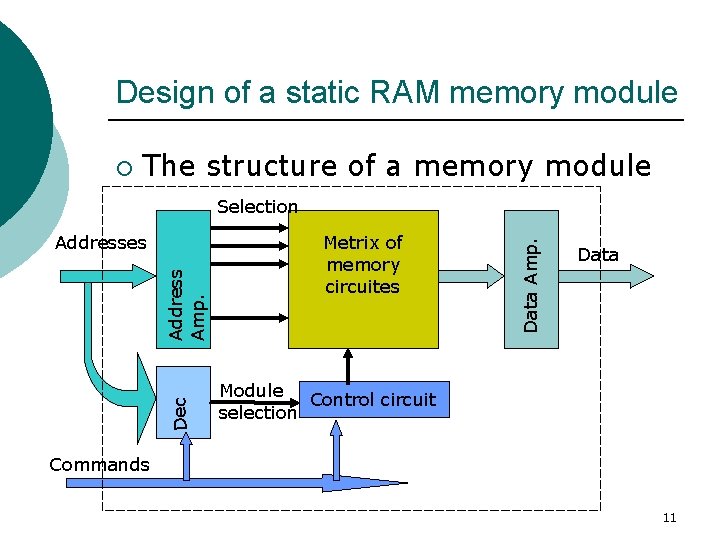

Design of a static RAM memory module ¡ The structure of a memory module Dec Address Amp. Addresses Metrix of memory circuites Data Amp. Selection Data Module Control circuit selection Commands 11

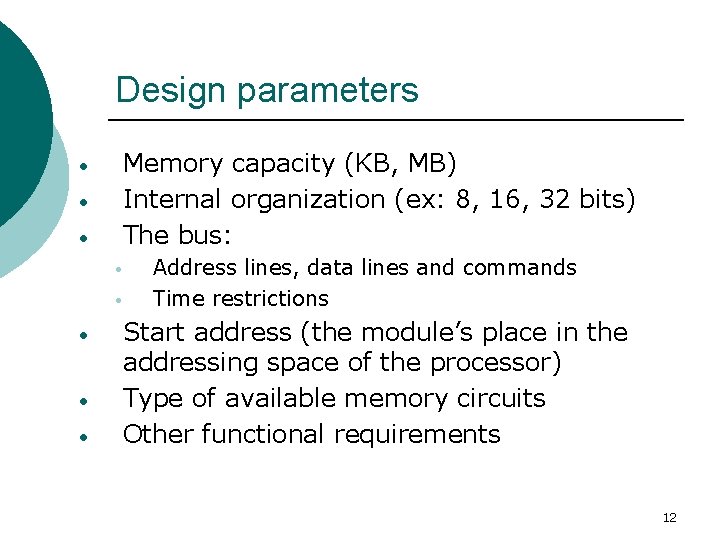

Design parameters • • • Memory capacity (KB, MB) Internal organization (ex: 8, 16, 32 bits) The bus: • • • Address lines, data lines and commands Time restrictions Start address (the module’s place in the addressing space of the processor) Type of available memory circuits Other functional requirements 12

Design steps 1. 2. 3. 4. 5. 6. Building of a memory sub-module with the required data width Build the memory matrix with the required capacity, using the previously built sub-modules Design the decoder module Design of address amplifiers Design of data amplifiers Design of the control circuit (if needed) 13

Design example Capacity: 1 Mbytes ¡ Organization: 16 bits with access on 8 bits ¡ too ¡ The bus: l ISA (24 address lines, 16 data lines, MRDC, MWTC) Start address: C 0000 H ¡ Available circuits: 64 Kbytes ¡ 14

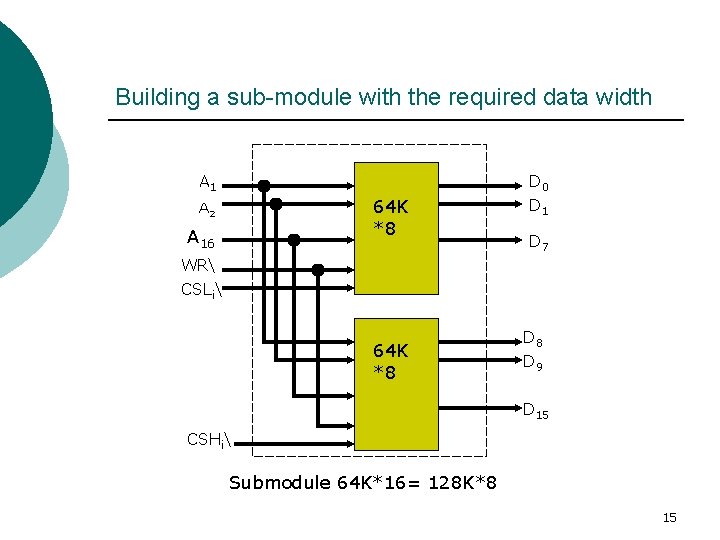

Building a sub-module with the required data width A 1 64 K *8 A 2 A 16 D 0 D 1 D 7 WR CSLi 64 K *8 D 9 D 15 CSHi Submodule 64 K*16= 128 K*8 15

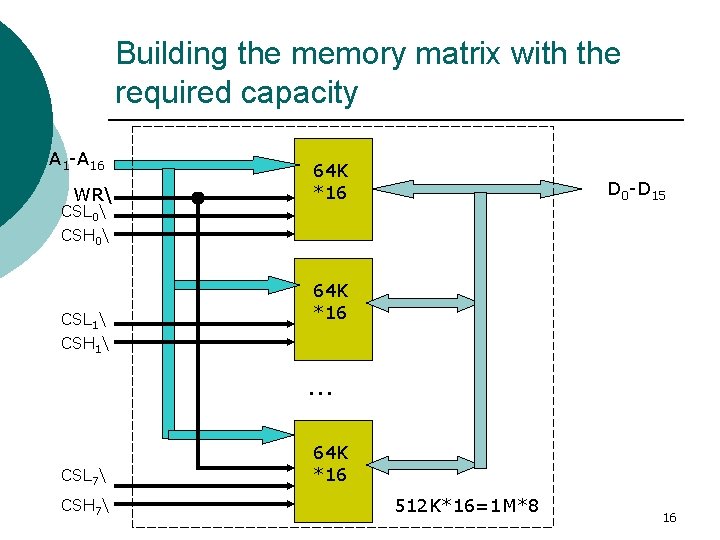

Building the memory matrix with the required capacity A 1 -A 16 WR CSL 0 CSH 0 CSL 1 CSH 1 64 K *16 D 0 -D 15 64 K *16 … CSL 7 CSH 7 64 K *16 512 K*16=1 M*8 16

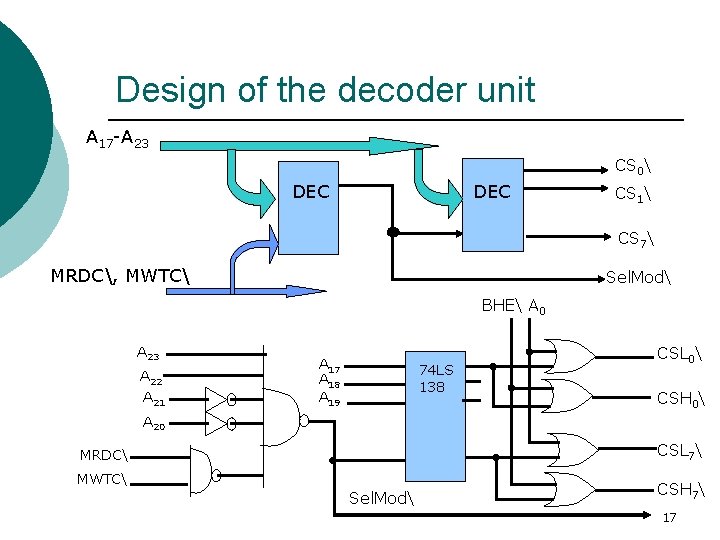

Design of the decoder unit A 17 -A 23 CS 0 DEC CS 1 CS 7 MRDC, MWTC Sel. Mod BHE A 0 A 23 A 22 A 21 A 17 A 18 A 19 74 LS 138 CSL 0 CSH 0 A 20 CSL 7 MRDC MWTC Sel. Mod CSH 7 17

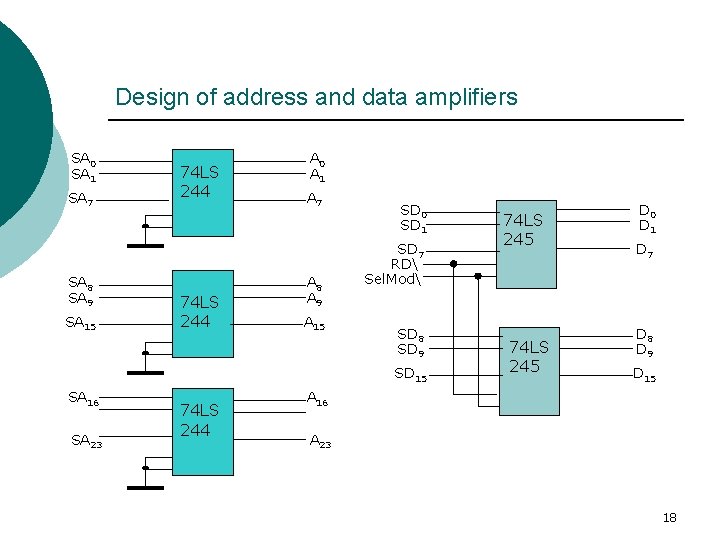

Design of address and data amplifiers SA 0 SA 1 SA 7 SA 8 SA 9 SA 15 74 LS 244 A 0 A 1 A 7 A 8 A 9 A 15 SD 0 SD 1 SD 7 RD Sel. Mod SD 8 SD 9 SD 15 SA 16 SA 23 74 LS 244 74 LS 245 D 0 D 1 D 7 D 8 D 9 D 15 A 16 A 23 18

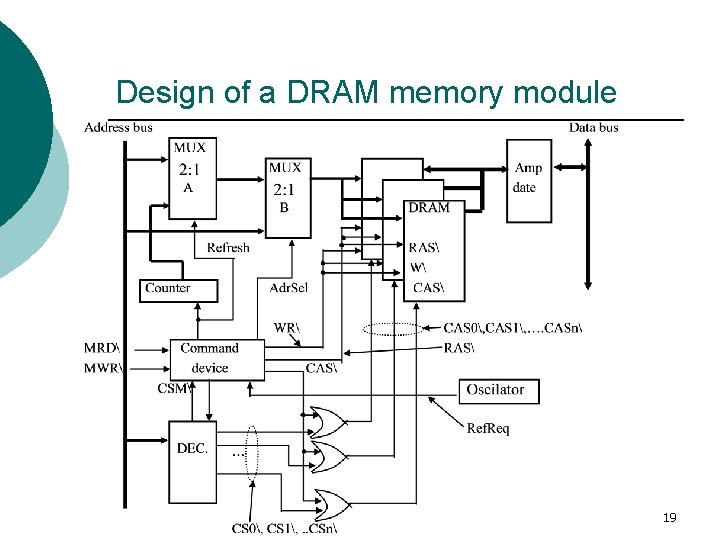

Design of a DRAM memory module 19

- Slides: 19