MICROPROCESSOR THEORY AND INTERFACING Week10 INTERFACING Memory Interfacing

- Slides: 20

MICROPROCESSOR THEORY AND INTERFACING Week-10 INTERFACING

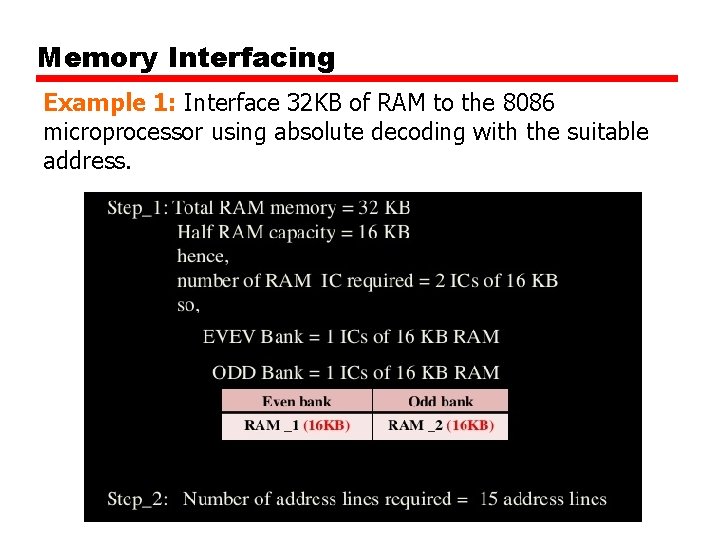

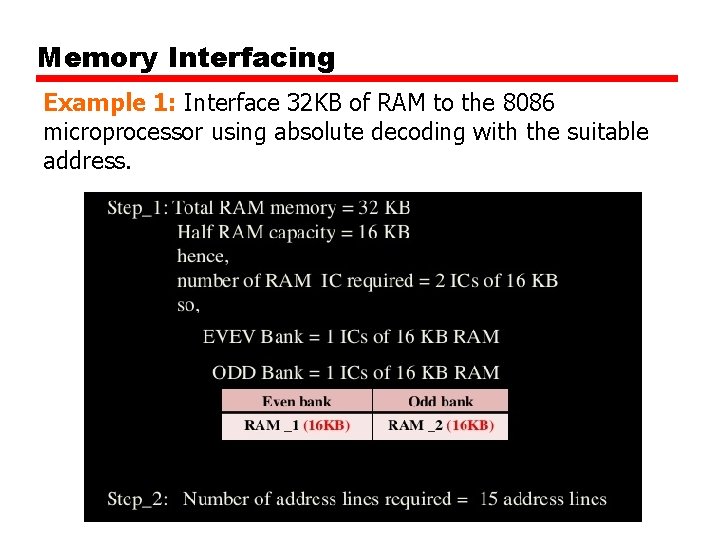

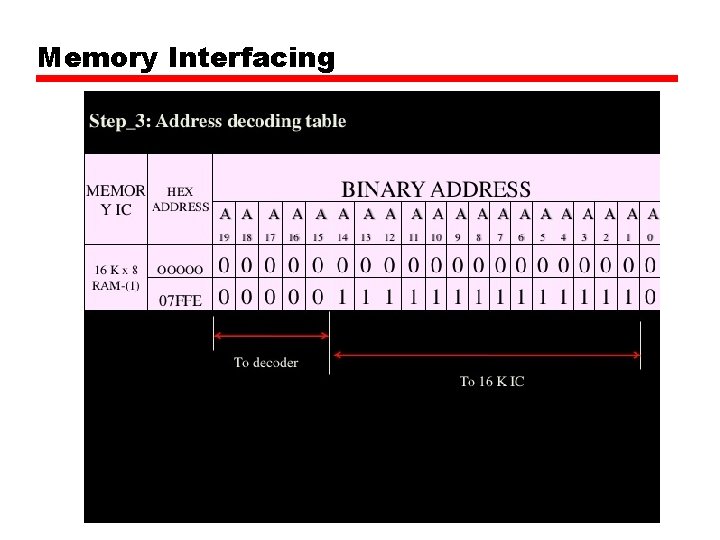

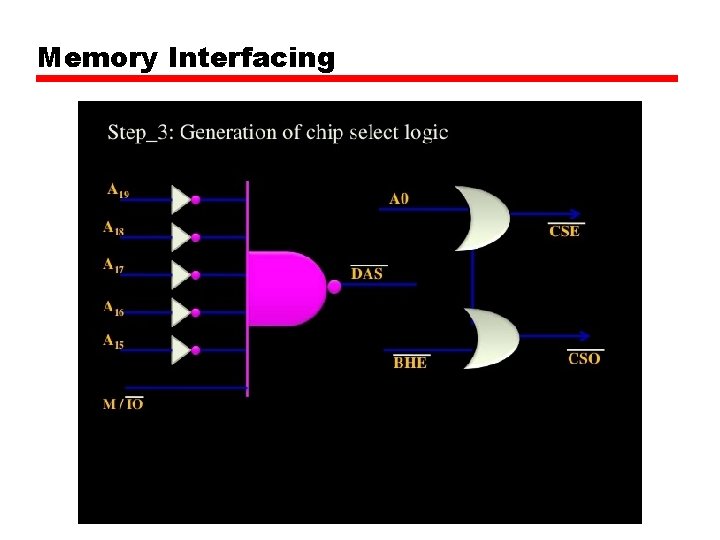

Memory Interfacing Example 1: Interface 32 KB of RAM to the 8086 microprocessor using absolute decoding with the suitable address.

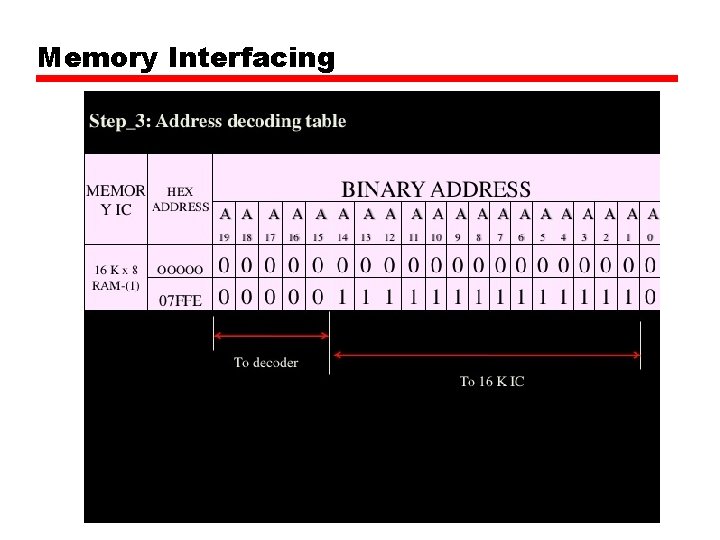

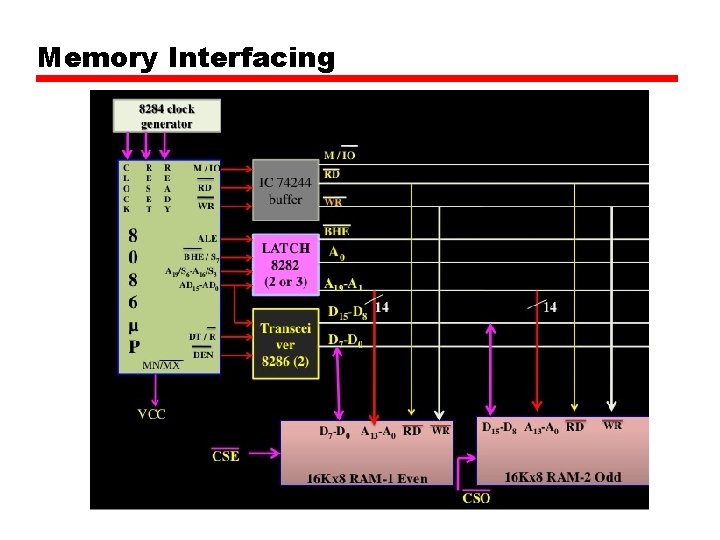

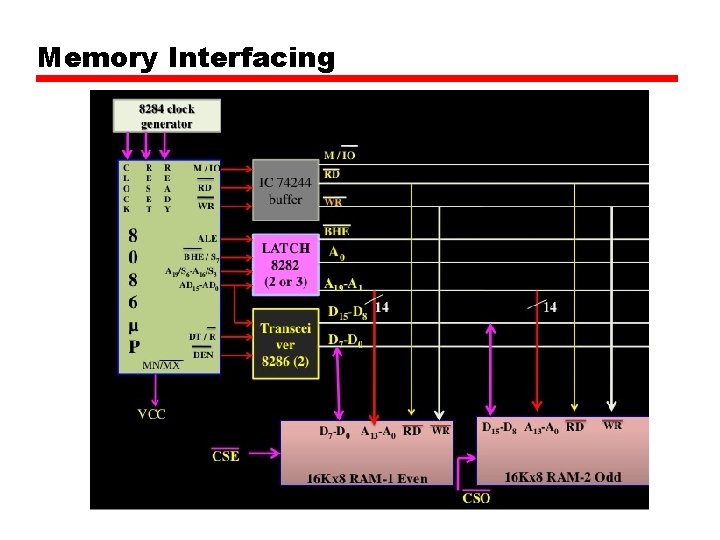

Memory Interfacing

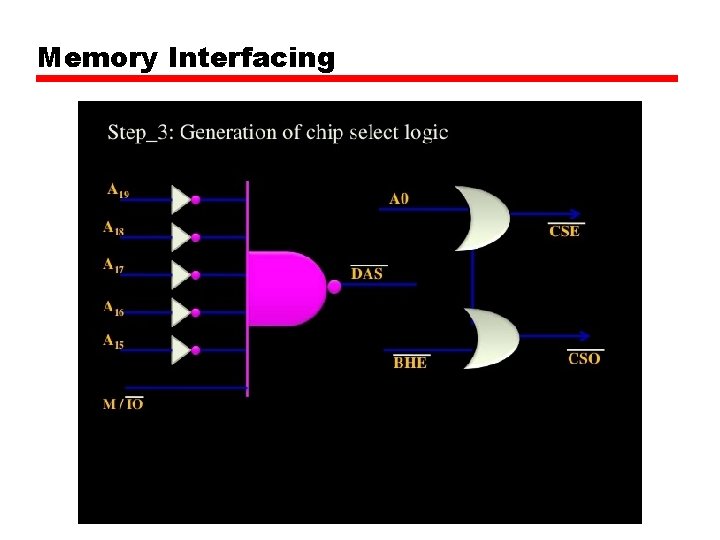

Memory Interfacing

Memory Interfacing

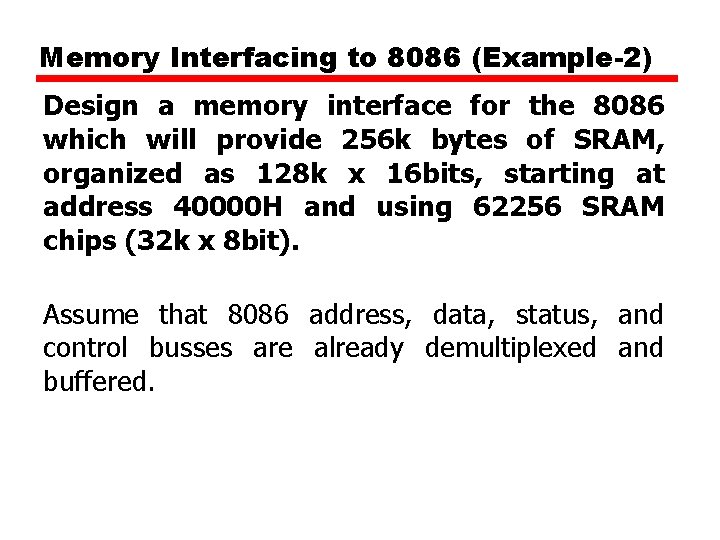

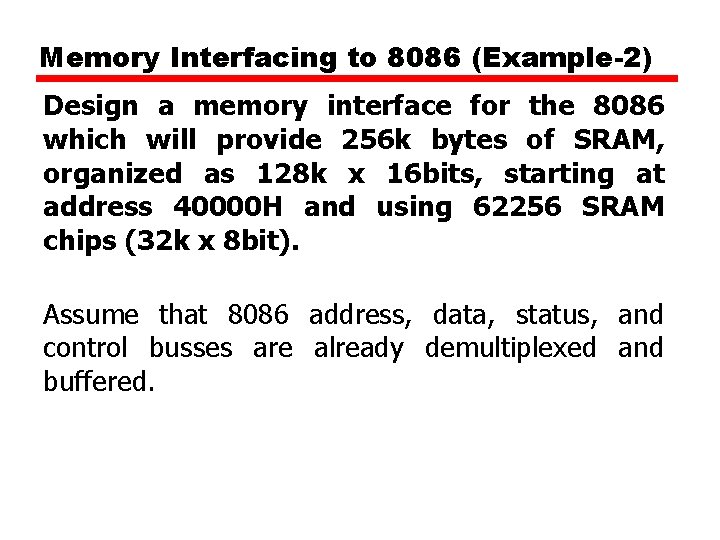

Memory Interfacing to 8086 (Example-2) Design a memory interface for the 8086 which will provide 256 k bytes of SRAM, organized as 128 k x 16 bits, starting at address 40000 H and using 62256 SRAM chips (32 k x 8 bit). Assume that 8086 address, data, status, and control busses are already demultiplexed and buffered.

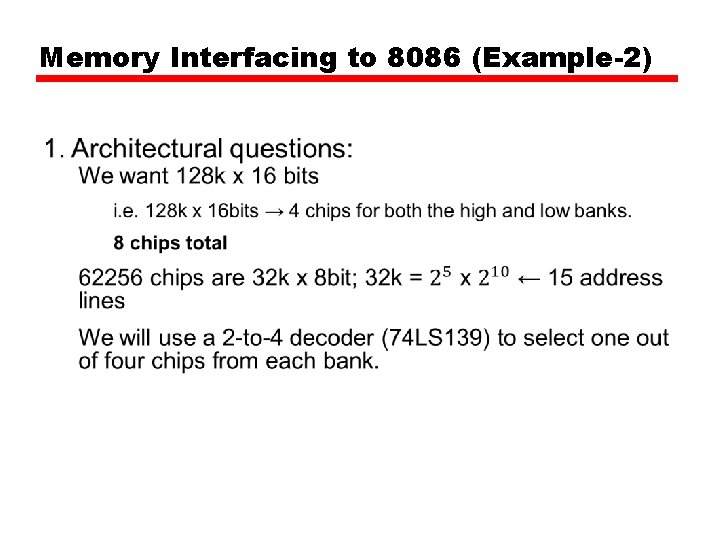

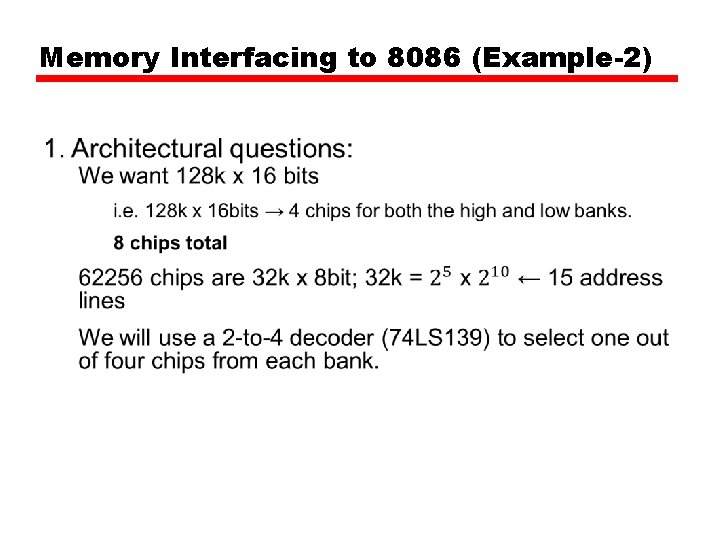

Memory Interfacing to 8086 (Example-2)

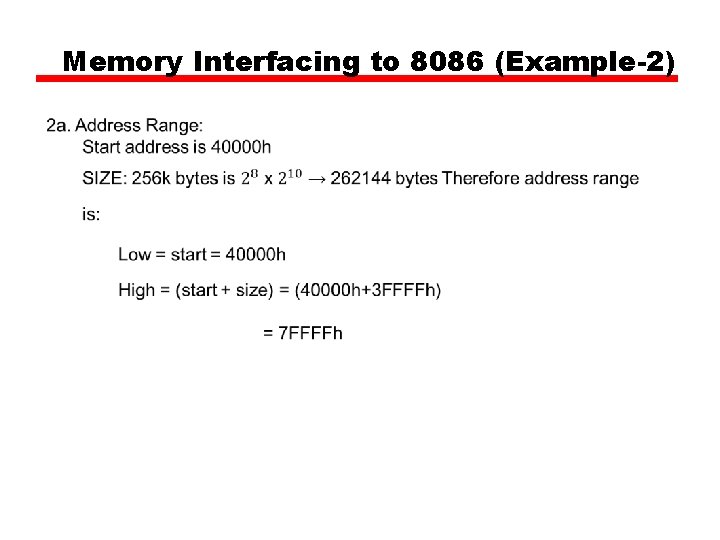

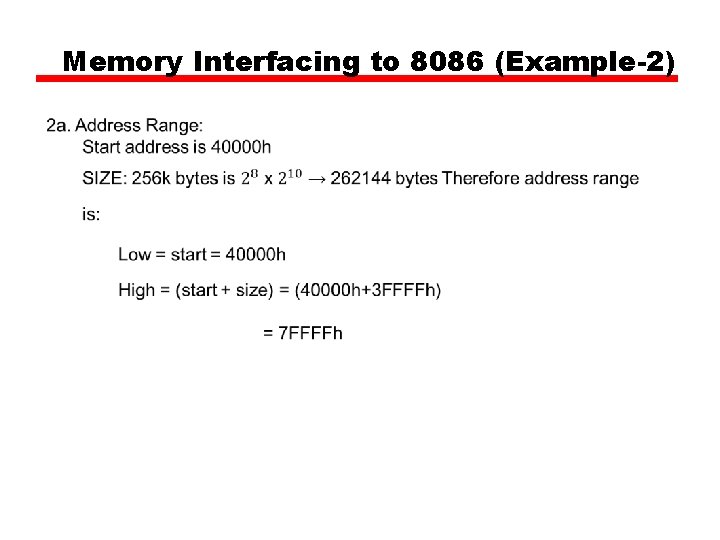

Memory Interfacing to 8086 (Example-2)

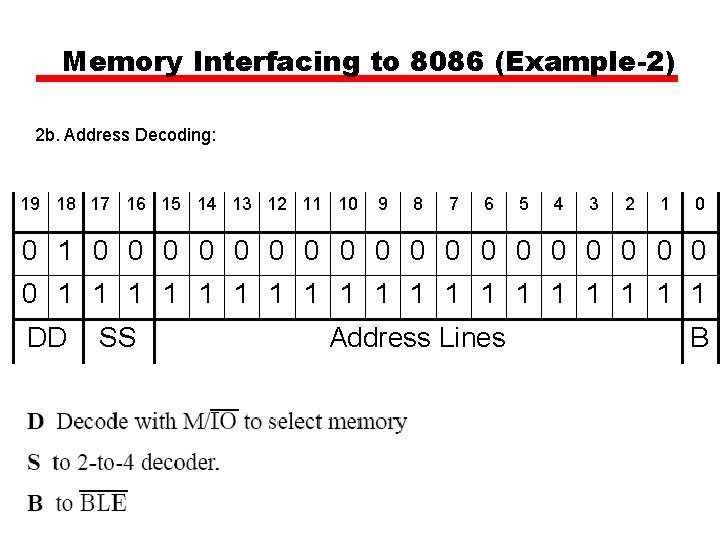

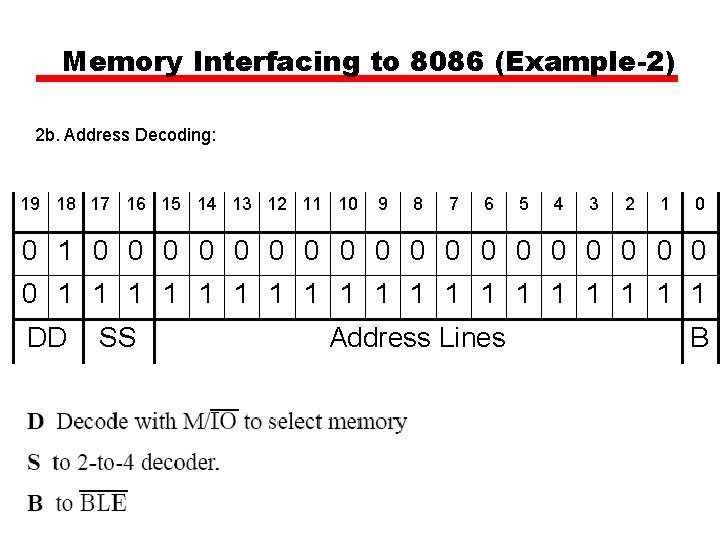

Memory Interfacing to 8086 (Example-2) 2 b. Address Decoding: 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 0 0 0 0 0 1 1 1 1 1 DD SS Address Lines B

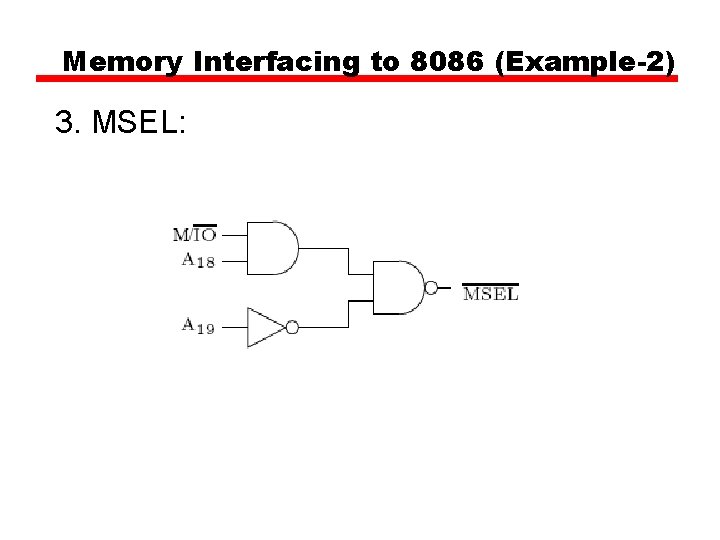

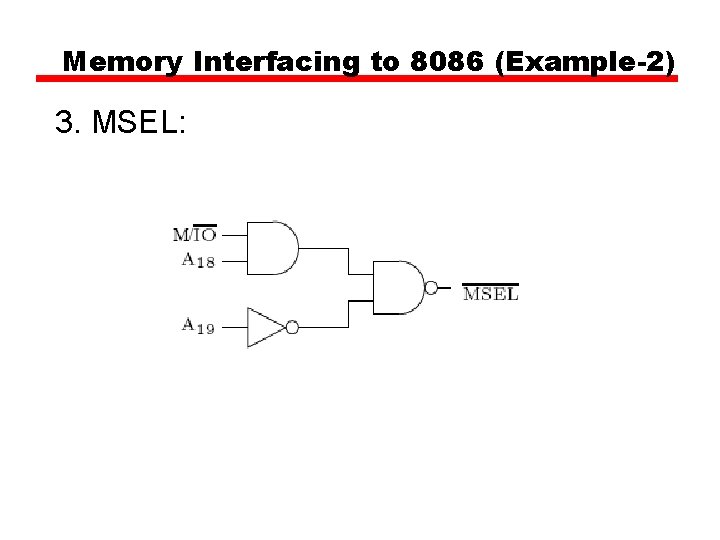

Memory Interfacing to 8086 (Example-2) 3. MSEL:

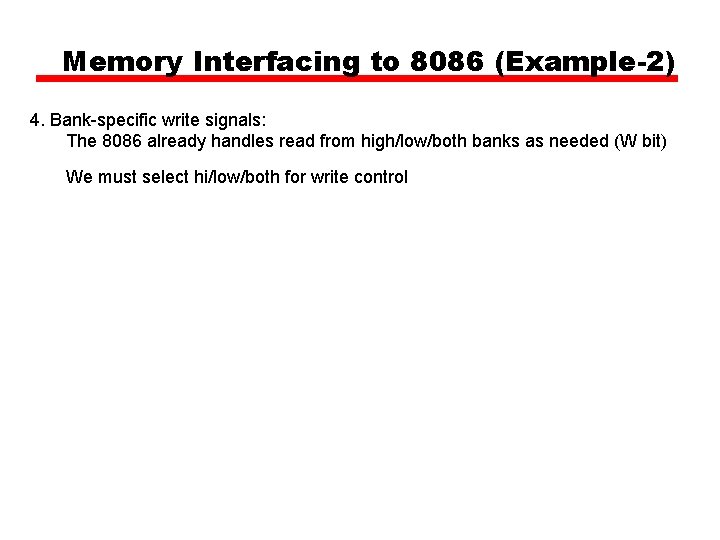

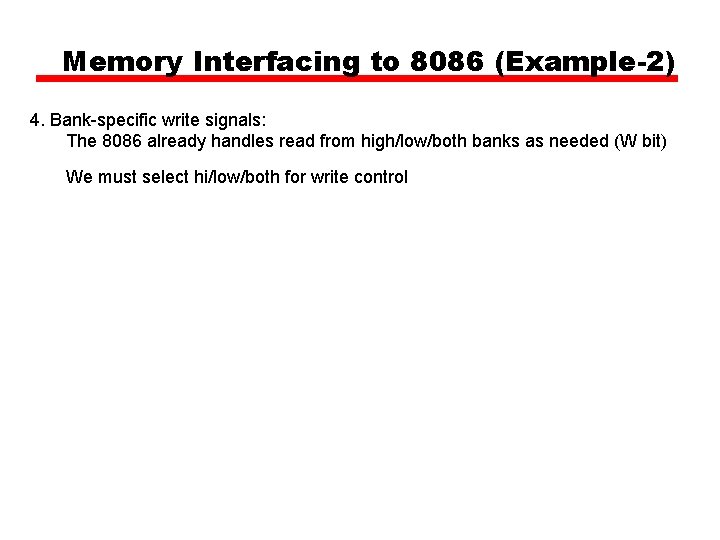

Memory Interfacing to 8086 (Example-2) 4. Bank-specific write signals: The 8086 already handles read from high/low/both banks as needed (W bit) We must select hi/low/both for write control

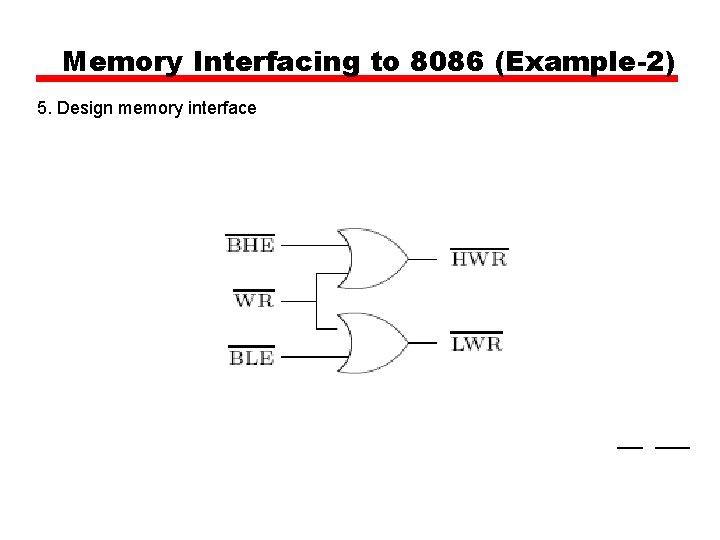

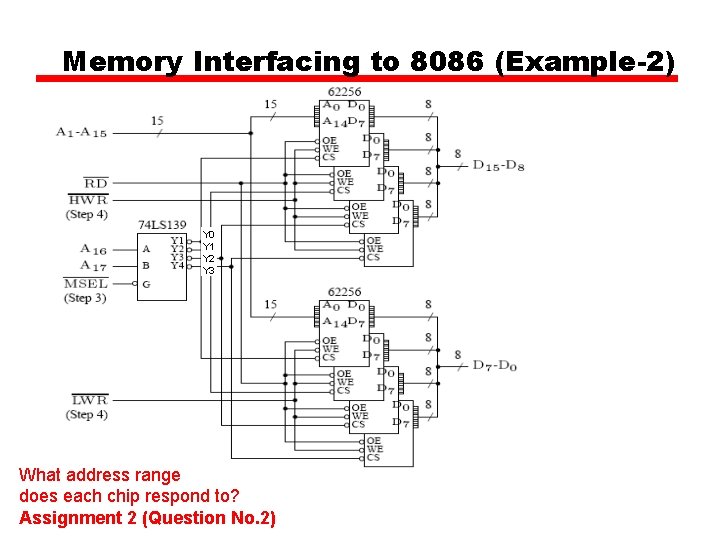

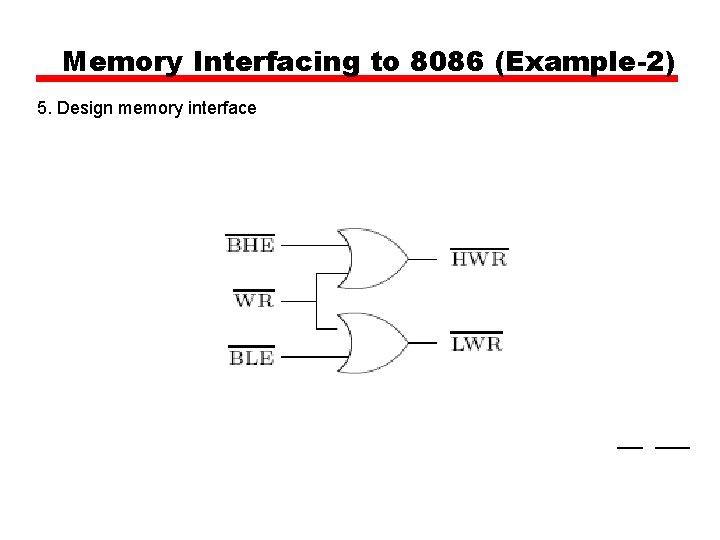

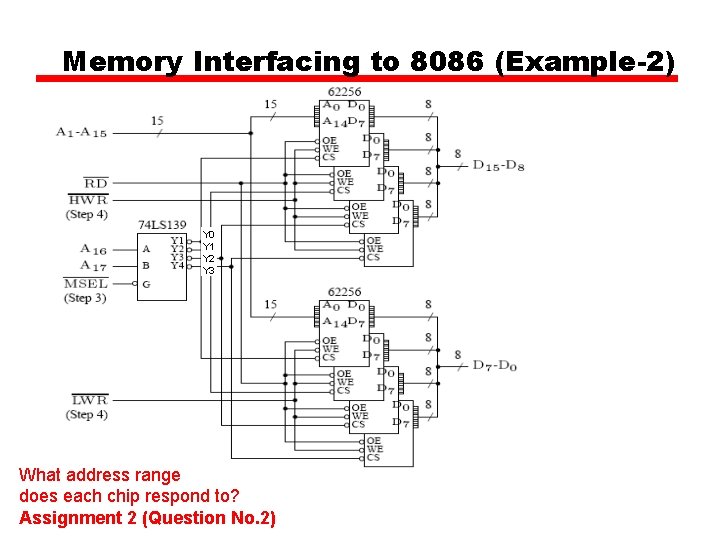

Memory Interfacing to 8086 (Example-2) 5. Design memory interface

Memory Interfacing to 8086 (Example-2) Y 0 Y 1 Y 2 Y 3 What address range does each chip respond to? Assignment 2 (Question No. 2)

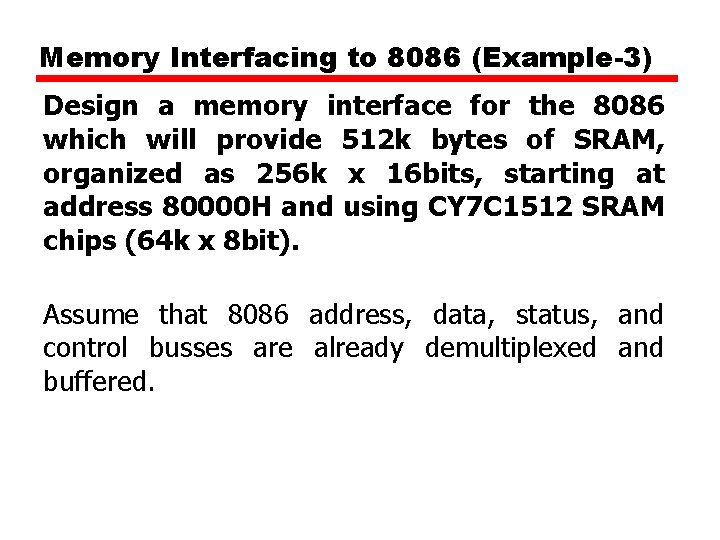

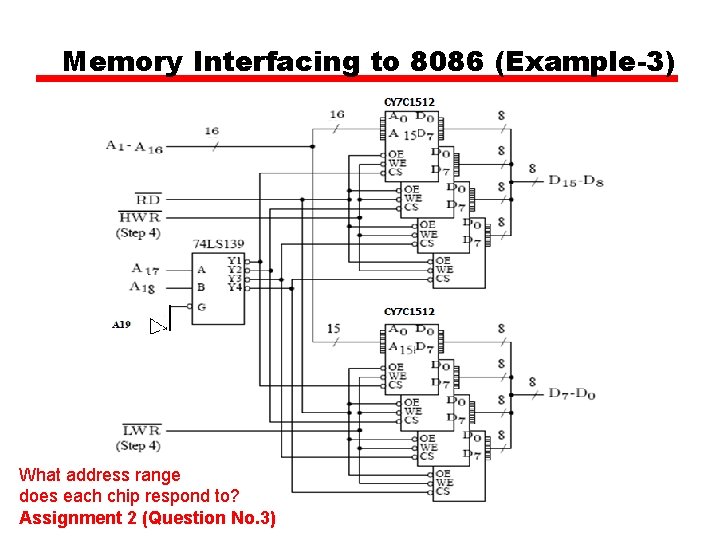

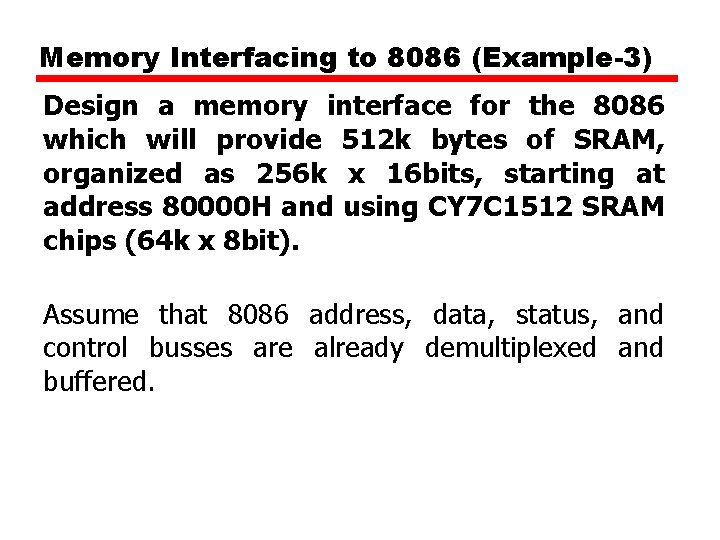

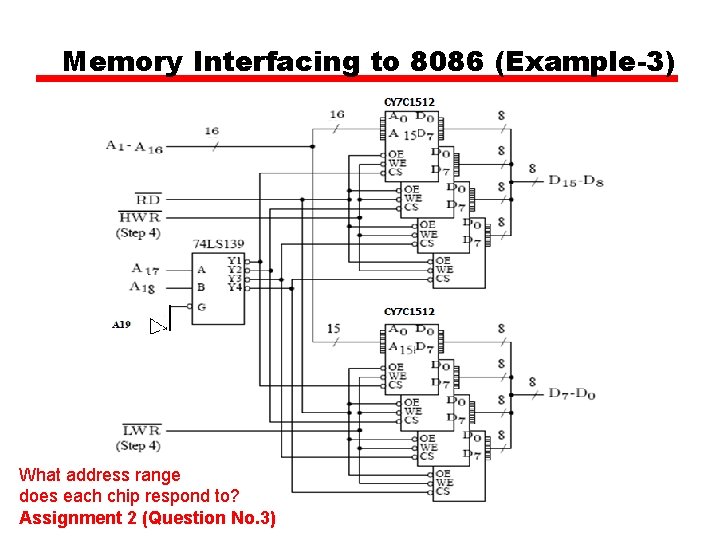

Memory Interfacing to 8086 (Example-3) Design a memory interface for the 8086 which will provide 512 k bytes of SRAM, organized as 256 k x 16 bits, starting at address 80000 H and using CY 7 C 1512 SRAM chips (64 k x 8 bit). Assume that 8086 address, data, status, and control busses are already demultiplexed and buffered.

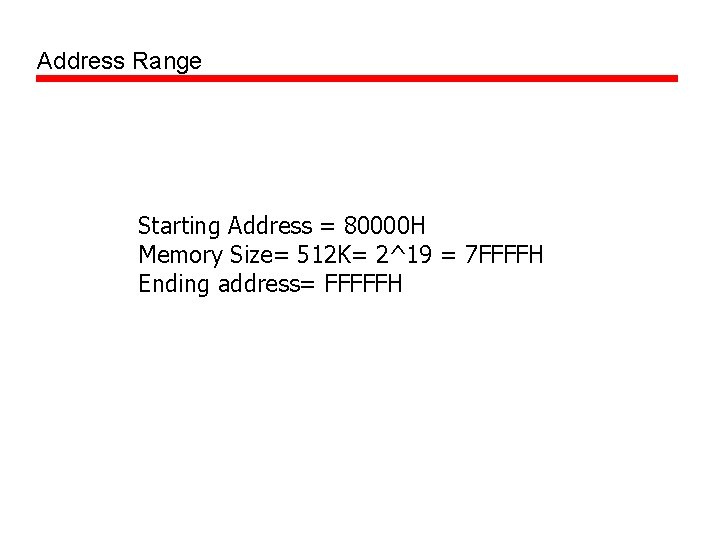

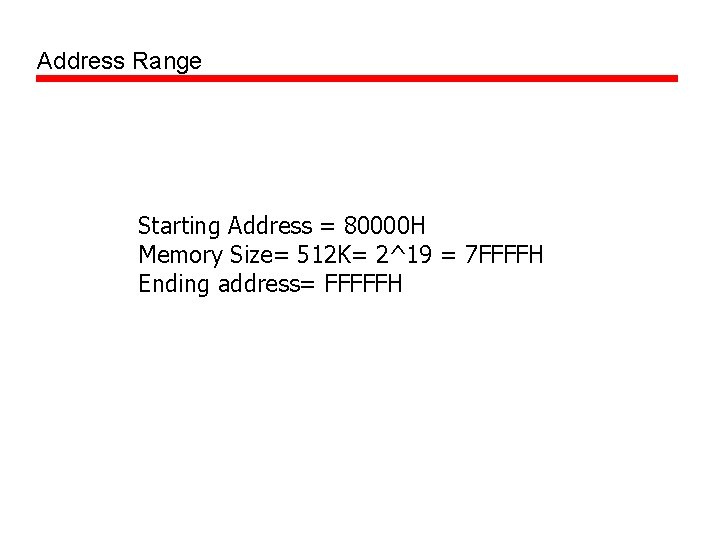

Address Range Starting Address = 80000 H Memory Size= 512 K= 2^19 = 7 FFFFH Ending address= FFFFFH

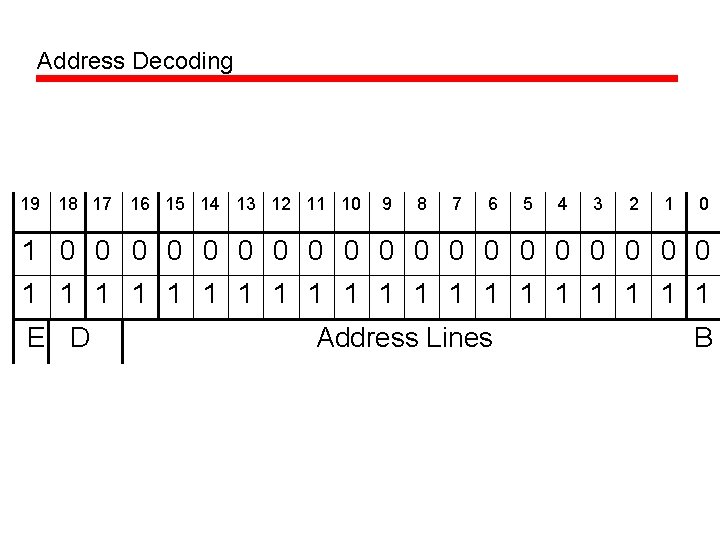

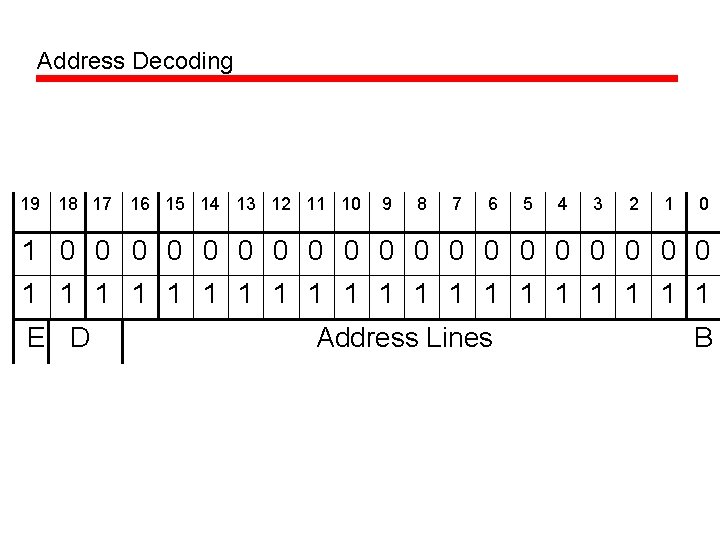

Address Decoding 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 0 0 0 0 1 1 1 1 1 E D Address Lines B

Memory Interfacing to 8086 (Example-3) What address range does each chip respond to? Assignment 2 (Question No. 3)

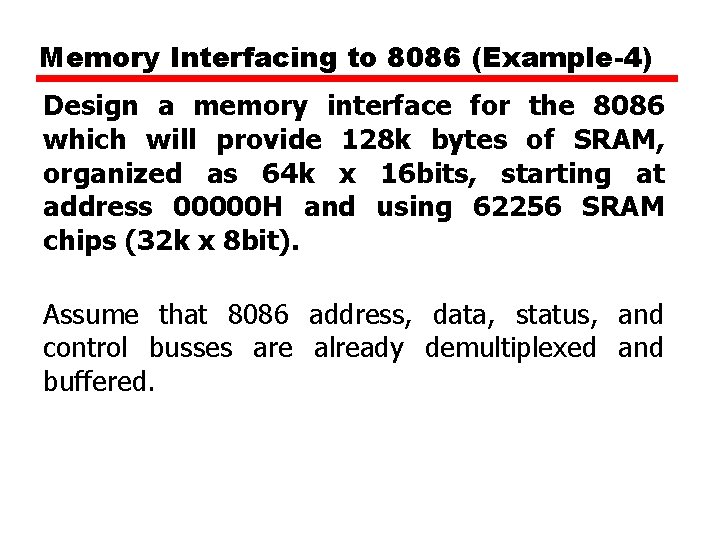

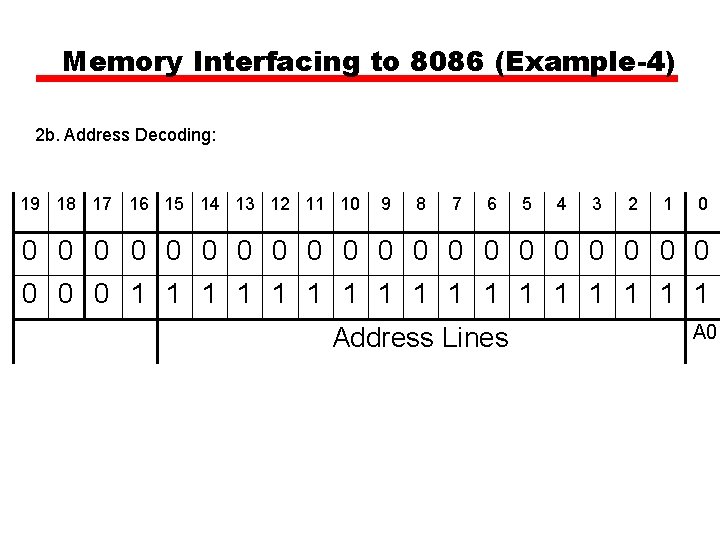

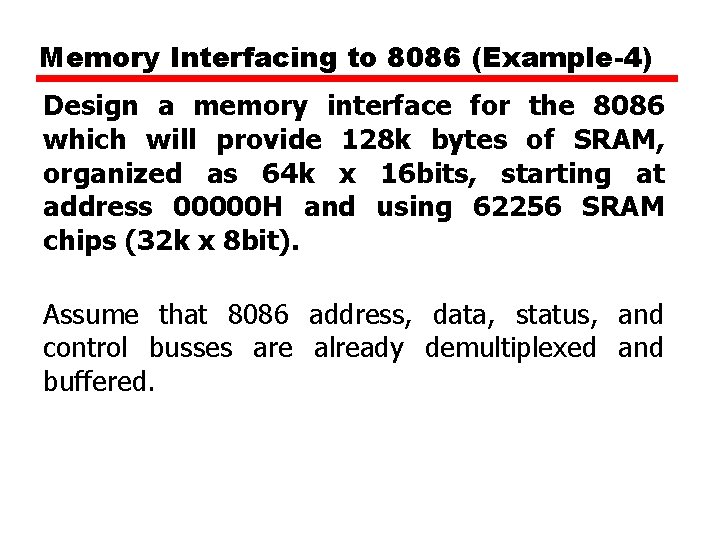

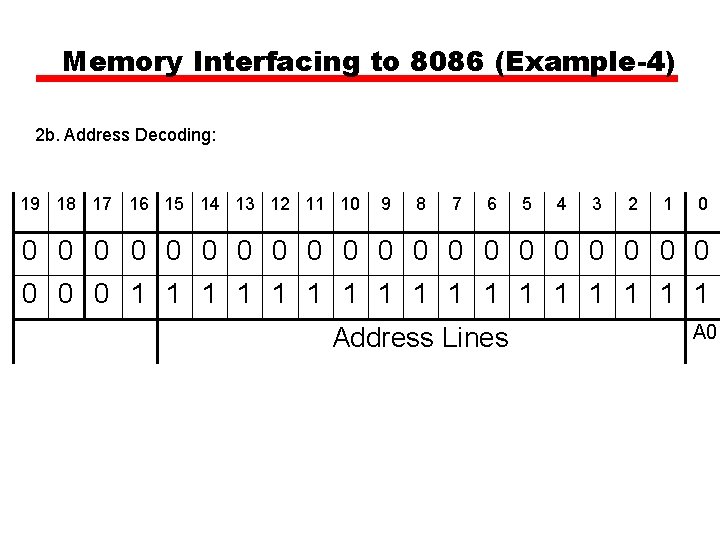

Memory Interfacing to 8086 (Example-4) Design a memory interface for the 8086 which will provide 128 k bytes of SRAM, organized as 64 k x 16 bits, starting at address 00000 H and using 62256 SRAM chips (32 k x 8 bit). Assume that 8086 address, data, status, and control busses are already demultiplexed and buffered.

Memory Interfacing to 8086 (Example-4) 2 b. Address Decoding: 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 0 0 0 0 0 1 1 1 1 1 Address Lines A 0

REVIEW