Microprocesseurs Hautes Performances Andr Seznec IRISAINRIA http www

![18 Activités dans le pipeline du R 4000 § 5] DF (Data Fetch, First 18 Activités dans le pipeline du R 4000 § 5] DF (Data Fetch, First](https://slidetodoc.com/presentation_image_h/1ed39d281306b131b17de10db6c55f40/image-18.jpg)

- Slides: 124

Microprocesseurs Hautes Performances André Seznec IRISA/INRIA http: //www. irisa. fr/caps 1

2 N’oubliez pas Pour comprendre l’architecture, il faut une vision minimale du contexte technologique mais aussi économique Contexte technologique = Cible mouvante Contexte économique « Intel est le plus fort »

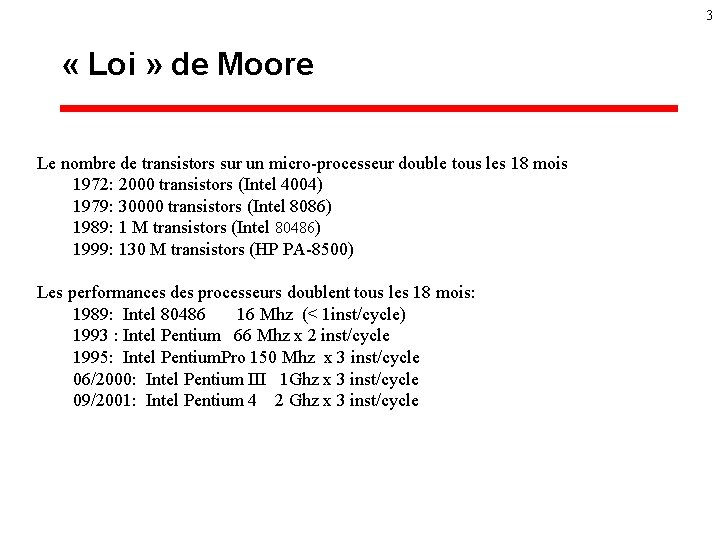

3 « Loi » de Moore Le nombre de transistors sur un micro-processeur double tous les 18 mois 1972: 2000 transistors (Intel 4004) 1979: 30000 transistors (Intel 8086) 1989: 1 M transistors (Intel 80486) 1999: 130 M transistors (HP PA-8500) Les performances des processeurs doublent tous les 18 mois: 1989: Intel 80486 16 Mhz (< 1 inst/cycle) 1993 : Intel Pentium 66 Mhz x 2 inst/cycle 1995: Intel Pentium. Pro 150 Mhz x 3 inst/cycle 06/2000: Intel Pentium III 1 Ghz x 3 inst/cycle 09/2001: Intel Pentium 4 2 Ghz x 3 inst/cycle

4 Quelques repères (sept. 2001) § § Fréquence : 700 Mhz à 2 Ghz Durée d'une opération ALU: 1 cycle Durée d'une opération flottante : 3 cycles Lecture/écriture dans un registre : 1 -3 cycles è souvent un chemin critique. . . § Lecture/écriture du cache L 1: 1 -2 cycles è dilemme taille-associativité-temps d ’accès

5 Quelques repères (2001) § L'intégration : 0. 25 m, 0. 18 m, 0. 125 m (fin 2001) § 10 à 20 millions de transistors de logique § Le reste en mémoire cache: jusqu'à 100 millions de transistors § 20 à 75 Watts è > 100 W bientôt § 400 à 600 broches è > 1000 bientôt

6 Quelques repères (sept. 2001) § Processeurs x 86 pour PC: è bas de gamme: Celeron 733 Mhz, 64 $ è haut de gamme: Pentium 4 2 Ghz, 550 $ § La mémoire DRAM : 0. 15 $ le Mbyte § La mémoire SRAM : 50$ le Mbyte

7 Compatibilité binaire § Une donnée économique : 500 000 de PCs ! è un nouveau jeu d'instructions: RISQUÉ !! § Le monde change (peut-être): è les processeurs enfouis, le multimédia è l'IA 64 arrive è x 86: mutation vers 64 bits (AMD ) ?

8 Architecture 32 ou 64 bits § Architecture 32 bits: l'adresse virtuelle est de 32 bits è Power. PC, x 86, § Architecture 64 bits : l'adresse virtuelle est de 64 bits. è MIPS III, Alpha, Ultrasparc, HP-PA 2. x, IA 64 è En 2005: les jeux ? Word ? § LE MOUVEMENT EST INEXORABLE: è x 86 la rupture?

9 L’angoisse de l’architecte § 400 mm 2 de silicium § 3 générations de technologie en avant § que faire pour obtenir les performances ? è Pipeline è Parallélisme d’instruction è L’exécution spéculative è La hiérarchie mémoire è demain, le parallélisme de processus

Le pipeline 10

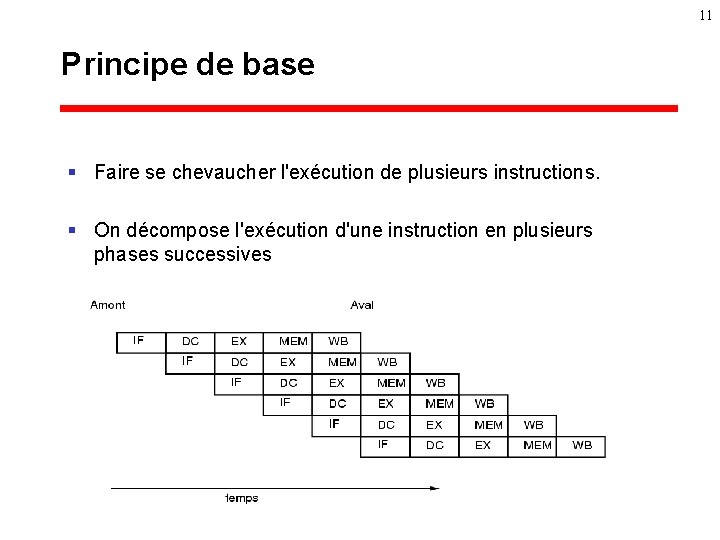

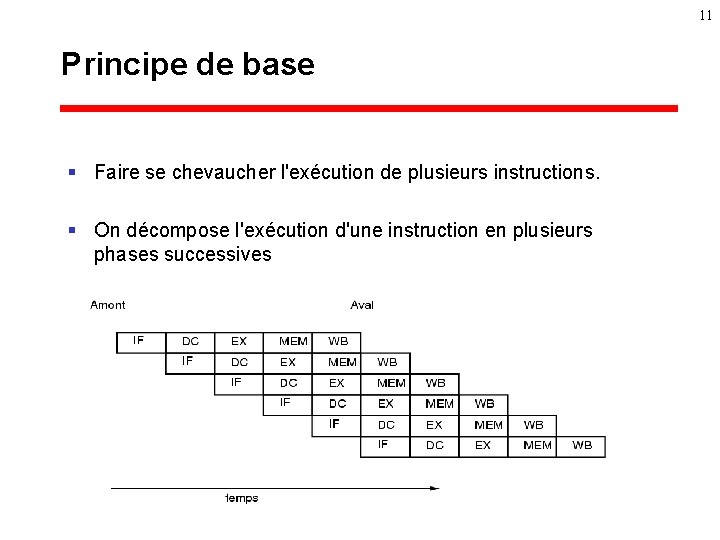

11 Principe de base § Faire se chevaucher l'exécution de plusieurs instructions. § On décompose l'exécution d'une instruction en plusieurs phases successives

12 Pipeline (2) § On ajuste les phases pour qu'elles aient la même durée : è 1 cycle de la machine § L'exécution d'une instruction est allongée è Difficile de découper en phases de même durée è Le découpage entraîne un surcoût : • traversée de buffers § Mais une instruction peut être lancée tous les cycles.

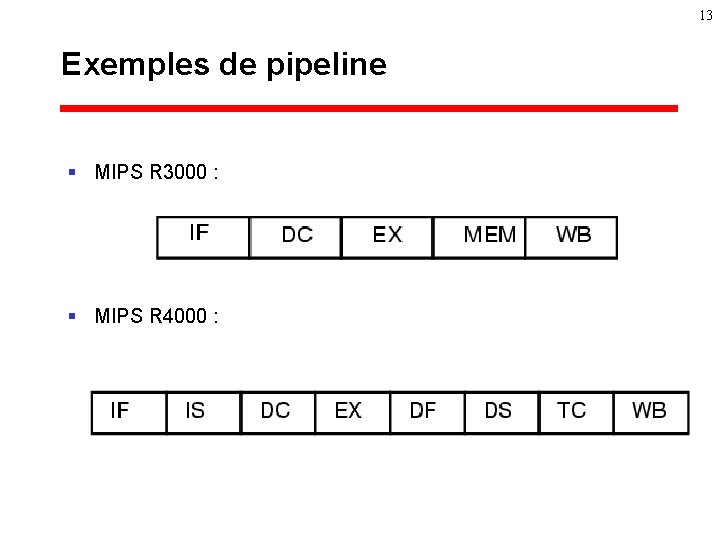

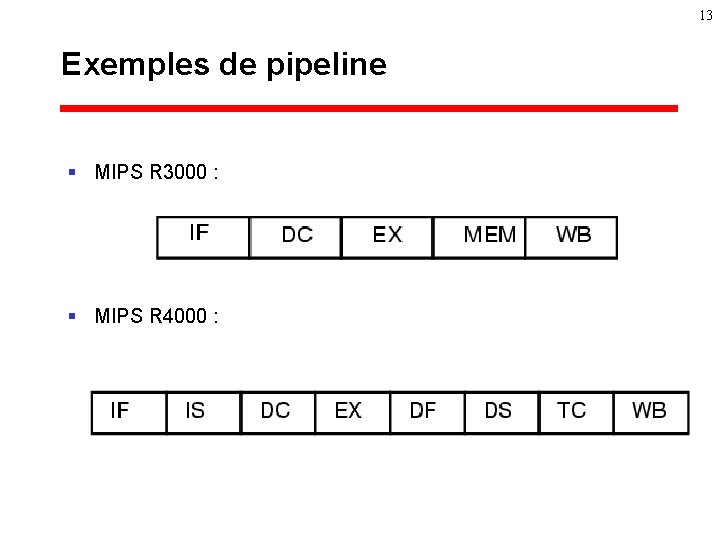

13 Exemples de pipeline § MIPS R 3000 : § MIPS R 4000 :

14 Exemples de pipeline (2) § DEC 21064 : è 2 étages d’exécution § Cypress Sparc è étages EX et MEM confondus

15 Le débit d'un pipeline § Hypothèse on peut séquencer une instruction par cycle § débit maximum d'1 instruction par cycle § Exemple : 5 étages è Sur une machine non pipeline : 3 ns, 4 ns, 3 ns , 2 ns, 4 ns • Durée totale = 16 ns è Sur une machine pipeline : cycle 5 ns = 4 ns + 1 ns (pour les buffers) • Speed-up potentiel : 3. 2 § Limite en multipliant les étages du pipeline : overhead des buffers

16 Attention aux pipelines longs § Sur les entiers : è multiplication : 5 -10 cycles è division : 20 -50 cycles § Sur les flottants : è Addition : 2 -5 cycles è Multiplication: 2 -6 cycles è Division: 10 -50 cycles

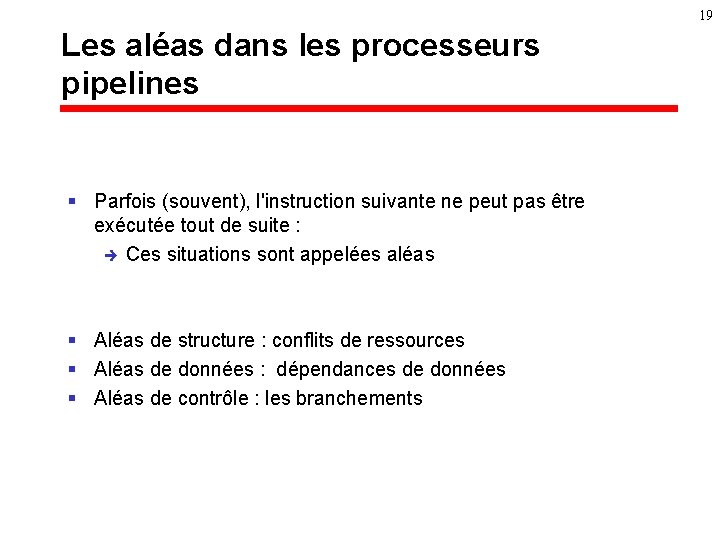

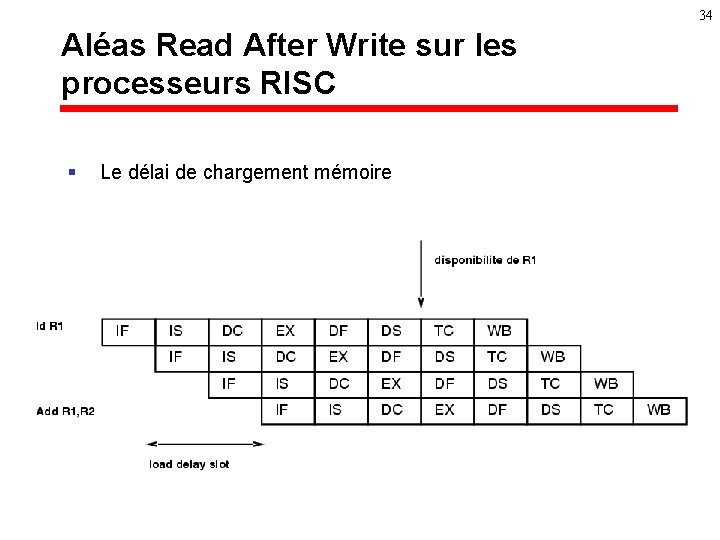

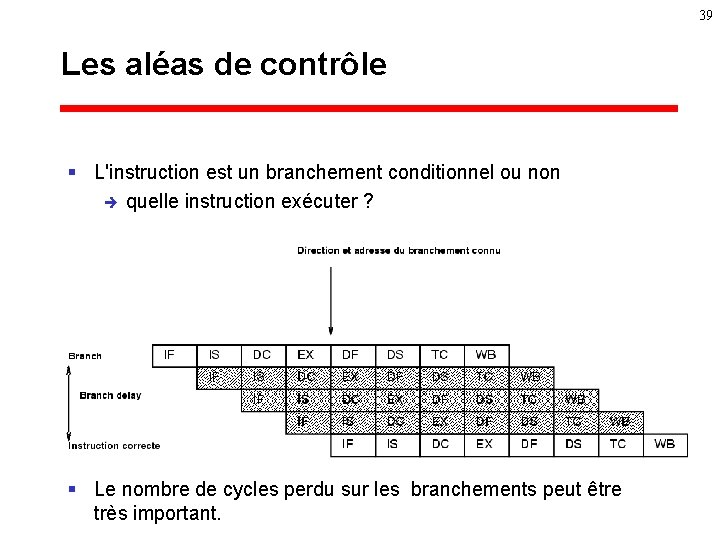

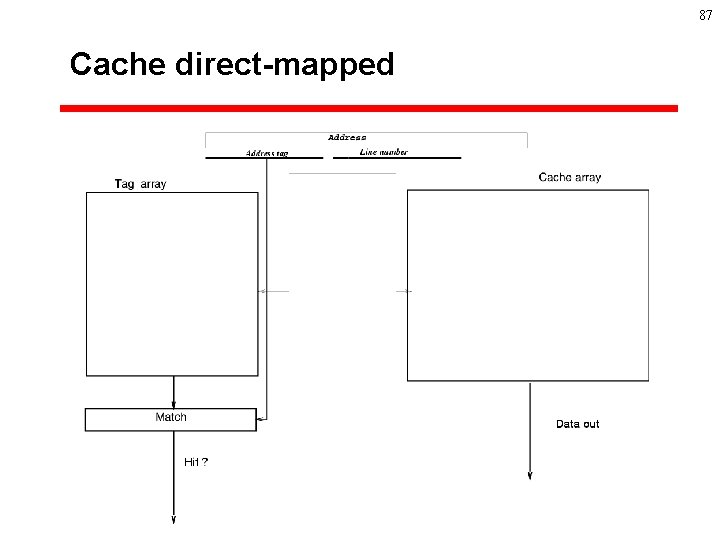

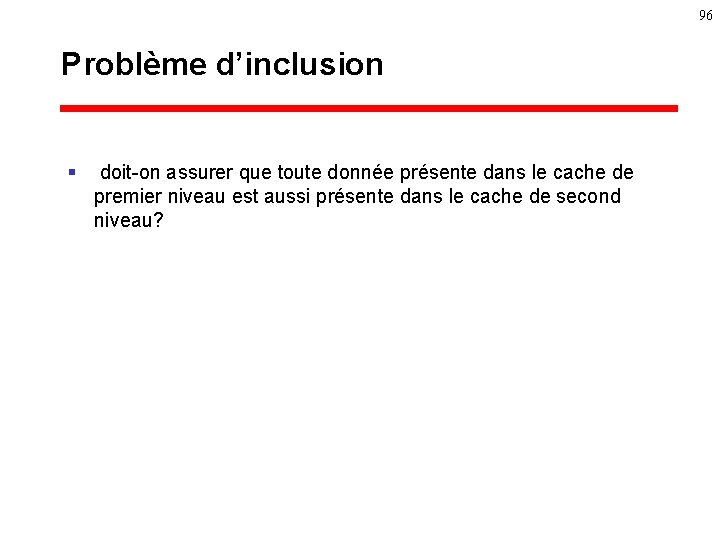

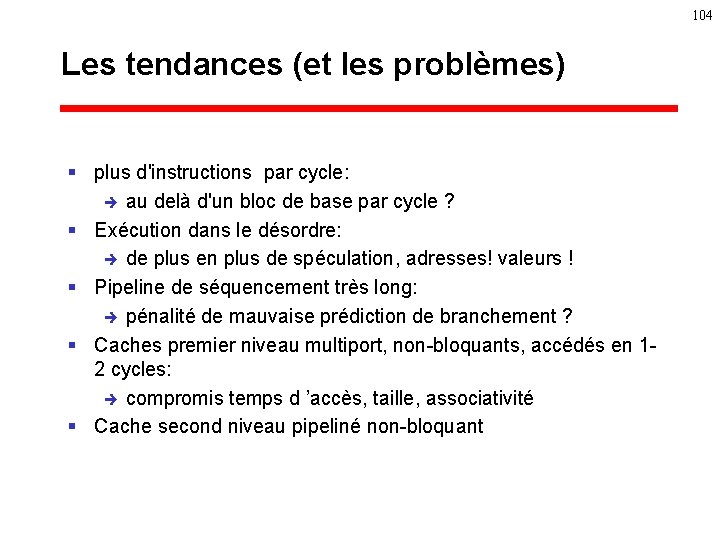

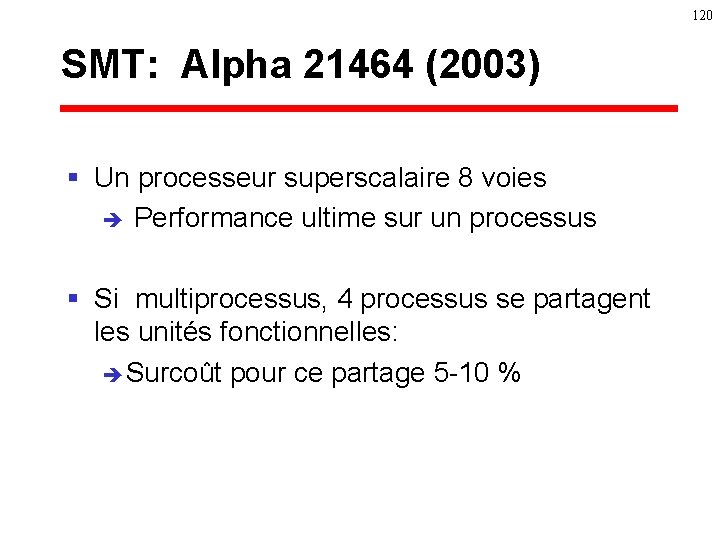

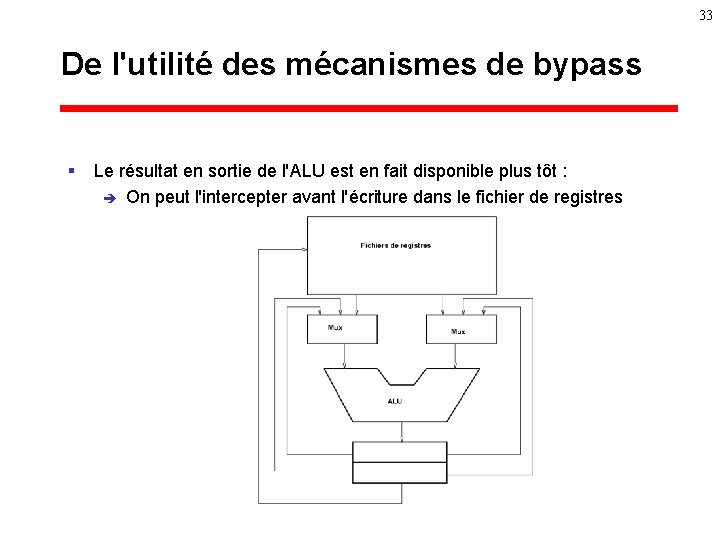

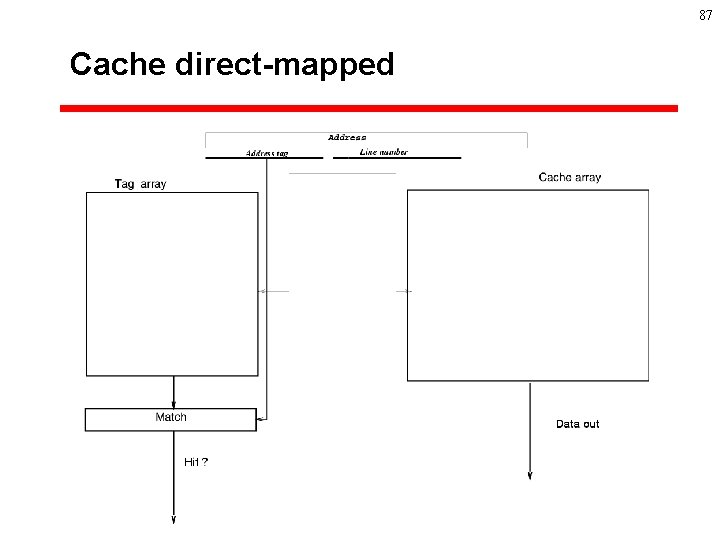

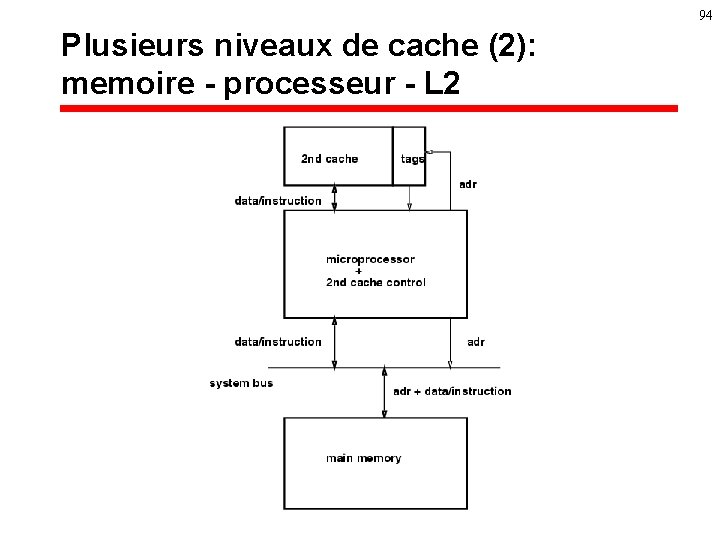

17 Activités dans le pipeline du MIPS R 4000 § 1. IF (Instruction Fetch). è Lecture du cache instructions et lecture du TLB § 2. IS (Instruction Fetch, Second Half) è Fin de lecture du TLB et du cache instructions § 3. RF (Register File): è Décodage de línstruction , lecture des opérandes, vérification des étiquettes § 4. EX (Exécution). è Exécution des opérations registre-registre ou è calcul de l’adresse virtuelle pour les Load/Store ou è calcul de l'adresse virtuelle de la cible pour les branchements

![18 Activités dans le pipeline du R 4000 5 DF Data Fetch First 18 Activités dans le pipeline du R 4000 § 5] DF (Data Fetch, First](https://slidetodoc.com/presentation_image_h/1ed39d281306b131b17de10db6c55f40/image-18.jpg)

18 Activités dans le pipeline du R 4000 § 5] DF (Data Fetch, First Half): è accès au cache de données, et parallèlement, et traduction de l'adresse virtuelle en adresse physique § 6. DS (Data Fetch, Second Half): è fin de l'accès au cache et de la traduction d'adresses. § 7. TC (Tag Check) : è comparaison de l'étiquette du cache avec l'adresse physique du TLB pour déterminer si il y a eu un défaut de cache ou non. § 8. WB (Write Back) : è Ecriture du résultat de l'instruction dans un registre (s'il y a lieu).

19 Les aléas dans les processeurs pipelines § Parfois (souvent), l'instruction suivante ne peut pas être exécutée tout de suite : è Ces situations sont appelées aléas § Aléas de structure : conflits de ressources § Aléas de données : dépendances de données § Aléas de contrôle : les branchements

20 Que faire sur les aléas? § Gestion par matériel : è détecter les aléas et les éviter en retardant l'avancée de l'instruction amont en attendant la résolution de l'aléa. § Gestion par logiciel : è retarder les instructions pour éviter les dépendances, . .

Petite digression: De l'avantage d'un jeu d'instruction régulier pour le pipeline 21

22 RISC versus CISC § Entre 1960 et 1980, la complexité des opérations qui pouvaient être implémentées en matériel a augmenté § les jeux d'instructions ont suivi le même chemin.

23 Complex Instruction Set Computing (CISC). § But: une instruction machine = une instruction langage de haut niveau è VAX, Intel 80 x 86, Motorola 680 x 0, IBM 360 § sur le VAX, une opération arithmétique (2 opérandes, un résultat) : è è è opérandes et résultat soit en registre, soit en mémoire 8 cas Le calcul de l'adresse pour chacun des accès à la mémoire peut être : • absolu : adresse codée dans l'instruction • basé : registre + immédiat • indexé : registre + registre • indirect : lue en mémoire

24 CISC (2) § Codage compact des applications: è peu demandeur en lecture sur les instructions è Tailles d'instructions variables (1 à 15 octets sur le xxx 86) è Temps d'exécution variables et occupation chaotique des ressources: • une même instruction peut occuper 6 fois la mémoire sur le VAX.

25 De la difficulté du pipeline sur les CISC § Taille variable des instructions è pour connaître l'adresse de l'instruction suivante, il faut d'abord décoder l'instruction courante. § Le séquencement des instructions entraîne de nombreux conflits de ressource : è plusieurs utilisations de la même unité fonctionnelles § Pipeline difficile, mais pas impossible : è Le coût de la logique de contrôle est relativement important

26 RISC : Reduced Instruction Set Computer § Concept mis en forme par Patterson et Ditzel (1980), préexistait bien avant. § Principes : è Une seule taille d'instruction : 32 bits en général , simplifie le décodage è Architecture load/store : pas d'opérations avec opérandes ou résultat en mémoire è Modes d'adressage simples : basé et indexé è Instructions simples registre-registre : opérandes dans les registres et résultat dans les registres

27 RISC (2) § Code relativement volumineux : è C= A+B : • load A, R 2 • load B, R 3 • add R 3, R 2, R 1 § pour une même application: è 1. 5 à 2 fois le volume que pour un CISC. § Avantage : se pipeline bien ! è è Lecture de l'instruction et décodage en temps constant. Occupation d'une unité fonctionnelle à un instant précis

28 La saga RISC § § § 1980 : Patterson et Ditzel formalisent le concept 1982 : IBM 801, RISC I et RISC II 1987 -88 : MIPS R 2000, Sparc 1990 : IBM Power, Intel i 860 1992 - : DEC Alpha, TI Supersparc, MIPS R 4000, R 8000 et R 10000, HP 8000, Ultrasparc , . . § Intel xxx 86 fait de la résistance !

29 Jeux d'instructions des processeurs RISC Principes communs § Une seule taille d'instruction : 32 bits en général è simplifie le décodage et le calcul de l'anticipation de l'adresse suivante § Architecture load/store § Modes d'adressage simples : basé et indexé § Instructions simples registre-registre § Presque consensus: è 32 registres è Bloc de registres distincts pour les flottants

Retour au pipeline 30

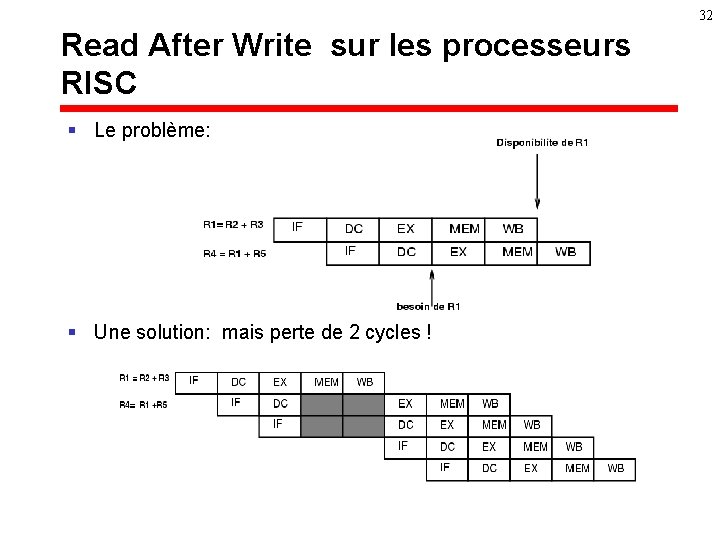

31 Les aléas de données § L’exécution pipeline d'une séquence d'instructions doit produire le même résultat qu'une exécution séquentielle. § 3 types d'aléas peuvent se produire: i précède j è RAW (Read After Write) : è è • j utilise un résultat de i comme opérande: – le résultat doit être écrit par avant que j ne le lise. WAR (Write After Read) : • j écrit un résultat dans une source de i – i doit avoir lu sa source avant que j ne l'écrive WAW (Write After Write) : • i et j écrivent leurs résultats à la même place – j doit écrire son résultat après i

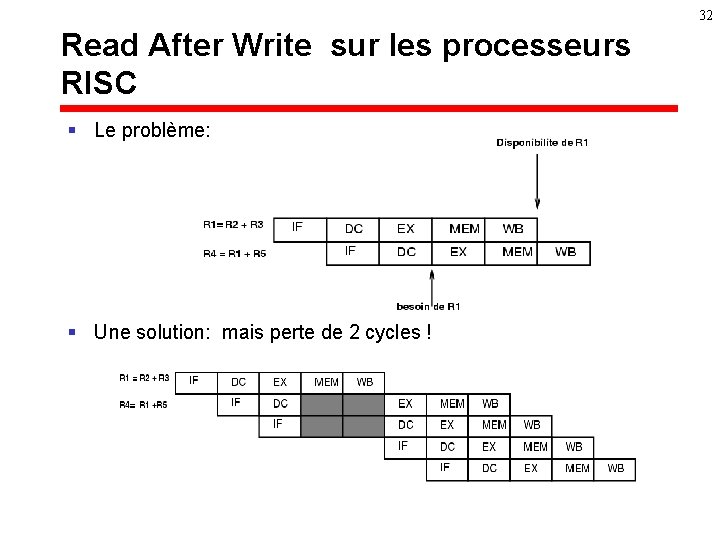

32 Read After Write sur les processeurs RISC § Le problème: § Une solution: mais perte de 2 cycles !

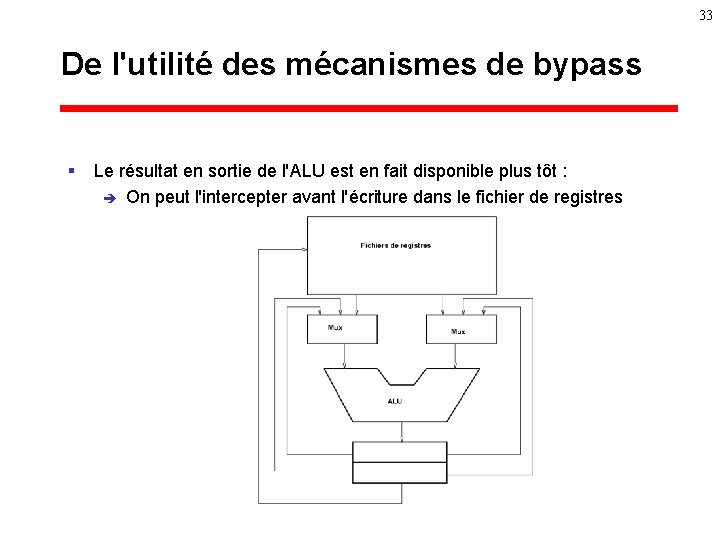

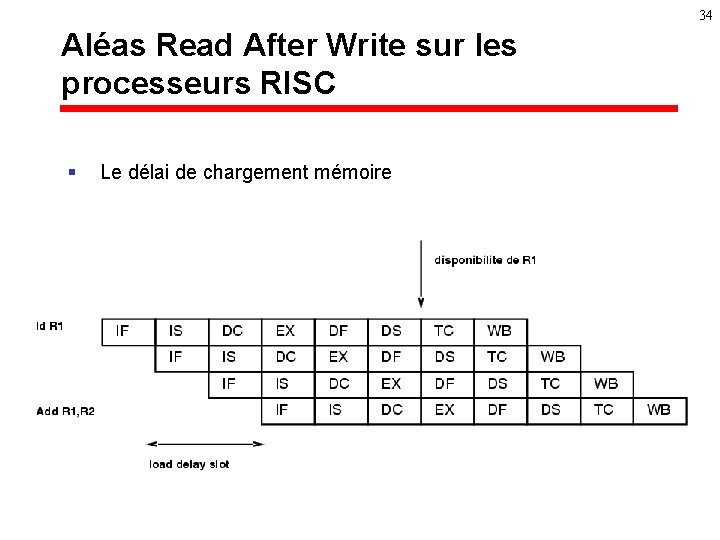

33 De l'utilité des mécanismes de bypass § Le résultat en sortie de l'ALU est en fait disponible plus tôt : è On peut l'intercepter avant l'écriture dans le fichier de registres

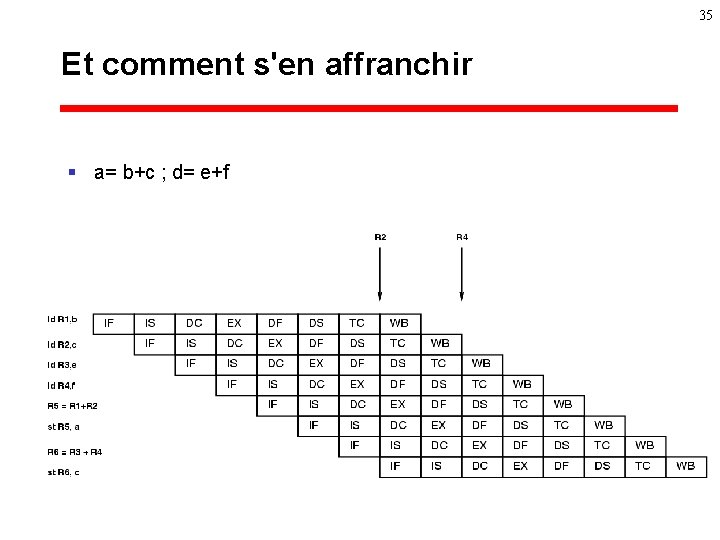

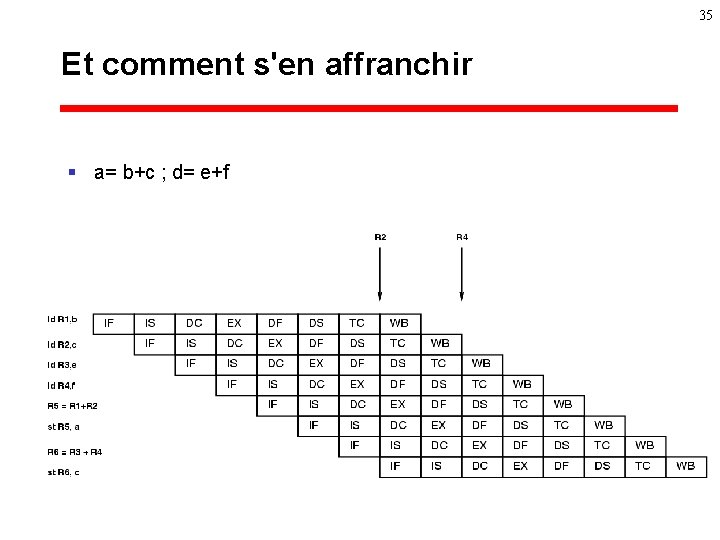

34 Aléas Read After Write sur les processeurs RISC § Le délai de chargement mémoire

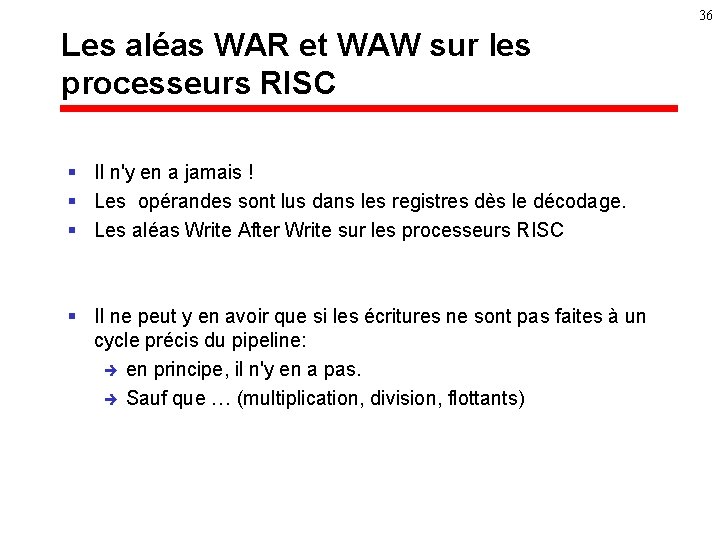

35 Et comment s'en affranchir § a= b+c ; d= e+f

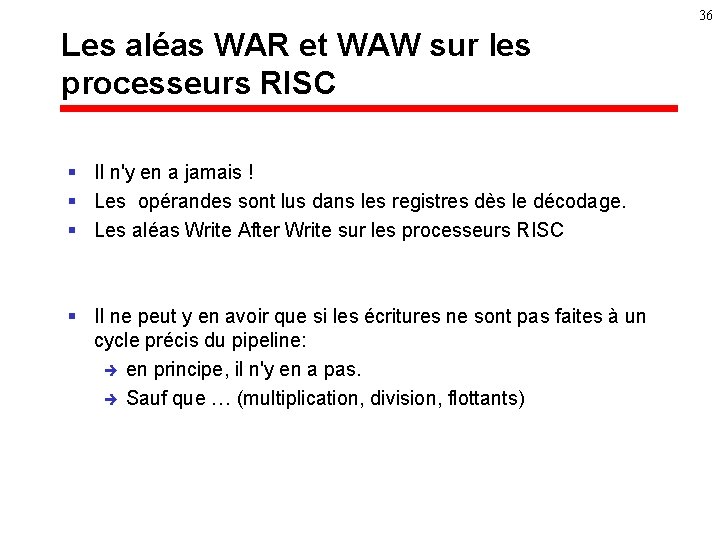

36 Les aléas WAR et WAW sur les processeurs RISC § Il n'y en a jamais ! § Les opérandes sont lus dans les registres dès le décodage. § Les aléas Write After Write sur les processeurs RISC § Il ne peut y en avoir que si les écritures ne sont pas faites à un cycle précis du pipeline: è en principe, il n'y en a pas. è Sauf que … (multiplication, division, flottants)

37 Les aléas de données sur les processeurs CISC § Tous les types d'aléas sont possibles : è Read After Write è Write after Read : • le nombre des opérandes d'une instruction est très élevé. è Write after Write : • la durée d'exécution des instructions est tout à fait variable § Pipeliner l'exécution de plusieurs instructions sur un processeur CISC requiert beaucoup de précautions.

38 RISC versus CISC § RISC : è mécanismes de contrôle plus simple è possibilité de réordonnancement de code è RISC : coût et temps de conception plus réduit. è RISC : taille du composant plus réduit (à performance et technologies équivalentes) § CISC : volume de code plus réduit

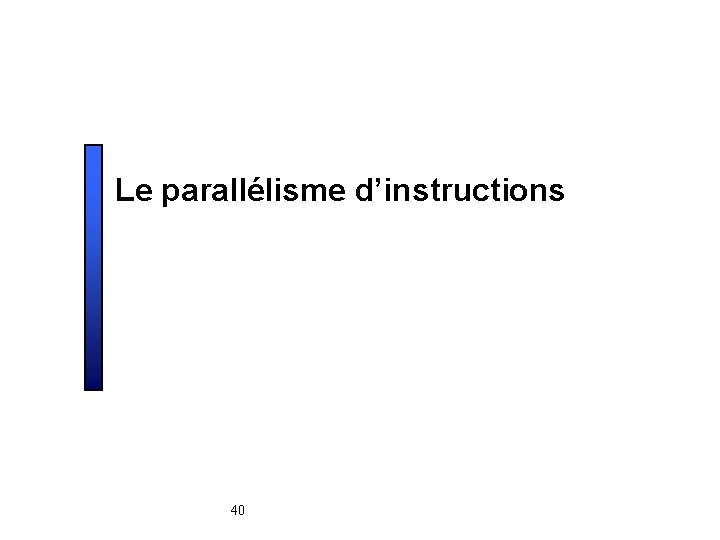

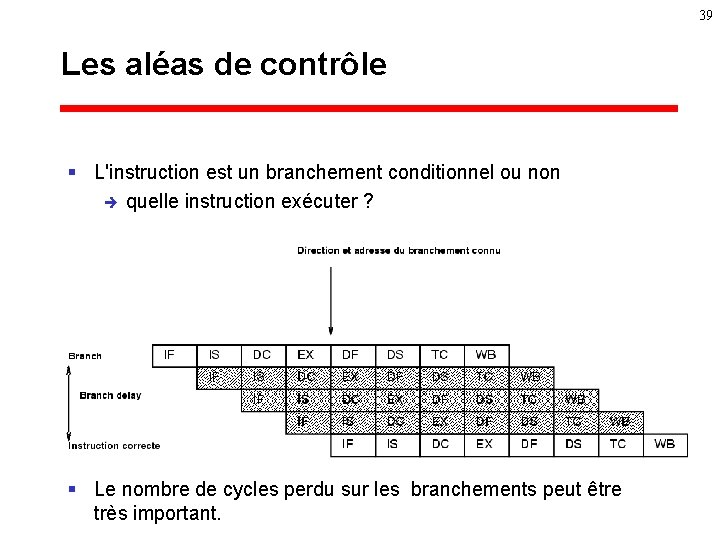

39 Les aléas de contrôle § L'instruction est un branchement conditionnel ou non è quelle instruction exécuter ? § Le nombre de cycles perdu sur les branchements peut être très important.

Le parallélisme d’instructions 40

41 Toujours plus de puissance : les processeurs superscalaires et VLIW § Processeurs RISC jusqu'en 1991 : è objectif 1 instruction par cycle § mais comment aller plus vite : è Diviser le temps de cycle et multiplier les étages : superpipeline è Lancer plusieurs instructions par cycle : • qui contrôle: – Le matériel: superscalaire – Le compilateur: VLIW (Very Long Instruction Word)

42 Les processeurs superscalaires § le droit de lancer les instruction par cycle est géré à l'exécution par matériel: è aléas de ressource : e. g. partage d'une même unité fonctionnelle è è aléas de données : ne pas lancer 2 opérations dépendantes aléas de contrôle : attention aux branchements § permet la compatibilité binaire d'une génération de processeurs à l'autre: è du processeur RISC (1 instruction par cycle) au processeur superscalaire (x instructions par cycle) § TOUS LES PROCESSEURS ANNONCES DEPUIS 1993 SONT SUPERSCALAIRES

43 VLIW: Very Long Instruction Word § Parallélisme contrôlé par logiciel: è Le compilateur est en charge de contrôler les unités fonctionnelles: • gère les aléas de contrôle, de données et de ressources § Problème: l’absence de compatibilité binaire § Pas utilisé pour les processeurs généraux

44 Superscalaire : les problèmes § Parallélisme d'instructions limité: è 3 à 8 instructions par cycle è Le fichier de registres: • le nombre de ports augmentent : chemin critique § La fourniture des instructions § La gestion des dépendances de données § Les branchements.

45 superscalaire « naturel » 1995 § les unités fonctionnelles existantes dans les microprocesseurs ne sont pas dupliquées: è ALU è Unité flottante è Accès à la mémoire è Unité de séquencement § DEC 21064, IBM Power, Power 601 § Certaines unités fonctionnelles dupliquées : è TI Super. Sparc : 2 ALUs è MIPS R 8000, IBM Power 2 : 2 opérateurs flottants, 2 accès au cache

46 Le degré superscalaire § Difficile à définir: è « performance qu’on est certain de ne pas dépasser » § 4 inst / cycles sur presque tous les processeurs existants § 6 inst / cycles sur Itanium § 8 inst / cycles sur le (futur) Alpha 21464 § 16 -32 sur Alpha 21964 ? ? En 2012 ? : =)

47 Superscalaire : les problèmes § Parallélisme d'instructions limité : 3 à 8 instructions par cycle § Le fichier de registres : è le nombre de ports augmentent è chemin critique § La fourniture des instructions aux UFs § La dépendances de données § Les branchements.

Exécution dans l’ordre ou dans le désordre § Respecter l’ordre du programme ou non: è Ah! Si toutes latences étaient connues statiquement, … § Les « partisans » de l ’ordre: è Ultra. Sparc 3, Itanium è Le compilateur doit faire le travail § Les « partisans » du désordre: è Alpha 21264, Pentium III, Athlon, Power (PC), HP -PA 8500 48

Pourquoi l’exécution dans l’ordre § simple à mettre en œuvre è moins de transistors è moins de temps de développement è horloge rapide (discutable) § pipeline moins profond § le compilateur « voit » tout: è la micro-architecture è le programme 49

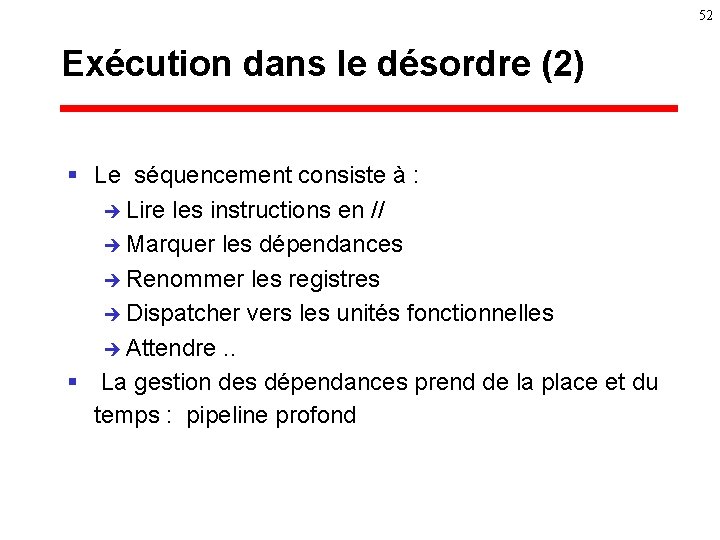

Pourquoi l’exécution dans le désordre § l ’ILP statique est limité dans les codes non réguliers § le compilateur ne « voit » pas tout: è latences inconnues à la compilation è (in)dépendances inconnues à la compilation § pas besoin de recompiler è hum !! 50

51 Exécution dans le désordre (1) § Principe : è exécuter les instructions dès que : opérandes disponibles et unités fonctionnelles disponibles § Mise en œuvre : è une grande fenêtre d'instructions où on choisit les instructions exécutables

52 Exécution dans le désordre (2) § Le séquencement consiste à : è Lire les instructions en // è Marquer les dépendances è Renommer les registres è Dispatcher vers les unités fonctionnelles è Attendre. . § La gestion des dépendances prend de la place et du temps : pipeline profond

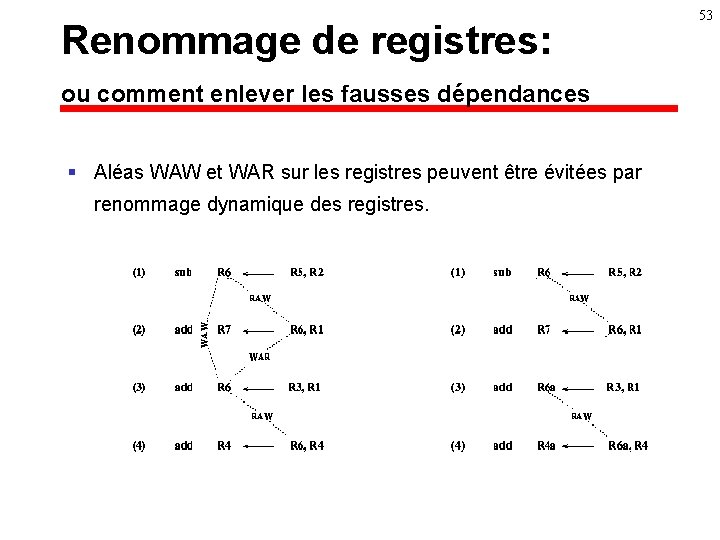

53 Renommage de registres: ou comment enlever les fausses dépendances § Aléas WAW et WAR sur les registres peuvent être évitées par renommage dynamique des registres.

54 Dépendances mémoires § pour exécuter une écriture sur la mémoire, on a besoin de la donnée à écrire § en dehors de toute information, toute lecture mémoire est potentiellement dépendante de toute écriture mémoire précédente § solution (provisoire): è Calcul des adresses dans l'ordre du programme è Dépassement des écritures par les lectures avec détection des aléas

55 Dépendances mémoires (2) § Solution (actuelle): è Exécution optimiste dans le désordre è Réparation si la dépendance existe è Pb: coût de la réparation § Prochaine génération: la prédiction de dépendances sur la mémoire è Moshovos et Sohi, Micro'30, décembre 1997 è Chrysos et Emer, ISCA ’ 26, juin 1998

56 Les dépendances de contrôle § 15 à 30% des instructions sont des branchements. § La cible et la direction d'un branchement sont connues très tard dans le pipeline : è Cycle 7 sur le DEC 21264 è Cycle 11 sur l'Intel Pentium II è Cycle 18 sur l ’Intel Pentium 4 § Pas question de perdre tous ces cycles !

Prédiction de branchement dynamique § Garder un historique des derniers passages et utiliser cet historique pour anticiper le branchement § Mise en œuvre: une table lue en même temps que le cache d’instructions § On prédit: è la cible et la direction des branchements è les retours de procédures è les branchements indirects 57

58 Branchements conditionnels § Plus important de prédire la direction que la cible è Schémas de prédiction de plus en plus complexes • adresse • historique des derniers branchements – global ou local • schémas hybrides

59 Prédiction de branchement § § 1992: DEC 21064, schéma à 1 bit 1993: Pentium, schéma à 2 bits 1995: Pentium. Pro, historique local 1998: DEC 21264, prédicteur hybride

Prédiction de branchement: tendance générale § Schémas de plus en plus complexes § Découplage de la prédiction de l'adresse et de la direction § Pile de retour pour les procédures § Support dans les jeux d'instructions pour l’exécution spéculative: è CMOV è prédicats de l ’IA 64 60

Exécution dans le désordre: Savoir « défaire » § Mauvaise prédiction de branchement § Mauvaise anticipation d'indépendance § Interruption, exception § Valider dans l’ordre du programme § Ne rien faire de définitif dans le désordre 61

62 Savoir « défaire » § Une copie du fichier de registres est mise à jour dans l'ordre du programme § ou § Une <<carte>> registres logiques-registres physiques est sauvegardée § Les écritures en mémoire sont faites à la validation

Petit retour sur le pipeline 63

Le pipeline: de plus en plus profond § Plus on stresse l'horloge, moins on en fait en un cycle. § 1 cycle = traversée d’une ALU + rebouclage § Communications intra-CPU de + en + longues: è plusieurs cycles pour traverser le composant § Le contrôle est de + en + complexe: è plus d’instructions en // è plus de spéculation 64

Quelques profondeurs de pipeline § § 12 -14 cycles sur l’Intel Pentium III 10 -12 cycles sur l’AMD Athlon 7 -9 cycles sur l’Alpha 21264 9 cycles sur l’Ultra. Sparc § 10 cycles sur l’Itanium (fin 2000) § 20 cycles sur le Pentium 4 (fin 2000) § Et ça ne va pas s’améliorer !! 65

Retour au jeu d’instruction 66

67 Un jeu d’instruction pour le parallélisme d ’instructions § parallélisme explicite entre les instructions (à la VLIW) § support pour l’exécution spéculative § Compatibilité assurée par le matériel

68 Le jeu d’instruction EPIC IA 64 § EPIC IA 64 = è RISC è + plus de registres (128 entiers, 128 flottants) è + 3 instructions codées en 128 bits è + 64 registres de prédicats è + dépendances gérées par le matériel è + (? ) Advanced Loads § le compilateur gère le parallélisme d’instructions, § mais la compatibilité est assurée par le matériel

69 IA 64 § L’angoisse de la page blanche !? è è è -Support matériel au pipeline logiciel • Rotating registers • Gestion de boucle -Fenêtres de registres: à taille variable! -Pas d’adressage basé -adressage post-incrémenté - (? ) Advanced Loads

Intel Pentium. Pro ou comment s’abstraire du jeu d’instruction 70

71 De la difficulté du superscalaire sur les jeux d'instruction non réguliers § Les difficultés liées au jeu d'instructions: è è Taille d'instructions variables (1 à 15 bytes) Plusieurs occupations successives d'une même ressource Nombre d'itérations inconnu sur certaines instructions Temps d'exécution imprévisible pour certaines instructions

72 Intel Pentium. Pro: la solution adoptée § Une constation : è les jeux d'instruction RISC sont plus simples à pipeliner et exécuter en parallèle § La solution : è exécuter du "code " RISC ! § Comment ? è Le décodage des instructions est remplacée par une traduction en è pseudo-code RISC

73 Intel Pentium. Pro § MEM + REG MEM: è 4 microoperations (RISC-like) § La plupart des instructions sont traduites en 1 à 4 microopérations en un cycle § Certaines instructions ne peuvent pas être traduites en un nombre fixé de microopérations (boucles, instruction flottantes transcendantales , . . ) : è traduites en plusieurs cycles § 3 traducteurs en parallèles (1 complexe + 2 simples)

74 Intel Pentium. Pro § Les microopérations venant de différentes instructions sont executées dans le désordre comme sur les processeurs superscalaires out-of-order RISC è è renommage de registres è stations de réservations. . è Buffer de réordonnancement è Jusqu'à 5 microopérations par cycle.

75 Pentium 4 et Trace cache: juste un coup plus loin § Pourquoi retraduire les instructions x 86 à chaque nouvelle utilisation ? è Perte de temps è Consommation électrique § Idée simple mais logique: è Mémoriser les mopérations dans un cache: le Trace Cache

Jeu d’instruction: est-ce important ? § 32 ou 64 bits: è vers l’abandon (ou la mutation !) d’x 86 è AMD x 86 -64 ! § Les performances: è et x 86 ? : =) è en flottant !! è à technologie égale ? 76

Jeu d’instruction: est-ce important (2) ? § x 86: traduction en m. Opérations è 4 cycles perdus ! è Ou utilisation d’un trace cache § x 86 pas assez de registres flottants § Alpha 21264: 2 opérandes 1 résultat è le + performant des RISCs § Itanium: l ’IA 64 dans l’ordre è 800 Mhz en 0. 18 m è Alpha 21164 700 Mhz 0. 35 m (1997) 77

La hiérarchie mémoire 78

79 La mémoire § § Plus une mémoire est grande, plus son temps d’accès est long 3 types de mémoire è banc de registres • peu d’entrées, temps d’accès court (cycle), plusieurs ports è mémoire dynamique (DRAM) • mémorisation d’une charge sur une capacité, 1 transistor par bit • grande densité d’intégration (16 -64 Mbits) • temps d’accès long: 50 -100 ns • utilisé comme mémoire principale è mémoire statique (SRAM) • mémorisation par bouclage de 2 portes: 1 -4 Mbits • cher • temps d’accès court: 5 -10 ns

80 Latence mémoire § La latence mémoire n’est pas seulement constituée par le temps d’accès DRAM è traduction d’adresse è traverser les broches du processeur et le bus externe è multiplexage si plusieurs bancs mémoires § Latence mémoire principale: 100 -200 ns è à 1 GHz, ça fait 100 à 200 cycles CPU § problème !!

81 Les caches § La mémoire est: è bon marché et lente ou è chère et rapide. § Les caches : donner l'illusion d'une mémoire globale rapide. § Principe: utiliser les propriétés de localité temporelles et spatiales des applications

82 Principes de fonctionnement d'un cache § Le cache est une petite mémoire rapide dont le contenu est une image d'un sous-ensemble de la mémoire. § Lors d'une référence à la mémoire, la requête est: è è 1. ) présentée au cache 2. ) si la donnée absente alors la requête est présentée à la mémoire principale (ou à un second niveau de cache).

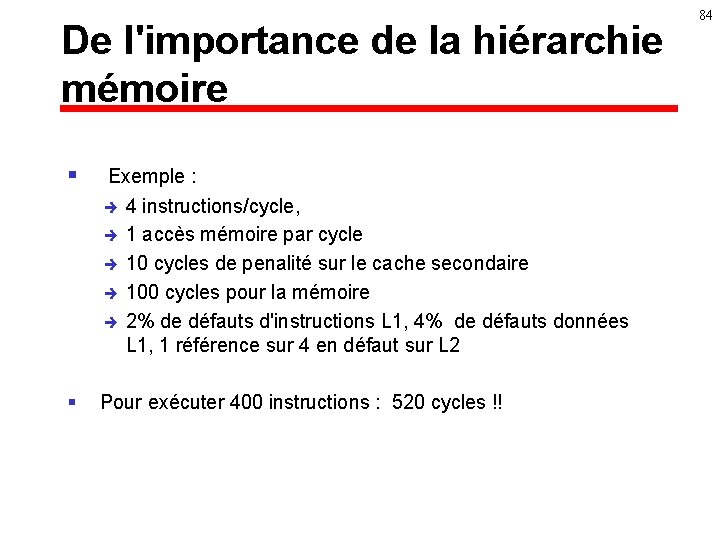

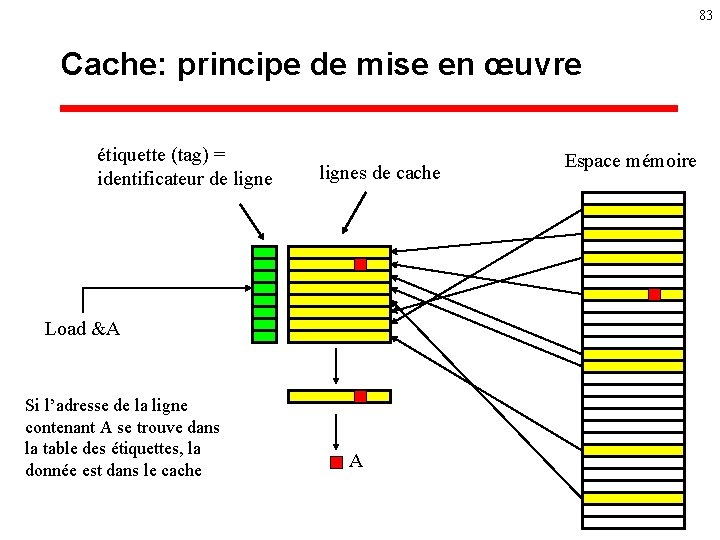

83 Cache: principe de mise en œuvre étiquette (tag) = identificateur de lignes de cache Load &A Si l’adresse de la ligne contenant A se trouve dans la table des étiquettes, la donnée est dans le cache A Espace mémoire

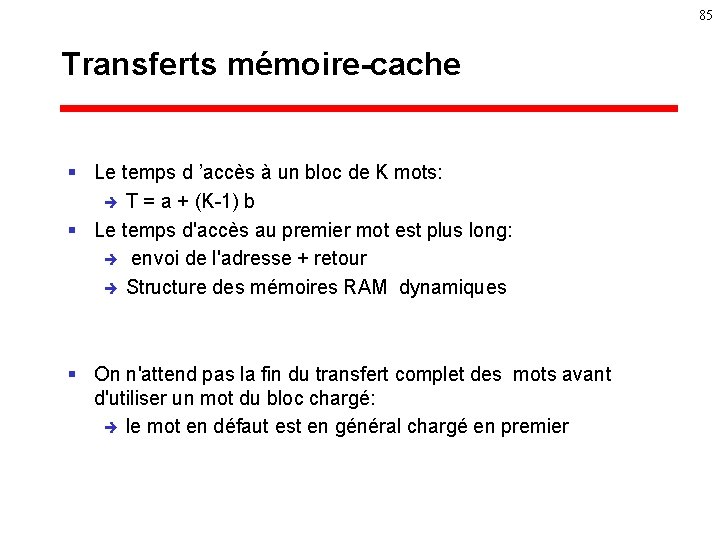

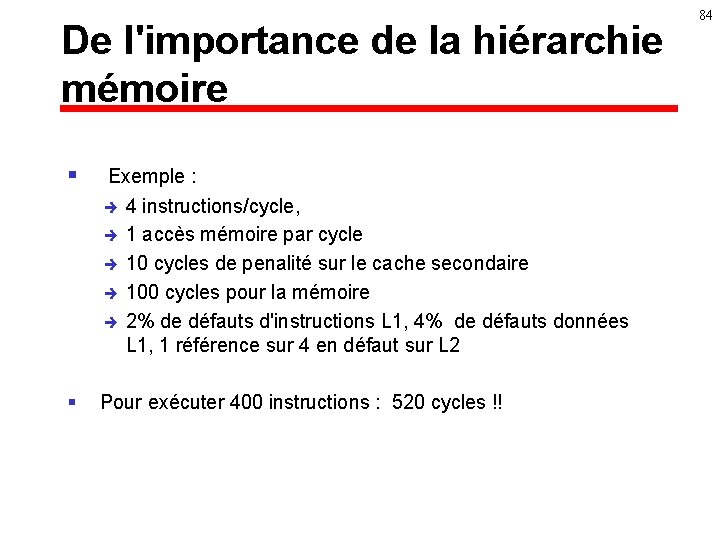

De l'importance de la hiérarchie mémoire § Exemple : è è è 4 instructions/cycle, 1 accès mémoire par cycle 10 cycles de penalité sur le cache secondaire 100 cycles pour la mémoire 2% de défauts d'instructions L 1, 4% de défauts données L 1, 1 référence sur 4 en défaut sur L 2 § Pour exécuter 400 instructions : 520 cycles !! 84

85 Transferts mémoire-cache § Le temps d ’accès à un bloc de K mots: è T = a + (K-1) b § Le temps d'accès au premier mot est plus long: è envoi de l'adresse + retour è Structure des mémoires RAM dynamiques § On n'attend pas la fin du transfert complet des mots avant d'utiliser un mot du bloc chargé: è le mot en défaut est en général chargé en premier

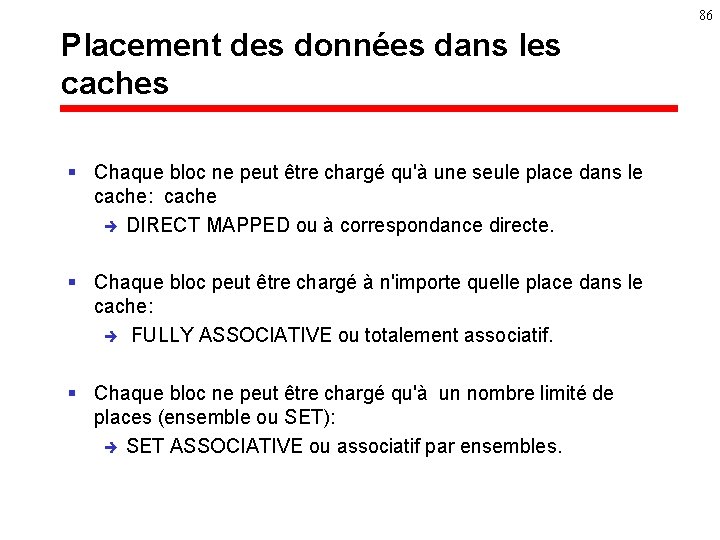

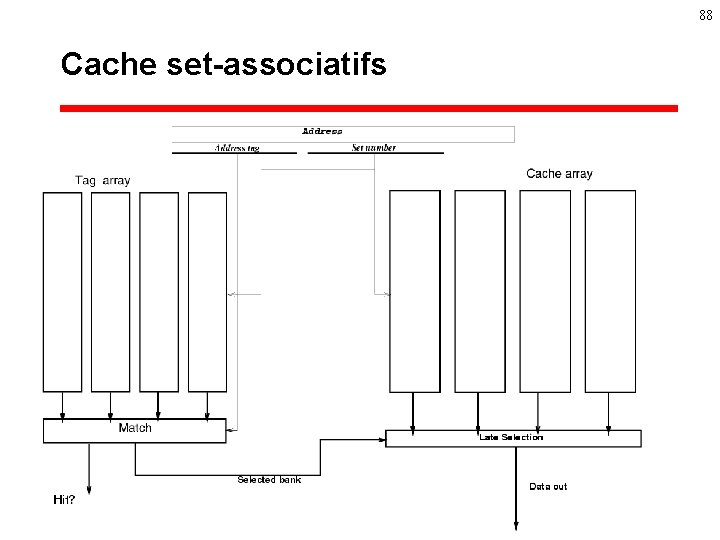

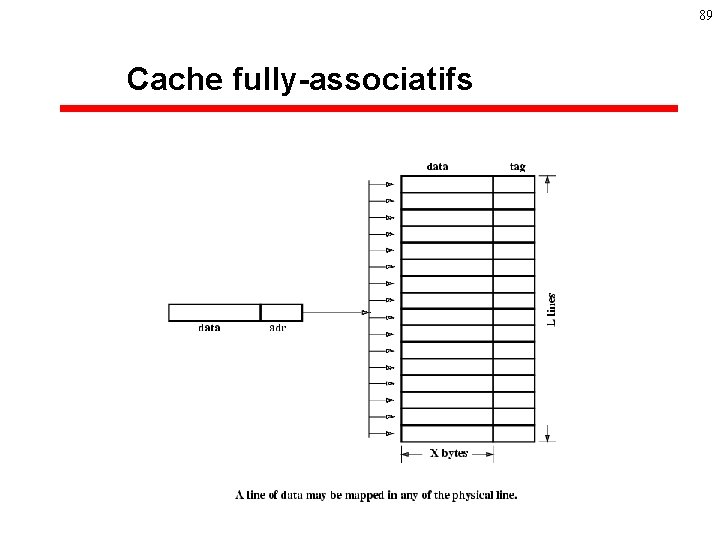

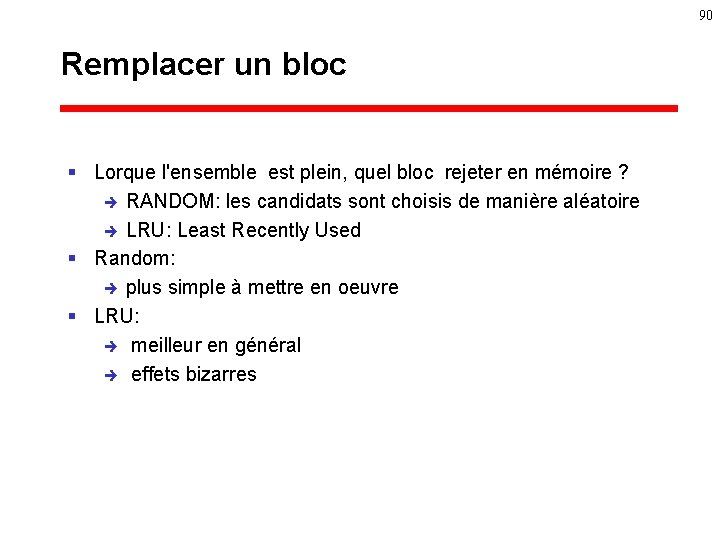

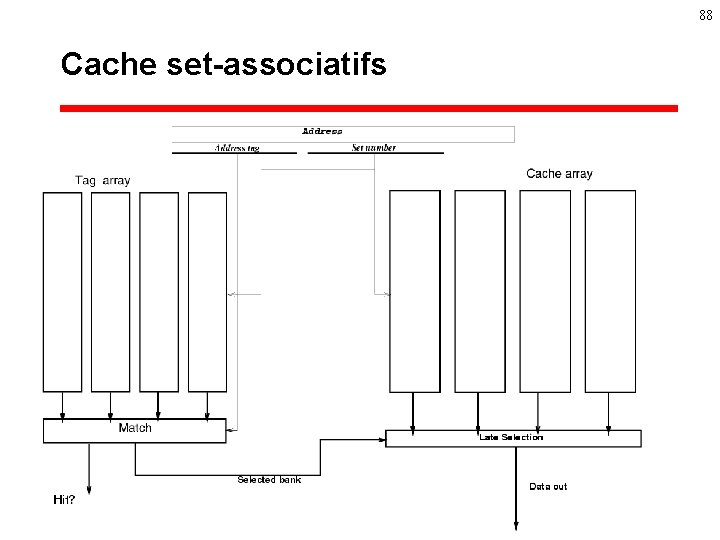

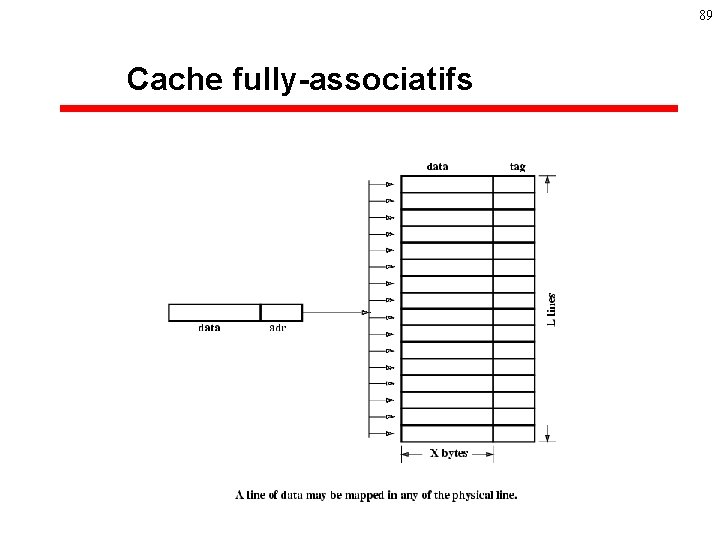

86 Placement des données dans les caches § Chaque bloc ne peut être chargé qu'à une seule place dans le cache: cache è DIRECT MAPPED ou à correspondance directe. § Chaque bloc peut être chargé à n'importe quelle place dans le cache: è FULLY ASSOCIATIVE ou totalement associatif. § Chaque bloc ne peut être chargé qu'à un nombre limité de places (ensemble ou SET): è SET ASSOCIATIVE ou associatif par ensembles.

87 Cache direct-mapped

88 Cache set-associatifs

89 Cache fully-associatifs

90 Remplacer un bloc § Lorque l'ensemble est plein, quel bloc rejeter en mémoire ? è RANDOM: les candidats sont choisis de manière aléatoire è LRU: Least Recently Used § Random: è plus simple à mettre en oeuvre § LRU: è meilleur en général è effets bizarres

91 Ecrire § Toute écriture doit être répercutée dans la mémoire: è Tout de suite: WRITE THROUGH è ou plus tard: WRITE BACK ( quand le bloc est évincé du cache) § WRITE BACK: è moins de trafic sur la mémoire è problème de cohérence entre la mémoire et le cache § WRITE THROUGH: è trafic important vers la mémoire

92 Quelle taille de bloc ? § Blocs longs: è bénéficie de la localité spatiale è réduit le nombre de blocs et perd de la place § Blocs courts: è nombreux défauts sur des blocs contigus § Expérimentalement : è 16 - 64 bytes pour les caches 8 -32 Kbytes

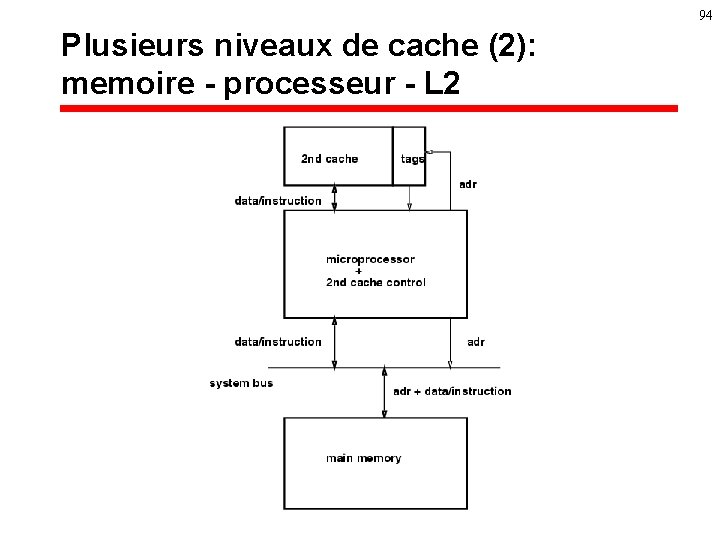

93 Plusieurs niveaux de caches § Une hiérarchie de caches: è des capacités de plus en plus grandes è des temps d'accès de plus en plus longs. § L 2 devenu la règle générale: è sur le composant ou sur le même module que le processeur è temps d ’accès: 7 -15 cycles

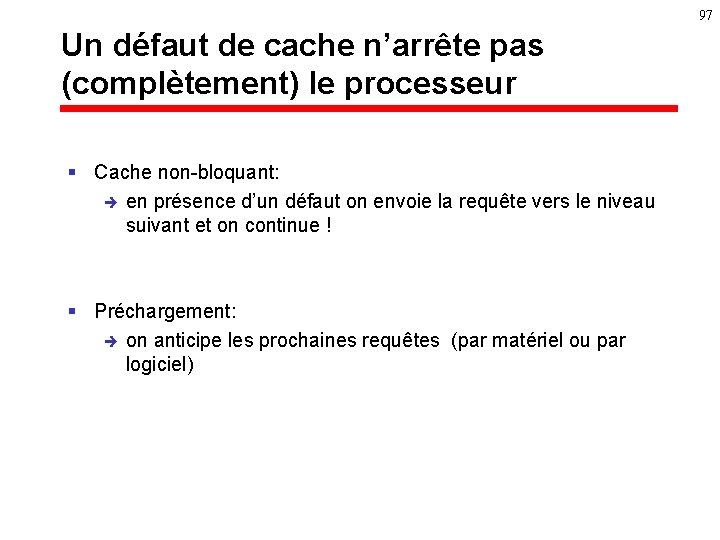

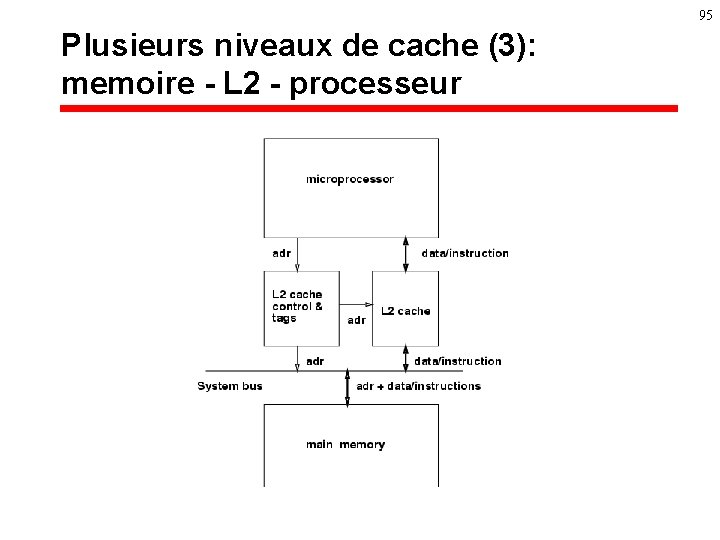

94 Plusieurs niveaux de cache (2): memoire - processeur - L 2

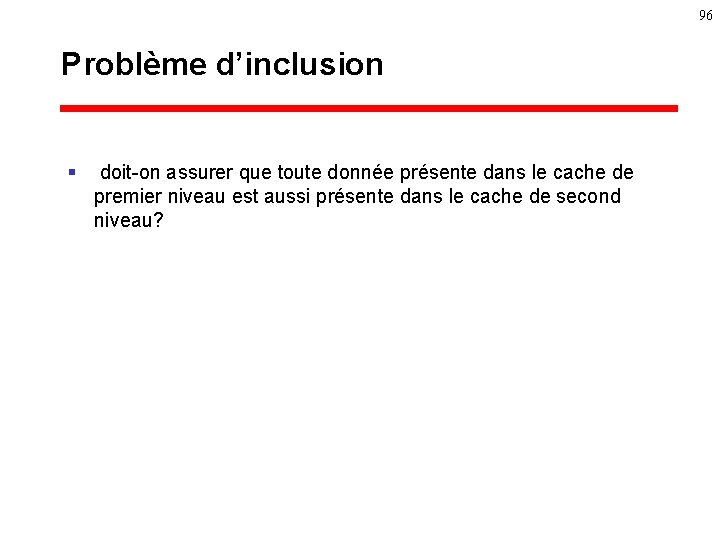

95 Plusieurs niveaux de cache (3): memoire - L 2 - processeur

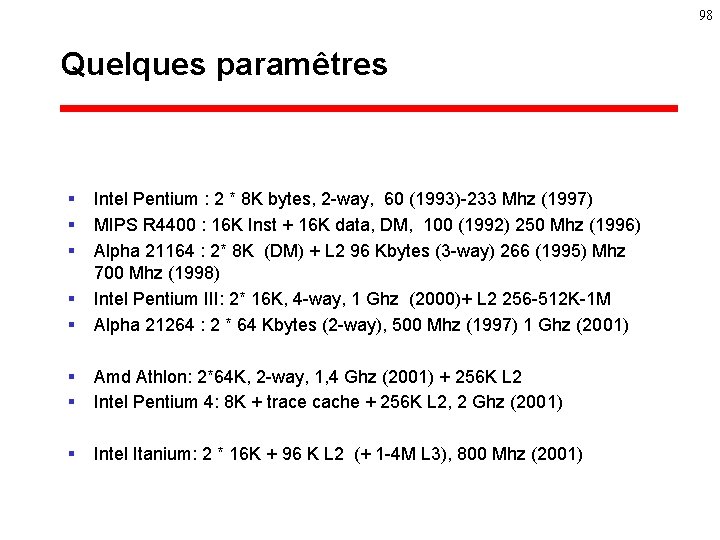

96 Problème d’inclusion § doit-on assurer que toute donnée présente dans le cache de premier niveau est aussi présente dans le cache de second niveau?

97 Un défaut de cache n’arrête pas (complètement) le processeur § Cache non-bloquant: è en présence d’un défaut on envoie la requête vers le niveau suivant et on continue ! § Préchargement: è on anticipe les prochaines requêtes (par matériel ou par logiciel)

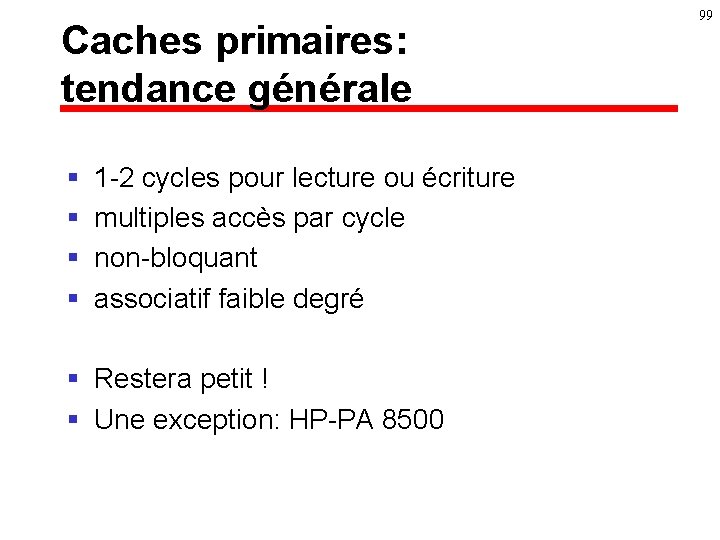

98 Quelques paramêtres § § § Intel Pentium : 2 * 8 K bytes, 2 -way, 60 (1993)-233 Mhz (1997) MIPS R 4400 : 16 K Inst + 16 K data, DM, 100 (1992) 250 Mhz (1996) Alpha 21164 : 2* 8 K (DM) + L 2 96 Kbytes (3 -way) 266 (1995) Mhz 700 Mhz (1998) Intel Pentium III: 2* 16 K, 4 -way, 1 Ghz (2000)+ L 2 256 -512 K-1 M Alpha 21264 : 2 * 64 Kbytes (2 -way), 500 Mhz (1997) 1 Ghz (2001) § § Amd Athlon: 2*64 K, 2 -way, 1, 4 Ghz (2001) + 256 K L 2 Intel Pentium 4: 8 K + trace cache + 256 K L 2, 2 Ghz (2001) § Intel Itanium: 2 * 16 K + 96 K L 2 (+ 1 -4 M L 3), 800 Mhz (2001)

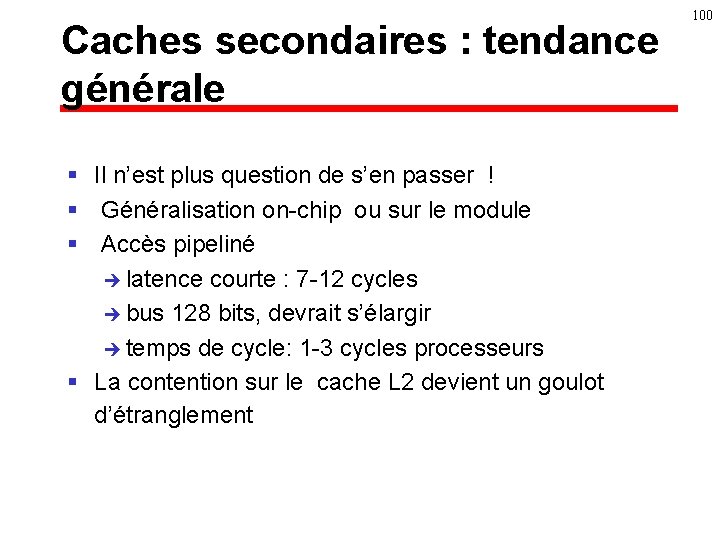

Caches primaires: tendance générale § § 1 -2 cycles pour lecture ou écriture multiples accès par cycle non-bloquant associatif faible degré § Restera petit ! § Une exception: HP-PA 8500 99

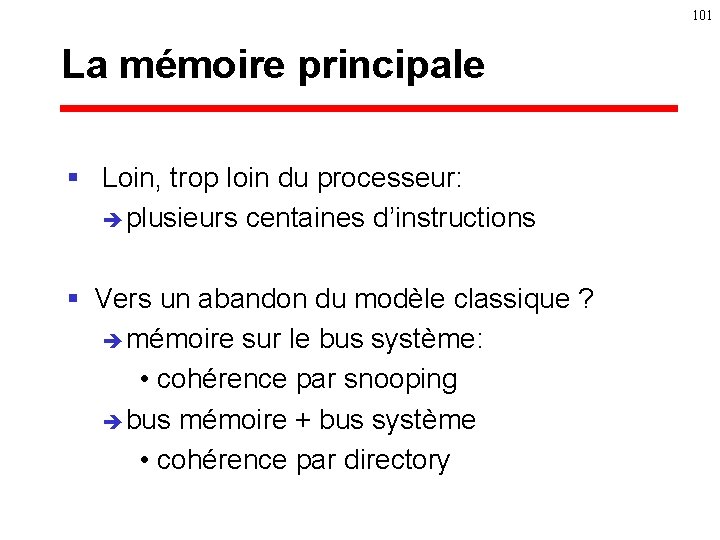

Caches secondaires : tendance générale § Il n’est plus question de s’en passer ! § Généralisation on-chip ou sur le module § Accès pipeliné è latence courte : 7 -12 cycles è bus 128 bits, devrait s’élargir è temps de cycle: 1 -3 cycles processeurs § La contention sur le cache L 2 devient un goulot d’étranglement 100

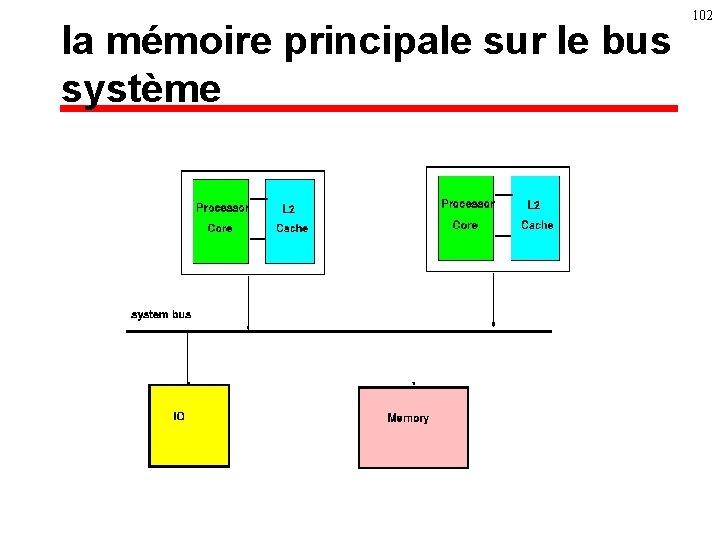

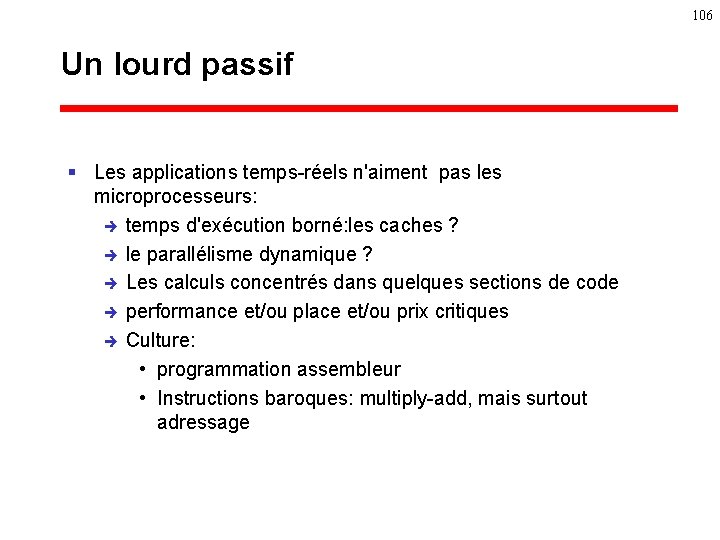

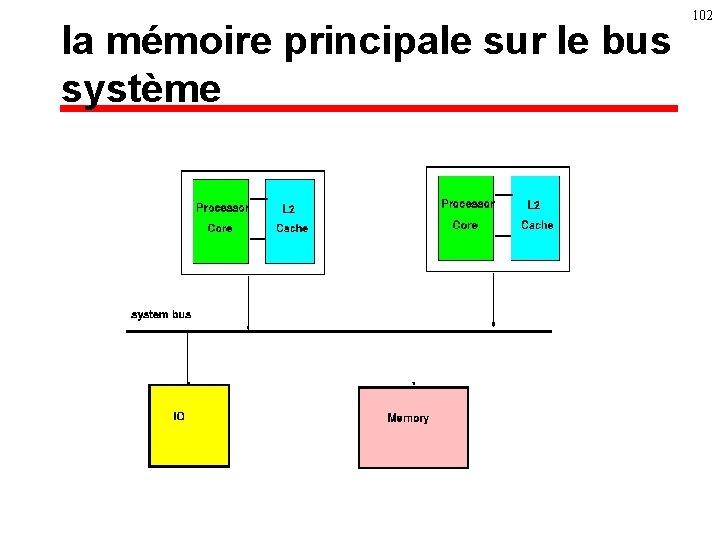

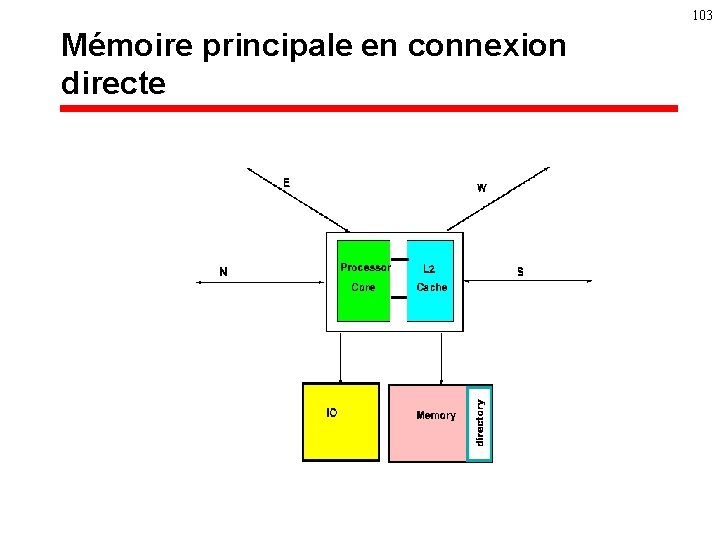

101 La mémoire principale § Loin, trop loin du processeur: è plusieurs centaines d’instructions § Vers un abandon du modèle classique ? è mémoire sur le bus système: • cohérence par snooping è bus mémoire + bus système • cohérence par directory

la mémoire principale sur le bus système 102

103 Mémoire principale en connexion directe

104 Les tendances (et les problèmes) § plus d'instructions par cycle: è au delà d'un bloc de base par cycle ? § Exécution dans le désordre: è de plus en plus de spéculation, adresses! valeurs ! § Pipeline de séquencement très long: è pénalité de mauvaise prédiction de branchement ? § Caches premier niveau multiport, non-bloquants, accédés en 12 cycles: è compromis temps d ’accès, taille, associativité § Cache second niveau pipeliné non-bloquant

Microprocesseurs généraux, processeurs enfouis, DSP: vers une convergence ? 105

106 Un lourd passif § Les applications temps-réels n'aiment pas les microprocesseurs: è temps d'exécution borné: les caches ? è le parallélisme dynamique ? è Les calculs concentrés dans quelques sections de code è performance et/ou place et/ou prix critiques è Culture: • programmation assembleur • Instructions baroques: multiply-add, mais surtout adressage

107 Un monde qui change (1) § Impossibilité d'atteindre les performances sans cache: è Gestion de tous les mouvements de données à la main: • à peu près impossible ! • et les mouvements d'instructions ! § caches dans les nouveaux DSPs: Tri. Media, TMS 320 C 62 xx, . . è De plus en plus de contrôle dans les applications è Parallélisme d'instruction nécessaire pour la performance (mais VLIW possible !)

108 Un monde qui change (2) § Le recyclage designs de processeurs: è les coeurs des microcontrolleurs d'aujourd'hui sont dérivés des microprocesseurs d'hier: • Des microcontrolleurs sont dérivés de toutes les grandes familles de processeurs. è Disponibilité de logiciels

109 Un monde qui change (3) è è Une culture qui évolue dans le monde des DSPs: • parallélisme d'instructions, pipeline profond: – écriture de plus en plus difficile en assembleur. Compilateurs de plus en plus matures: pipeline logiciel time-to-market des systèmes enfouis: SURTOUT le logiciel programmation en langages de haut niveau (euh, C)

110 Un monde qui change (4) § Les jeux d'instruction multimédias: è Calcul vectoriel sur des données 8 ou 16 bits § présents sur tous les processeurs généraux

Et demain ? 111

Que faire avec un milliard de transistors ou plus? § IRAM: le processeur et sa mémoire § monoprocesseur + exécution spéculative § Le parallélisme de processus: è multiprocesseur à mémoire partagée è processeur SMT 112

113 IRAM § le processeur et sa mémoire sur un même composant è bande passante mémoire énorme à un coût limité § Une fausse bonne idée è Consommation mémoire des applications augmente è Extensibilité ? § La solution pour certaines applications enfouies

Un monoprocesseur + exécution spéculative § superscalaire 16 ou 32 voies § hyperspéculation: è branchements, dépendances, données. . § Les défis: è la qualité de la prédiction è les temps de communication sur le composant è la contention sur les structures: • caches , registres, . . . 114

Le //isme de processus: à la croisée des chemins § Le parallélisme « gros grain » arrive sur le composant è Un multiprocesseur on-chip ? • IBM Power 4 ( fin 2001) è Simultaneous Multithreading ? • Compaq Alpha 21464 ( 2003) 115

116 Un multiprocesseur on-chip § Peut-être la solution, mais. . è Où sont les applications? è La bande passante sur la mémoire? è Et la performance sur un processus ? è Manquons-nous d'imagination à ce point?

multiprocesseur on-chip: IBM Power 4 (2001) § Marché visé: les serveurs § 2 processeurs superscalaire 4 voies sur un composant: è cache secondaire partagé § 4 composants sur un même MCM (multichip module) è bande passante énorme sur le MCM 117

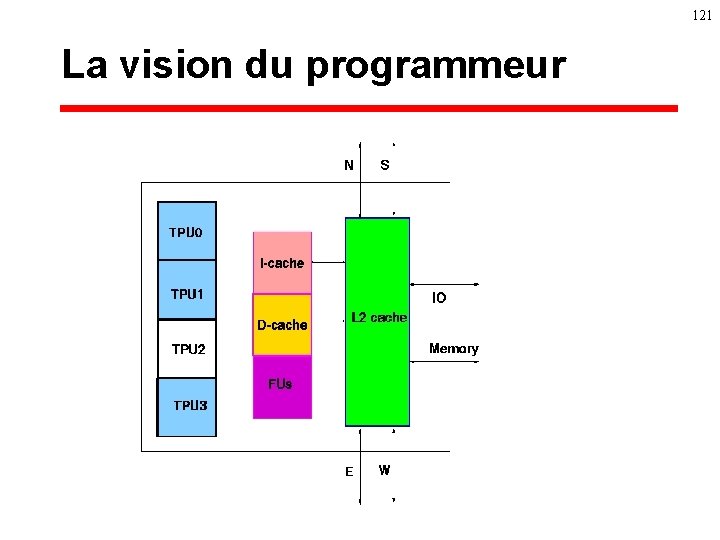

118 La vision du programmeur

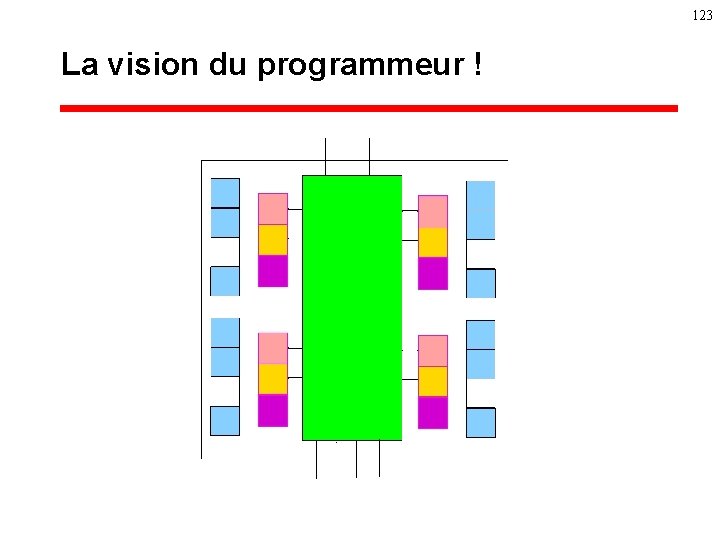

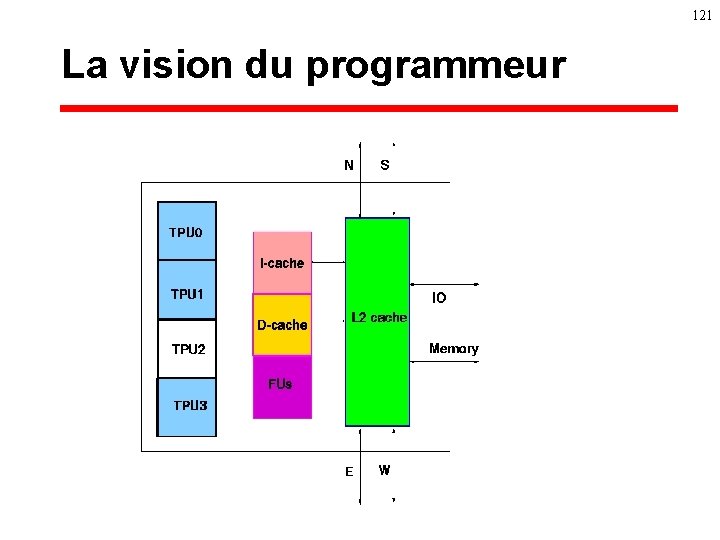

Simultaneous Multithreading (SMT) § Les UFs d’un processeur sont sous-utilisées § SMT: è Partager les UFs d’un processeur superscalaire entre plusieurs processus § Avantages: è 1 processus a toutes les ressources è partage dynamique des structures (caches, prédicteurs, UFs) 119

120 SMT: Alpha 21464 (2003) § Un processeur superscalaire 8 voies è Performance ultime sur un processus § Si multiprocessus, 4 processus se partagent les unités fonctionnelles: è Surcoût pour ce partage 5 -10 %

121 La vision du programmeur

122 Le processeur de l ’an 2010 ? § Jeu d'instruction x 86+ ? è extension pour mode 64 bits § (Multi ? ) Superscalaire 10 voies SMT § Exécution dans le désordre très aggressive

123 La vision du programmeur !

124 Les grandes questions § Saura-t-on maitriser la complexité du design? § Qui saura programmer ces monstres ?