MICROPROCESSEURS ET SOCKETS MICROPROCESSEUR SOCKET SOMMAIRE LES MICROPROCESSEURS

- Slides: 82

MICROPROCESSEURS ET SOCKETS

MICROPROCESSEUR SOCKET

SOMMAIRE LES MICROPROCESSEURS LES SOCKETS CONSTRUCTION D’UN MICROPROCESSEUR CHEZ INTEL ÉVOLUTION DES PERFORMANCES CHEZ INTEL LES MICROPROCESSEURS SERVEURS LES PRIX DES MICROPROCESSEURS ACTUELLES

LES MICROPROCESSEURS Définition Principe de fonctionnement Loi de Moore Éléments principaux Caractéristiques essentielles Amélioration des performances Rappel sur le déroulement de l’exécution d’une instruction

DÉFINITION Le processeur (CPU, pour Central Processing Unit) est le cerveau de l'ordinateur, c'est lui qui effectue les calculs et exécute les instructions qui ont été programmées. Il manipule des informations numériques situés dans la mémoire vive (ex : RAM) ou dans la mémoire morte (ex : BIOS). Ces informations sont codées sous forme de mots binaires que le microprocesseur peut lire, décoder et exécuter.

PRINCIPE Pour réaliser ces traitements, les microprocesseurs utilisent de ‘petits interrupteurs’ utilisant l'effet transistor. Cette effet fut découvert en 1947 par John Barden et Walter Brittan. Il existe plusieurs millions de ces transistors sur un seul microprocesseur.

PRINCIPE Voici un aperçu de l’intérieur d’un microprocesseur

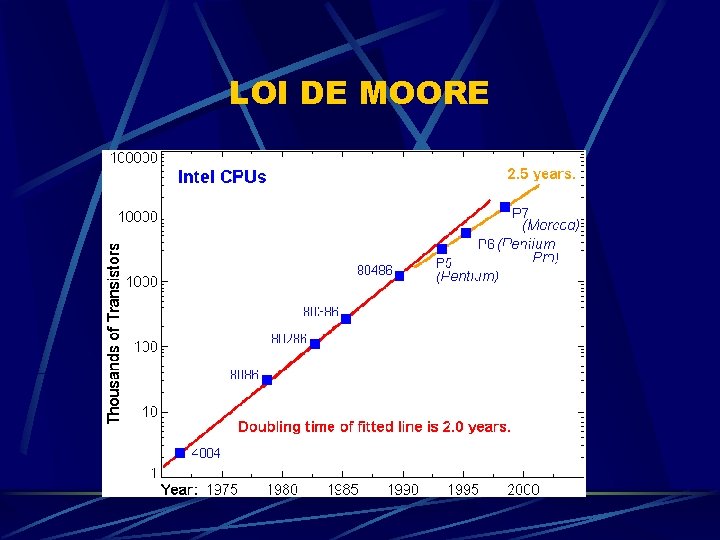

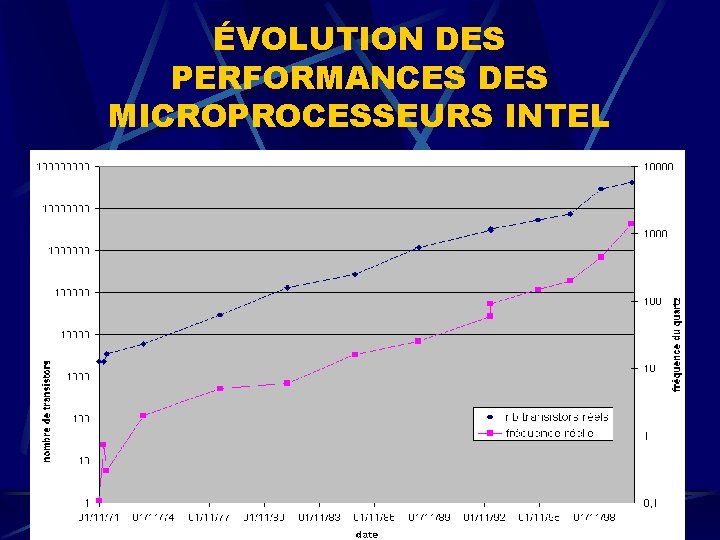

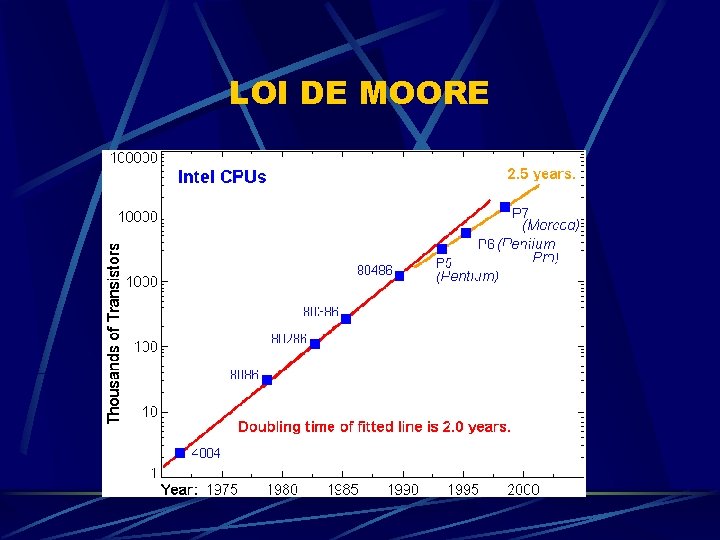

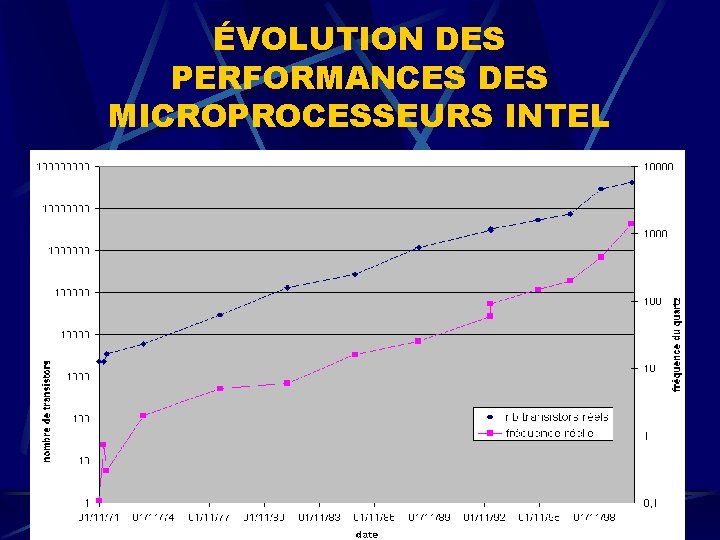

LOI DE MOORE • En 1965, Gordon Moore (cofondateur d’Intel), en préparant un exposé fit une curieuse constatation sur des puces mémoires. • Il a constater que tous les 18 mois, le nombre de transistor dans les puces doublait. • En extrapolant la tendance, on constaterait une évolution exponentielle de la capacité des mémoires comme de la performance de calcul des puces microprocesseur. • En effet, cette tendance est encore vraie aujourd'hui, et elle est connue comme la Loi de Moore.

LOI DE MOORE

ÉLÉMENTS PRINCIPAUX Voici de quoi est constituer le cœur d’un microprocesseur : l De registres l D’une unité arithmétique et logique l D’une unité de commande et de contrôle l D’une unité de décodage des instructions l De bus internes

LES REGISTRES Un registre est une zone de mémoire vive très rapide situé dans le microprocesseur. Ils sont utilisés pour stocker les informations nécessaires aux traitements. En fait, il permettent à l’unité de traiter des données sans avoir accès à la mémoire.

LES REGISTRES Il existe plusieurs type de registre dans le microprocesseur. l Les registres de données l Les registres d’état l Les registres pointeurs Voici une représentation schématique des registres :

LES REGISTRES DE DONNÉES Ils servent de mémoire temporaire pour les calculs. Les principaux permettent de stocker les résultats de façon temporaire. La majorité des calculs effectués par le microprocesseur utilisent ces registres. Les échanges entre les registres et l’UAL se font grâce au bus de données interne au microprocesseur. Dans les microprocesseurs x 86 d’Intel, les registres de données sont nommés AL, BL, CL, DL, AX, BX, CX, DX

LES REGISTRES D’ÉTAT Il regroupe les Flags ou indicateurs d’état. Ces indicateurs sont mis à 0 ou 1 en fonction du résultat de l’opération qui vient d’être exécutée. Voici deux indicateurs dans le registre d’état : l l Le bit d’état Z (zéro) est positionner à 1 quand le résultat d’un opération est nul. Le bit de signe S vaut 1 quand le résultat d’un opération est négative, sinon il vaut 0.

LES REGISTRES POINTEURS Ce sont des registres particuliers utilisé par le microprocesseur pour stocker des adresses de valeurs en mémoire centrale. Par exemple dans le microprocesseur 8088 de Intel les registres sont nommé DI, SI, BX et BP. Le compteur ordinal est le registre de type pointeur le plus important de l’ordinateur car il contient l’adresse mémoire de la prochaine instruction qui doit être exécutée.

L’UAL signifie Unité Arithmétique et Logique Elle effectue des opérations arithmétiques : l ADD (+), SUB (-), MUL (*), DIV (: ), INC (+1), DEC (-1) Et des opérations logiques : l l AND, OR, XOR, NOT, CMP LSL, LSR, ASR (décalages)

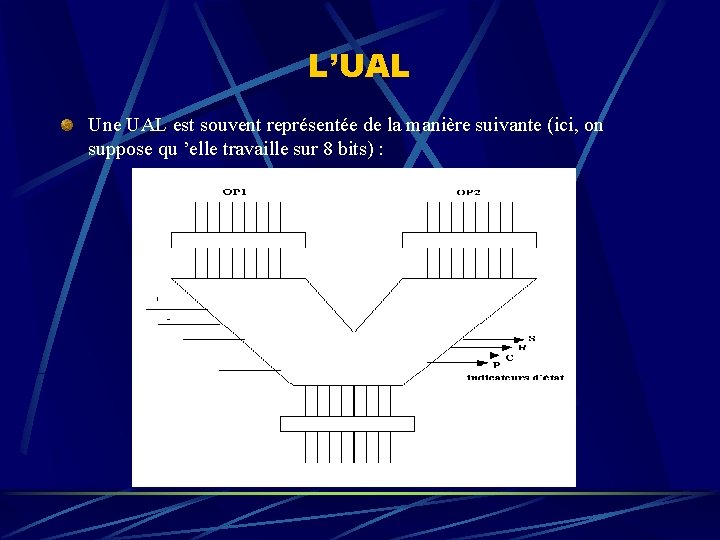

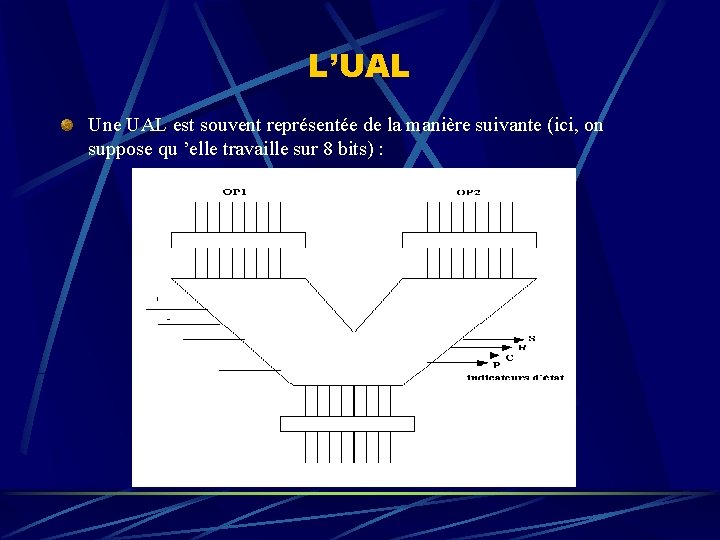

L’UAL Une UAL est souvent représentée de la manière suivante (ici, on suppose qu ’elle travaille sur 8 bits) :

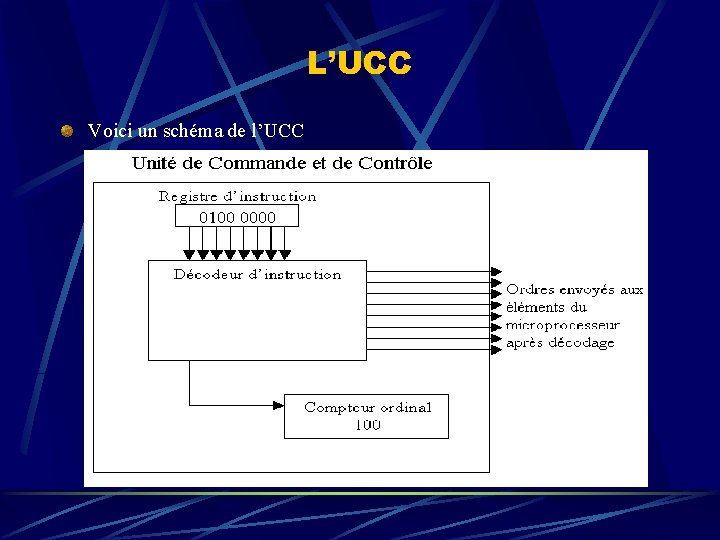

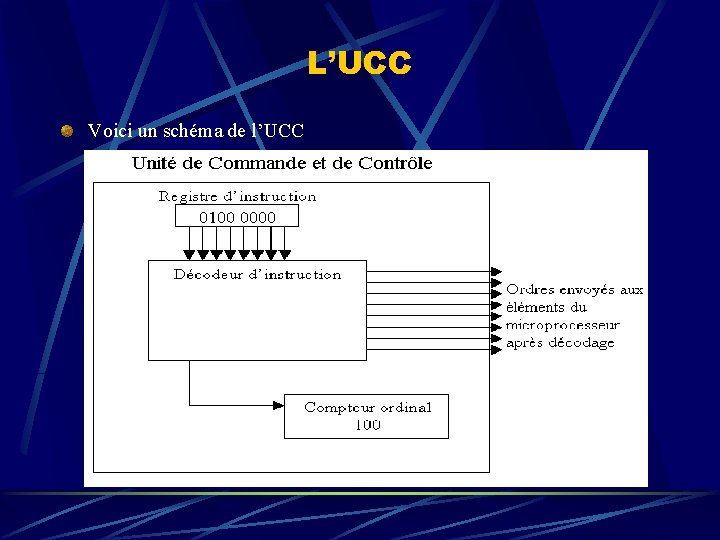

L’UCC signifie Unité de Commande et de Contrôle Elle est composée : l l D’un compteur ordinal qui mémorise l’adresse de la prochaine instruction à exécuter. D’un registre d’instruction qui mémorise l’instruction en cours. D’un décodeur qui assure le décodage de l’instruction en cours et l’envoie sous forme de micro-instruction au séquenceur. D’un séquenceur qui, à la réception des micros-instructions, envoie des commandes aux différents organes concernés. Pour cela, elle utilise l’horloge.

L’UCC Voici un schéma de l’UCC

CARACTÉRISTIQUES ESSENTIELLES Un microprocesseur se caractérise par : l La taille des données traitées l La fréquence d’horloge l Les MIPS l Les FLOPS l La fréquence du FSB l La taille des transistors l La puissance dissipée par les transistors

LA TAILLE DES DONNÉES TRAITÉES • En générale, elle est précisée en bits. • 8, 16, 32, 64 bits selon le type du microprocesseur. • Plus la taille des données que le microprocesseur peut traiter est grande, plus le microprocesseur va vite pour faire les calculs. • Par exemple, pour additionner deux valeurs représentées sur 32 bits, il vaut mieux traiter deux blocs de 32 bits que 4 fois 2 octets avec des retenus.

LA FRÉQUENCE D’HORLOGE 1. Elle se mesure maintenant en Gigahertz. 2. C’est en fait la fréquence de fonctionnement interne du microprocesseur. 3. Par exemple, une fréquence de 2, 5 GHz donne une période de 0, 4 ns donc un top d’horloge tous les 4 ns, soit. 4. Certains microprocesseur ont des fréquences plus faible que d’autre mais ils exécutent les programmes plus rapidement. 5. Ceci pour montrer que la fréquence d’horloge ne fait pas toute la rapidité d’exécution d’un microprocesseur.

LES MIPS signifie Million d’Instruction Par Seconde. C’est un des premiers critères de la puissance d’un microprocesseur. Les instructions sont des opérations simples (calculs arithmétiques sur des entiers, tests, …). Les valeurs mesurées en MIPS sont inférieures à la fréquence d’horloge car certaines instructions nécessite encore plusieurs cycle d’horloge pour s ’exécuter.

LES FLPOS • FLOPS signifie Floating Point Operations Per Second (opération en virgule flottante). • C’est une mesure de performance appliquée aux ordinateurs scientifiques dédiés au calcul numérique (nombres réels en virgules flottante). • Les performances se mesures en Mflops, Gflops.

LA FRÉQUENCE DU FSB • Le FSB (Front Side Bus) est le bus de sortie du microprocesseur. • Il relie le microprocesseur au chipset et aux autres composants de l’ordinateur. • La fréquence du FSB est mesurée en MHZ. • Plus le fréquence est grande et plus le microprocesseur travaille vite avec les autres composants de l’ordinateur.

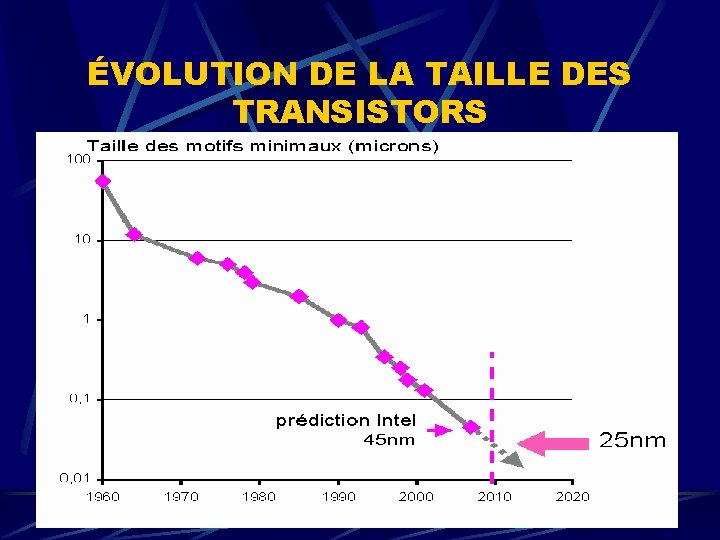

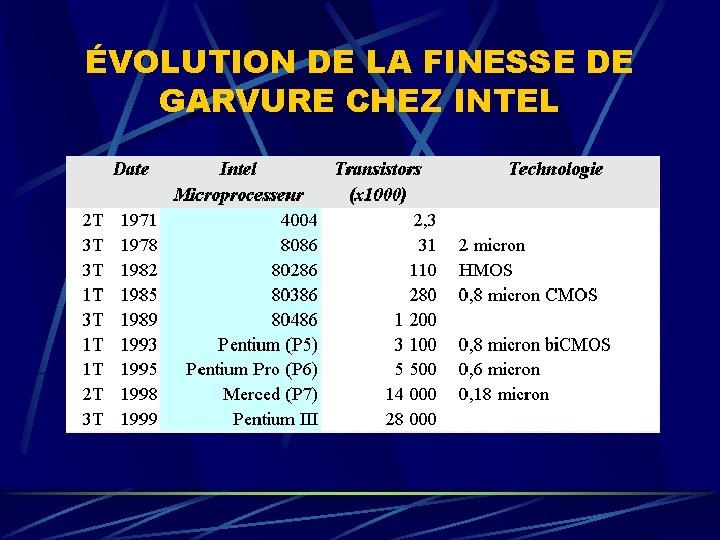

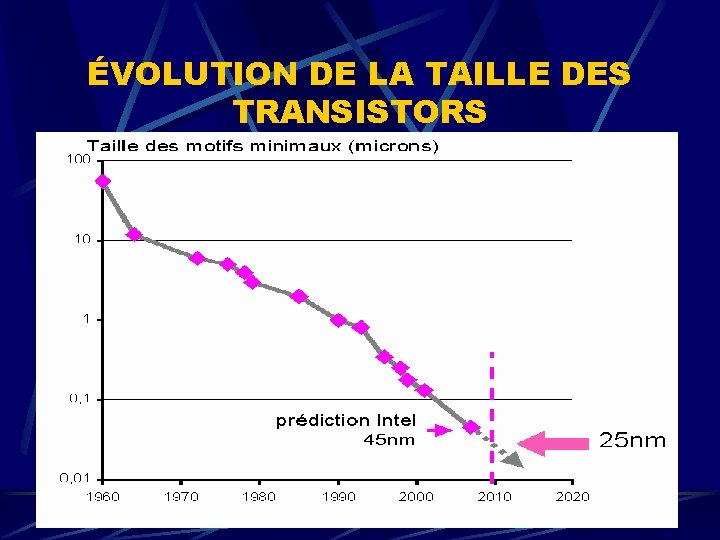

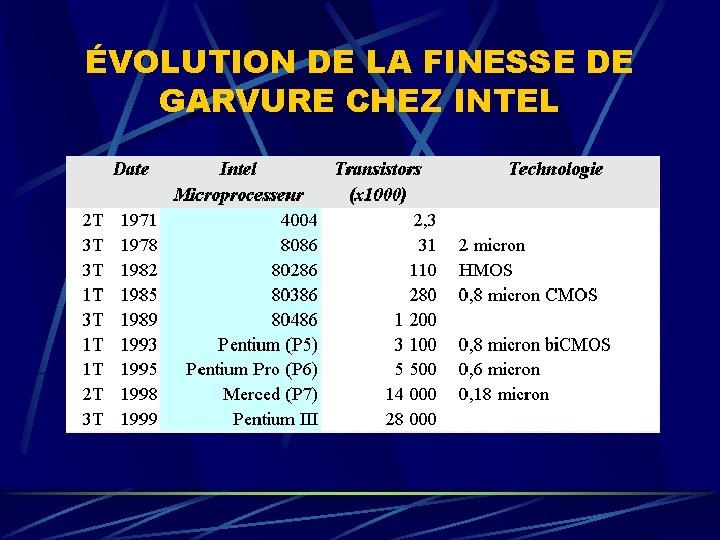

TAILLE DES TRANSISTORS 1. Elle est calculé selon l’épaisseur des traits qui servent à dessiner un transistor. 2. La taille des traits se mesure en micron. 3. De nos jour, certains microprocesseurs comme le Pentium 4 sont dessinés avec des traits de 0, 09 micron. 4. Un dessin en 0. 065 micron est annoncé pour 2005, 0. 045 pour 2007, 0. 032 pour 2009, 0. 022 pour 2011. 5. Il faut remarquer que plus un transistor est petit, plus il va vite et moins il chauffe.

LA PUISSANCE DISSIPÉE DES TANSISTORS • Cette aspect est pénalisant pour le fonctionnement du microprocesseur. • Par exemple, un cœur de microprocesseur mesure un peu près 150 mm² (1, 2 x 1, 2 cm) et il y a des millions de transistor qui chauffent à l’intérieur. • C’est pour cela que les microprocesseurs actuel sont fournis avec des ventilateur.

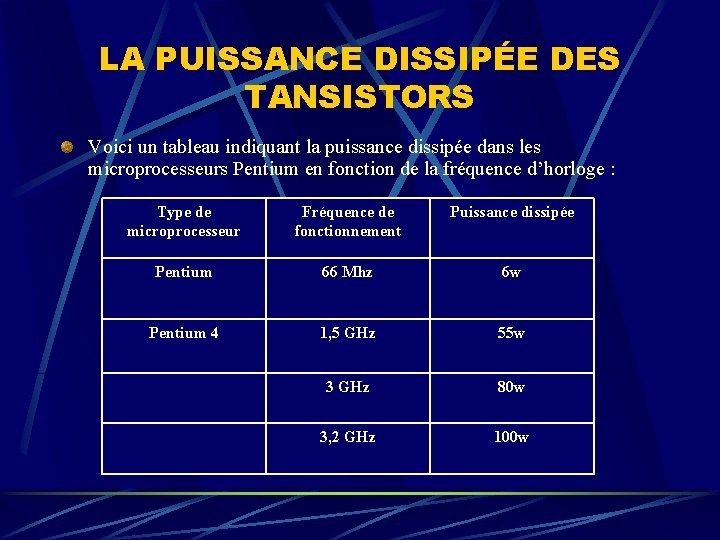

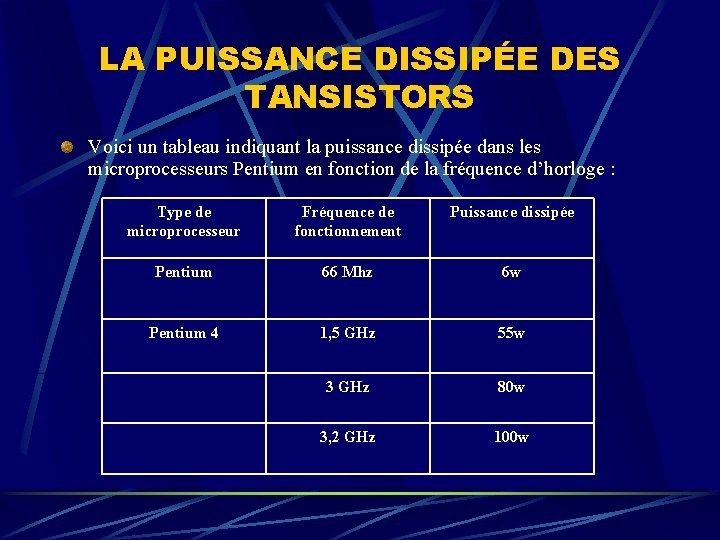

LA PUISSANCE DISSIPÉE DES TANSISTORS Voici un tableau indiquant la puissance dissipée dans les microprocesseurs Pentium en fonction de la fréquence d’horloge : Type de microprocesseur Fréquence de fonctionnement Puissance dissipée Pentium 66 Mhz 6 w Pentium 4 1, 5 GHz 55 w 3 GHz 80 w 3, 2 GHz 100 w

AMÉLIORATION DES PERFORMANCES Le but est d’améliorer la puissance de calcul du microprocesseur et de réaliser une instruction par top d’horloge. Pour améliorer cela, il y a plusieurs possibilités : l Travailler sur la fabrication des composants l Travailler sur l’architecture

AMÉLIORATION DE LA FABRICATION Améliorer la fabrication d’un microprocesseur c’est : l Améliorer les composants l Augmenter la fréquence de fonctionnement l Améliorer la vitesse des composants internes l Augmenter la taille des données traitées l Améliorer la vitesse des échanges avec la mémoire

DIMINUER LA TAILLE DES TRANSISTORS Le but est de diminuer le volume des transistors. Un transistor plus petit sera traversé plus vite par le courant électrique et il chauffera moins. Le problème c’est qu’il y a de plus en plus de transistors dans une surface de plus en plus petite. L’évolution de la taille des transistors n’est possible qu’en faisant évoluer leur technique de fabrication avec de nouvelles machines qui content de plus en plus chères.

ÉVOLUTION DE LA TAILLE DES TRANSISTORS

AUGMENTER LA FRÉQUENCE DE FONCTIONNEMENT Il s’agit de la fréquence de fonctionnement interne du microprocesseur. Après fabrication, les microprocesseurs sont testé et certifiés pour des fréquences de fonctionnement plus ou moins élevés. En agissant sur certains paramètres de fabrication et en limitant les défauts, les fabricants cherchent à augmenter cette fréquence de fonctionnement. La diminution de la taille des transistors compte beaucoup dans l’augmentation de la fréquence.

AMÉLIORER LA VITESSE DE FONCTIONNEMENT DES UNITÉS DE CALCUL Les fabricants essayent de diminuer le nombre de tops d’horloge pour réaliser une opération. En mettant plusieurs UAL dans un microprocesseur, on augmente le nombre de calcul avec le même nombre de top d’horloge. Ceci est dans le cadre d’un fonctionnement en parallèle.

AUGMENTER LA TAILLE DES DONNÉES TRAITÉES La plupart des microprocesseur actuelle travaillent sur 32 bits, les nouveaux commencent à sortir sur 64 bits. L’intérêt : l l l Permet d’obtenir 8 octets d’un seul coup donc on double les données traitées par rapport à un 32 bits. Sur 64 bits, les instructions vont pouvoir être lues sur un seul mot, ce qui évite un retour en mémoire pour aller cher le reste de l’instruction. Il sera possible d’avoir deux instructions dans un même mots de 64 bits donc une seule lecture permet d’obtenir deux instructions et donc de gagner du temps d’acquisition.

AMÉLIORER LES ÉCHANGES AVEC LA MÉMOIRE Le microprocesseur effectue beaucoup d’échanges avec la mémoire. Or la mémoire est plus lente que le microprocesseur donc il faut améliorer la vitesse de ces échanges. La vitesse des échanges avec la mémoire dépend dons de la mémoire et du débit du FSB. Actuellement, on voit la fréquence des FSB augmenter. Aussi, pour améliorer les échanges, on peut raccourcir la distance entre le microprocesseur et les composants, placer le maximum de mémoire cache sur le microprocesseur.

AMÉLIORER LA STRUCTURE INTERNE Afin d’améliorer la structure interne d’un microprocesseur, différentes procédé ont été mis en place : l Les architectures C. I. S. C. et R. I. S. C l La mémoire cache l L’architecture Pipeline l L’architecture Superscalaire l L’architecture Hyperthreadind l L’architecture Bicoeur l L’architecture Net. Burst l L’architecture EPIC l Le concept du « PC on a chip »

L’ARCHITECTURES C. I. S. C. L’architecture CISC signifie Complex Instruction Set Computer. Elle dispose d'un jeu de plus de 400 instructions. Elle a été utilisé dans les premiers microprocesseurs, et continue de l'être majoritairement. Les microprocesseurs basés sur l'architecture C. I. S. C. sont dits compatibles x 86 ou compatibles Intel, puisque les instructions C. I. S. C. sont majoritairement utilisées par toutes les familles de processeurs Intel.

L’ARCHITECTURES R. I. S. C. L’architecture RISC signifie Reduced Instruction Set Computer. Elle dispose d’un jeu 128 instructions simples. Les instructions vont donc plus vite à décoder et à exécuter. Il faut moins de transistors pour les réaliser donc on en profite pour augmenter le nombre de registre, la taille de la mémoire cache, et l’architectures comme par exemple agir sur le parallélisme. Actuellement, les processeur de type R. I. S. C. sont plus performants que les C. I. S. C.

LA MÉMOIRE CACHE Chaque processeur intègre une quantité variable de mémoire cache. Cette mémoire très rapide est indispensable pour bénéficier de bonnes performances dans les applications. Elle permet de stocker les données les plus fréquemment demandées par le processeur.

LA MÉMOIRE CACHE On distingue trois niveaux de cache : l Le cache L 1 (cache de premier niveau) : La quantité intégrée est généralement faible (16 Ko, voire 128). l Le cache L 2 (cache de second niveau) : Cette quantité varie de 128 Ko à 1 Mo, ce cache est légèrement moins rapide que le cache L 1 l Le cache L 3 (cache de troisième niveau) : Ce cache disponible seulement sur les Pentiums 4 Extrême Édition peut vous permettre de gagner 10% de performances en plus en fonction des applications. Plus le niveau de cache est élevé, plus le processeur coûte cher.

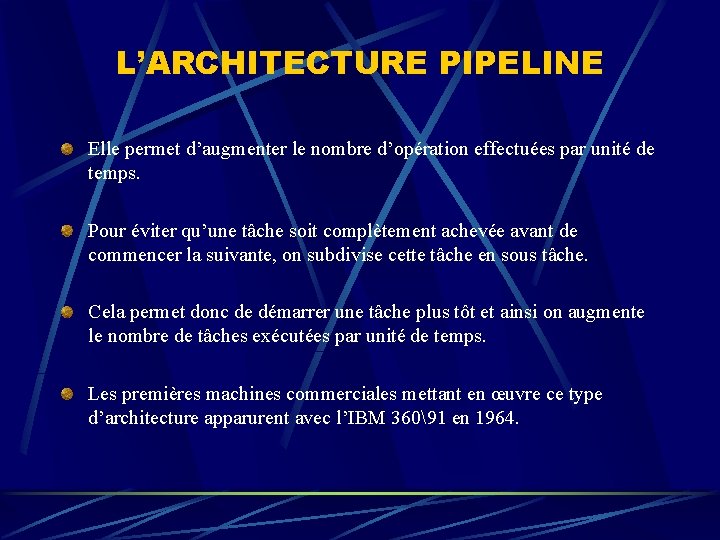

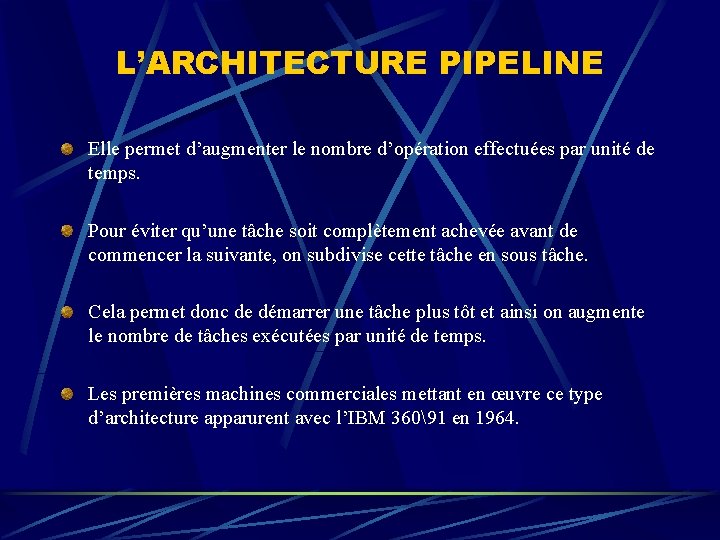

L’ARCHITECTURE PIPELINE Elle permet d’augmenter le nombre d’opération effectuées par unité de temps. Pour éviter qu’une tâche soit complètement achevée avant de commencer la suivante, on subdivise cette tâche en sous tâche. Cela permet donc de démarrer une tâche plus tôt et ainsi on augmente le nombre de tâches exécutées par unité de temps. Les premières machines commerciales mettant en œuvre ce type d’architecture apparurent avec l’IBM 36091 en 1964.

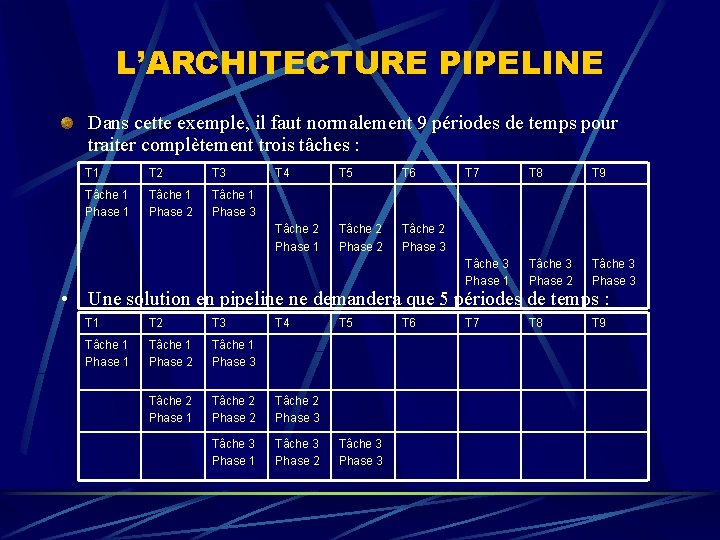

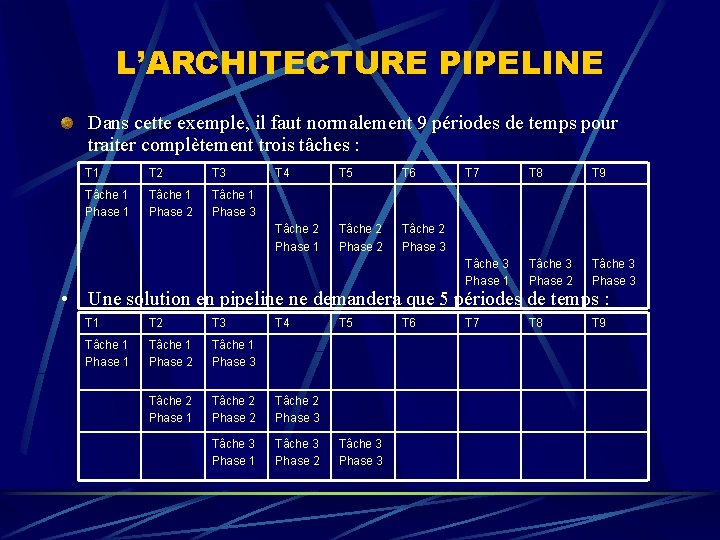

L’ARCHITECTURE PIPELINE Dans cette exemple, il faut normalement 9 périodes de temps pour traiter complètement trois tâches : T 1 T 2 T 3 Tâche 1 Phase 1 Tâche 1 Phase 2 Tâche 1 Phase 3 T 4 T 5 T 6 Tâche 2 Phase 1 Tâche 2 Phase 2 Tâche 2 Phase 3 T 7 T 8 T 9 Tâche 3 Phase 1 Tâche 3 Phase 2 Tâche 3 Phase 3 T 7 T 8 T 9 • Une solution en pipeline ne demandera que 5 périodes de temps : T 1 T 2 T 3 T 4 Tâche 1 Phase 1 Tâche 1 Phase 2 Tâche 1 Phase 3 Tâche 2 Phase 1 Tâche 2 Phase 2 Tâche 2 Phase 3 Tâche 3 Phase 1 Tâche 3 Phase 2 T 5 Tâche 3 Phase 3 T 6

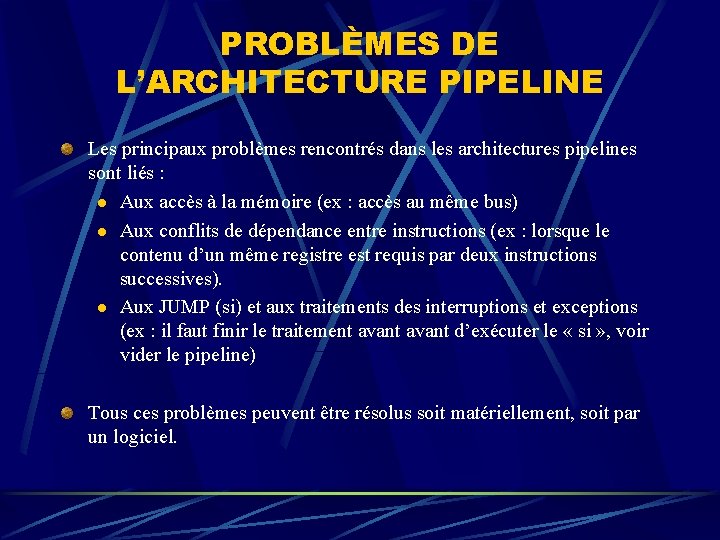

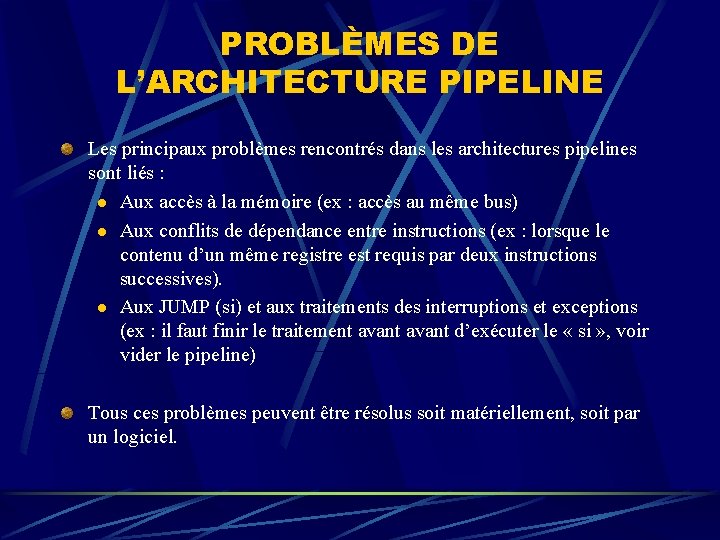

PROBLÈMES DE L’ARCHITECTURE PIPELINE Les principaux problèmes rencontrés dans les architectures pipelines sont liés : l Aux accès à la mémoire (ex : accès au même bus) l Aux conflits de dépendance entre instructions (ex : lorsque le contenu d’un même registre est requis par deux instructions successives). l Aux JUMP (si) et aux traitements des interruptions et exceptions (ex : il faut finir le traitement avant d’exécuter le « si » , voir vider le pipeline) Tous ces problèmes peuvent être résolus soit matériellement, soit par un logiciel.

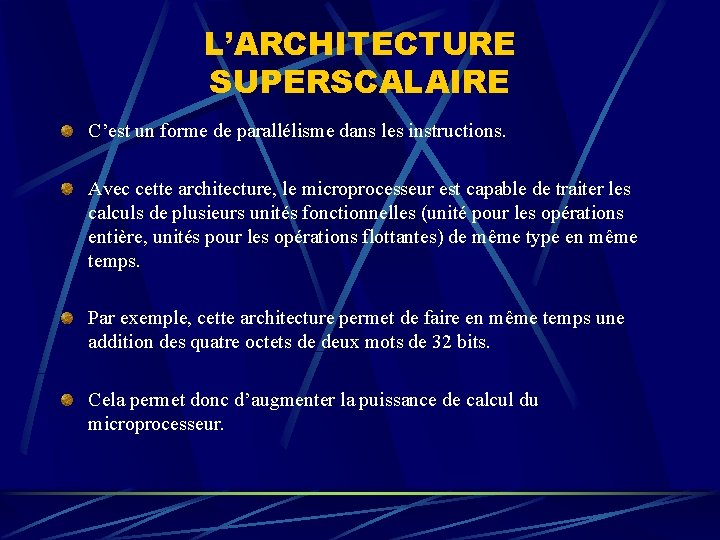

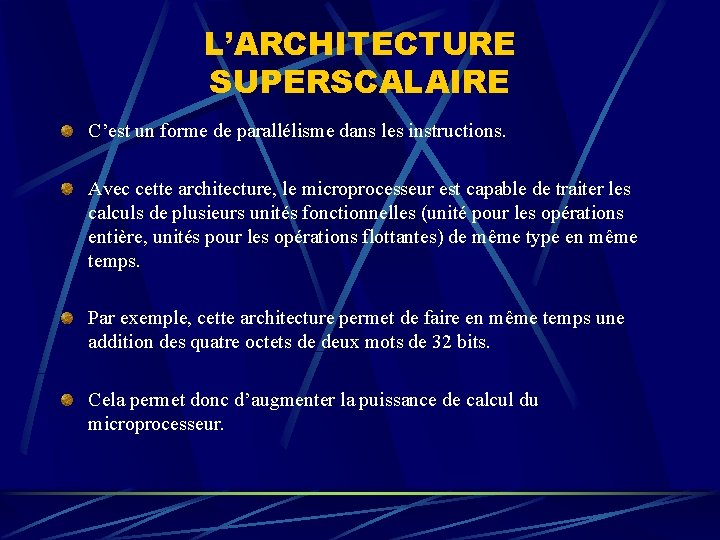

L’ARCHITECTURE SUPERSCALAIRE C’est un forme de parallélisme dans les instructions. Avec cette architecture, le microprocesseur est capable de traiter les calculs de plusieurs unités fonctionnelles (unité pour les opérations entière, unités pour les opérations flottantes) de même type en même temps. Par exemple, cette architecture permet de faire en même temps une addition des quatre octets de deux mots de 32 bits. Cela permet donc d’augmenter la puissance de calcul du microprocesseur.

L’ARCHITECTURE HYPERTHREADING Cette technologie à pour principe de base de permettre à un processeur d’être considérer comme deux processeur par le système d’exploitation. Parfois cela peut optimiser l’efficacité du microprocesseur lorsqu’il n’est pas utilisé dans son intégralité par un « thread » . Un « thread » est une partie d’un programme pouvant être exécuté indépendamment des autres aspects du programme.

L’ARCHITECTURE BICOEUR Un processeur bicœur comporte deux cœurs d'exécution à part entière. Allié à la technologie Hyper-Threading d'Intel, ce doublement permettra concrètement aux processeurs Intel pour serveurs de gérer de front deux, trois, ou quatre « threads » . Ceci optimise donc la rapidité d’exécution des instructions.

L’ARCHITECTURE NETBURST Elle a été mise au point pour manipuler plus aisément des tâches relatives à Internet telles que : l l'encodage des données l la compression vidéo l l'échange de fichiers via les réseaux "peer to peer". Elle permet de traiter plus de données, avec des vitesses de transfert encore plus élevées.

L’ARCHITECTURE E. P. I. C. signifie Explicit Parallel Instruction Computing. Elle est basé sur le traitement en parallèle des données et elle apparaît sur les microprocesseurs 64 bits. Actuellement, c'est le compilateur qui optimise le code afin de tirer parti du traitement en parallèle mais désormais, les microprocesseurs essayent de prévoir ce qui va leur être demandés. Cette méthode fait perdre quelques cycles d'horloge si la prévision est mauvaise Les microprocesseurs EPIC contourneront le problème en calculant en parallèle les diverses possibilités, la bonne étant ensuite conservée. Pour cela, il faudra un flux de données important, afin de gérer tous les calculs en parallèle sans perte de vitesse.

LE CONCEPT « PC ON A CHIP » Dans les années à venir, on va de plus en plus voir apparaître des « PCon-a-chip » . Ce sont des puces qui intègrent à la fois un microprocesseur, un circuit graphique et un contrôleur mémoire sur le même morceau de silicium. Cette méthode permettrait d'éliminer certains goulets d'étranglement (bandes passantes « faibles » ) constitués par le sous-système, tout en diminuant les coûts de production. Mais il est difficile à croire que les circuits ajoutés au microprocesseur soient les plus performants, puisque la taille du circuit devrait être assez limitée.

DEROULEMENT DE L’EXÉCUTION D’UNE INSTRUCTION Il y a trois phases principales pour que le microprocesseur exécute une instruction : l La recherche et l’acquisition de l’instruction l Le décodage de l’instruction l L’exécution de l’instruction Le registre le plus important pour ce fonctionnement est le compteur ordinal (registre pointeur) Le compteur ordinal contient l’adresse du prochain octet à lire en mémoire centrale et il s’incrémente automatiquement. C’est donc lui qui dit au microprocesseur ce qui doit être lu en mémoire.

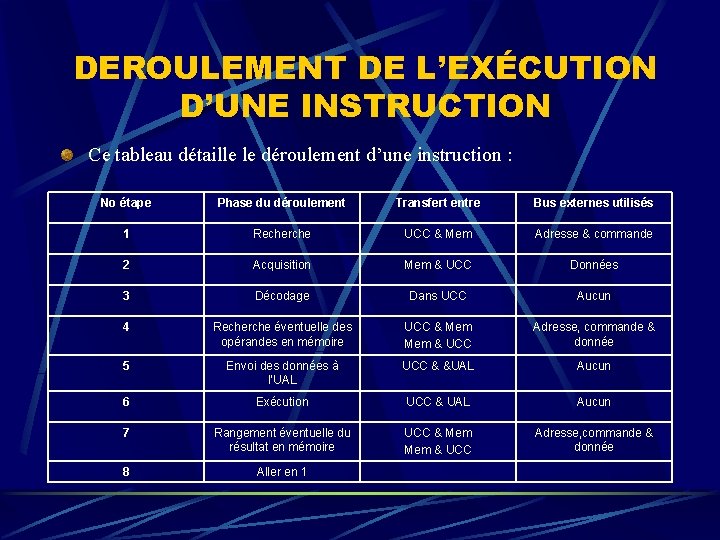

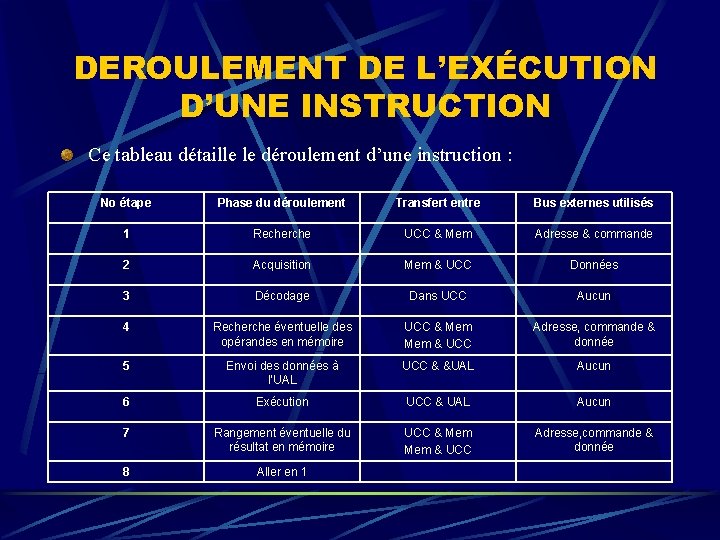

DEROULEMENT DE L’EXÉCUTION D’UNE INSTRUCTION Ce tableau détaille le déroulement d’une instruction : No étape Phase du déroulement Transfert entre Bus externes utilisés 1 Recherche UCC & Mem Adresse & commande 2 Acquisition Mem & UCC Données 3 Décodage Dans UCC Aucun 4 Recherche éventuelle des opérandes en mémoire UCC & Mem & UCC Adresse, commande & donnée 5 Envoi des données à l’UAL UCC & &UAL Aucun 6 Exécution UCC & UAL Aucun 7 Rangement éventuelle du résultat en mémoire UCC & Mem & UCC Adresse, commande & donnée 8 Aller en 1

LES SOCKETS

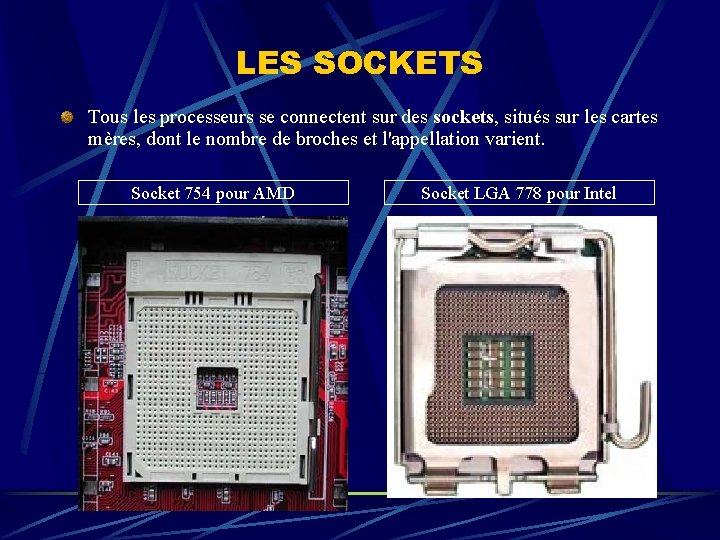

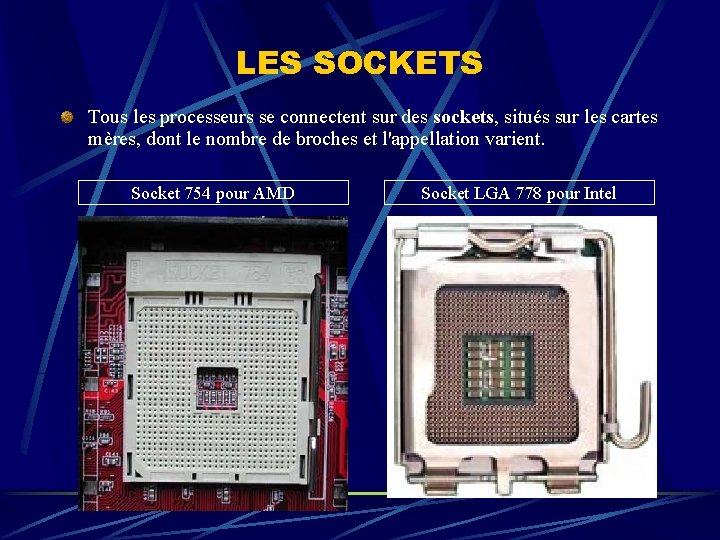

LES SOCKETS Tous les processeurs se connectent sur des sockets, situés sur les cartes mères, dont le nombre de broches et l'appellation varient. Socket 754 pour AMD Socket LGA 778 pour Intel

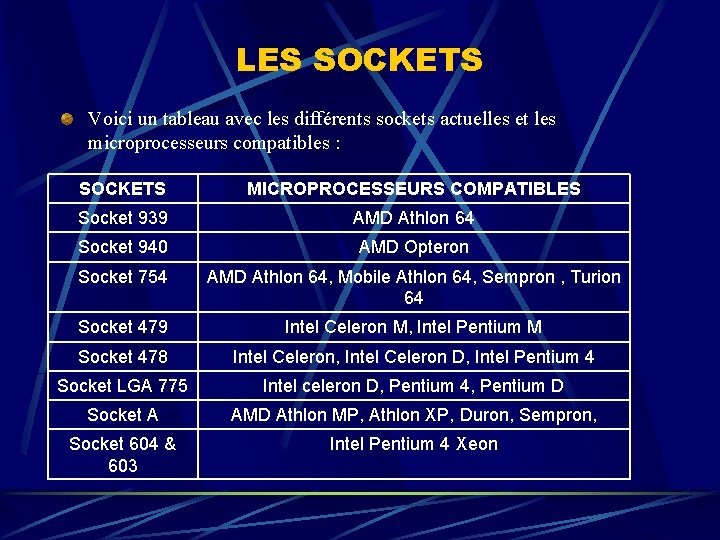

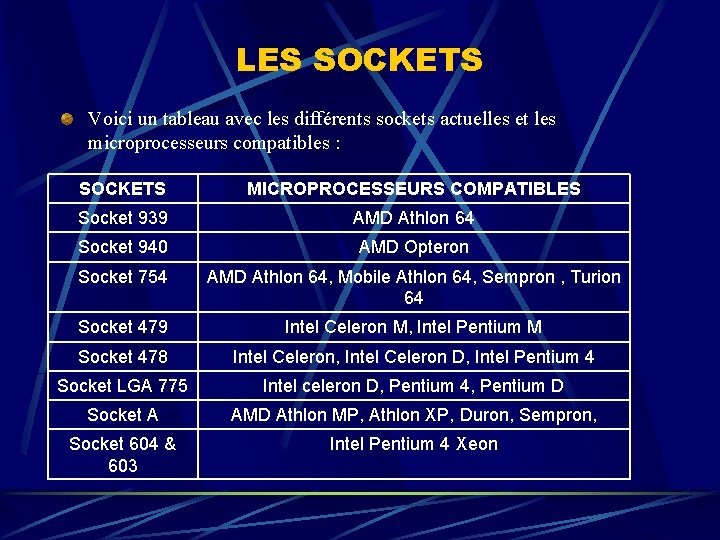

LES SOCKETS Voici un tableau avec les différents sockets actuelles et les microprocesseurs compatibles : SOCKETS MICROPROCESSEURS COMPATIBLES Socket 939 AMD Athlon 64 Socket 940 AMD Opteron Socket 754 AMD Athlon 64, Mobile Athlon 64, Sempron , Turion 64 Socket 479 Intel Celeron M, Intel Pentium M Socket 478 Intel Celeron, Intel Celeron D, Intel Pentium 4 Socket LGA 775 Intel celeron D, Pentium 4, Pentium D Socket A AMD Athlon MP, Athlon XP, Duron, Sempron, Socket 604 & 603 Intel Pentium 4 Xeon

LES SOCKETS

CONSTRUCTION D’UN MICROPROCESSEUR CHEZ INTEL LES ÉTAPES LES CONTRAINTES

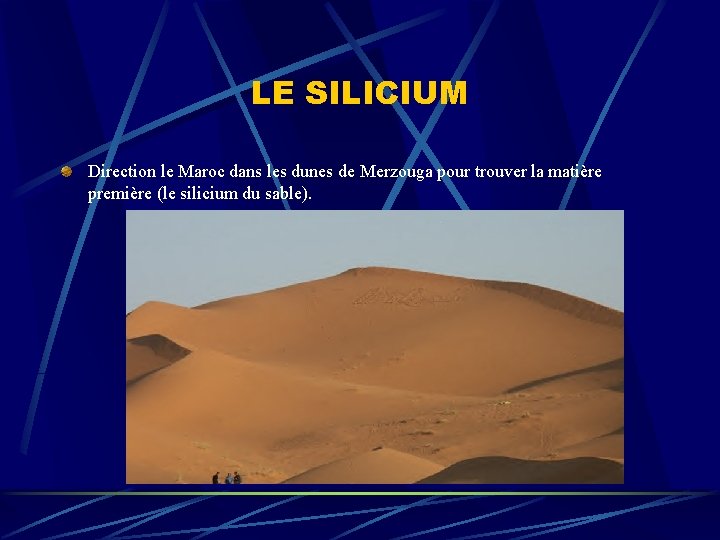

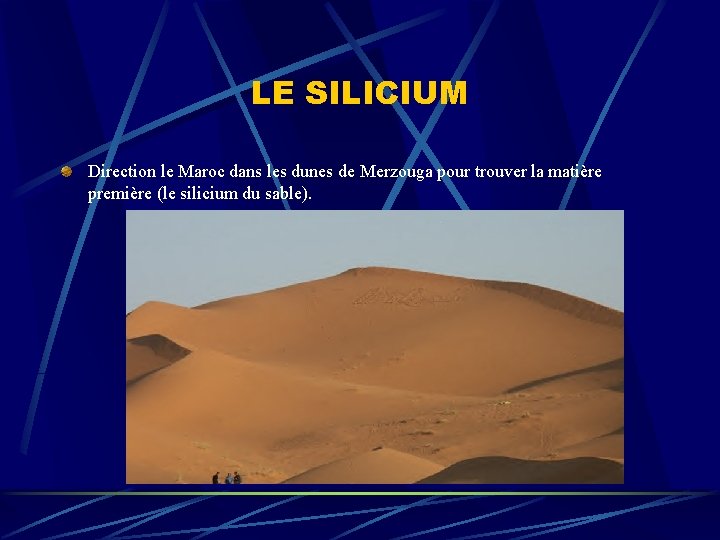

LE SILICIUM Direction le Maroc dans les dunes de Merzouga pour trouver la matière première (le silicium du sable).

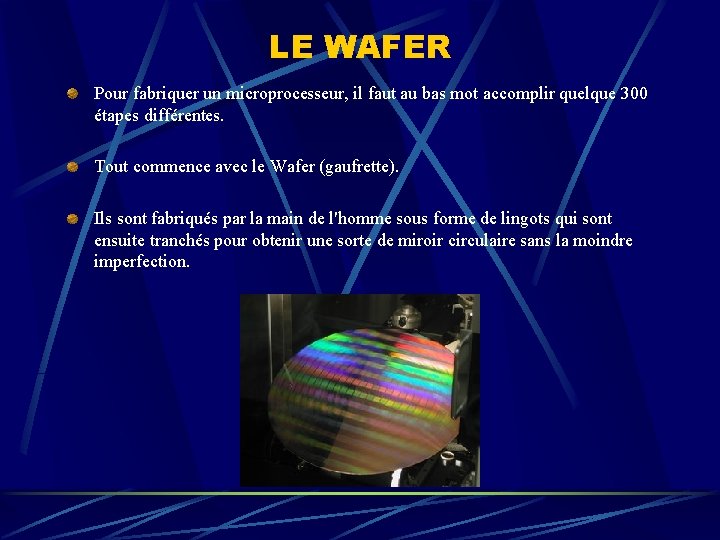

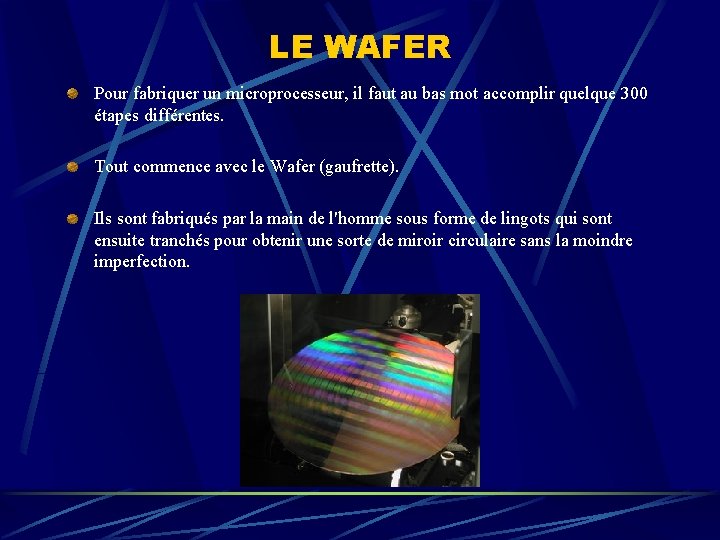

LE WAFER Pour fabriquer un microprocesseur, il faut au bas mot accomplir quelque 300 étapes différentes. Tout commence avec le Wafer (gaufrette). Ils sont fabriqués par la main de l'homme sous forme de lingots qui sont ensuite tranchés pour obtenir une sorte de miroir circulaire sans la moindre imperfection.

LE WAFER La première étape consiste à chauffer le wafer en le plaçant dans un four à très haute température afin de faire apparaître une couche d'oxyde qui agira comme un isolant (sorte de portier électrique empêchant ou permettant au courant de circuler). Le Wafer est ensuite enduit d'une substance photosensible qui devient soluble lorsqu'elle est exposée aux lumières ultra-violettes.

LE WAFER Puis c'est le tour de la lithographie, où le cœur des puces et donc les millions de transistors qu'elles contiennent sont déposés sur le wafer. Rappelons, pour vous donner une idée d'échelle qu'un transistor est mille fois plus petit que l'épaisseur d'un cheveu humain et que son fonctionnement se résume à laisser passer ou non le courant. Schématiquement un transistor peut allumer ou éteindre la lumière près d'un trillion de fois à la seconde.

LE WAFER Le Wafer subit ensuite le « doping » (ou dopage en français). Cette opération consiste à bombarder les zones exposées du Wafer par des ions chargés négativement et positivement afin d'altérer la façon dont le courant circule dans la puce.

LES MICROPROCESSEURS Un Wafer de 300 mm peut compter jusqu'à 500 processeurs Prescott. Une fois le Wafer produit, il faut le tester. Une fois validé, le Wafer est découpé pour obtenir les microprocesseurs C'est uniquement en toute fin de production que la puce est testée pour déterminer sa fréquence maximale de fonctionnement avant d'être marquée.

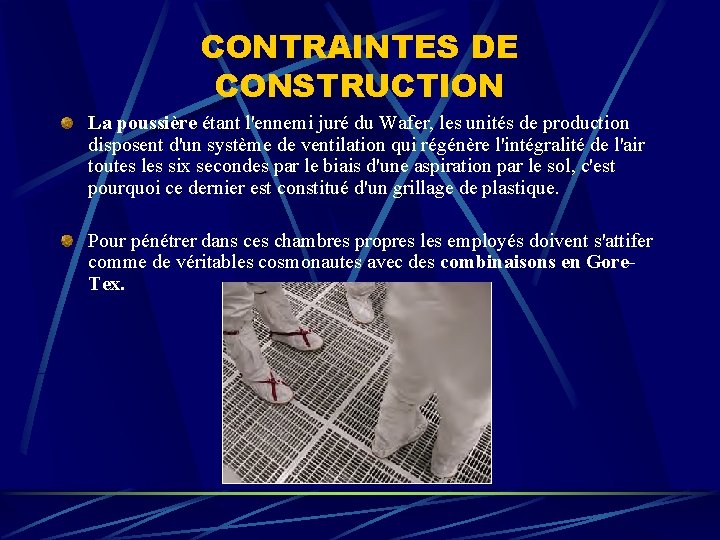

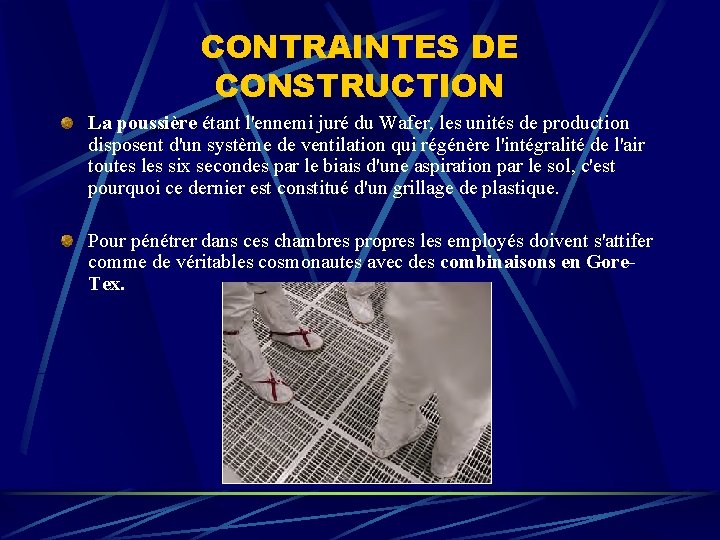

CONTRAINTES DE CONSTRUCTION La poussière étant l'ennemi juré du Wafer, les unités de production disposent d'un système de ventilation qui régénère l'intégralité de l'air toutes les six secondes par le biais d'une aspiration par le sol, c'est pourquoi ce dernier est constitué d'un grillage de plastique. Pour pénétrer dans ces chambres propres les employés doivent s'attifer comme de véritables cosmonautes avec des combinaisons en Gore. Tex.

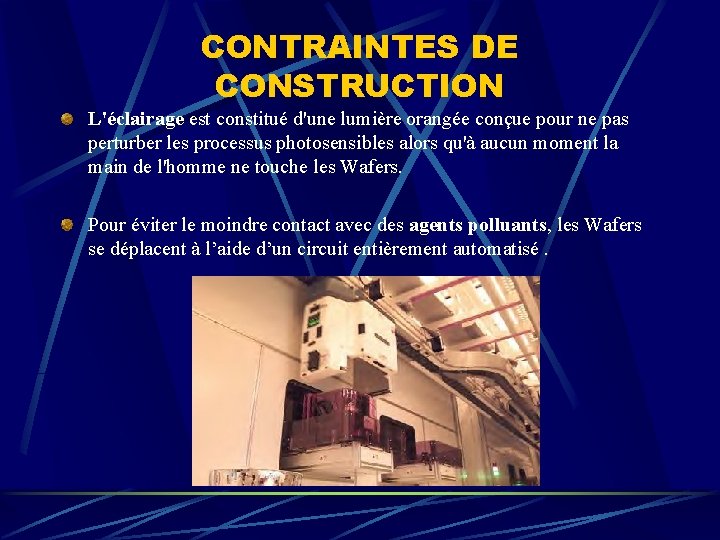

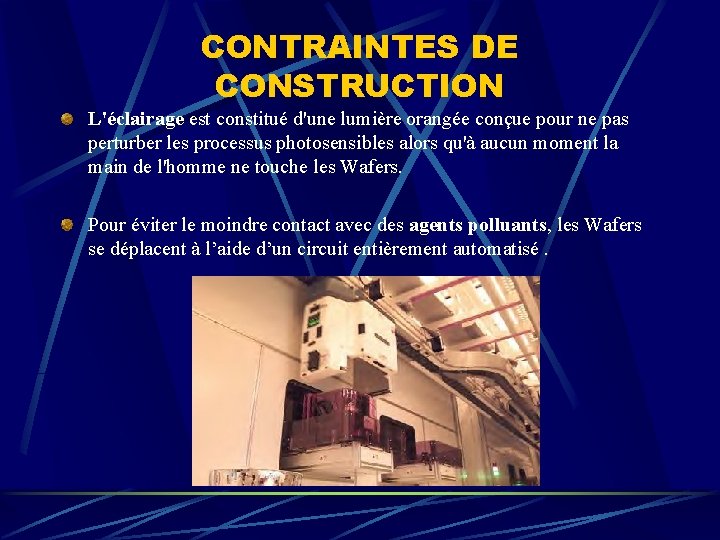

CONTRAINTES DE CONSTRUCTION L'éclairage est constitué d'une lumière orangée conçue pour ne pas perturber les processus photosensibles alors qu'à aucun moment la main de l'homme ne touche les Wafers. Pour éviter le moindre contact avec des agents polluants, les Wafers se déplacent à l’aide d’un circuit entièrement automatisé.

ÉVOLUTION DES PERFORMANCES CHEZ INTEL

ÉVOLUTION DES PERFORMANCES DES MICROPROCESSEURS INTEL

ÉVOLUTION DE LA FINESSE DE GARVURE CHEZ INTEL

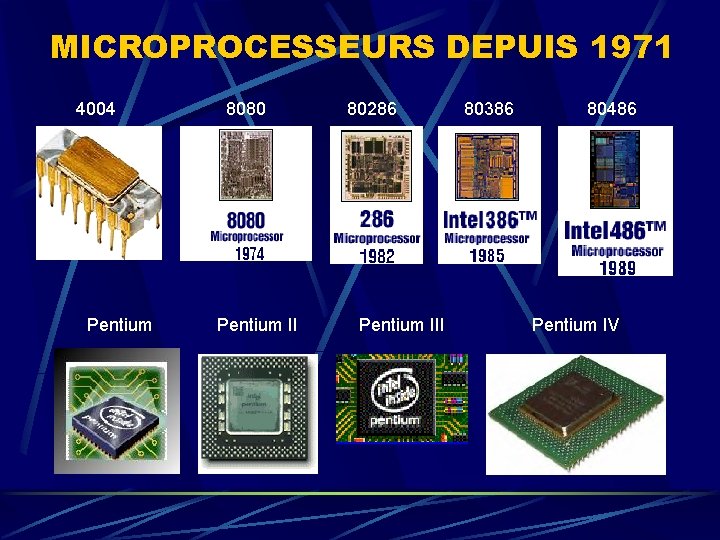

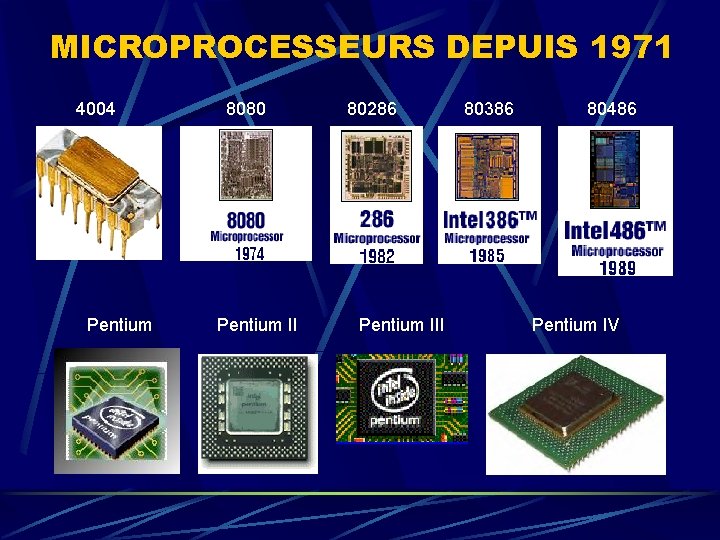

MICROPROCESSEURS DEPUIS 1971 4004 Pentium 8080 Pentium II 80286 Pentium III 80386 80486 Pentium IV

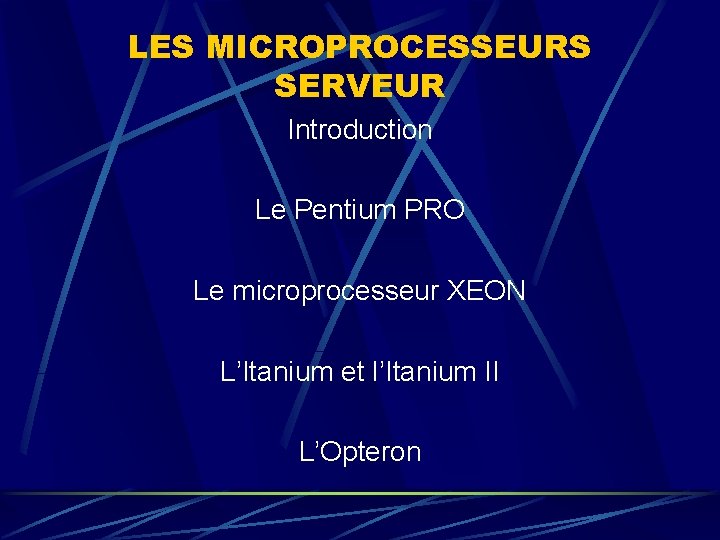

LES MICROPROCESSEURS SERVEUR Introduction Le Pentium PRO Le microprocesseur XEON L’Itanium et l’Itanium II L’Opteron

INTRODUCTION Même si un microprocesseur PC standard peut être utilisé dans un serveur réseau (et vis versa), INTEL et AMD ont développé des microprocesseurs spécifiques pour les serveurs réseaux.

LE PENTIUM PRO Le Pentium Pro est le premier microprocesseur INTEL de 6ème génération. les caches (en taille et en vitesse) sont supérieurs à celles des processeurs standard Pentium II et suivants. Ceci améliore fortement les performances. Le Pentium Pro autorise l'utilisation jusque 8 processeurs simultanément

LES MICRORPOCESSEURS XEON Ils sont sortis en mars 99 avec un cache de 512 kb pour les stations de 1 MB pour les serveurs réseaux. La vitesse actuelle (avril 2003) est de 3, 06 Ghz avec un socket 604. Les architectures actuelles se limitent à 8 microprocesseurs en grappe. Le microprocesseur XEON utilise l'Hyper-Threading.

LES MICRORPOCESSEURS XEON Début 2004, INTEL annonce la sortie prochaine d'une nouvelle architecture XEON dénommée NOCOMA. Ce processeur utilisera une architecture hybride 32 - 64 bits (au même titre que l'Opteron d'AMD). Il se comporte comme un processeur 32 bits lorsqu'il tourne avec un système d'exploitation 32 bits et comme un processeur 64 bits lorsqu'il fait tourner des applications 32 bits ou 64 bits lorsqu'il tourne avec un système d'exploitation 64 bits.

L’ITANIUM ET L’ITANIUM II Le premier processeur 64 bits est sorti en 2001. Presque inconnu du grand public, ses caractéristiques en font une "bête de vitesse" par rapport aux processeurs bureautiques courants. L'architecture EPIC utilisée (Explicity Parallel Instruction Computing) lui est spécifiquement dédiée. Couplé avec le chipset spécifique (le 460 GX), les Itanium peuvent être configurés avec un banc allant jusqu'à 512 processeurs. L'Itanium utilise, comme les XEON, trois caches: l L 1 de 32 K (16 K + 16 K) l L 2 de 96 K l L 3 de 2 ou 4 MB

L’ITANIUM ET L’ITANIUM II L‘Itanium II sort fin 2002. Ses caractéristiques ne sont pas très différentes de l'Itanium I. Les vitesses varient de 900 Mhz à 1 Ghz. Le cache L 3 est réduit à 1. 5 ou 3 MB.

L’OPTERON Connus anciennement sous le nom de code « HAMMER » . L'Opteron est sorti début 2003 et il accepte les instruction usuelles 32 bits. Les Opteron sont gravés en 0, 13µ et utilisent un socket spécifique de type 940. Le cache L 2 est de 1 MB. La gestion mémoire n'est plus dévolue au chipset, mais bien directement au processeur qui gère 2 bancs (32 bits) de DDR 333.

L’OPTERON L'Opteron utilise 3 bus Hypertransports qui peuvent être reliés directement à un autre processeur (3, 2 GB/s en bidirectionnel). L'Opteron est décliné sous 3 versions: 100, 200 et 800 (respectivement de 0, 1 et 3 bus processeurs pouvant être utilisés pour des machines utilisant 1, 2 et 8 opteron). Développé par Intel pour sa gamme de processeurs Pentium 4, les instructions SSE 2 font désormais partie de l'Opteron. Elles permettent la manipulation de registres 128 bits et offrent, en théorie, un gain de performance significatif sur les applications de calculs Audio/Vidéo/3 D.

PRIX DES MICROPROCESSEURS ACTUELLES

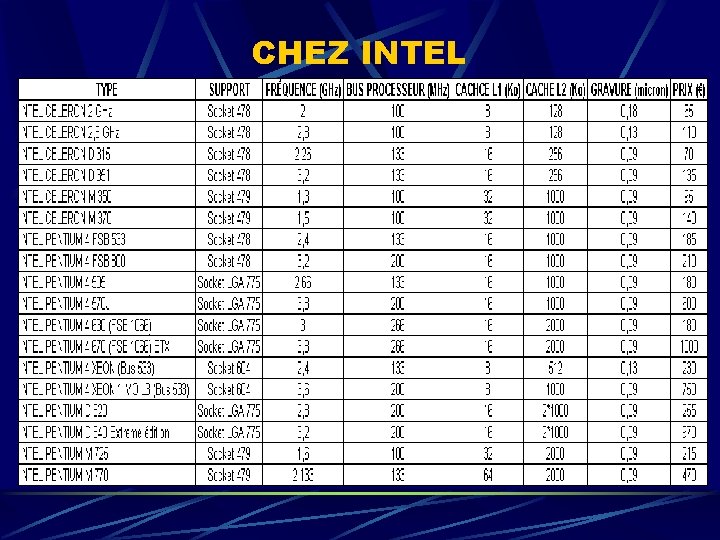

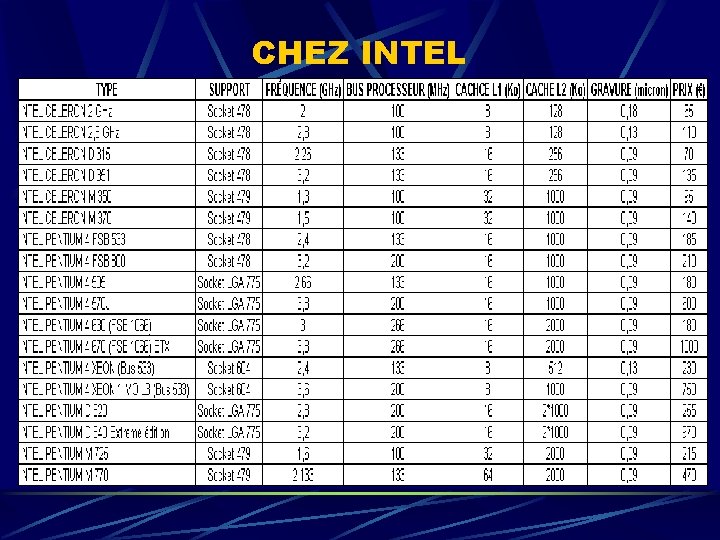

CHEZ INTEL

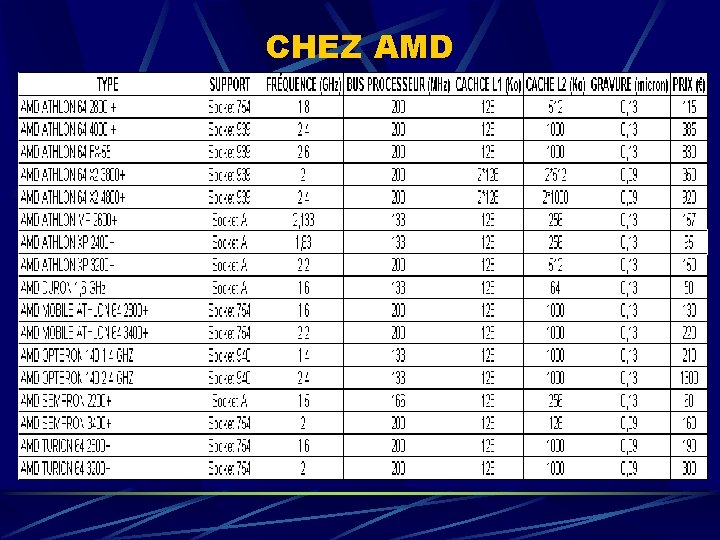

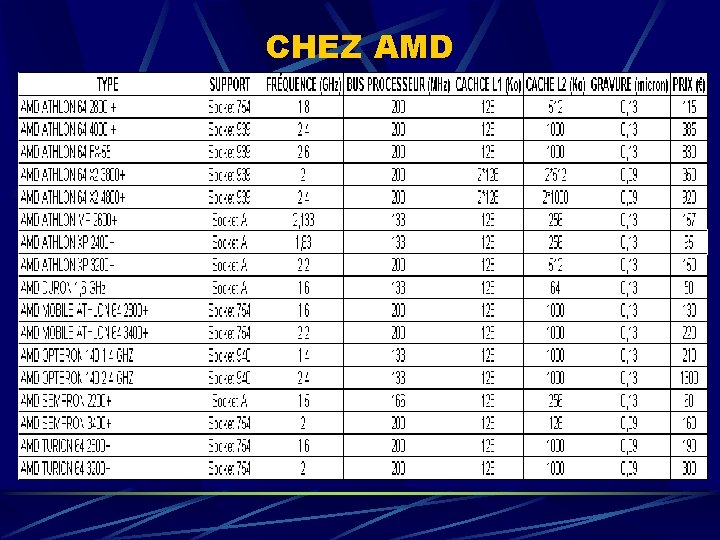

CHEZ AMD

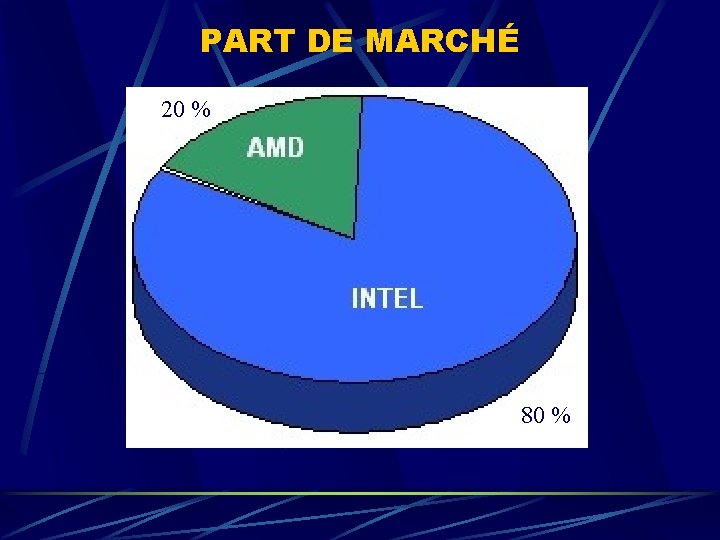

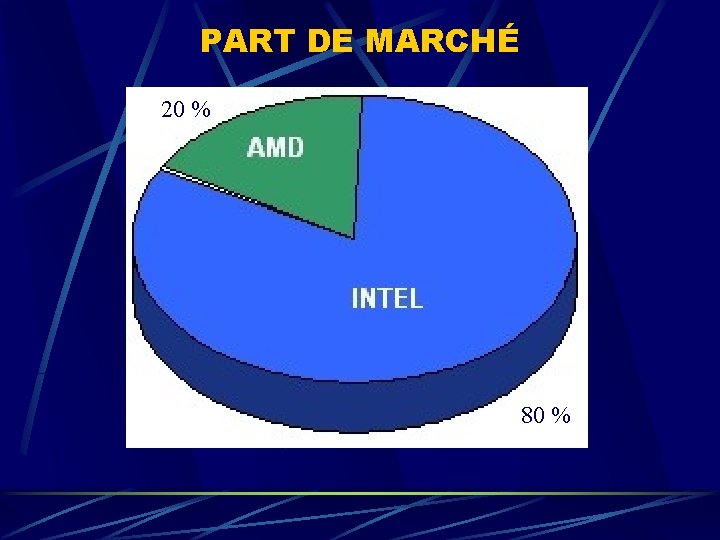

PART DE MARCHÉ 20 % 80 %