Microelectronics Today Problems and Solutions Frank Sill Torres

Microelectronics Today Problems and Solutions Frank Sill Torres Opt. MAlab / ART Universidade Federal de Minas Gerais (UFMG), Brazil Sill Torres: Microelectronics 1

About Me § I’m German (from the North. East) § Master / Ph. D. in Electrical Engenering / Microelectronics (Universität Rostock, Germany) § Research areas: – Low Power Integrated Circuit (IC) Design – IC Design for Reliability (analog / digital) – Nanoelectronics –. . . Sill Torres: Microelectronics 2

Outline 1. Areas of Microelectronics 2. Chip Design 3. State of the Art 4. Problems 5. Solutions 6. Microelectronics at UFMG and in Brazil Sill Torres: Microelectronics 3

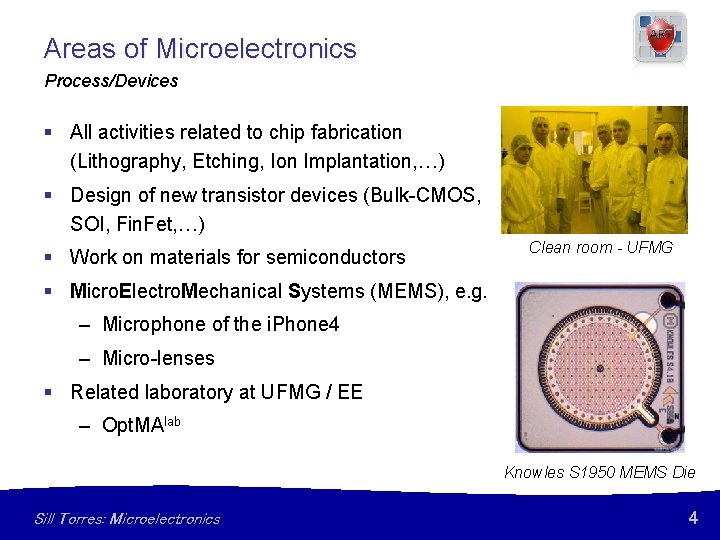

Areas of Microelectronics Process/Devices § All activities related to chip fabrication (Lithography, Etching, Ion Implantation, …) § Design of new transistor devices (Bulk-CMOS, SOI, Fin. Fet, …) § Work on materials for semiconductors Clean room - UFMG § Micro. Electro. Mechanical Systems (MEMS), e. g. – Microphone of the i. Phone 4 – Micro-lenses § Related laboratory at UFMG / EE – Opt. MAlab Knowles S 1950 MEMS Die Sill Torres: Microelectronics 4

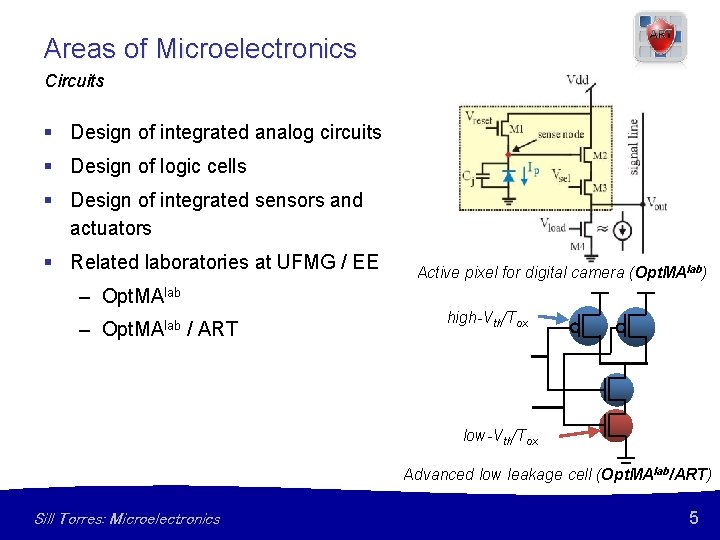

Areas of Microelectronics Circuits § Design of integrated analog circuits § Design of logic cells § Design of integrated sensors and actuators § Related laboratories at UFMG / EE Active pixel for digital camera (Opt. MAlab) – Opt. MAlab / ART high-Vth/Tox low-Vth/Tox Advanced low leakage cell (Opt. MAlab/ART) Sill Torres: Microelectronics 5

Areas of Microelectronics Systems § Design of integrated systems – Application Specific Integrated Systems (ASIC) – Processors – System on Chip (SOC) – Digital / Analog / Mixed-Signal § Design of Intellectual Property (IP) blocks § FPGA design § Related laboratories at UFMG / EE Copyright: ELV. de – Opt. MAlab / ART – LSI – Lab. SCI Sill Torres: Microelectronics 6

Chip Design Sill Torres: Microelectronics 7

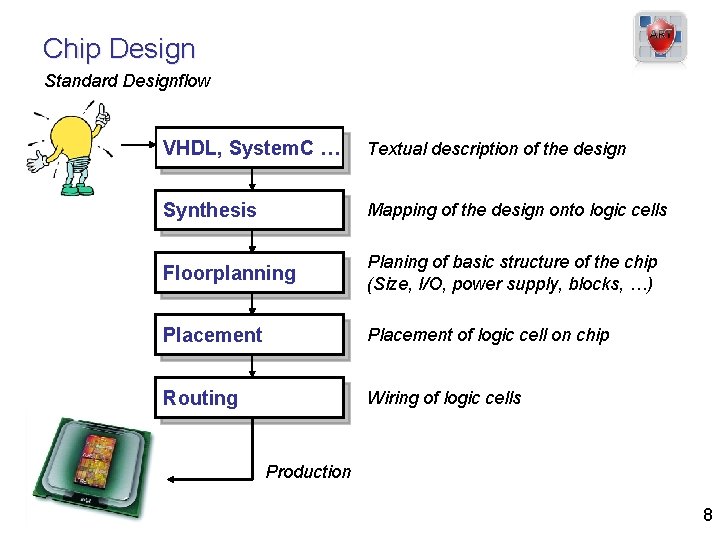

Chip Design Standard Designflow VHDL, System. C … Textual description of the design Synthesis Mapping of the design onto logic cells Floorplanning Planing of basic structure of the chip (Size, I/O, power supply, blocks, …) Placement of logic cell on chip Routing Wiring of logic cells Production Sill Torres: Microelectronics 88

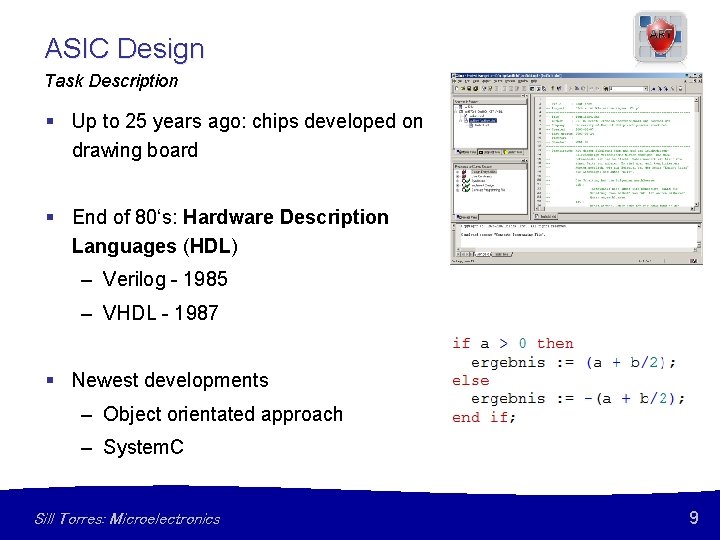

ASIC Design Task Description § Up to 25 years ago: chips developed on drawing board § End of 80‘s: Hardware Description Languages (HDL) – Verilog - 1985 – VHDL - 1987 § Newest developments – Object orientated approach – System. C Sill Torres: Microelectronics 9

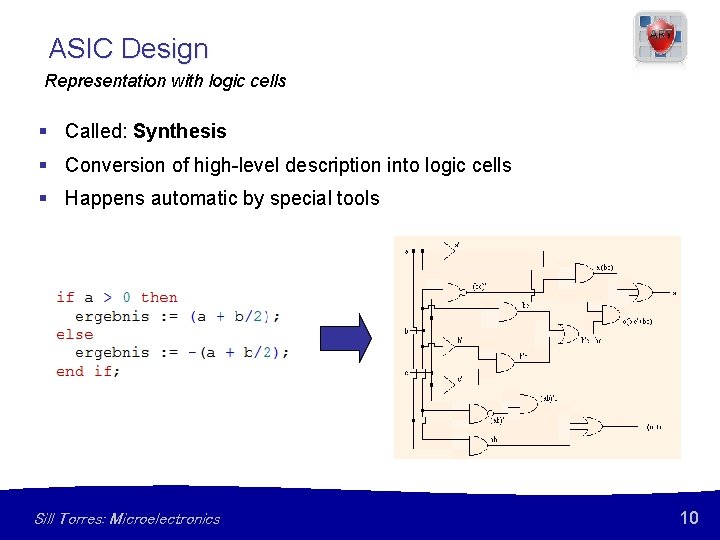

ASIC Design Representation with logic cells § Called: Synthesis § Conversion of high-level description into logic cells § Happens automatic by special tools Sill Torres: Microelectronics 10

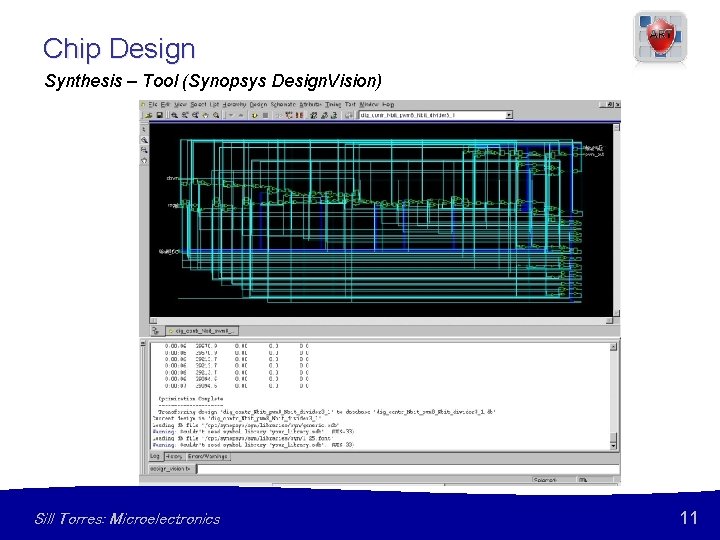

Chip Design Synthesis – Tool (Synopsys Design. Vision) Sill Torres: Microelectronics 11

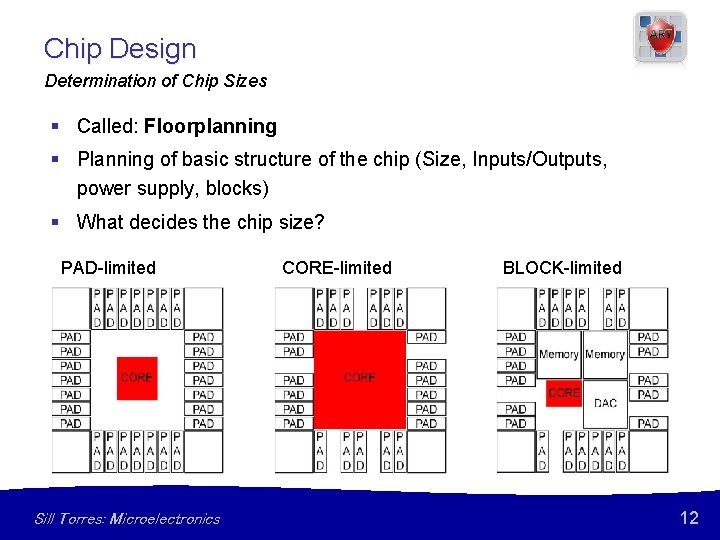

Chip Design Determination of Chip Sizes § Called: Floorplanning § Planning of basic structure of the chip (Size, Inputs/Outputs, power supply, blocks) § What decides the chip size? PAD-limited Sill Torres: Microelectronics CORE-limited BLOCK-limited 12

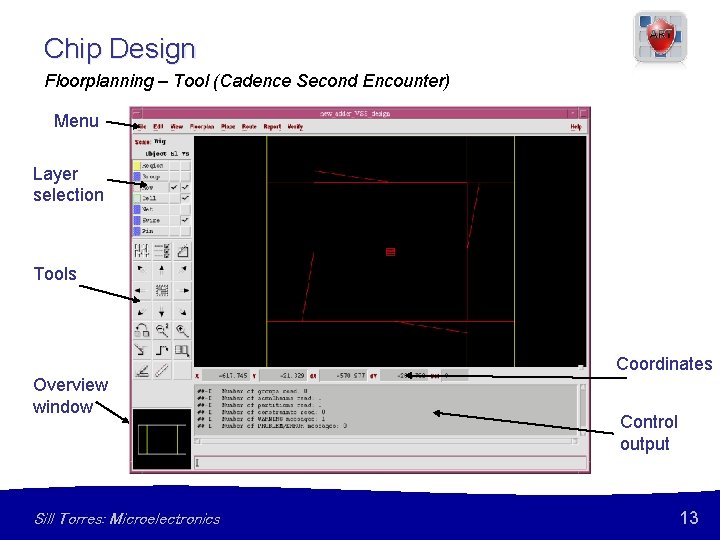

Chip Design Floorplanning – Tool (Cadence Second Encounter) Menu Layer selection Tools Coordinates Overview window Sill Torres: Microelectronics Control output 13

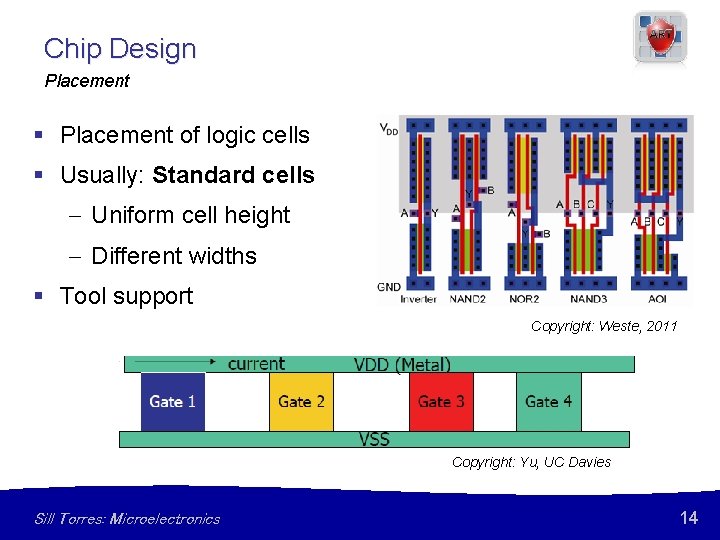

Chip Design Placement § Placement of logic cells § Usually: Standard cells - Uniform cell height - Different widths § Tool support Copyright: Weste, 2011 Copyright: Yu, UC Davies Sill Torres: Microelectronics 14

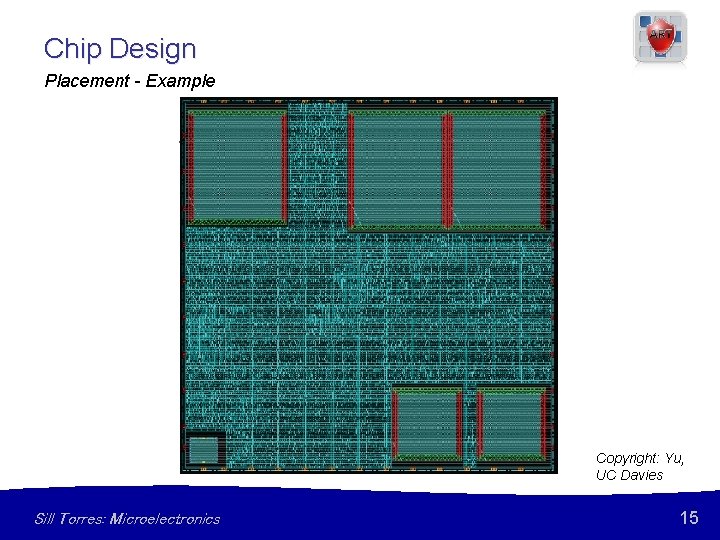

Chip Design Placement - Example Copyright: Yu, UC Davies Sill Torres: Microelectronics 15

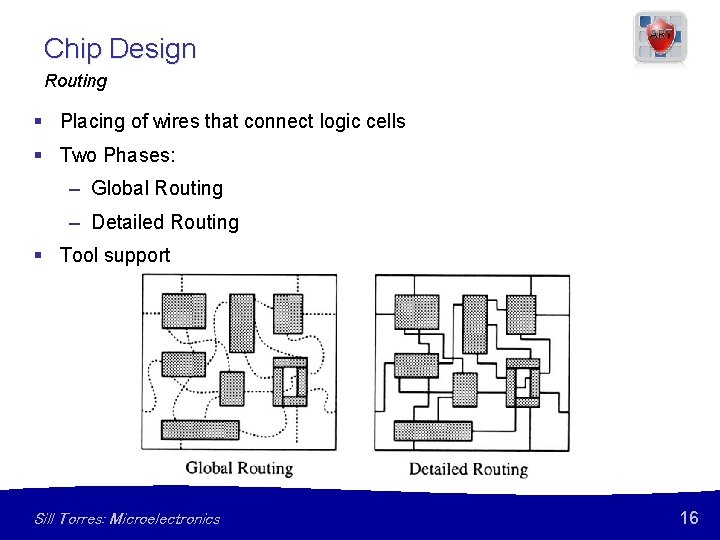

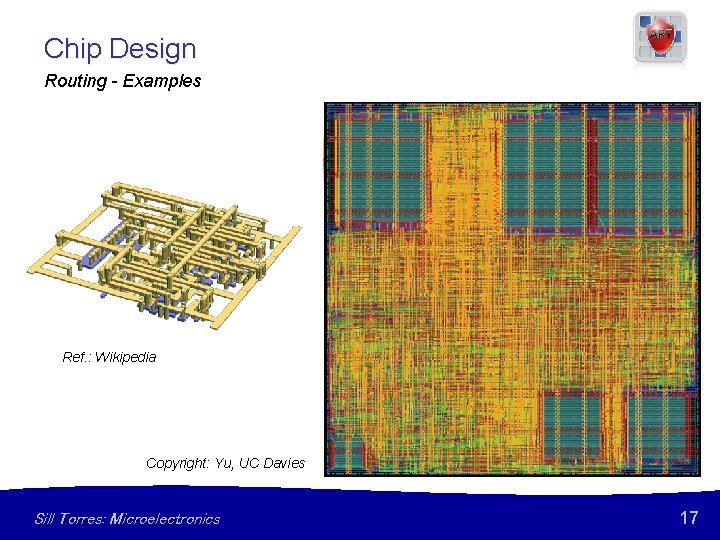

Chip Design Routing § Placing of wires that connect logic cells § Two Phases: – Global Routing – Detailed Routing § Tool support Sill Torres: Microelectronics 16

Chip Design Routing - Examples Ref. : Wikipedia Copyright: Yu, UC Davies Sill Torres: Microelectronics 17

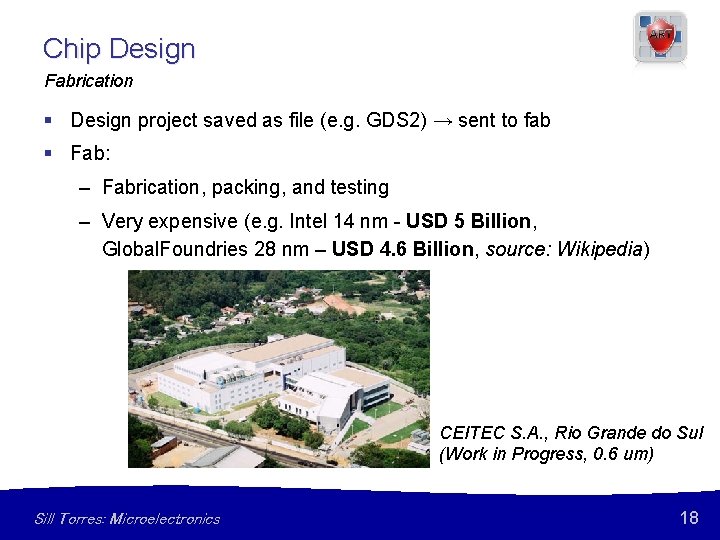

Chip Design Fabrication § Design project saved as file (e. g. GDS 2) → sent to fab § Fab: – Fabrication, packing, and testing – Very expensive (e. g. Intel 14 nm - USD 5 Billion, Global. Foundries 28 nm – USD 4. 6 Billion, source: Wikipedia) CEITEC S. A. , Rio Grande do Sul (Work in Progress, 0. 6 um) Sill Torres: Microelectronics 18

Chip Design Houses § In the past – Chip designer and factories together – Intellectual Property belongs to factory § Today – Chip designers and factories separate – Intellectual Property stays with designer Sill Torres: Microelectronics 19

State of the Art Sill Torres: Microelectronics 20

State of the Art Overview § Technology sizes: starting from 22 nm § Processors with 64 bit § Multi-cores § Processors for – Servers (Opteron, Xeon, …) – PCs (Core i 3/i 5/i 7, Fusion, …) – Smartphones / Pads (ARM, Atom, . . . ) § High integration of functionalities – Memory controller – Graphic card Sill Torres: Microelectronics 21

![State of the Art Processors Transistors [Mill. ] Transistors 130 n. M 400 90 State of the Art Processors Transistors [Mill. ] Transistors 130 n. M 400 90](http://slidetodoc.com/presentation_image/0a323f164c5e917793aeae6daa2a57cb/image-22.jpg)

State of the Art Processors Transistors [Mill. ] Transistors 130 n. M 400 90 n. M 100 n. M 300 Yonah 65 n. M 151 Mill. 200 100 0 0 Northwood 55 Mill. Prescott 125 Mill. 45 n. M Yonah, 151 Mill. 2002 Sill Torres: Microelectronics 2004 150 n. M Technology Wolfdale 410 Mill. 500 2006 Year 50 n. M 2008 22

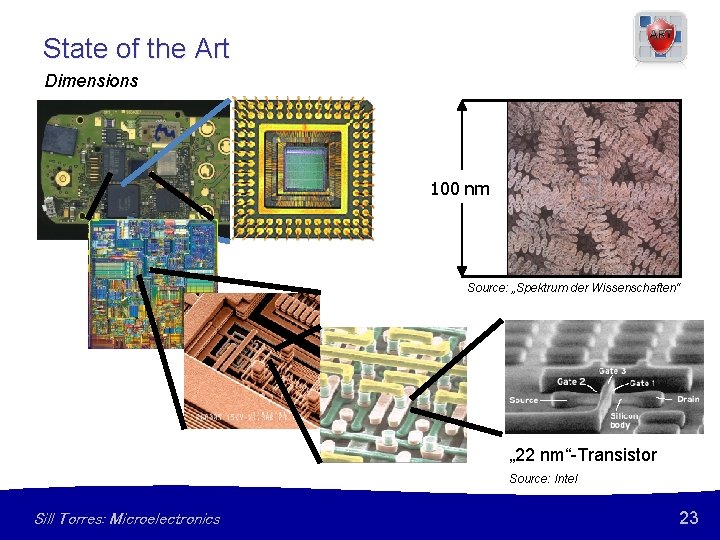

State of the Art Dimensions m 10 cm 100 nm 10 111 mm cm µm µm Source: „Spektrum der Wissenschaften“ „ 22 nm“-Transistor Source: Intel Sill Torres: Microelectronics 23

Problems Sill Torres: Microelectronics 24

![Problems Power Dissipation So. C Consumer Portable Power Trend [Source: ITRS, 2010 Update] Sill Problems Power Dissipation So. C Consumer Portable Power Trend [Source: ITRS, 2010 Update] Sill](http://slidetodoc.com/presentation_image/0a323f164c5e917793aeae6daa2a57cb/image-25.jpg)

Problems Power Dissipation So. C Consumer Portable Power Trend [Source: ITRS, 2010 Update] Sill Torres: Microelectronics 25

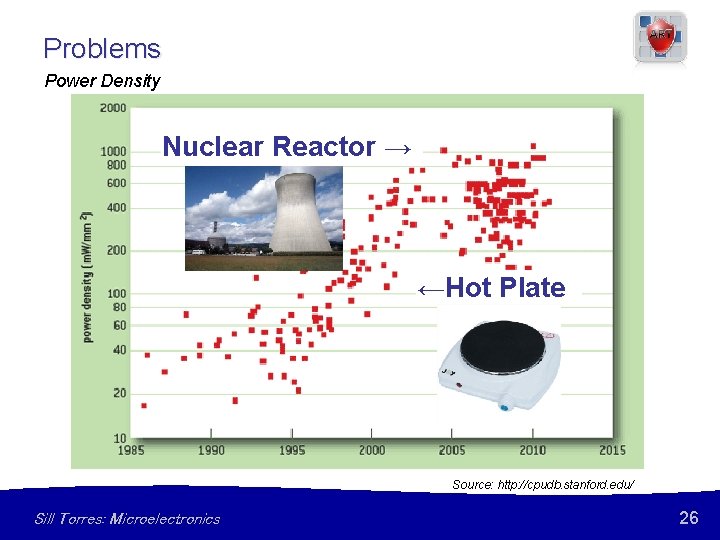

Problems Power Density Nuclear Reactor → ←Hot Plate Source: http: //cpudb. stanford. edu/ Sill Torres: Microelectronics 26

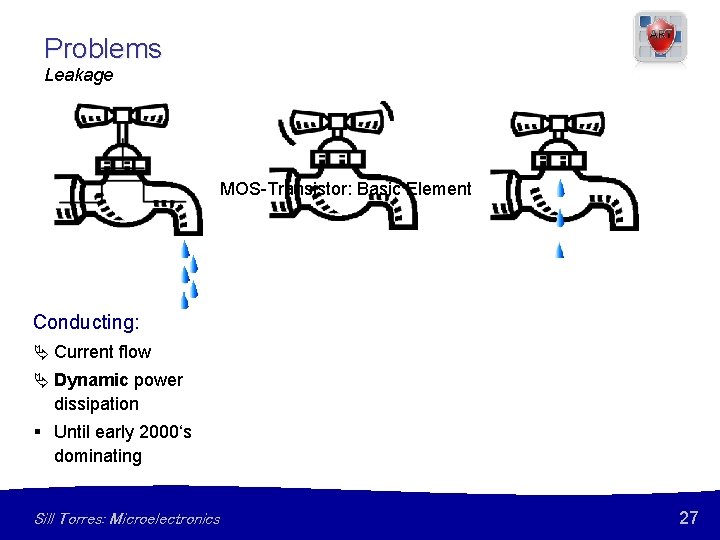

Problems Leakage MOS-Transistor: Basic Element Conducting: Closed (ideal): Closed (real): Current flow No Current Still current flow Dynamic power dissipation No power dissipation (Leakage) § Until early 2000‘s dominating Sill Torres: Microelectronics Power dissipation 27

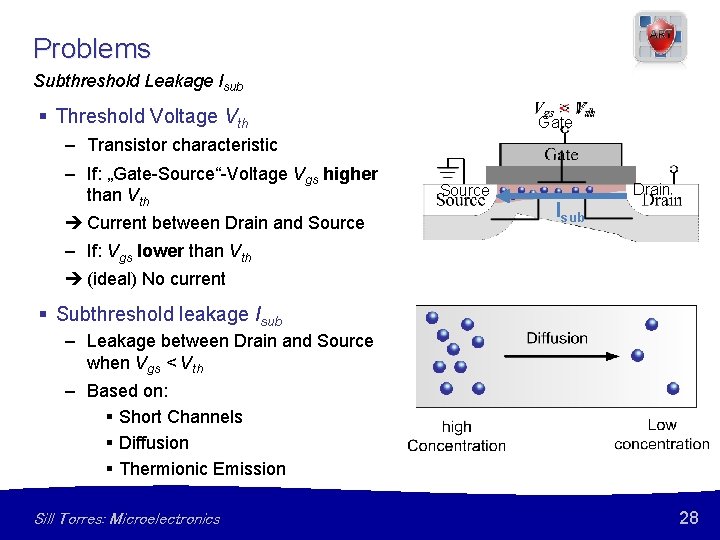

Problems Subthreshold Leakage Isub § Threshold Voltage Vth Gate – Transistor characteristic – If: „Gate-Source“-Voltage Vgs higher than Vth Current between Drain and Source Drain Isub – If: Vgs lower than Vth (ideal) No current § Subthreshold leakage Isub – Leakage between Drain and Source when Vgs < Vth – Based on: § Short Channels § Diffusion § Thermionic Emission Sill Torres: Microelectronics 28

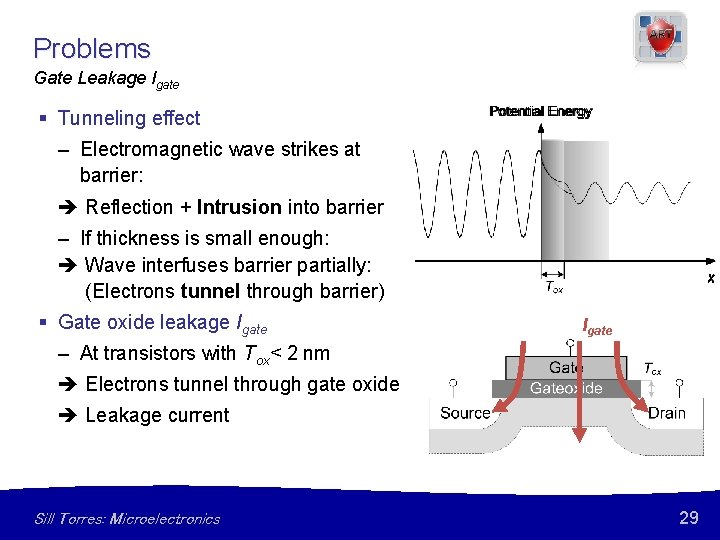

Problems Gate Leakage Igate § Tunneling effect – Electromagnetic wave strikes at barrier: Reflection + Intrusion into barrier – If thickness is small enough: Wave interfuses barrier partially: (Electrons tunnel through barrier) § Gate oxide leakage Igate – At transistors with Tox< 2 nm Electrons tunnel through gate oxide Leakage current Sill Torres: Microelectronics 29

Problems Process Failures § Occur at production phase § Based on – Process Variations – Particles – … Source: Mak Sill Torres: Microelectronics 30

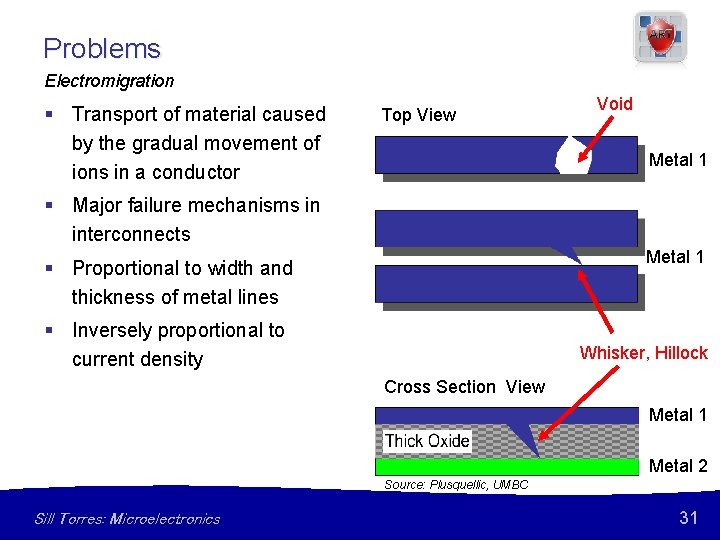

Problems Electromigration § Transport of material caused by the gradual movement of ions in a conductor Top View Void Metal 1 § Major failure mechanisms in interconnects Metal 1 § Proportional to width and thickness of metal lines § Inversely proportional to current density Whisker, Hillock Cross Section View Metal 1 Metal 2 Source: Plusquellic, UMBC Sill Torres: Microelectronics 31

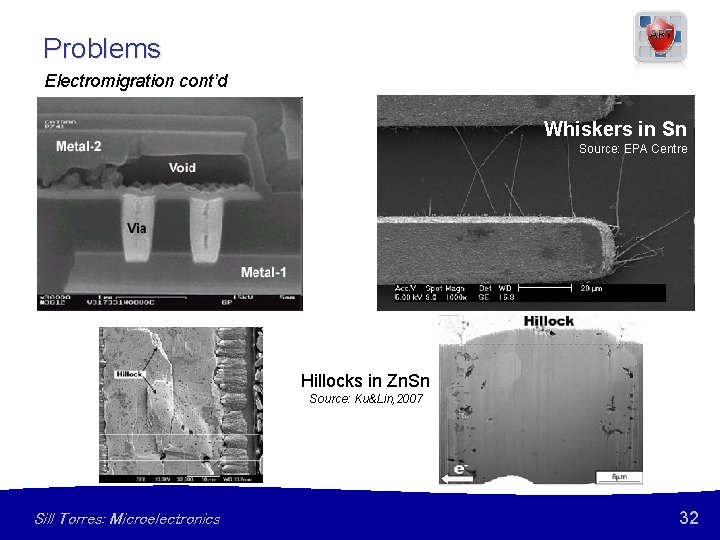

Problems Electromigration cont’d Void in 0. 45 mm Al-0. 5%Cu line Source: IMM-Bologna Whiskers in Sn Source: EPA Centre Hillocks in Zn. Sn Source: Ku&Lin, 2007 Sill Torres: Microelectronics 32

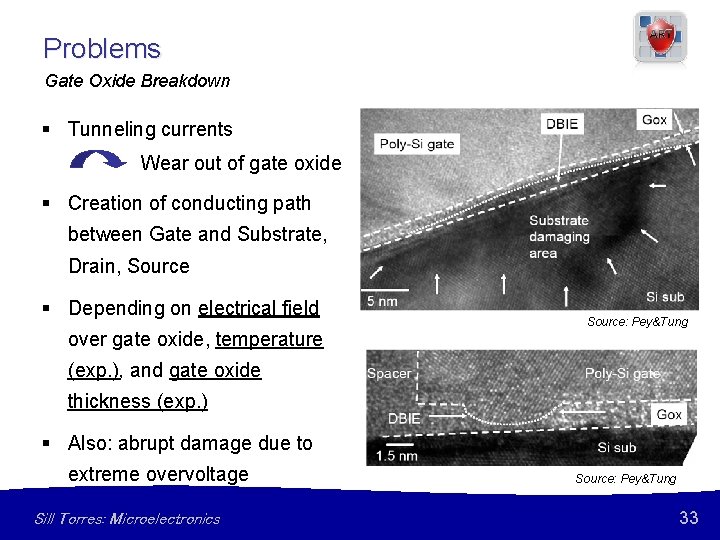

Problems Gate Oxide Breakdown § Tunneling currents Wear out of gate oxide § Creation of conducting path between Gate and Substrate, Drain, Source § Depending on electrical field over gate oxide, temperature Source: Pey&Tung (exp. ), and gate oxide thickness (exp. ) § Also: abrupt damage due to extreme overvoltage Sill Torres: Microelectronics Source: Pey&Tung 33

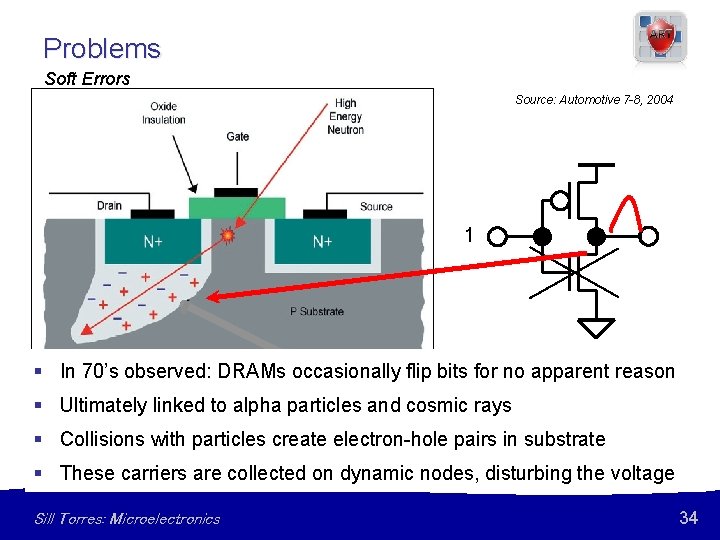

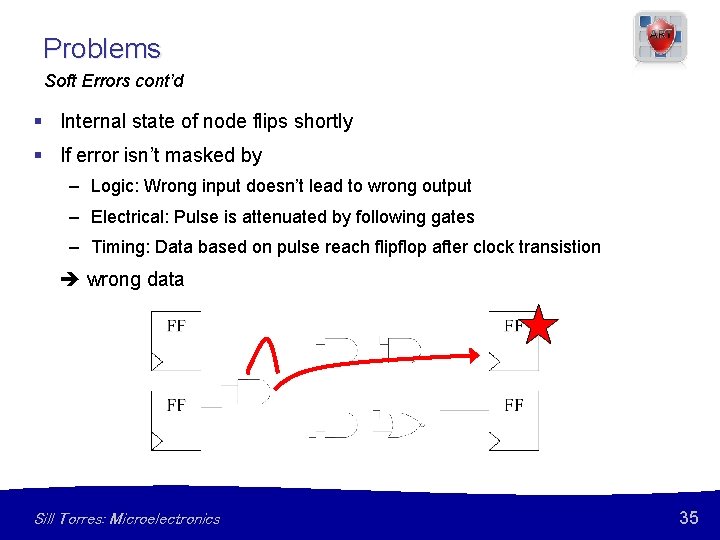

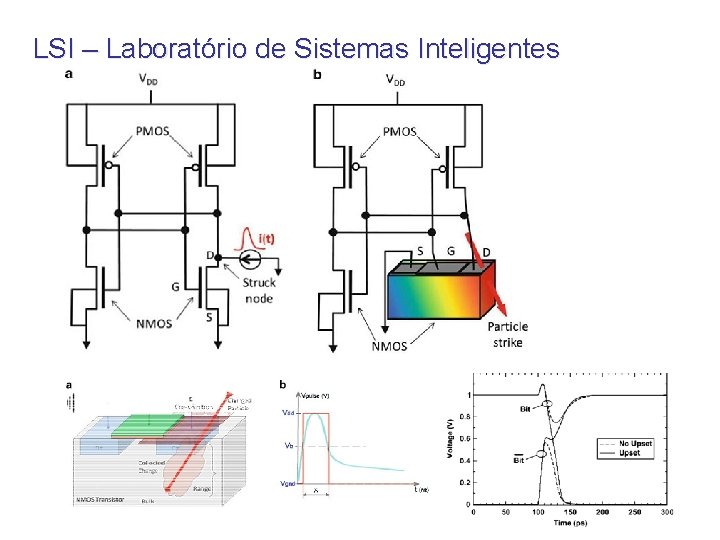

Problems Soft Errors Source: Automotive 7 -8, 2004 1 § In 70’s observed: DRAMs occasionally flip bits for no apparent reason § Ultimately linked to alpha particles and cosmic rays § Collisions with particles create electron-hole pairs in substrate § These carriers are collected on dynamic nodes, disturbing the voltage Sill Torres: Microelectronics 34

Problems Soft Errors cont’d § Internal state of node flips shortly § If error isn’t masked by – Logic: Wrong input doesn’t lead to wrong output – Electrical: Pulse is attenuated by following gates – Timing: Data based on pulse reach flipflop after clock transistion wrong data Sill Torres: Microelectronics 35

![Problems Delay [s] S la y ID de Drain current IDS [p. A] Temperature Problems Delay [s] S la y ID de Drain current IDS [p. A] Temperature](http://slidetodoc.com/presentation_image/0a323f164c5e917793aeae6daa2a57cb/image-36.jpg)

Problems Delay [s] S la y ID de Drain current IDS [p. A] Temperature Variations Temperature [°C] Threshold voltage Vth changes with temperature drain-source current changes delay changes Source: Burleson, UMASS, 2007 Sill Torres: Microelectronics 36

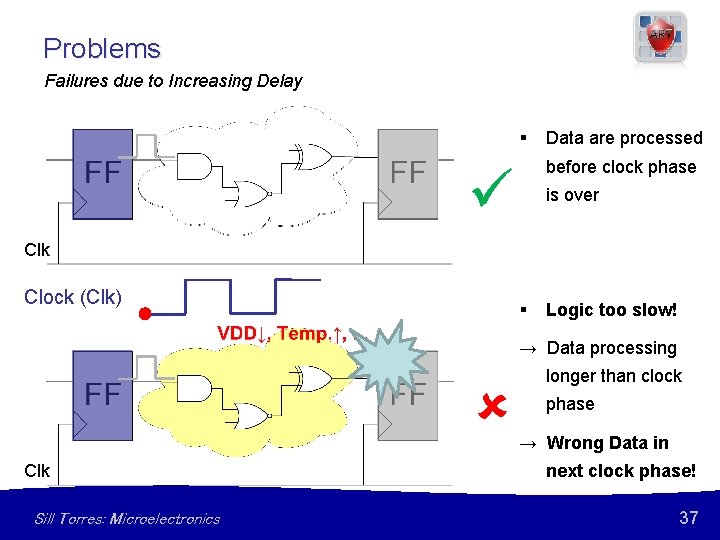

Problems Failures due to Increasing Delay § Data are processed before clock phase is over Clk Clock (Clk) § Logic too slow! → Data processing Clk Sill Torres: Microelectronics longer than clock phase → Wrong Data in next clock phase! 37

Solutions Sill Torres: Microelectronics 38

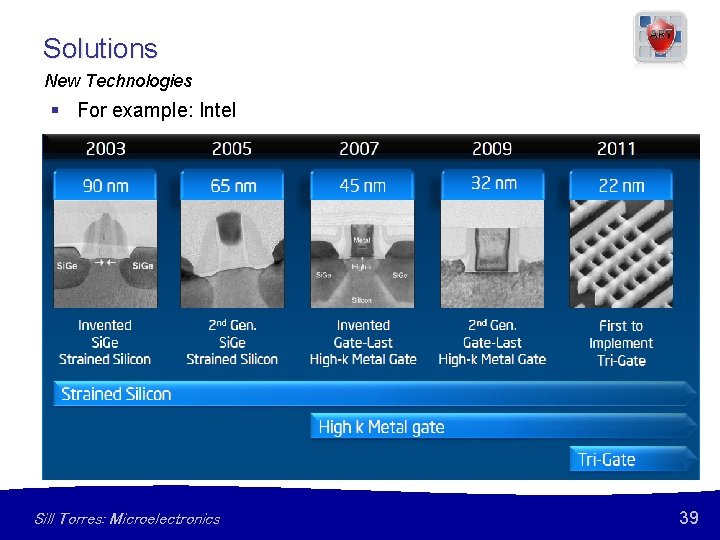

Solutions New Technologies § For example: Intel Sill Torres: Microelectronics 39

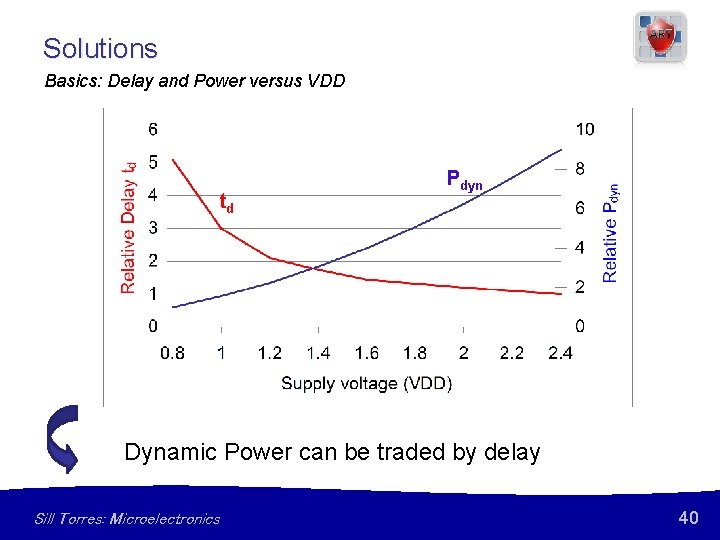

Solutions Basics: Delay and Power versus VDD td Pdyn Dynamic Power can be traded by delay Sill Torres: Microelectronics 40

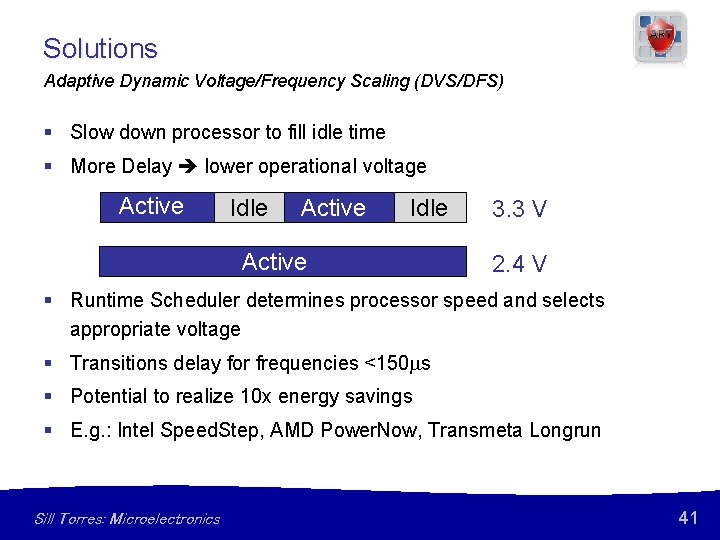

Solutions Adaptive Dynamic Voltage/Frequency Scaling (DVS/DFS) § Slow down processor to fill idle time § More Delay lower operational voltage Active Idle Active 3. 3 V 2. 4 V § Runtime Scheduler determines processor speed and selects appropriate voltage § Transitions delay for frequencies <150 s § Potential to realize 10 x energy savings § E. g. : Intel Speed. Step, AMD Power. Now, Transmeta Longrun Sill Torres: Microelectronics 41

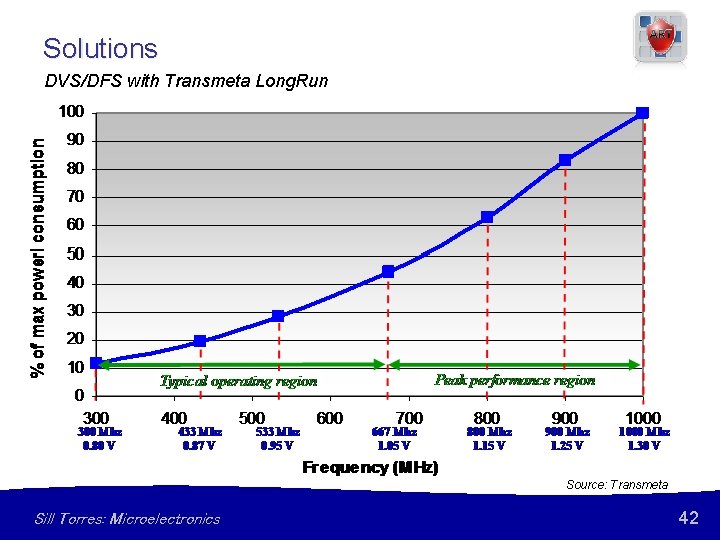

Solutions DVS/DFS with Transmeta Long. Run Source: Transmeta Sill Torres: Microelectronics 42

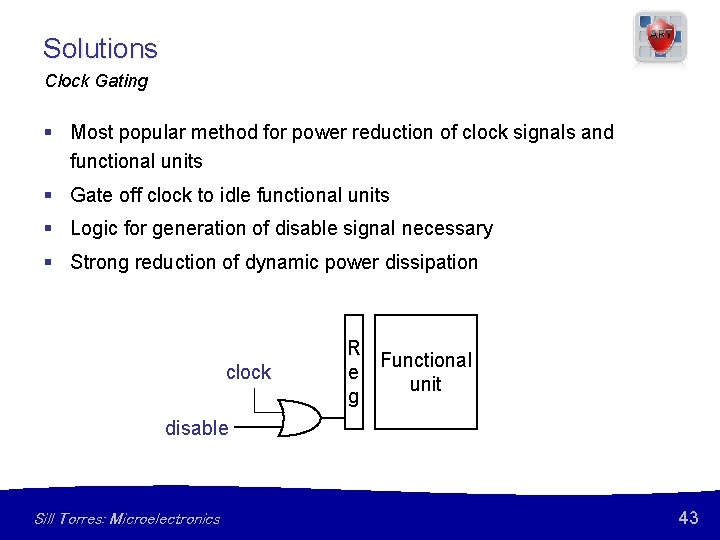

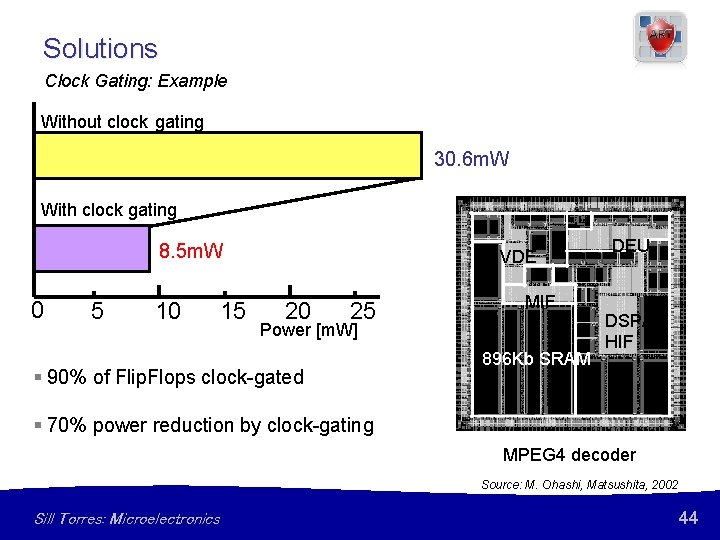

Solutions Clock Gating § Most popular method for power reduction of clock signals and functional units § Gate off clock to idle functional units § Logic for generation of disable signal necessary § Strong reduction of dynamic power dissipation clock R Functional e unit g disable Sill Torres: Microelectronics 43

Solutions Clock Gating: Example Without clock gating 30. 6 m. W With clock gating 8. 5 m. W 0 5 10 15 VDE 20 25 MIF Power [m. W] § 90% of Flip. Flops clock-gated 896 Kb SRAM DEU DSP/ HIF § 70% power reduction by clock-gating MPEG 4 decoder Source: M. Ohashi, Matsushita, 2002 Sill Torres: Microelectronics 44

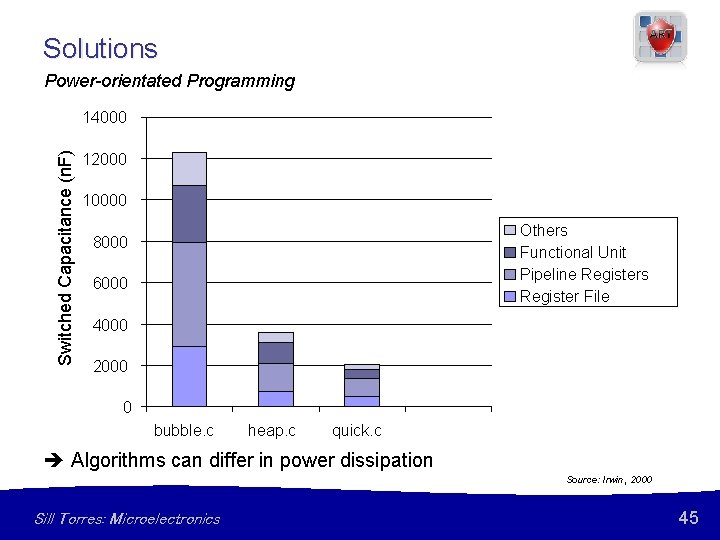

Solutions Power-orientated Programming Switched Capacitance (n. F) 14000 12000 10000 Others Functional Unit Pipeline Registers Register File 8000 6000 4000 2000 0 bubble. c heap. c quick. c Algorithms can differ in power dissipation Source: Irwin, 2000 Sill Torres: Microelectronics 45

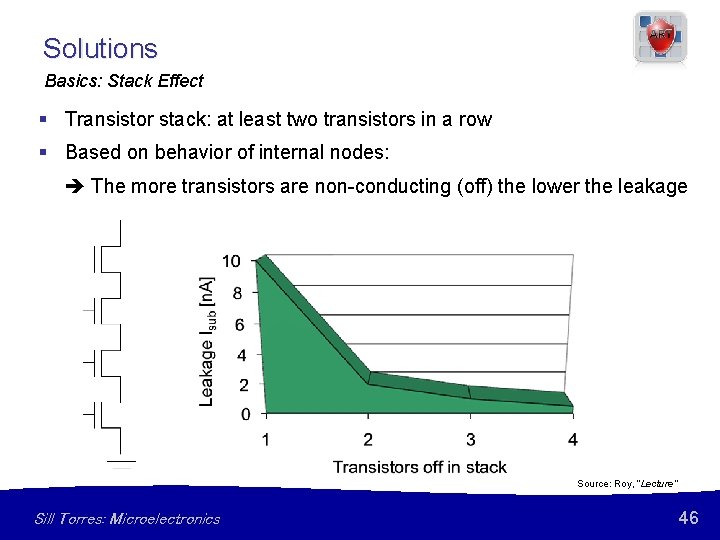

Solutions Basics: Stack Effect § Transistor stack: at least two transistors in a row § Based on behavior of internal nodes: The more transistors are non-conducting (off) the lower the leakage Source: Roy, “Lecture” Sill Torres: Microelectronics 46

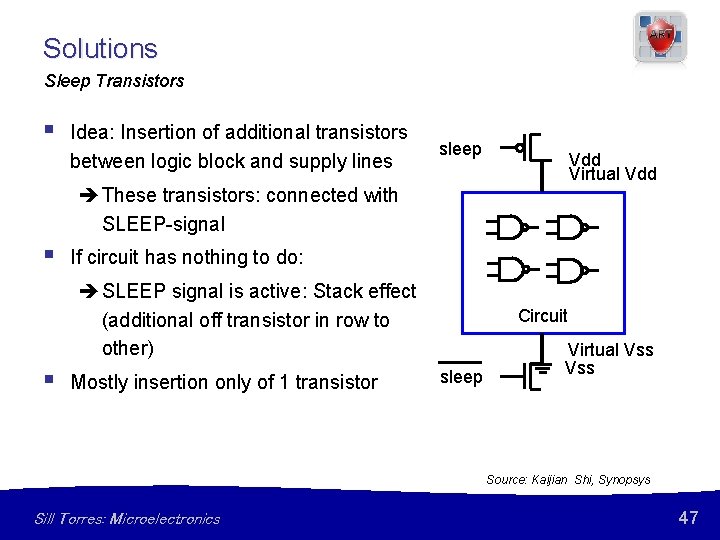

Solutions Sleep Transistors § Idea: Insertion of additional transistors between logic block and supply lines sleep Vdd Virtual Vdd These transistors: connected with SLEEP-signal § If circuit has nothing to do: SLEEP signal is active: Stack effect (additional off transistor in row to other) § Mostly insertion only of 1 transistor Circuit sleep Virtual Vss Source: Kaijian Shi, Synopsys Sill Torres: Microelectronics 47

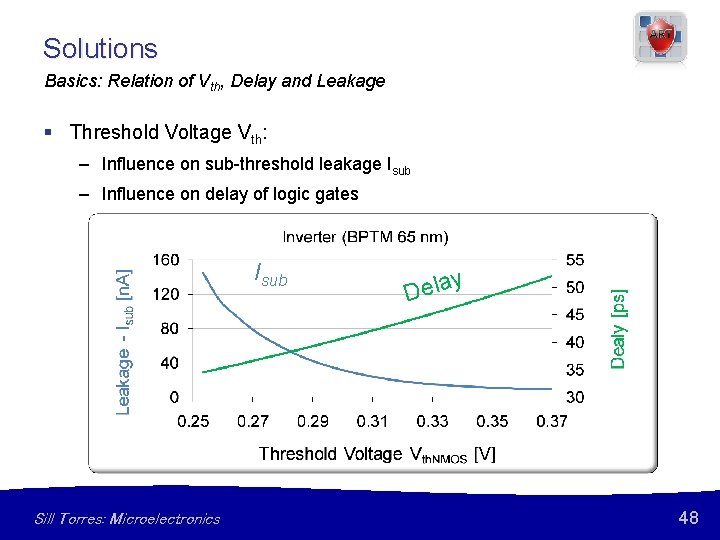

Solutions Basics: Relation of Vth, Delay and Leakage § Threshold Voltage Vth: – Influence on sub-threshold leakage Isub – Influence on delay of logic gates Isub Sill Torres: Microelectronics y a l e D 48

Solutions Dual-Vth “LVT”- Cells § § Cells consist of transistors with low Vth Low delay High leakage For critical paths “HVT”- Cells § § Cells consist of transistors with high Vth Longer delay Low leakage For uncritical paths Leakage reduction at constant performance Sill Torres: Microelectronics 49

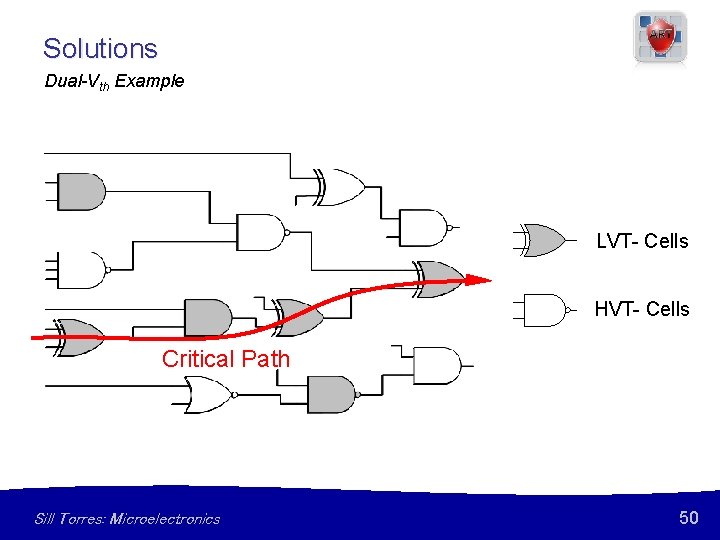

Solutions Dual-Vth Example LVT- Cells HVT- Cells Critical Path Sill Torres: Microelectronics 50

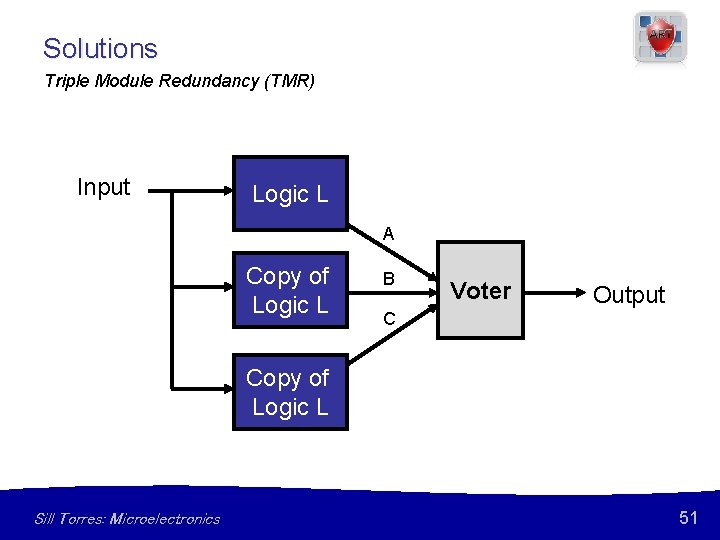

Solutions Triple Module Redundancy (TMR) Input Logic L A Copy of Logic L B Voter Output C Copy of Logic L Sill Torres: Microelectronics 51

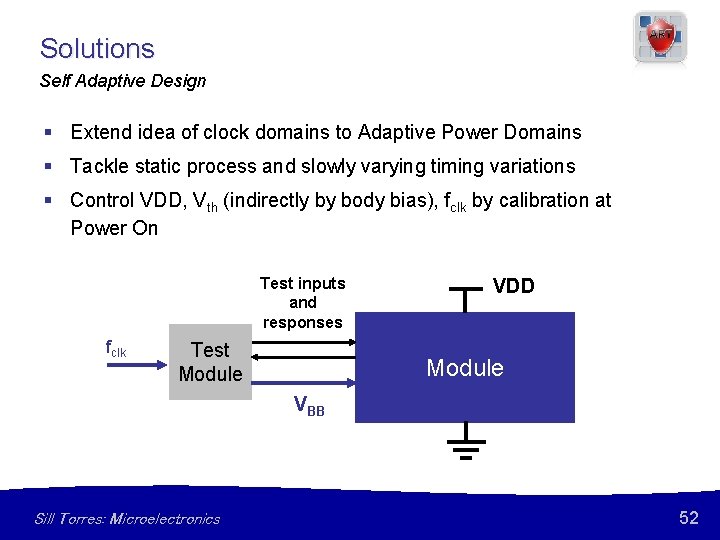

Solutions Self Adaptive Design § Extend idea of clock domains to Adaptive Power Domains § Tackle static process and slowly varying timing variations § Control VDD, Vth (indirectly by body bias), fclk by calibration at Power On Test inputs and responses fclk Test Module VDD Module VBB Sill Torres: Microelectronics 52

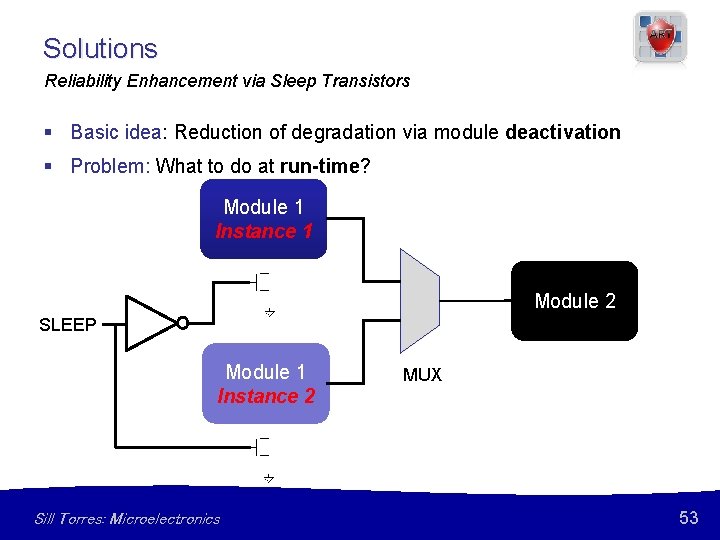

Solutions Reliability Enhancement via Sleep Transistors § Basic idea: Reduction of degradation via module deactivation § Problem: What to do at run-time? Module 1 Instance 1 Module 2 SLEEP Module 1 Instance 2 Sill Torres: Microelectronics MUX 53

Opportunities in Brazil and Activities at UFMG Sill Torres: Microelectronics 54

Opportunities in Brazil § CEITEC S. A. – Design House and Chip factory (Rio Grande do Sul) § Over 22 Design Houses – DHBH in Belo Horizonte – MINASIC in Itajubá – CTI, Eldorado, LSI-TEC, von Braun, … § Many other companies, e. g. : – AEGIS / SEMIKRON: Power devices – SMART / HT Micron: Back-end for memories – FREESCALE: Design center Sill Torres: Microelectronics 55

Opportunities in Brazil cont’d § Minas Gerais – Invent. Vision - Optical Systems, FPGA – Jasper - Verification – CBS (wafer production) - planned – CMinas (MEMS) - planned – Foxconn (Displays) - planned Sill Torres: Microelectronics 56

Activities at UFMG / EE Opt. MAlab § § § Laboratory for Optronics and Microtechnologies (Opt. MAlab) Located at PPGEE / UFMG Coordinator: Dr. Davies William de Lima Monteiro Adaptive Optics: wavefront aberration, components and systems Microelectronics: Analog Integrated-Circuit design custom pixels, image sensors and optical position-sensitive devices (PSDs) § Micromachining: silicon wet processing micro-optics § Ophthalmic Optics: technology and characterization of intraocular lenses § Photovoltaics: alternative self-configurable cells Sill Torres: Microelectronics 57

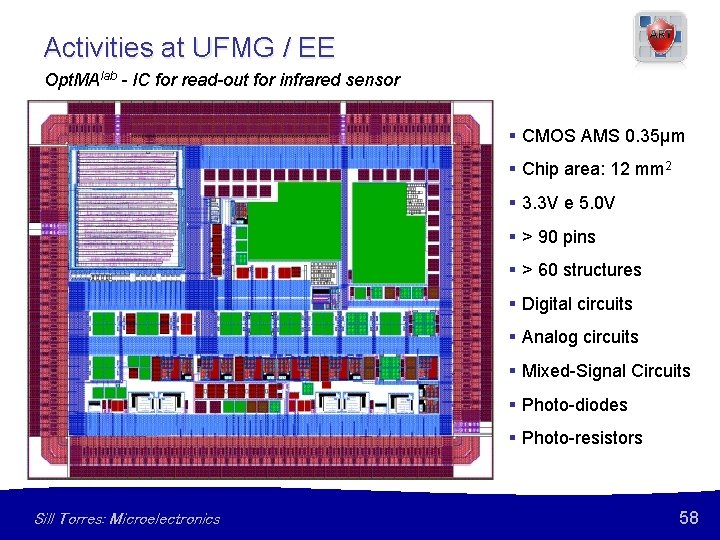

Activities at UFMG / EE Opt. MAlab - IC for read-out for infrared sensor § CMOS AMS 0. 35µm § Chip area: 12 mm 2 § 3. 3 V e 5. 0 V § > 90 pins § > 60 structures § Digital circuits § Analog circuits § Mixed-Signal Circuits § Photo-diodes § Photo-resistors Sill Torres: Microelectronics 58

Activities at UFMG / EE Opt. MA - ART § Asic-Reliabi. Tiy (Opt. MAlab / ART) § Extension of Opt. MAlab at PPGEE/UFMG § Coordinator: Frank Sill Torres § Dedicated to reliability in micro- and nanoelectronics applications § Activities in the field of – Design for Reliability – Low Leakage / Low Power Chip Design – Development of CAD tools extensions – Robust Nanoelectronics § More information: www. asic-reliabity. com Sill Torres: Microelectronics 59

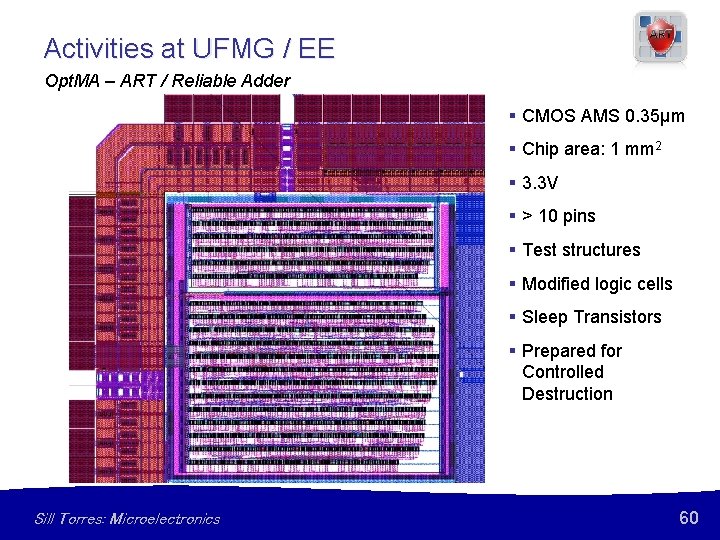

Activities at UFMG / EE Opt. MA – ART / Reliable Adder § CMOS AMS 0. 35µm § Chip area: 1 mm 2 § 3. 3 V § > 10 pins § Test structures § Modified logic cells § Sleep Transistors § Prepared for Controlled Destruction Sill Torres: Microelectronics 60

LSI – Laboratório de Sistemas Inteligentes § Projeto: Desenvolvimento de um Sistema de Determinação de Atitude com Tolerância a Falhas para Satélites de Baixa Órbita. § Projeto Financiado pela AEB – Programa UNIESPAÇO – Colaboradores: INPE, UFABC, Opt. Ma § Síntese do Projeto: – – O que é Atitude Satélites que operam em Baixa Órbita Terrestre O ambiente hostil a que os CIs são colocados em funcionamento. Condições limitadoras: alta precisão de apontamento, baixa potência, baixo peso, baixo custo e confiabilidade 99, 99999% durante a missão. Sill Torres: Microelectronics 61

LSI – Laboratório de Sistemas Inteligentes Sill Torres: Microelectronics 62

LSI – Laboratório de Sistemas Inteligentes § Áreas de atuação da Microeletrônica: – Entender e modelar o efeito de falhas em CIs. § Diversidade de Dispositivos § Diversidade de Arquiteturas § Diversidade de Ambientes e Situações – Emular o efeito de falhas em CIs. – Mitigar o efeito das falhas dos CIs nos Sistemas que os compreendem Técnicas de Tolerância a Falhas Sill Torres: Microelectronics 63

LSI – Laboratório de Sistemas Inteligentes § Equipe atual: – Fernando Esquírio Torres (bolsista de mestrado CPDEE) – Thalles Hermes R. Gomes (bolsista PET-EE) – Wagno Alves Bragança J. (bolsista PET-EE) – Bruno Henrique S. Guimarães (voluntário IC-EE) –. . . ? ? § Contato: – Prof. Ricardo de Oliveira Duarte Email: ricardoduarte@ufmg. br Sala pessoal: 2521 Sala do LSI: 2515 Sill Torres: Microelectronics 64

LSI – Laboratório de Sistemas Inteligentes Sill Torres: Microelectronics 65

Thank you! franksill@ufmg. br ART Opt. MAlab / ART www. asic-reliability. com Sill Torres: Microelectronics 66

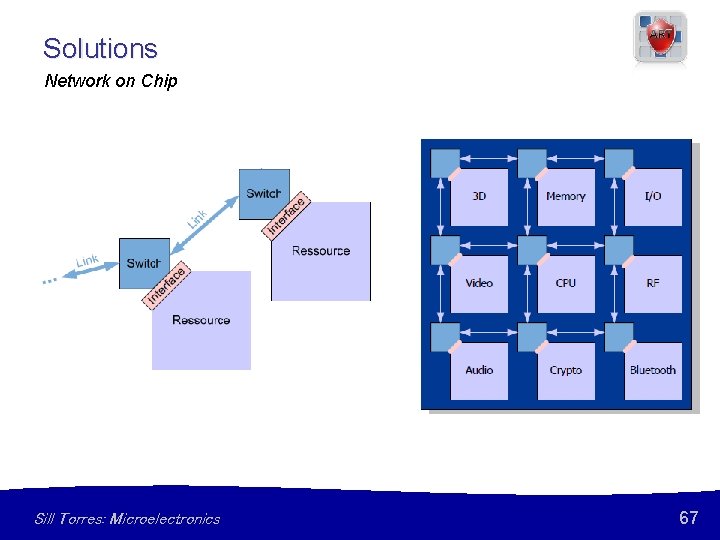

Solutions Network on Chip Sill Torres: Microelectronics 67

- Slides: 67