MICROCONTROLLERS 8051 WHAT IS A MICROCONTROLLER All of

- Slides: 85

MICROCONTROLLERS 8051

WHAT IS A MICROCONTROLLER? • All of the components needed for a controller were built right onto one chip. • A microcontroller is a highly integrated chip which includes, on one chip, all or most of the parts needed for a controller. • The microcontroller could be called a "onechip solution".

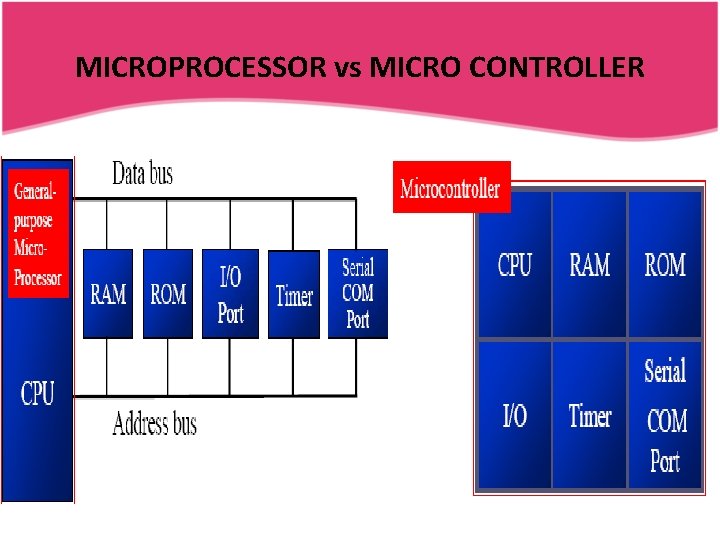

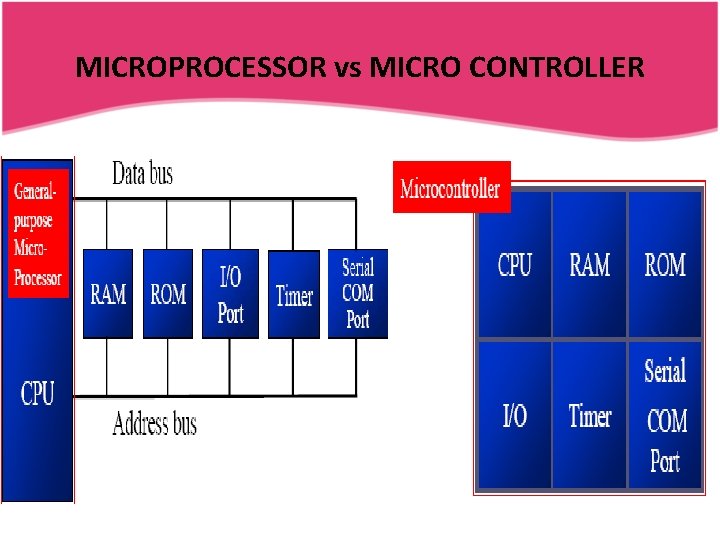

MICROPROCESSOR vs MICRO CONTROLLER

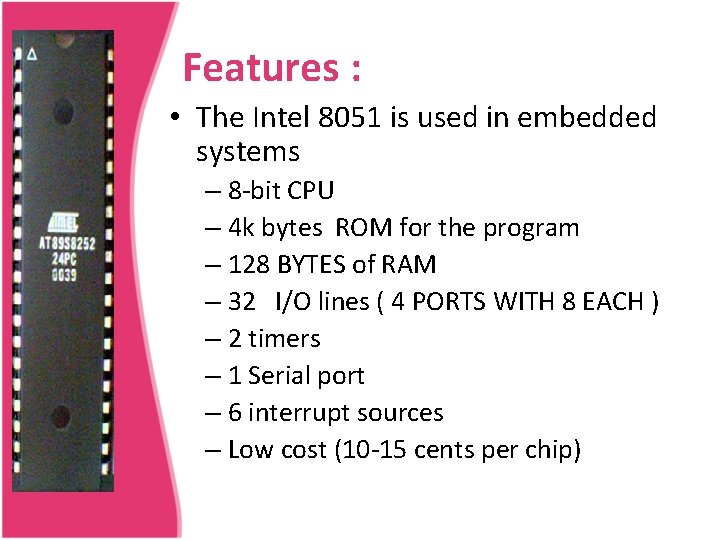

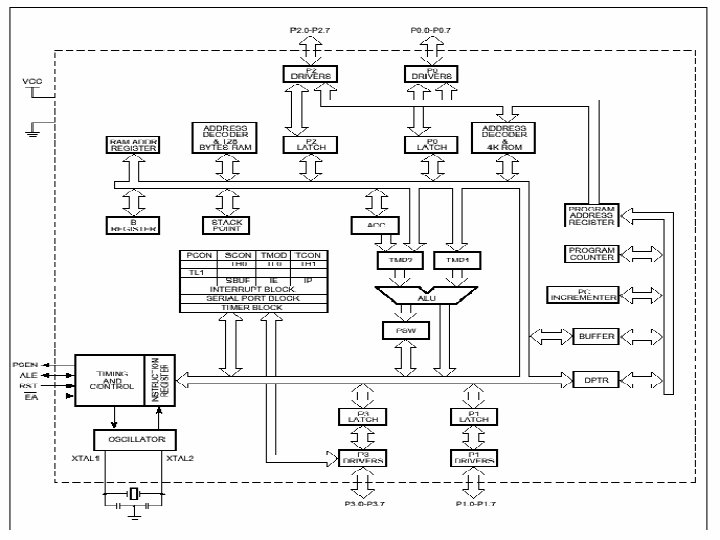

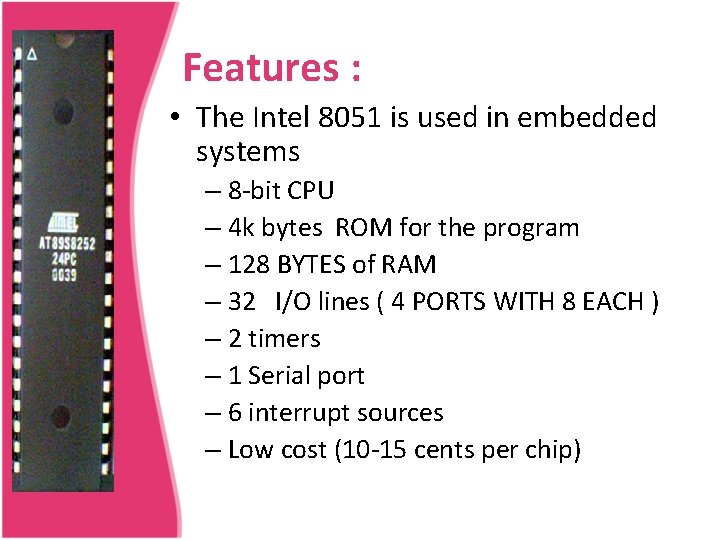

Features : • The Intel 8051 is used in embedded systems – 8 -bit CPU – 4 k bytes ROM for the program – 128 BYTES of RAM – 32 I/O lines ( 4 PORTS WITH 8 EACH ) – 2 timers – 1 Serial port – 6 interrupt sources – Low cost (10 -15 cents per chip)

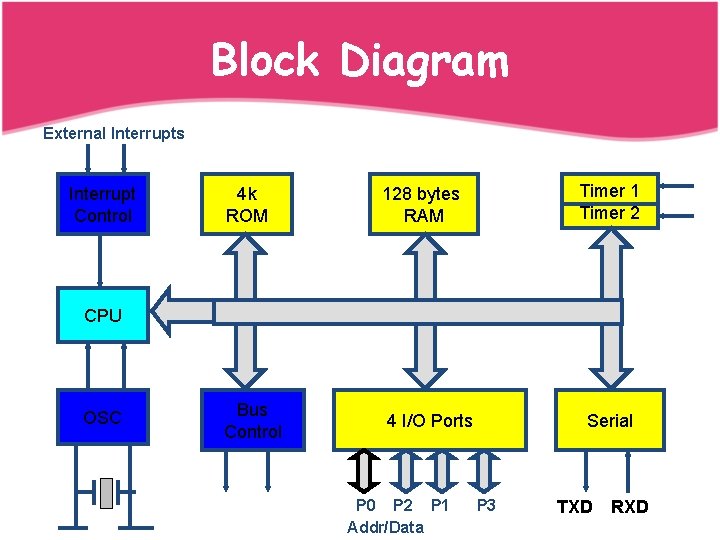

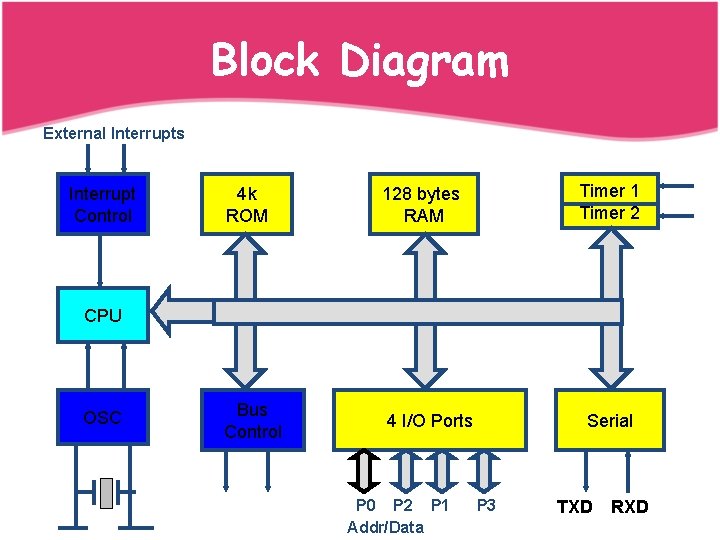

Block Diagram External Interrupts Interrupt Control 4 k ROM 128 bytes RAM Bus Control 4 I/O Ports Timer 1 Timer 2 CPU OSC P 0 P 2 P 1 Addr/Data Serial P 3 TXD RXD

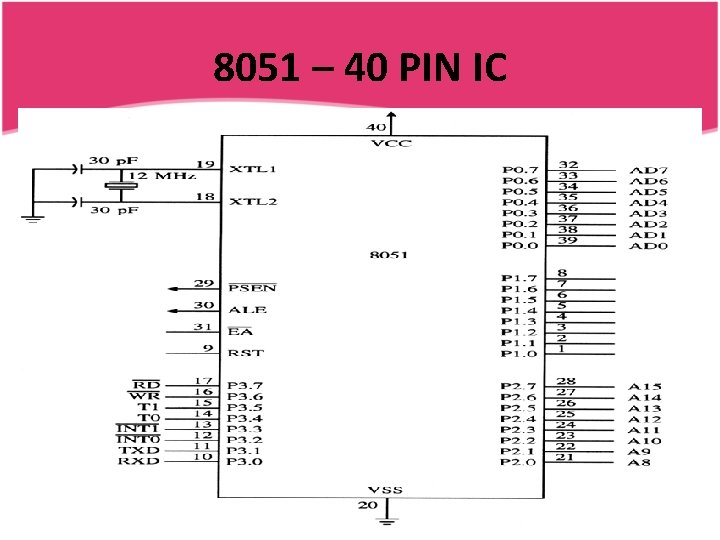

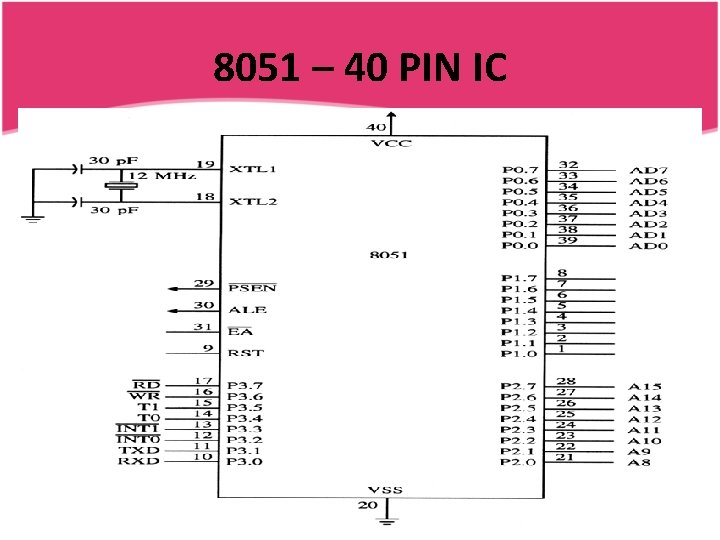

8051 – PIN DIAGRAM

8051 – 40 PIN IC

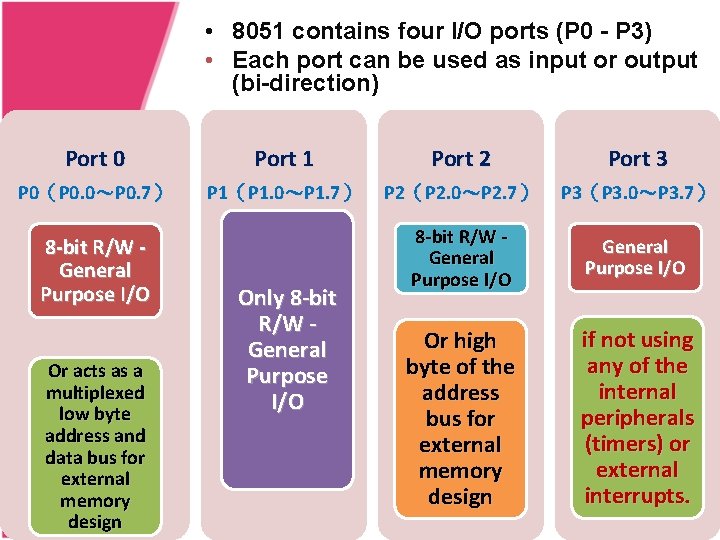

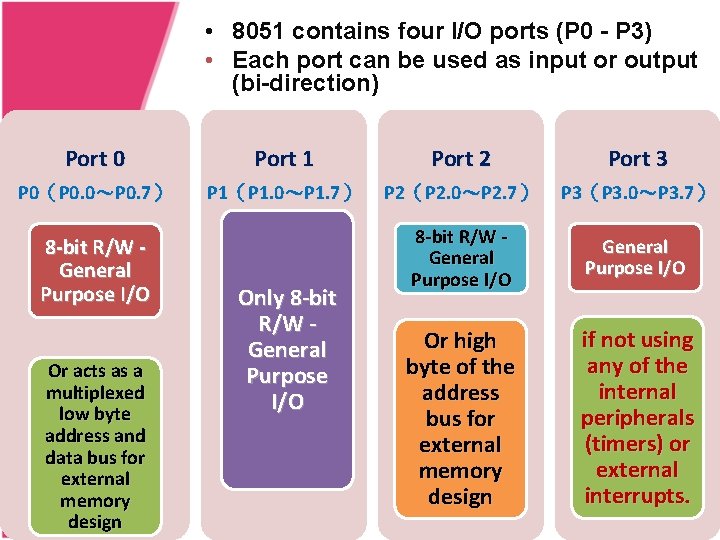

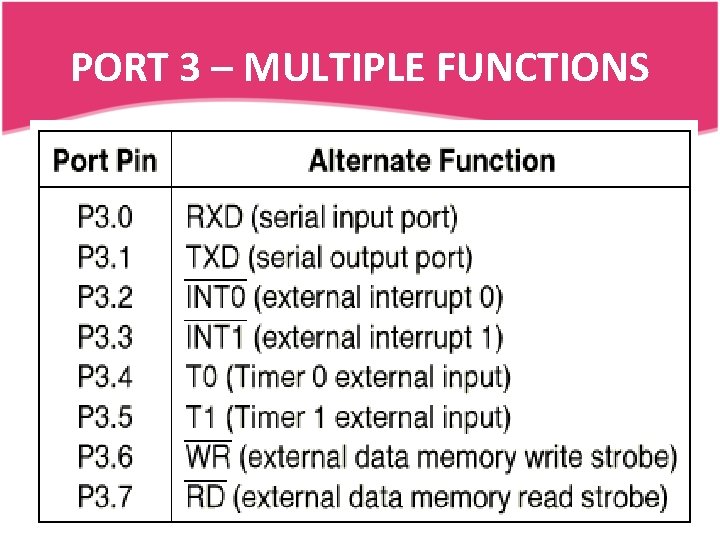

• 8051 contains four I/O ports (P 0 - P 3) • Each port can be used as input or output (bi-direction) Port 0 Port 1 Port 2 Port 3 P 0(P 0. 0~P 0. 7) P 1(P 1. 0~P 1. 7) P 2(P 2. 0~P 2. 7) P 3(P 3. 0~P 3. 7) 8 -bit R/W General Purpose I/O Or high byte of the address bus for external memory design if not using any of the internal peripherals (timers) or external interrupts. 8 -bit R/W General Purpose I/O Or acts as a multiplexed low byte address and data bus for external memory design Only 8 -bit R/W General Purpose I/O

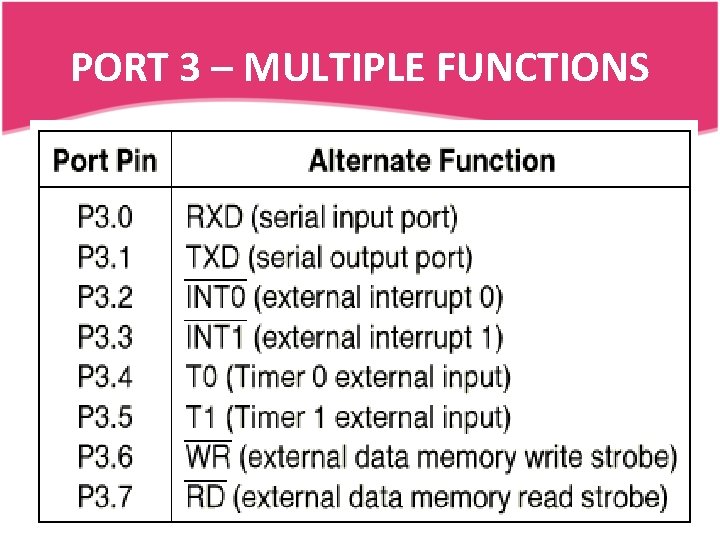

PORT 3 – MULTIPLE FUNCTIONS

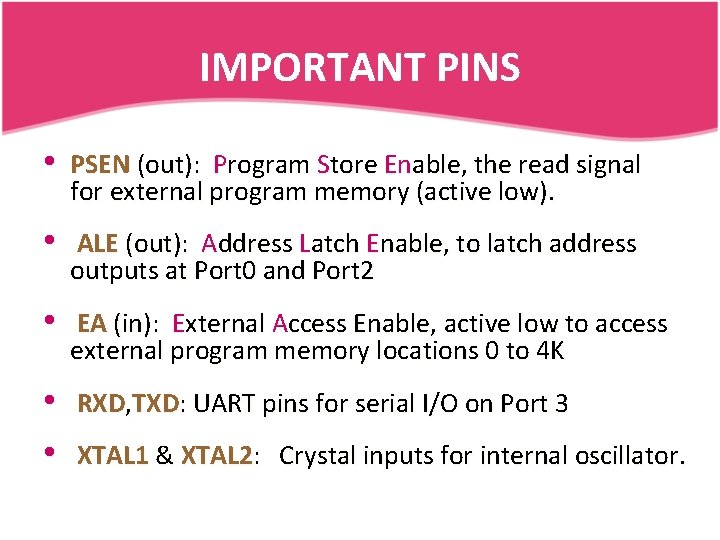

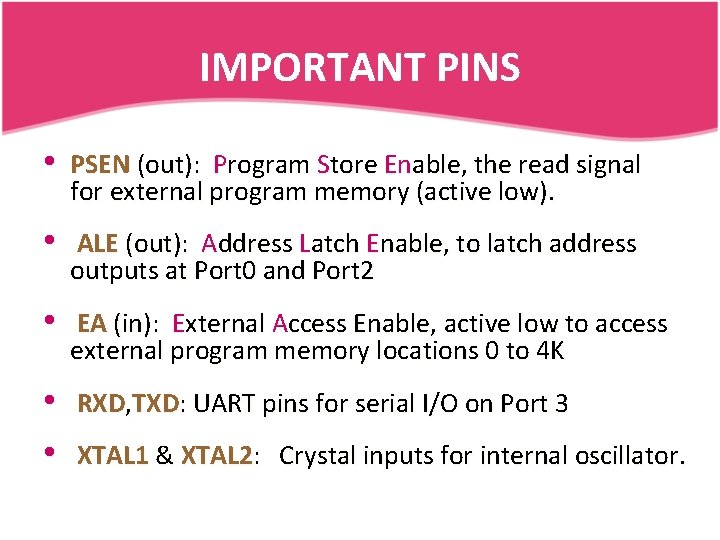

IMPORTANT PINS • PSEN (out): Program Store Enable, the read signal for external program memory (active low). • ALE (out): Address Latch Enable, to latch address outputs at Port 0 and Port 2 • EA (in): External Access Enable, active low to access external program memory locations 0 to 4 K • • RXD, TXD: UART pins for serial I/O on Port 3 XTAL 1 & XTAL 2: Crystal inputs for internal oscillator.

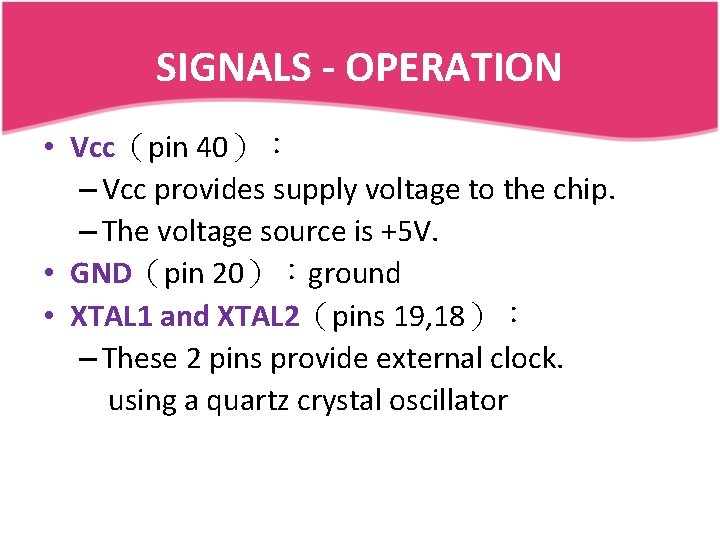

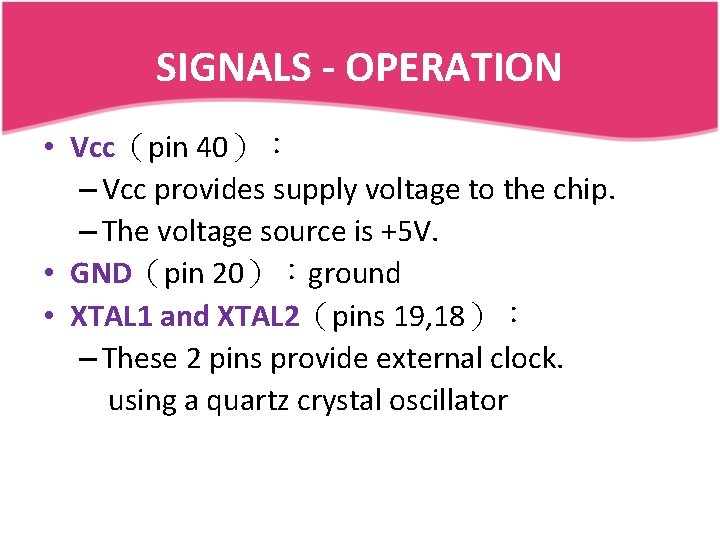

SIGNALS - OPERATION • Vcc(pin 40): – Vcc provides supply voltage to the chip. – The voltage source is +5 V. • GND(pin 20):ground • XTAL 1 and XTAL 2(pins 19, 18): – These 2 pins provide external clock. using a quartz crystal oscillator

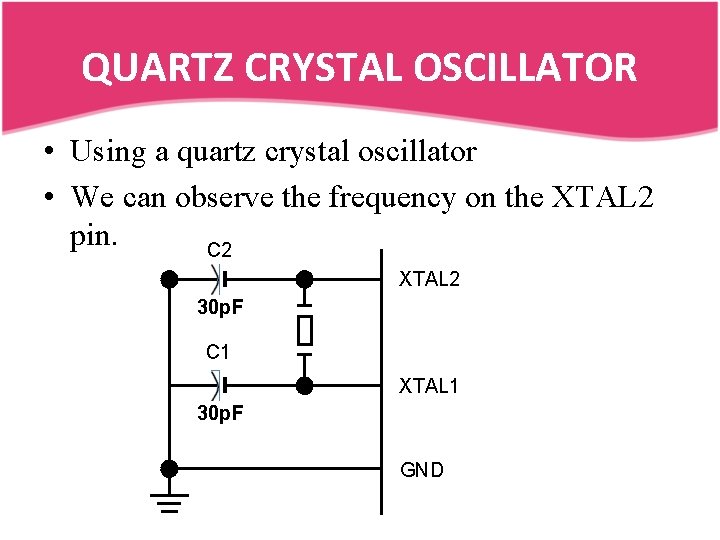

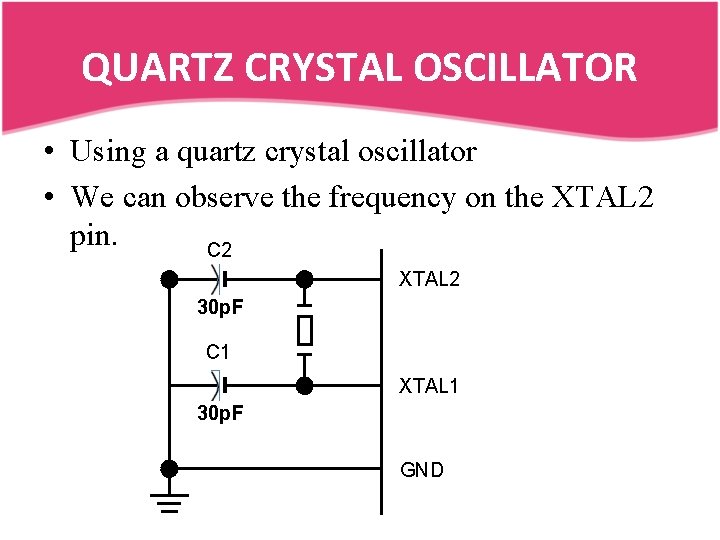

QUARTZ CRYSTAL OSCILLATOR • Using a quartz crystal oscillator • We can observe the frequency on the XTAL 2 pin. C 2 XTAL 2 30 p. F C 1 XTAL 1 30 p. F GND

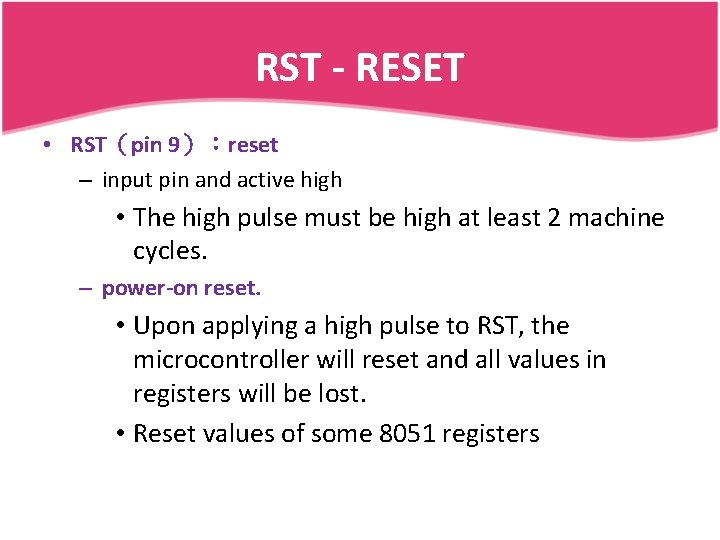

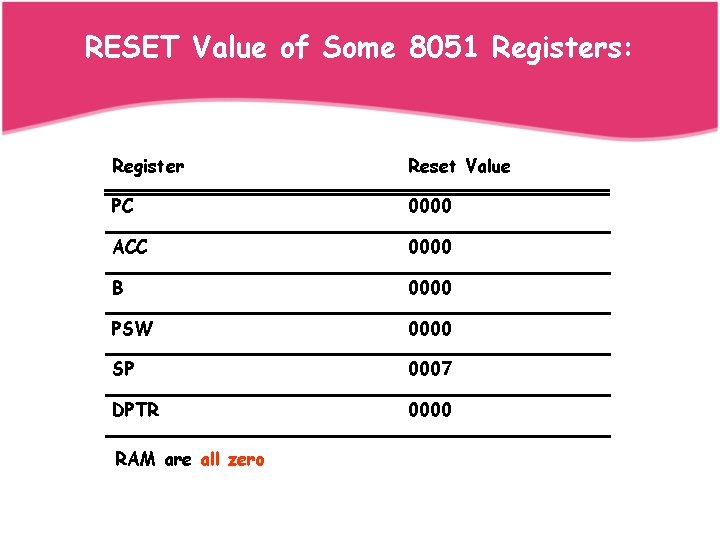

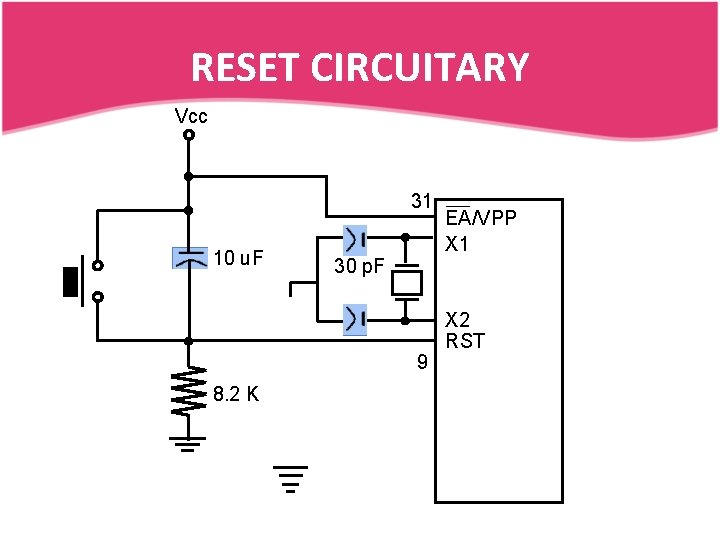

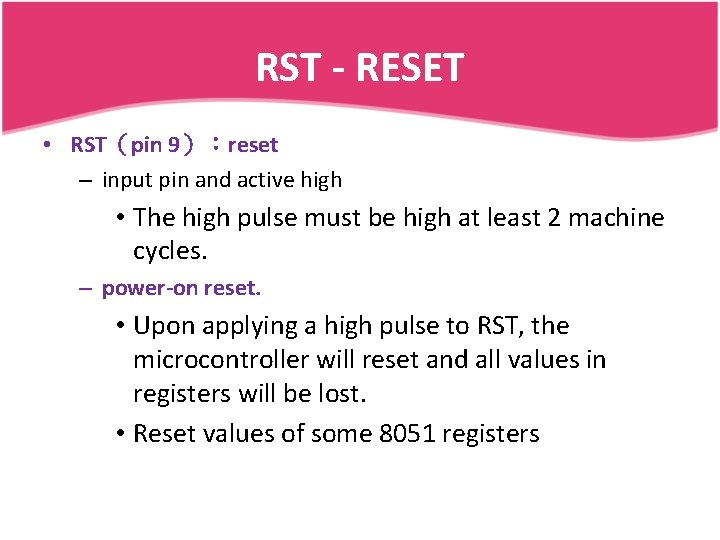

RST - RESET • RST(pin 9):reset – input pin and active high • The high pulse must be high at least 2 machine cycles. – power-on reset. • Upon applying a high pulse to RST, the microcontroller will reset and all values in registers will be lost. • Reset values of some 8051 registers

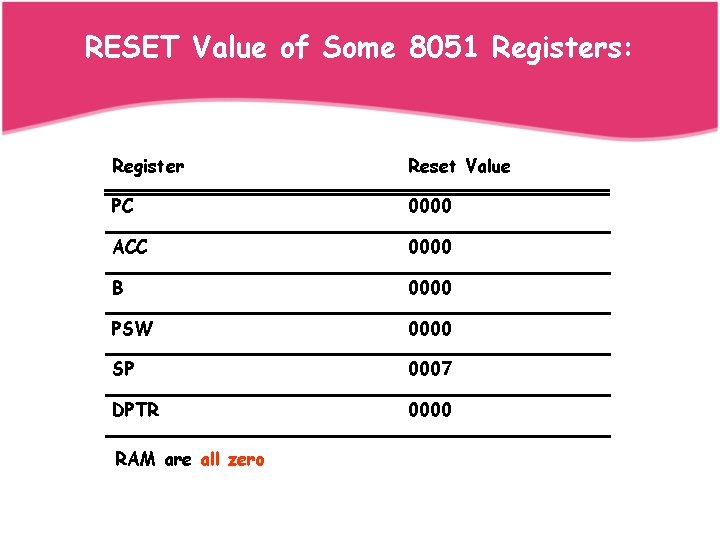

RESET Value of Some 8051 Registers: Register Reset Value PC 0000 ACC 0000 B 0000 PSW 0000 SP 0007 DPTR 0000 RAM are all zero

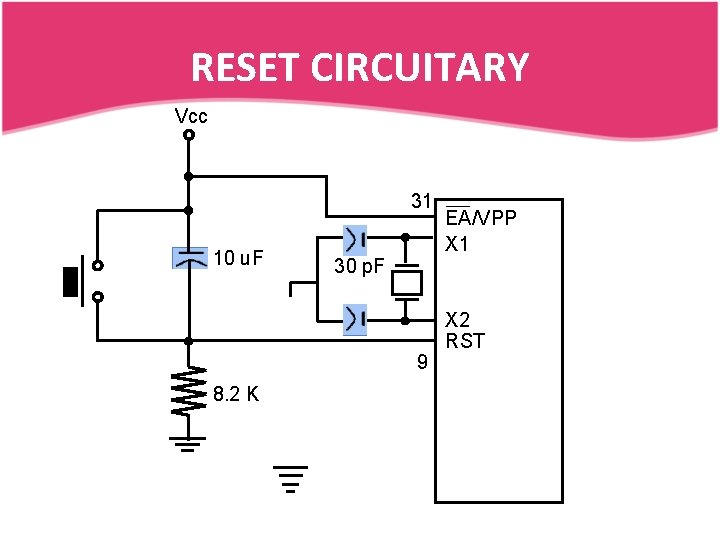

RESET CIRCUITARY Vcc 31 10 u. F 30 p. F 9 8. 2 K EA/VPP X 1 X 2 RST

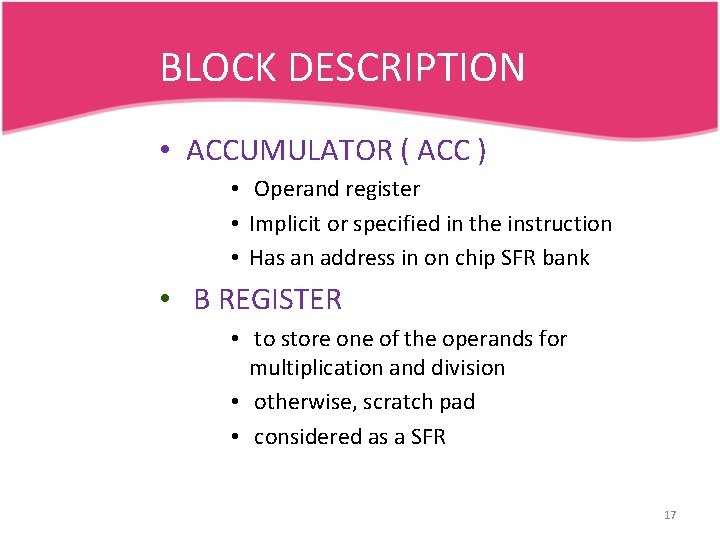

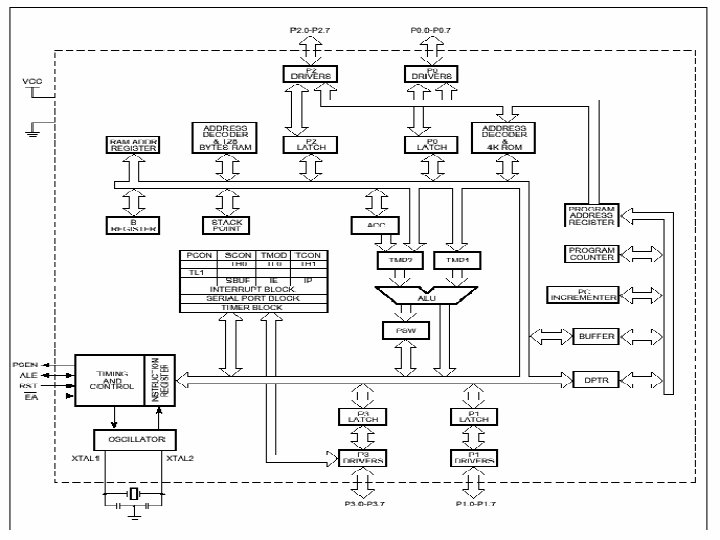

BLOCK DESCRIPTION • ACCUMULATOR ( ACC ) • Operand register • Implicit or specified in the instruction • Has an address in on chip SFR bank • B REGISTER • to store one of the operands for multiplication and division • otherwise, scratch pad • considered as a SFR 17

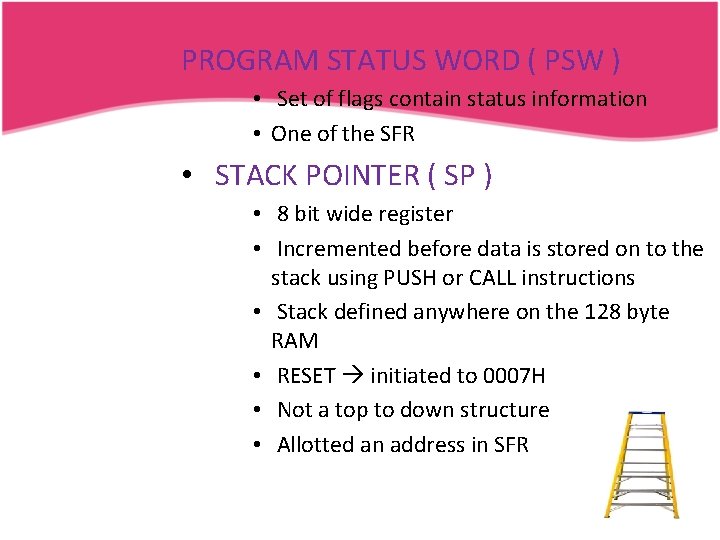

PROGRAM STATUS WORD ( PSW ) • Set of flags contain status information • One of the SFR • STACK POINTER ( SP ) • 8 bit wide register • Incremented before data is stored on to the stack using PUSH or CALL instructions • Stack defined anywhere on the 128 byte RAM • RESET initiated to 0007 H • Not a top to down structure • Allotted an address in SFR 18

• DATA POINTER ( DPTR ) • • 16 bit register contains DPH and DPL Pointer to external RAM address DPH and DPL allotted separate addresses in SFR bank • PORT 0 TO 3 LATCHES & DRIVERS • • Each i/o port allotted a latch and a driver Latches allotted address in SFR User can communicate via these ports P 0, P 1, P 2, P 3 19

• SERIAL DATA BUFFER • • • internally had TWO independent registers TRANSMIT buffer parallel in serial out ( PISO ) RECEIVE buffer serial in parallel out (SIPO) identified by SBUF and allotted an address in SFR byte written to SBUF initiates serial TX byte read from SBUF reads serially received data • TIMER REGISTERS • for Timer 0 ( 16 bit register – TL 0 & TH 0 ) • for Timer 1 ( 16 bit register – TL 1 & TH 1 ) • four addresses allotted in SFR 20

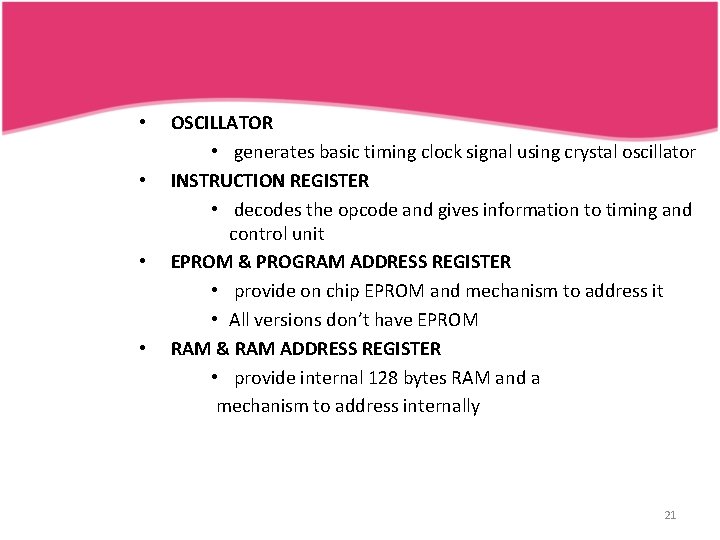

• • OSCILLATOR • generates basic timing clock signal using crystal oscillator INSTRUCTION REGISTER • decodes the opcode and gives information to timing and control unit EPROM & PROGRAM ADDRESS REGISTER • provide on chip EPROM and mechanism to address it • All versions don’t have EPROM RAM & RAM ADDRESS REGISTER • provide internal 128 bytes RAM and a mechanism to address internally 21

• ALU • Performs 8 bit arithmetic and logical operations over the operands held by TEMP 1 and TEMP 2 • User cannot access temporary registers • SFR REGISTER BANK • set of special function registers • address range : 80 H to FF H 22

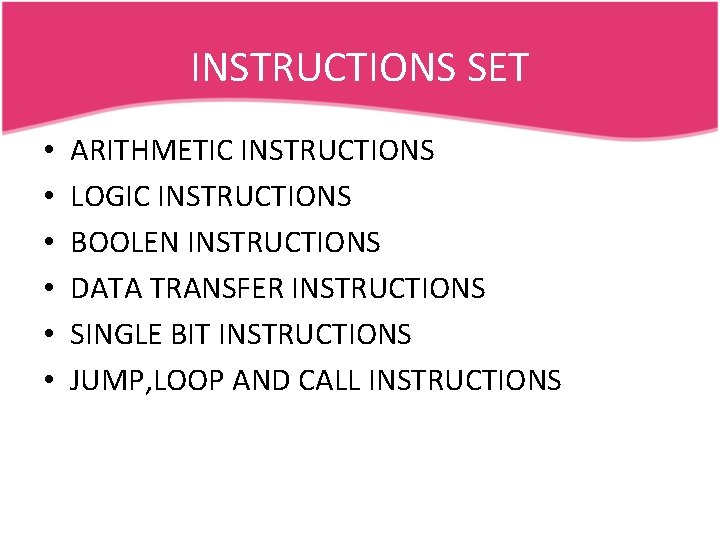

INSTRUCTIONS SET • • • ARITHMETIC INSTRUCTIONS LOGIC INSTRUCTIONS BOOLEN INSTRUCTIONS DATA TRANSFER INSTRUCTIONS SINGLE BIT INSTRUCTIONS JUMP, LOOP AND CALL INSTRUCTIONS

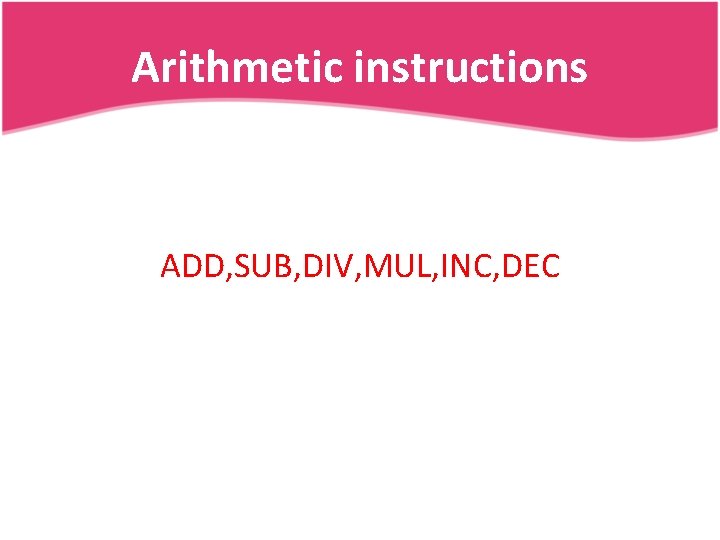

Arithmetic instructions ADD, SUB, DIV, MUL, INC, DEC

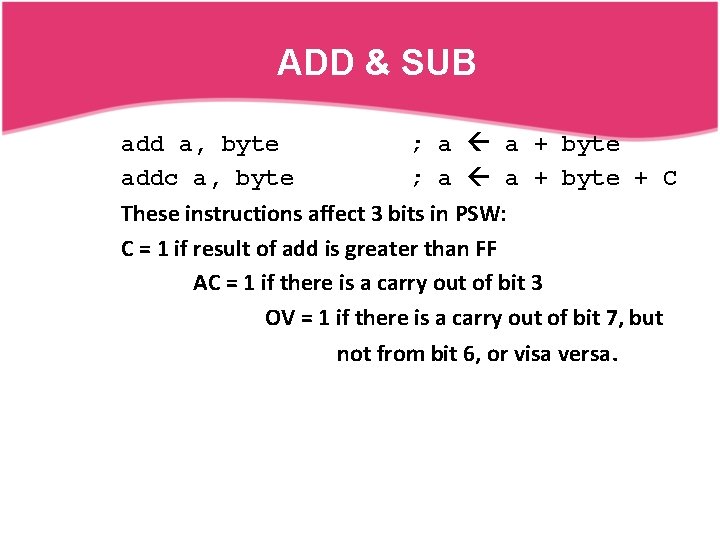

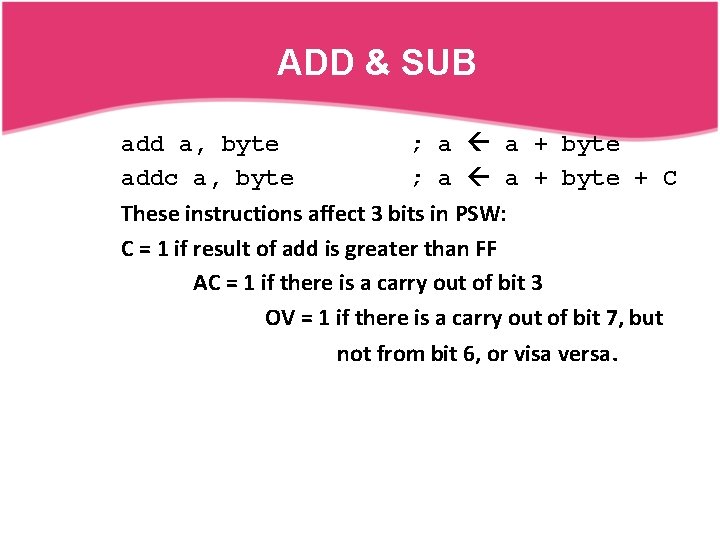

ADD & SUB add a, byte ; a a + byte addc a, byte ; a a + byte + C These instructions affect 3 bits in PSW: C = 1 if result of add is greater than FF AC = 1 if there is a carry out of bit 3 OV = 1 if there is a carry out of bit 7, but not from bit 6, or visa versa.

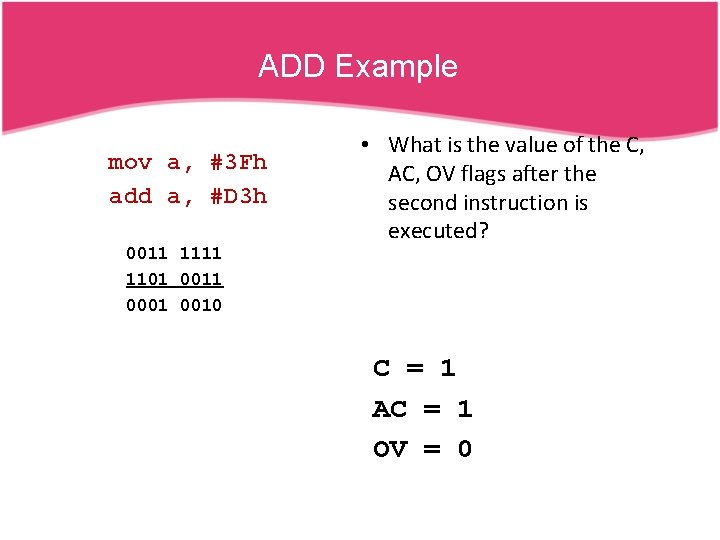

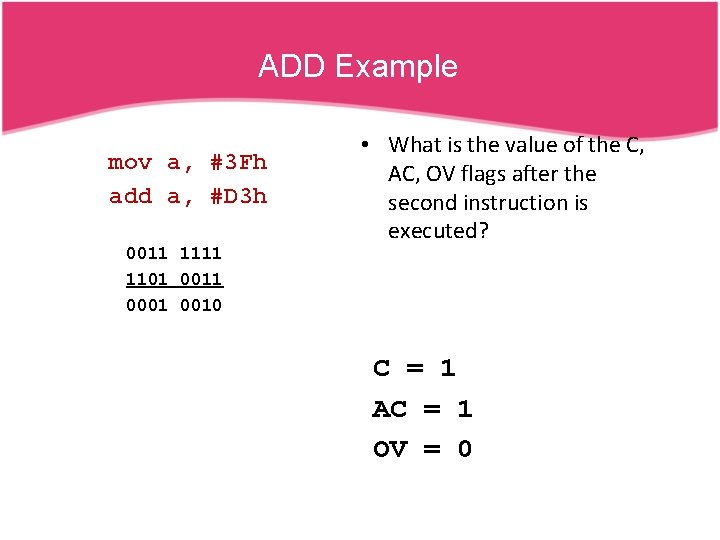

ADD Example mov a, #3 Fh add a, #D 3 h 0011 1101 0011 0001 0010 • What is the value of the C, AC, OV flags after the second instruction is executed? C = 1 AC = 1 OV = 0

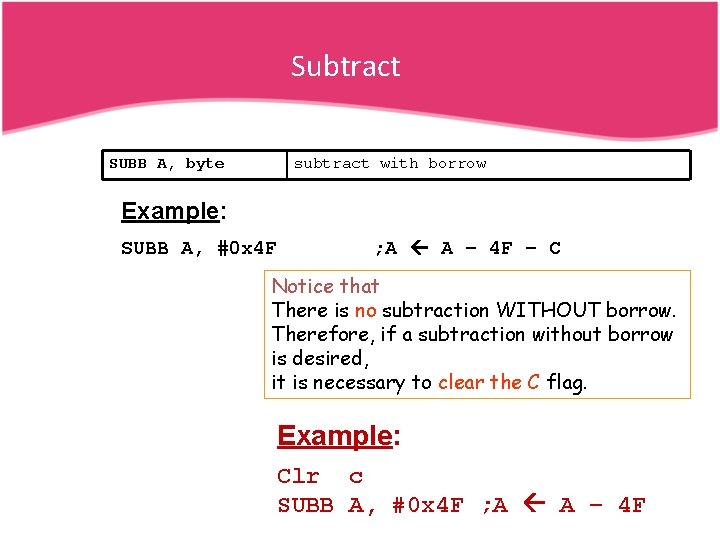

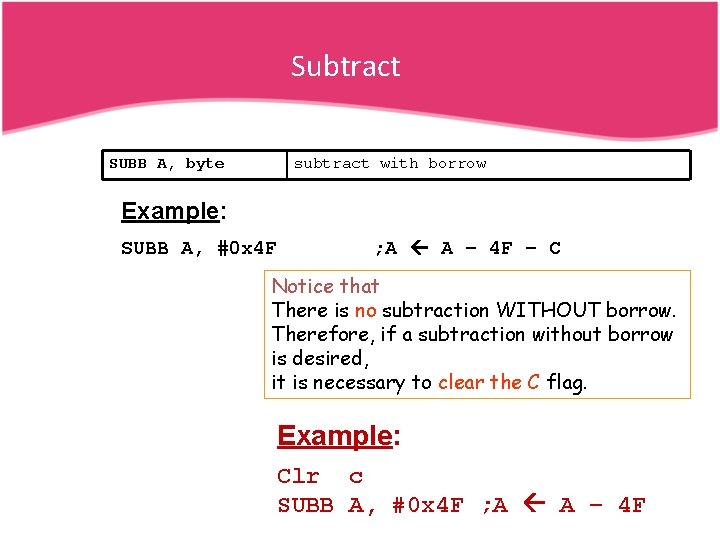

Subtract SUBB A, byte subtract with borrow Example: SUBB A, #0 x 4 F ; A A – 4 F – C Notice that There is no subtraction WITHOUT borrow. Therefore, if a subtraction without borrow is desired, it is necessary to clear the C flag. Example: Clr c SUBB A, #0 x 4 F ; A A – 4 F

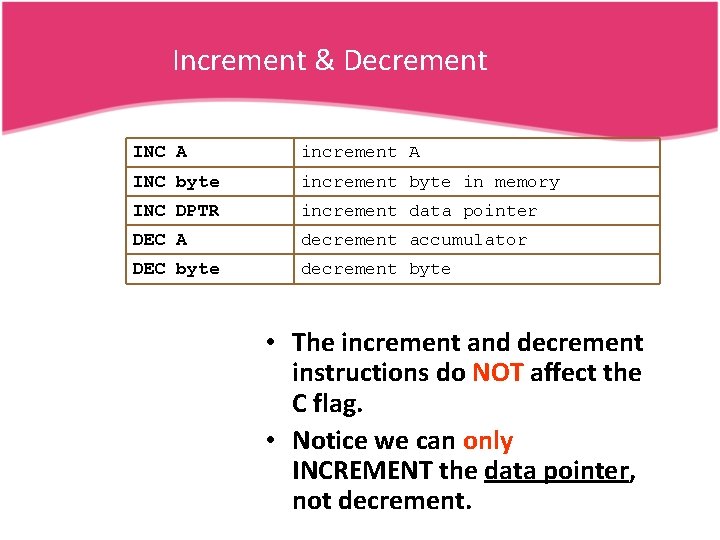

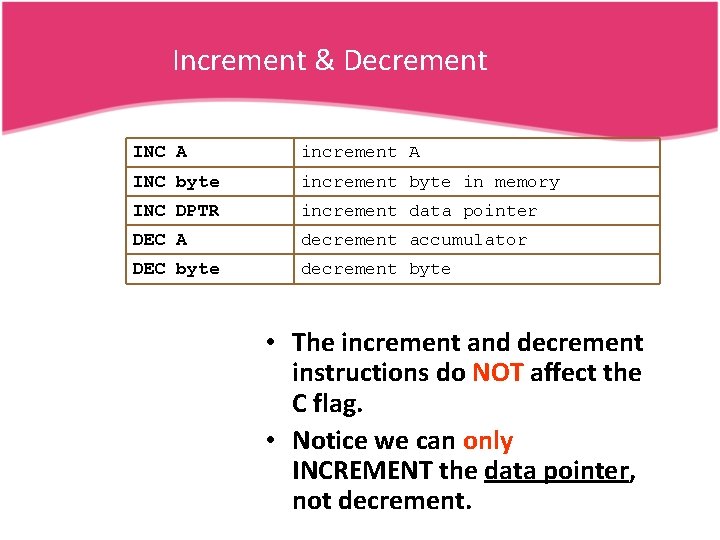

Increment & Decrement INC A increment A INC byte increment byte in memory INC DPTR increment data pointer DEC A decrement accumulator DEC byte decrement byte • The increment and decrement instructions do NOT affect the C flag. • Notice we can only INCREMENT the data pointer, not decrement.

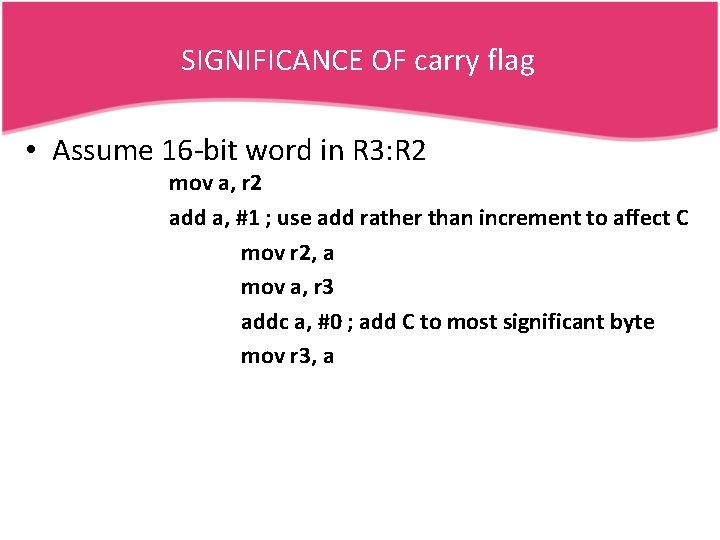

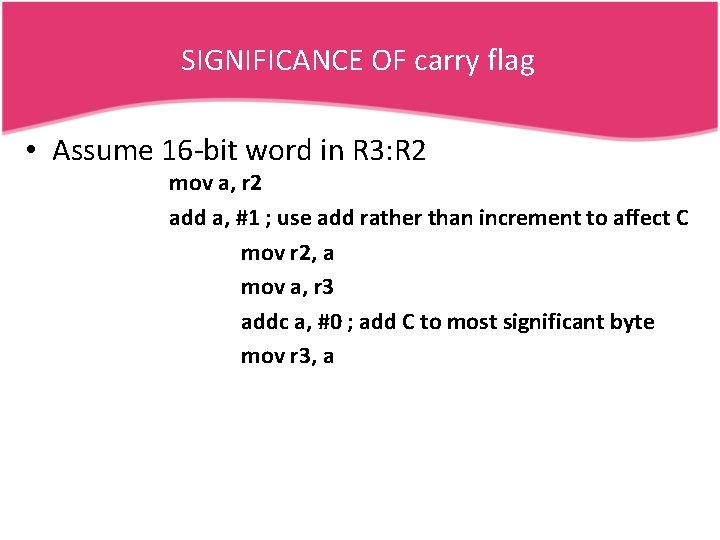

SIGNIFICANCE OF carry flag • Assume 16 -bit word in R 3: R 2 mov a, r 2 add a, #1 ; use add rather than increment to affect C mov r 2, a mov a, r 3 addc a, #0 ; add C to most significant byte mov r 3, a

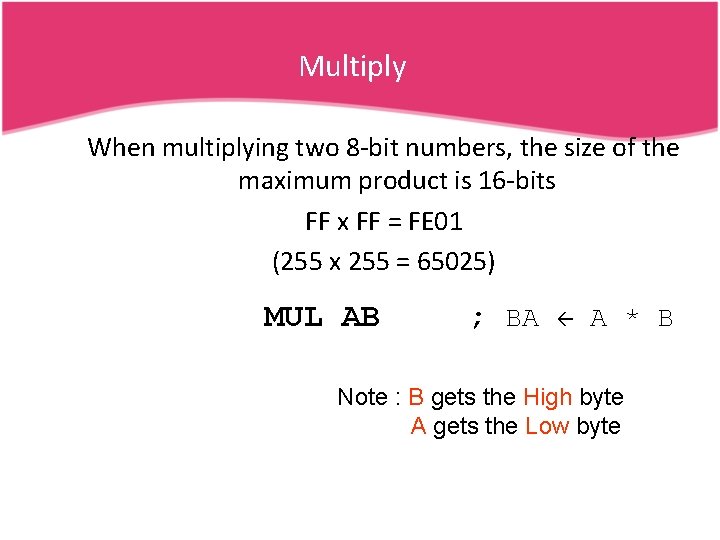

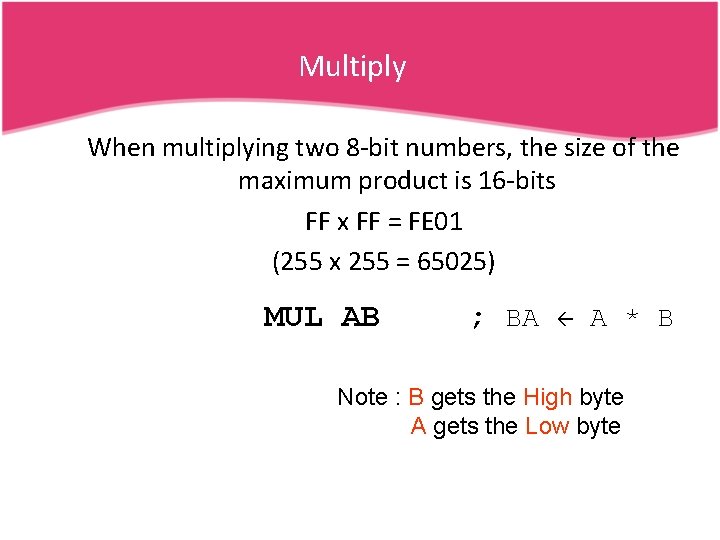

Multiply When multiplying two 8 -bit numbers, the size of the maximum product is 16 -bits FF x FF = FE 01 (255 x 255 = 65025) MUL AB ; BA A * B Note : B gets the High byte A gets the Low byte

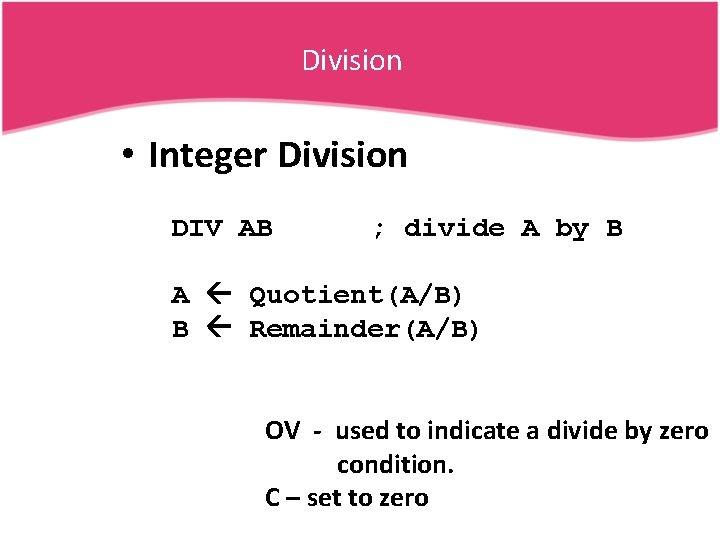

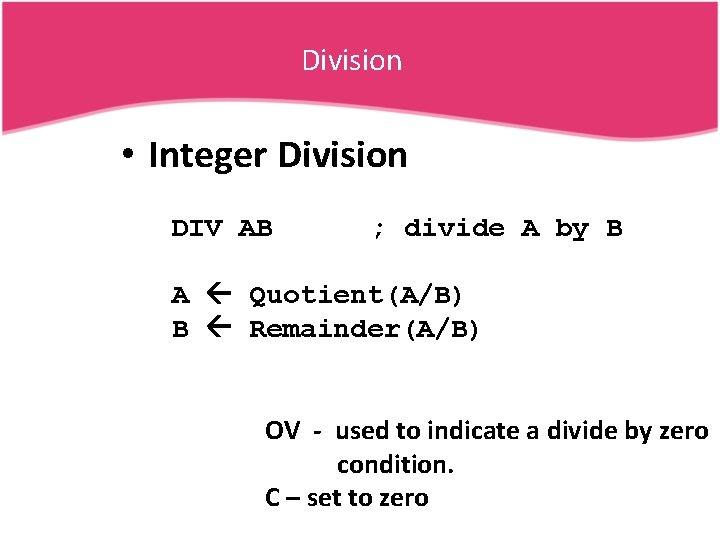

Division • Integer Division DIV AB ; divide A by B A Quotient(A/B) B Remainder(A/B) OV - used to indicate a divide by zero condition. C – set to zero

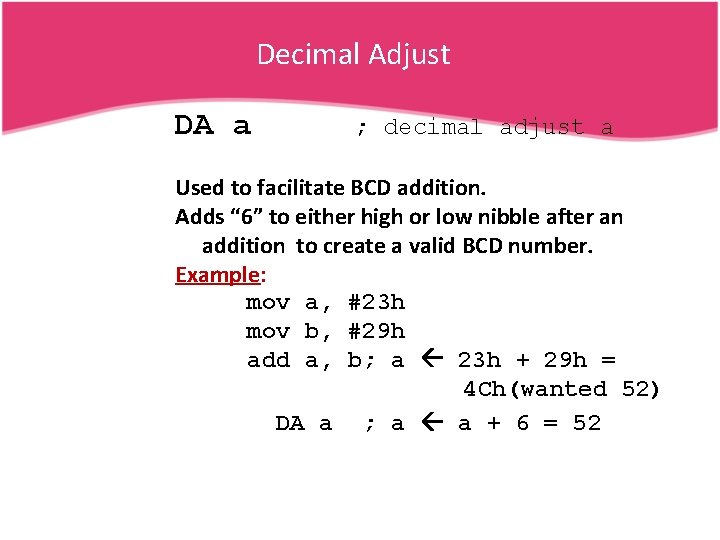

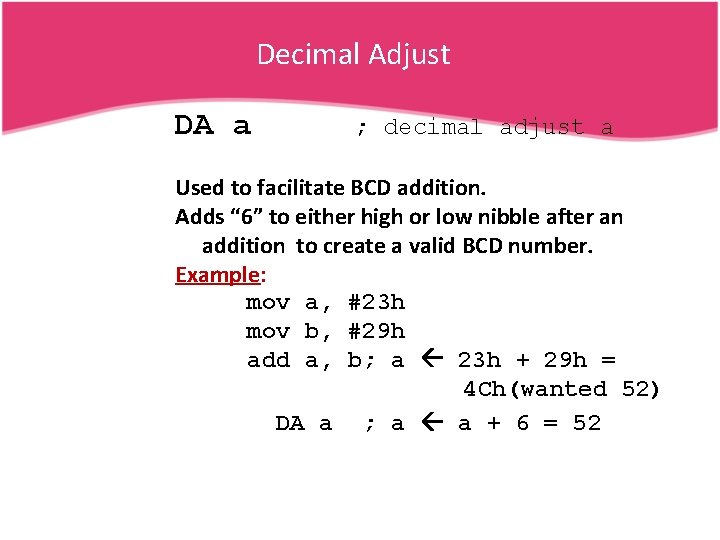

Decimal Adjust DA a ; decimal adjust a Used to facilitate BCD addition. Adds “ 6” to either high or low nibble after an addition to create a valid BCD number. Example: mov a, #23 h mov b, #29 h add a, b; a 23 h + 29 h = 4 Ch(wanted 52) DA a ; a a + 6 = 52

BOOLEAN INSTRUCTIONS CLR, CPL, SETB, AND, OR

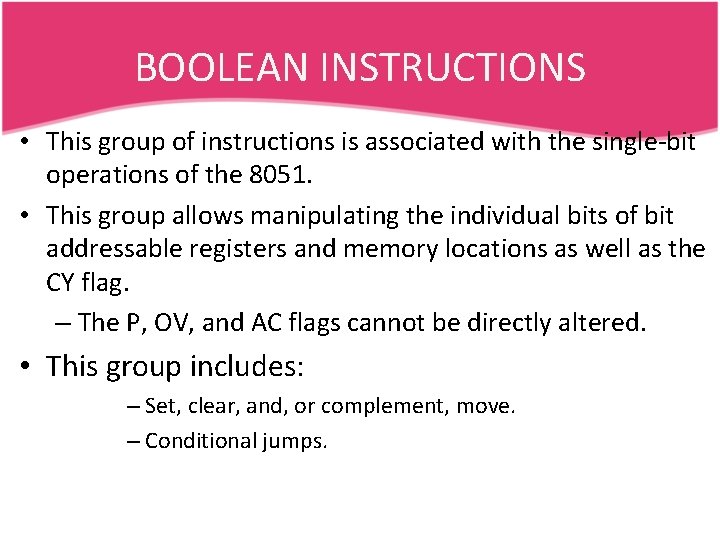

BOOLEAN INSTRUCTIONS • This group of instructions is associated with the single-bit operations of the 8051. • This group allows manipulating the individual bits of bit addressable registers and memory locations as well as the CY flag. – The P, OV, and AC flags cannot be directly altered. • This group includes: – Set, clear, and, or complement, move. – Conditional jumps.

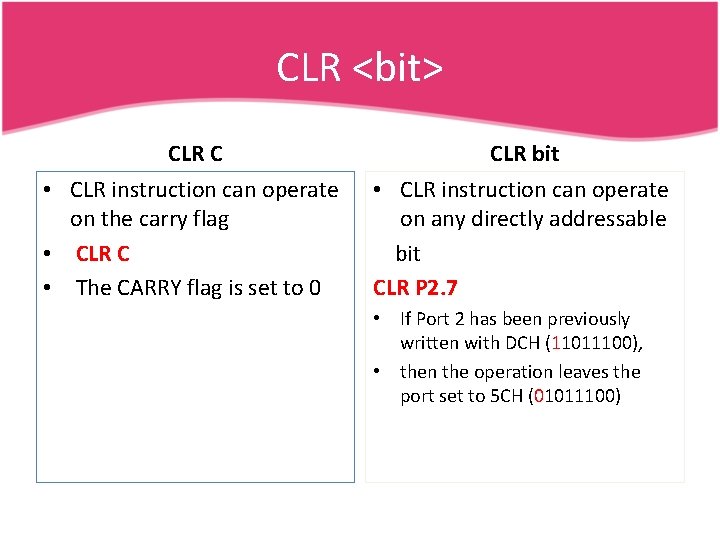

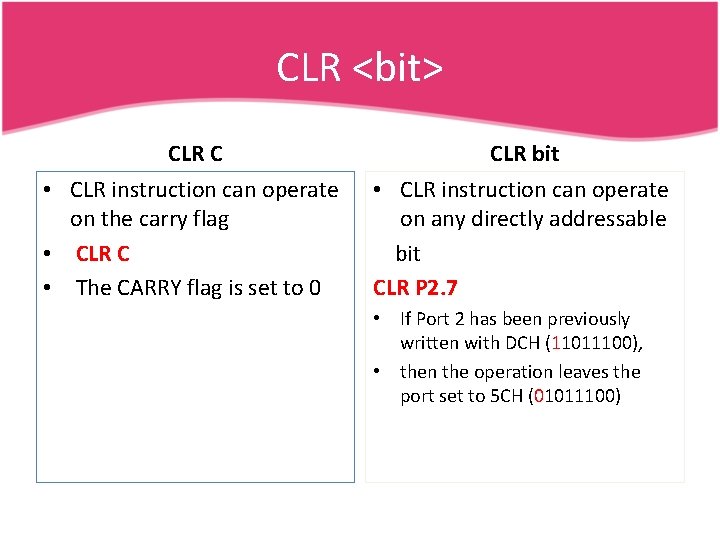

CLR <bit> CLR C CLR bit • CLR instruction can operate on the carry flag • CLR C • The CARRY flag is set to 0 • CLR instruction can operate on any directly addressable bit CLR P 2. 7 • If Port 2 has been previously written with DCH (11011100), • then the operation leaves the port set to 5 CH (01011100)

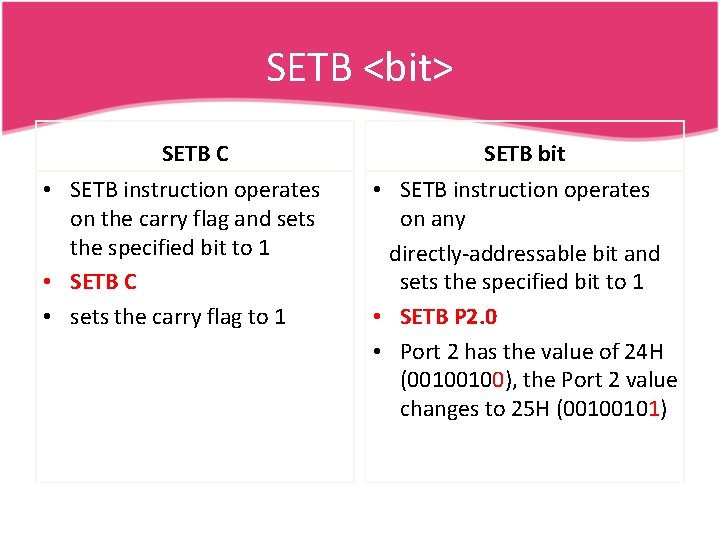

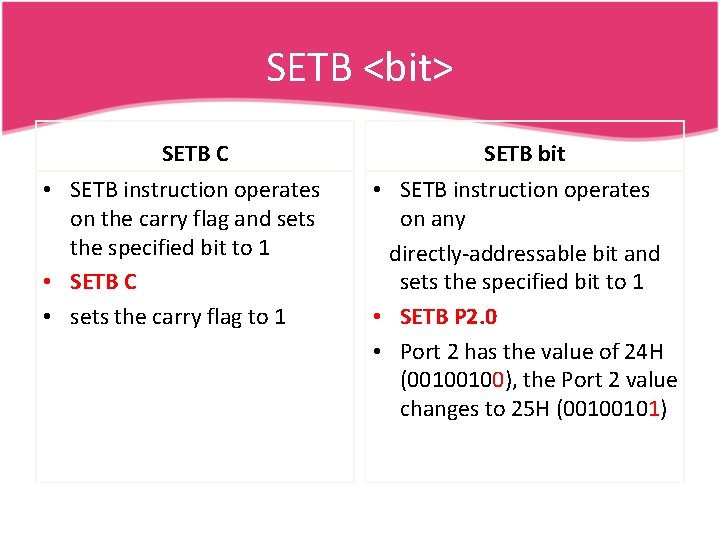

SETB <bit> SETB C • SETB instruction operates on the carry flag and sets the specified bit to 1 • SETB C • sets the carry flag to 1 SETB bit • SETB instruction operates on any directly-addressable bit and sets the specified bit to 1 • SETB P 2. 0 • Port 2 has the value of 24 H (00100100), the Port 2 value changes to 25 H (00100101)

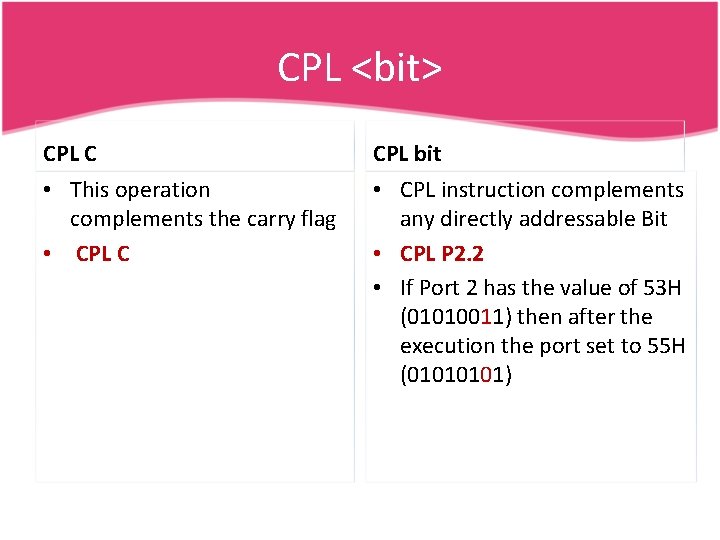

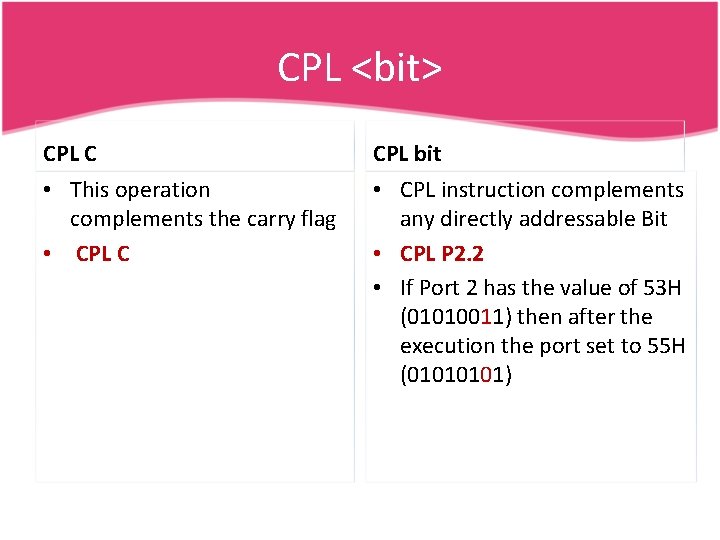

CPL <bit> CPL C CPL bit • This operation complements the carry flag • CPL C • CPL instruction complements any directly addressable Bit • CPL P 2. 2 • If Port 2 has the value of 53 H (01010011) then after the execution the port set to 55 H (0101)

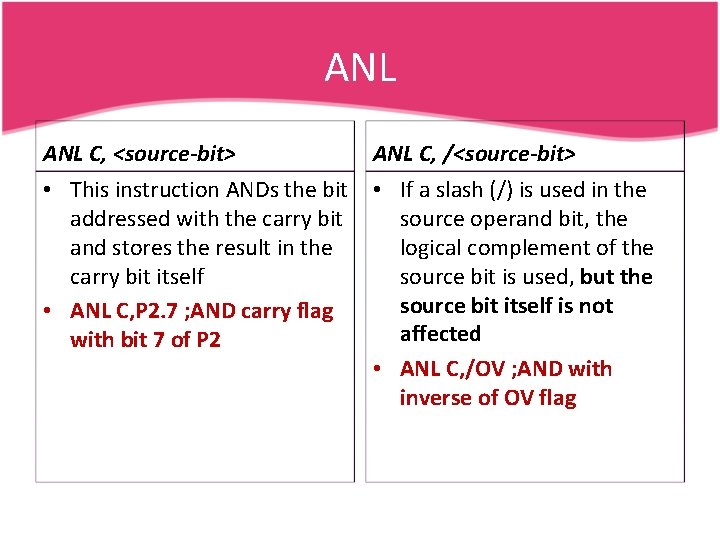

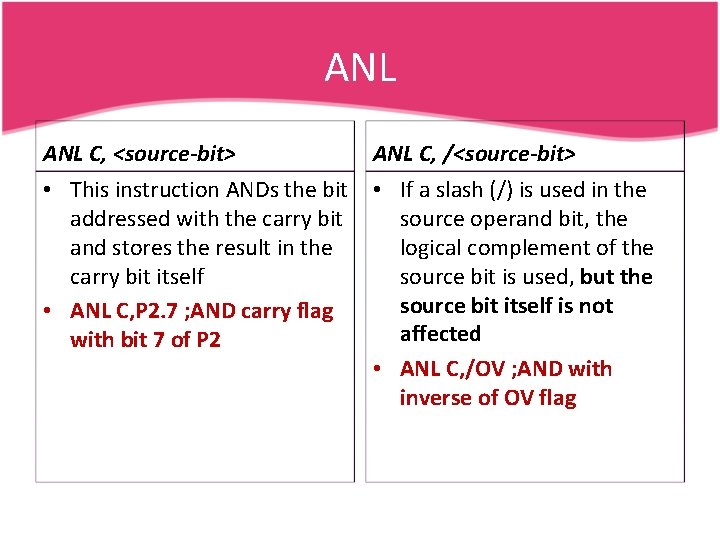

ANL C, <source-bit> ANL C, /<source-bit> • This instruction ANDs the bit • If a slash (/) is used in the addressed with the carry bit source operand bit, the and stores the result in the logical complement of the carry bit itself source bit is used, but the source bit itself is not • ANL C, P 2. 7 ; AND carry flag affected with bit 7 of P 2 • ANL C, /OV ; AND with inverse of OV flag

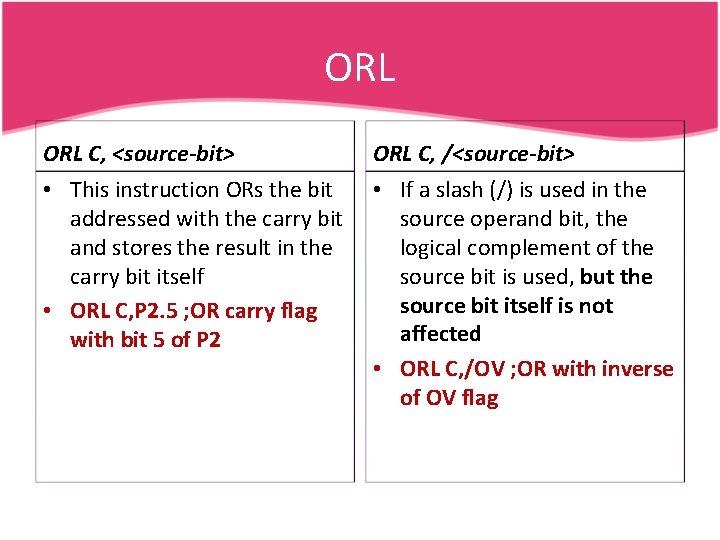

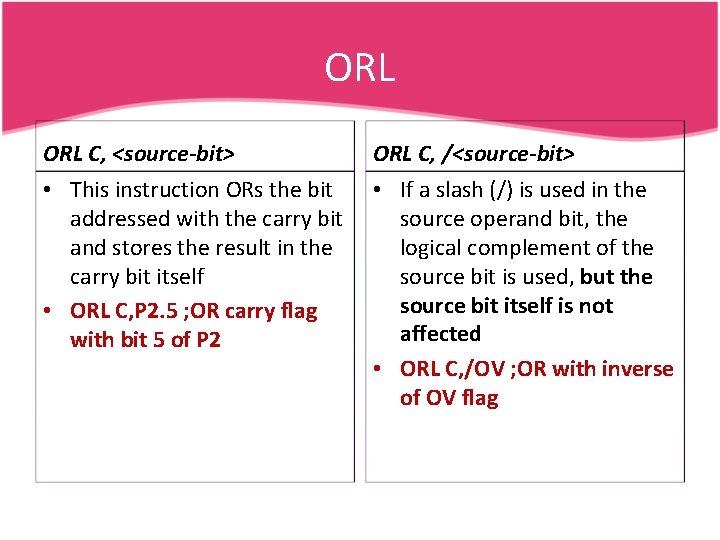

ORL C, <source-bit> ORL C, /<source-bit> • This instruction ORs the bit addressed with the carry bit and stores the result in the carry bit itself • ORL C, P 2. 5 ; OR carry flag with bit 5 of P 2 • If a slash (/) is used in the source operand bit, the logical complement of the source bit is used, but the source bit itself is not affected • ORL C, /OV ; OR with inverse of OV flag

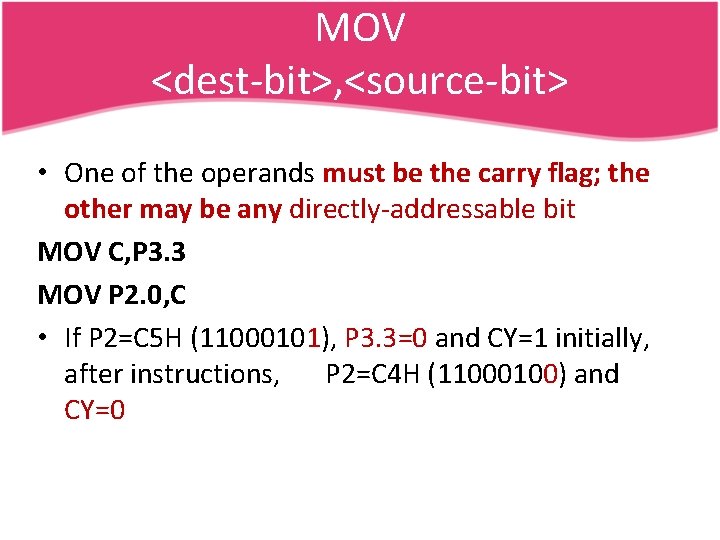

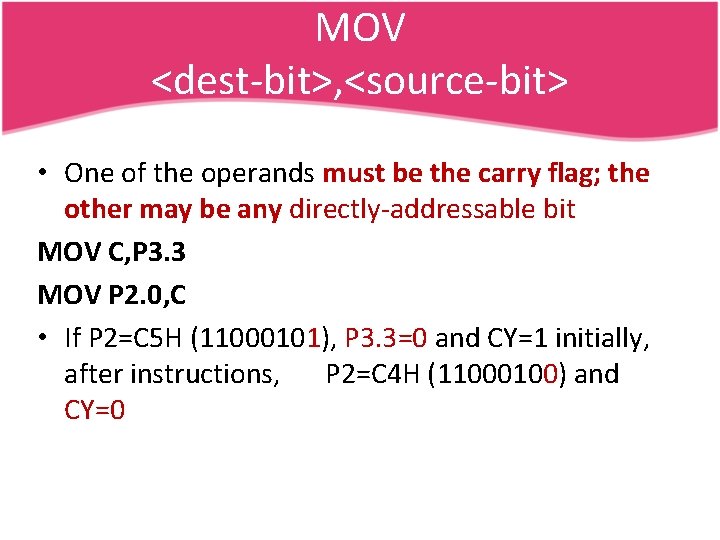

MOV <dest-bit>, <source-bit> • One of the operands must be the carry flag; the other may be any directly-addressable bit MOV C, P 3. 3 MOV P 2. 0, C • If P 2=C 5 H (11000101), P 3. 3=0 and CY=1 initially, after instructions, P 2=C 4 H (11000100) and CY=0

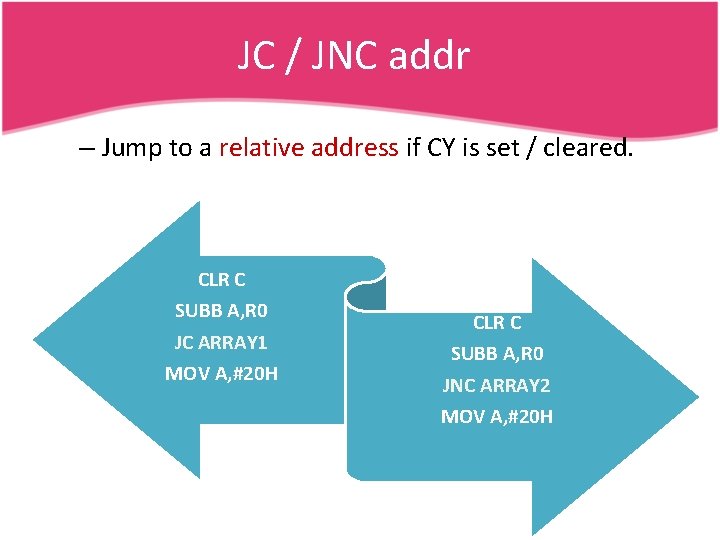

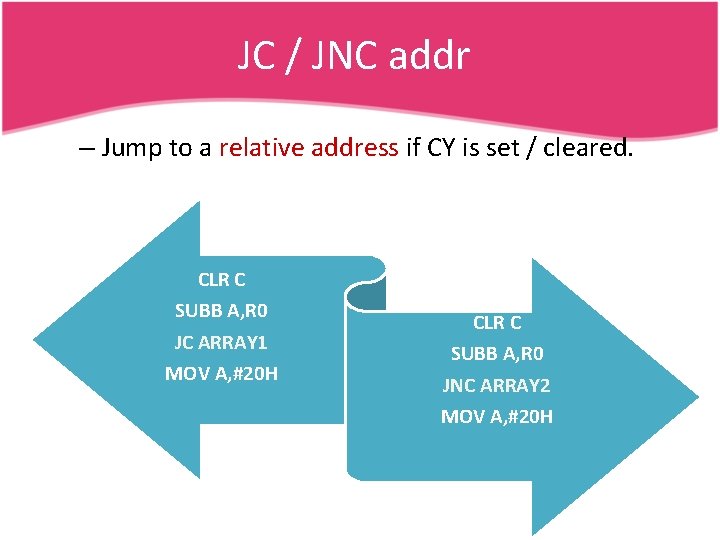

JC / JNC addr – Jump to a relative address if CY is set / cleared. CLR C SUBB A, R 0 JC ARRAY 1 MOV A, #20 H CLR C SUBB A, R 0 JNC ARRAY 2 MOV A, #20 H

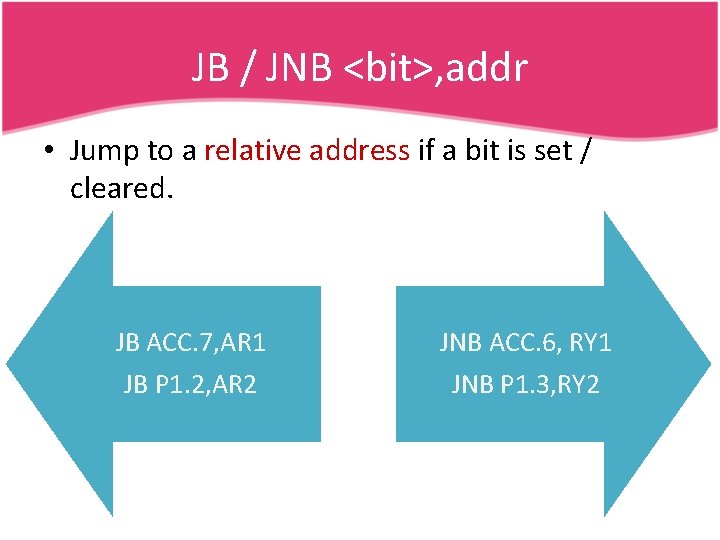

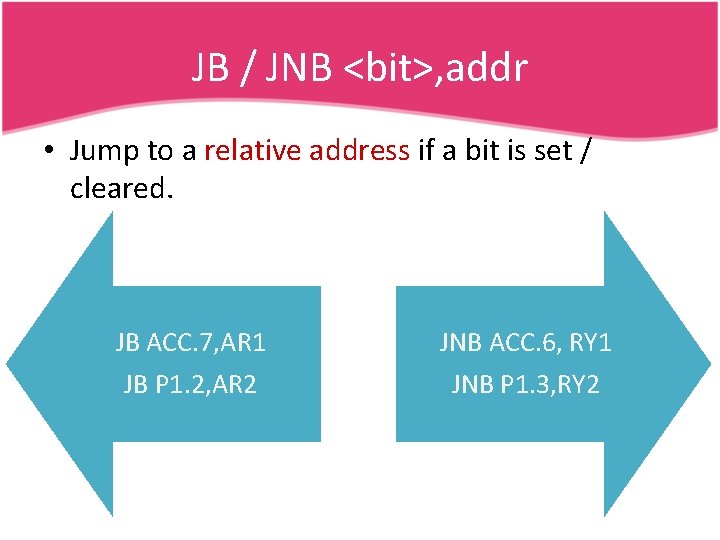

JB / JNB <bit>, addr • Jump to a relative address if a bit is set / cleared. JB ACC. 7, AR 1 JNB ACC. 6, RY 1 JB P 1. 2, AR 2 JNB P 1. 3, RY 2

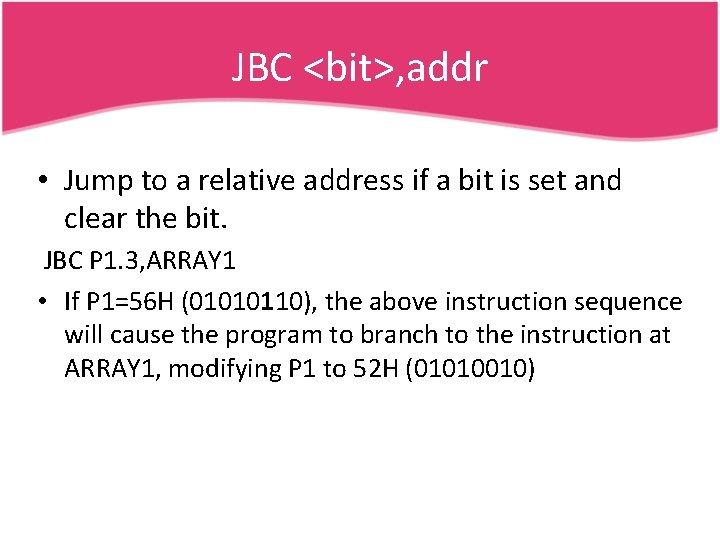

JBC <bit>, addr • Jump to a relative address if a bit is set and clear the bit. JBC P 1. 3, ARRAY 1 • If P 1=56 H (01010110), the above instruction sequence will cause the program to branch to the instruction at ARRAY 1, modifying P 1 to 52 H (01010010)

BRANCH INSTRUCTIONS CALL, JMP, RET

Branching instructions • Program branching instructions are used to control the flow of actions in a program • Some instructions provide decision making capabilities and transfer control to other parts of the program. – e. g. conditional and unconditional branches

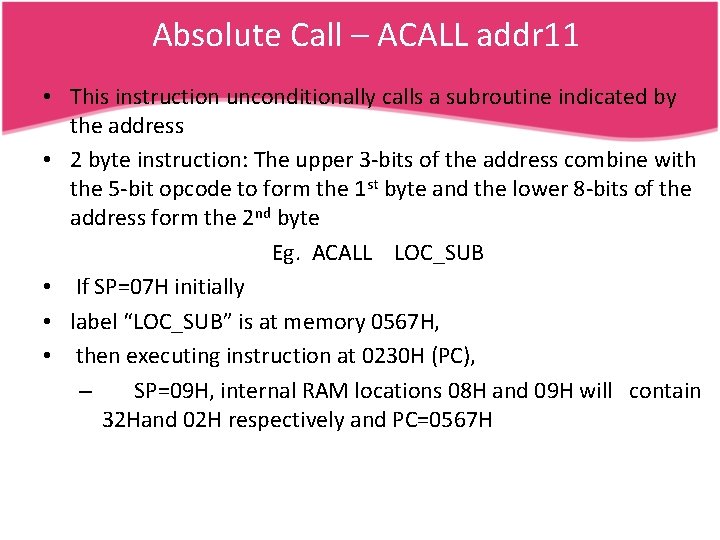

CALL ACALL & LCALL • The 8051 provides 2 forms for the CALL instruction: – Absolute Call – ACALL • Uses an 11 -bit address • The subroutine must be within the same 2 K page. – Long Call – LCALL • Uses a 16 -bit address • The subroutine can be anywhere. – Both forms push the 16 -bit address of PC on the stack and update the stack pointer.

Absolute Call – ACALL addr 11 • This instruction unconditionally calls a subroutine indicated by the address • 2 byte instruction: The upper 3 -bits of the address combine with the 5 -bit opcode to form the 1 st byte and the lower 8 -bits of the address form the 2 nd byte Eg. ACALL LOC_SUB • If SP=07 H initially • label “LOC_SUB” is at memory 0567 H, • then executing instruction at 0230 H (PC), – SP=09 H, internal RAM locations 08 H and 09 H will contain 32 Hand 02 H respectively and PC=0567 H

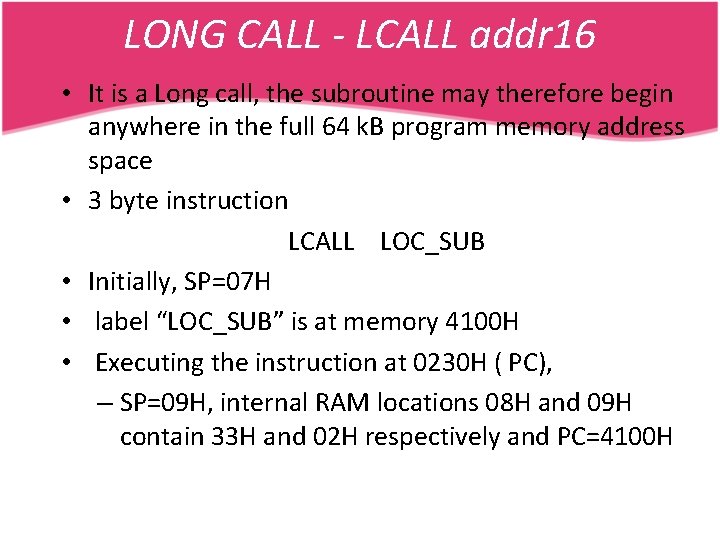

LONG CALL - LCALL addr 16 • It is a Long call, the subroutine may therefore begin anywhere in the full 64 k. B program memory address space • 3 byte instruction LCALL LOC_SUB • Initially, SP=07 H • label “LOC_SUB” is at memory 4100 H • Executing the instruction at 0230 H ( PC), – SP=09 H, internal RAM locations 08 H and 09 H contain 33 H and 02 H respectively and PC=4100 H

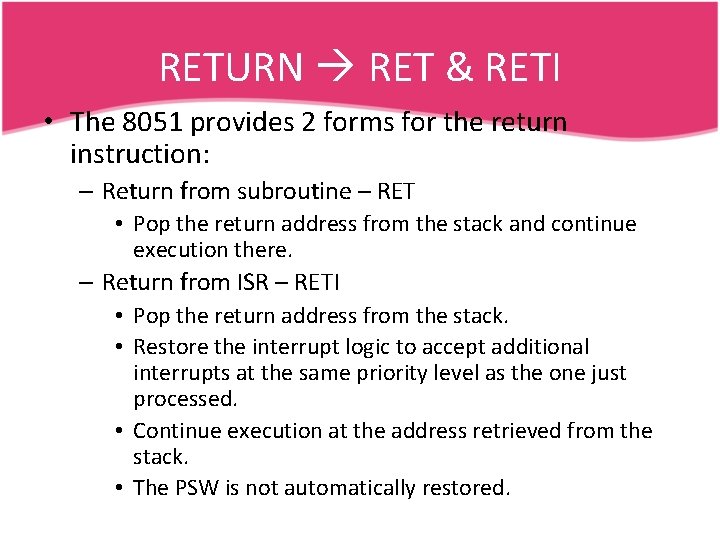

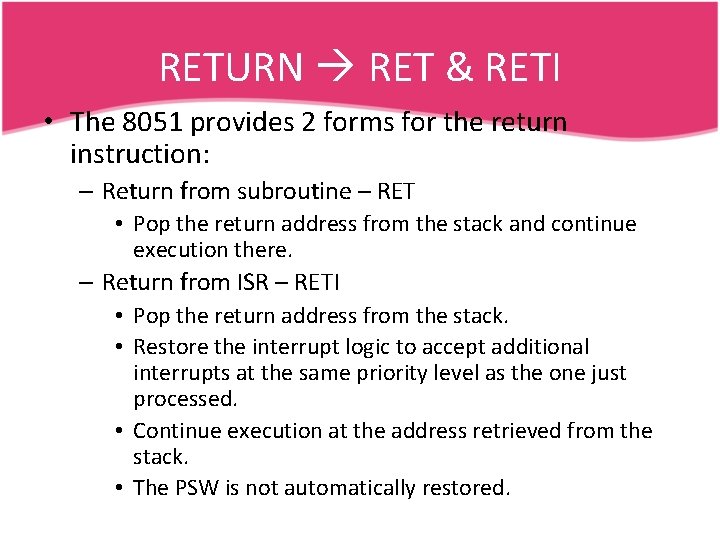

RETURN RET & RETI • The 8051 provides 2 forms for the return instruction: – Return from subroutine – RET • Pop the return address from the stack and continue execution there. – Return from ISR – RETI • Pop the return address from the stack. • Restore the interrupt logic to accept additional interrupts at the same priority level as the one just processed. • Continue execution at the address retrieved from the stack. • The PSW is not automatically restored.

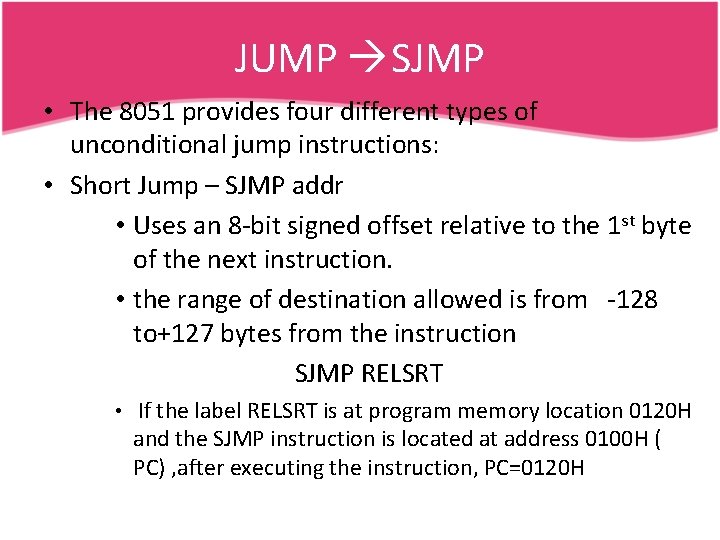

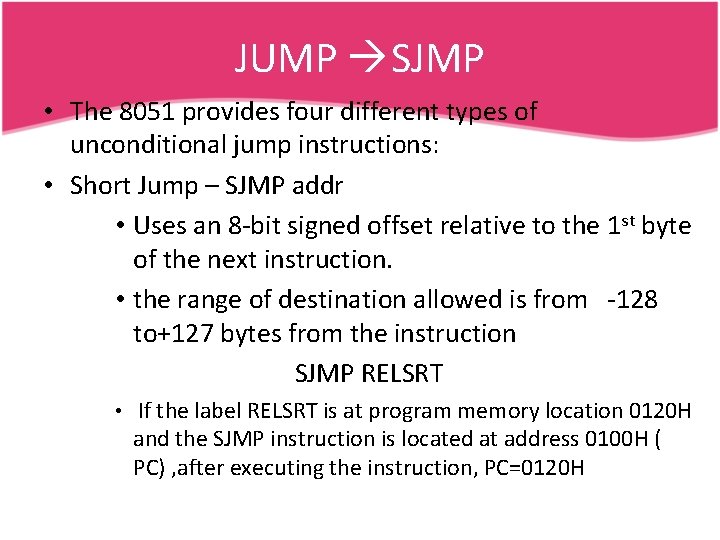

JUMP SJMP • The 8051 provides four different types of unconditional jump instructions: • Short Jump – SJMP addr • Uses an 8 -bit signed offset relative to the 1 st byte of the next instruction. • the range of destination allowed is from -128 to+127 bytes from the instruction SJMP RELSRT • If the label RELSRT is at program memory location 0120 H and the SJMP instruction is located at address 0100 H ( PC) , after executing the instruction, PC=0120 H

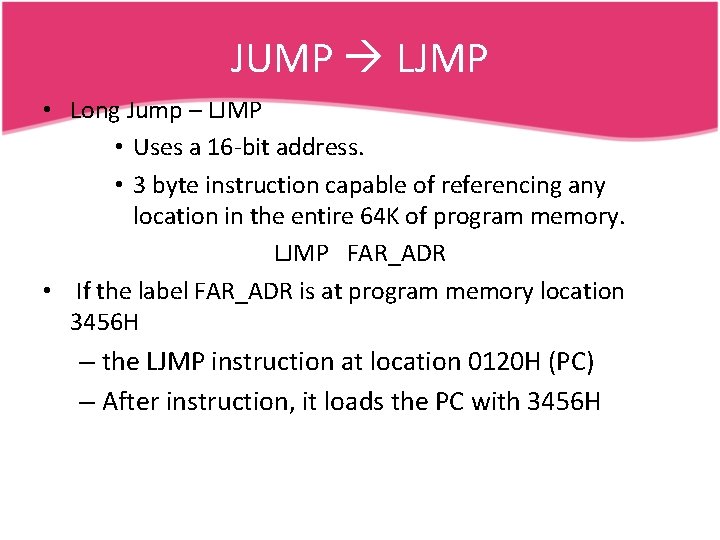

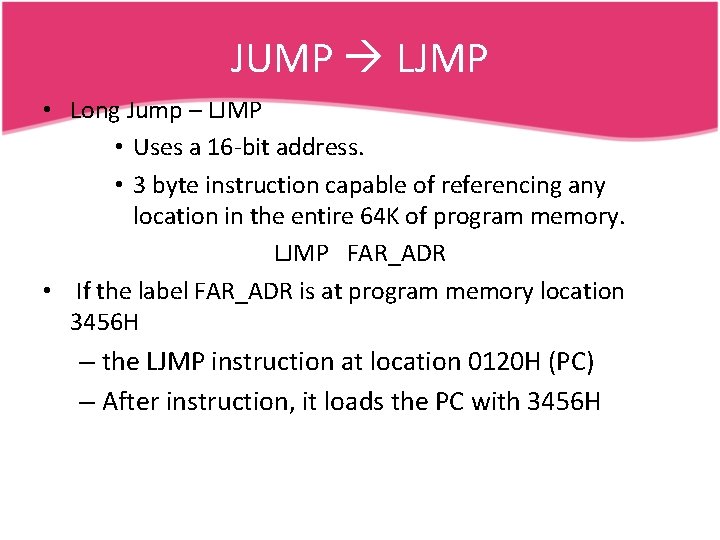

JUMP LJMP • Long Jump – LJMP • Uses a 16 -bit address. • 3 byte instruction capable of referencing any location in the entire 64 K of program memory. LJMP FAR_ADR • If the label FAR_ADR is at program memory location 3456 H – the LJMP instruction at location 0120 H (PC) – After instruction, it loads the PC with 3456 H

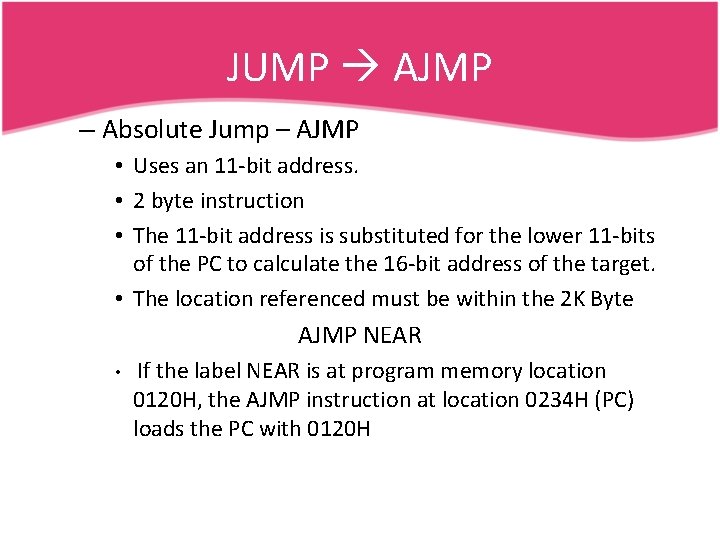

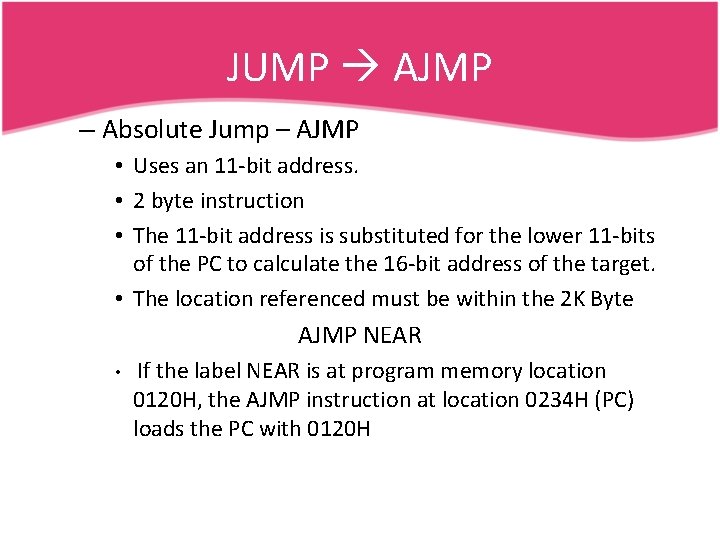

JUMP AJMP – Absolute Jump – AJMP • Uses an 11 -bit address. • 2 byte instruction • The 11 -bit address is substituted for the lower 11 -bits of the PC to calculate the 16 -bit address of the target. • The location referenced must be within the 2 K Byte AJMP NEAR • If the label NEAR is at program memory location 0120 H, the AJMP instruction at location 0234 H (PC) loads the PC with 0120 H

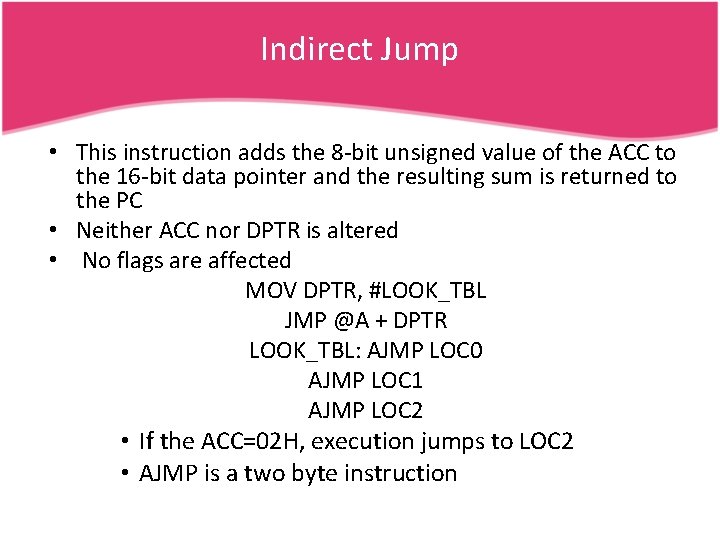

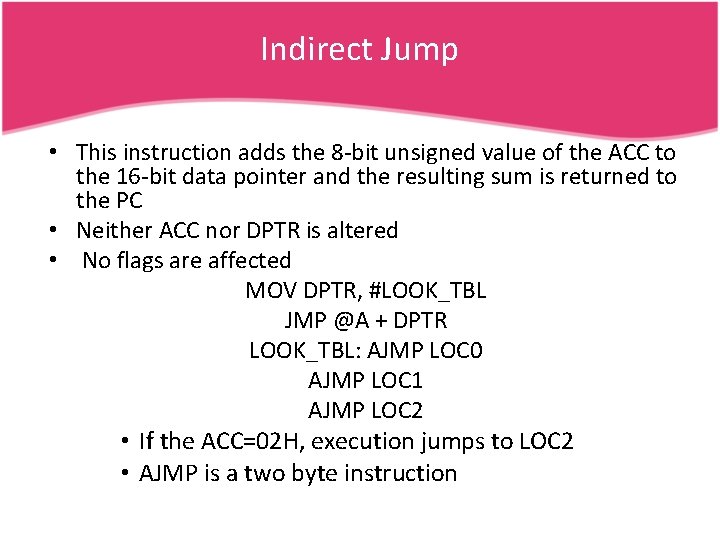

Indirect Jump • This instruction adds the 8 -bit unsigned value of the ACC to the 16 -bit data pointer and the resulting sum is returned to the PC • Neither ACC nor DPTR is altered • No flags are affected MOV DPTR, #LOOK_TBL JMP @A + DPTR LOOK_TBL: AJMP LOC 0 AJMP LOC 1 AJMP LOC 2 • If the ACC=02 H, execution jumps to LOC 2 • AJMP is a two byte instruction

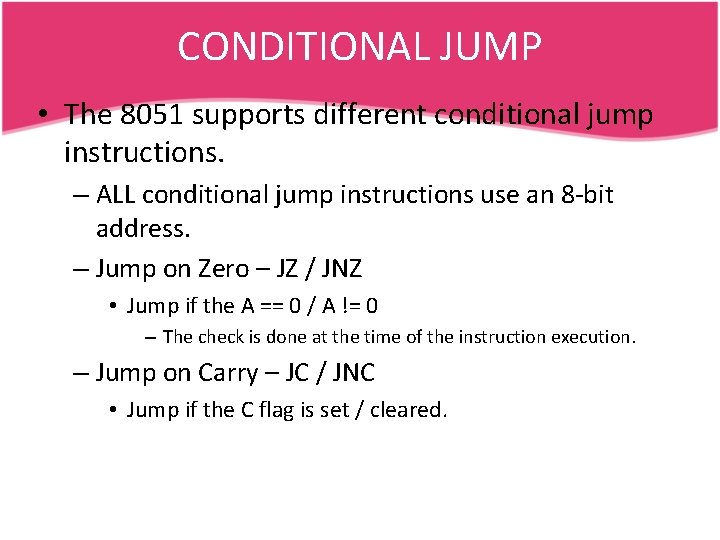

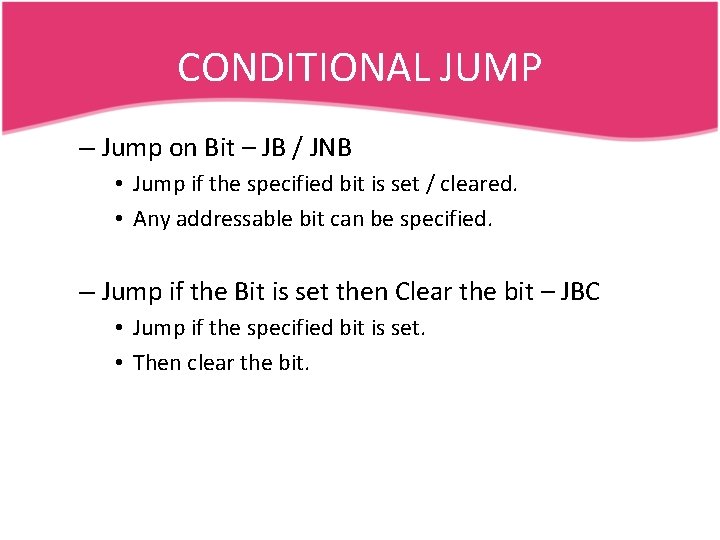

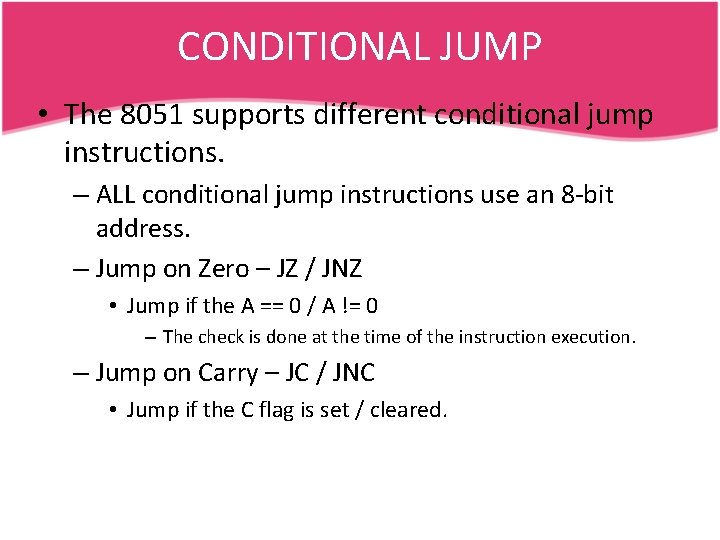

CONDITIONAL JUMP • The 8051 supports different conditional jump instructions. – ALL conditional jump instructions use an 8 -bit address. – Jump on Zero – JZ / JNZ • Jump if the A == 0 / A != 0 – The check is done at the time of the instruction execution. – Jump on Carry – JC / JNC • Jump if the C flag is set / cleared.

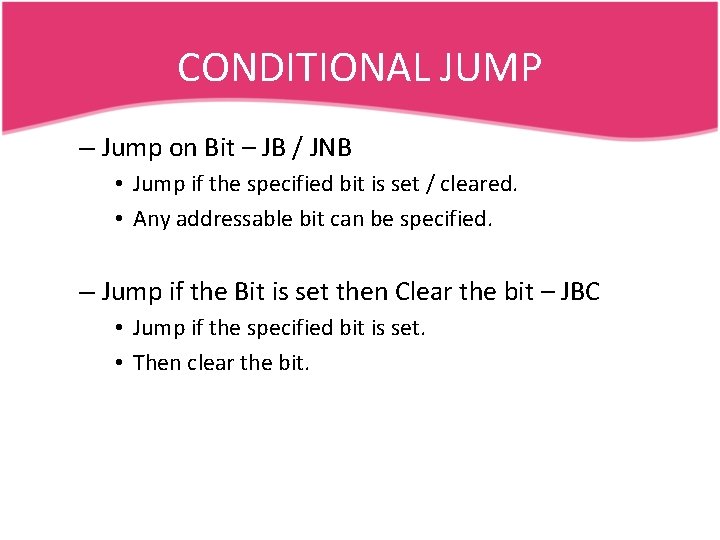

CONDITIONAL JUMP – Jump on Bit – JB / JNB • Jump if the specified bit is set / cleared. • Any addressable bit can be specified. – Jump if the Bit is set then Clear the bit – JBC • Jump if the specified bit is set. • Then clear the bit.

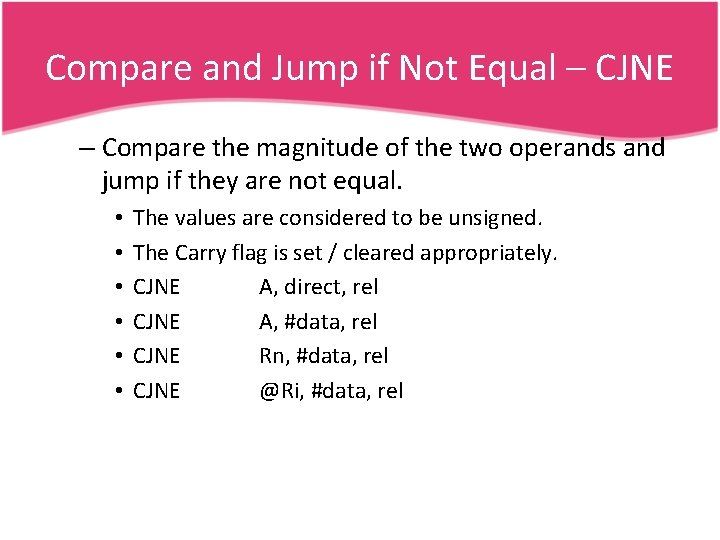

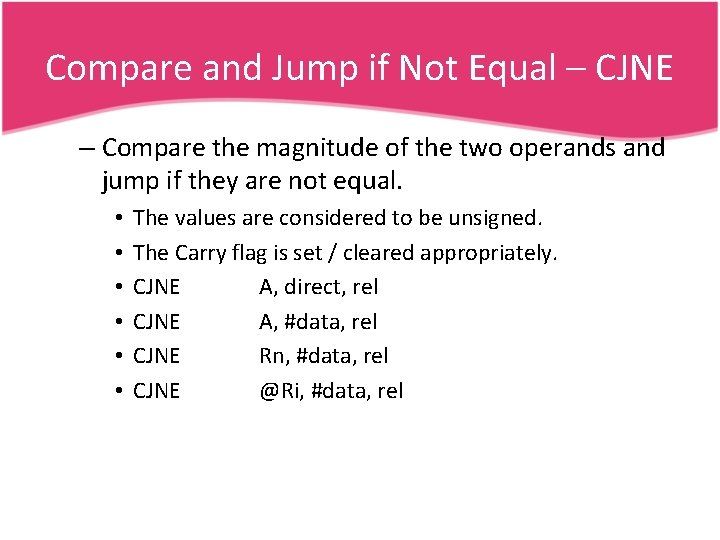

Compare and Jump if Not Equal – CJNE – Compare the magnitude of the two operands and jump if they are not equal. • • • The values are considered to be unsigned. The Carry flag is set / cleared appropriately. CJNE A, direct, rel CJNE A, #data, rel CJNE Rn, #data, rel CJNE @Ri, #data, rel

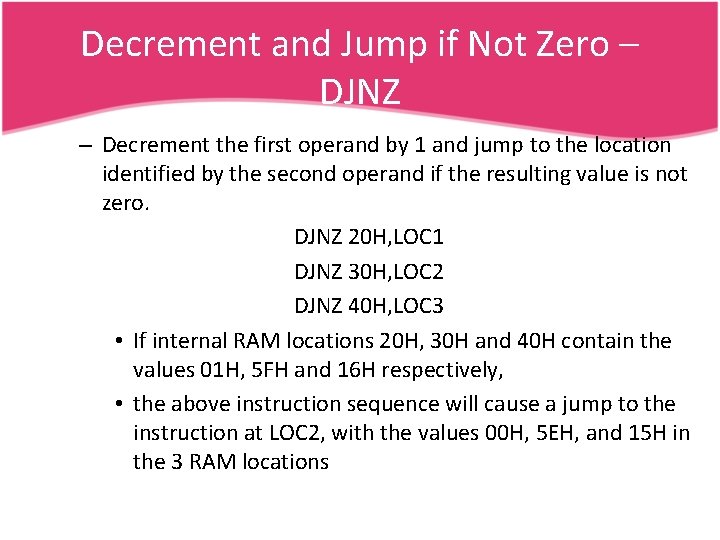

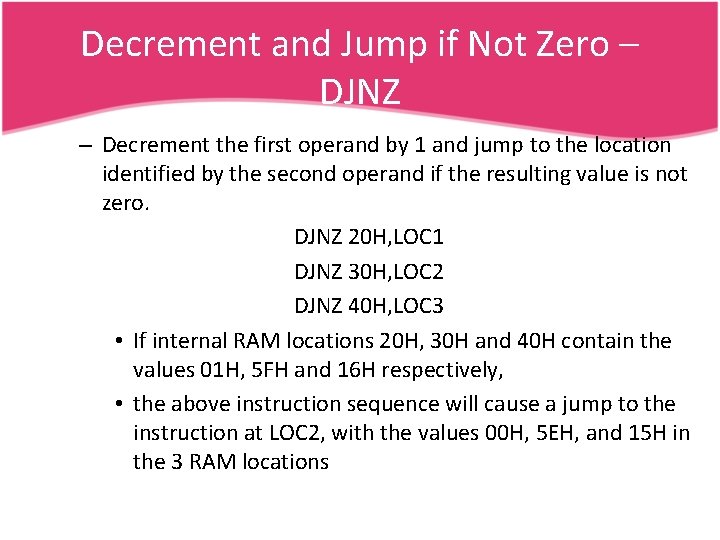

Decrement and Jump if Not Zero – DJNZ – Decrement the first operand by 1 and jump to the location identified by the second operand if the resulting value is not zero. DJNZ 20 H, LOC 1 DJNZ 30 H, LOC 2 DJNZ 40 H, LOC 3 • If internal RAM locations 20 H, 30 H and 40 H contain the values 01 H, 5 FH and 16 H respectively, • the above instruction sequence will cause a jump to the instruction at LOC 2, with the values 00 H, 5 EH, and 15 H in the 3 RAM locations

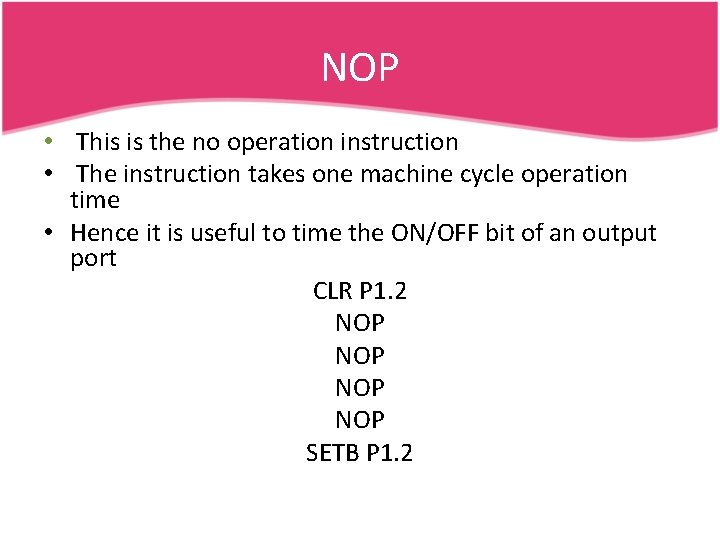

NOP • This is the no operation instruction • The instruction takes one machine cycle operation time • Hence it is useful to time the ON/OFF bit of an output port CLR P 1. 2 NOP NOP SETB P 1. 2

LOGICAL INSTRUCTIONS AND, OR, NOT, XOR, ROTATE, SWA P 59

Logic Instructions q Bitwise logic operations v (AND, OR, XOR, NOT) q Clear q Rotate q Swap • Logic instructions do NOT affect the flags in PSW 60

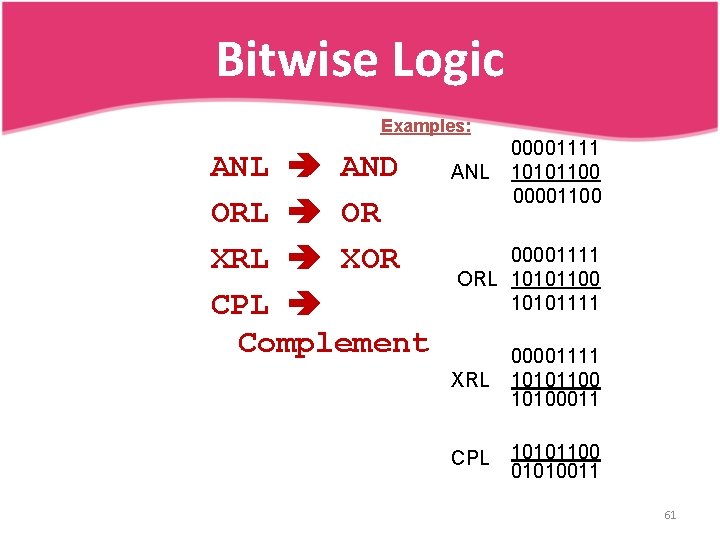

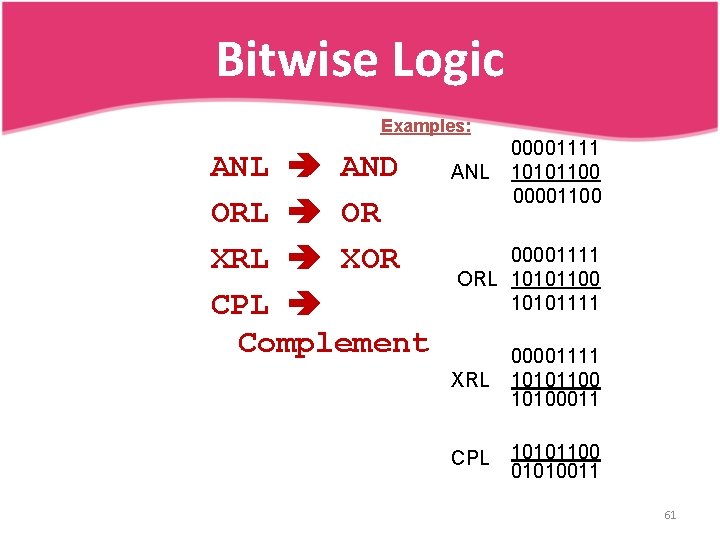

Bitwise Logic Examples: ANL AND ORL OR XRL XOR CPL Complement ANL 00001111 10101100 00001111 ORL 10101100 10101111 XRL 00001111 10101100 10100011 CPL 10101100 01010011 61

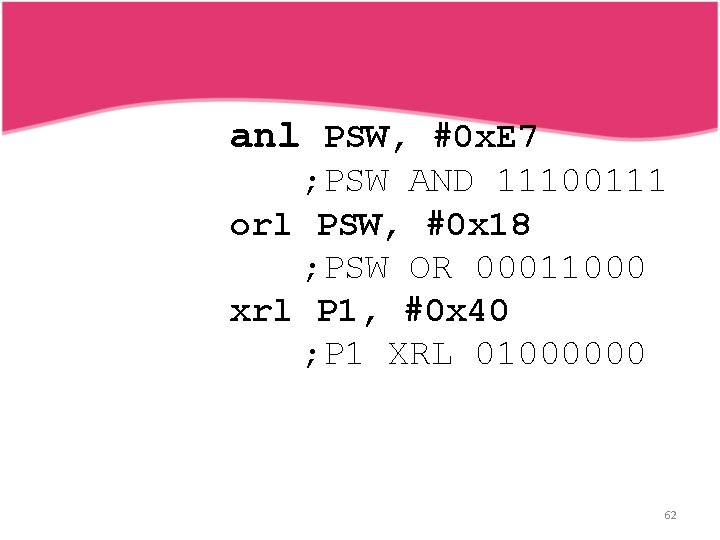

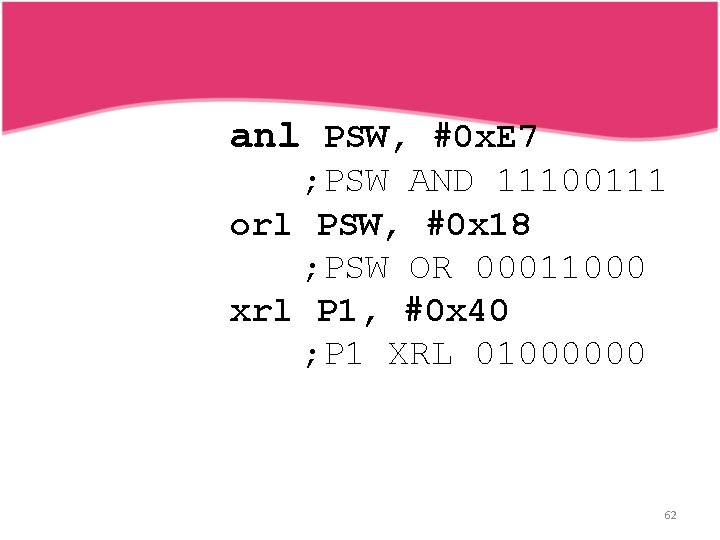

anl PSW, #0 x. E 7 ; PSW AND 11100111 orl PSW, #0 x 18 ; PSW OR 00011000 xrl P 1, #0 x 40 ; P 1 XRL 01000000 62

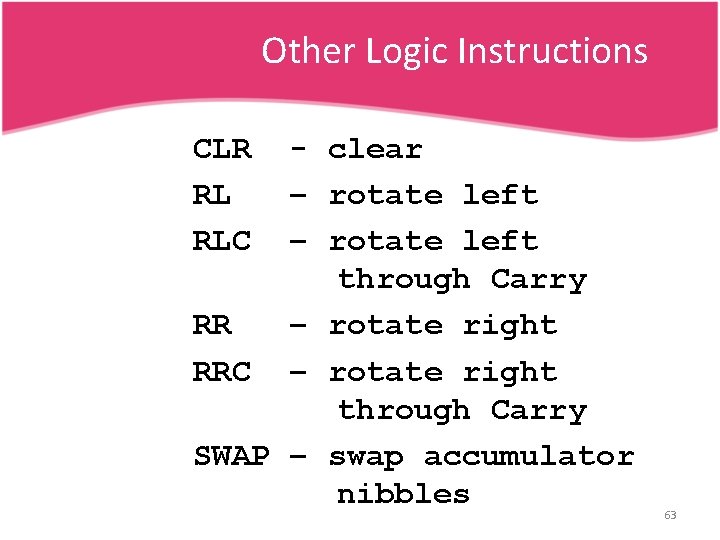

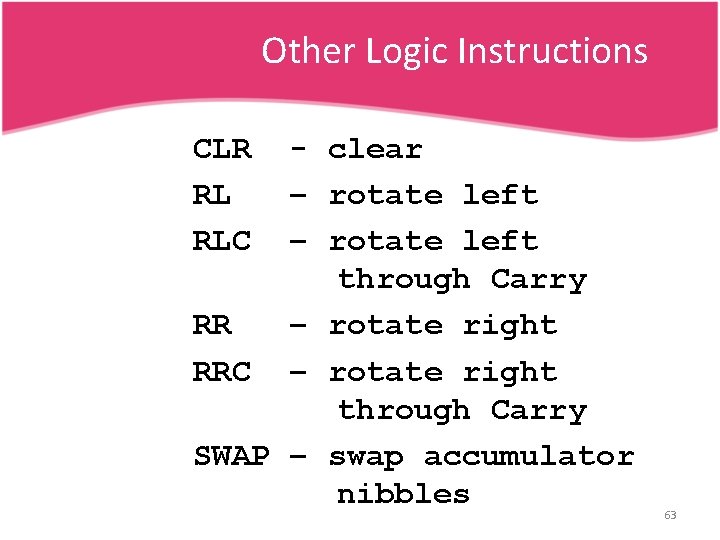

Other Logic Instructions CLR RL RLC - clear – rotate left through Carry RR – rotate right RRC – rotate right through Carry SWAP – swap accumulator nibbles 63

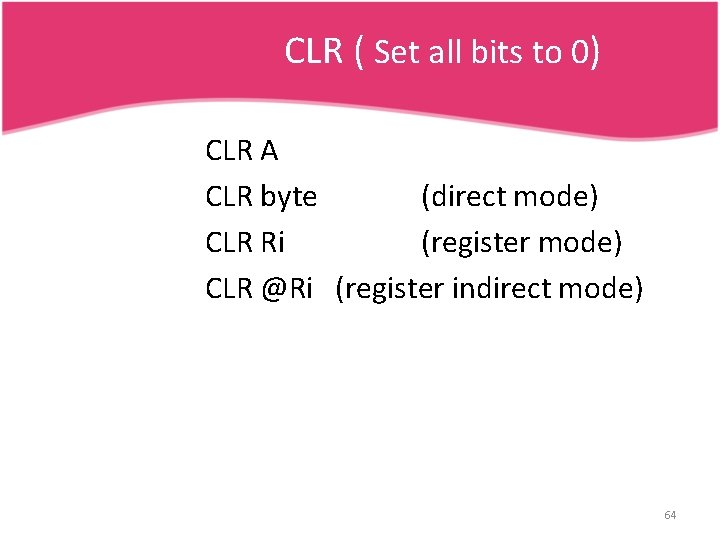

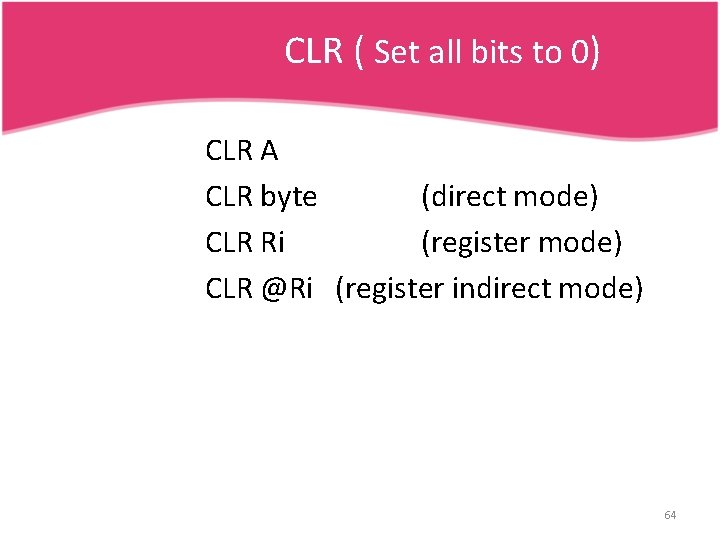

CLR ( Set all bits to 0) CLR A CLR byte (direct mode) CLR Ri (register mode) CLR @Ri (register indirect mode) 64

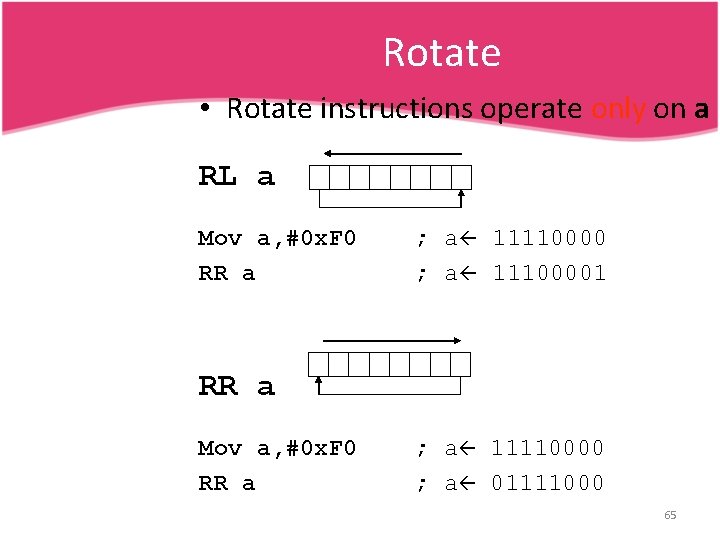

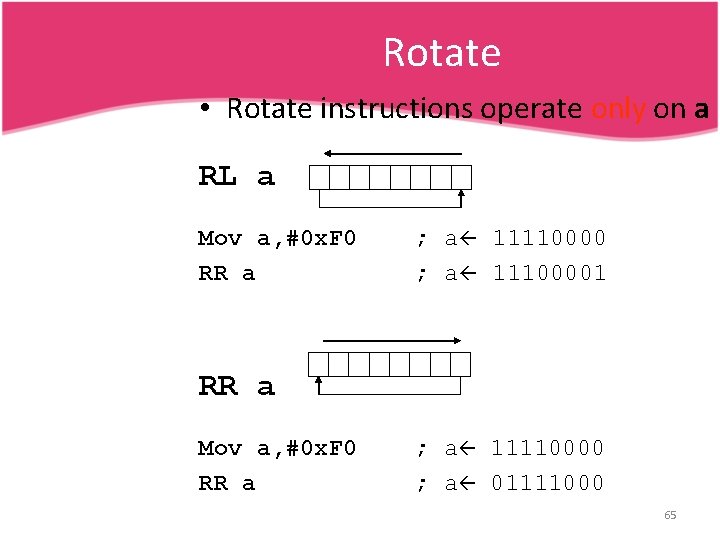

Rotate • Rotate instructions operate only on a RL a Mov a, #0 x. F 0 RR a ; a 11110000 ; a 11100001 RR a Mov a, #0 x. F 0 RR a ; a 11110000 ; a 01111000 65

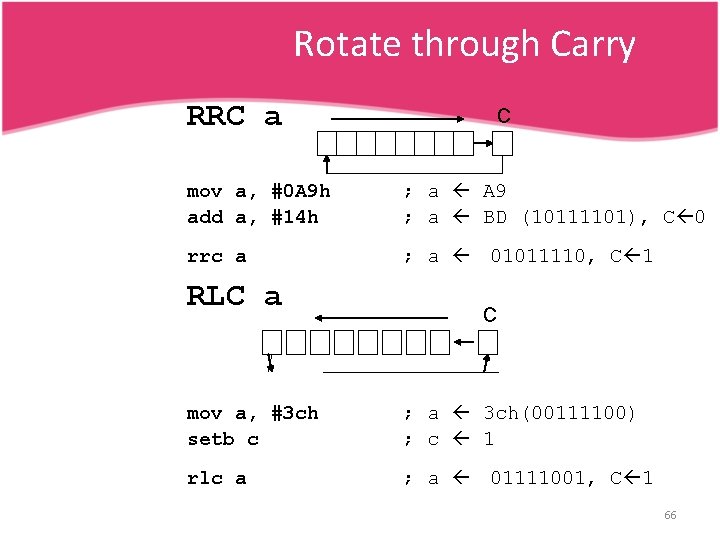

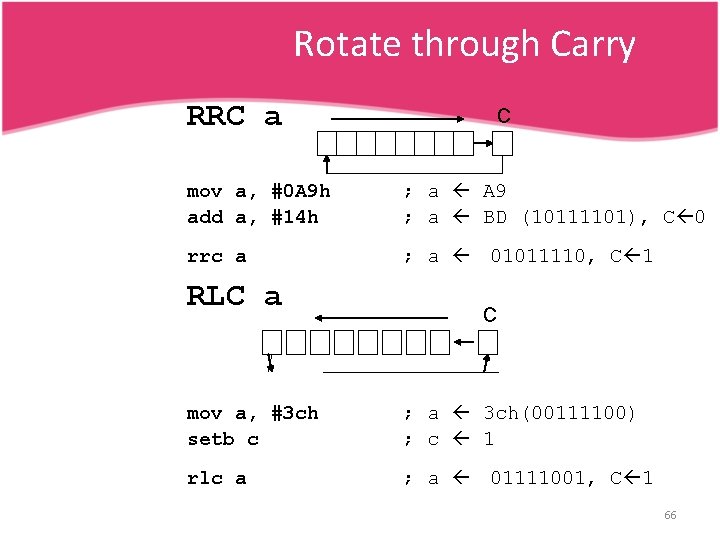

Rotate through Carry RRC a C mov a, #0 A 9 h add a, #14 h ; a A 9 ; a BD (10111101), C 0 rrc a ; a 01011110, C 1 RLC a C mov a, #3 ch setb c ; a 3 ch(00111100) ; c 1 rlc a ; a 01111001, C 1 66

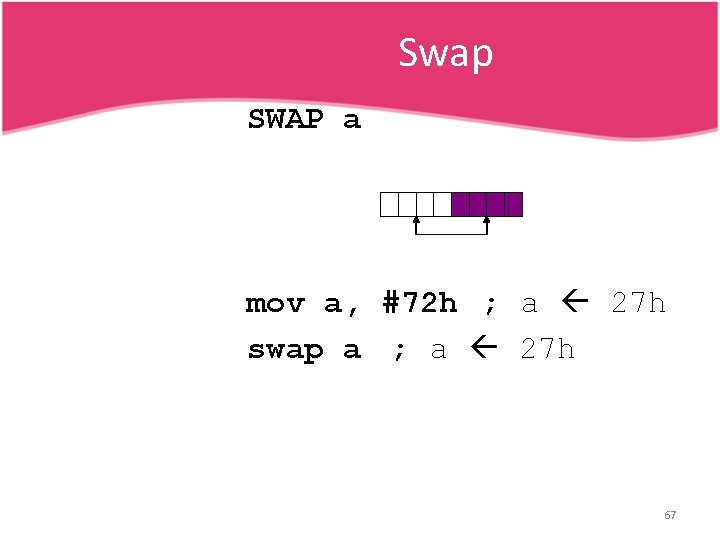

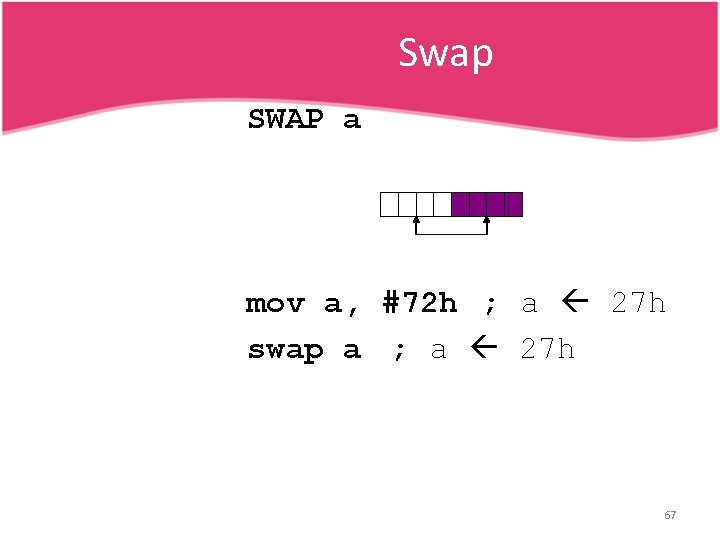

Swap SWAP a mov a, #72 h ; a 27 h swap a ; a 27 h 67

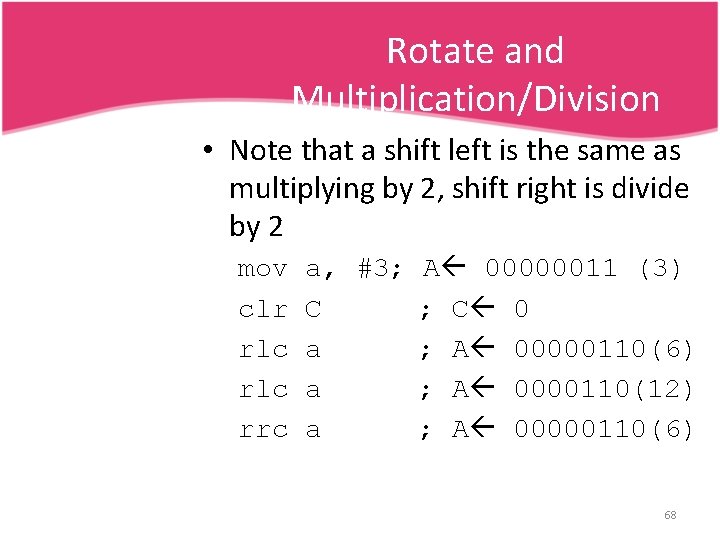

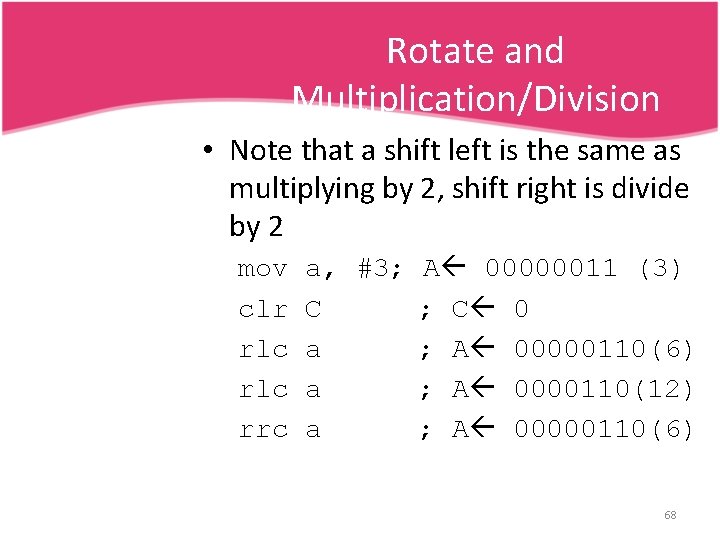

Rotate and Multiplication/Division • Note that a shift left is the same as multiplying by 2, shift right is divide by 2 mov clr rlc rrc a, #3; A 00000011 (3) C ; C 0 a ; A 00000110(6) a ; A 0000110(12) a ; A 00000110(6) 68

Serial Communication 69

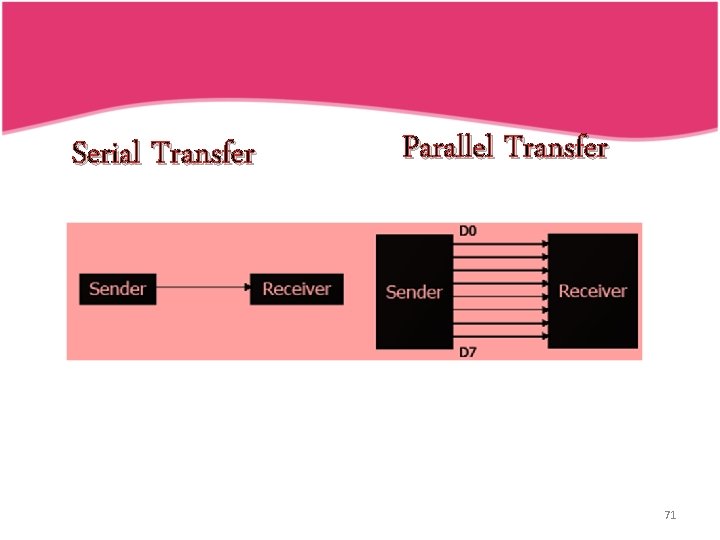

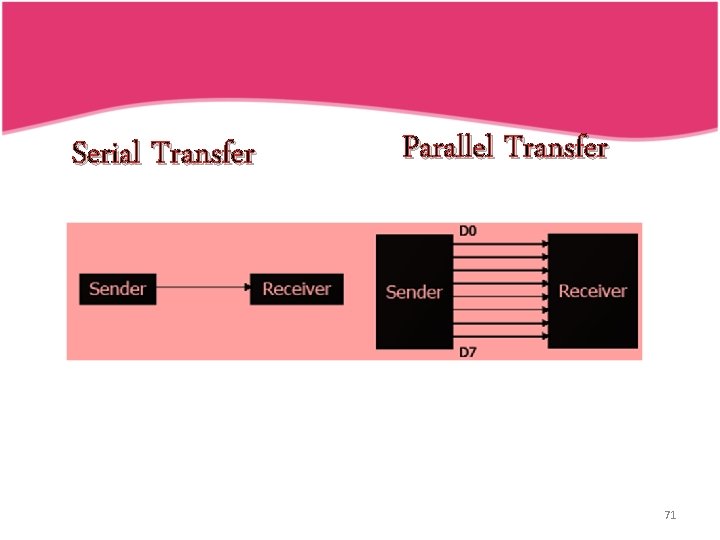

Ways of Data Transfer q Computers transfer data in two ways: • Parallel ü Often 8 or more lines (wire conductors) are used to transfer data to a device that is only a few feet away. • Serial ü To transfer to a device located many meters away, the serial method is used. The data is sent one bit at a time. 70

Serial Transfer Parallel Transfer 71

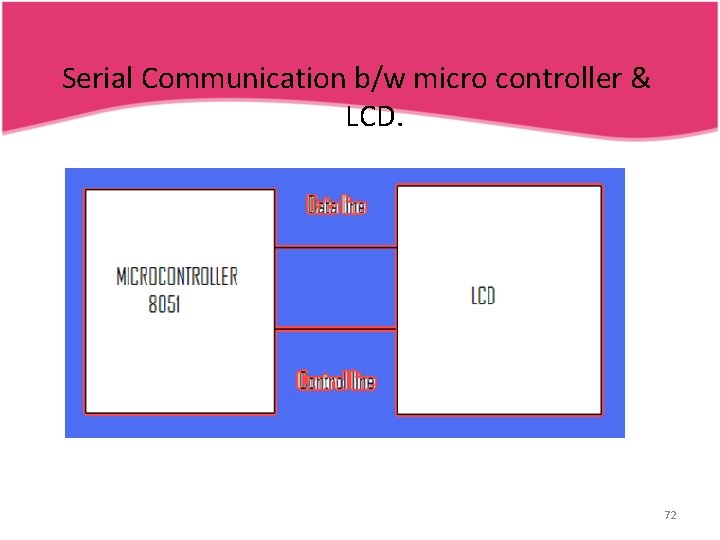

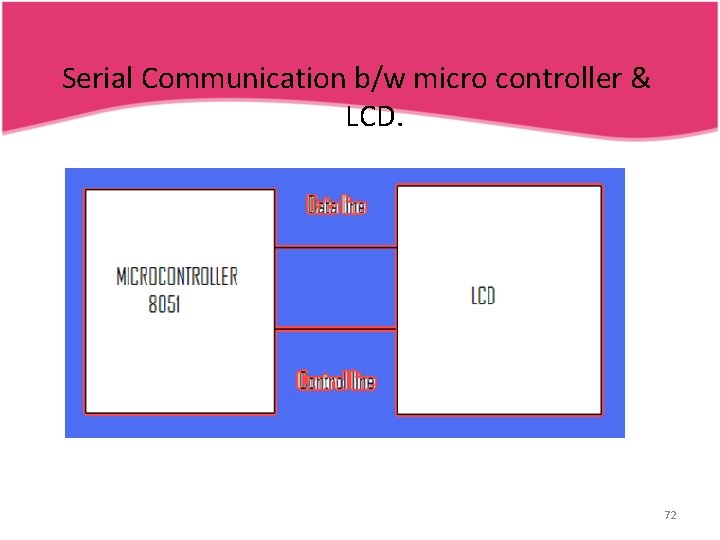

Serial Communication b/w micro controller & LCD. 72

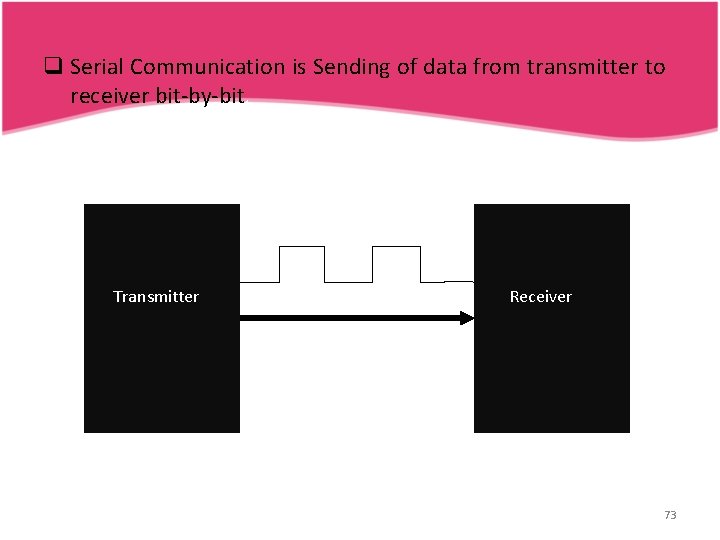

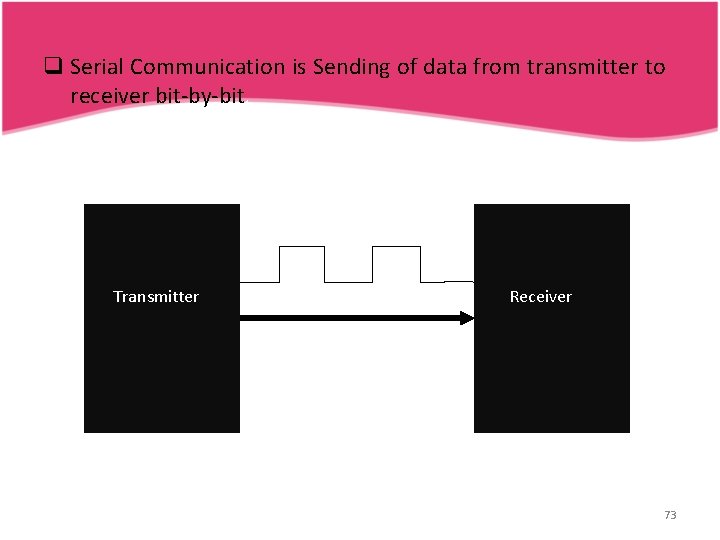

q Serial Communication is Sending of data from transmitter to receiver bit-by-bit. Transmitter Receiver 73

Advantages of Serial Communication • For long distances. • Low Cost. Disadvantages of Serial Communication • The speed of serial Communication is very slow than parallel communication. 74

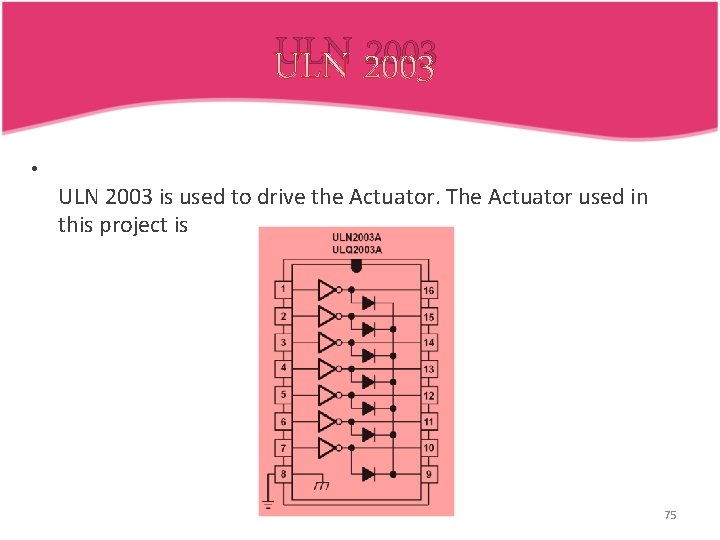

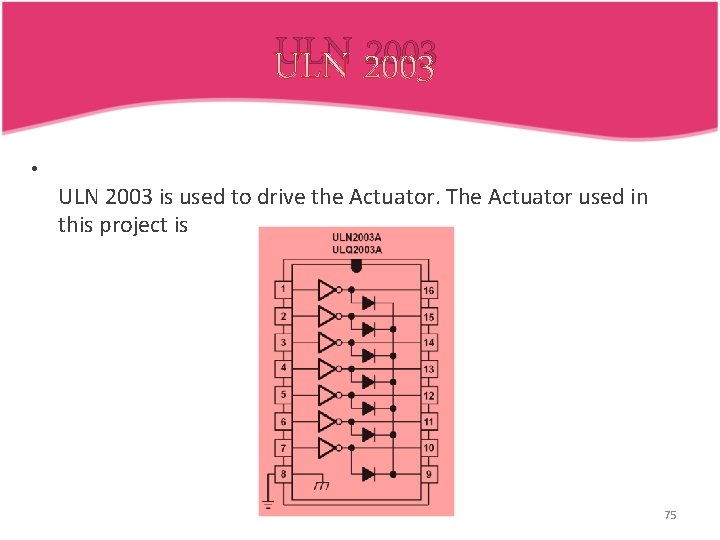

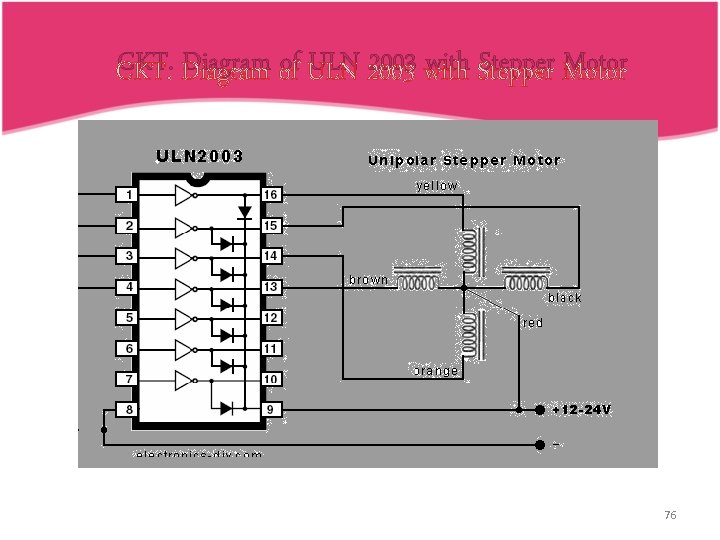

ULN 2003 • ULN 2003 is used to drive the Actuator. The Actuator used in this project is Stepper Motor. • Pin Diagram of ULN 2003 75

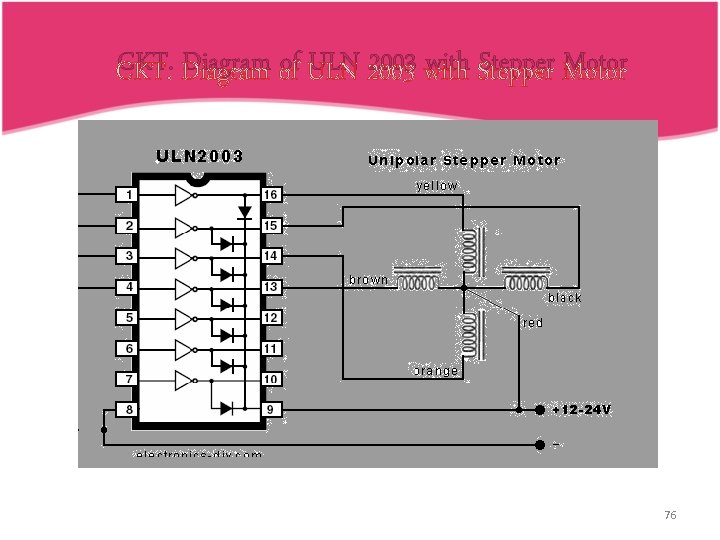

CKT. Diagram of ULN 2003 with Stepper Motor 76

Application of ULN 2003 • To control stepper motor , DC motor. Servomotor. • To operate Relays. 77

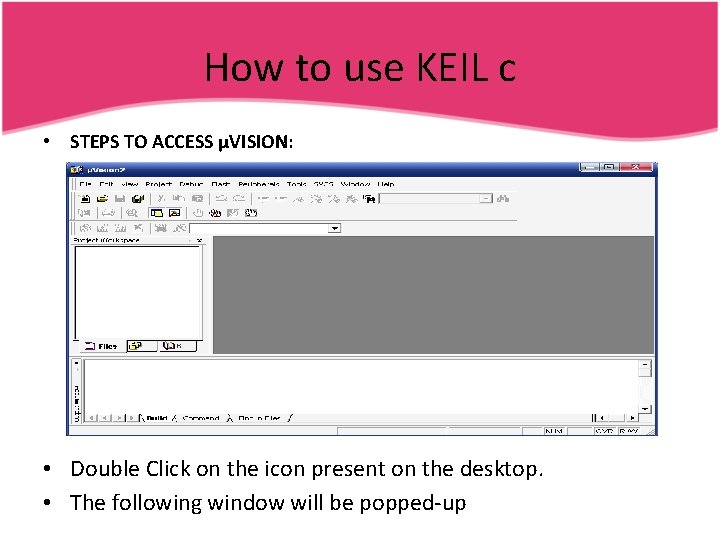

How to use KEIL c • STEPS TO ACCESS µVISION: • Double Click on the icon present on the desktop. • The following window will be popped-up

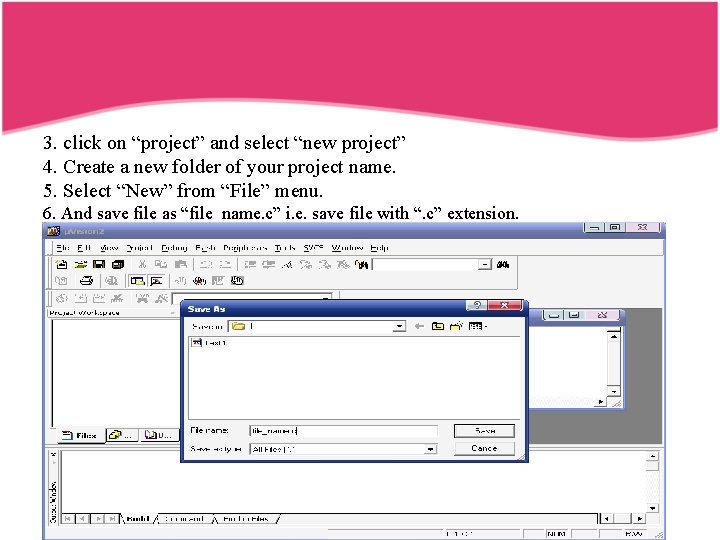

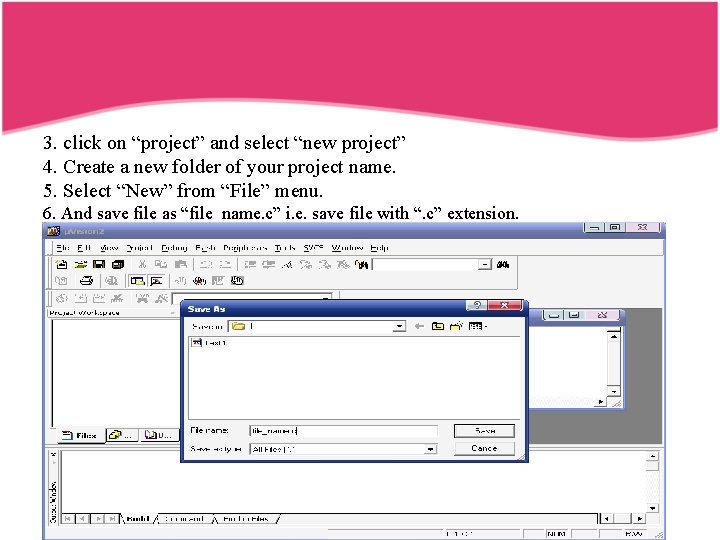

3. click on “project” and select “new project” 4. Create a new folder of your project name. 5. Select “New” from “File” menu. 6. And save file as “file_name. c” i. e. save file with “. c” extension.

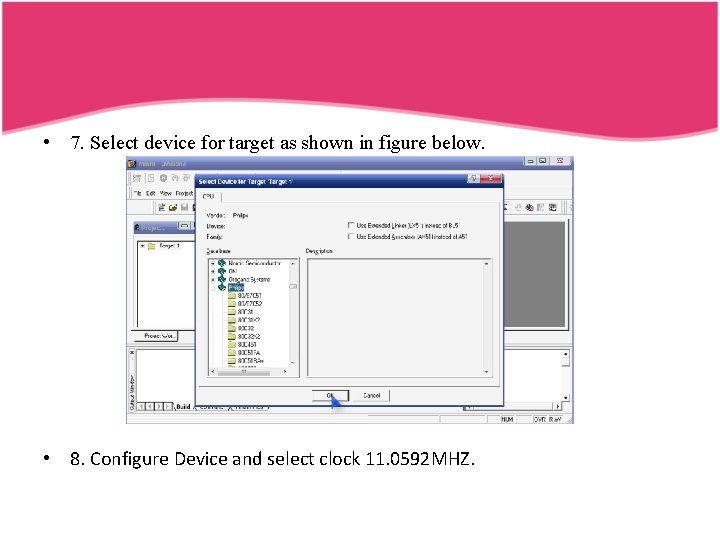

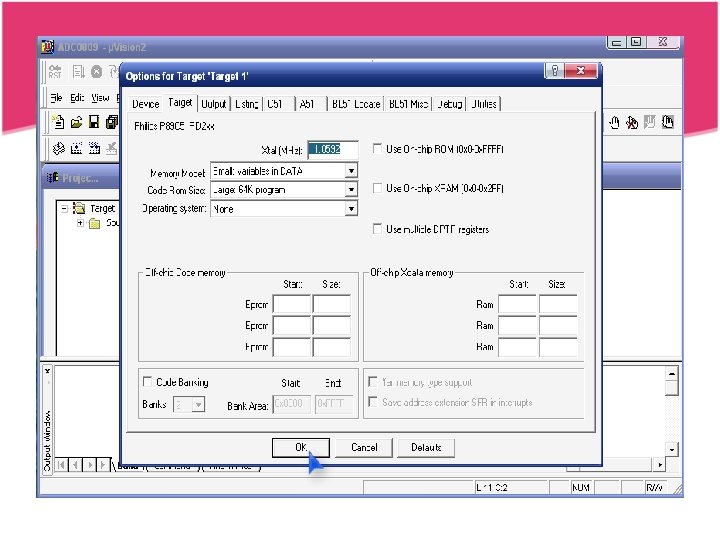

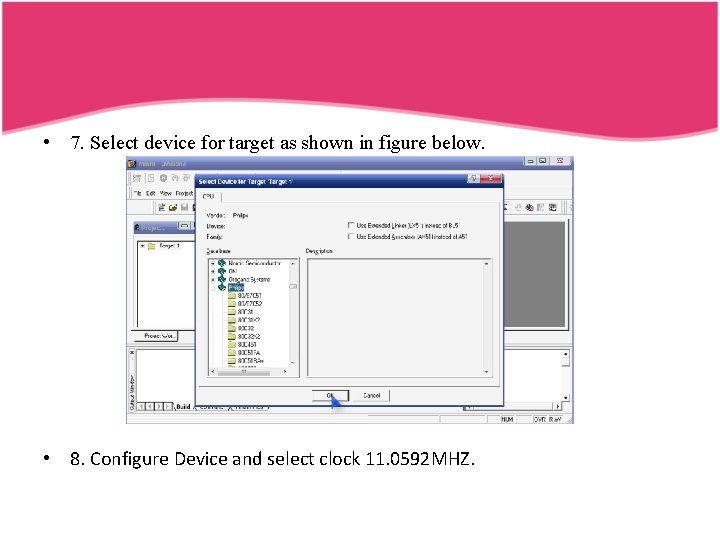

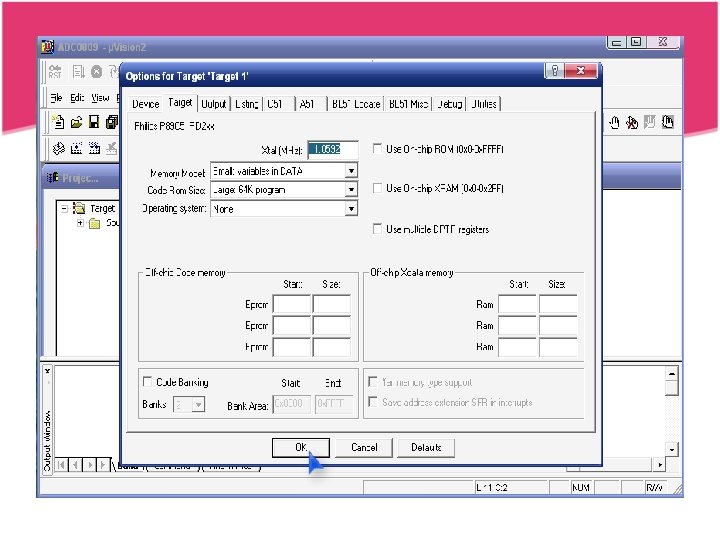

• 7. Select device for target as shown in figure below. • 8. Configure Device and select clock 11. 0592 MHZ.

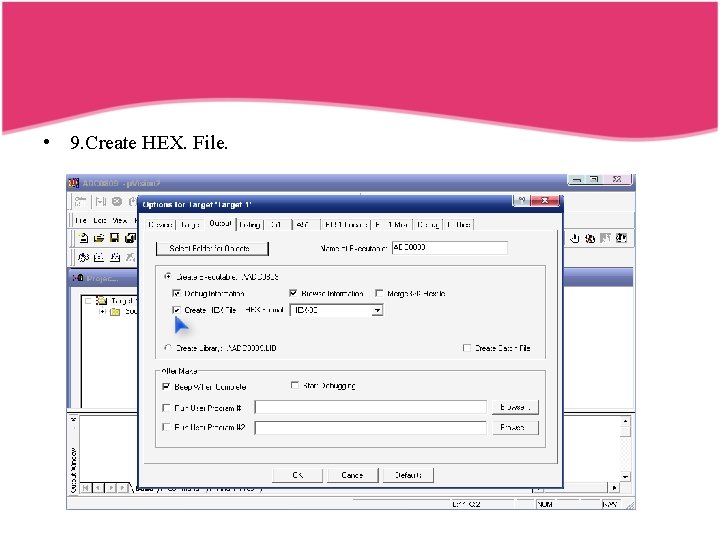

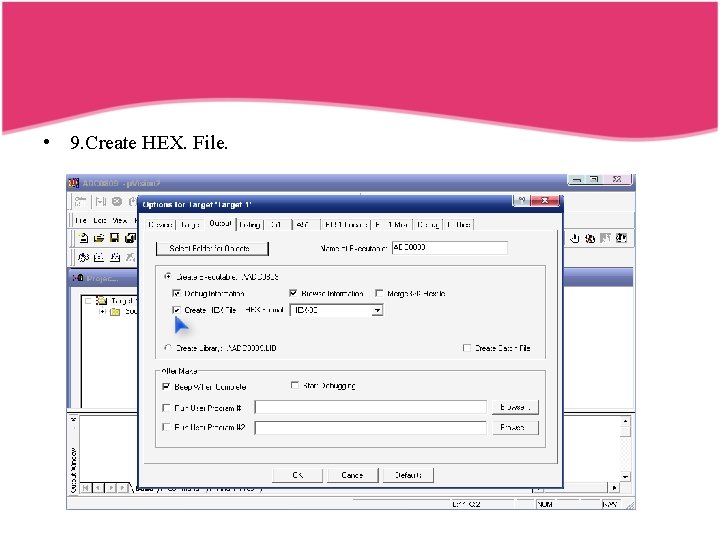

• 9. Create HEX. File.

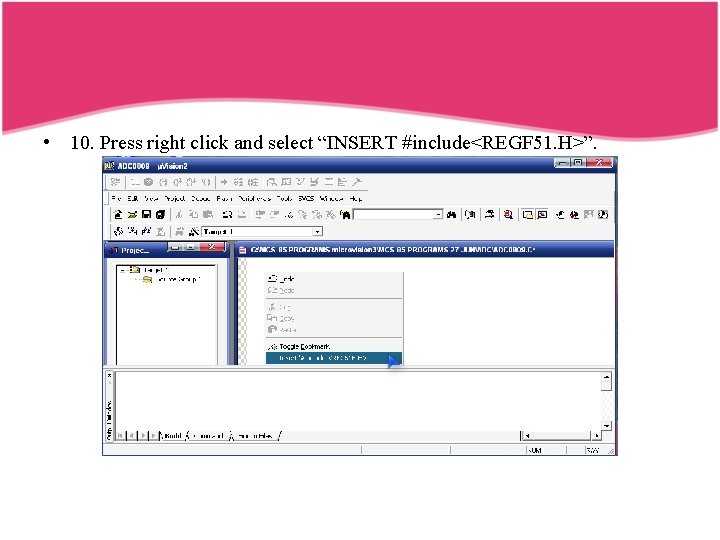

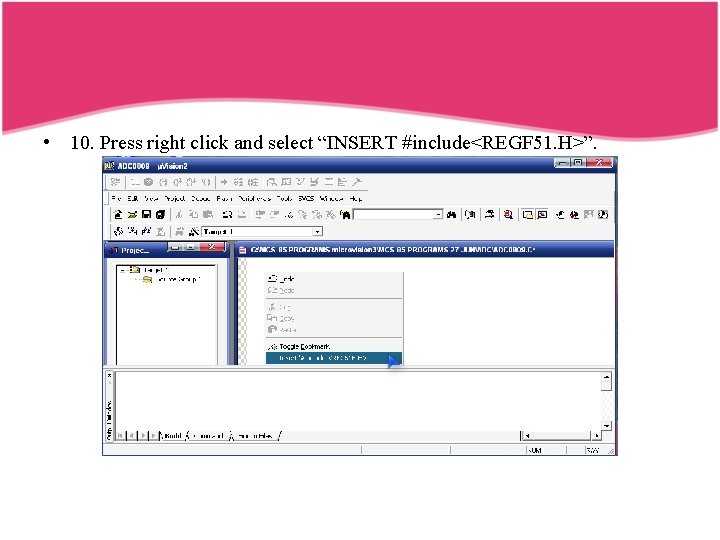

• 10. Press right click and select “INSERT #include<REGF 51. H>”.

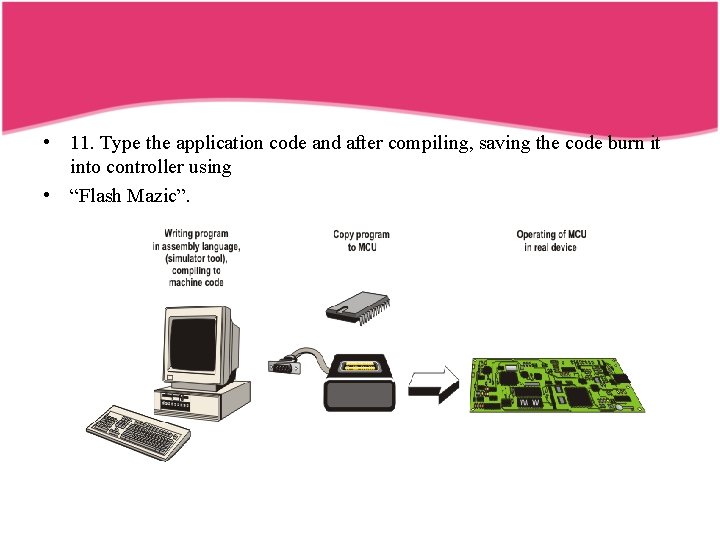

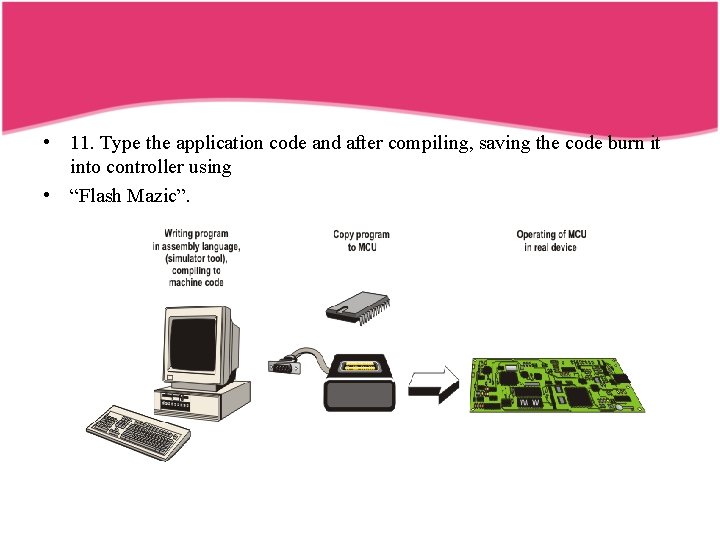

• 11. Type the application code and after compiling, saving the code burn it into controller using • “Flash Mazic”.