MICROCONTROLLER LAB 8051 Balaji Ramakrishna Prof Cherrice Traver

MICROCONTROLLER LAB- 8051 Balaji Ramakrishna

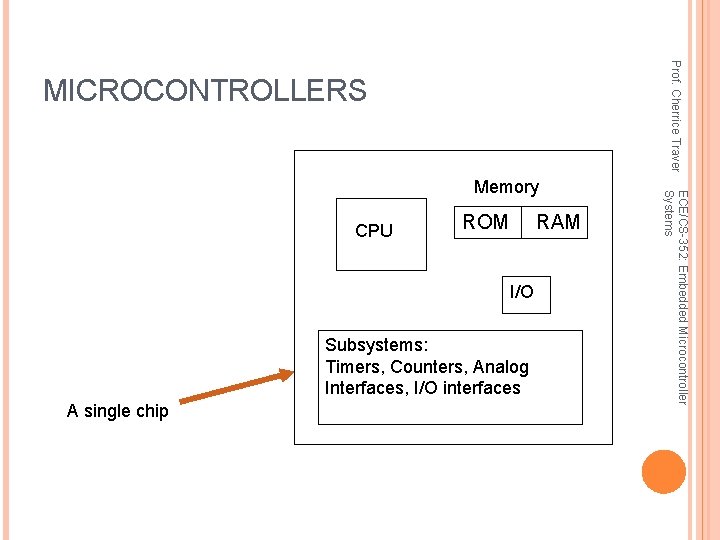

Prof. Cherrice Traver MICROCONTROLLERS CPU ROM RAM I/O Subsystems: Timers, Counters, Analog Interfaces, I/O interfaces A single chip ECE/CS-352: Embedded Microcontroller Systems Memory

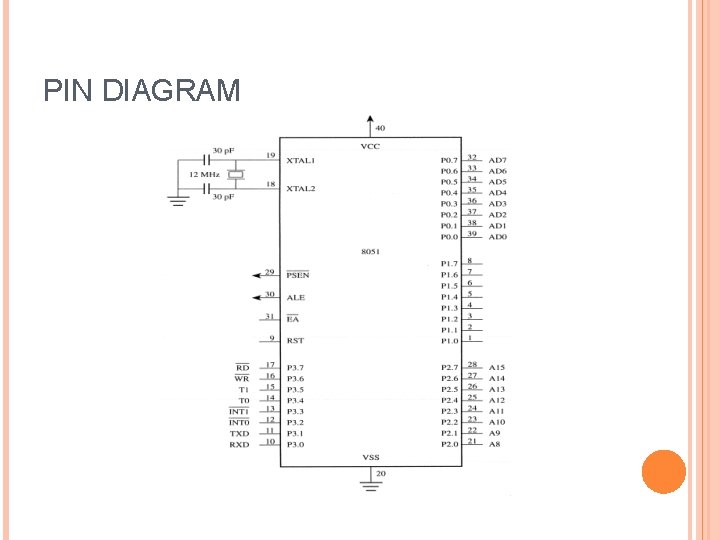

PIN DIAGRAM

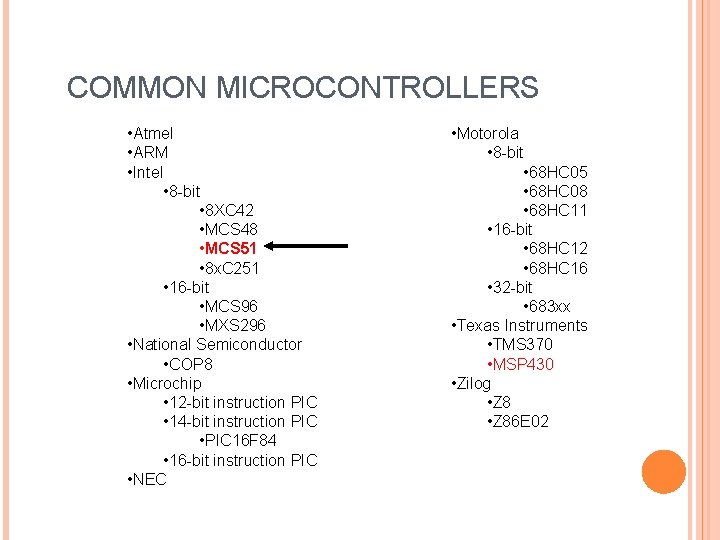

COMMON MICROCONTROLLERS • Atmel • ARM • Intel • 8 -bit • 8 XC 42 • MCS 48 • MCS 51 • 8 x. C 251 • 16 -bit • MCS 96 • MXS 296 • National Semiconductor • COP 8 • Microchip • 12 -bit instruction PIC • 14 -bit instruction PIC • PIC 16 F 84 • 16 -bit instruction PIC • NEC • Motorola • 8 -bit • 68 HC 05 • 68 HC 08 • 68 HC 11 • 16 -bit • 68 HC 12 • 68 HC 16 • 32 -bit • 683 xx • Texas Instruments • TMS 370 • MSP 430 • Zilog • Z 86 E 02

THE NECESSARY TOOLS FOR A MICROPROCESSOR/CONTROLL ER CPU: Central Processing Unit I/O: Input /Output Bus: Address bus & Data bus Memory: RAM & ROM Timer Interrupt Serial Port Parallel Port

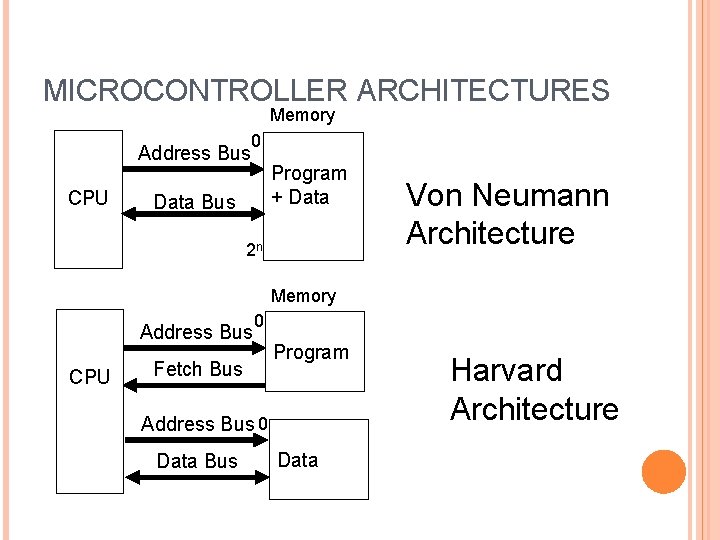

MICROCONTROLLER ARCHITECTURES Memory 0 Address Bus CPU Program + Data Bus 2 n Von Neumann Architecture Memory Address Bus CPU 0 Fetch Bus Program Address Bus 0 Data Bus Data Harvard Architecture

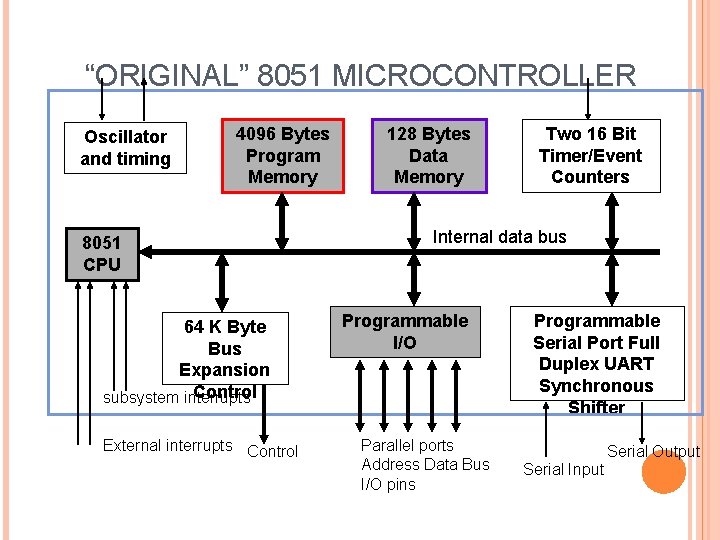

“ORIGINAL” 8051 MICROCONTROLLER Oscillator and timing 4096 Bytes Program Memory 8051 CPU 64 K Byte Bus Expansion Control subsystem interrupts External interrupts Control 128 Bytes Data Memory Two 16 Bit Timer/Event Counters Internal data bus Programmable I/O Parallel ports Address Data Bus I/O pins Programmable Serial Port Full Duplex UART Synchronous Shifter Serial Output Serial Input

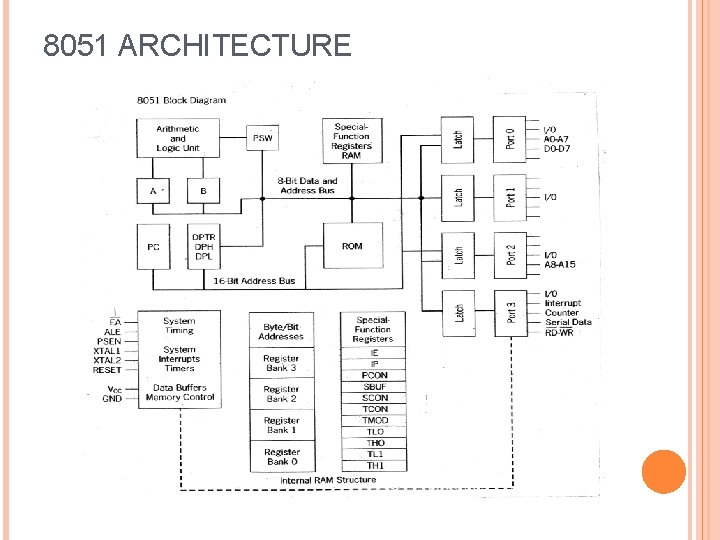

8051 ARCHITECTURE

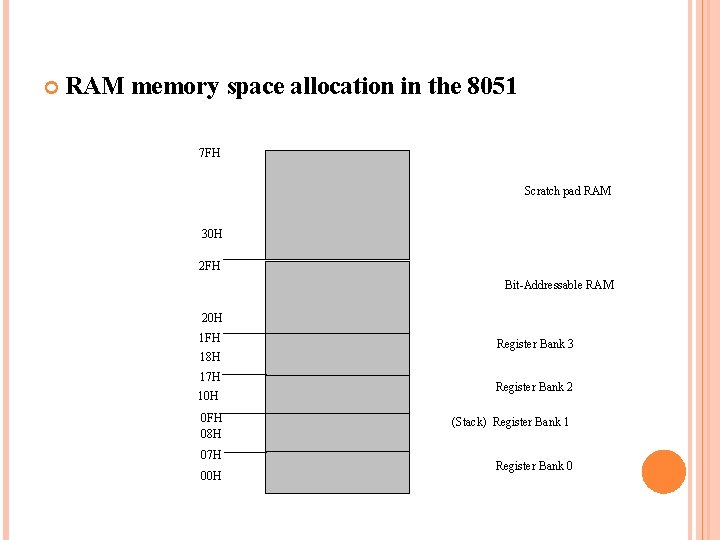

RAM memory space allocation in the 8051 7 FH Scratch pad RAM 30 H 2 FH Bit-Addressable RAM 20 H 1 FH 18 H 17 H 10 H 0 FH 08 H 07 H 00 H Register Bank 3 Register Bank 2 (Stack) Register Bank 1 Register Bank 0

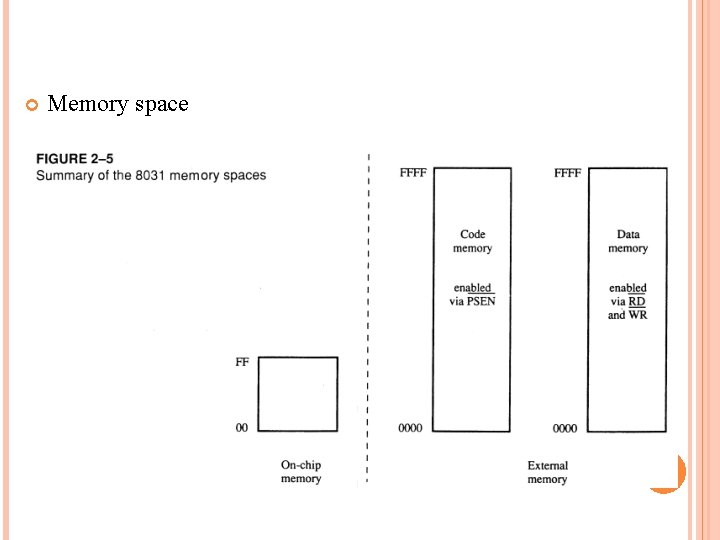

Memory space

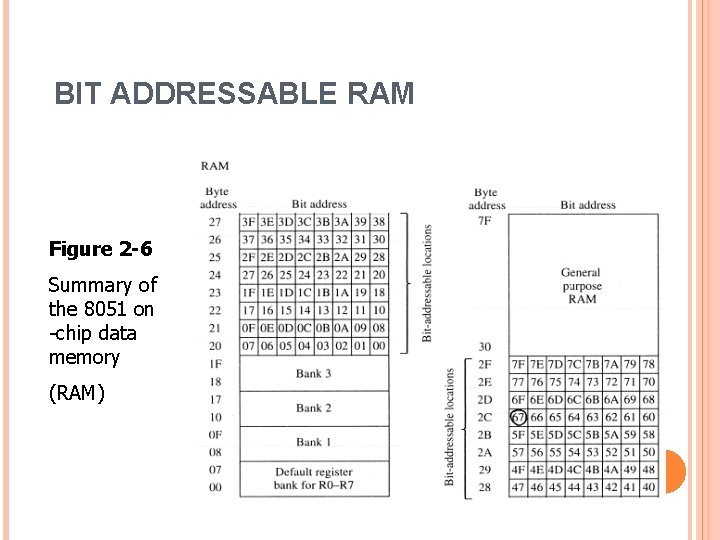

BIT ADDRESSABLE RAM Figure 2 -6 Summary of the 8051 on -chip data memory (RAM)

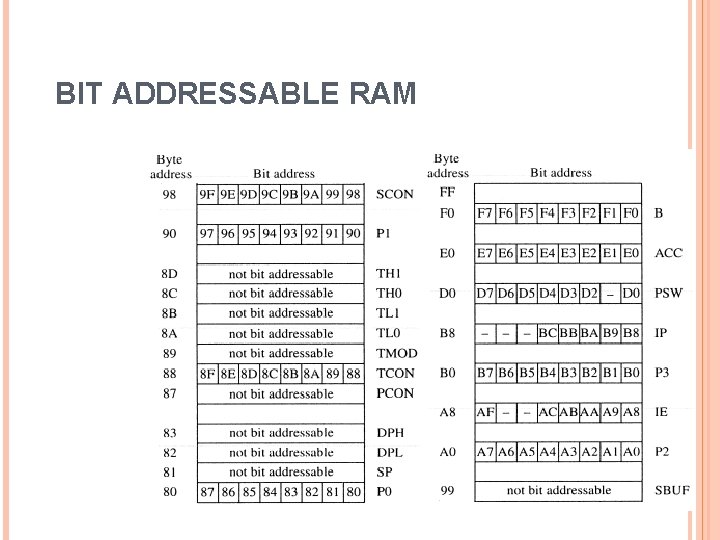

BIT ADDRESSABLE RAM

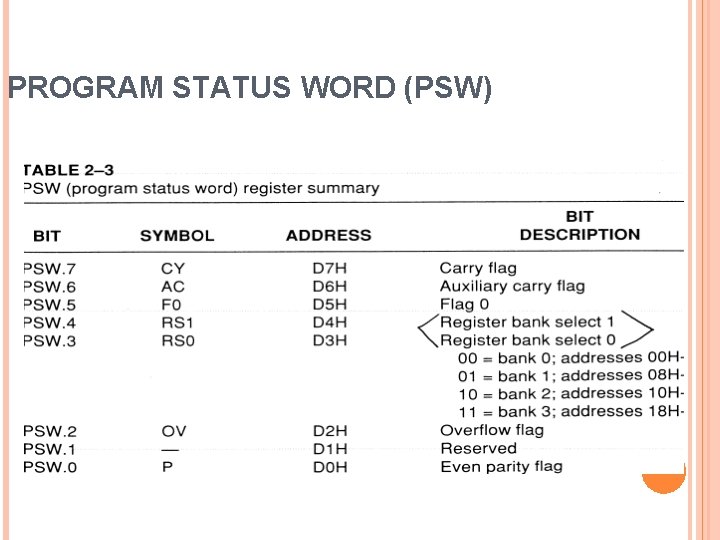

PROGRAM STATUS WORD (PSW)

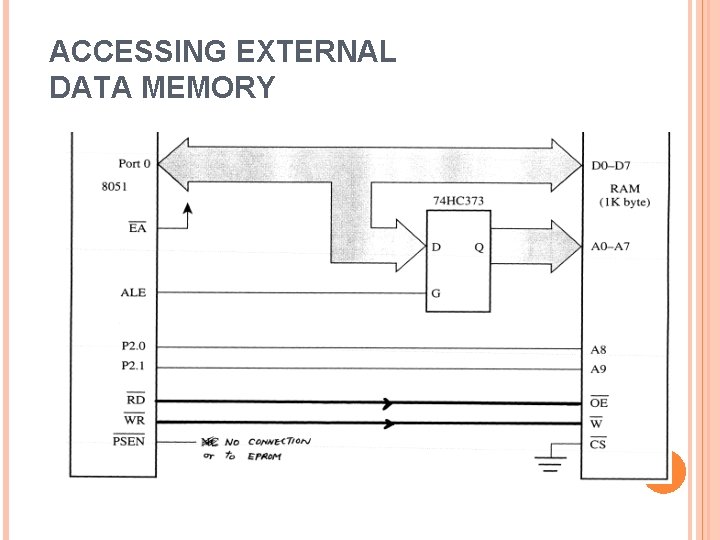

ACCESSING EXTERNAL DATA MEMORY

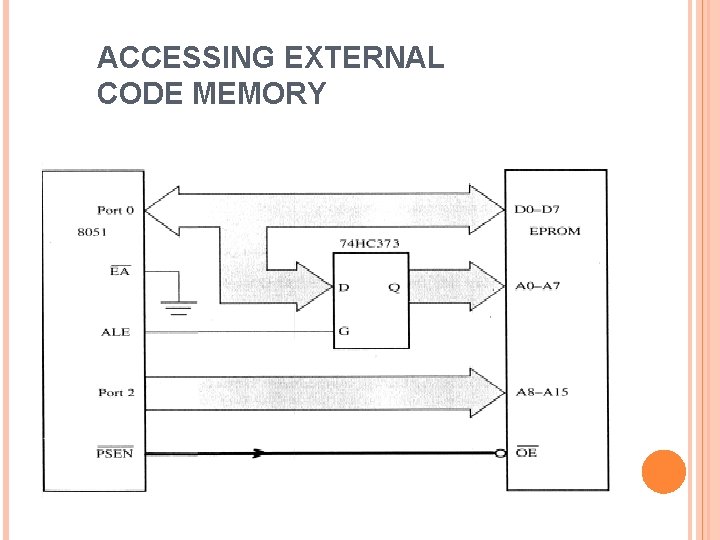

ACCESSING EXTERNAL CODE MEMORY

INTERFACING WITH EXTERNAL ROM

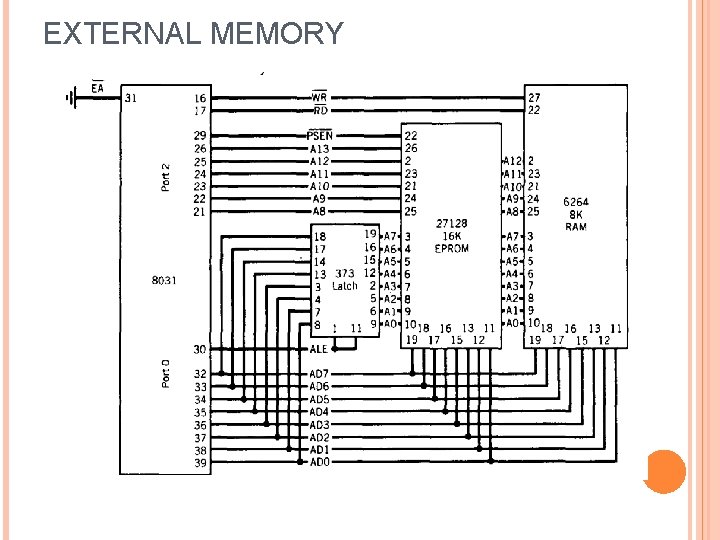

EXTERNAL MEMORY

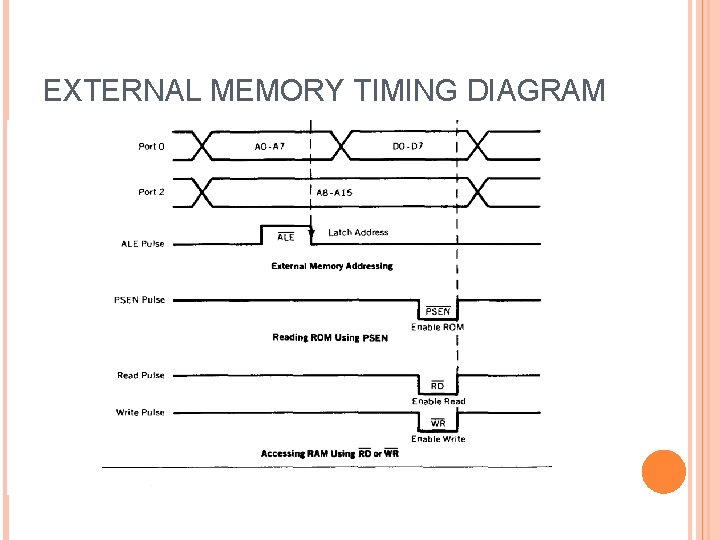

EXTERNAL MEMORY TIMING DIAGRAM

THE EA' (EXTERNAL ACCESS) PIN IS USED TO CONTROL THE INTERNAL OR EXTERNAL MEMORY ACCESS. THE SIGNAL 0 IS FOR EXTERNAL MEMORY ACCESS AND SIGNAL 1 FOR INTERNAL MEMORY ACCESS. THE PSEN' (PROGRAM STORE ENABLE) IS FOR READING EXTERNAL CODE MEMORY WHEN IT IS LOW (0) AND EA IS ALSO 0. THE ALE (ADDRESS LATCH ENABLE) ACTIVATES THE PORT 0 JOINED WITH PORT 2 TO PROVIDE 16 BIT EXTERNAL ADDRESS BUS TO ACCESS THE EXTERNAL MEMORY. THE ALE MULTIPLEXES THE P 0: ALE=1 FOR LATCHING ADDRESS ON P 0 AS A 0 -A 7 IN THE 16 BIT ADDRESS BUSS, ALE=0 FOR LATCHING P 0 AS DATA I/O. P 0. X IS NAMED ADX BECAUSE P 0 IS MULTIPLEXED FOR ADDRESS BUS AND DATA BUS AT DIFFERENT CLOCK TIME. WR' PROVIDES THE SIGNAL TO WRITE EXTERNAL DATA MEMORY RD' PROVIDES THE SIGNAL TO READ EXTERNAL DATA AND CODE MEMORY.

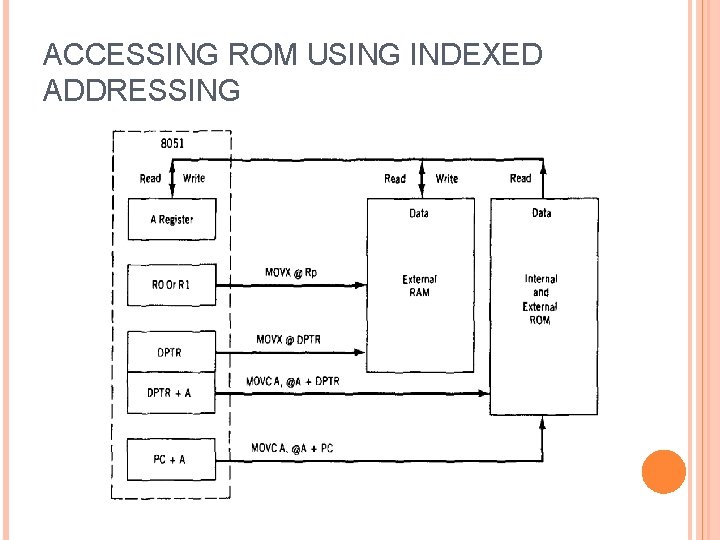

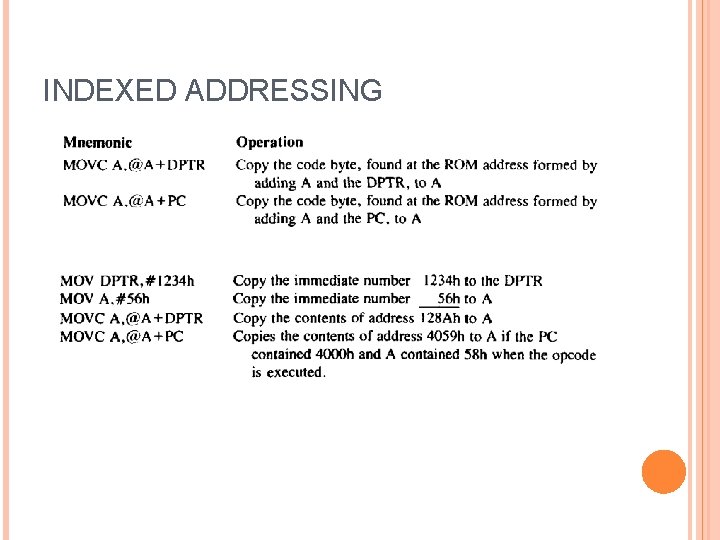

ACCESSING ROM USING INDEXED ADDRESSING

INDEXED ADDRESSING

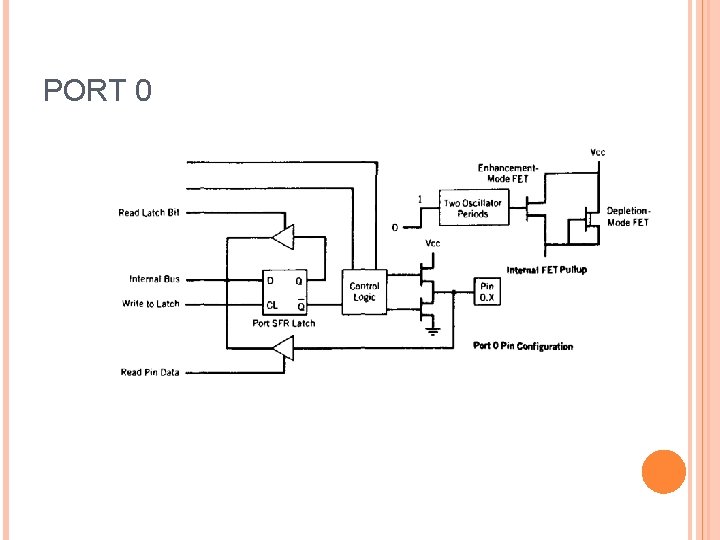

PORT 0

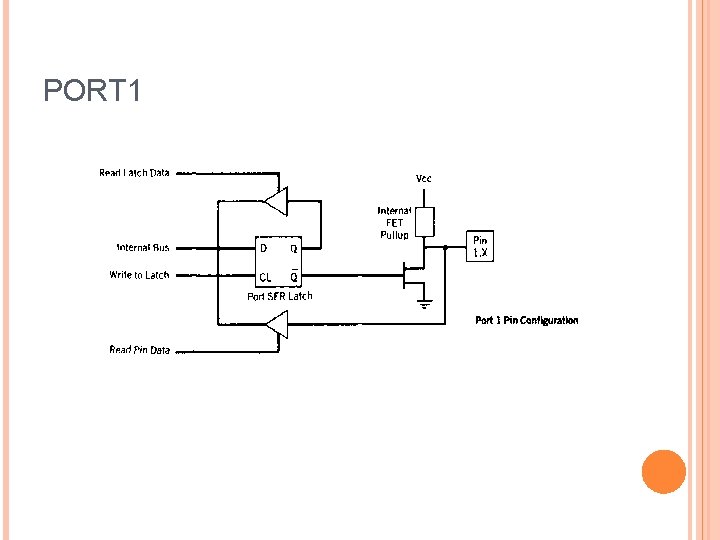

PORT 1

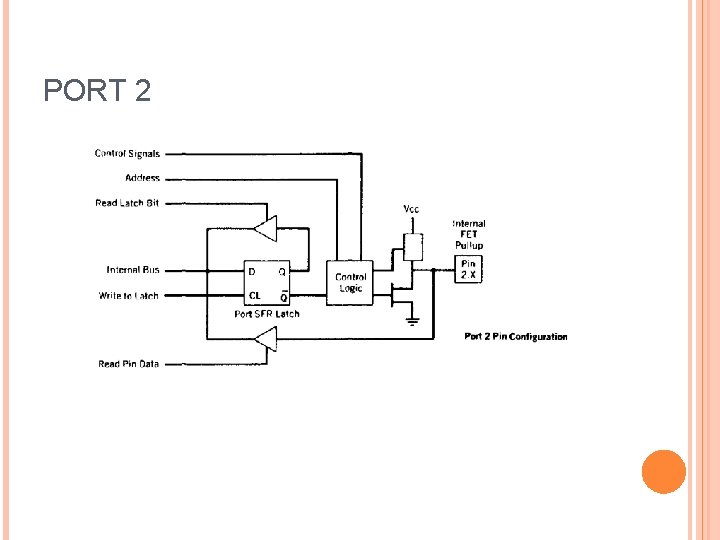

PORT 2

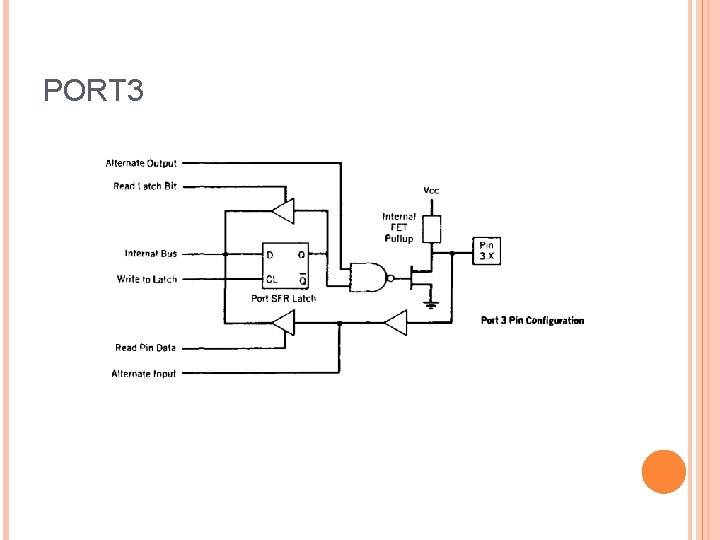

PORT 3

There are 4 8 -bit ports: P 0, P 1, P 2 and P 3. All of them are dual purpose ports except P 1 which is only used for I/O. The following diagram shows a single bit in an 8051 I/O port. When a program writes a one byte value to a port or a single bit value to a bit of a port, assigning the value to the port as follows: P 1 = 0 x 12; or P 1^2=1; P 1 represents the 8 bits of port 1 and P 1^2 is the pin #2 of the port 1 of 8051 defined in the reg 51. h of C 51, a C dedicated for 8051 family. When data is written to the port pin, it first appears on the latch input (D) and is then passed through to the output (Q) and through an inverter to the Field Effect Transistor (FET). If you write a logic 0 to the port pin(DFF Q=0), it is inverted to logic 1 and turns on the FET gate. It makes the port pin connected to ground (logic 0). If logic 1 is written to the port pin(DFF Q=1), , then it is inverted to a logic 0 and turns off the FET gate. Therefore the pin is at logic 1 because it is connected to high.

PORT P 1 (Pins 1 to 8): The port P 1 is a port dedicated for general I/O purpose. The other ports P 0, P 2 and P 3 have dual roles in addition to their basic I/O function. PORT P 0 (pins 32 to 39): When the external memory access is required then Port P 0 is multiplexed for address bus and data bus that can be used to access external memory in conjunction with port P 2. P 0 acts as A 0 -A 7 in address bus and D 0 -D 7 for port data. It can be used for general purpose I/O if no external memory presents. PORT P 2 (pins 21 to 28): Similar to P 0, the port P 2 can also play a role (A 8 -A 15) in the address bus in conjunction with PORT P 0 to access external memory.

PORT P 3 (Pins 10 to 17): In addition to acting as a normal I/O port, P 3. 0 can be used for serial receive input pin(RXD) P 3. 1 can be used for serial transmit output pin(TXD) in a serial port, P 3. 2 and P 3. 3 can be used as external interrupt pins(INT 0’ and INT 1’), P 3. 4 and P 3. 5 are used for external counter input pins(T 0 and T 1), P 3. 6 and P 3. 7 can be used as external data memory write and read control signal pins(WR’ and RD’)read and write pins for memory access.

- Slides: 28