MICROCONTROLADORE S MICROCONTROLADORES Introduccin Arquitectura Memoria IO Digital

- Slides: 133

MICROCONTROLADORE S

MICROCONTROLADORES Introducción Arquitectura Memoria I/O Digital Interrupciones I/O Analógica Timers/PWM Interfaces y Otros Periféricos

INTRODUCCIÓN Uso de los microcontroladores Microondas, Lavarropas, Televisores, . . . Automóviles, aviones, barcos Teléfonos Automatización industrial Pequeños dispositivos ad-hoc . . .

INTRODUCCIÓN Ejemplo. Se quiere: Leer periódicamente una temperatura Prender y apagar un calefactor Mostrar en un display la temperatura Permitir al usuario ajustar la temperatura Posibilidad de actualizar la funcionalidad con un interfase serie

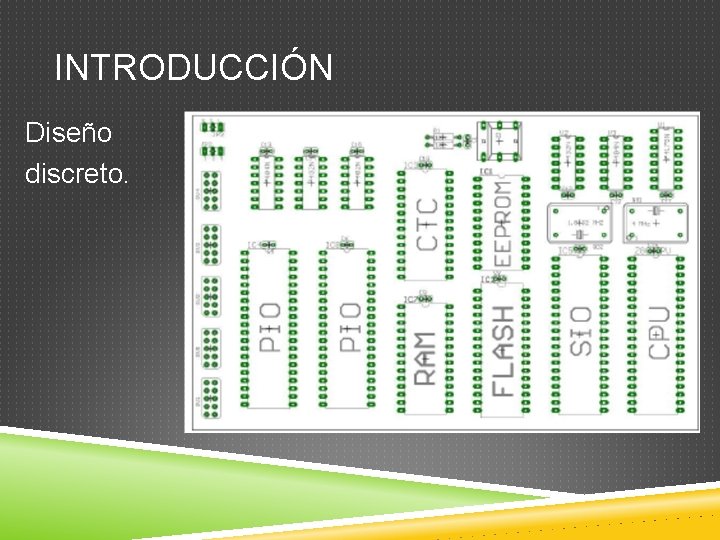

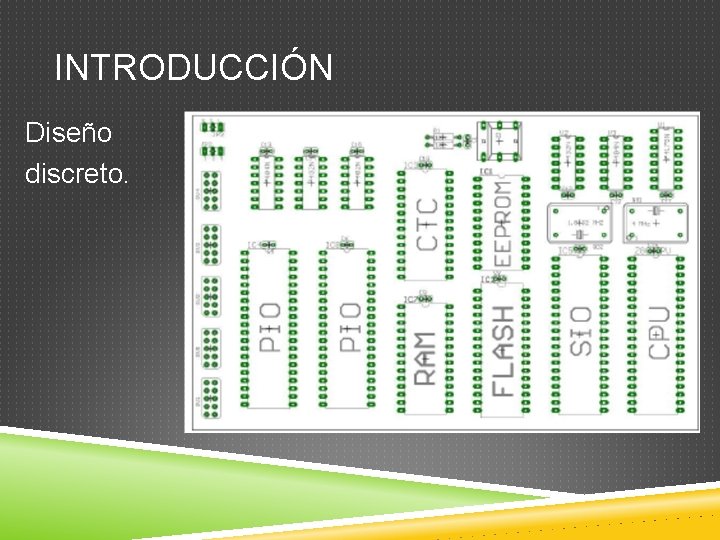

INTRODUCCIÓN Diseño discreto. Se requiere: Un microprocesador 20 líneas de I/O (2 chips de 16 c/u) 1 Interfaz serie (1 chip) 1 Timer (1 chip) Memoria SRAM (para variables) Memoria Flash (para programa) Memoria EEPROM (para constantes)

INTRODUCCIÓN Diseño discreto.

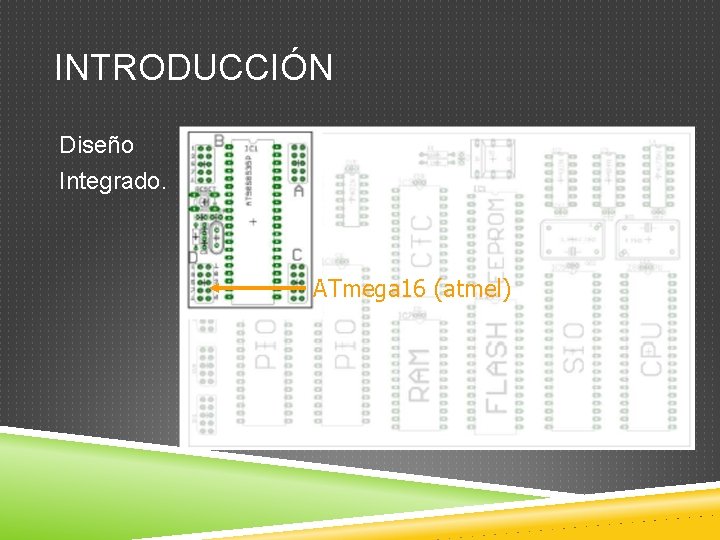

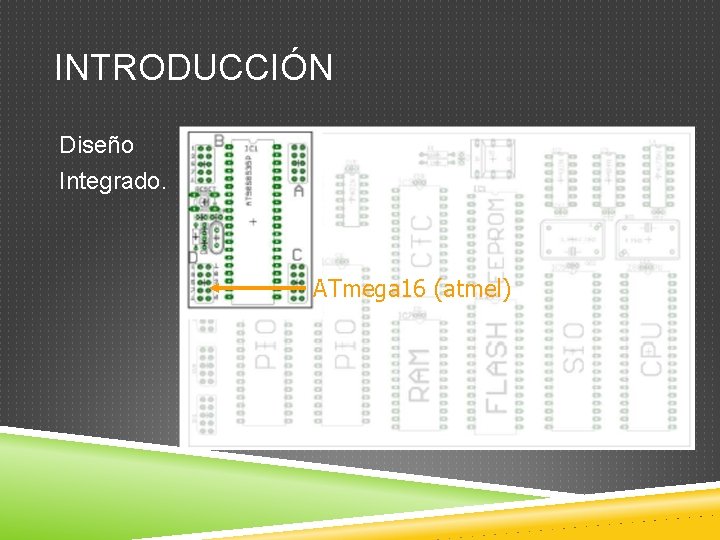

INTRODUCCIÓN Diseño Integrado. ATmega 16 (atmel)

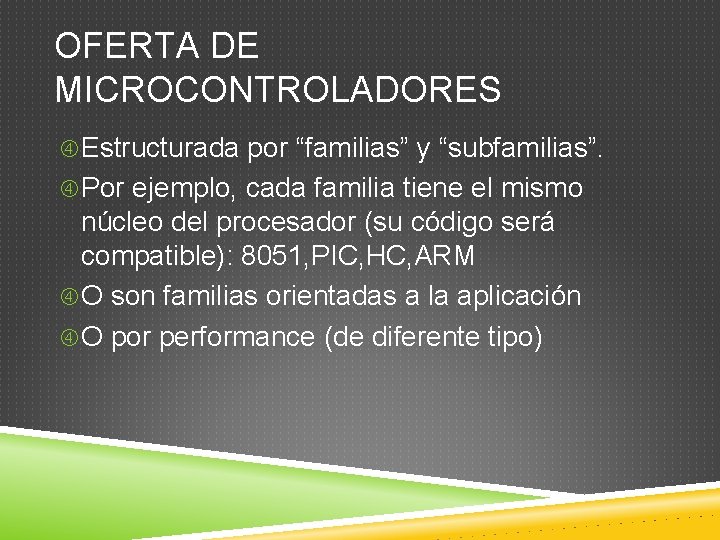

OFERTA DE MICROCONTROLADORES Estructurada por “familias” y “subfamilias”. Por ejemplo, cada familia tiene el mismo núcleo del procesador (su código será compatible): 8051, PIC, HC, ARM O son familias orientadas a la aplicación O por performance (de diferente tipo)

INTRODUCCIÓN

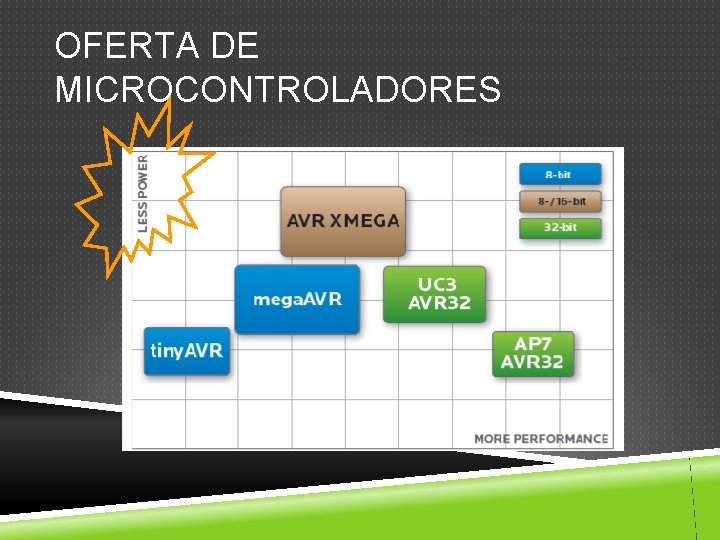

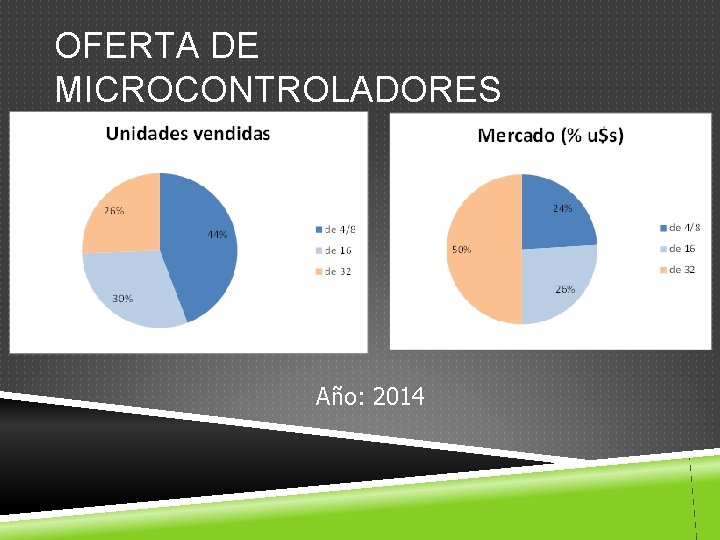

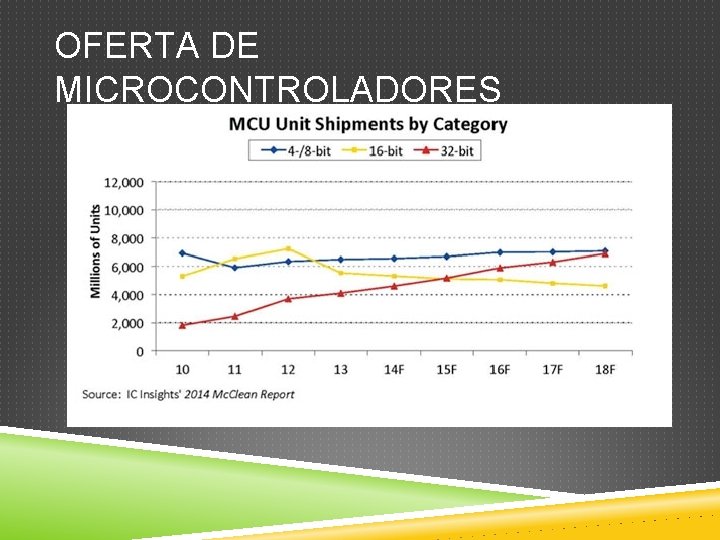

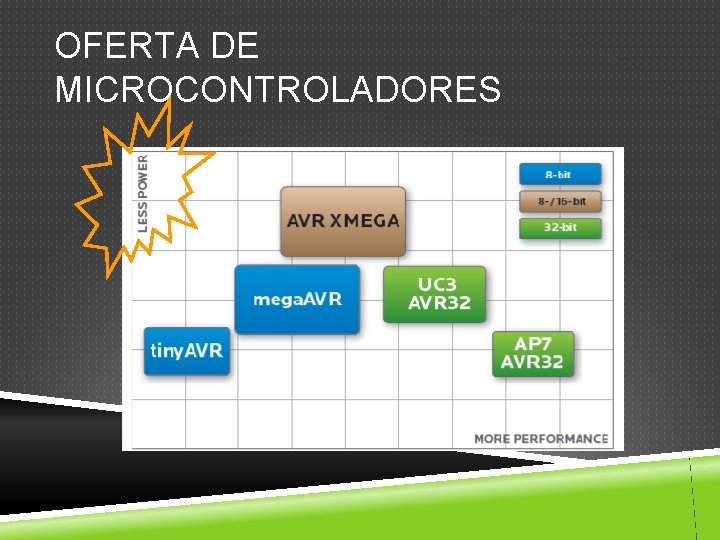

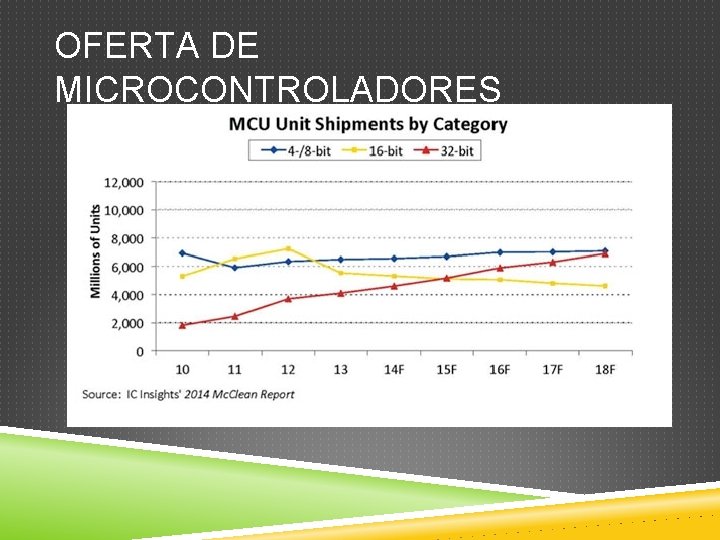

OFERTA DE MICROCONTROLADORES

OFERTA DE MICROCONTROLADORES

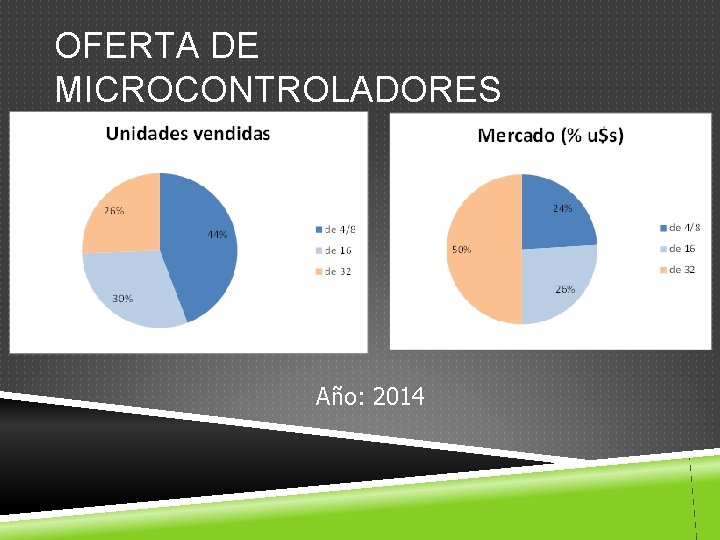

OFERTA DE MICROCONTROLADORES Año: 2014

OFERTA DE MICROCONTROLADORES

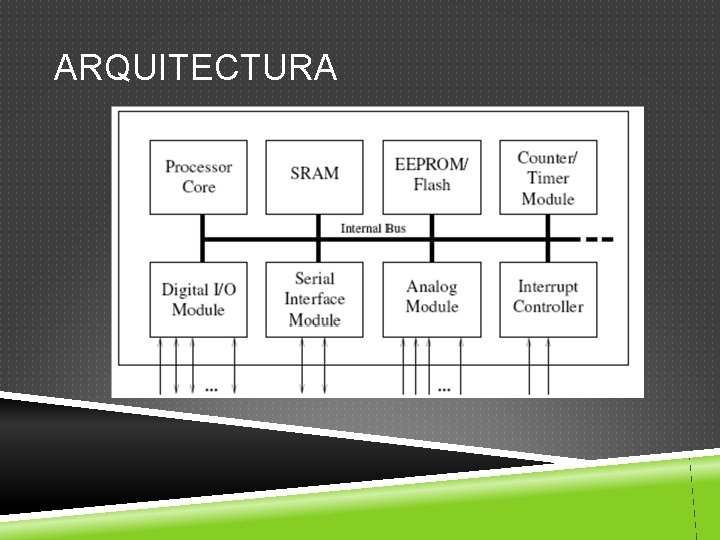

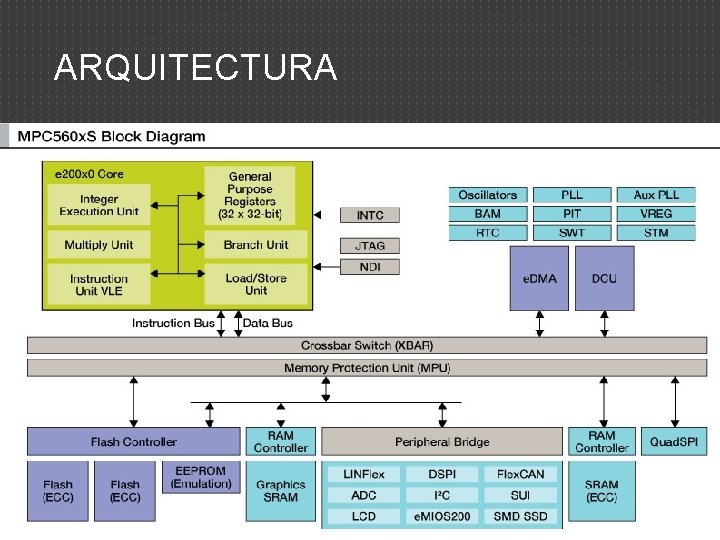

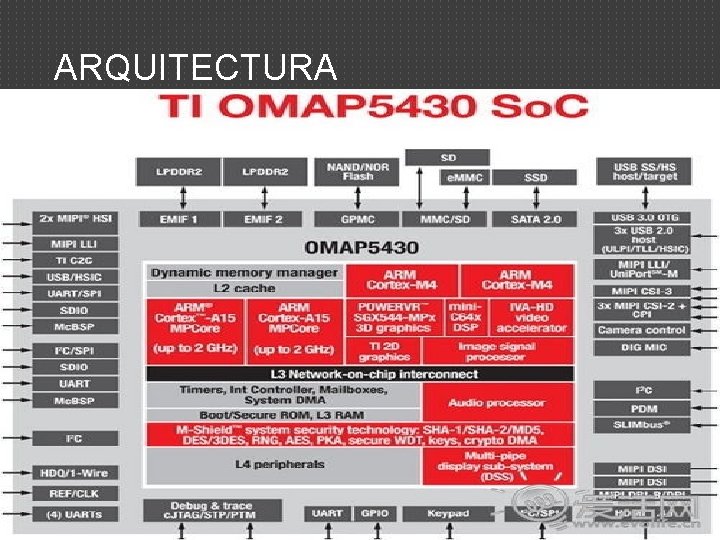

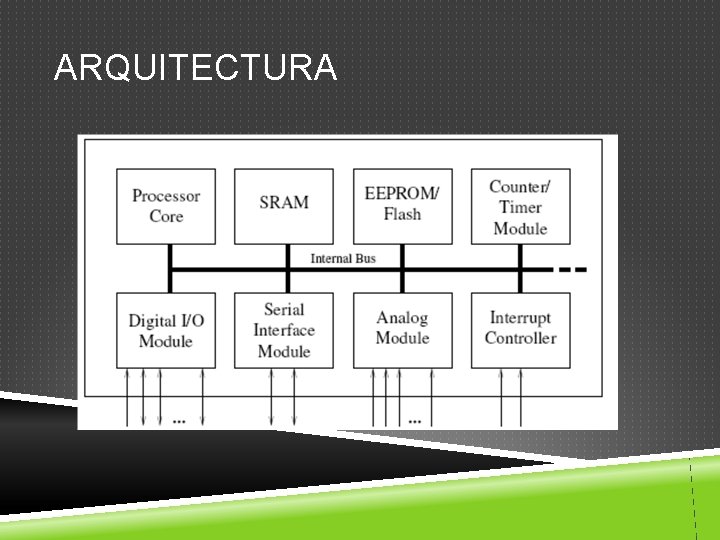

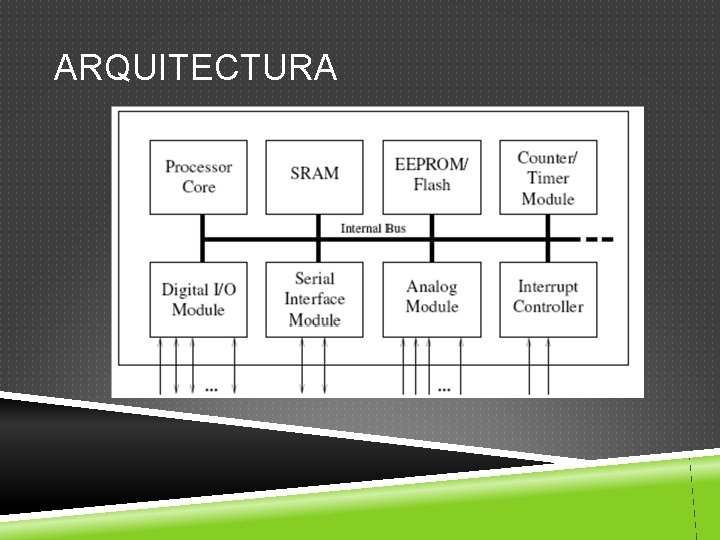

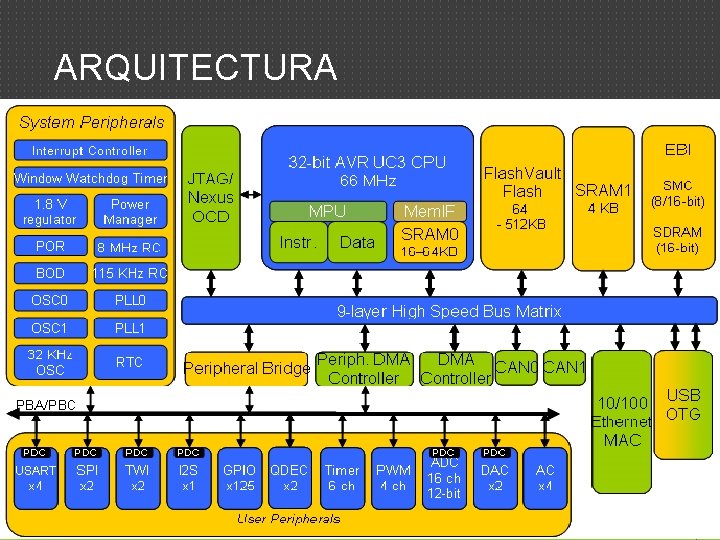

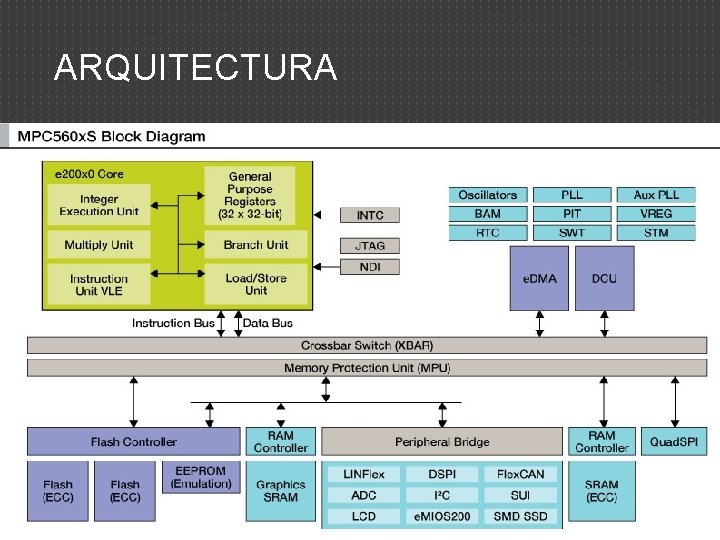

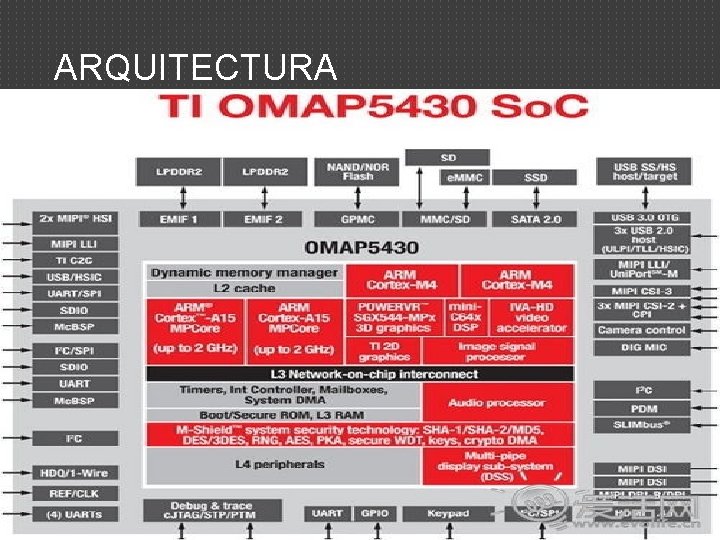

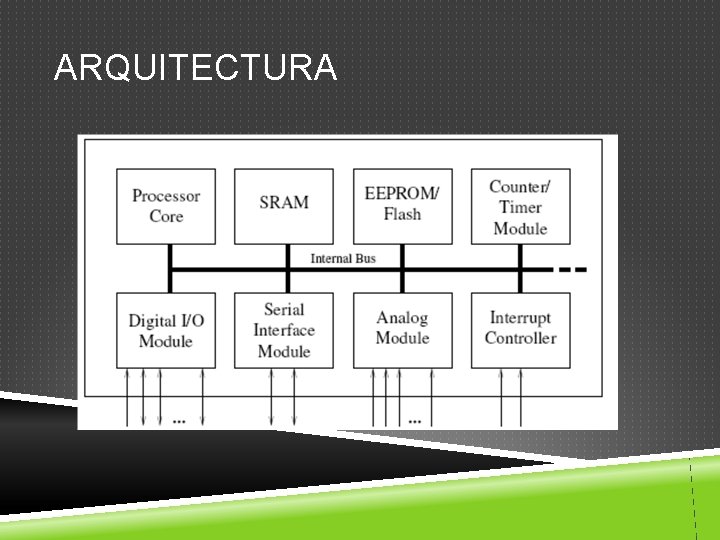

ARQUITECTURA

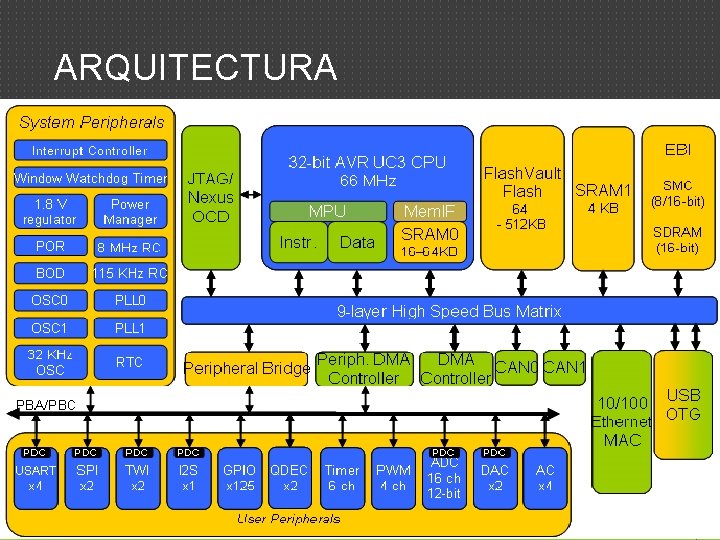

ARQUITECTURA

ARQUITECTURA

ARQUITECTURA

ARQUITECTURA

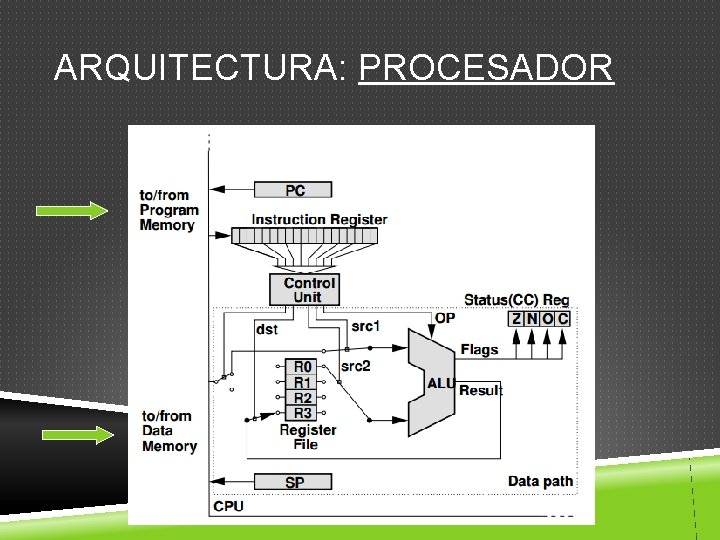

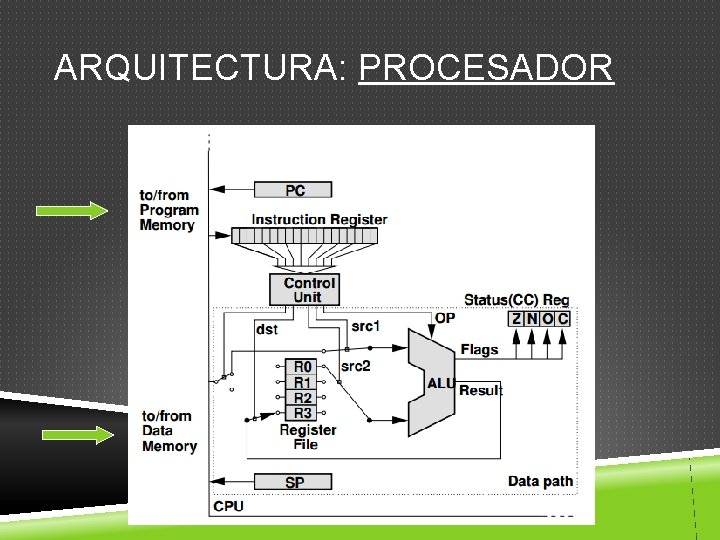

ARQUITECTURA: PROCESADOR

ARQUITECTURA Von Neuman vs. Hardvard CISC vs. RISC Tamaño/variedad de las instrucciones Velocidad: clock; 8/16/32 bits

SISTEMAS EMBEBIDOS Dos alternativas: “BARE METAL” Sobre un Sistema Operativo básico (administrador de tareas) de tiempo real (QNX, Free. RTOS, …) genérico (Linux, Android, Windows, …)

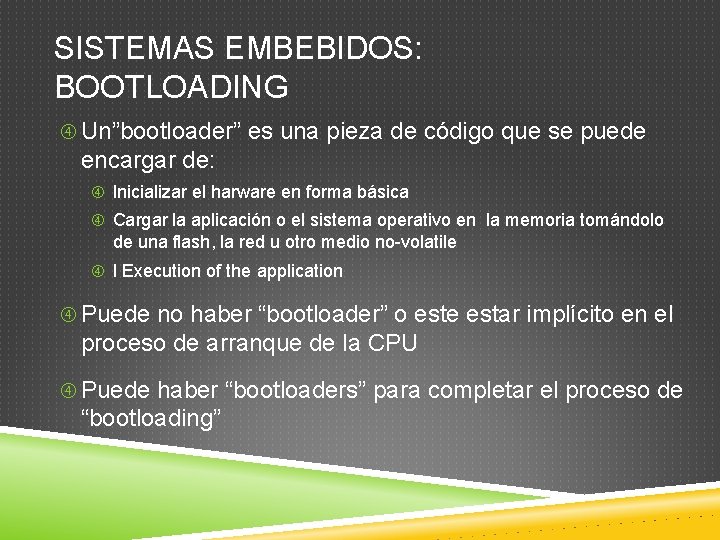

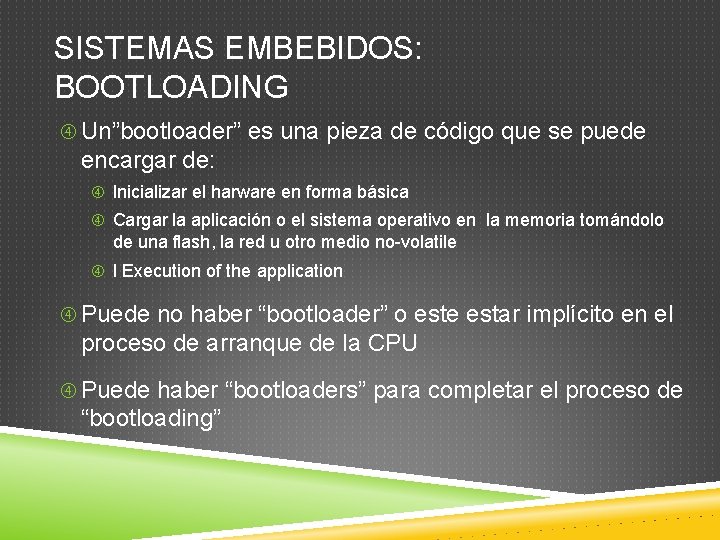

SISTEMAS EMBEBIDOS: BOOTLOADING Un”bootloader” es una pieza de código que se puede encargar de: Inicializar el harware en forma básica Cargar la aplicación o el sistema operativo en la memoria tomándolo de una flash, la red u otro medio no-volatile I Execution of the application Puede no haber “bootloader” o este estar implícito en el proceso de arranque de la CPU Puede haber “bootloaders” para completar el proceso de “bootloading”

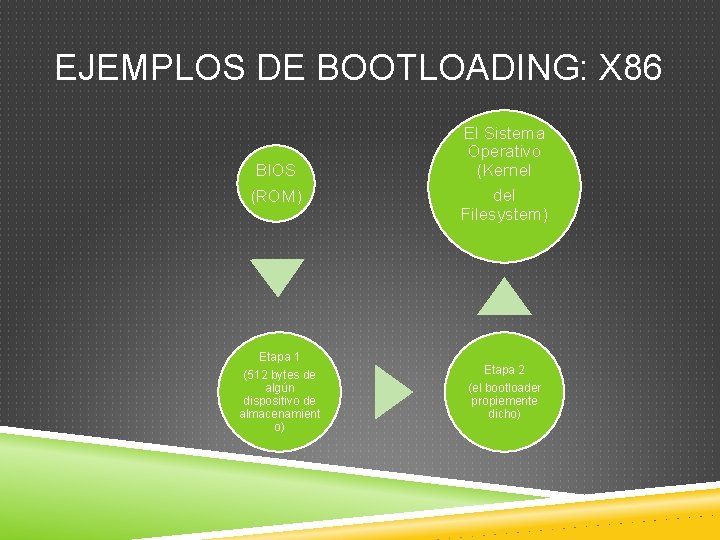

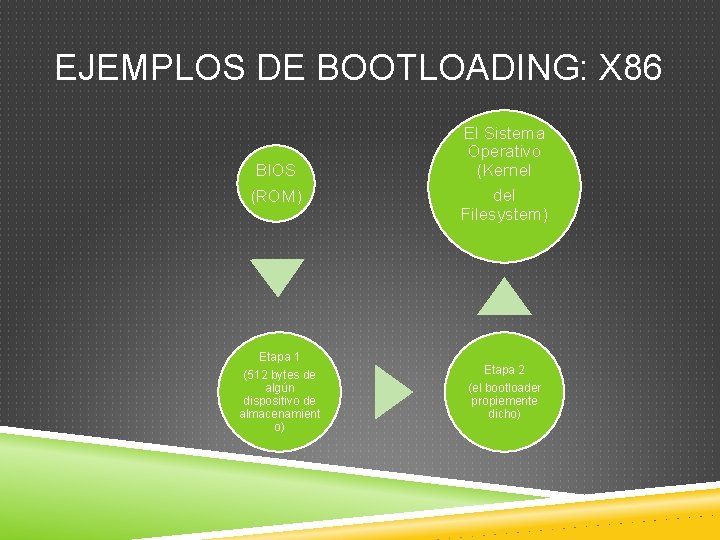

EJEMPLOS DE BOOTLOADING: X 86 BIOS (ROM) Etapa 1 (512 bytes de algún dispositivo de almacenamient o) El Sistema Operativo (Kernel del Filesystem) Etapa 2 (el bootloader propiemente dicho)

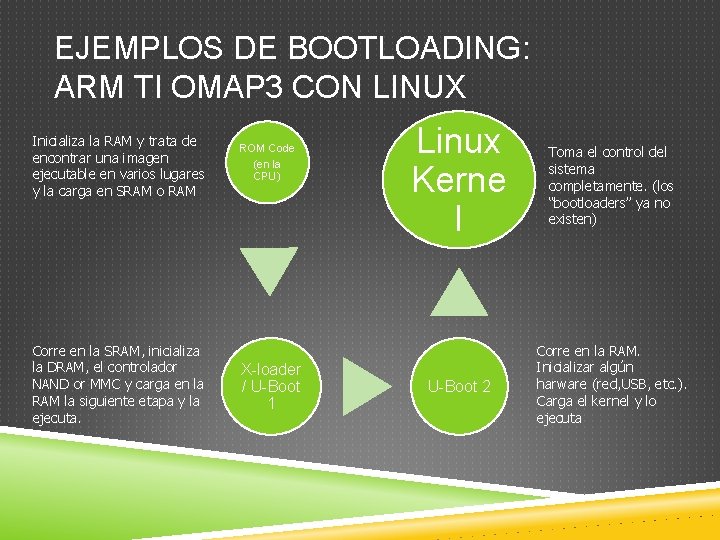

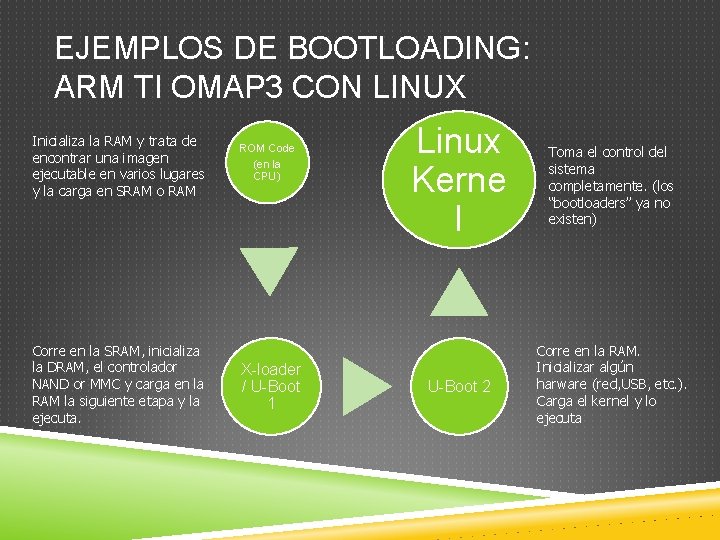

EJEMPLOS DE BOOTLOADING: ARM TI OMAP 3 CON LINUX Inicializa la RAM y trata de encontrar una imagen ejecutable en varios lugares y la carga en SRAM o RAM Corre en la SRAM, inicializa la DRAM, el controlador NAND or MMC y carga en la RAM la siguiente etapa y la ejecuta. ROM Code (en la CPU) X-loader / U-Boot 1 Linux Kerne l Toma el control del sistema completamente. (los “bootloaders” ya no existen) U-Boot 2 Corre en la RAM. Inicializar algún harware (red, USB, etc. ). Carga el kernel y lo ejecuta

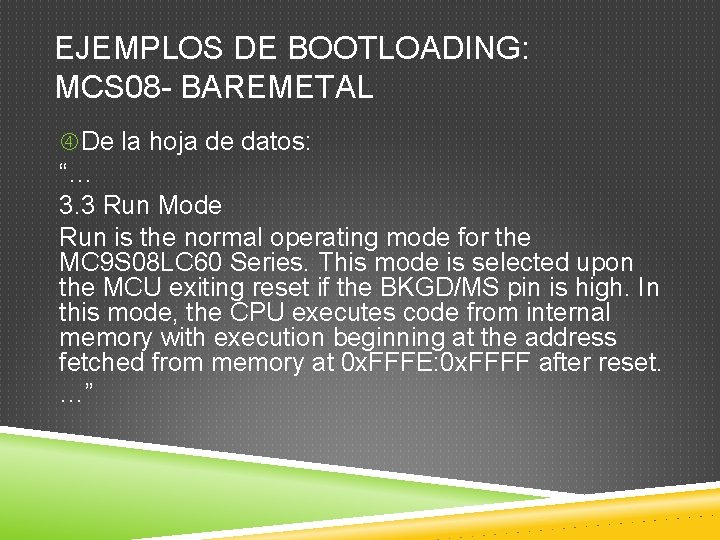

EJEMPLOS DE BOOTLOADING: MCS 08 - BAREMETAL De la hoja de datos: “… 3. 3 Run Mode Run is the normal operating mode for the MC 9 S 08 LC 60 Series. This mode is selected upon the MCU exiting reset if the BKGD/MS pin is high. In this mode, the CPU executes code from internal memory with execution beginning at the address fetched from memory at 0 x. FFFE: 0 x. FFFF after reset. …”

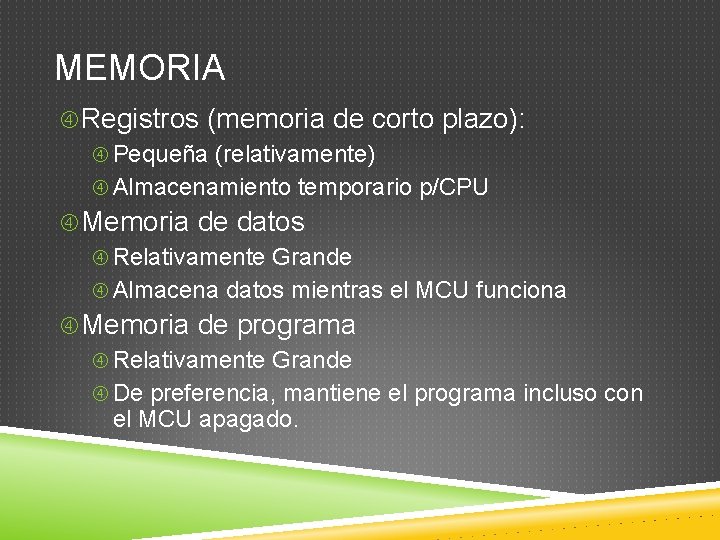

MEMORIA Registros (memoria de corto plazo): Pequeña (relativamente) Almacenamiento temporario p/CPU Memoria de datos Relativamente Grande Almacena datos mientras el MCU funciona Memoria de programa Relativamente Grande De preferencia, mantiene el programa incluso con el MCU apagado.

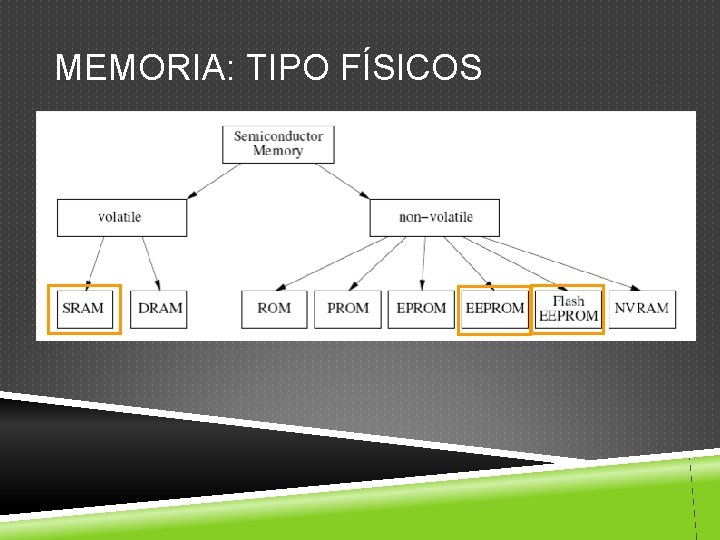

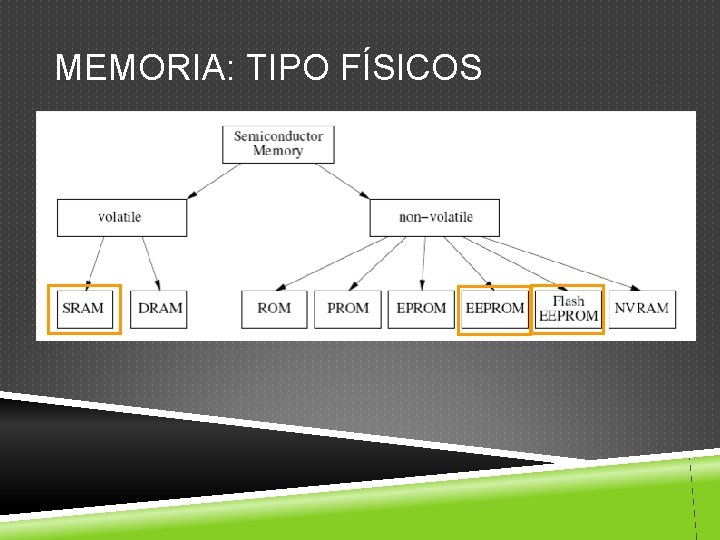

MEMORIA: TIPO FÍSICOS

MEMORIA S/DRAM: sin limite de escrituras EEPROM: 100. 000 ciclos de borrado Flash: 10. 000 ciclos de borrado

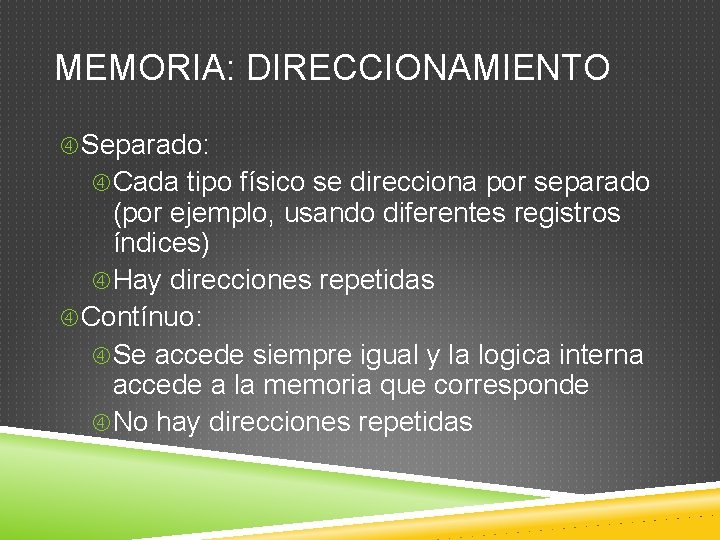

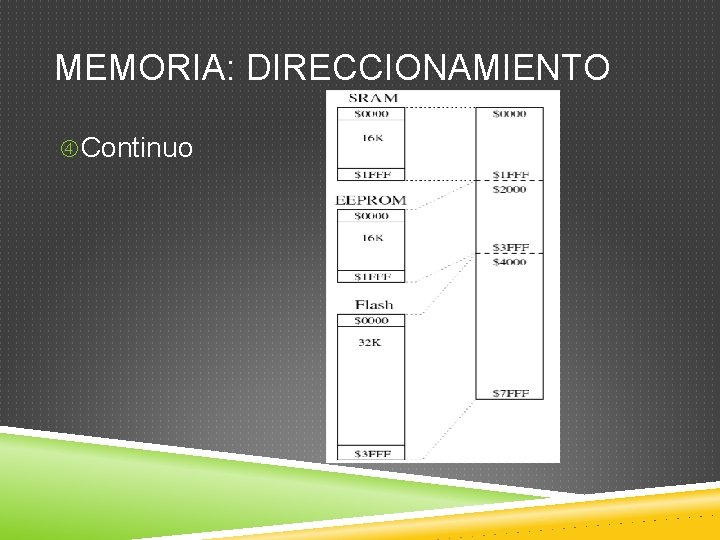

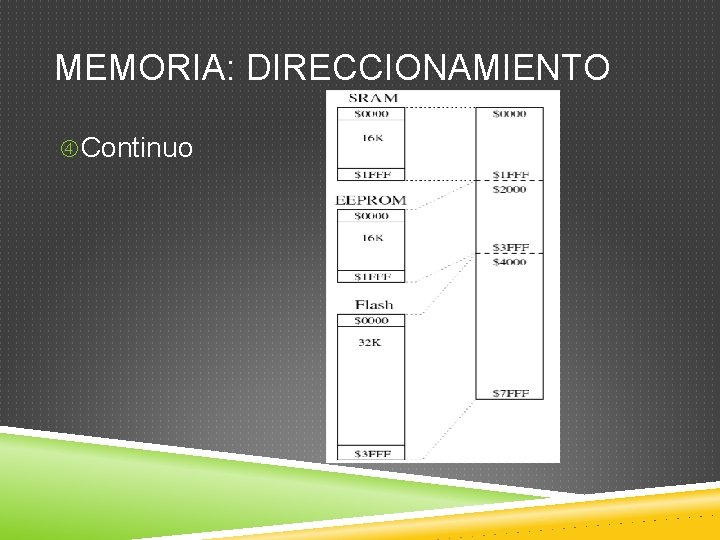

MEMORIA: DIRECCIONAMIENTO Separado: Cada tipo físico se direcciona por separado (por ejemplo, usando diferentes registros índices) Hay direcciones repetidas Contínuo: Se accede siempre igual y la logica interna accede a la memoria que corresponde No hay direcciones repetidas

MEMORIA: DIRECCIONAMIENTO Separado

MEMORIA: DIRECCIONAMIENTO Continuo

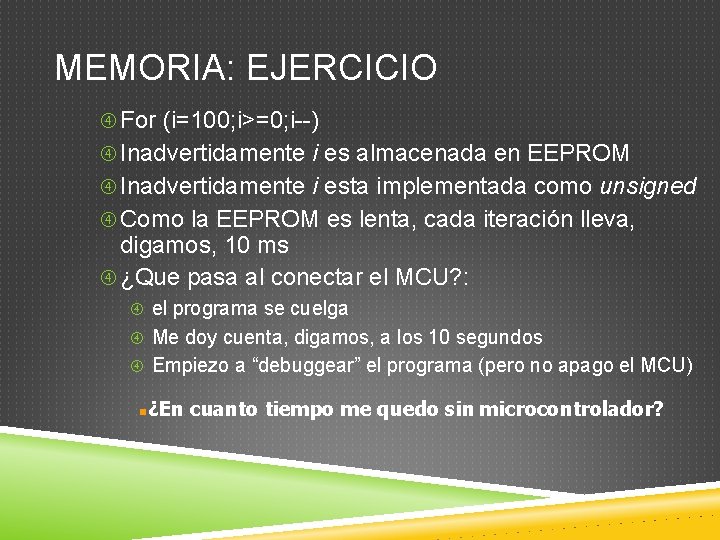

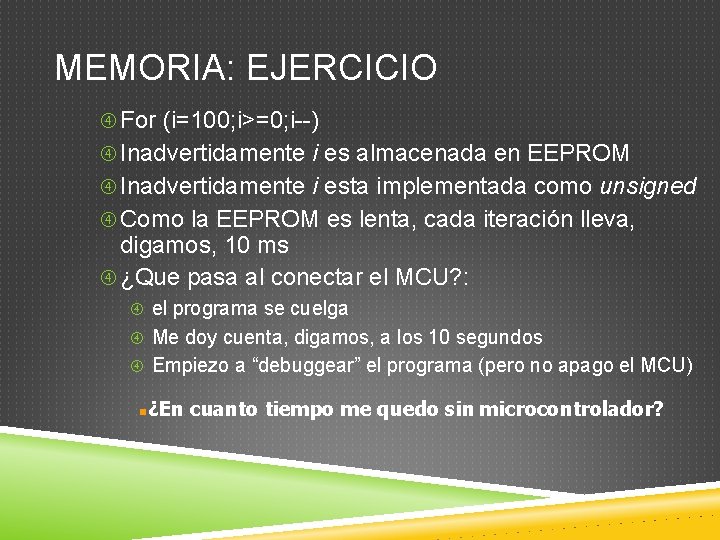

MEMORIA: EJERCICIO For (i=100; i>=0; i--) Inadvertidamente i es almacenada en EEPROM Inadvertidamente i esta implementada como unsigned Como la EEPROM es lenta, cada iteración lleva, digamos, 10 ms ¿Que pasa al conectar el MCU? : el programa se cuelga Me doy cuenta, digamos, a los 10 segundos Empiezo a “debuggear” el programa (pero no apago el MCU) n ¿En cuanto tiempo me quedo sin microcontrolador?

ENTRADA/SALIDA DIGITAL

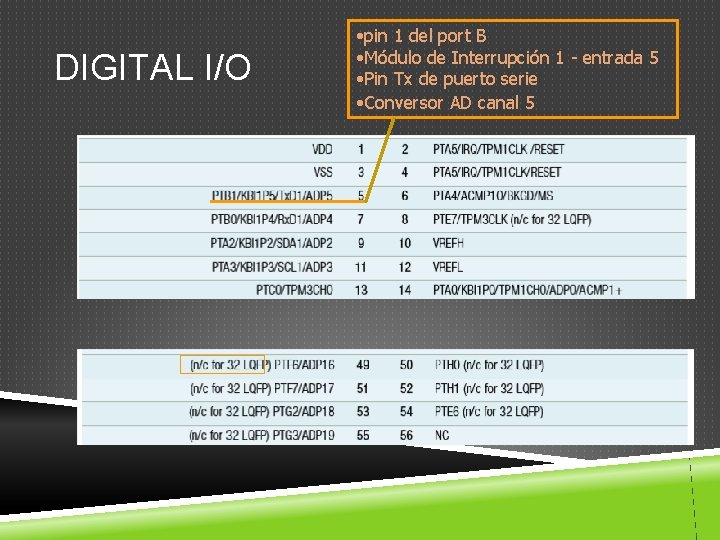

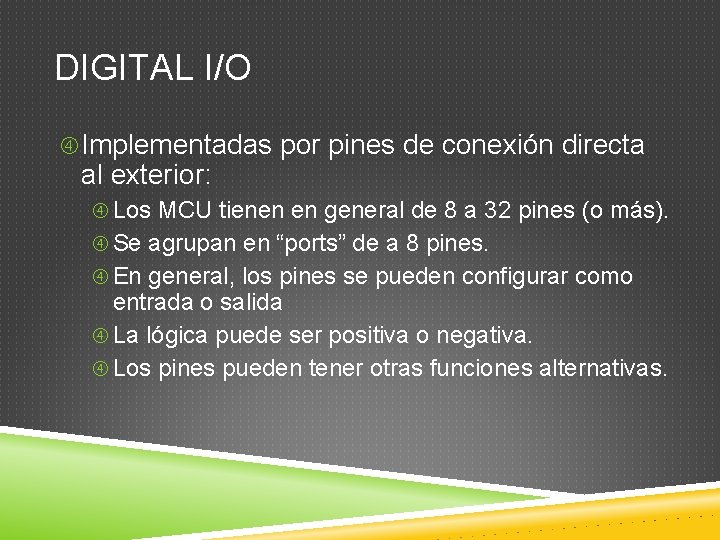

DIGITAL I/O Implementadas por pines de conexión directa al exterior: Los MCU tienen en general de 8 a 32 pines (o más). Se agrupan en “ports” de a 8 pines. En general, los pines se pueden configurar como entrada o salida La lógica puede ser positiva o negativa. Los pines pueden tener otras funciones alternativas.

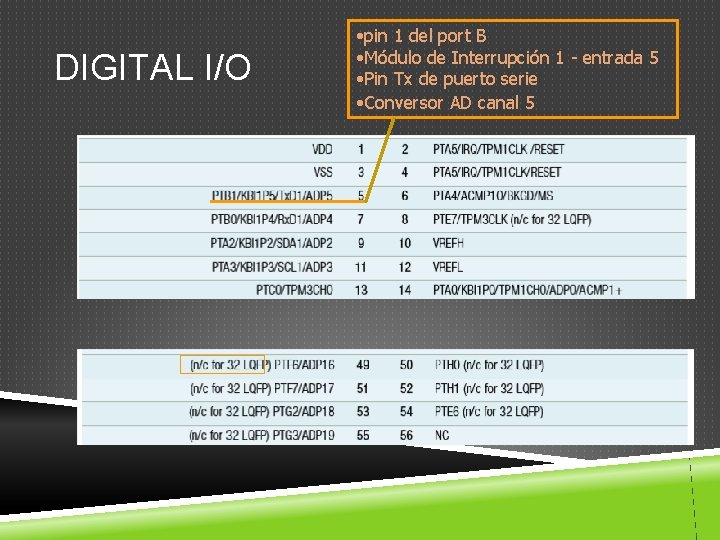

DIGITAL I/O • pin 1 del port B • Módulo de Interrupción 1 - entrada 5 • Pin Tx de puerto serie • Conversor AD canal 5

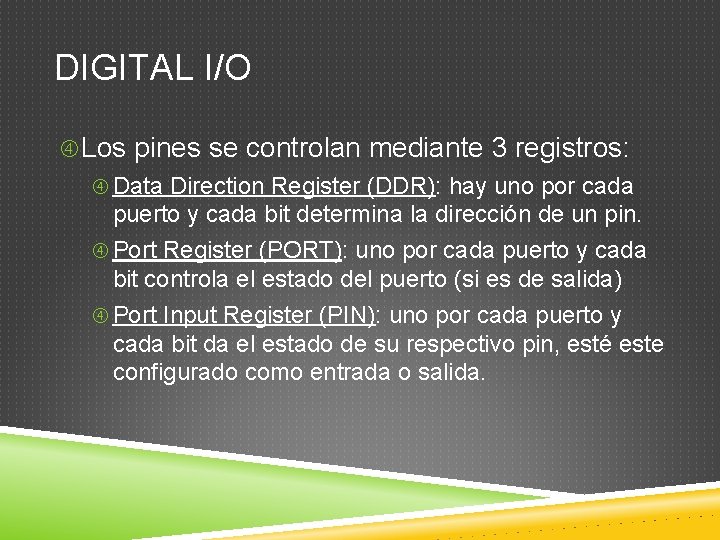

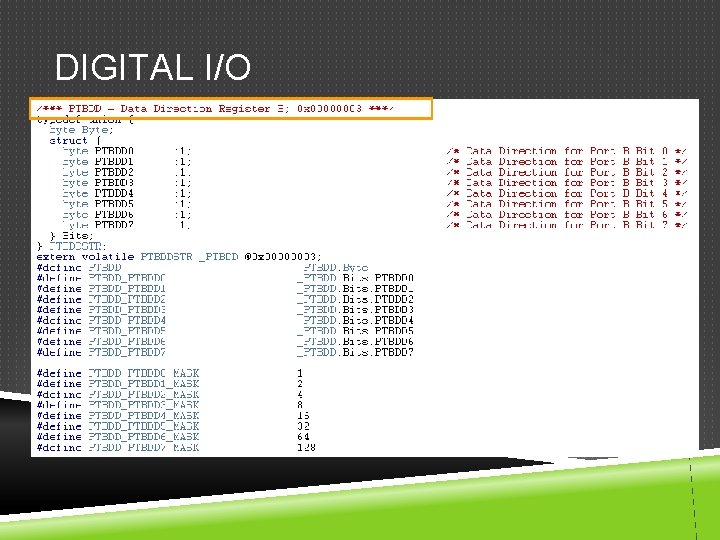

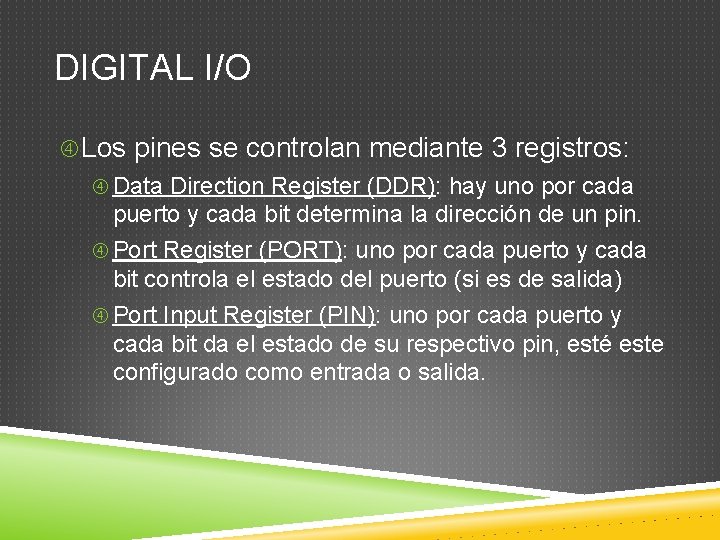

DIGITAL I/O Los pines se controlan mediante 3 registros: Data Direction Register (DDR): hay uno por cada puerto y cada bit determina la dirección de un pin. Port Register (PORT): uno por cada puerto y cada bit controla el estado del puerto (si es de salida) Port Input Register (PIN): uno por cada puerto y cada bit da el estado de su respectivo pin, esté este configurado como entrada o salida.

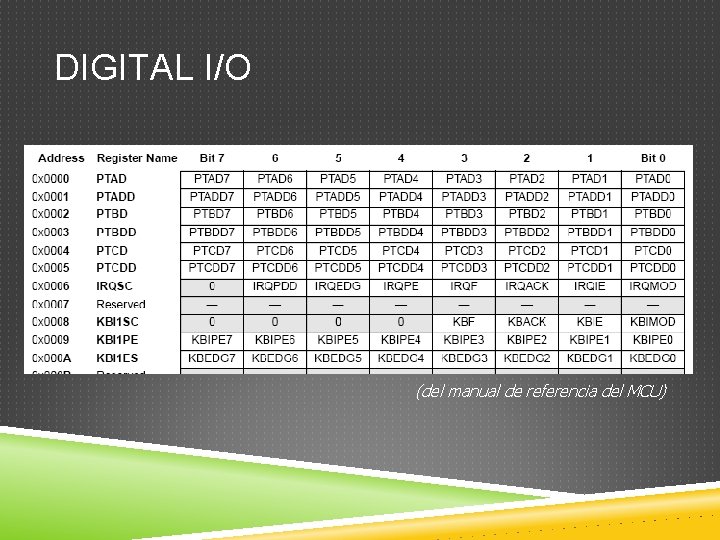

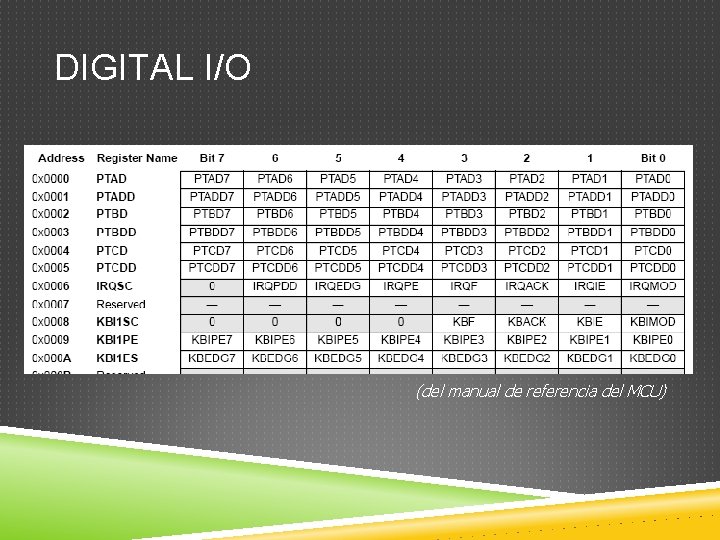

DIGITAL I/O (del manual de referencia del MCU)

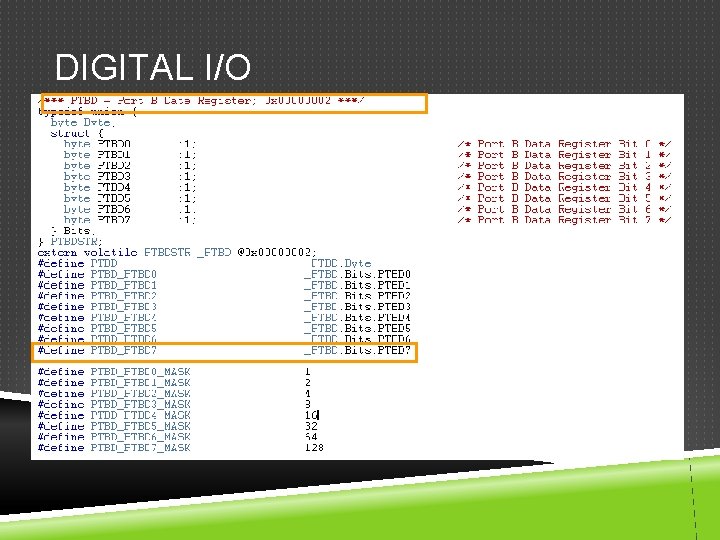

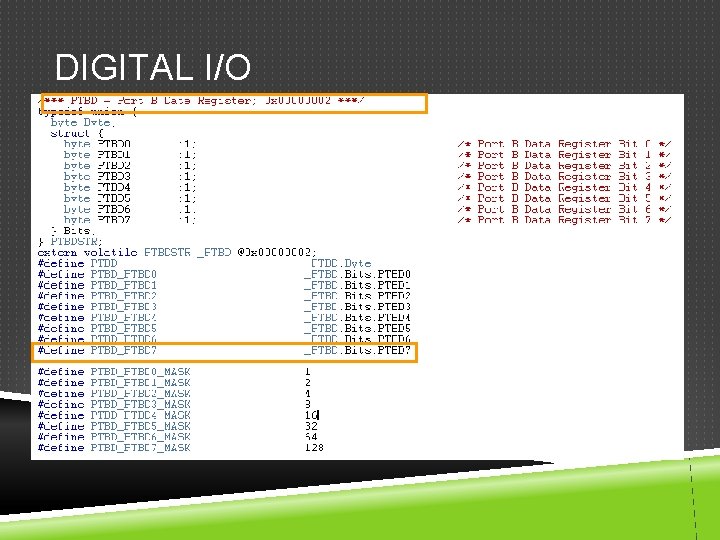

DIGITAL I/O

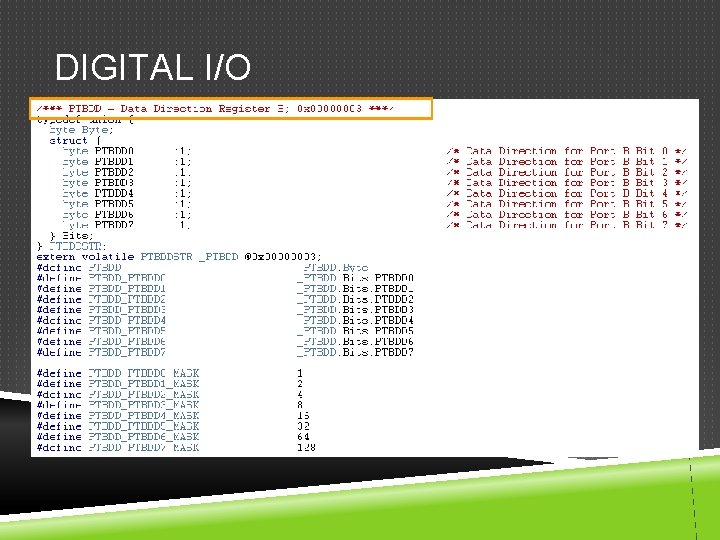

DIGITAL I/O

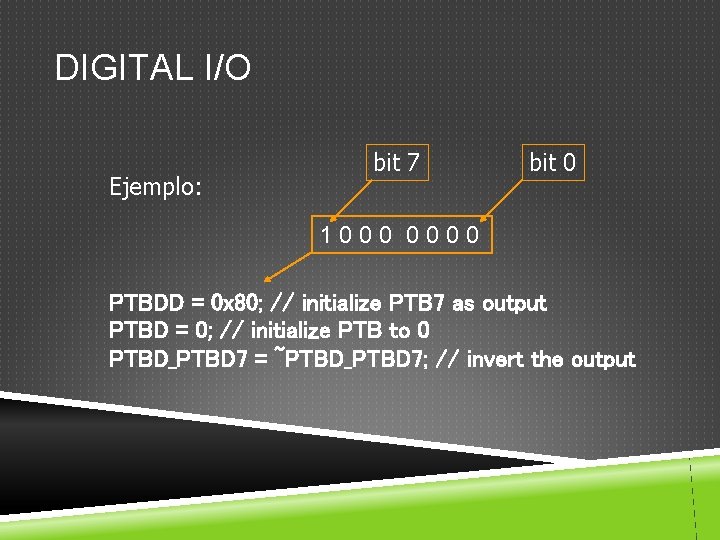

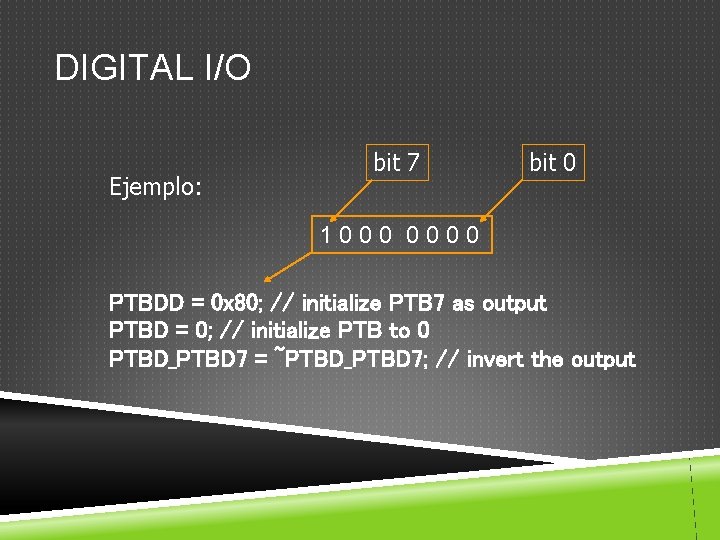

DIGITAL I/O Ejemplo: bit 7 bit 0 1000 0000 PTBDD = 0 x 80; // initialize PTB 7 as output PTBD = 0; // initialize PTB to 0 PTBD_PTBD 7 = ~PTBD_PTBD 7; // invert the output

DIGITAL I/O PORT Register: de preferencia debe escribirse con operaciones de escritura de bit, si estan disponibles Caso contrario usar : Read-Modify-Write con cuidado.

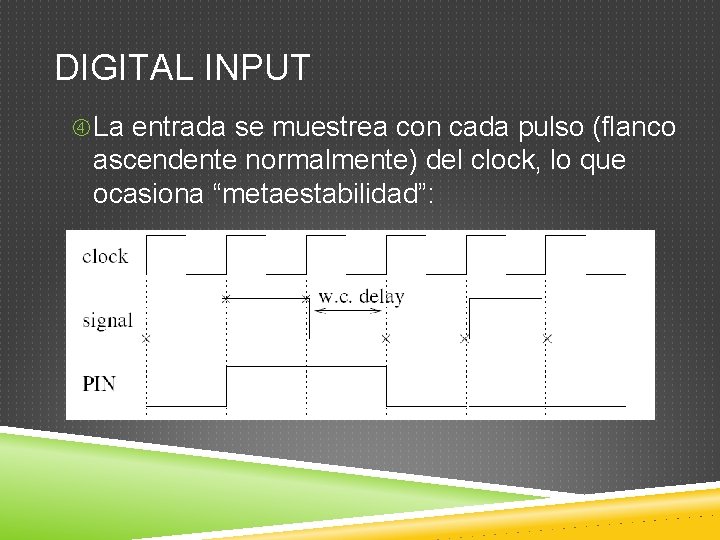

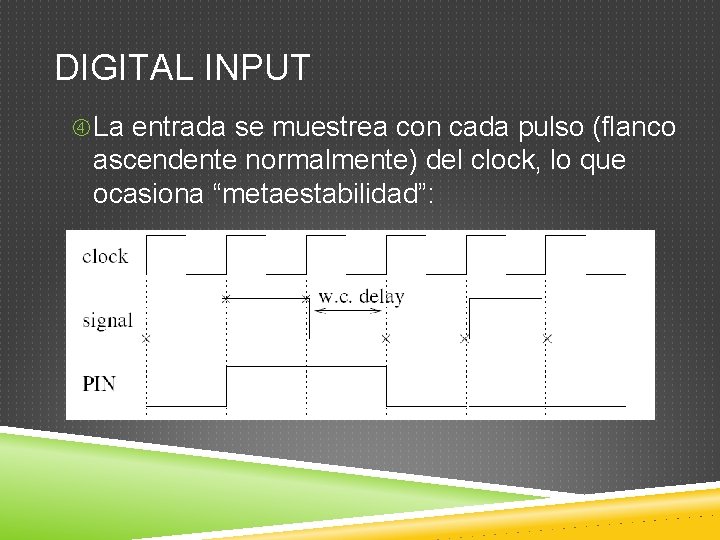

DIGITAL INPUT La entrada se muestrea con cada pulso (flanco ascendente normalmente) del clock, lo que ocasiona “metaestabilidad”:

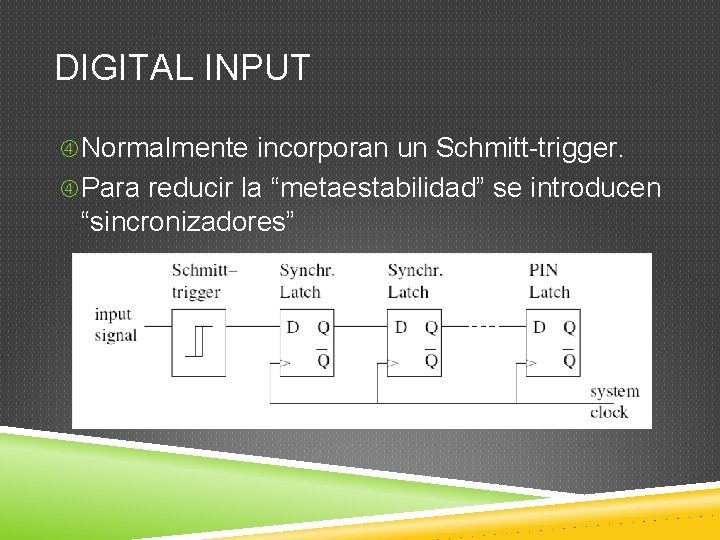

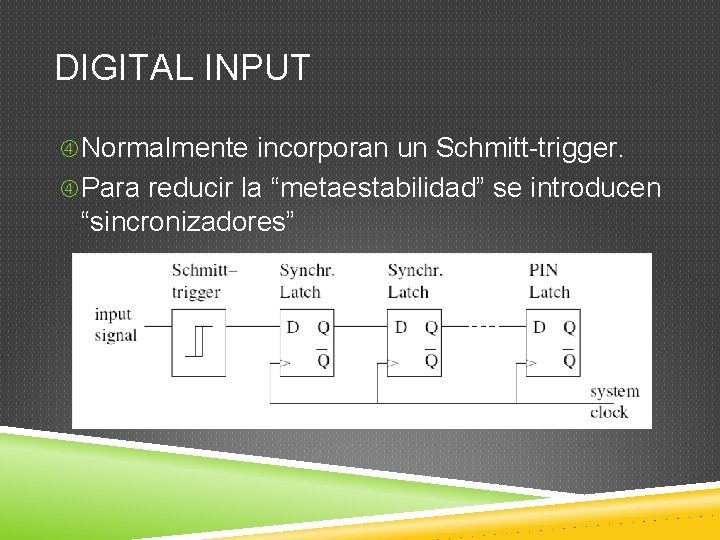

DIGITAL INPUT Normalmente incorporan un Schmitt-trigger. Para reducir la “metaestabilidad” se introducen “sincronizadores”

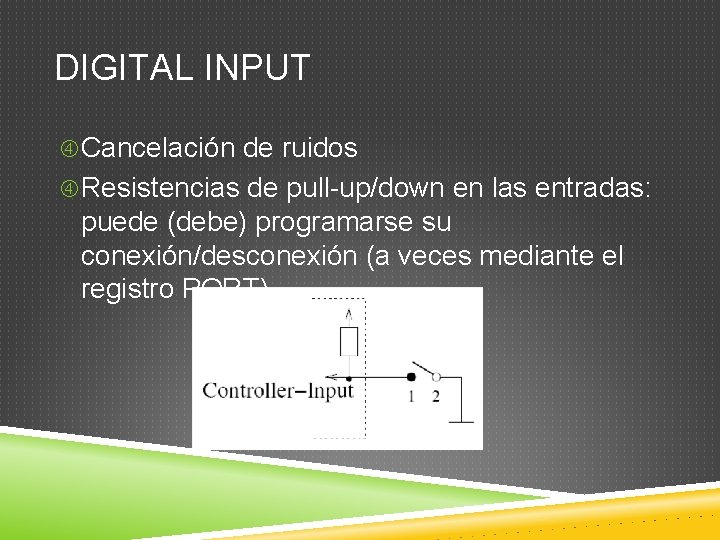

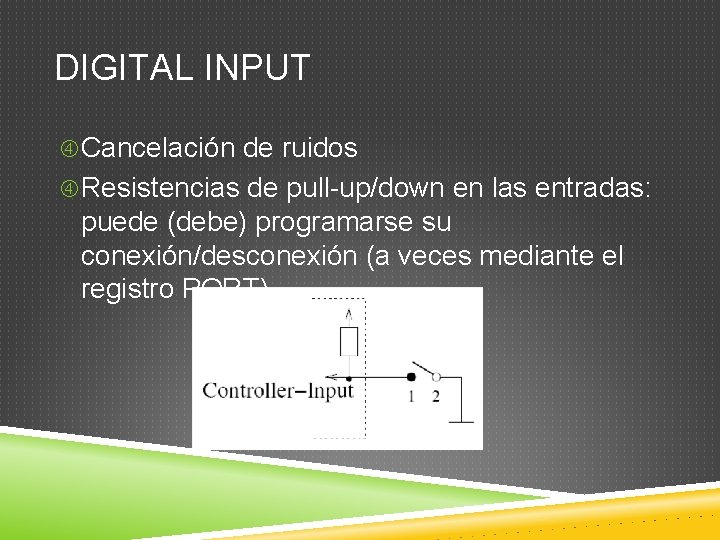

DIGITAL INPUT Cancelación de ruidos Resistencias de pull-up/down en las entradas: puede (debe) programarse su conexión/desconexión (a veces mediante el registro PORT).

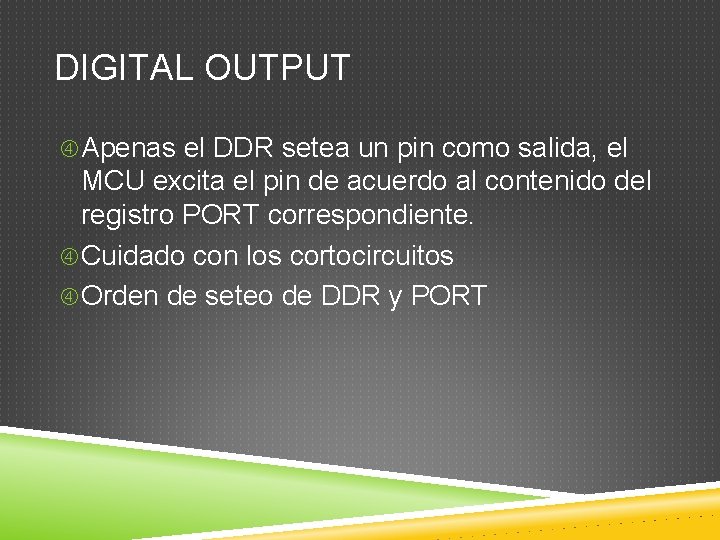

DIGITAL OUTPUT Apenas el DDR setea un pin como salida, el MCU excita el pin de acuerdo al contenido del registro PORT correspondiente. Cuidado con los cortocircuitos Orden de seteo de DDR y PORT

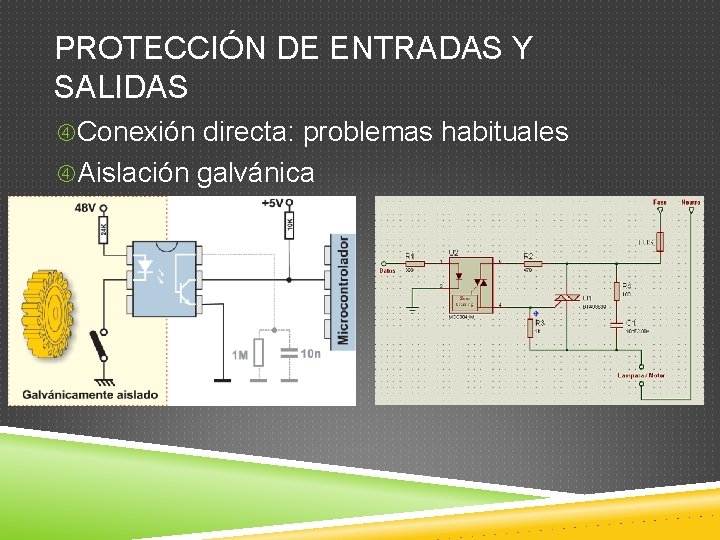

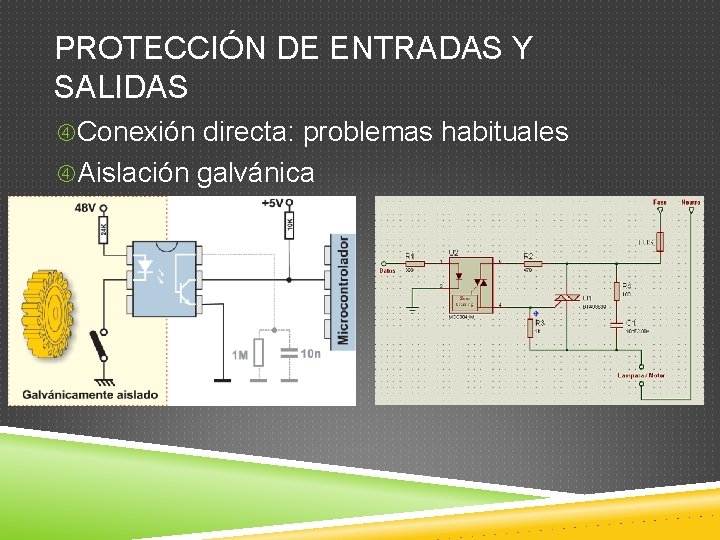

PROTECCIÓN DE ENTRADAS Y SALIDAS Conexión directa: problemas habituales Aislación galvánica

INTERRUPCIONES

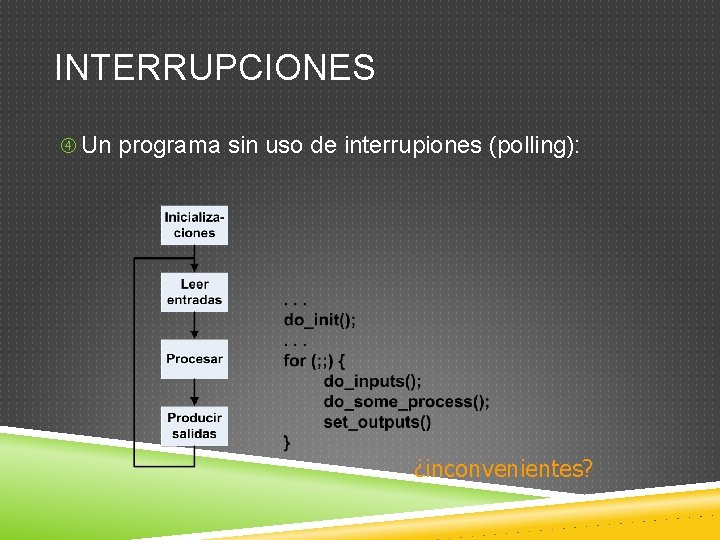

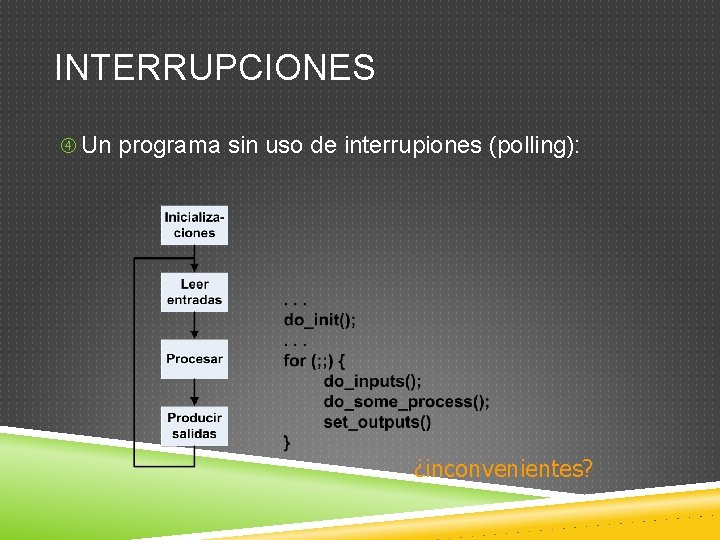

INTERRUPCIONES Un programa sin uso de interrupiones (polling): ¿inconvenientes?

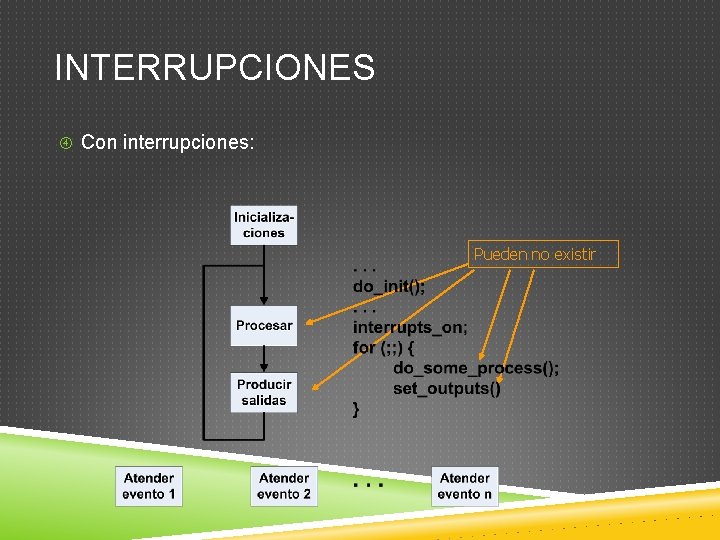

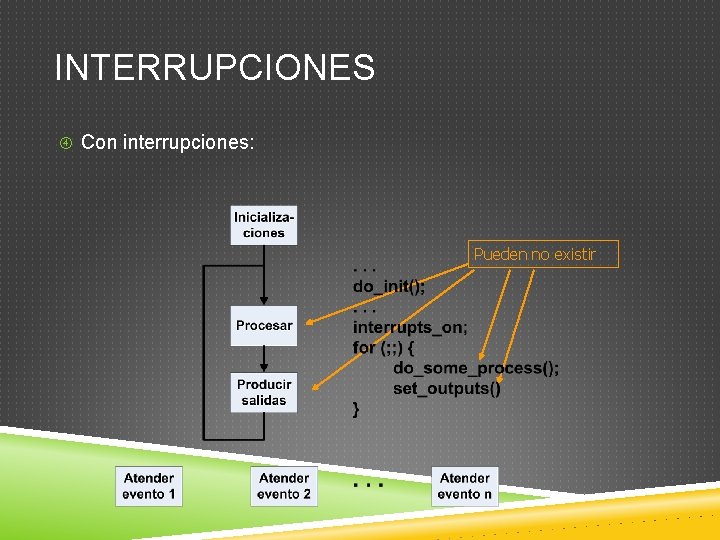

INTERRUPCIONES Con interrupciones: Pueden no existir

INTERRUPCIONES Las interrupciones se generan cuando cambia un “estado”. Permiten la reacción ante eventos Restricciones de tiempo real Polling vs. Interrupts Interrupt Service Routine (ISR)

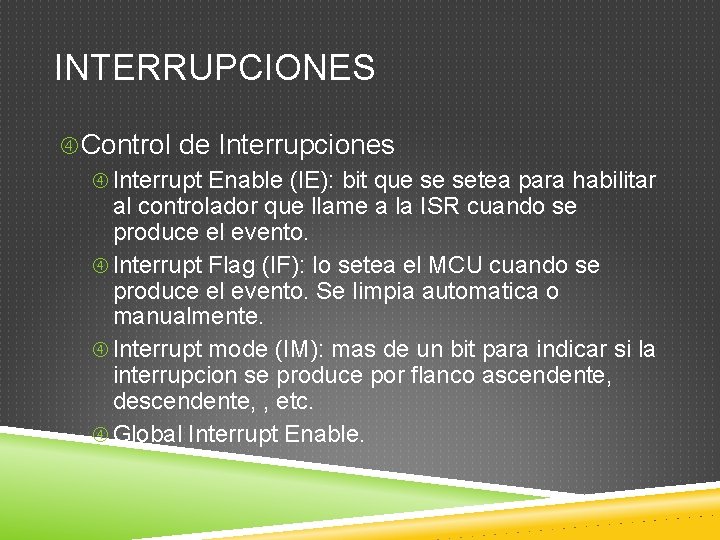

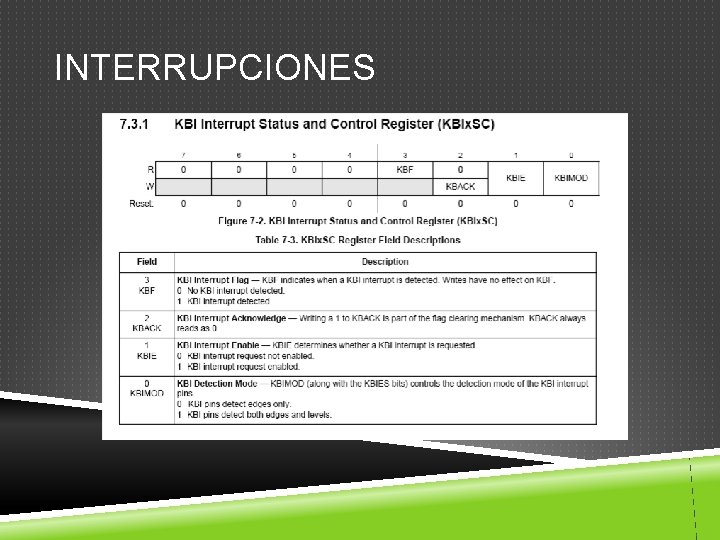

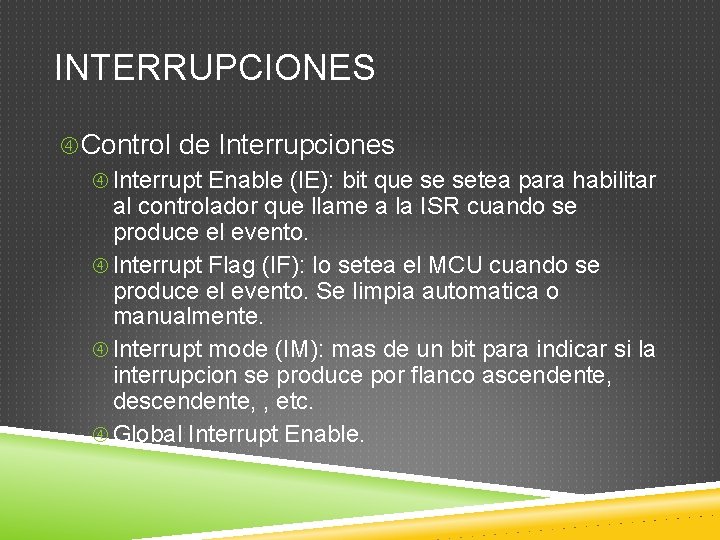

INTERRUPCIONES Control de Interrupciones Interrupt Enable (IE): bit que se setea para habilitar al controlador que llame a la ISR cuando se produce el evento. Interrupt Flag (IF): lo setea el MCU cuando se produce el evento. Se limpia automatica o manualmente. Interrupt mode (IM): mas de un bit para indicar si la interrupcion se produce por flanco ascendente, descendente, , etc. Global Interrupt Enable.

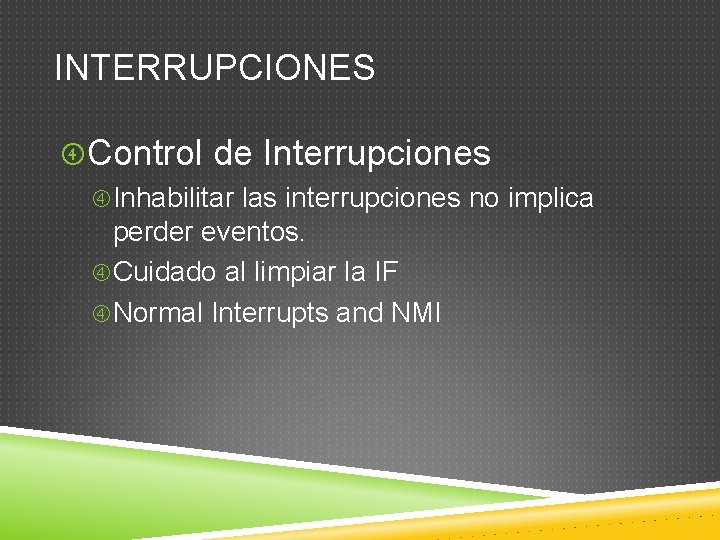

INTERRUPCIONES Control de Interrupciones Inhabilitar las interrupciones no implica perder eventos. Cuidado al limpiar la IF Normal Interrupts and NMI

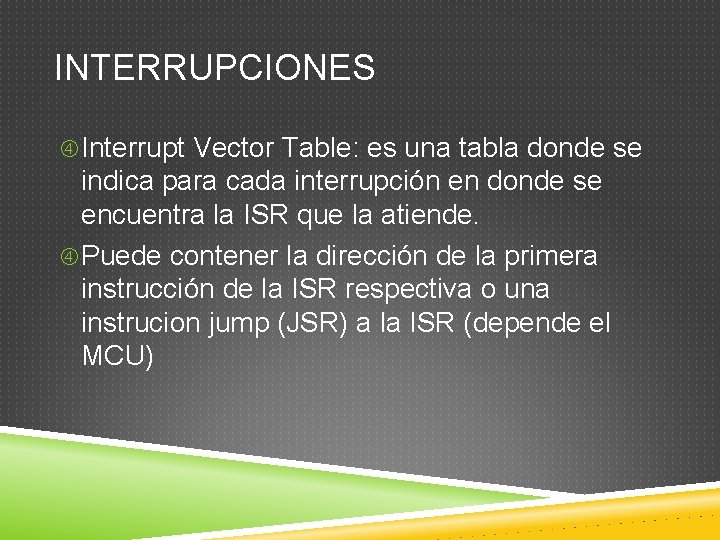

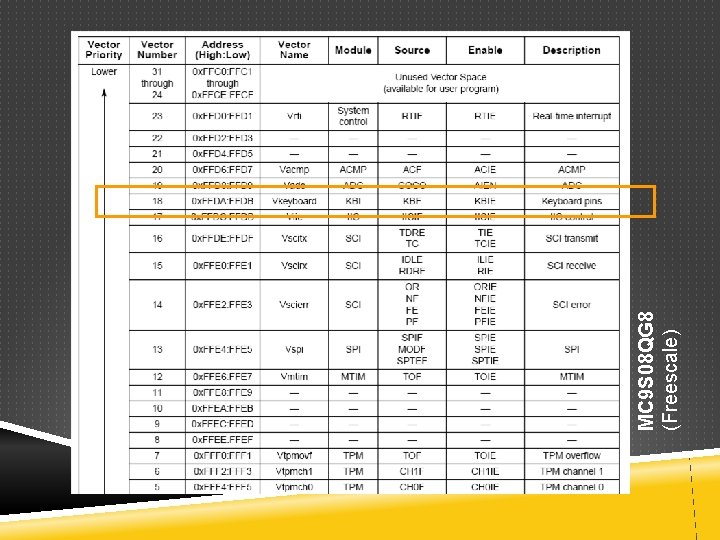

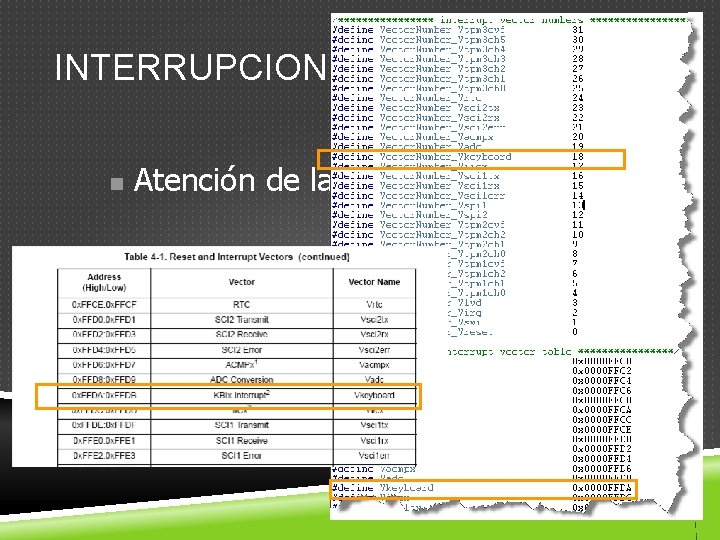

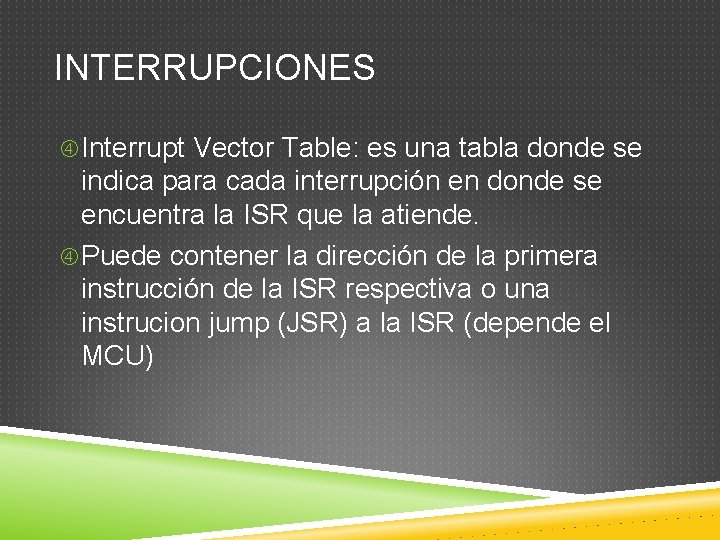

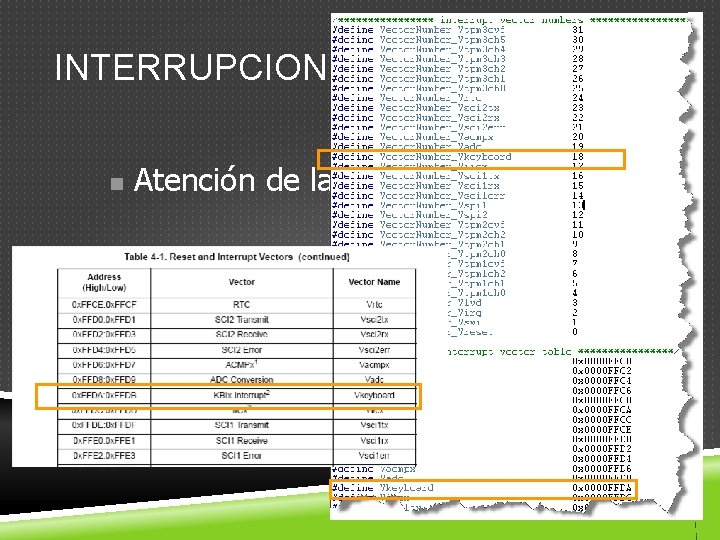

INTERRUPCIONES Interrupt Vector Table: es una tabla donde se indica para cada interrupción en donde se encuentra la ISR que la atiende. Puede contener la dirección de la primera instrucción de la ISR respectiva o una instrucion jump (JSR) a la ISR (depende el MCU)

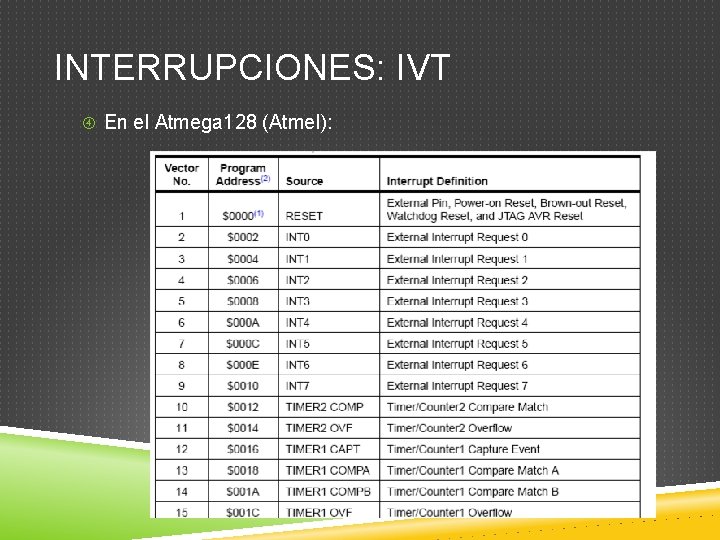

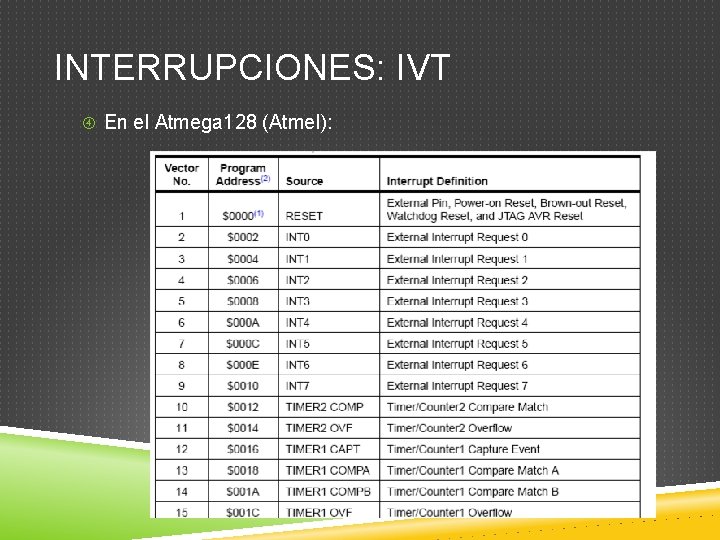

INTERRUPCIONES: IVT En el Atmega 128 (Atmel):

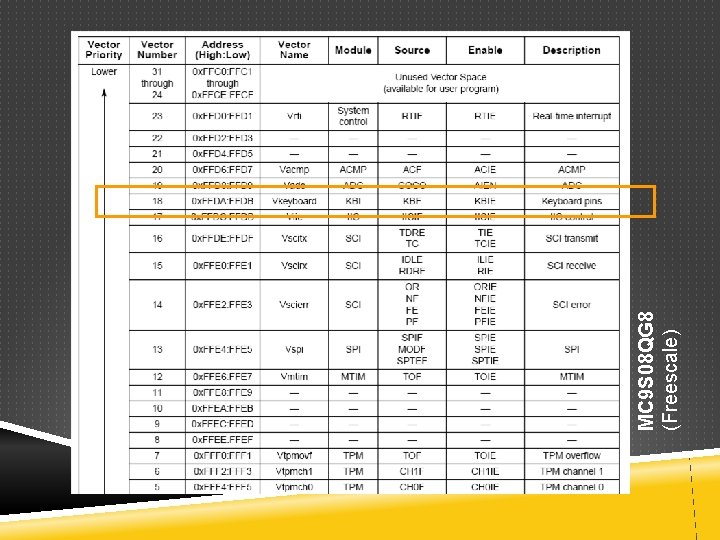

MC 9 S 08 QG 8 (Freescale)

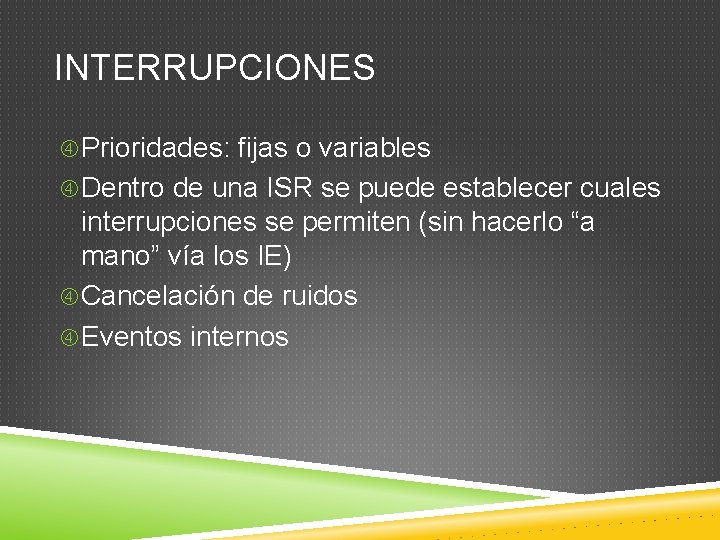

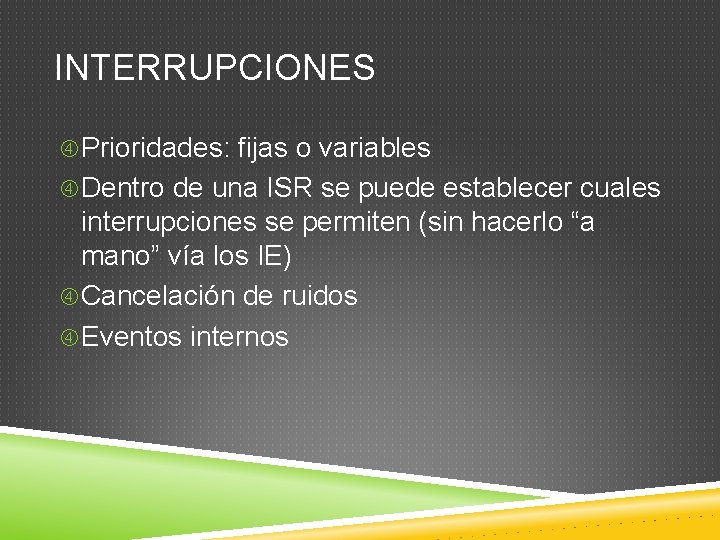

INTERRUPCIONES Prioridades: fijas o variables Dentro de una ISR se puede establecer cuales interrupciones se permiten (sin hacerlo “a mano” vía los IE) Cancelación de ruidos Eventos internos

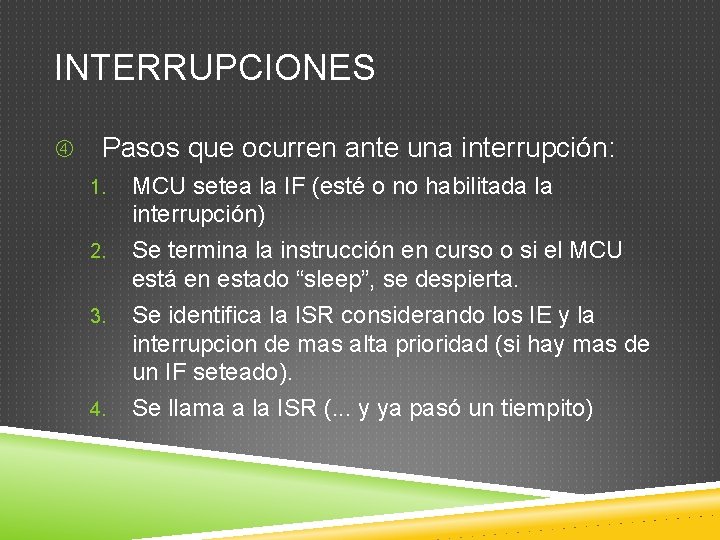

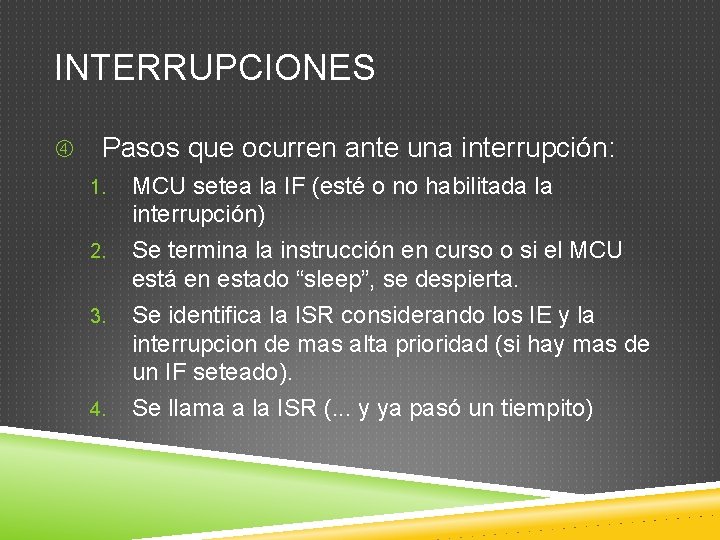

INTERRUPCIONES Pasos que ocurren ante una interrupción: 1. 2. 3. 4. MCU setea la IF (esté o no habilitada la interrupción) Se termina la instrucción en curso o si el MCU está en estado “sleep”, se despierta. Se identifica la ISR considerando los IE y la interrupcion de mas alta prioridad (si hay mas de un IF seteado). Se llama a la ISR (. . . y ya pasó un tiempito)

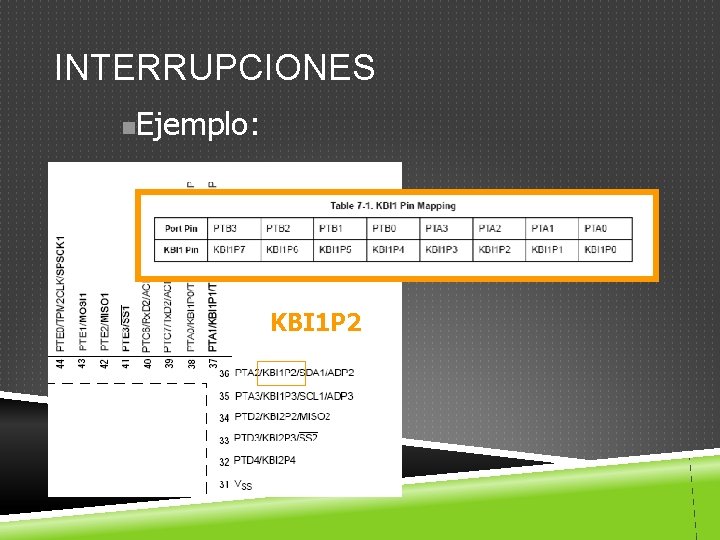

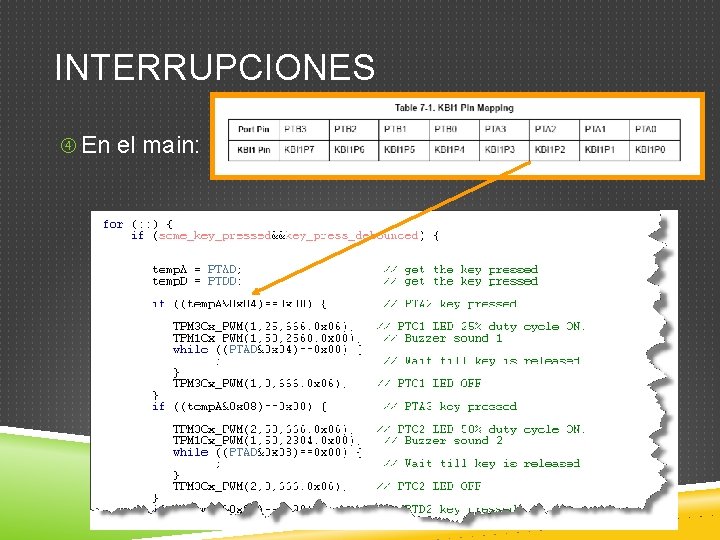

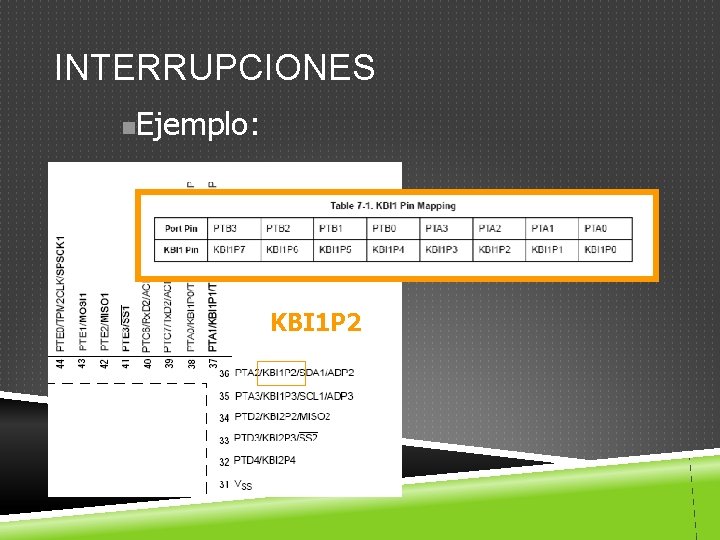

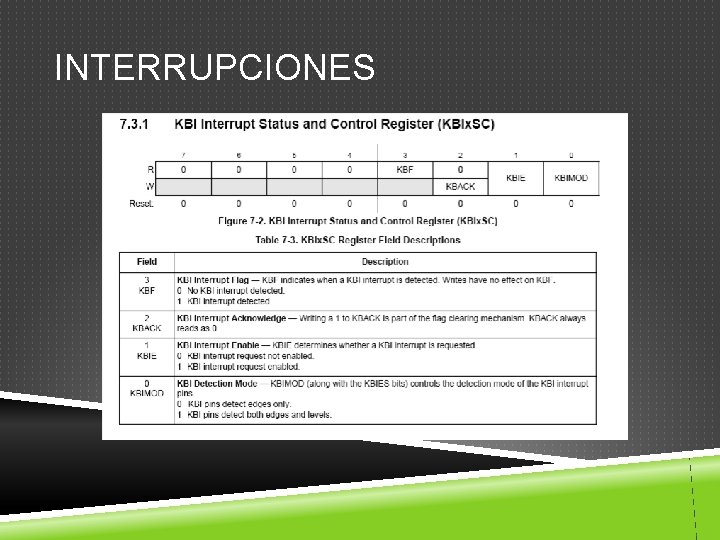

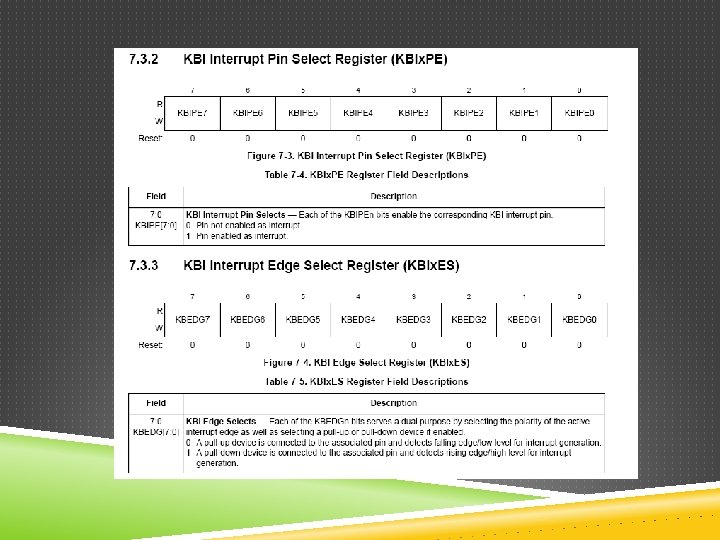

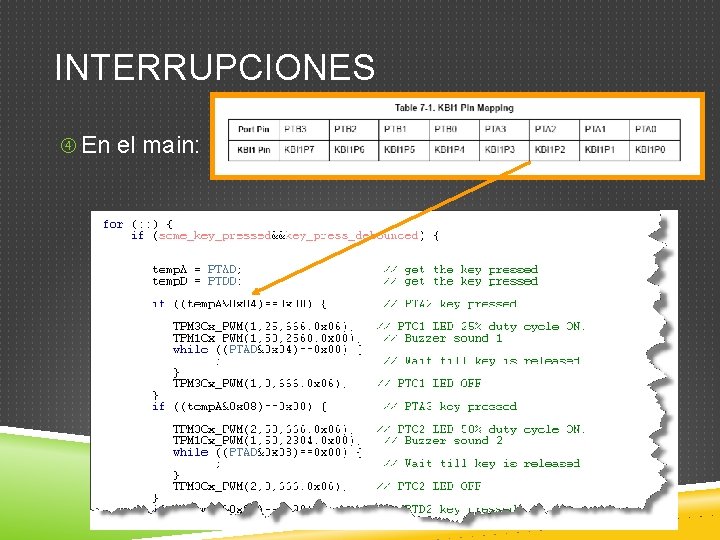

INTERRUPCIONES n Ejemplo: El controlador de interrupciones 1 (KBI 1) tiene 8 entradas conectadas a determinados puertos KBI 1 P 2

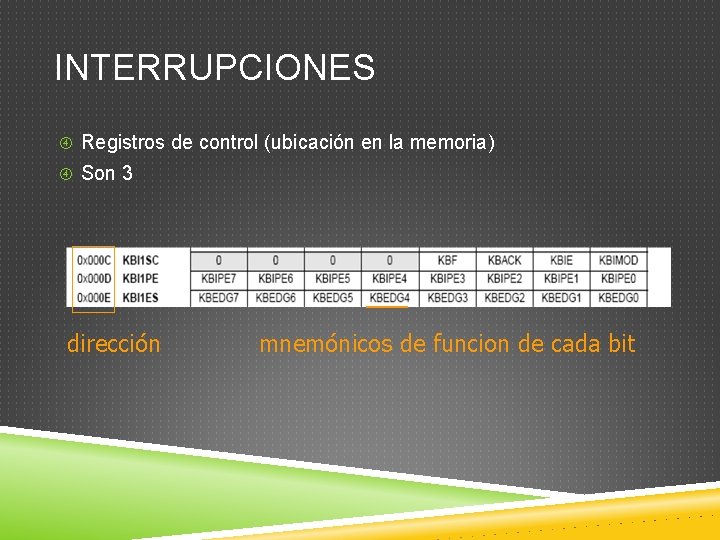

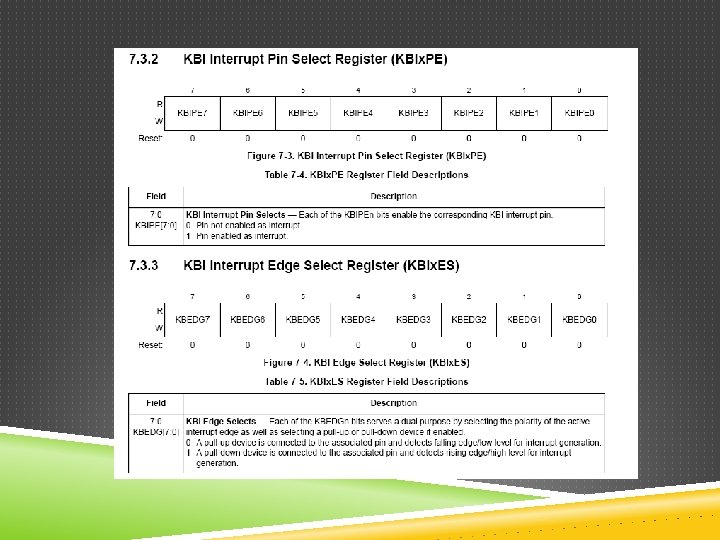

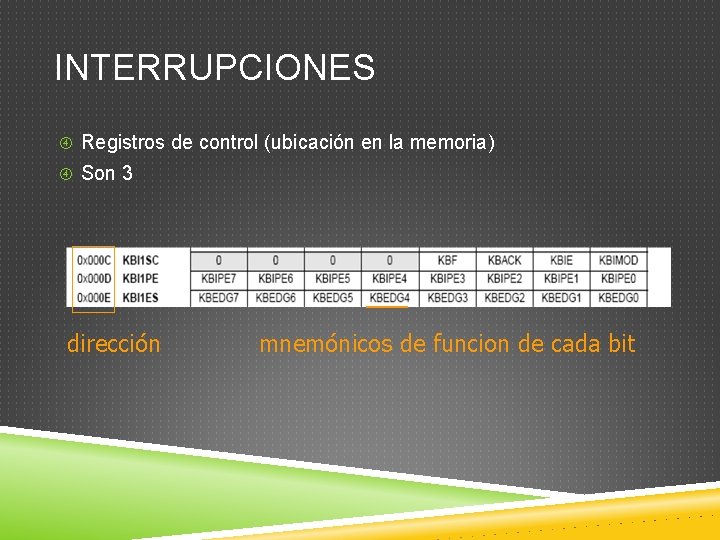

INTERRUPCIONES Registros de control (ubicación en la memoria) Son 3 dirección mnemónicos de funcion de cada bit

INTERRUPCIONES

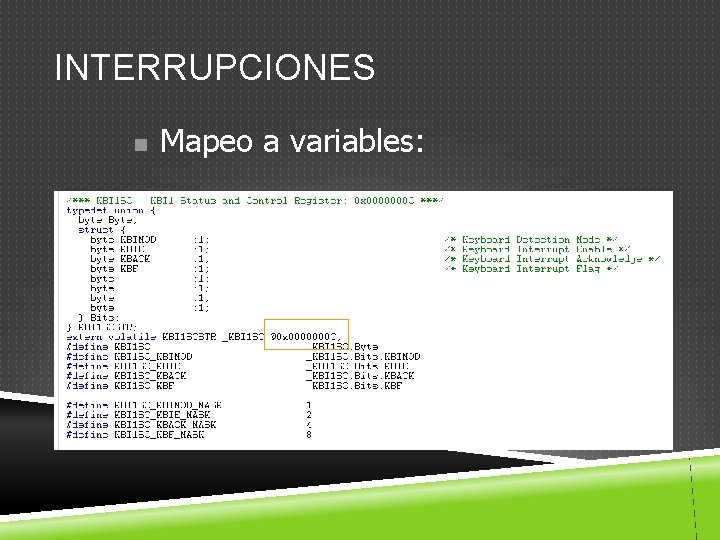

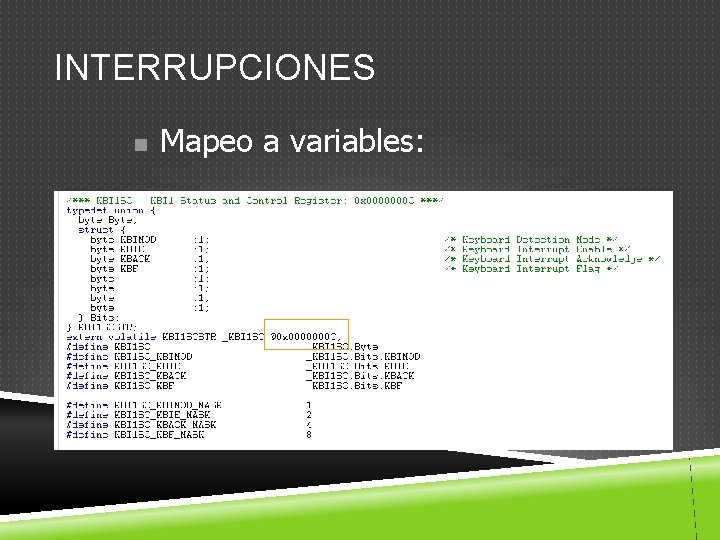

INTERRUPCIONES n Mapeo a variables:

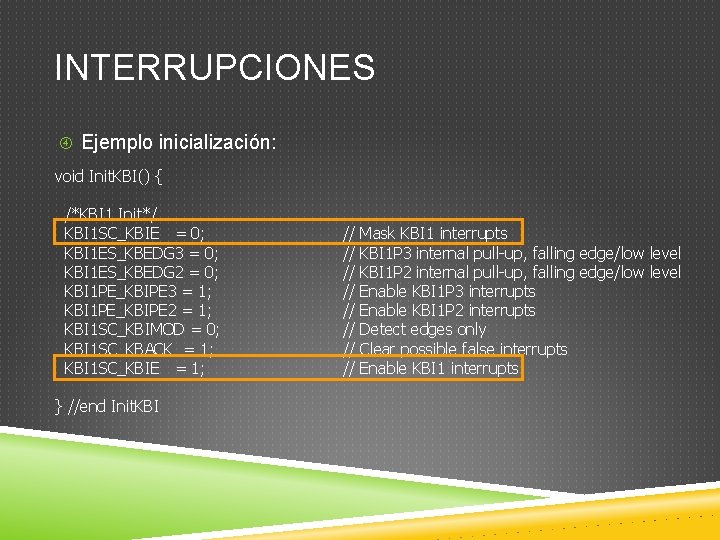

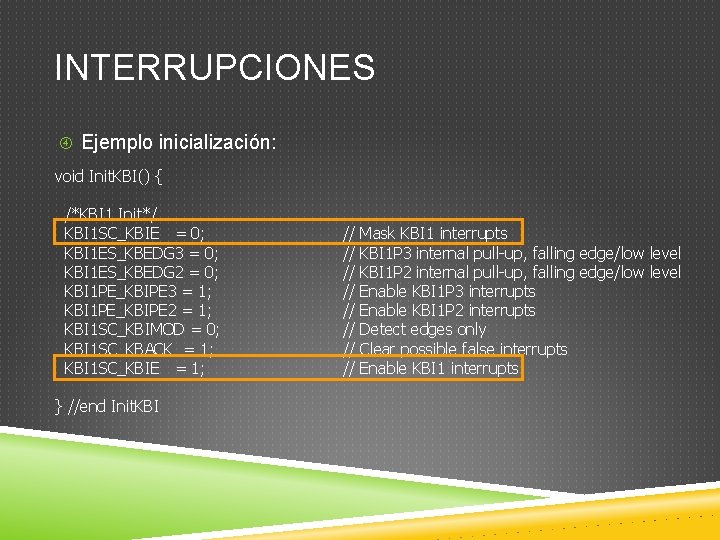

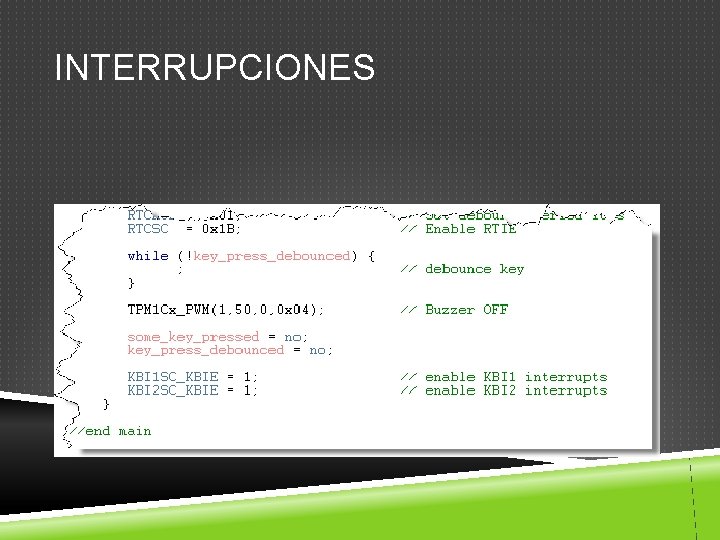

INTERRUPCIONES Ejemplo inicialización: void Init. KBI() { /*KBI 1 Init*/ KBI 1 SC_KBIE = 0; KBI 1 ES_KBEDG 3 = 0; KBI 1 ES_KBEDG 2 = 0; KBI 1 PE_KBIPE 3 = 1; KBI 1 PE_KBIPE 2 = 1; KBI 1 SC_KBIMOD = 0; KBI 1 SC_KBACK = 1; KBI 1 SC_KBIE = 1; } //end Init. KBI // // Mask KBI 1 interrupts KBI 1 P 3 internal pull-up, falling edge/low level KBI 1 P 2 internal pull-up, falling edge/low level Enable KBI 1 P 3 interrupts Enable KBI 1 P 2 interrupts Detect edges only Clear possible false interrupts Enable KBI 1 interrupts

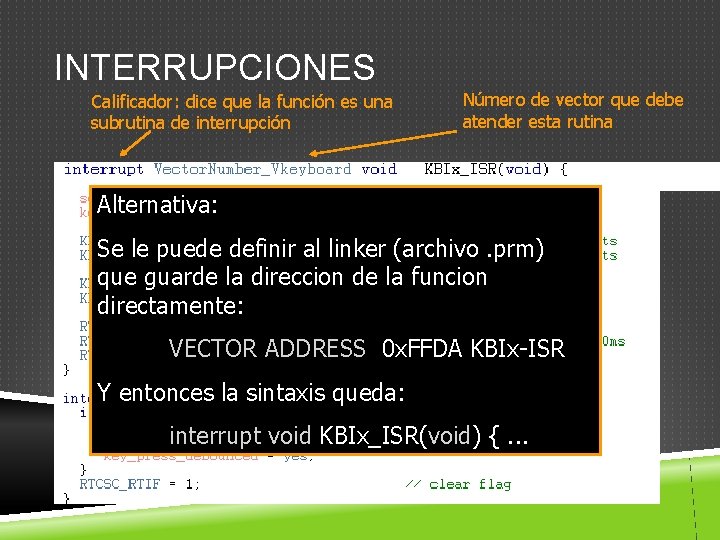

INTERRUPCIONES n Atención de la interrupción

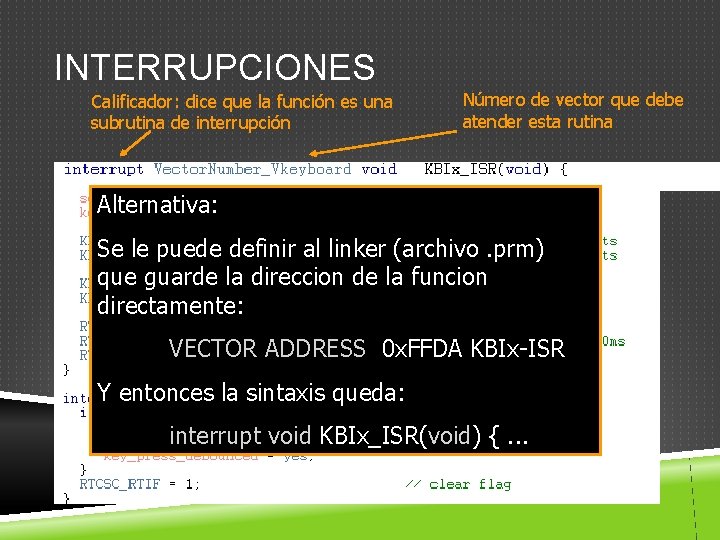

INTERRUPCIONES Calificador: dice que la función es una subrutina de interrupción Número de vector que debe atender esta rutina Alternativa: Se le puede definir al linker (archivo. prm) que guarde la direccion de la funcion directamente: VECTOR ADDRESS 0 x. FFDA KBIx-ISR Y entonces la sintaxis queda: interrupt void KBIx_ISR(void) {. . .

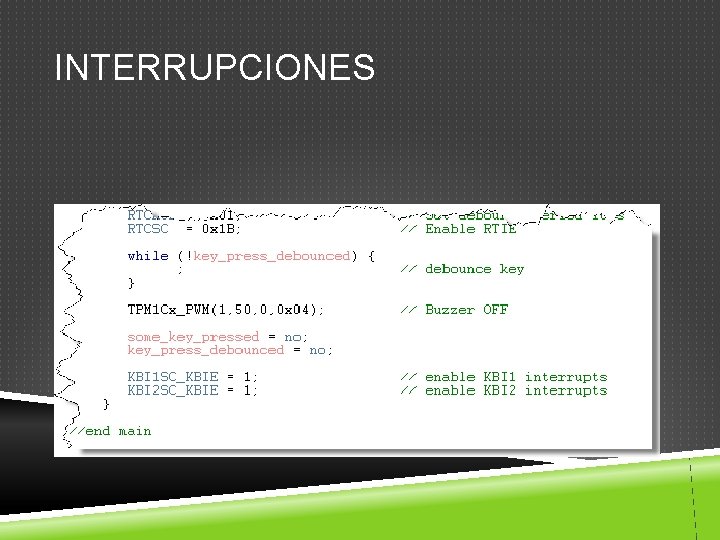

INTERRUPCIONES En el main:

INTERRUPCIONES

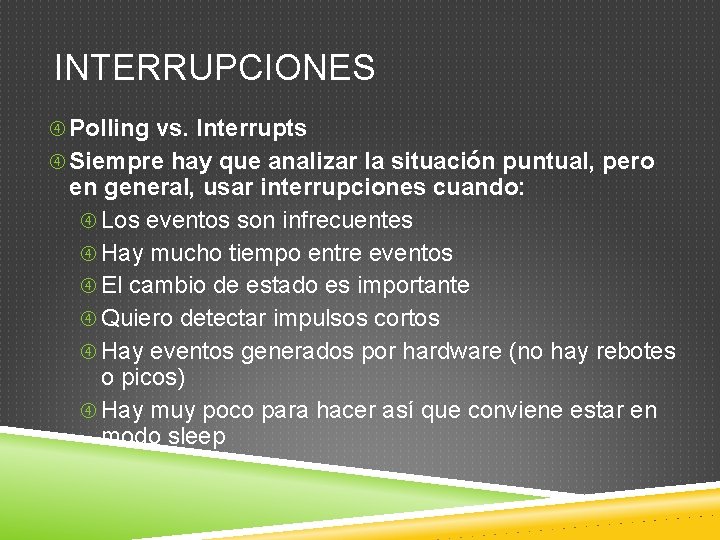

INTERRUPCIONES Polling vs. Interrupts Siempre hay que analizar la situación puntual, pero en general, usar interrupciones cuando: Los eventos son infrecuentes Hay mucho tiempo entre eventos El cambio de estado es importante Quiero detectar impulsos cortos Hay eventos generados por hardware (no hay rebotes o picos) Hay muy poco para hacer así que conviene estar en modo sleep

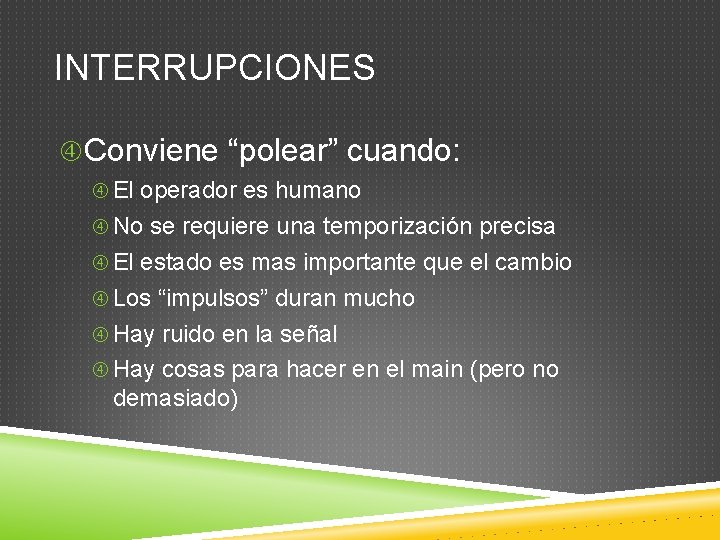

INTERRUPCIONES Conviene “polear” cuando: El operador es humano No se requiere una temporización precisa El estado es mas importante que el cambio Los “impulsos” duran mucho Hay ruido en la señal Hay cosas para hacer en el main (pero no demasiado)

MICROCONTROLADORES Introducción Arquitectura Memoria I/O Digital Interrupciones I/O Analógica Timers/PWM Interfaces y Otros Periféricos

ENTRADA/SALIDA ANALOGICA

ANALOG I/O Conversión DIGITAL a ANALOGICA: Usando un modulador de ancho de pulso

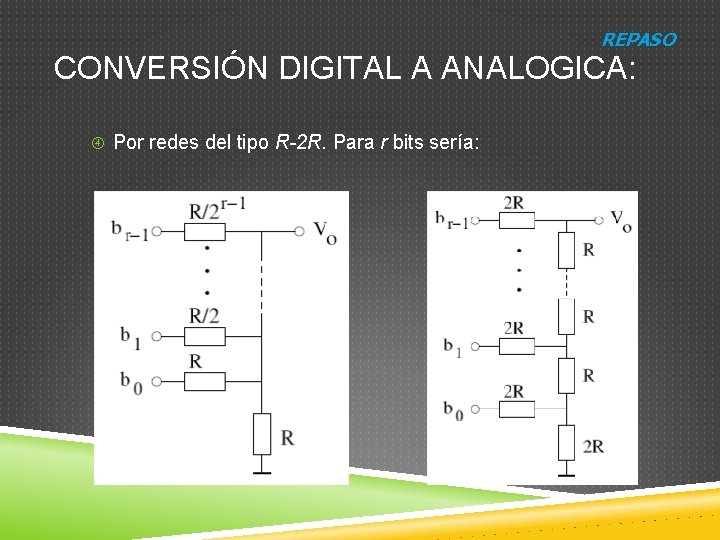

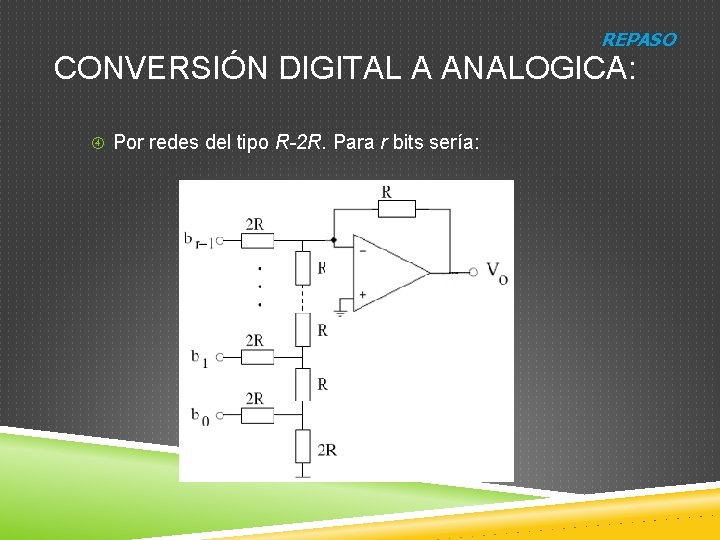

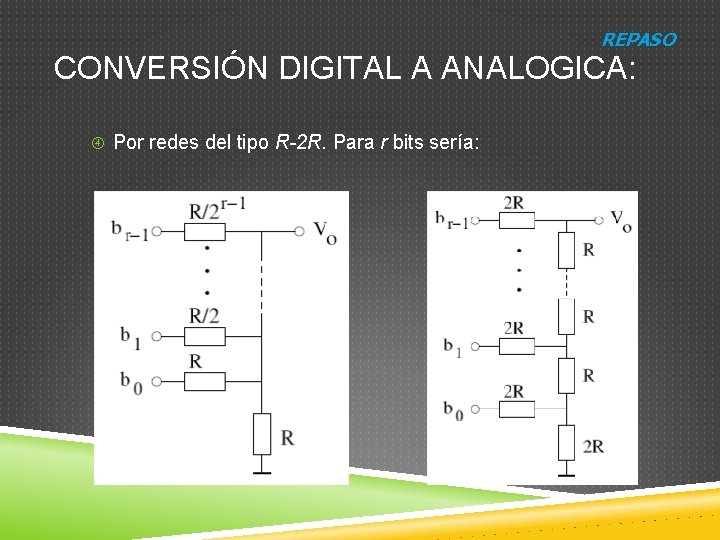

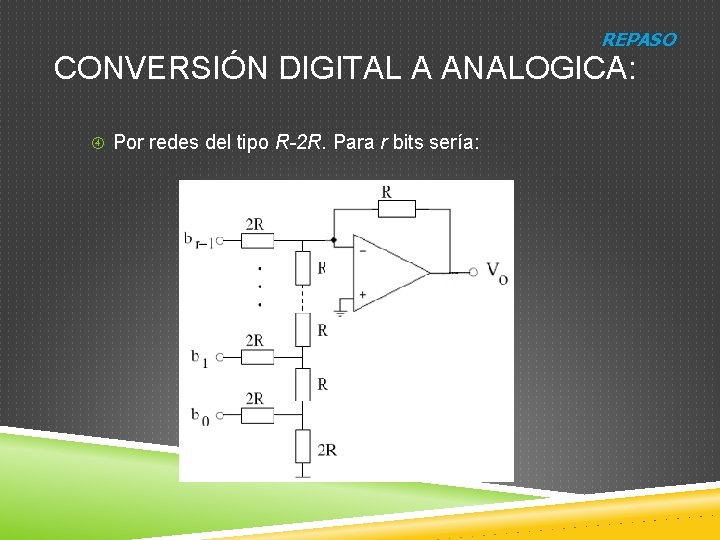

REPASO CONVERSIÓN DIGITAL A ANALOGICA: Por redes del tipo R-2 R. Para r bits sería:

REPASO CONVERSIÓN DIGITAL A ANALOGICA: Por redes del tipo R-2 R. Para r bits sería:

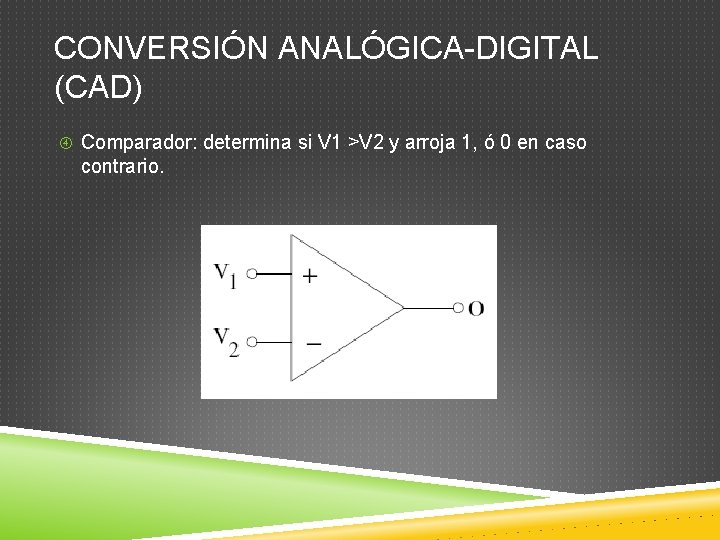

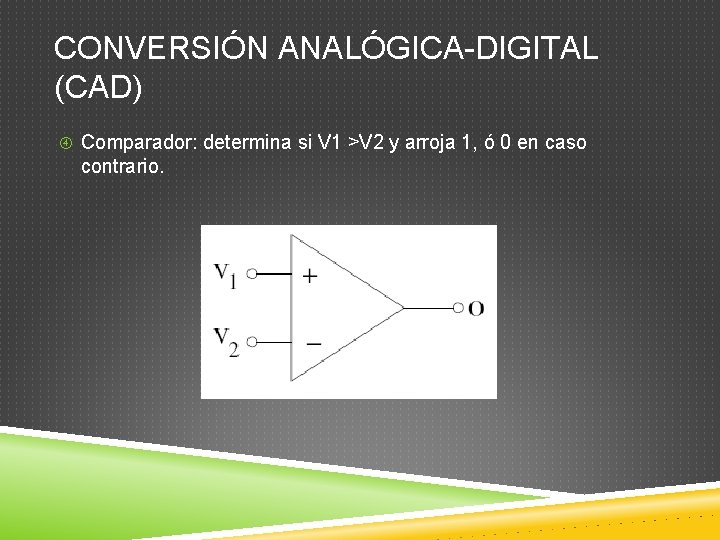

CONVERSIÓN ANALÓGICA-DIGITAL (CAD) Comparador: determina si V 1 >V 2 y arroja 1, ó 0 en caso contrario.

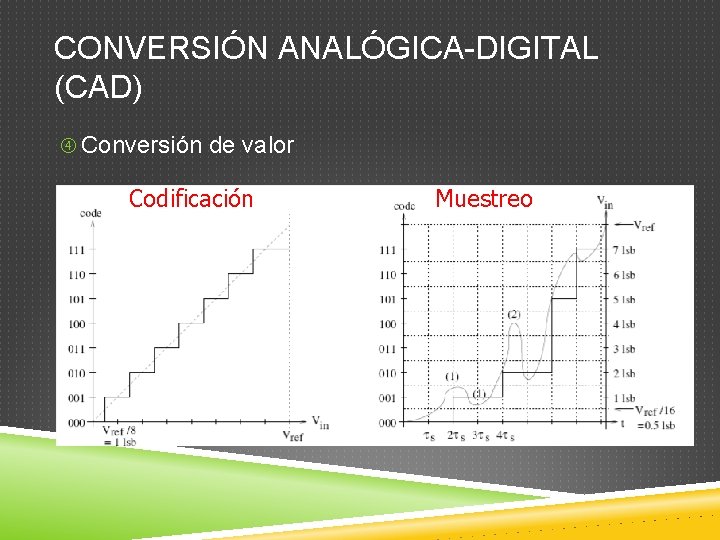

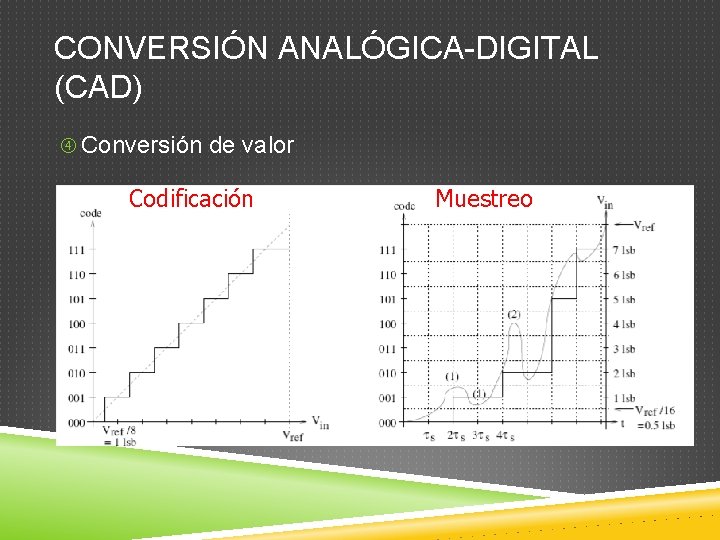

CONVERSIÓN ANALÓGICA-DIGITAL (CAD) Conversión de valor Codificación Muestreo

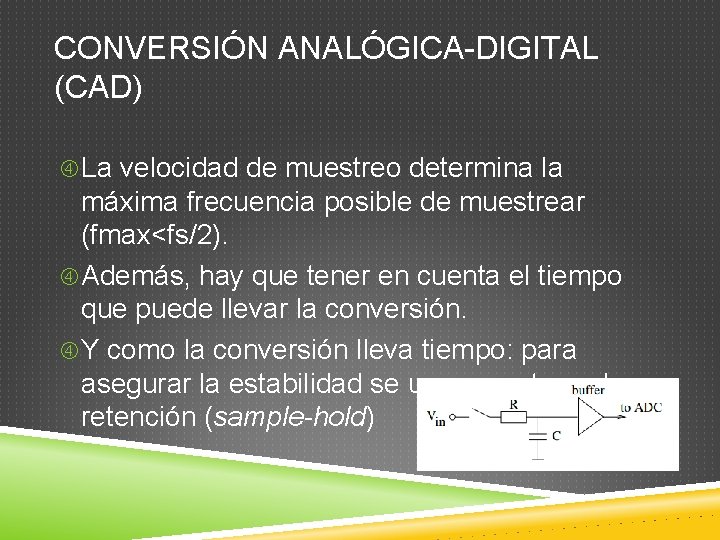

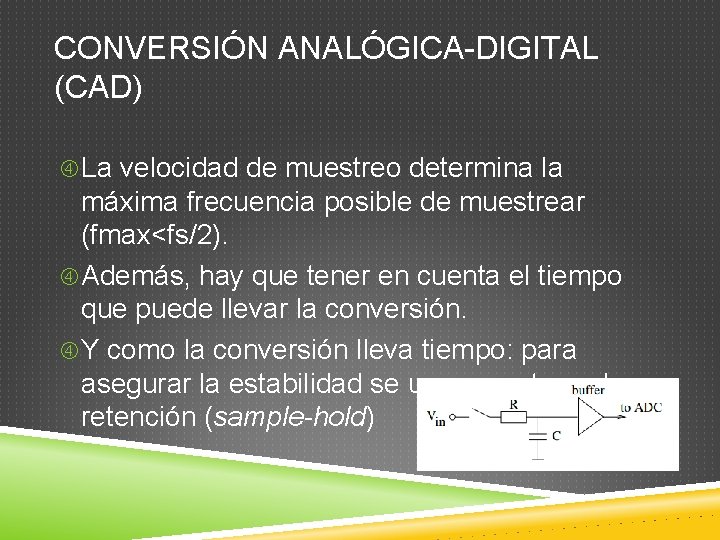

CONVERSIÓN ANALÓGICA-DIGITAL (CAD) La velocidad de muestreo determina la máxima frecuencia posible de muestrear (fmax<fs/2). Además, hay que tener en cuenta el tiempo que puede llevar la conversión. Y como la conversión lleva tiempo: para asegurar la estabilidad se usa una etapa de retención (sample-hold)

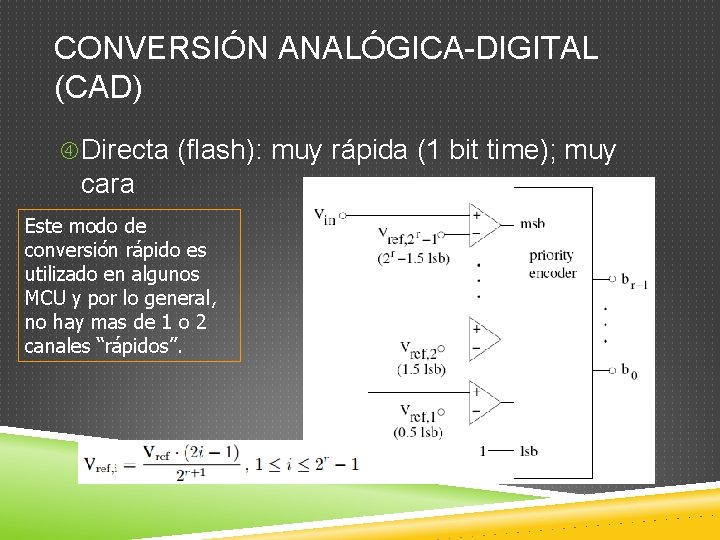

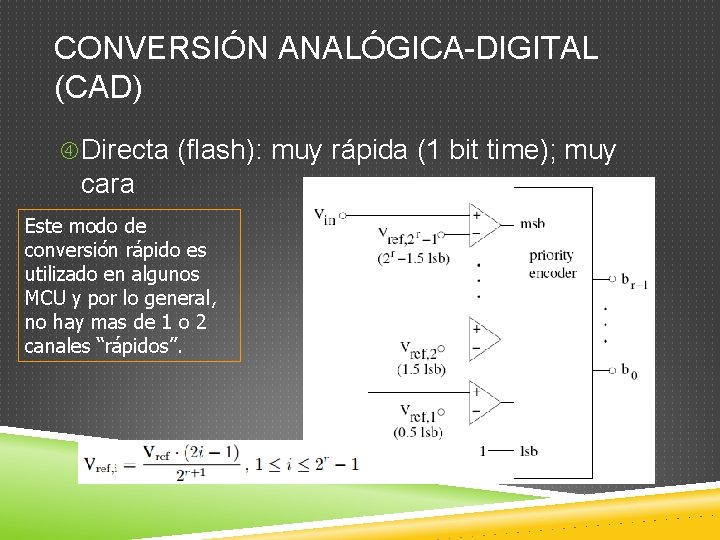

CONVERSIÓN ANALÓGICA-DIGITAL (CAD) Directa (flash): muy rápida (1 bit time); muy cara Este modo de conversión rápido es utilizado en algunos MCU y por lo general, no hay mas de 1 o 2 canales “rápidos”.

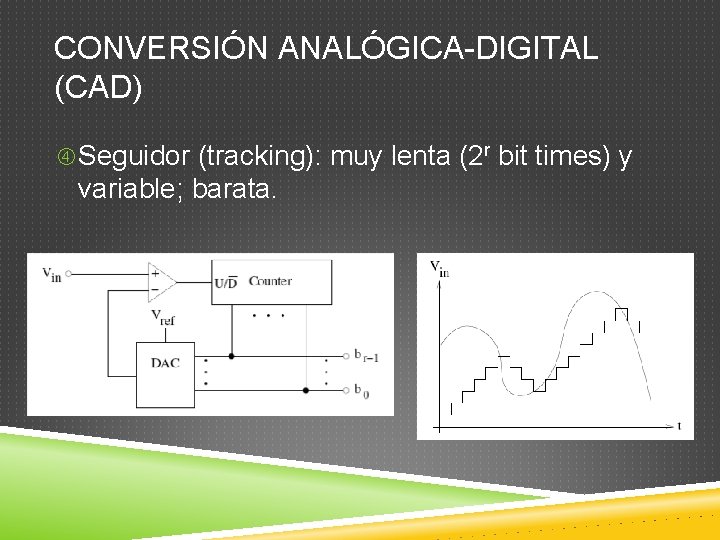

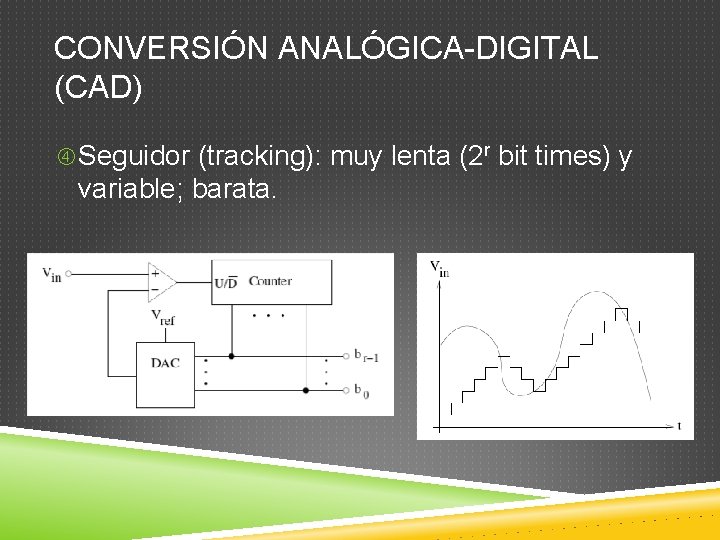

CONVERSIÓN ANALÓGICA-DIGITAL (CAD) Seguidor (tracking): muy lenta (2 r bit times) y variable; barata.

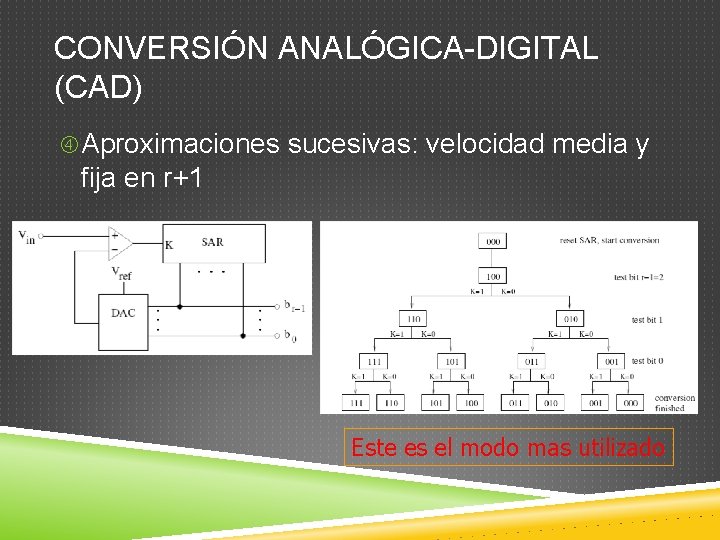

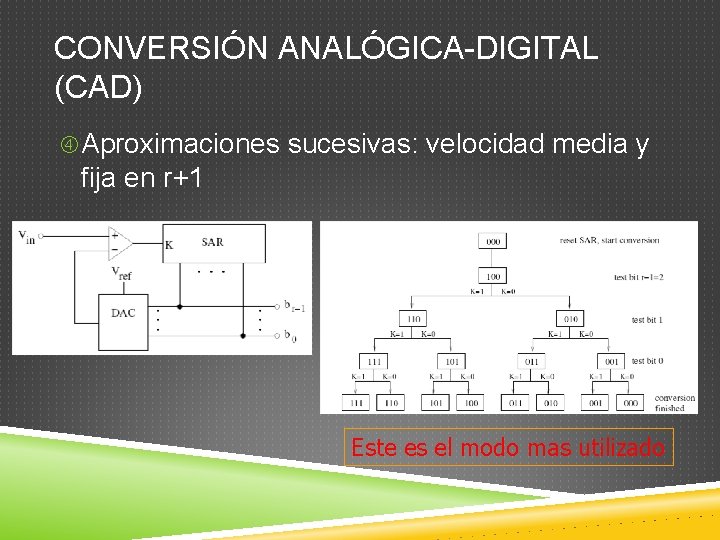

CONVERSIÓN ANALÓGICA-DIGITAL (CAD) Aproximaciones sucesivas: velocidad media y fija en r+1 Este es el modo mas utilizado

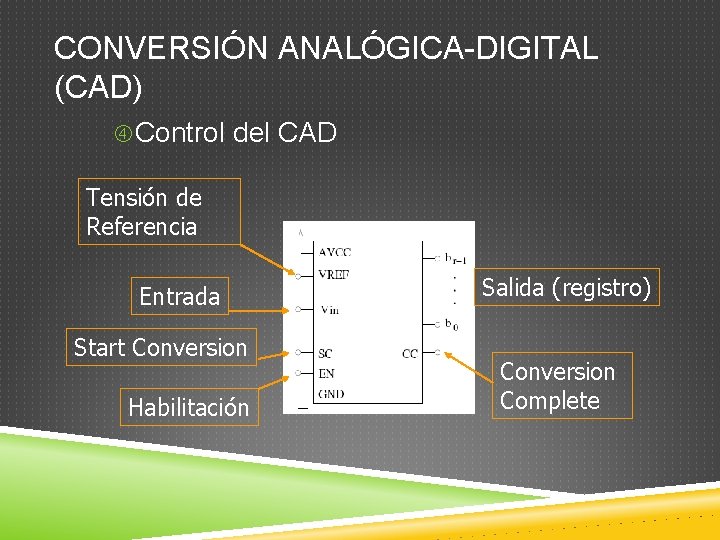

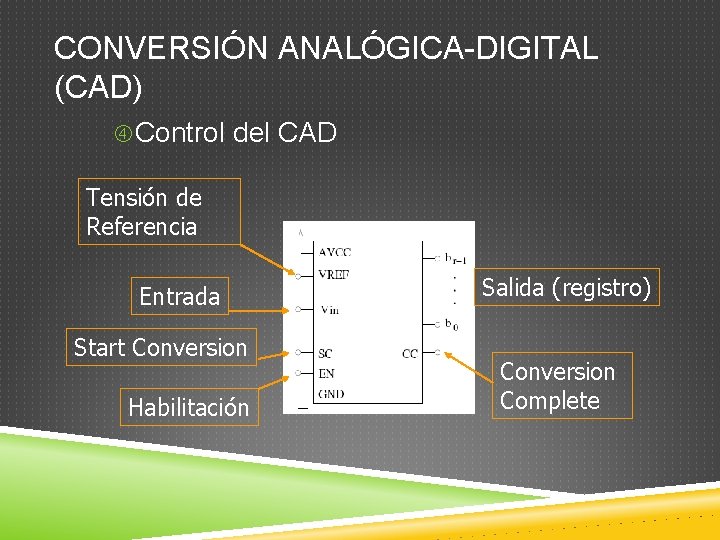

CONVERSIÓN ANALÓGICA-DIGITAL (CAD) Control del CAD Tensión de Referencia Entrada Start Conversion Habilitación Salida (registro) Conversion Complete

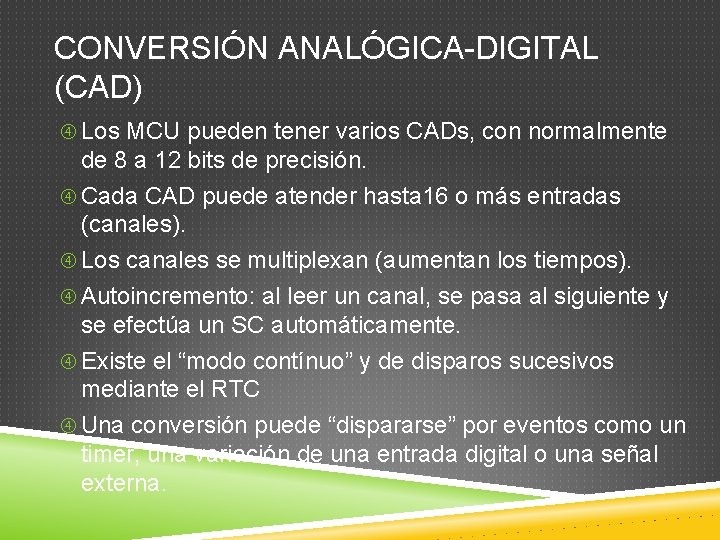

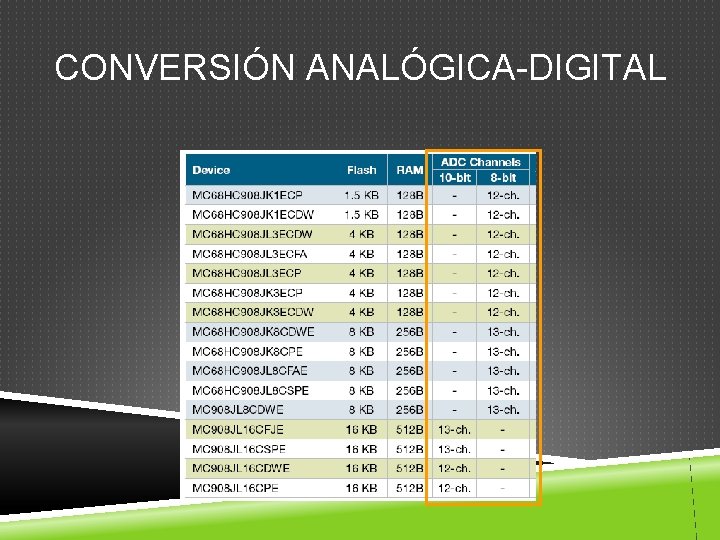

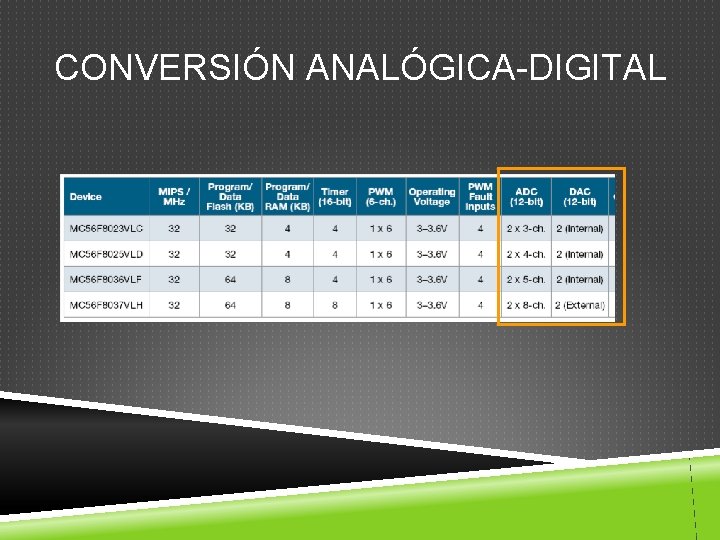

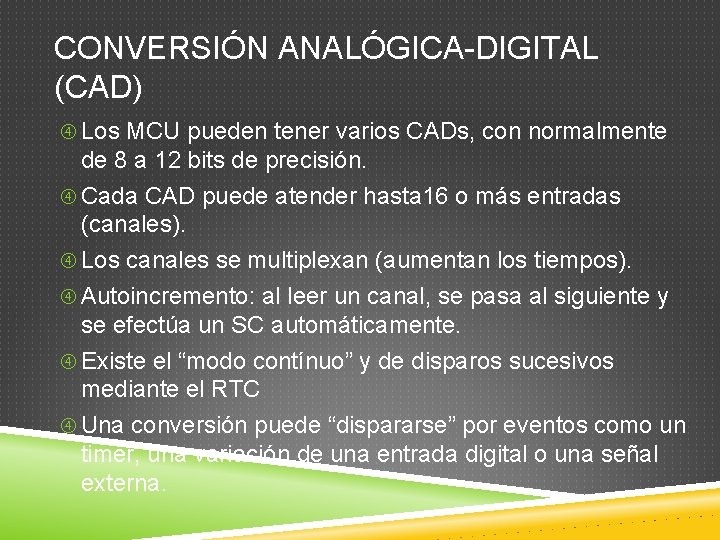

CONVERSIÓN ANALÓGICA-DIGITAL (CAD) Los MCU pueden tener varios CADs, con normalmente de 8 a 12 bits de precisión. Cada CAD puede atender hasta 16 o más entradas (canales). Los canales se multiplexan (aumentan los tiempos). Autoincremento: al leer un canal, se pasa al siguiente y se efectúa un SC automáticamente. Existe el “modo contínuo” y de disparos sucesivos mediante el RTC Una conversión puede “dispararse” por eventos como un timer, una variación de una entrada digital o una señal externa.

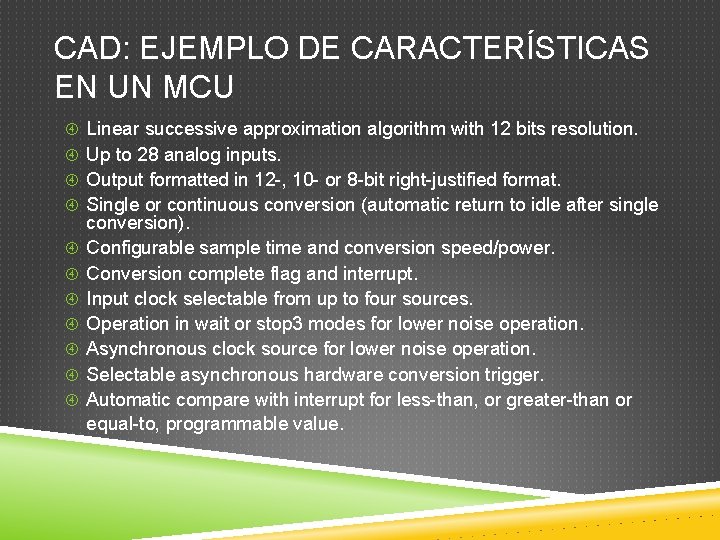

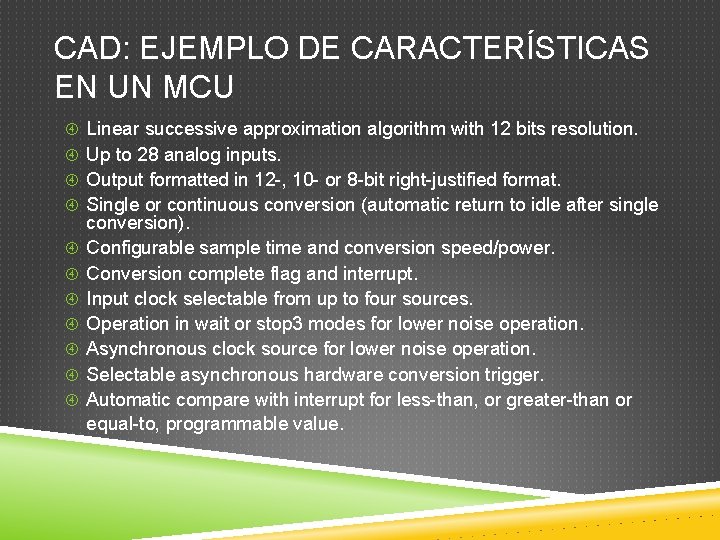

CAD: EJEMPLO DE CARACTERÍSTICAS EN UN MCU Linear successive approximation algorithm with 12 bits resolution. Up to 28 analog inputs. Output formatted in 12 -, 10 - or 8 -bit right-justified format. Single or continuous conversion (automatic return to idle after single conversion). Configurable sample time and conversion speed/power. Conversion complete flag and interrupt. Input clock selectable from up to four sources. Operation in wait or stop 3 modes for lower noise operation. Asynchronous clock source for lower noise operation. Selectable asynchronous hardware conversion trigger. Automatic compare with interrupt for less-than, or greater-than or equal-to, programmable value.

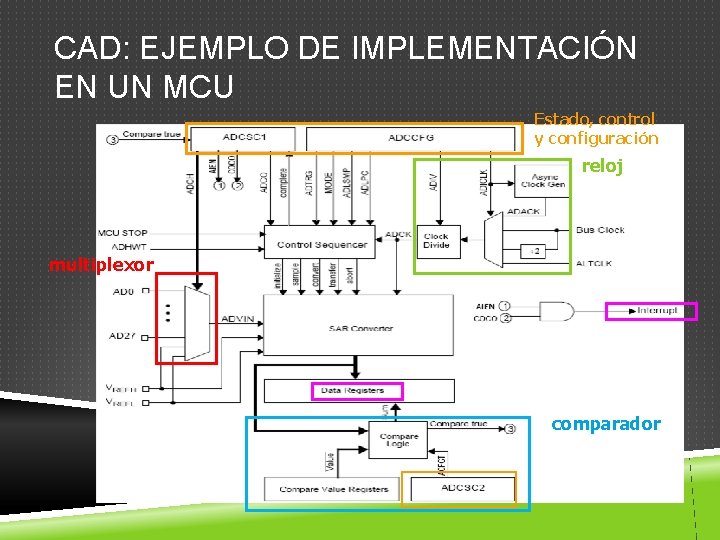

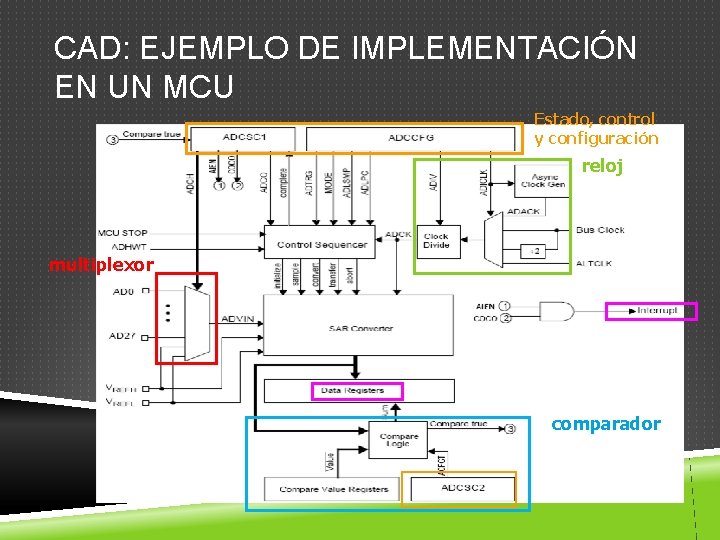

CAD: EJEMPLO DE IMPLEMENTACIÓN EN UN MCU Estado, control y configuración reloj multiplexor comparador

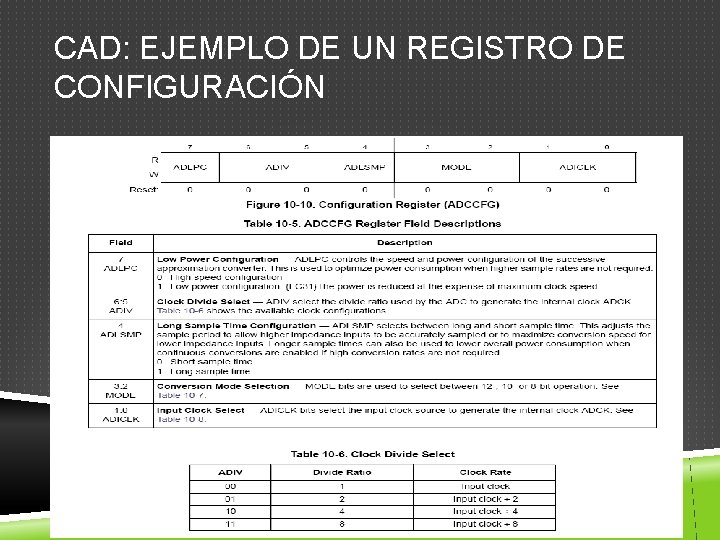

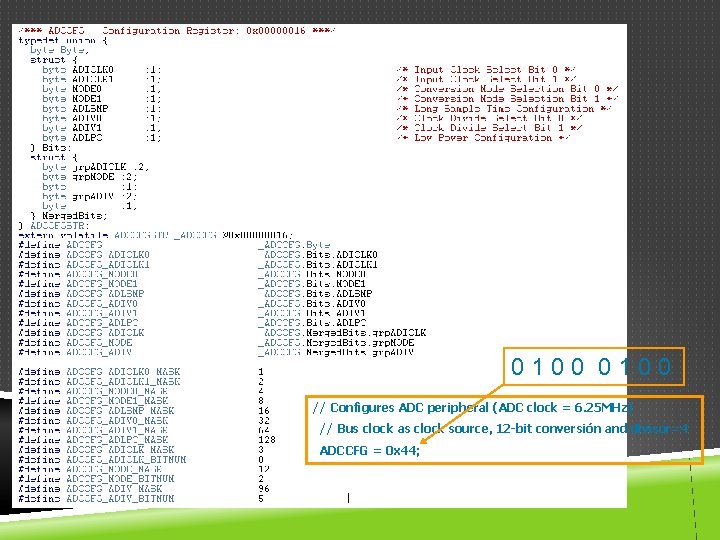

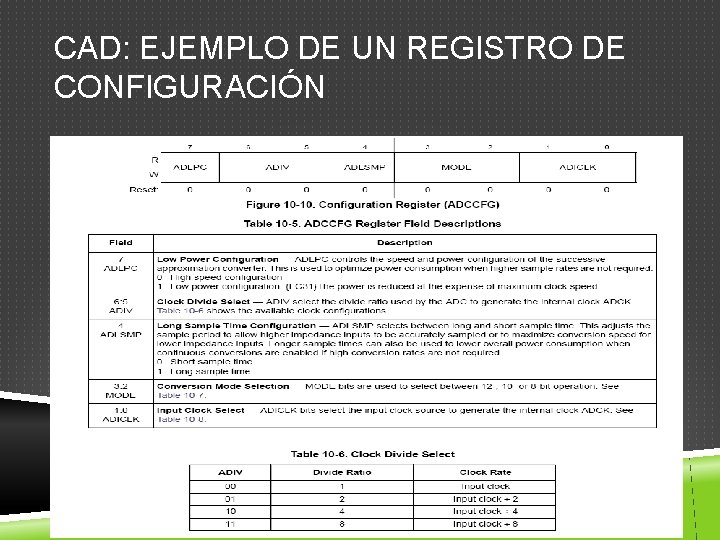

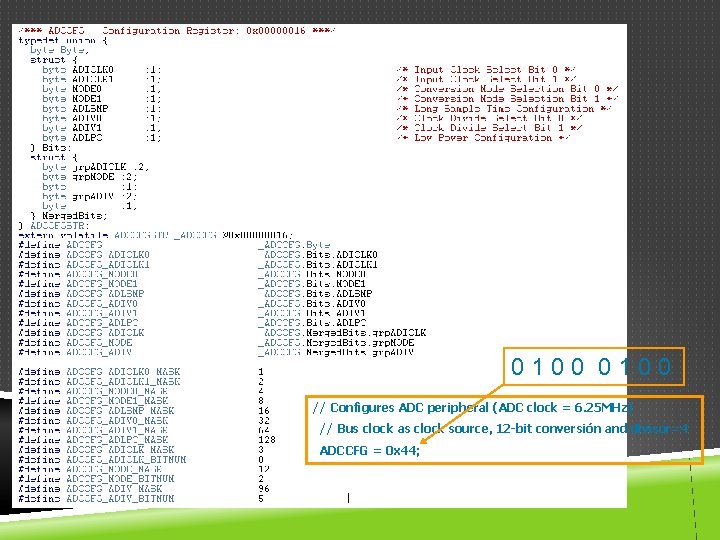

CAD: EJEMPLO DE UN REGISTRO DE CONFIGURACIÓN

0100 // Configures ADC peripheral (ADC clock = 6. 25 MHz) // Bus clock as clock source, 12 -bit conversión and divisor=4 ADCCFG = 0 x 44;

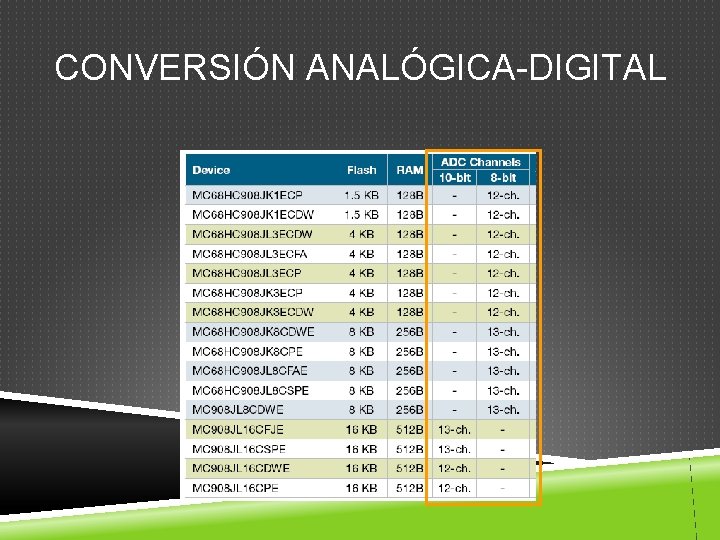

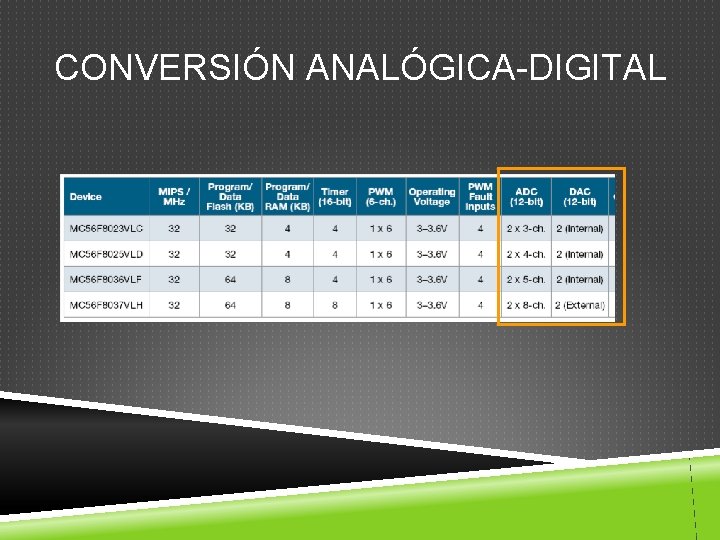

CONVERSIÓN ANALÓGICA-DIGITAL

CONVERSIÓN ANALÓGICA-DIGITAL

TIMERS / PWM

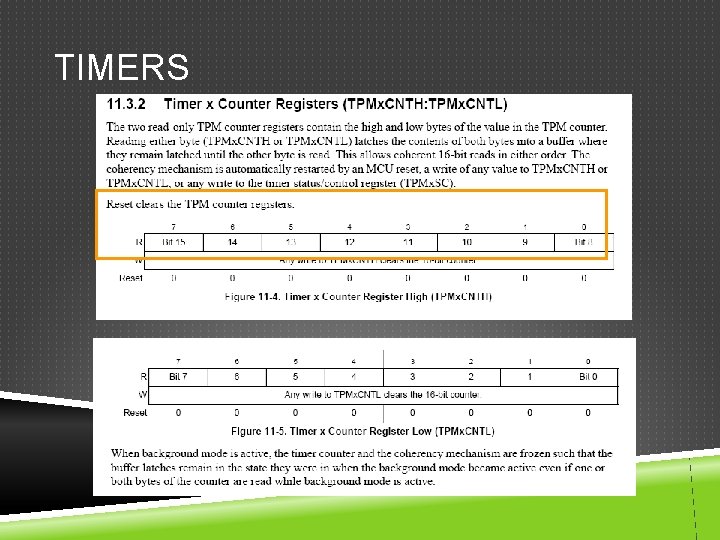

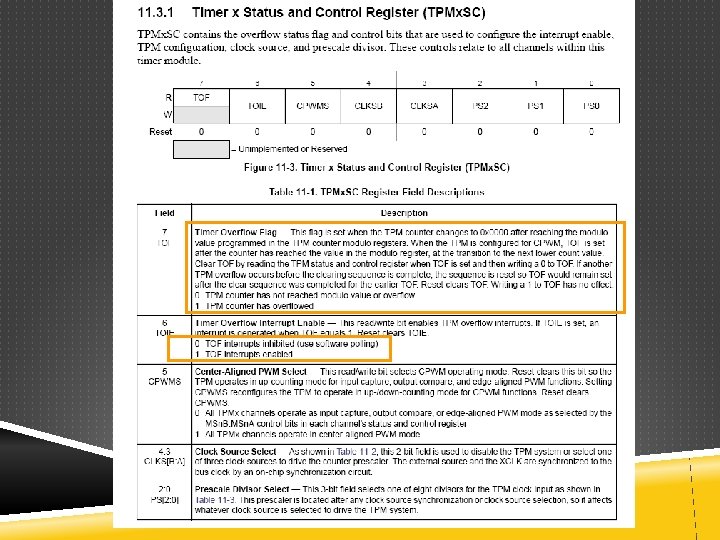

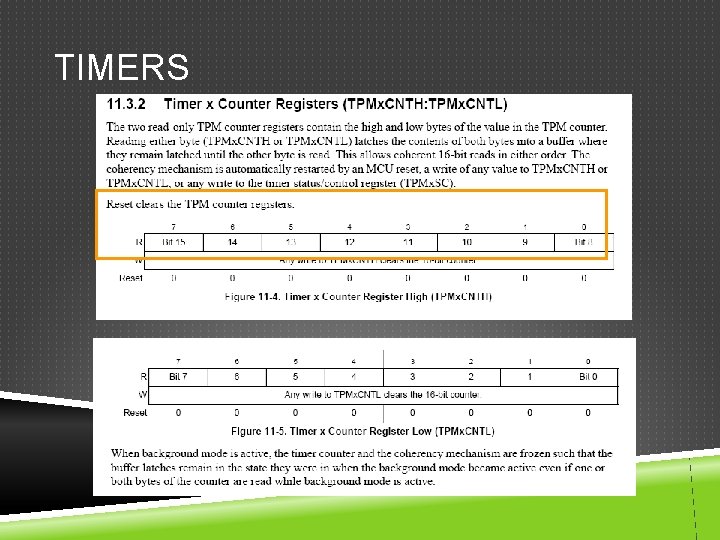

TIMERS Son contadores que suben o bajan con cada pulso de reloj. El valor actual se lee de un registro o se setea en el mismo. Cuidado al acceder a timers con longitud de registro mayor a la palabra del MCU

TIMERS Los timers generalmente generan una interrupción cuando hacen overflow Esto sirve para generar señales o eventos peródicos (con acotada precisión) Pueden tener una señal de clock independiente del MCU. Con ella se incrementa la cuenta.

TIMERS Prescaler Es otro contador (de 8 o 10 bits) que trabaja contra el clock y produce una salida que es la que entra al timer. Se logra una extension de tiempos a medir por la division del prescaler. Ejemplo: 8 bit timer, clock de 1 Mhz -> cuenta máxima 255 u. S con una resolución de 1 u. S 8 bit timer, clock de 1 Mhz, prescaler en 1024 -> cuenta máxima 260 ms con una resolución de 1 ms.

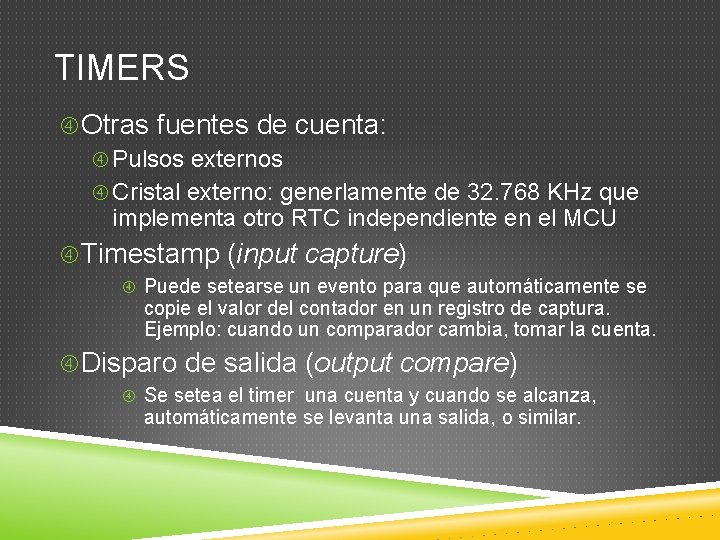

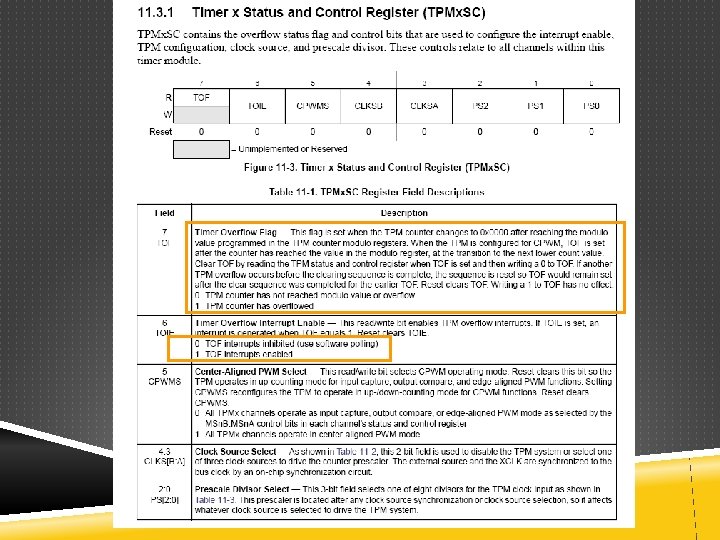

TIMERS Otras fuentes de cuenta: Pulsos externos Cristal externo: generlamente de 32. 768 KHz que implementa otro RTC independiente en el MCU Timestamp (input capture) Puede setearse un evento para que automáticamente se copie el valor del contador en un registro de captura. Ejemplo: cuando un comparador cambia, tomar la cuenta. Disparo de salida (output compare) Se setea el timer una cuenta y cuando se alcanza, automáticamente se levanta una salida, o similar.

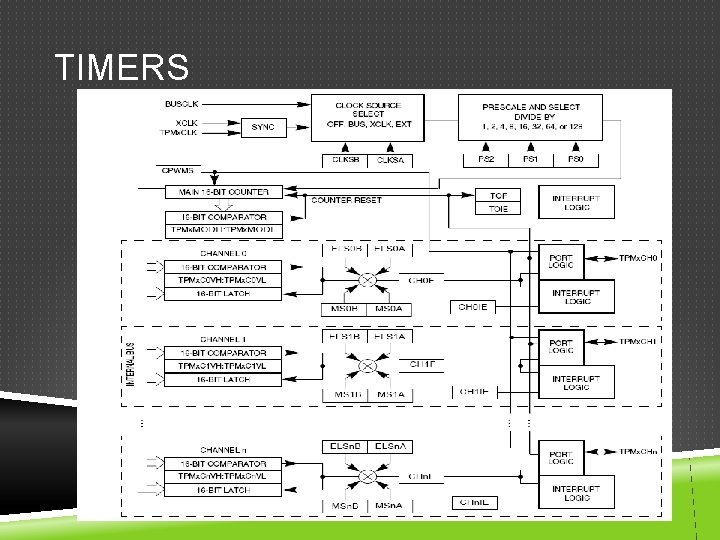

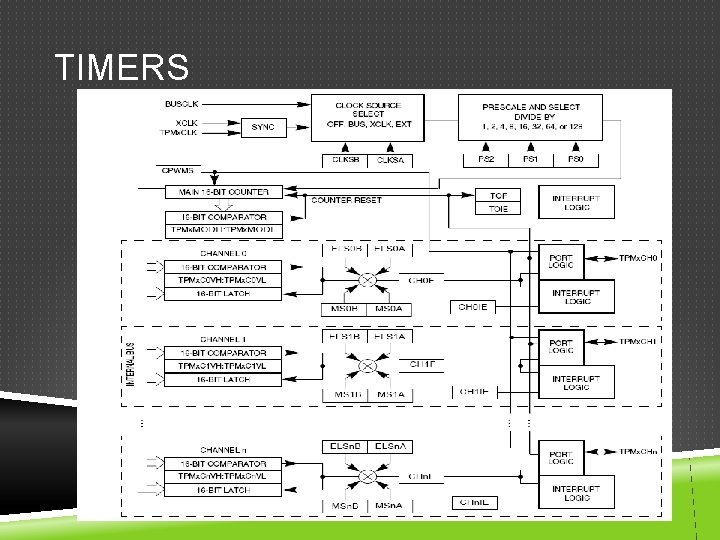

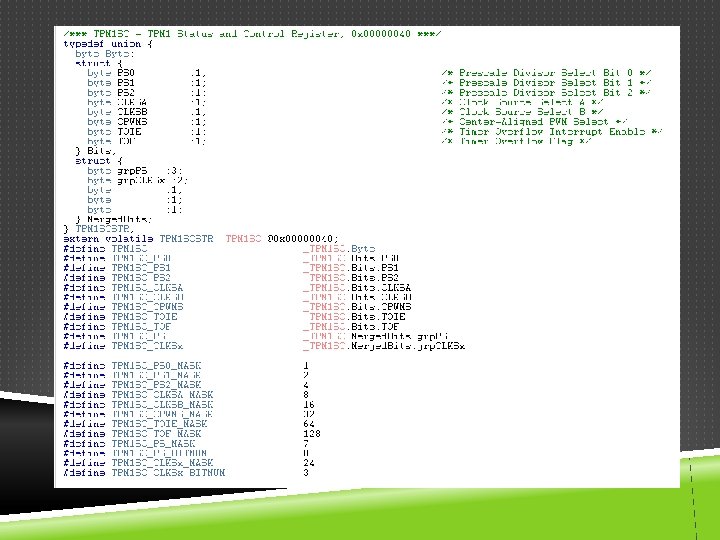

TIMERS

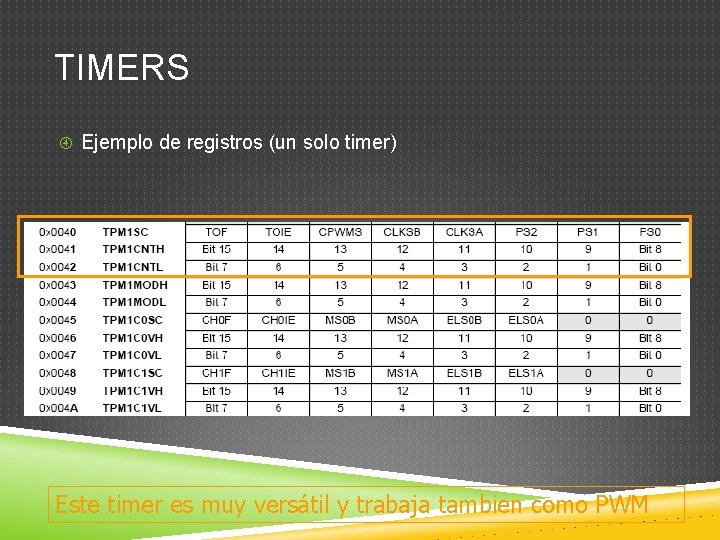

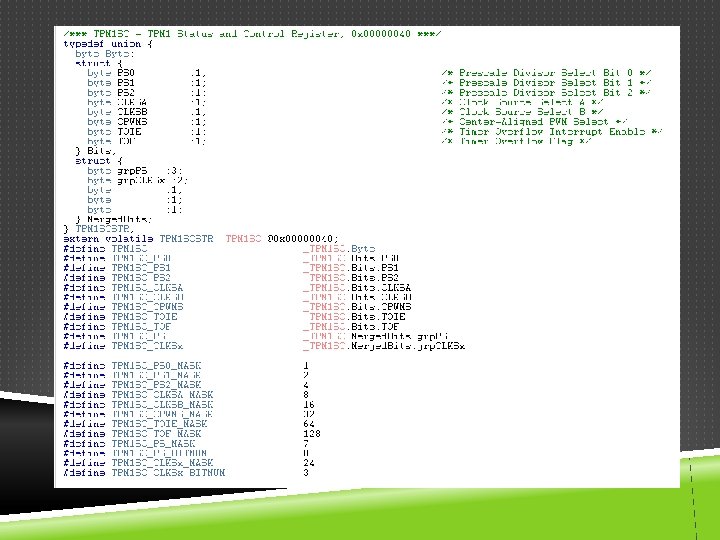

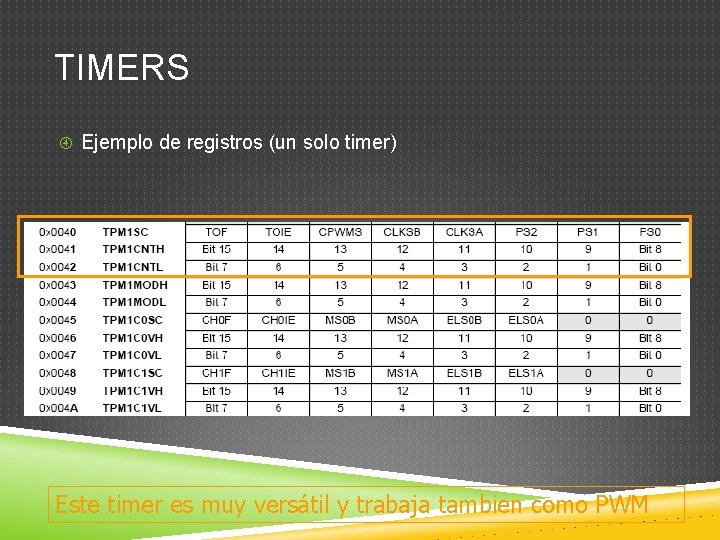

TIMERS Ejemplo de registros (un solo timer) Este timer es muy versátil y trabaja tambien como PWM

TIMERS

TIMERS

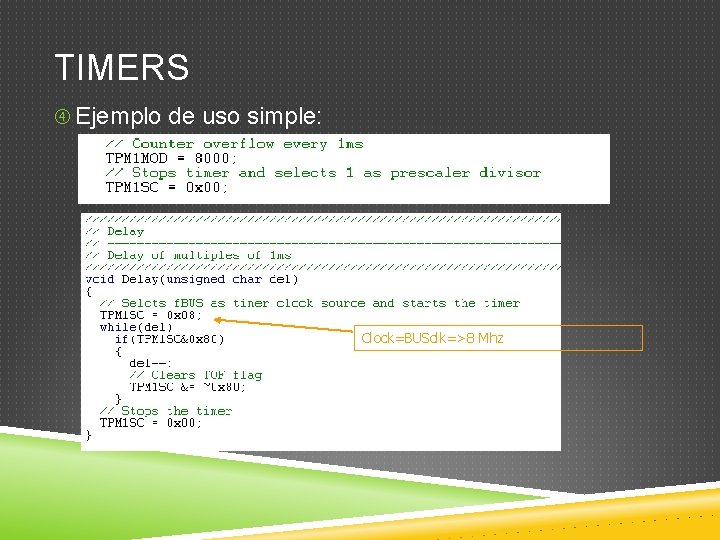

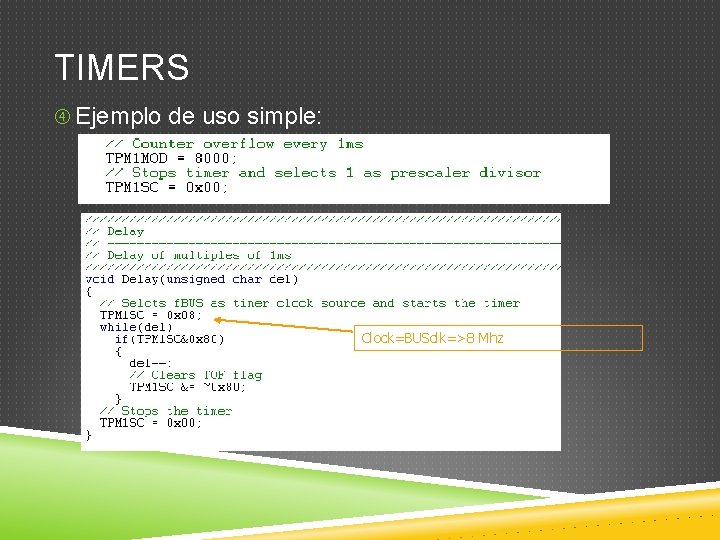

TIMERS Ejemplo de uso simple: Clock=BUSclk=>8 Mhz

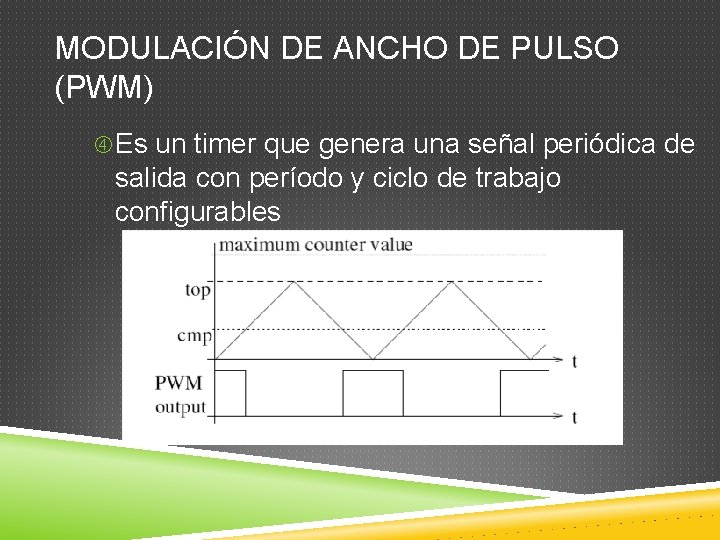

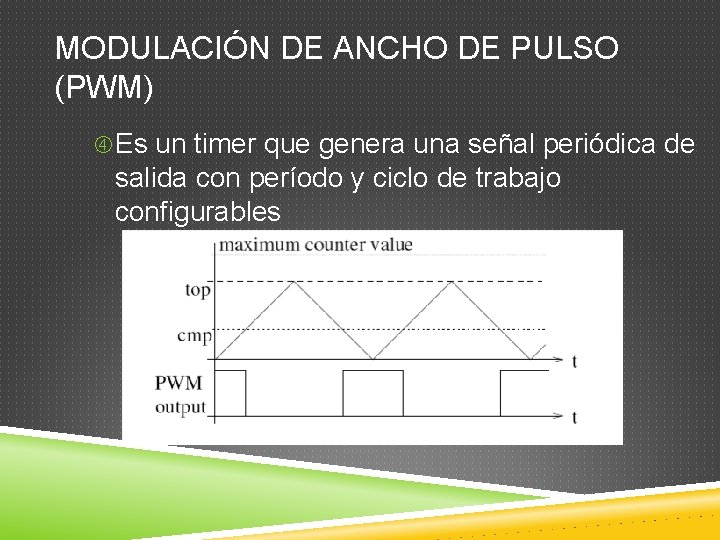

MODULACIÓN DE ANCHO DE PULSO (PWM) Es un timer que genera una señal periódica de salida con período y ciclo de trabajo configurables

MODULACIÓN DE ANCHO DE PULSO (PWM) Además de su uso como CDA, los PWM se usan para controlar ABS en autos, niveles de iluminación en LCDs, control de motores, etc.

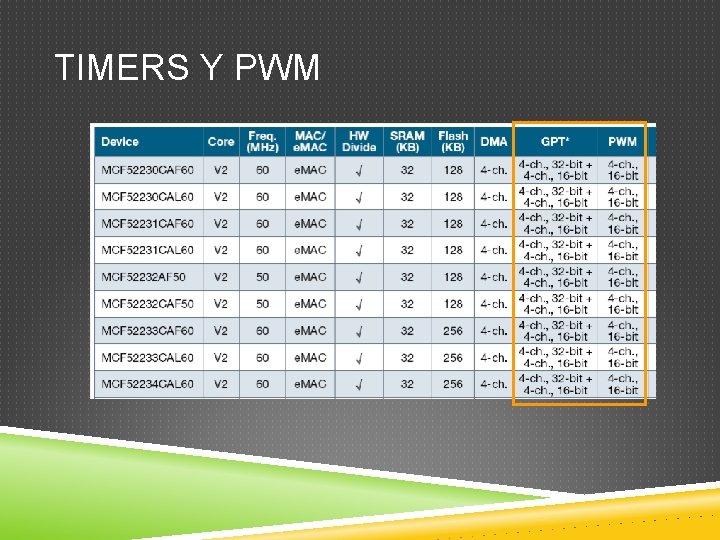

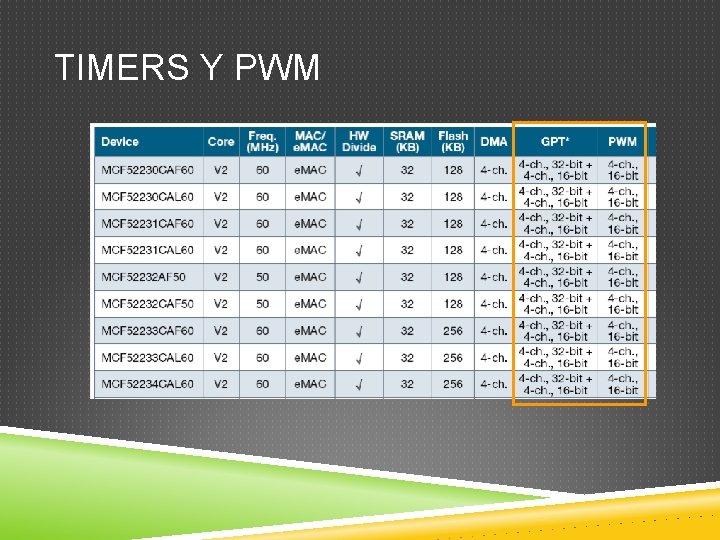

TIMERS Y PWM

INTRODUCCIÓN A LOS MICROCONTROLADORES Introducción Arquitectura Memoria I/O Interrupciones Timers Interfaces y Otros Periféricos

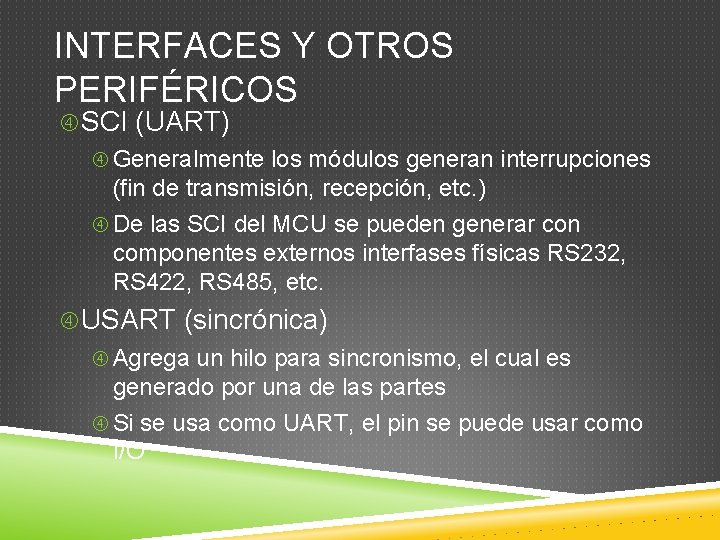

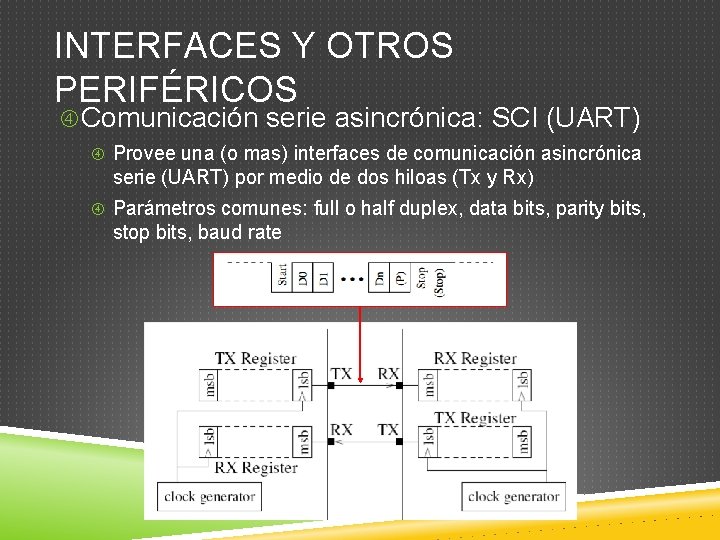

INTERFACES Y OTROS PERIFÉRICOS SCI (UART) Generalmente los módulos generan interrupciones (fin de transmisión, recepción, etc. ) De las SCI del MCU se pueden generar con componentes externos interfases físicas RS 232, RS 422, RS 485, etc. USART (sincrónica) Agrega un hilo para sincronismo, el cual es generado por una de las partes Si se usa como UART, el pin se puede usar como I/O

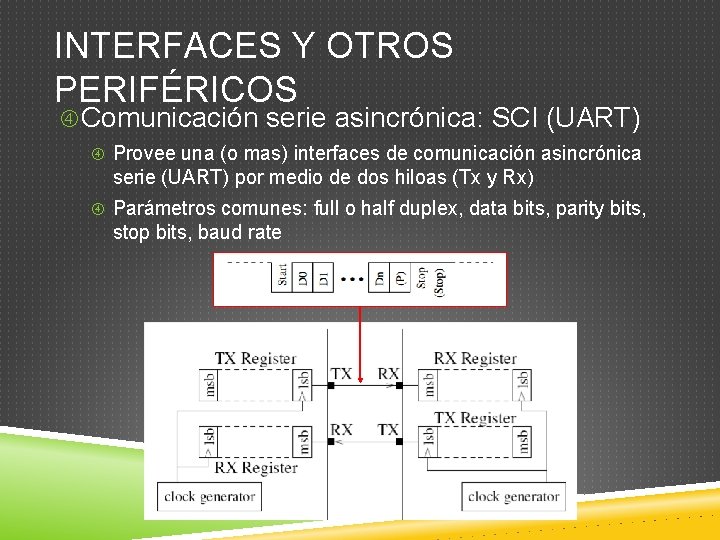

INTERFACES Y OTROS PERIFÉRICOS Comunicación serie asincrónica: SCI (UART) Provee una (o mas) interfaces de comunicación asincrónica serie (UART) por medio de dos hiloas (Tx y Rx) Parámetros comunes: full o half duplex, data bits, parity bits, stop bits, baud rate

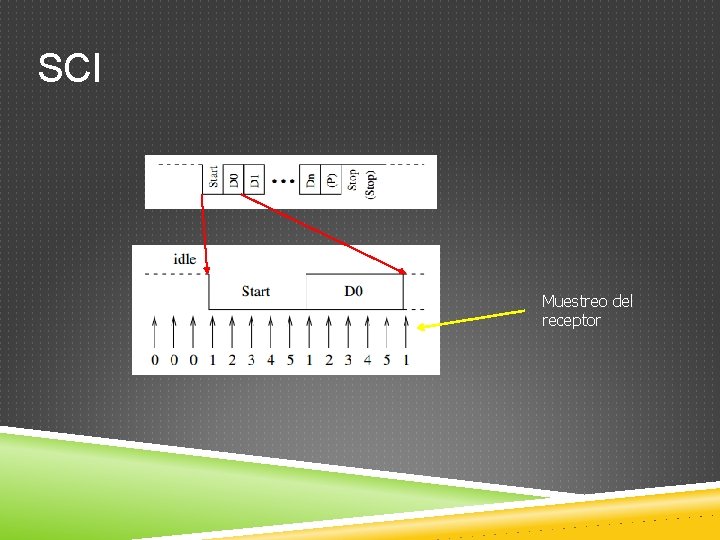

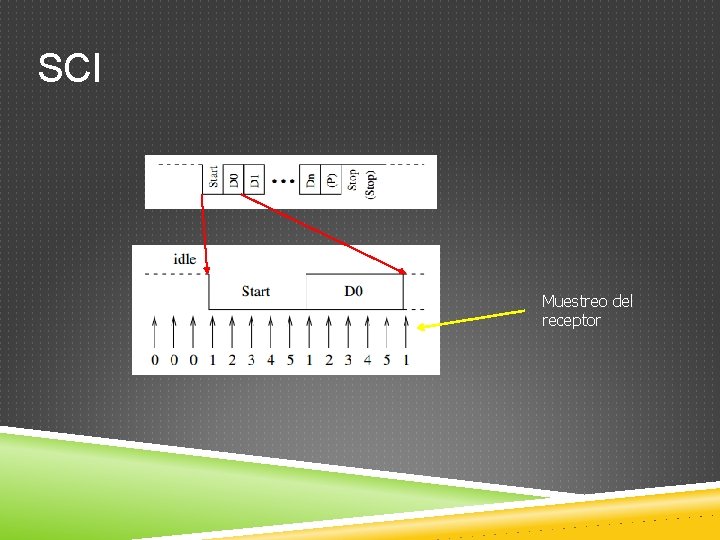

SCI Muestreo del receptor

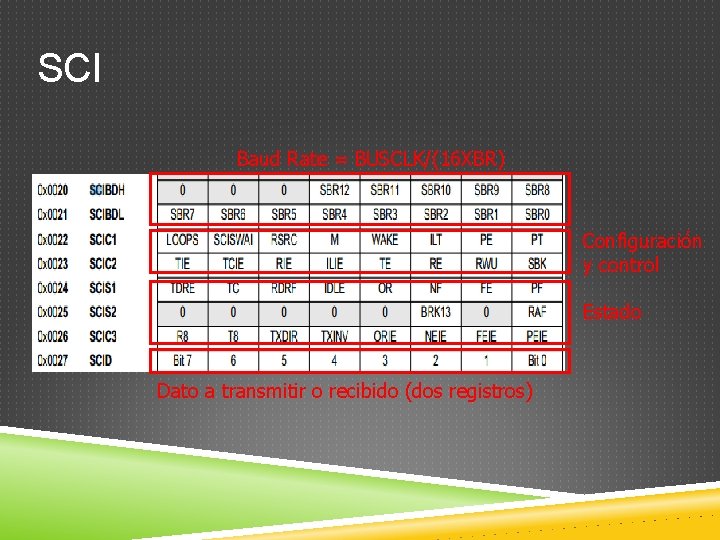

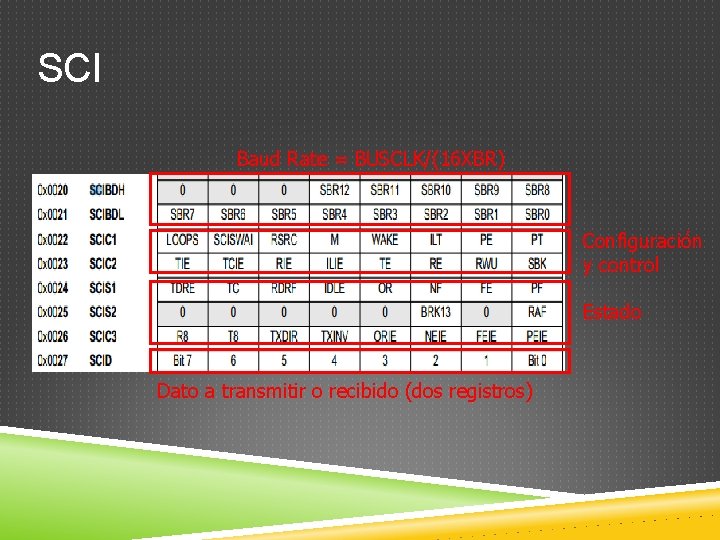

SCI Baud Rate = BUSCLK/(16 XBR) Configuración y control Estado Dato a transmitir o recibido (dos registros)

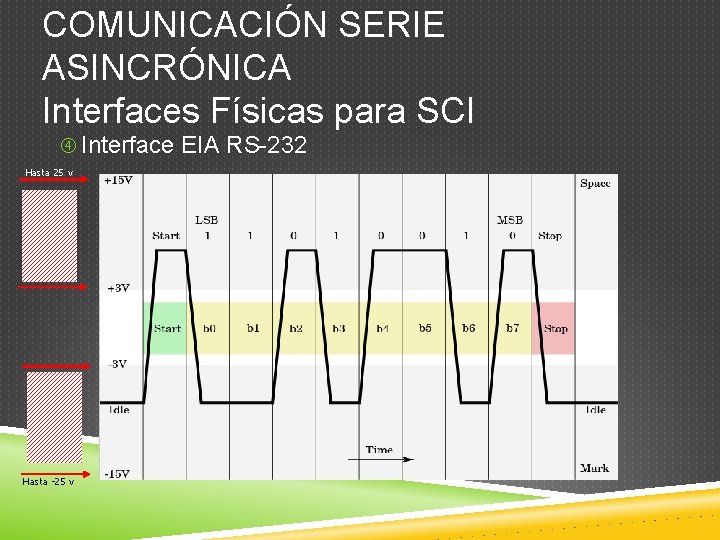

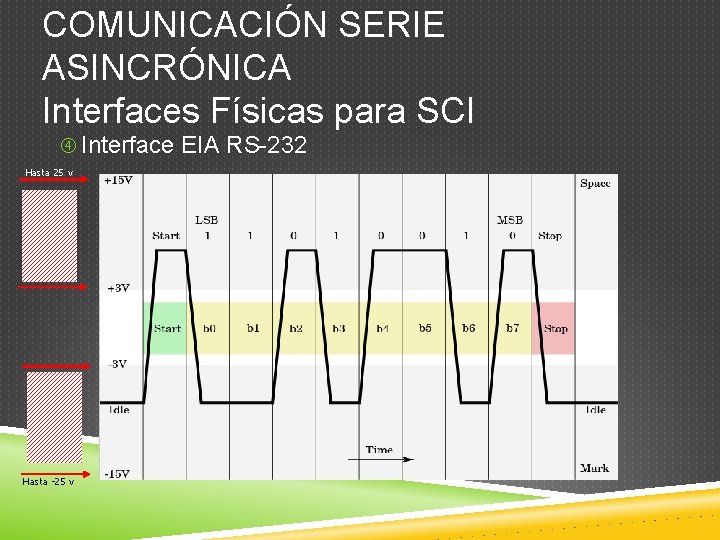

COMUNICACIÓN SERIE ASINCRÓNICA Interfaces Físicas para SCI Interface EIA RS-232 Hasta 25 v Hasta -25 v

COMUNICACIÓN SERIE ASINCRÓNICA Interface EIA RS-232 Cableado: de 3 a 10 hilos Longitud máxima por standard: 15 m o 2500 p. F (@9600 bps) Baud Rate (bps) Longitud (aprox. ) Susceptible al ruido 56000 2, 5 38400 3, 7 19200 7, 5 9600 15 4800 30 2400 60

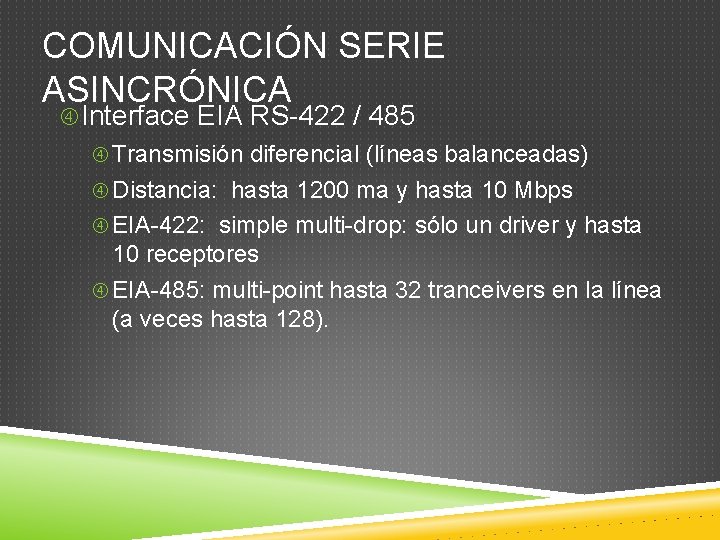

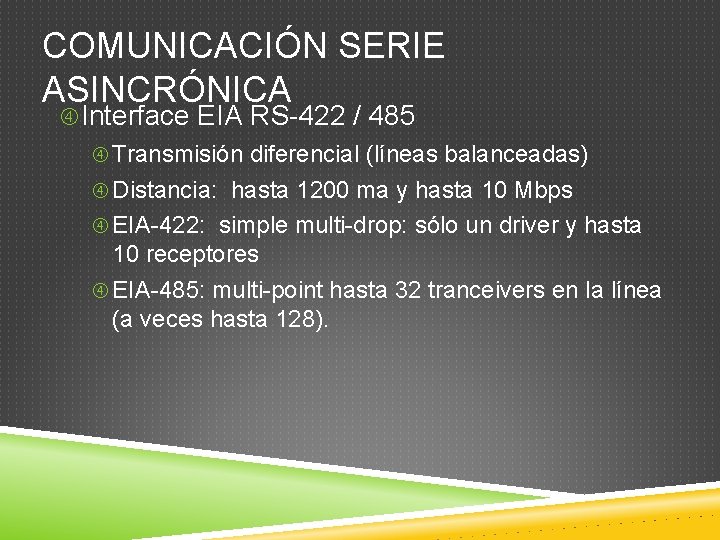

COMUNICACIÓN SERIE ASINCRÓNICA Interface EIA RS-422 / 485 Transmisión diferencial (líneas balanceadas) Distancia: hasta 1200 ma y hasta 10 Mbps EIA-422: simple multi-drop: sólo un driver y hasta 10 receptores EIA-485: multi-point hasta 32 tranceivers en la línea (a veces hasta 128).

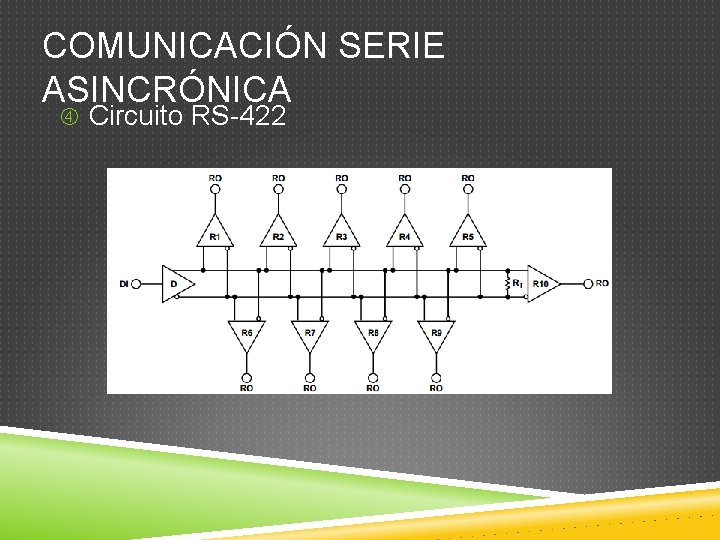

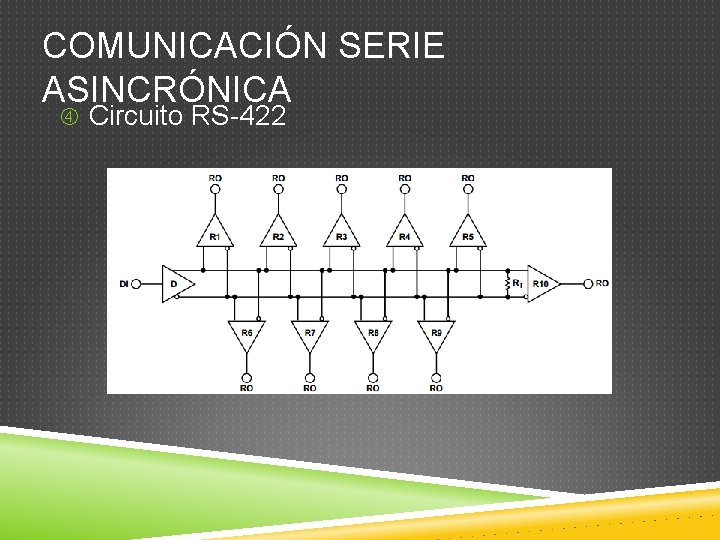

COMUNICACIÓN SERIE ASINCRÓNICA Circuito RS-422

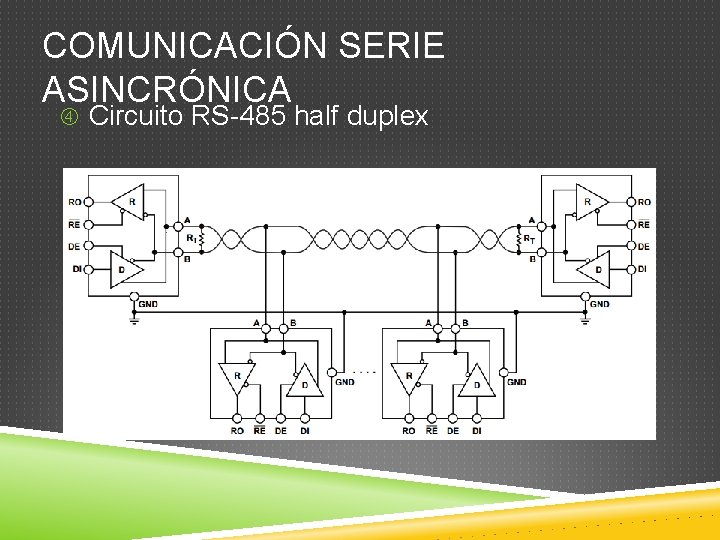

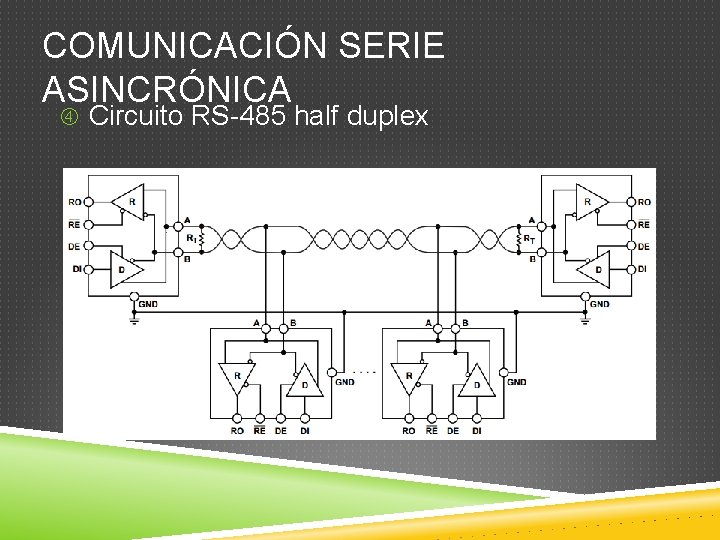

COMUNICACIÓN SERIE ASINCRÓNICA Circuito RS-485 half duplex

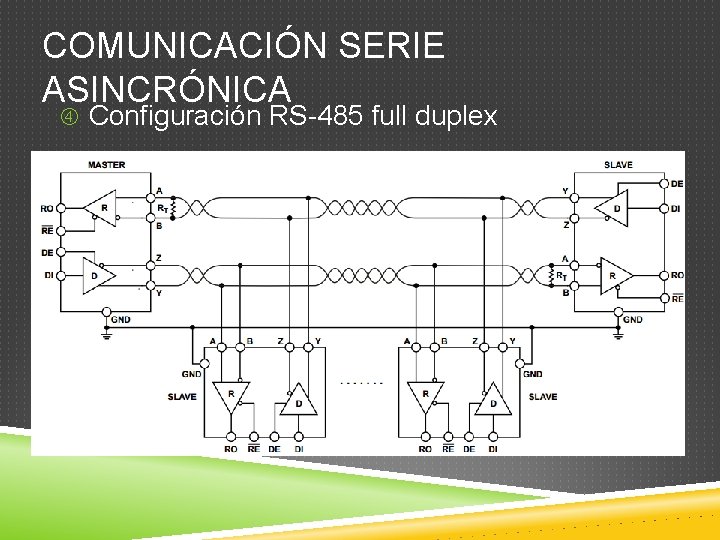

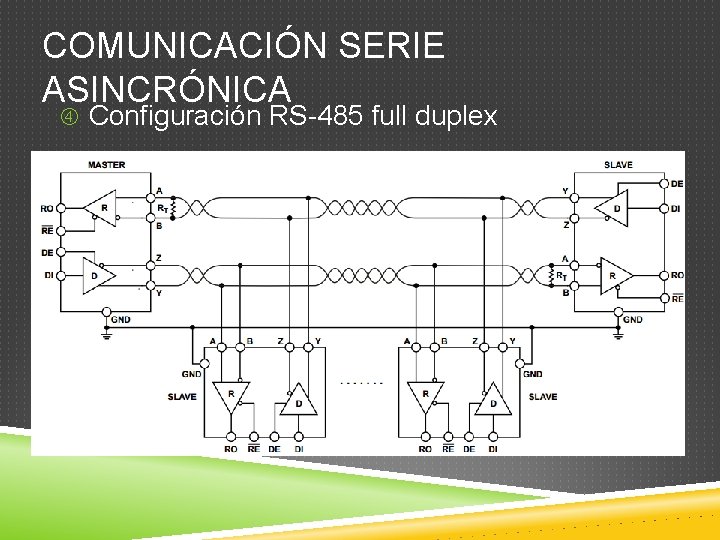

COMUNICACIÓN SERIE ASINCRÓNICA Configuración RS-485 full duplex

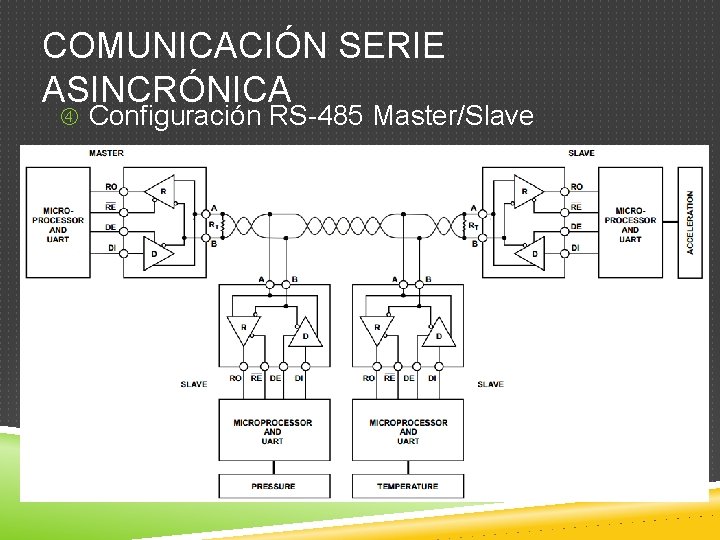

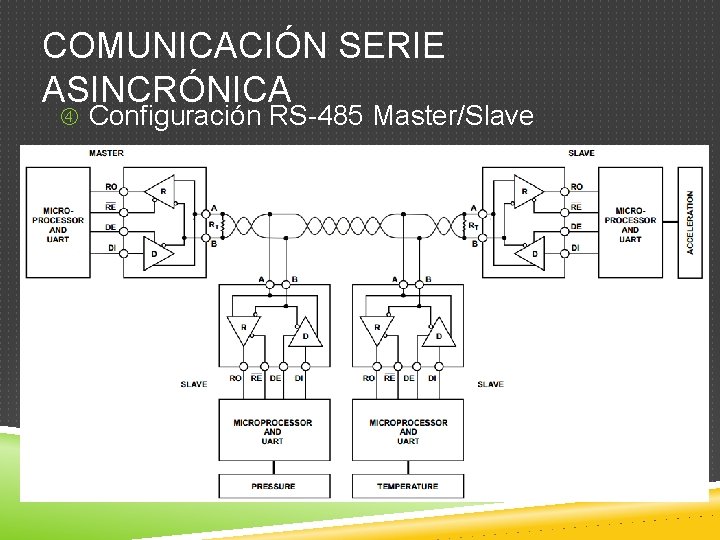

COMUNICACIÓN SERIE ASINCRÓNICA Configuración RS-485 Master/Slave

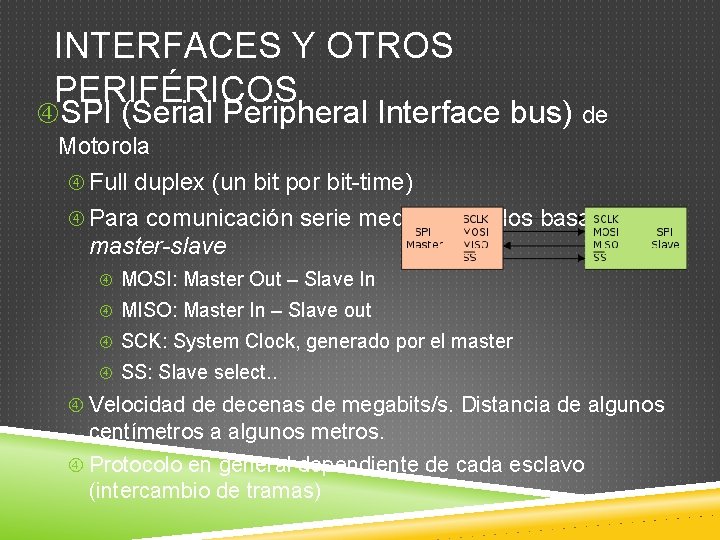

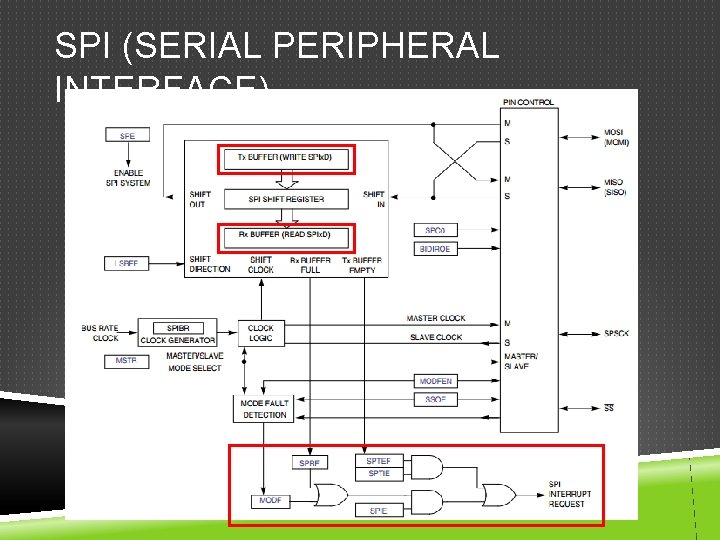

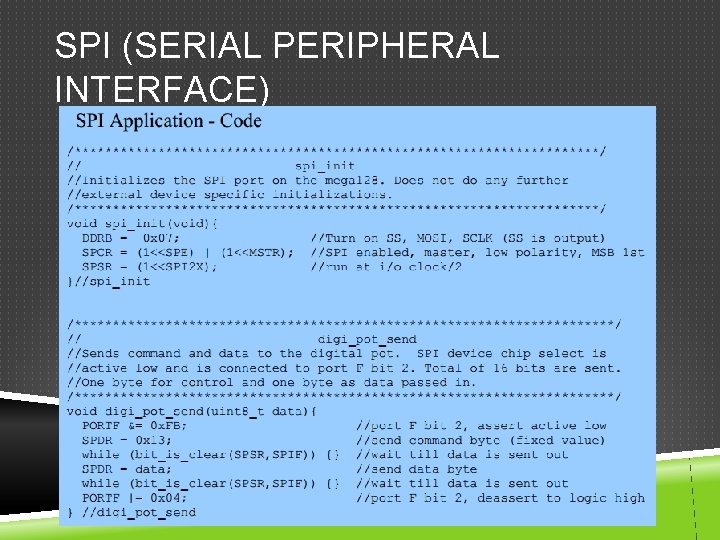

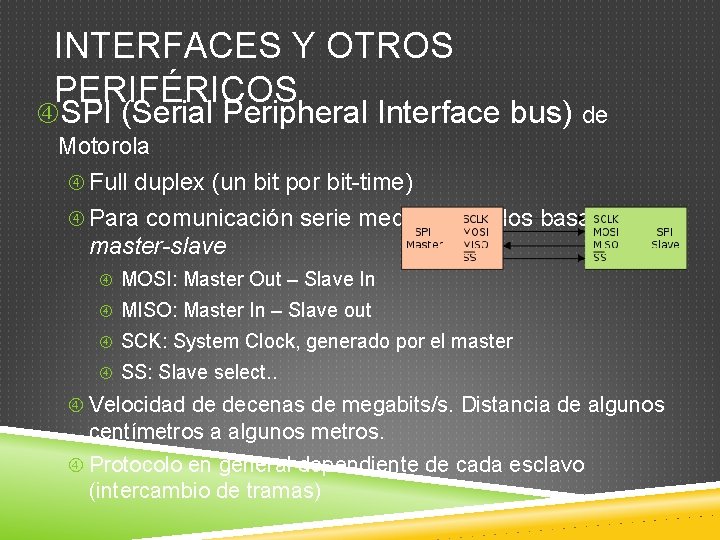

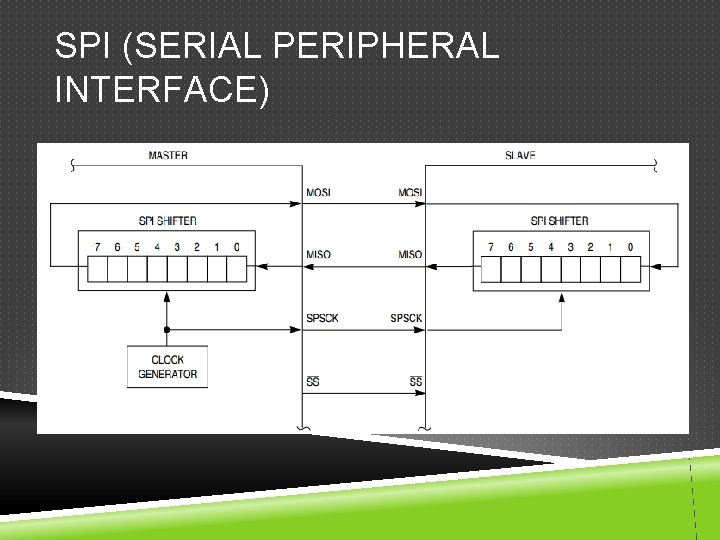

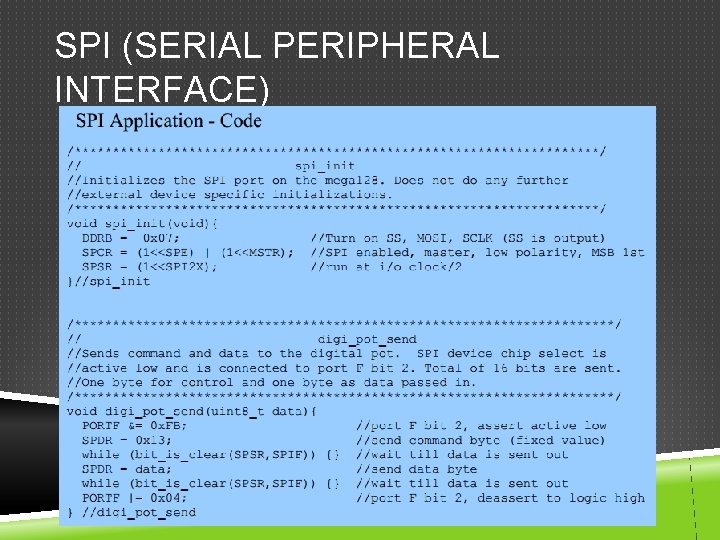

INTERFACES Y OTROS PERIFÉRICOS SPI (Serial Peripheral Interface bus) de Motorola Full duplex (un bit por bit-time) Para comunicación serie mediante 4 hilos basada en master-slave MOSI: Master Out – Slave In MISO: Master In – Slave out SCK: System Clock, generado por el master SS: Slave select. . Velocidad de decenas de megabits/s. Distancia de algunos centímetros a algunos metros. Protocolo en general dependiente de cada esclavo (intercambio de tramas)

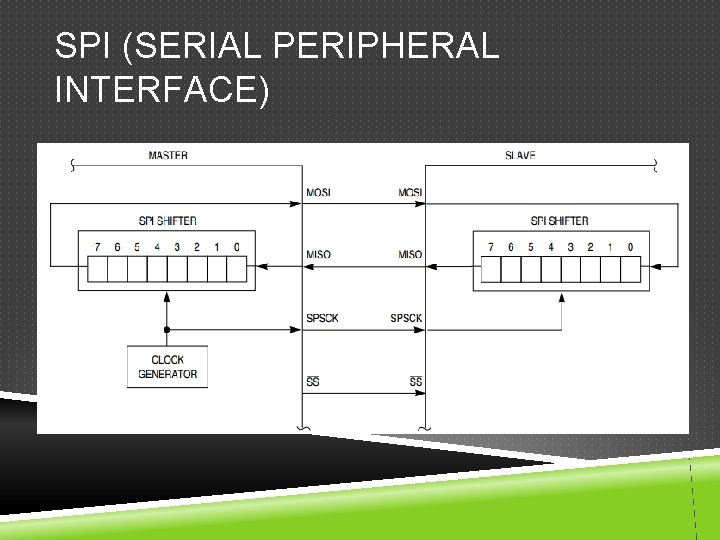

SPI (SERIAL PERIPHERAL INTERFACE)

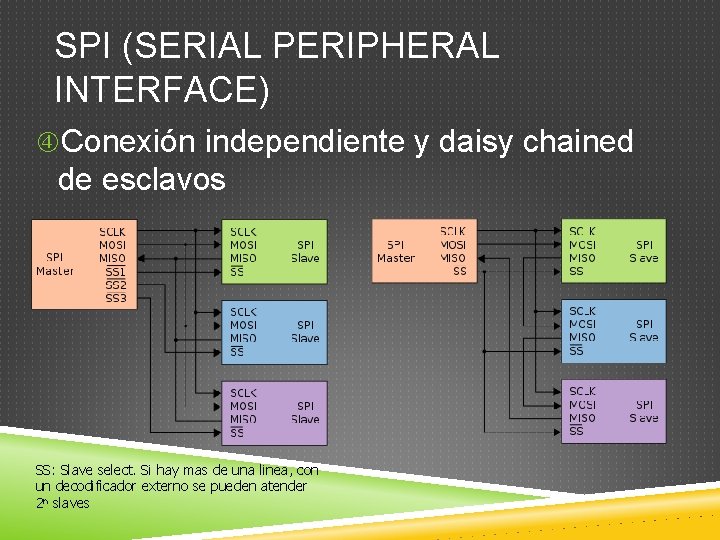

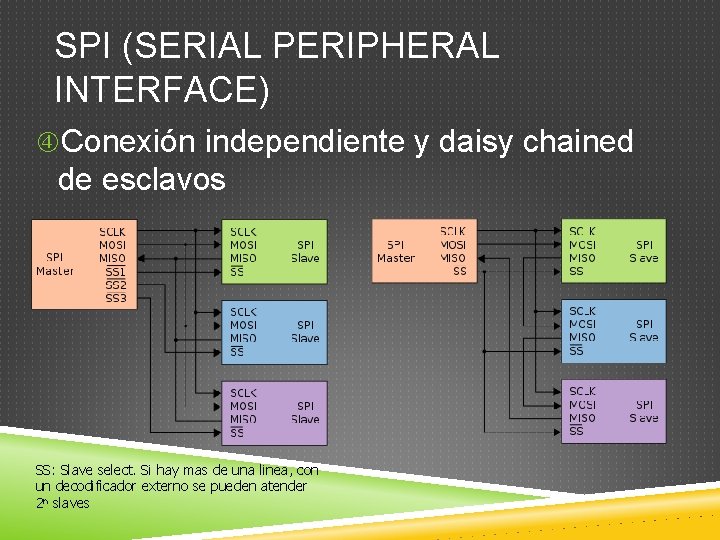

SPI (SERIAL PERIPHERAL INTERFACE) Conexión independiente y daisy chained de esclavos SS: Slave select. Si hay mas de una linea, con un decodificador externo se pueden atender 2 n slaves

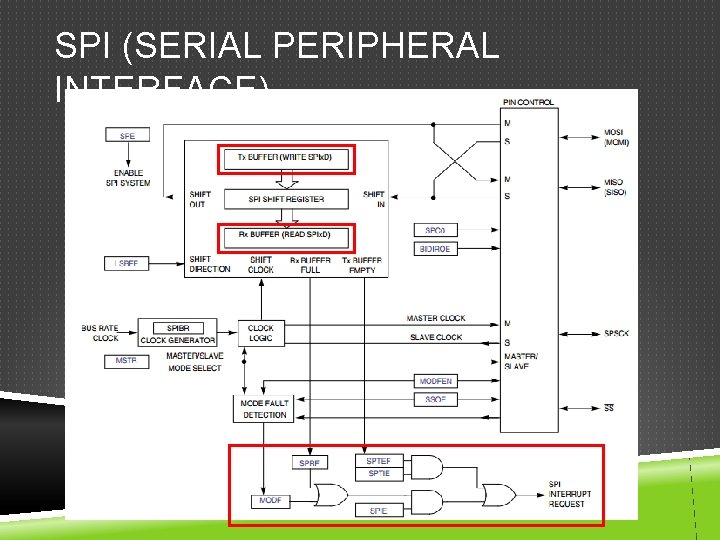

SPI (SERIAL PERIPHERAL INTERFACE)

SPI (SERIAL PERIPHERAL INTERFACE)

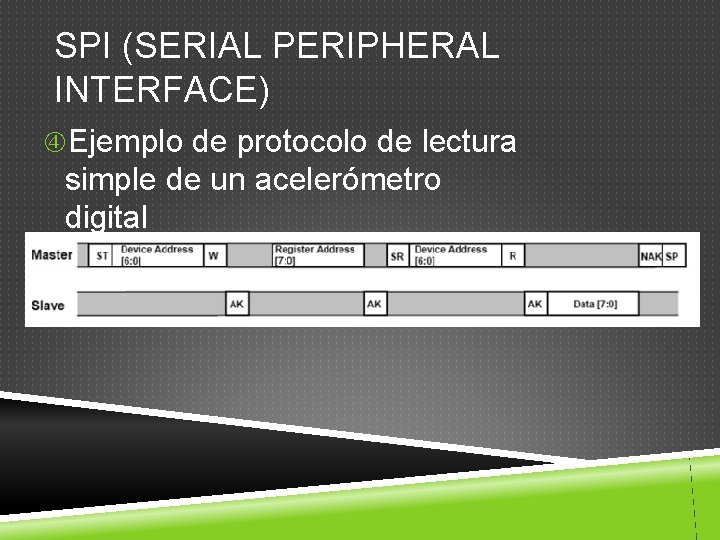

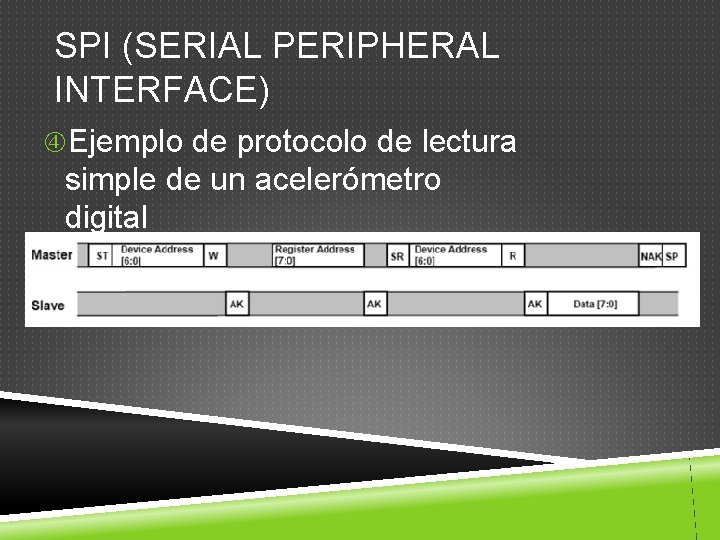

SPI (SERIAL PERIPHERAL INTERFACE) Ejemplo de protocolo de lectura simple de un acelerómetro digital

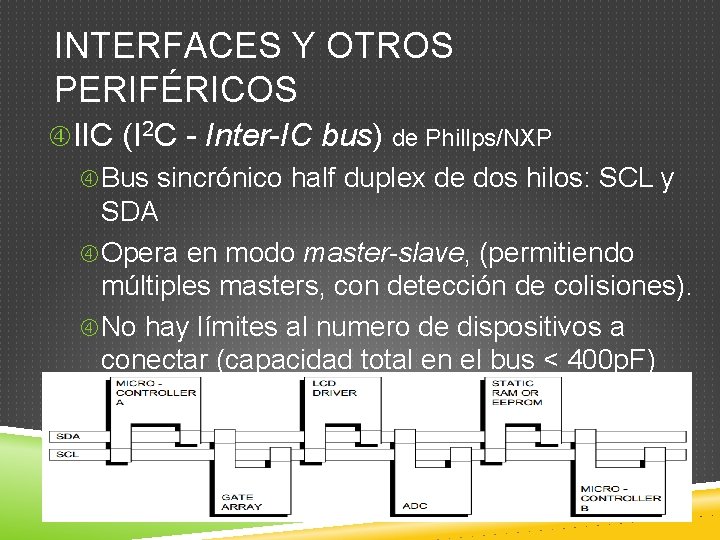

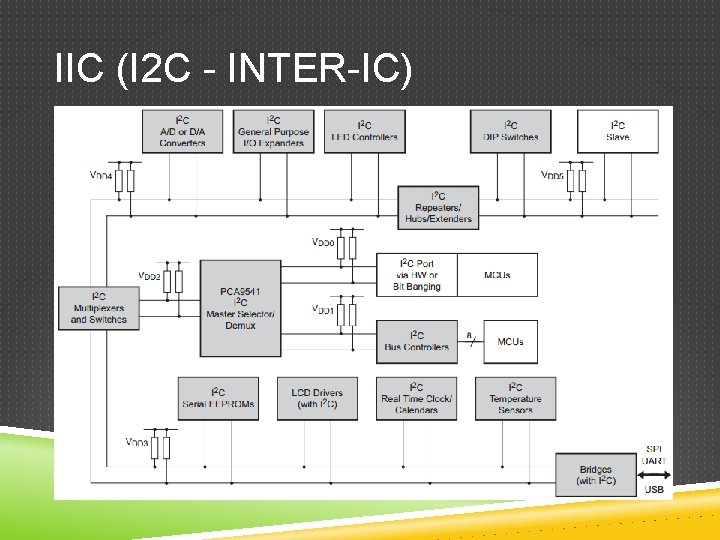

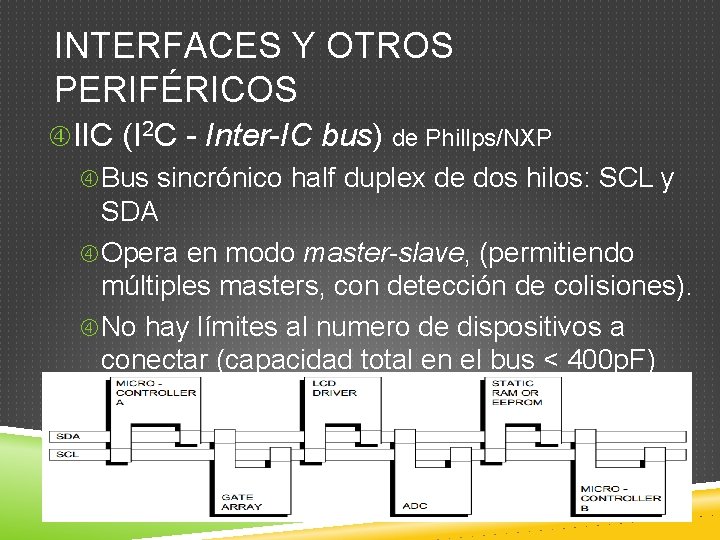

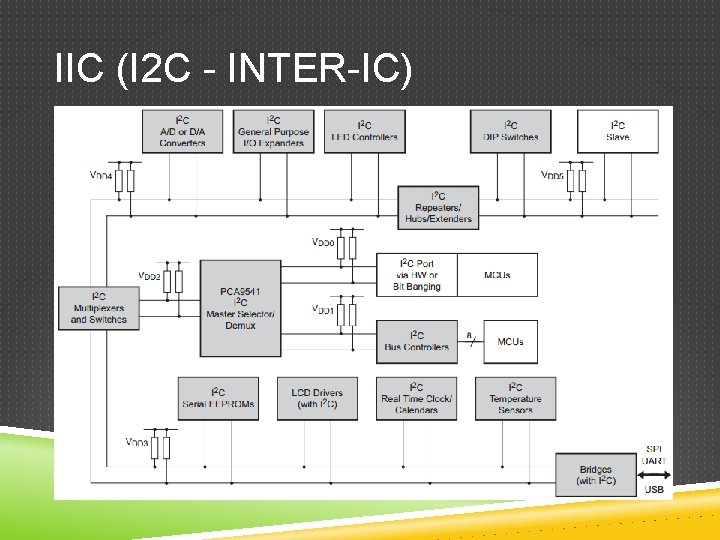

INTERFACES Y OTROS PERIFÉRICOS IIC (I 2 C - Inter-IC bus) de Phillps/NXP Bus sincrónico half duplex de dos hilos: SCL y SDA Opera en modo master-slave, (permitiendo múltiples masters, con detección de colisiones). No hay límites al numero de dispositivos a conectar (capacidad total en el bus < 400 p. F)

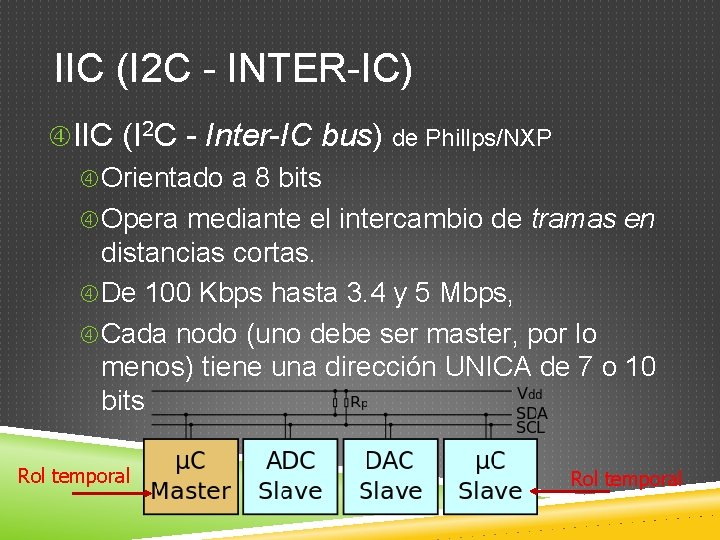

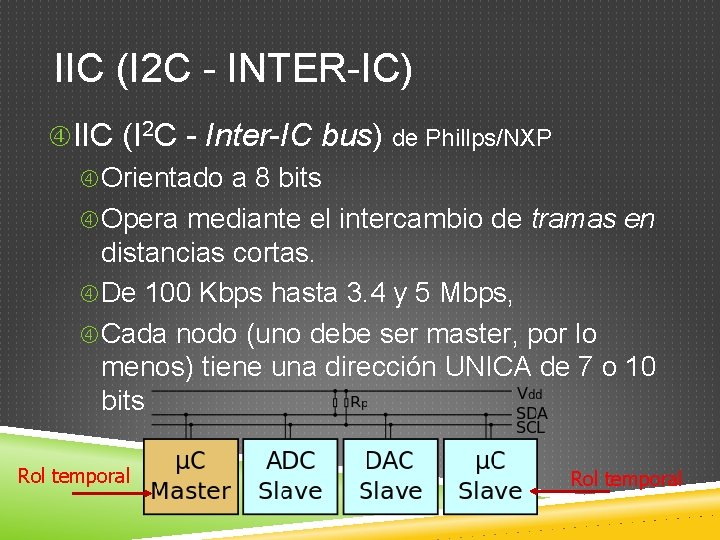

IIC (I 2 C - INTER-IC) IIC (I 2 C - Inter-IC bus) de Phillps/NXP Orientado a 8 bits Opera mediante el intercambio de tramas en distancias cortas. De 100 Kbps hasta 3. 4 y 5 Mbps, Cada nodo (uno debe ser master, por lo menos) tiene una dirección UNICA de 7 o 10 bits Rol temporal

IIC (I 2 C - INTER-IC)

IIC (I 2 C - INTER-IC) Definiciones Transmisor: el dispositivo que envía datos al bus Receptor: el dispositivo que recibe datos desde el bus. Master: el dispositivo que inicia una transferencia, genera el clock y termina la transferecnia. Slave: el dispositivo direccionado por un master.

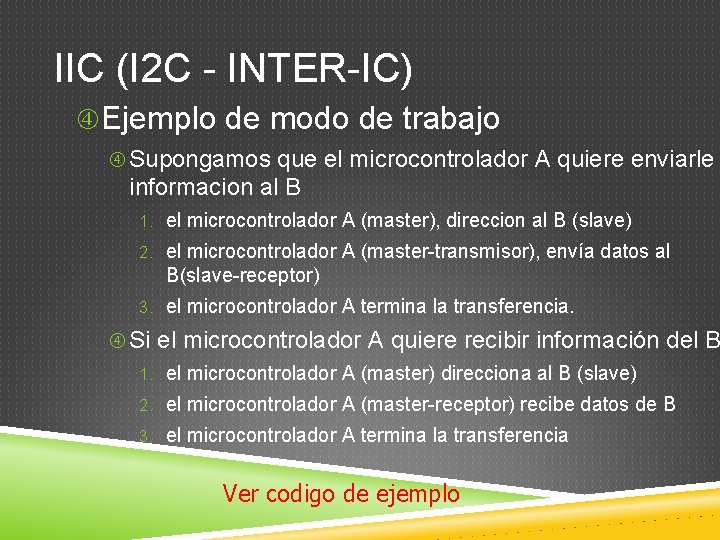

IIC (I 2 C - INTER-IC) Ejemplo de modo de trabajo Supongamos que el microcontrolador A quiere enviarle informacion al B 1. el microcontrolador A (master), direccion al B (slave) 2. el microcontrolador A (master-transmisor), envía datos al B(slave-receptor) 3. el microcontrolador A termina la transferencia. Si el microcontrolador A quiere recibir información del B 1. el microcontrolador A (master) direcciona al B (slave) 2. el microcontrolador A (master-receptor) recibe datos de B 3. el microcontrolador A termina la transferencia Ver codigo de ejemplo

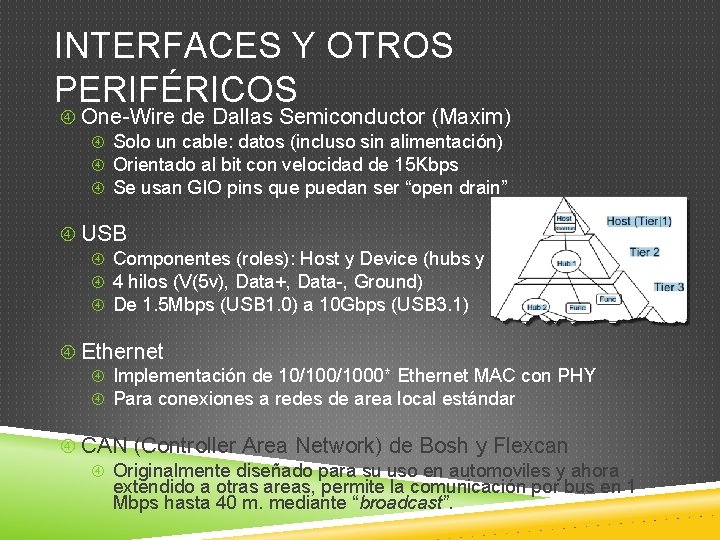

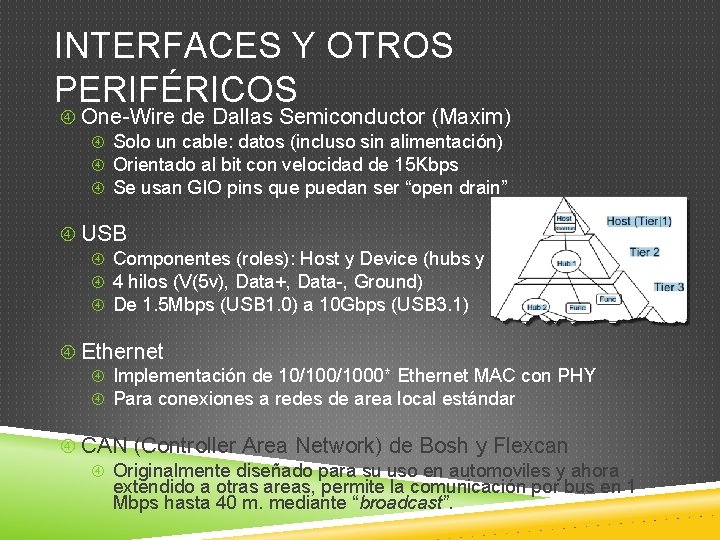

INTERFACES Y OTROS PERIFÉRICOS One-Wire de Dallas Semiconductor (Maxim) Solo un cable: datos (incluso sin alimentación) Orientado al bit con velocidad de 15 Kbps Se usan GIO pins que puedan ser “open drain” USB Componentes (roles): Host y Device (hubs y function) 4 hilos (V(5 v), Data+, Data-, Ground) De 1. 5 Mbps (USB 1. 0) a 10 Gbps (USB 3. 1) Ethernet Implementación de 10/1000* Ethernet MAC con PHY Para conexiones a redes de area local estándar CAN (Controller Area Network) de Bosh y Flexcan Originalmente diseñado para su uso en automoviles y ahora extendido a otras areas, permite la comunicación por bus en 1 Mbps hasta 40 m. mediante “broadcast”.

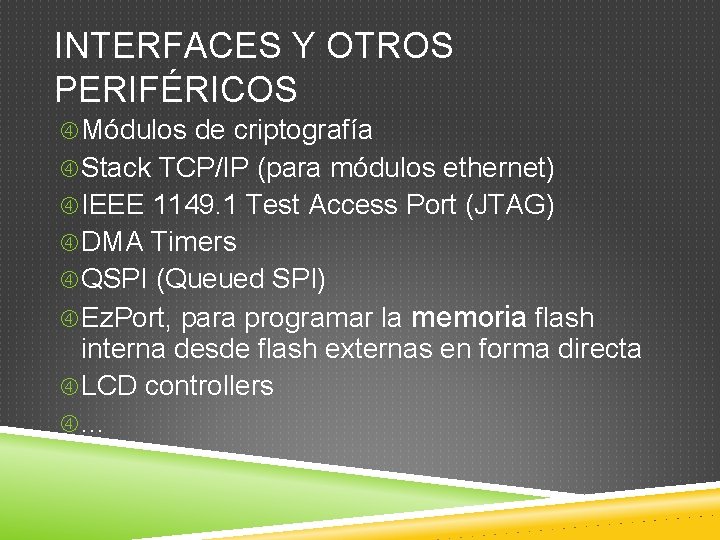

INTERFACES Y OTROS PERIFÉRICOS Módulos de criptografía Stack TCP/IP (para módulos ethernet) IEEE 1149. 1 Test Access Port (JTAG) DMA Timers QSPI (Queued SPI) Ez. Port, para programar la memoria flash interna desde flash externas en forma directa LCD controllers . . .

INTERFACES Y OTROS PERIFÉRICOS

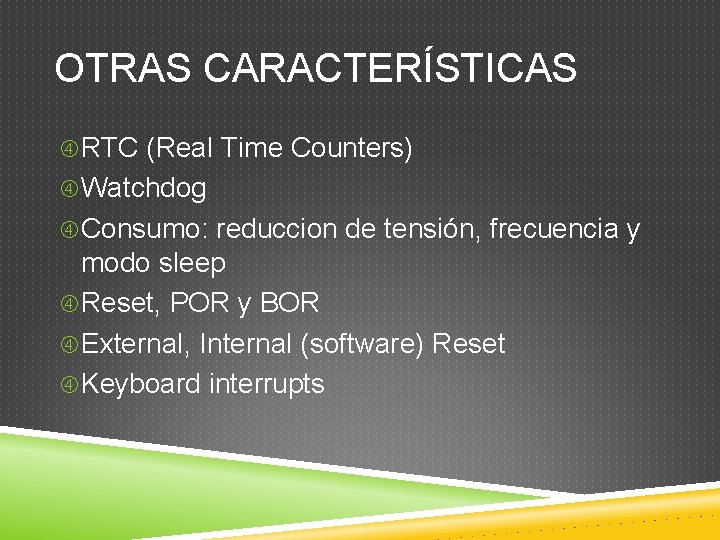

OTRAS CARACTERÍSTICAS RTC (Real Time Counters) Watchdog Consumo: reduccion de tensión, frecuencia y modo sleep Reset, POR y BOR External, Internal (software) Reset Keyboard interrupts

ARQUITECTURA

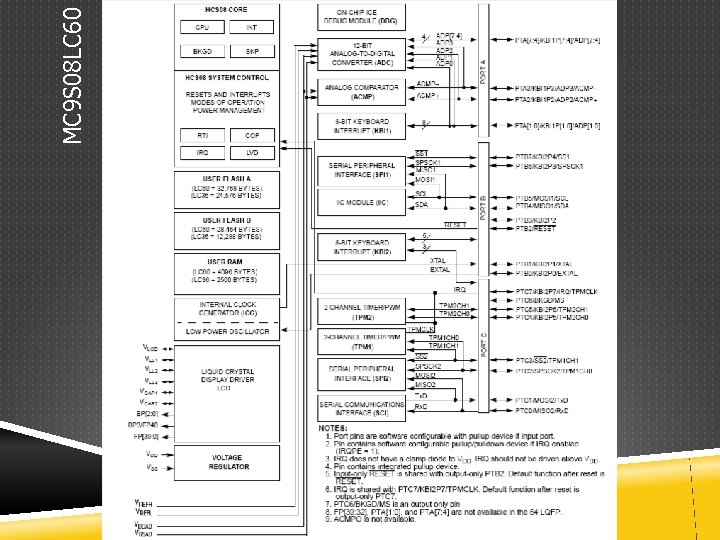

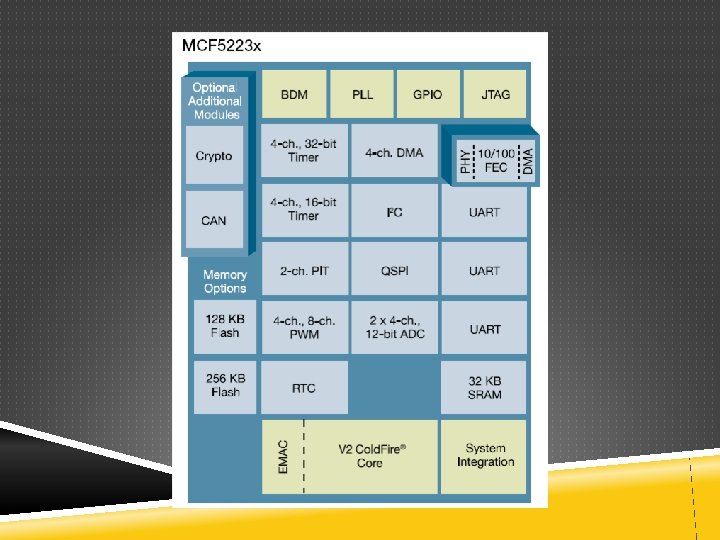

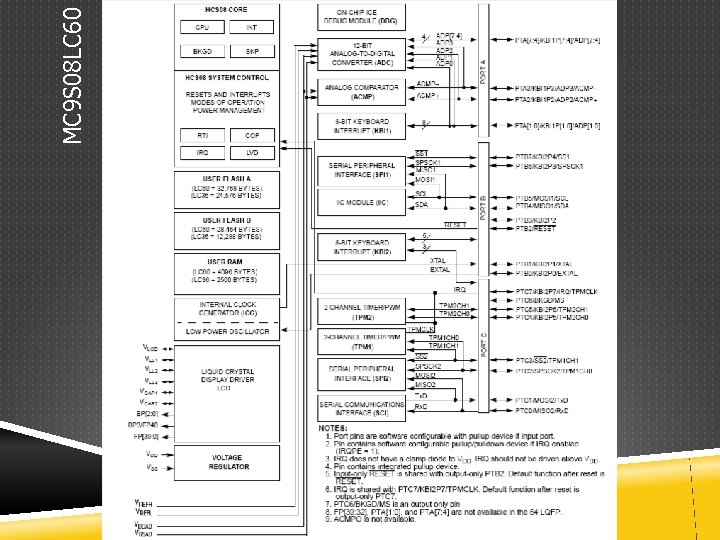

MC 9 S 08 LC 60

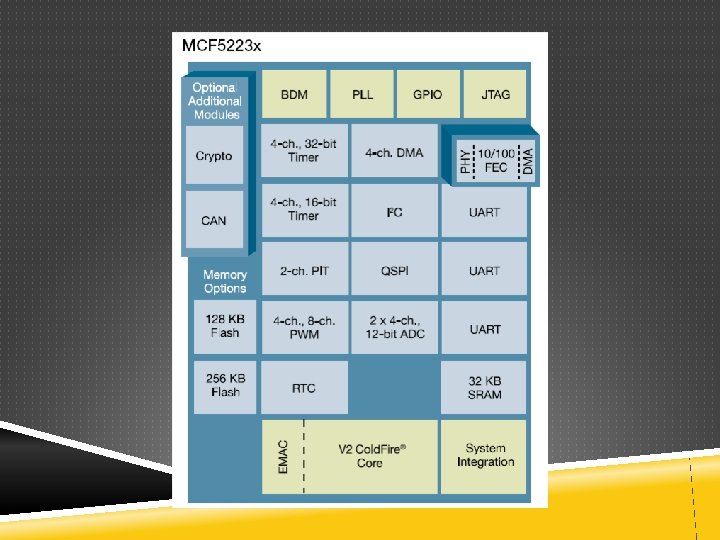

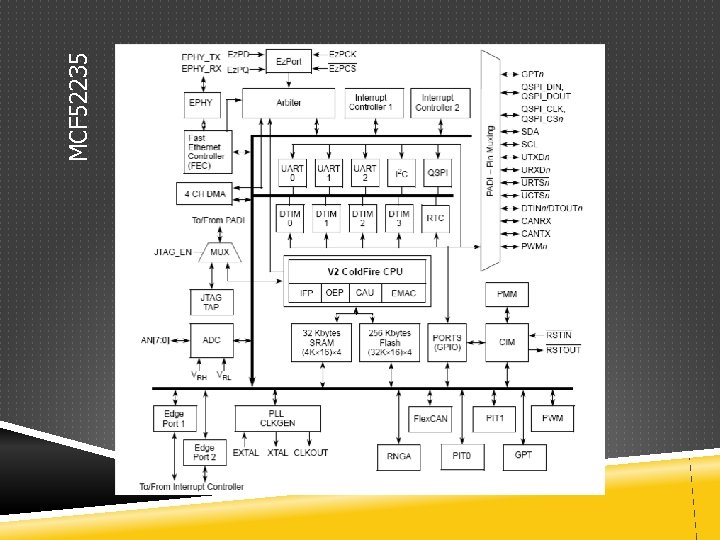

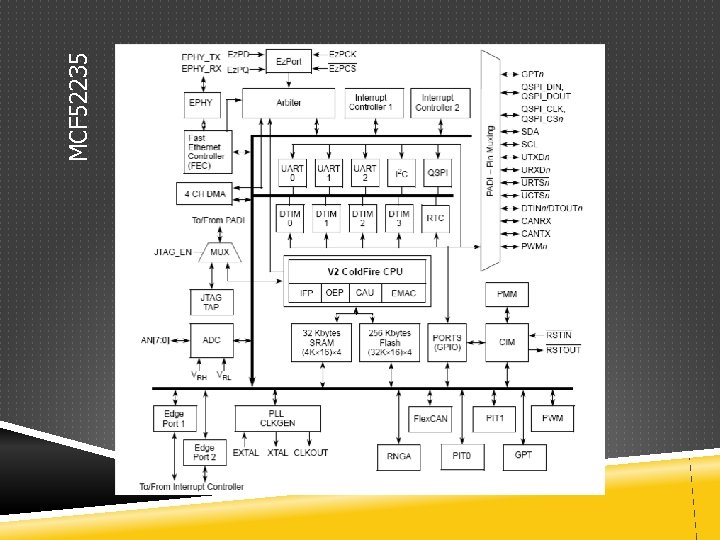

MCF 52235