Microcomputer Systems 1 Visual DSP Development Tool Veton

![C Source with Alternate Sections foo. doj foo. c section (“sdram 0”) int array[256]; C Source with Alternate Sections foo. doj foo. c section (“sdram 0”) int array[256];](https://slidetodoc.com/presentation_image/73a5584d59da543255fe4ef27f5c71c0/image-12.jpg)

- Slides: 43

Microcomputer Systems 1 Visual DSP++ Development Tool Veton Këpuska

Goals u u u Basic Software Build Process in Visual DSP++ Specific Blackfin issues Optimization Example using Built-In Optimizer and Cache. 9/25/2020 Veton Këpuska 2

Visual DSP++ Development Tool Outline u Software Build Process in Visual DSP++ u Explanation of Linker Description File u Programming Blackfin Processors In C u Developing Efficient C Code u Ogg Vorbis Tremor Example 9/25/2020 Veton Këpuska 3

Software Build Process in Visual. DSP++ Veton Këpuska

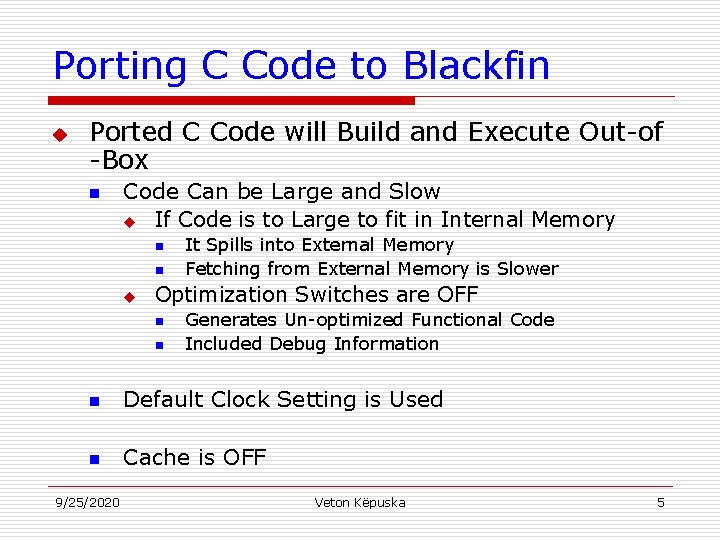

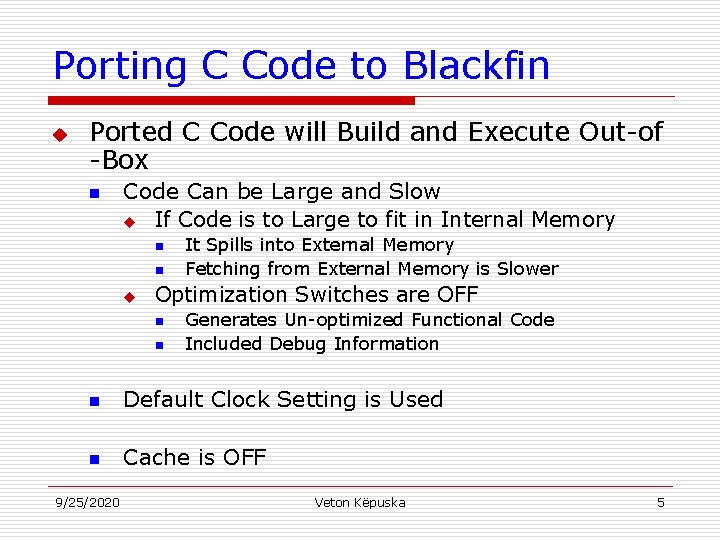

Porting C Code to Blackfin u Ported C Code will Build and Execute Out-of -Box n Code Can be Large and Slow u If Code is to Large to fit in Internal Memory n n u It Spills into External Memory Fetching from External Memory is Slower Optimization Switches are OFF n n Generates Un-optimized Functional Code Included Debug Information n Default Clock Setting is Used n Cache is OFF 9/25/2020 Veton Këpuska 5

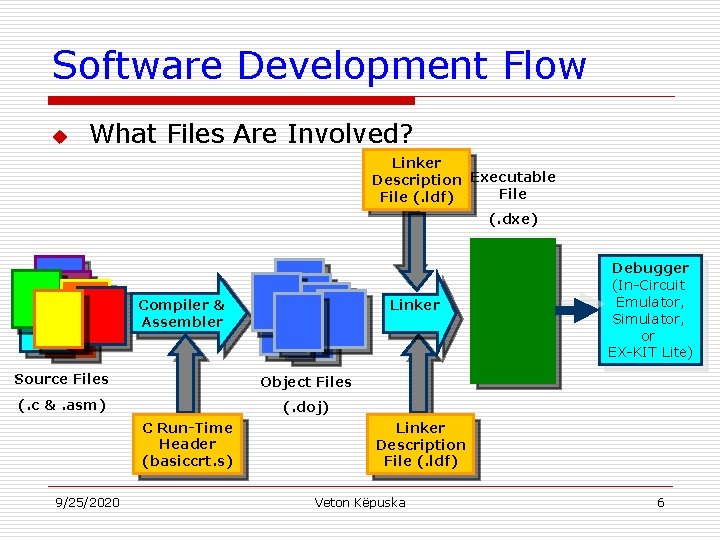

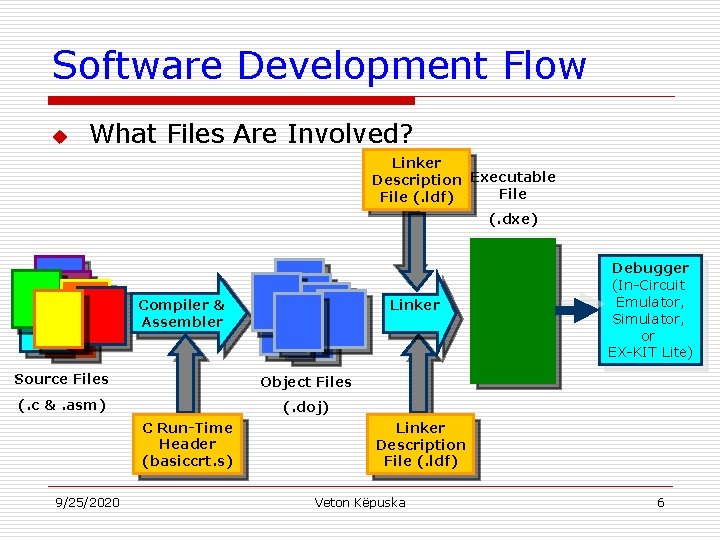

Software Development Flow u What Files Are Involved? Linker Description Executable File (. ldf) (. dxe) Compiler & Assembler Linker Source Files Object Files (. c &. asm) (. doj) C Run-Time Header (basiccrt. s) 9/25/2020 Debugger (In-Circuit Emulator, Simulator, or EX-KIT Lite) Linker Description File (. ldf) Veton Këpuska 6

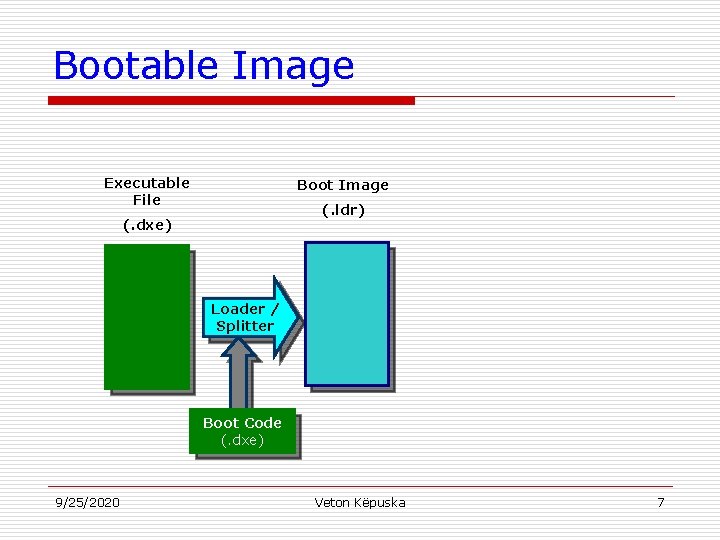

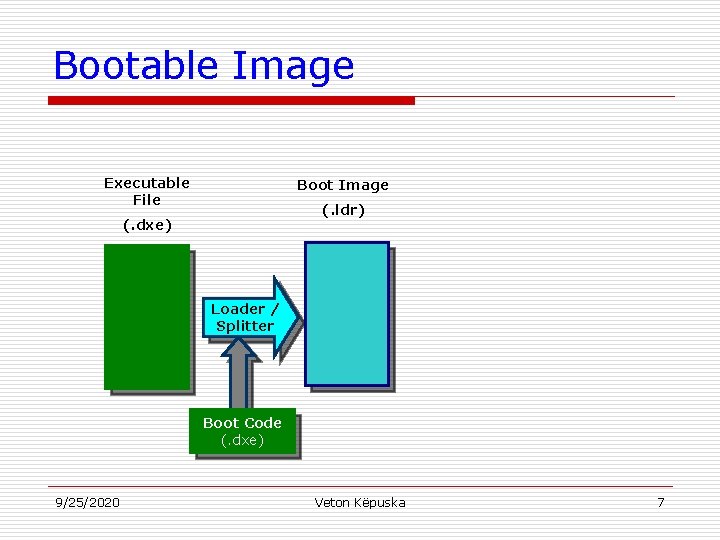

Bootable Image Executable File Boot Image (. ldr) (. dxe) Loader / Splitter Boot Code (. dxe) 9/25/2020 Veton Këpuska 7

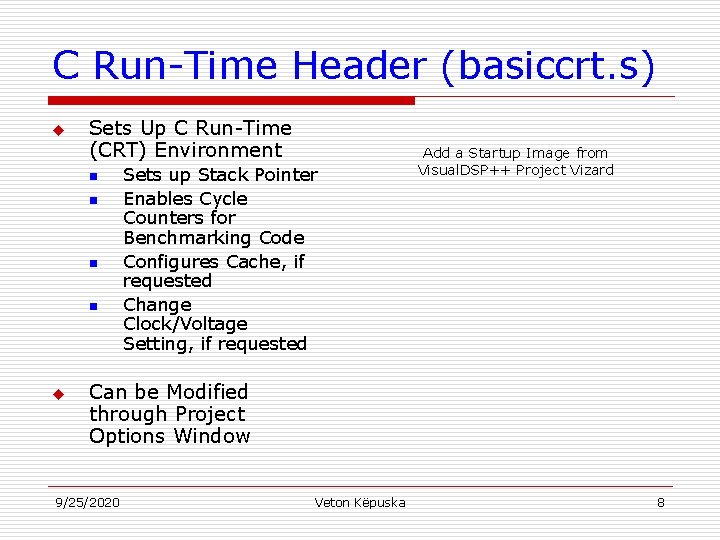

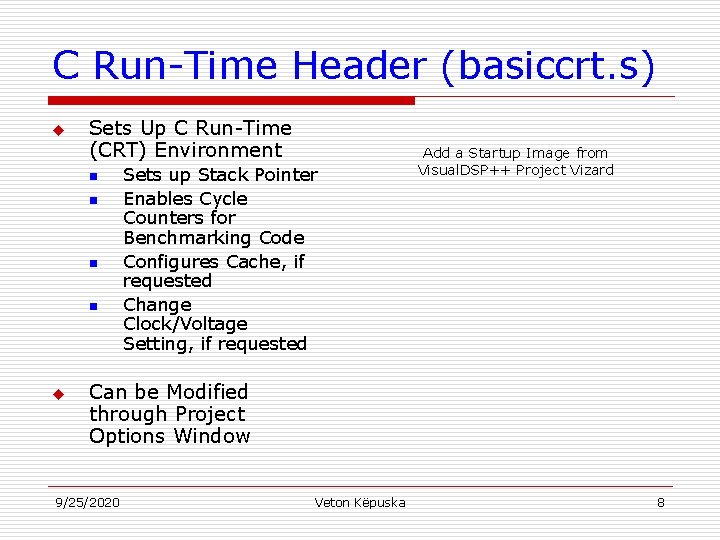

C Run-Time Header (basiccrt. s) u Sets Up C Run-Time (CRT) Environment n n u Sets up Stack Pointer Enables Cycle Counters for Benchmarking Code Configures Cache, if requested Change Clock/Voltage Setting, if requested Add a Startup Image from Visual. DSP++ Project Vizard Can be Modified through Project Options Window 9/25/2020 Veton Këpuska 8

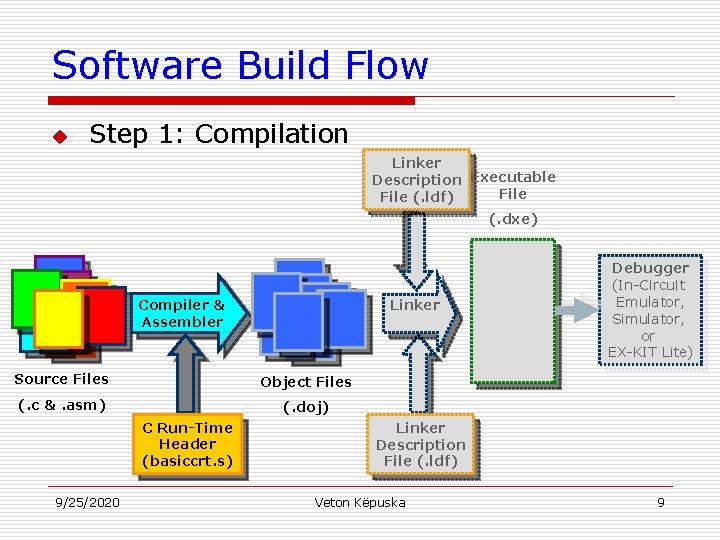

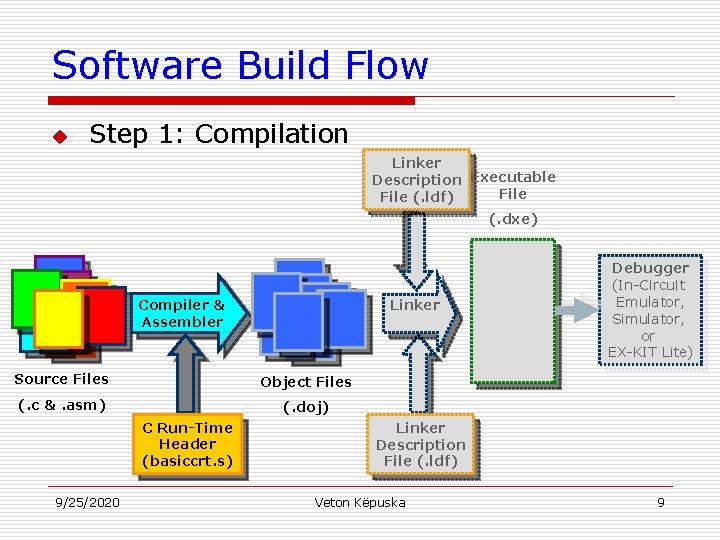

Software Build Flow u Step 1: Compilation Linker Description Executable File (. ldf) (. dxe) Compiler & Assembler Linker Source Files Object Files (. c &. asm) (. doj) C Run-Time Header (basiccrt. s) 9/25/2020 Debugger (In-Circuit Emulator, Simulator, or EX-KIT Lite) Linker Description File (. ldf) Veton Këpuska 9

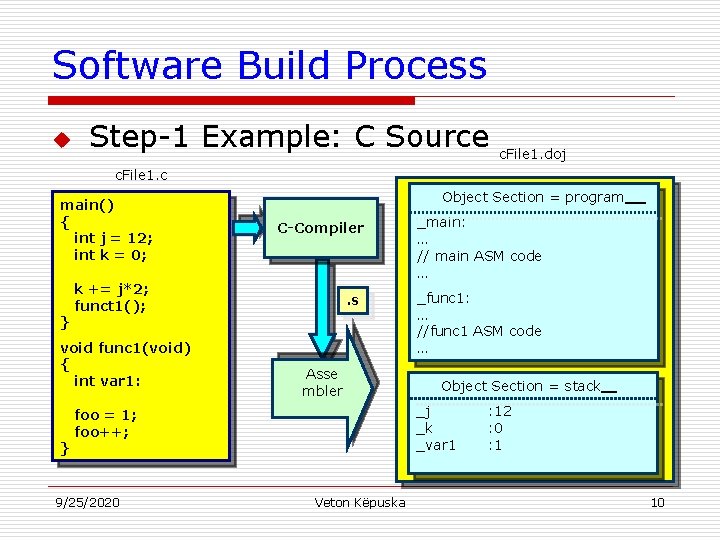

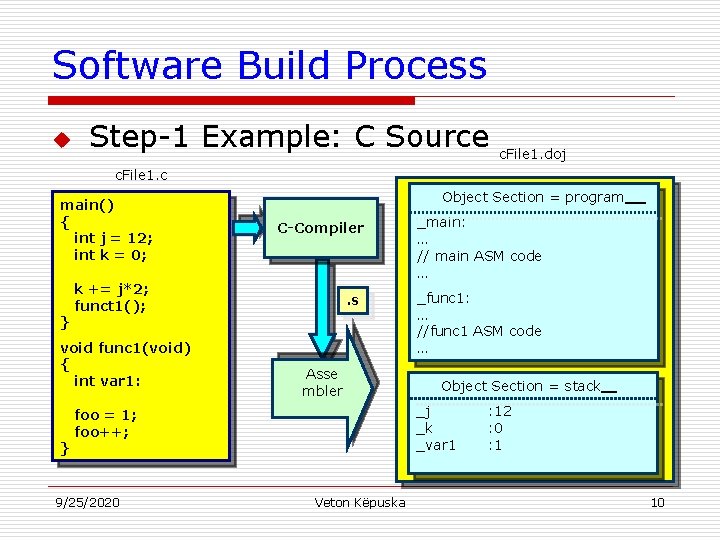

Software Build Process u Step-1 Example: C Source c. File 1. doj c. File 1. c main() { int j = 12; int k = 0; } C-Compiler k += j*2; funct 1(); void func 1(void) { int var 1: } Object Section = program . s Asse mbler _func 1: … //func 1 ASM code … Object Section = stack _j _k _var 1 foo = 1; foo++; 9/25/2020 _main: … // main ASM code … Veton Këpuska : 12 : 0 : 1 10

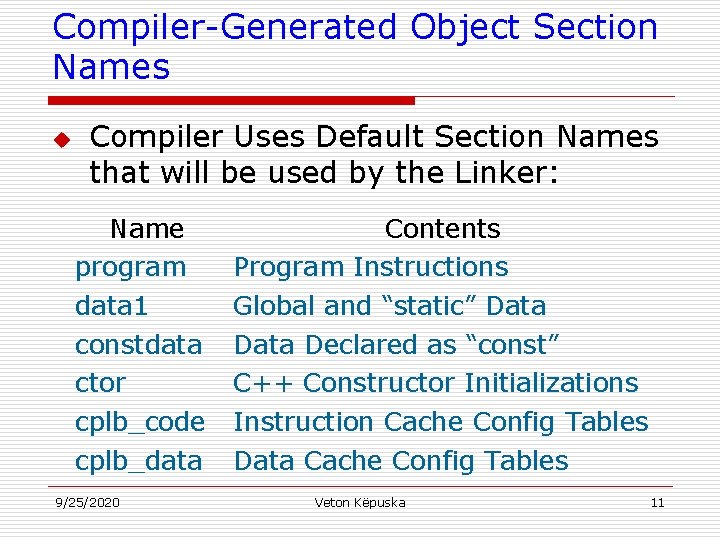

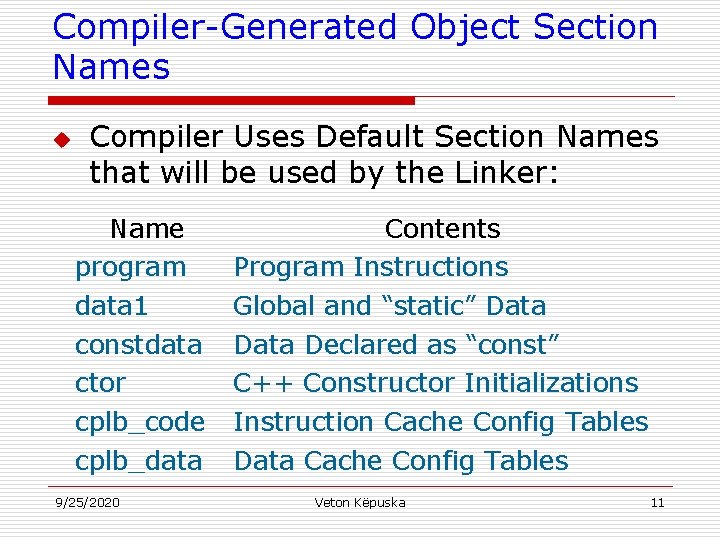

Compiler-Generated Object Section Names u Compiler Uses Default Section Names that will be used by the Linker: Name program data 1 constdata ctor cplb_code cplb_data 9/25/2020 Contents Program Instructions Global and “static” Data Declared as “const” C++ Constructor Initializations Instruction Cache Config Tables Data Cache Config Tables Veton Këpuska 11

![C Source with Alternate Sections foo doj foo c section sdram 0 int array256 C Source with Alternate Sections foo. doj foo. c section (“sdram 0”) int array[256];](https://slidetodoc.com/presentation_image/73a5584d59da543255fe4ef27f5c71c0/image-12.jpg)

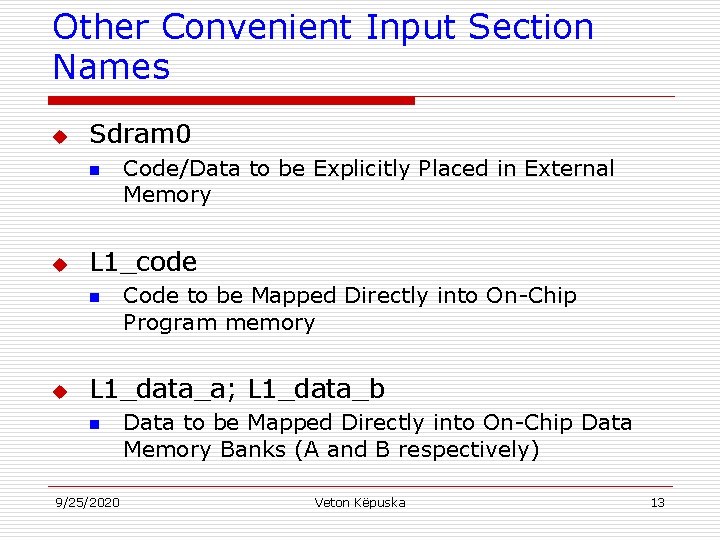

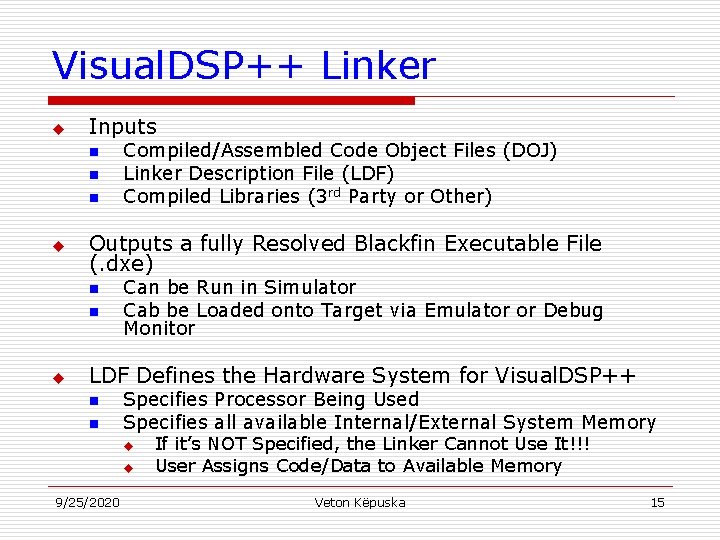

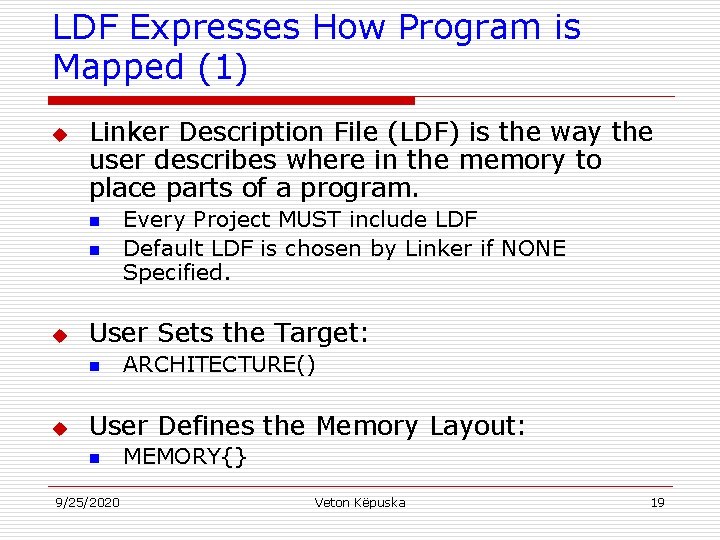

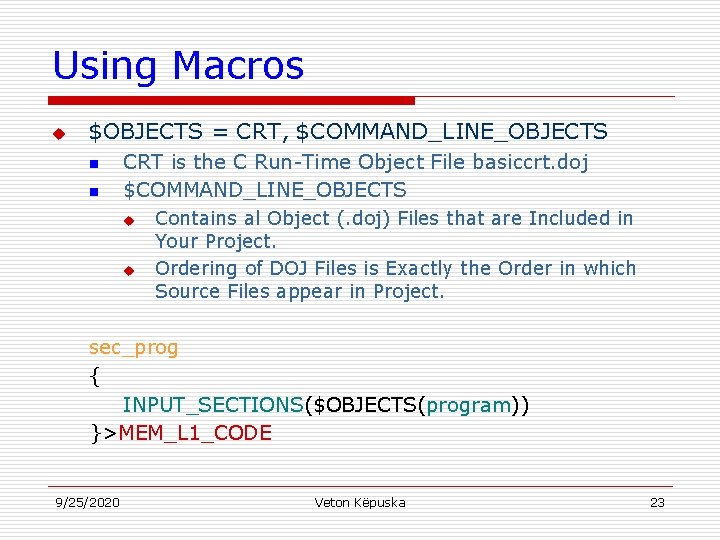

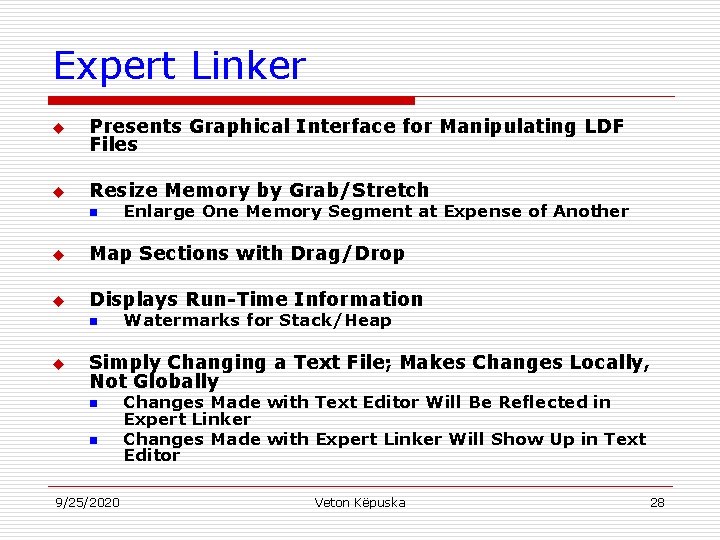

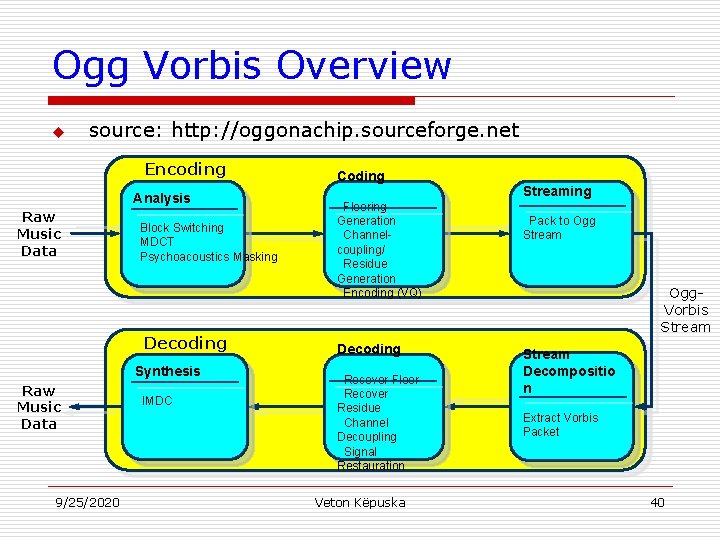

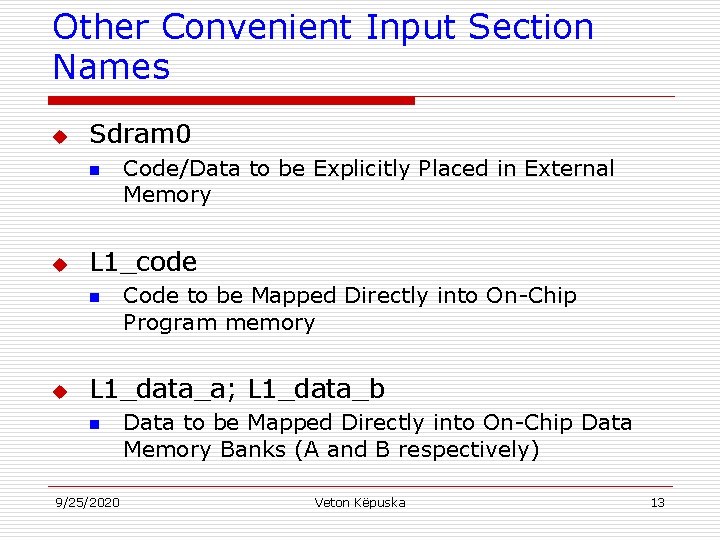

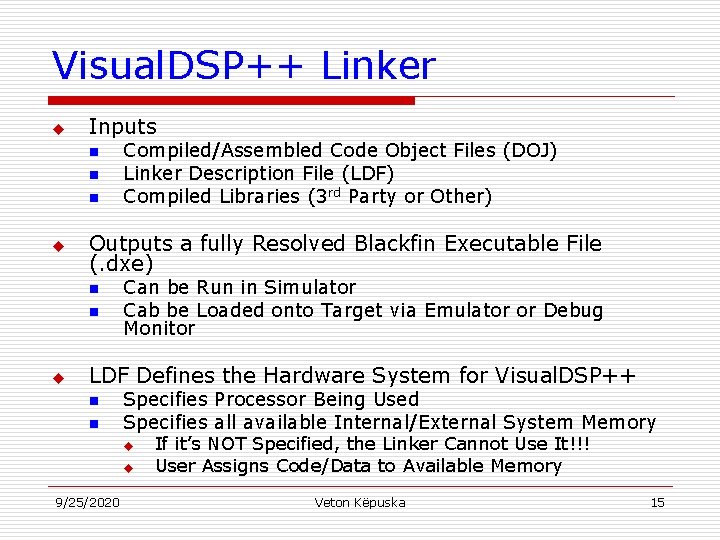

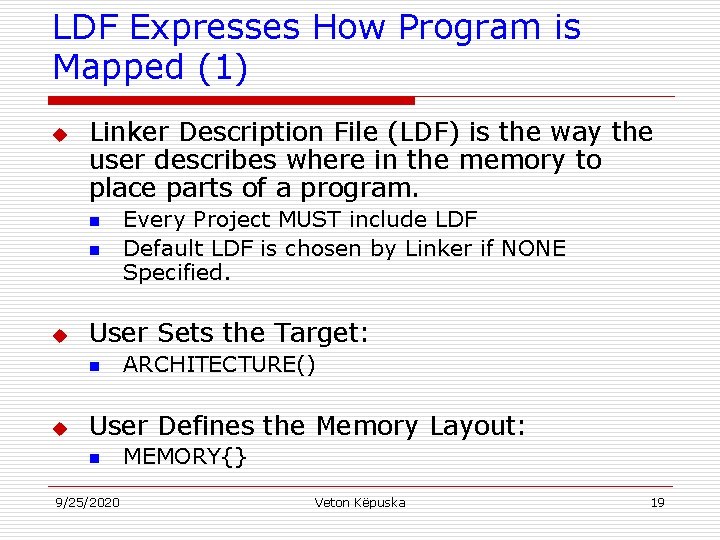

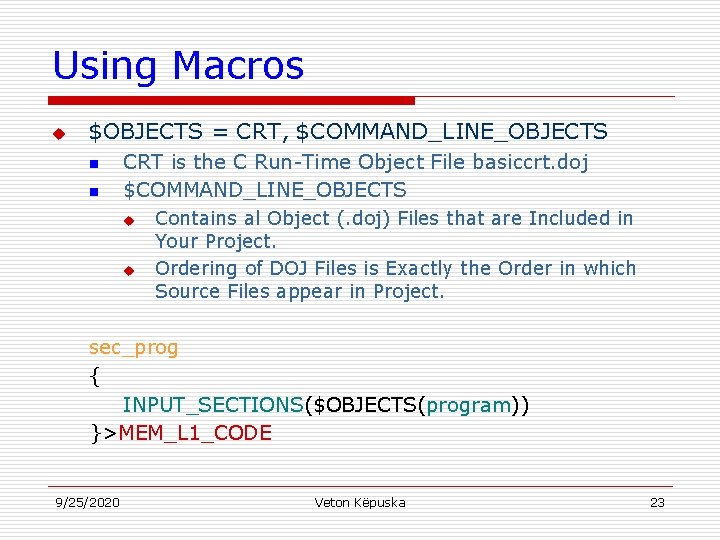

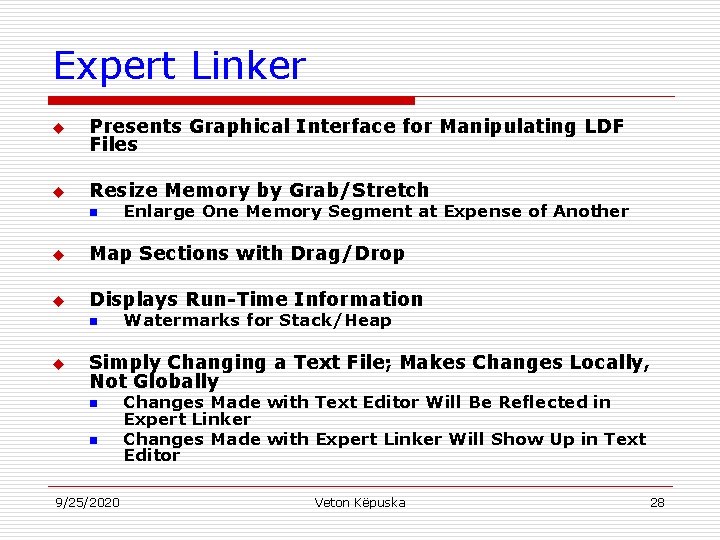

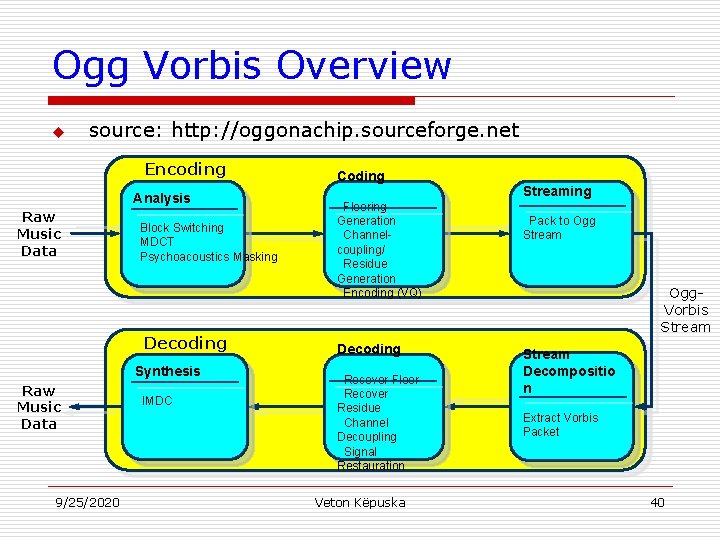

C Source with Alternate Sections foo. doj foo. c section (“sdram 0”) int array[256]; section (“L 1_code”) void bar (void) { int foovar: } foovar = 1; foovar ++; Object Section = sdram 0 _array [00] _array [01] … _array[255] Object Section = L 1_code _bar … : // bar ASM code C-Compiler Asse mbler Object Section = stack _foovar : 1 Note: The section() directive is used to place data or code into a section other than the default section used by the compiler. 9/25/2020 Veton Këpuska 12

Other Convenient Input Section Names u Sdram 0 n u L 1_code n u Code/Data to be Explicitly Placed in External Memory Code to be Mapped Directly into On-Chip Program memory L 1_data_a; L 1_data_b n 9/25/2020 Data to be Mapped Directly into On-Chip Data Memory Banks (A and B respectively) Veton Këpuska 13

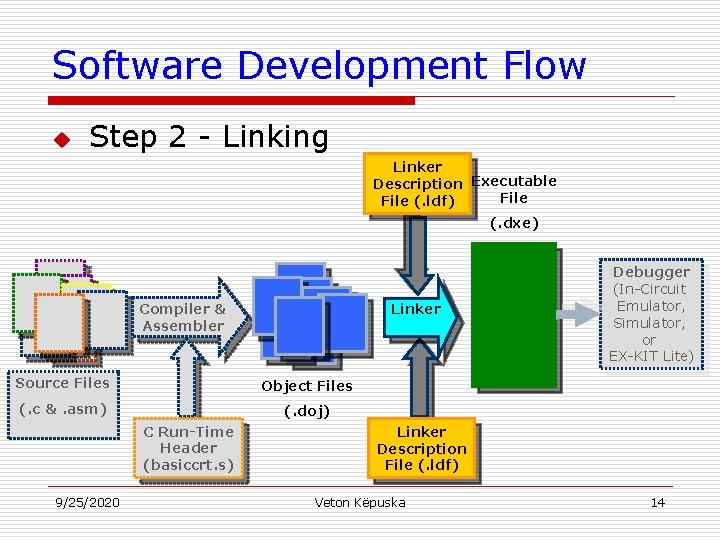

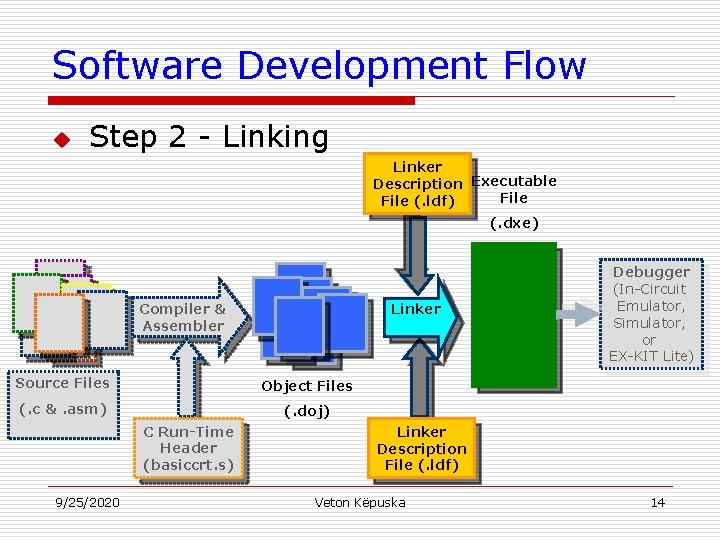

Software Development Flow u Step 2 - Linking Linker Description Executable File (. ldf) (. dxe) Compiler & Assembler Linker Source Files Object Files (. c &. asm) (. doj) C Run-Time Header (basiccrt. s) 9/25/2020 Debugger (In-Circuit Emulator, Simulator, or EX-KIT Lite) Linker Description File (. ldf) Veton Këpuska 14

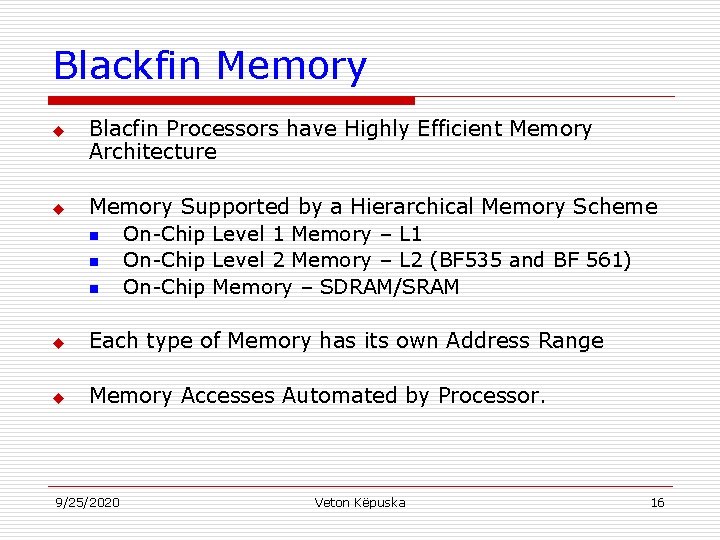

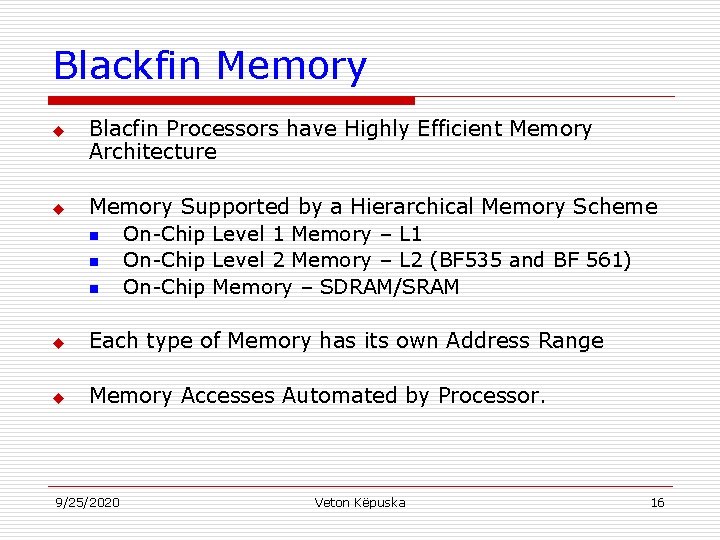

Visual. DSP++ Linker u Inputs n n n u Outputs a fully Resolved Blackfin Executable File (. dxe) n n u Compiled/Assembled Code Object Files (DOJ) Linker Description File (LDF) Compiled Libraries (3 rd Party or Other) Can be Run in Simulator Cab be Loaded onto Target via Emulator or Debug Monitor LDF Defines the Hardware System for Visual. DSP++ n n Specifies Processor Being Used Specifies all available Internal/External System Memory u u 9/25/2020 If it’s NOT Specified, the Linker Cannot Use It!!! User Assigns Code/Data to Available Memory Veton Këpuska 15

Blackfin Memory u u Blacfin Processors have Highly Efficient Memory Architecture Memory Supported by a Hierarchical Memory Scheme n On-Chip Level 1 Memory – L 1 n On-Chip Level 2 Memory – L 2 (BF 535 and BF 561) n On-Chip Memory – SDRAM/SRAM u Each type of Memory has its own Address Range u Memory Accesses Automated by Processor. 9/25/2020 Veton Këpuska 16

Details of Linker Description File (LDF) Veton Këpuska

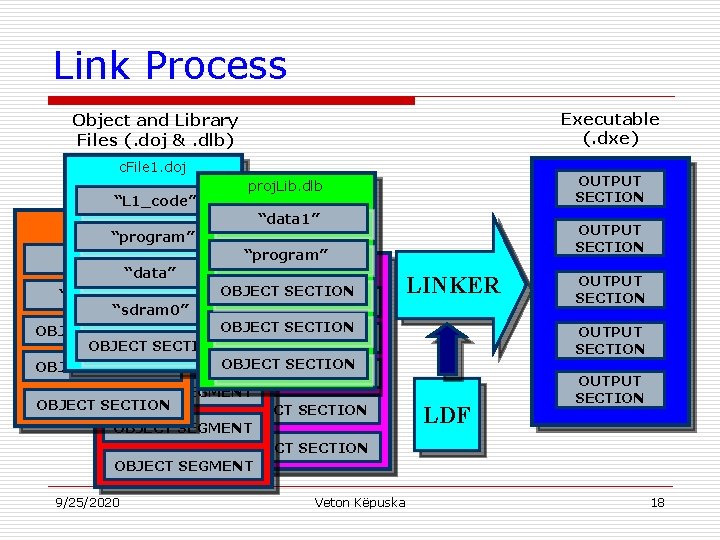

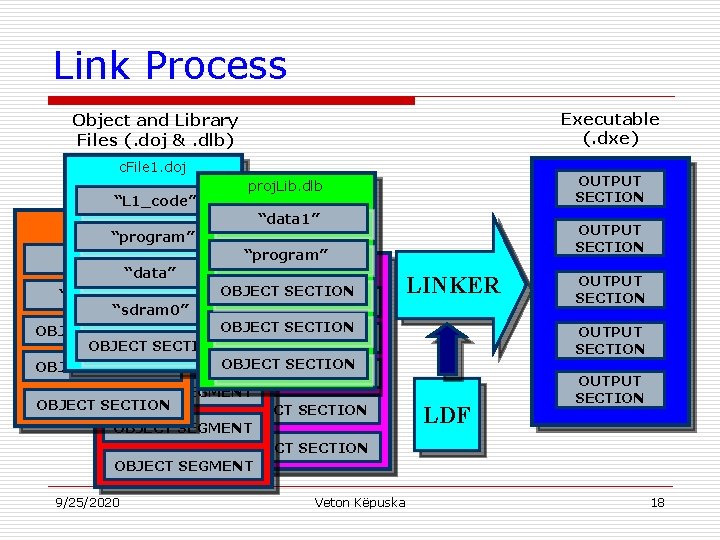

Link Process Executable (. dxe) Object and Library Files (. doj &. dlb) c. File 1. doj “L 1_code” OUTPUT SECTION proj. Lib. dlb “data 1” OUTPUT SECTION “program” “data 1” “data” “program” OBJECT SECTION “program” “data 1” “sdram 0” OBJECT SEGMENT OBJECT SECTION “program” OBJECT SECTION OBJECT SEGMENT OBJECT SECTION OBJECT SEGMENT 9/25/2020 Veton Këpuska LINKER OUTPUT SECTION LDF OUTPUT SECTION 18

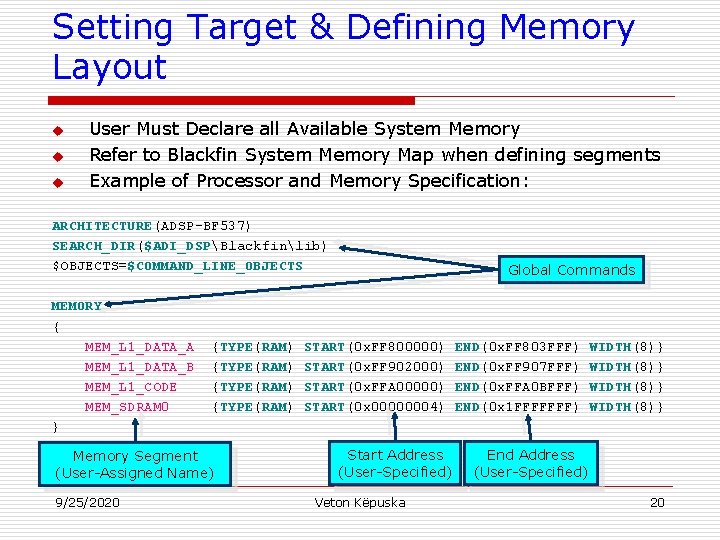

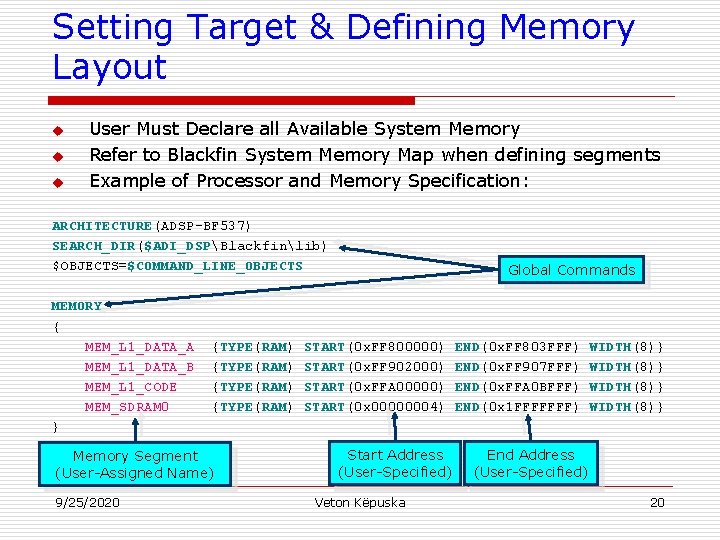

LDF Expresses How Program is Mapped (1) u Linker Description File (LDF) is the way the user describes where in the memory to place parts of a program. n n u User Sets the Target: n u Every Project MUST include LDF Default LDF is chosen by Linker if NONE Specified. ARCHITECTURE() User Defines the Memory Layout: n 9/25/2020 MEMORY{} Veton Këpuska 19

Setting Target & Defining Memory Layout u u u User Must Declare all Available System Memory Refer to Blackfin System Memory Map when defining segments Example of Processor and Memory Specification: ARCHITECTURE(ADSP-BF 537) SEARCH_DIR($ADI_DSPBlackfinlib) $OBJECTS=$COMMAND_LINE_OBJECTS MEMORY { MEM_L 1_DATA_A MEM_L 1_DATA_B MEM_L 1_CODE MEM_SDRAM 0 } {TYPE(RAM) Memory Segment (User-Assigned Name) 9/25/2020 Global Commands START(0 x. FF 800000) START(0 x. FF 902000) START(0 x. FFA 00000) START(0 x 00000004) Start Address (User-Specified) Veton Këpuska END(0 x. FF 803 FFF) END(0 x. FF 907 FFF) END(0 x. FFA 0 BFFF) END(0 x 1 FFFFFFF) WIDTH(8)} End Address (User-Specified) 20

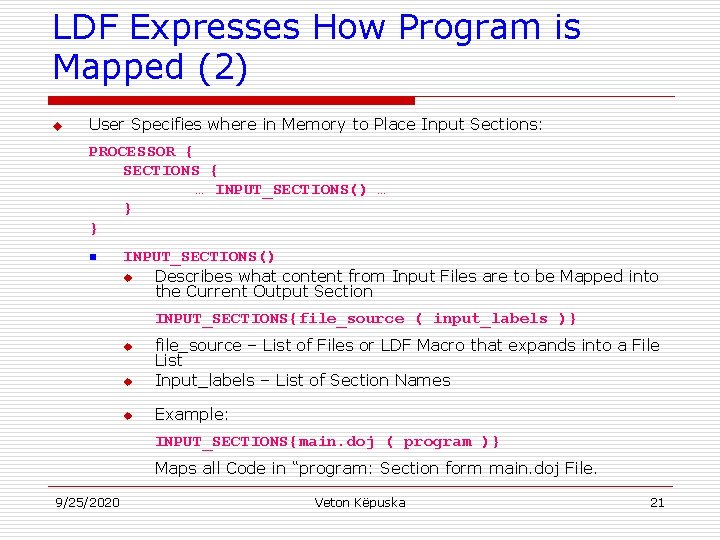

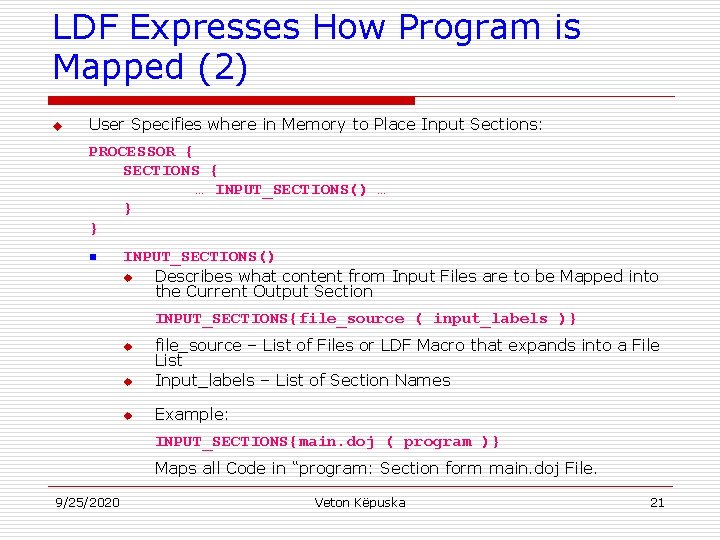

LDF Expresses How Program is Mapped (2) u User Specifies where in Memory to Place Input Sections: PROCESSOR { SECTIONS { … INPUT_SECTIONS() … } } n INPUT_SECTIONS() u Describes what content from Input Files are to be Mapped into the Current Output Section INPUT_SECTIONS{file_source ( input_labels )} u file_source – List of Files or LDF Macro that expands into a File List Input_labels – List of Section Names u Example: u INPUT_SECTIONS{main. doj ( program )} Maps all Code in “program: Section form main. doj File. 9/25/2020 Veton Këpuska 21

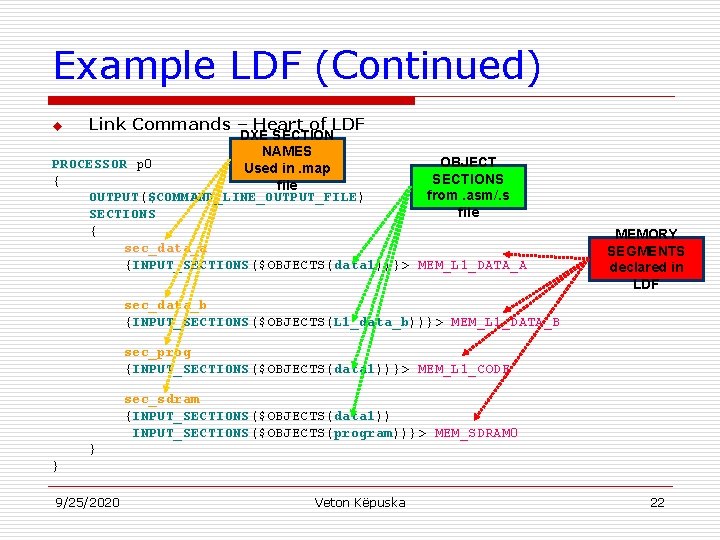

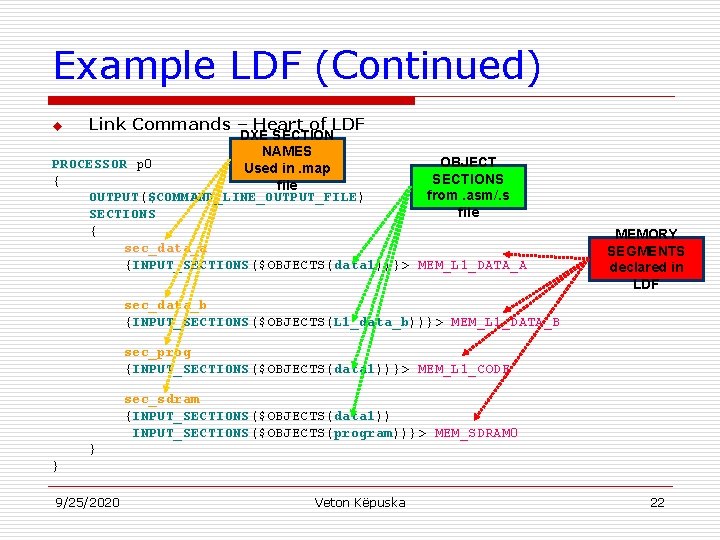

Example LDF (Continued) u Link Commands – Heart of LDF DXE SECTION NAMES OBJECT PROCESSOR p 0 Used in. map SECTIONS { file from. asm/. s OUTPUT($COMMAND_LINE_OUTPUT_FILE) file SECTIONS { sec_data_a {INPUT_SECTIONS($OBJECTS(data 1))}> MEM_L 1_DATA_A MEMORY SEGMENTS declared in LDF sec_data_b {INPUT_SECTIONS($OBJECTS(L 1_data_b))}> MEM_L 1_DATA_B sec_prog {INPUT_SECTIONS($OBJECTS(data 1))}> MEM_L 1_CODE sec_sdram {INPUT_SECTIONS($OBJECTS(data 1)) INPUT_SECTIONS($OBJECTS(program))}> MEM_SDRAM 0 } } 9/25/2020 Veton Këpuska 22

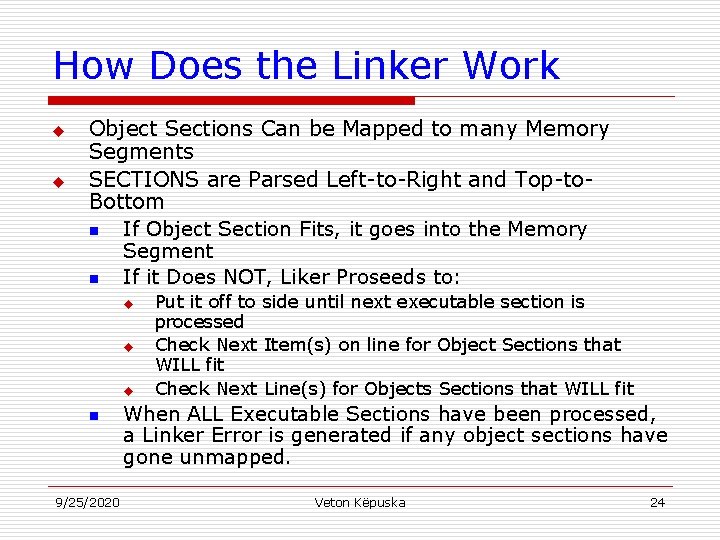

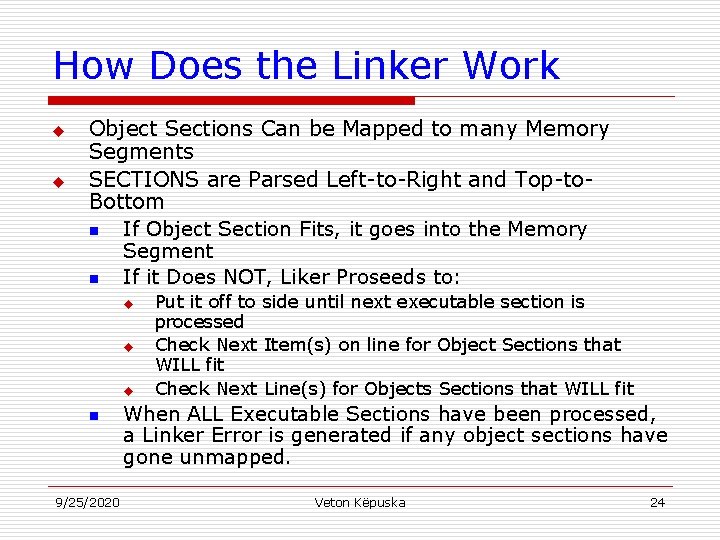

Using Macros u $OBJECTS = CRT, $COMMAND_LINE_OBJECTS n n CRT is the C Run-Time Object File basiccrt. doj $COMMAND_LINE_OBJECTS u u Contains al Object (. doj) Files that are Included in Your Project. Ordering of DOJ Files is Exactly the Order in which Source Files appear in Project. sec_prog { INPUT_SECTIONS($OBJECTS(program)) }>MEM_L 1_CODE 9/25/2020 Veton Këpuska 23

How Does the Linker Work u u Object Sections Can be Mapped to many Memory Segments SECTIONS are Parsed Left-to-Right and Top-to. Bottom n If Object Section Fits, it goes into the Memory Segment n If it Does NOT, Liker Proseeds to: u u u n 9/25/2020 Put it off to side until next executable section is processed Check Next Item(s) on line for Object Sections that WILL fit Check Next Line(s) for Objects Sections that WILL fit When ALL Executable Sections have been processed, a Linker Error is generated if any object sections have gone unmapped. Veton Këpuska 24

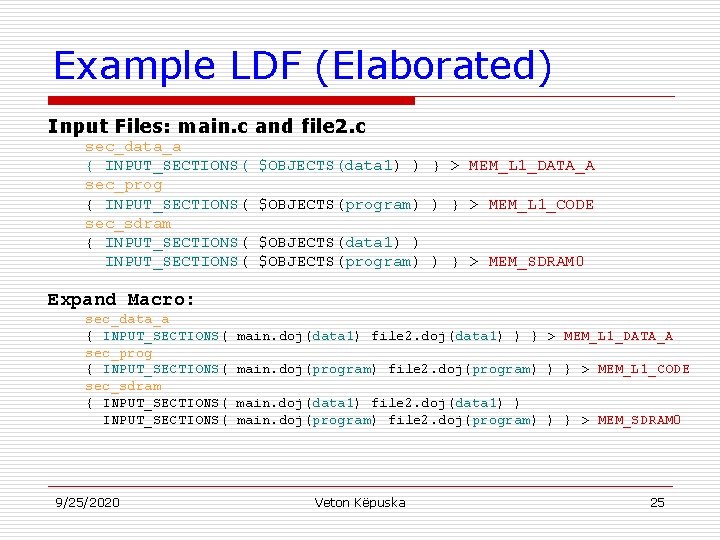

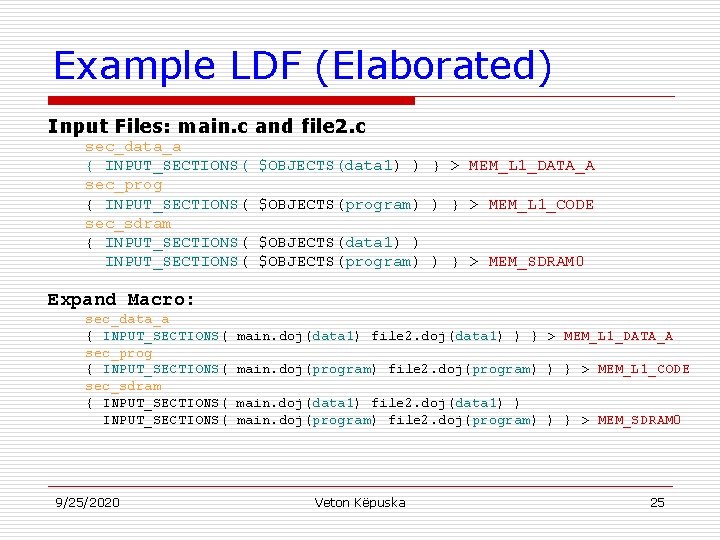

Example LDF (Elaborated) Input Files: main. c and file 2. c sec_data_a { INPUT_SECTIONS( sec_prog { INPUT_SECTIONS( sec_sdram { INPUT_SECTIONS( $OBJECTS(data 1) ) } > MEM_L 1_DATA_A $OBJECTS(program) ) } > MEM_L 1_CODE $OBJECTS(data 1) ) $OBJECTS(program) ) } > MEM_SDRAM 0 Expand Macro: sec_data_a { INPUT_SECTIONS( sec_prog { INPUT_SECTIONS( sec_sdram { INPUT_SECTIONS( 9/25/2020 main. doj(data 1) file 2. doj(data 1) ) } > MEM_L 1_DATA_A main. doj(program) file 2. doj(program) ) } > MEM_L 1_CODE main. doj(data 1) file 2. doj(data 1) ) main. doj(program) file 2. doj(program) ) } > MEM_SDRAM 0 Veton Këpuska 25

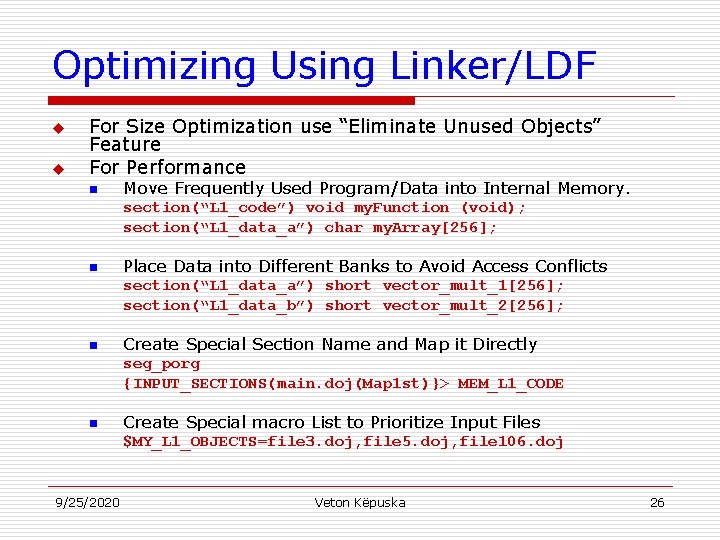

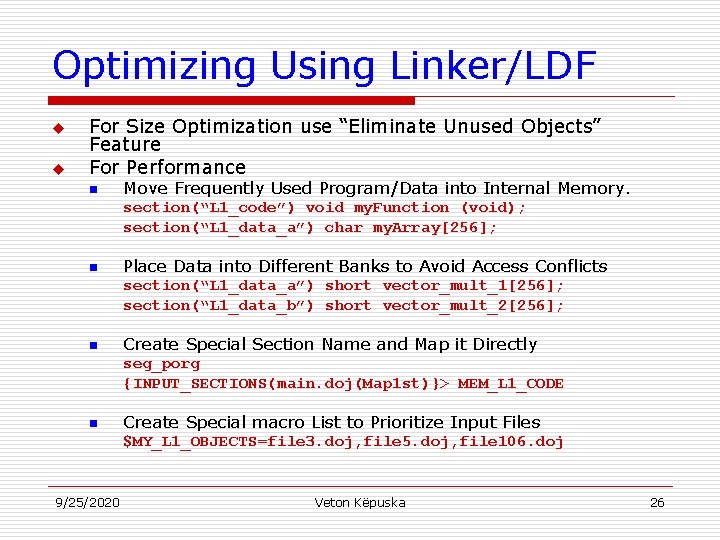

Optimizing Using Linker/LDF u u For Size Optimization use “Eliminate Unused Objects” Feature For Performance n Move Frequently Used Program/Data into Internal Memory. section(“L 1_code”) void my. Function (void); section(“L 1_data_a”) char my. Array[256]; n Place Data into Different Banks to Avoid Access Conflicts section(“L 1_data_a”) short vector_mult_1[256]; section(“L 1_data_b”) short vector_mult_2[256]; n Create Special Section Name and Map it Directly seg_porg {INPUT_SECTIONS(main. doj(Map 1 st)}> MEM_L 1_CODE n Create Special macro List to Prioritize Input Files $MY_L 1_OBJECTS=file 3. doj, file 5. doj, file 106. doj 9/25/2020 Veton Këpuska 26

Expert Linker Veton Këpuska

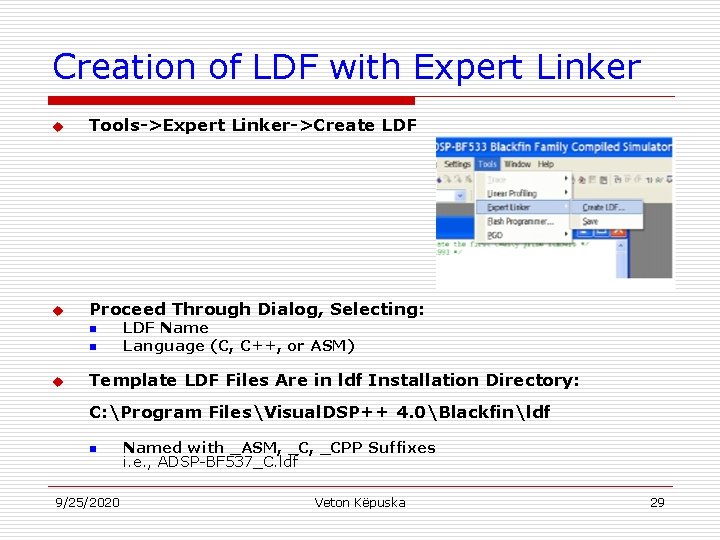

Expert Linker u Presents Graphical Interface for Manipulating LDF Files u Resize Memory by Grab/Stretch n Enlarge One Memory Segment at Expense of Another u Map Sections with Drag/Drop u Displays Run-Time Information n u Watermarks for Stack/Heap Simply Changing a Text File; Makes Changes Locally, Not Globally n n 9/25/2020 Changes Made with Text Editor Will Be Reflected in Expert Linker Changes Made with Expert Linker Will Show Up in Text Editor Veton Këpuska 28

Creation of LDF with Expert Linker u Tools->Expert Linker->Create LDF u Proceed Through Dialog, Selecting: n n u LDF Name Language (C, C++, or ASM) Template LDF Files Are in ldf Installation Directory: C: Program FilesVisual. DSP++ 4. 0Blackfinldf n 9/25/2020 Named with _ASM, _CPP Suffixes i. e. , ADSP-BF 537_C. ldf Veton Këpuska 29

Programming Blackfin Processors in C Veton Këpuska

Making Use of Peripherals u u Blackfin Peripherals are Programmed/Used via Sets of memory-Mapped Registers (MMRs) System Services and Device Drivers Automatically Handle Programming of these MMRs. 9/25/2020 Veton Këpuska 31

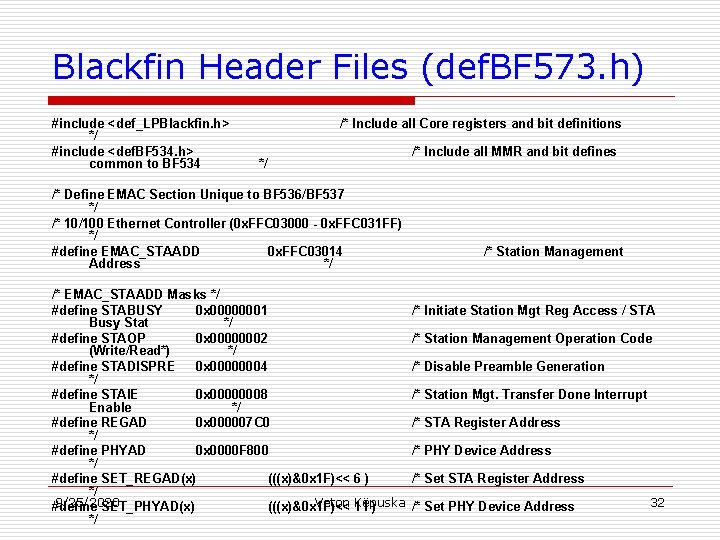

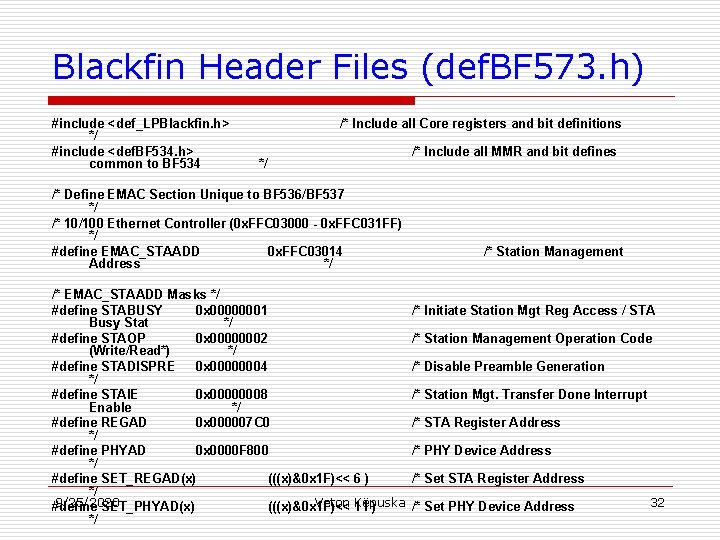

Blackfin Header Files (def. BF 573. h) #include <def_LPBlackfin. h> */ #include <def. BF 534. h> common to BF 534 /* Include all Core registers and bit definitions */ /* Define EMAC Section Unique to BF 536/BF 537 */ /* 10/100 Ethernet Controller (0 x. FFC 03000 - 0 x. FFC 031 FF) */ #define EMAC_STAADD 0 x. FFC 03014 Address */ /* EMAC_STAADD Masks */ #define STABUSY 0 x 00000001 Busy Stat */ #define STAOP 0 x 00000002 (Write/Read*) */ #define STADISPRE 0 x 00000004 */ #define STAIE 0 x 00000008 Enable */ #define REGAD 0 x 000007 C 0 */ #define PHYAD 0 x 0000 F 800 */ #define SET_REGAD(x) (((x)&0 x 1 F)<< 6 ) */ 9/25/2020 Veton Këpuska #define SET_PHYAD(x) (((x)&0 x 1 F)<< 11 ) */ /* Include all MMR and bit defines /* Station Management /* Initiate Station Mgt Reg Access / STA /* Station Management Operation Code /* Disable Preamble Generation /* Station Mgt. Transfer Done Interrupt /* STA Register Address /* PHY Device Address /* Set STA Register Address /* Set PHY Device Address 32

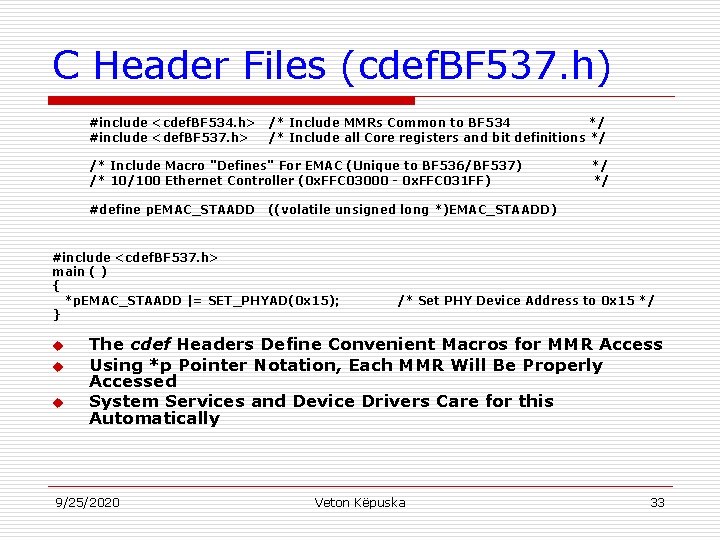

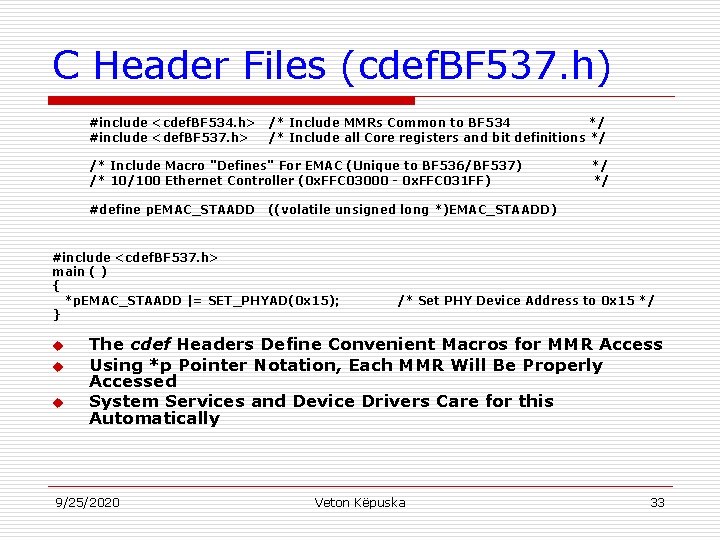

C Header Files (cdef. BF 537. h) #include <cdef. BF 534. h> /* Include MMRs Common to BF 534 */ #include <def. BF 537. h> /* Include all Core registers and bit definitions */ /* Include Macro "Defines" For EMAC (Unique to BF 536/BF 537) /* 10/100 Ethernet Controller (0 x. FFC 03000 - 0 x. FFC 031 FF) #define p. EMAC_STAADD ((volatile unsigned long *)EMAC_STAADD) #include <cdef. BF 537. h> main ( ) { *p. EMAC_STAADD |= SET_PHYAD(0 x 15); } u u u */ */ /* Set PHY Device Address to 0 x 15 */ The cdef Headers Define Convenient Macros for MMR Access Using *p Pointer Notation, Each MMR Will Be Properly Accessed System Services and Device Drivers Care for this Automatically 9/25/2020 Veton Këpuska 33

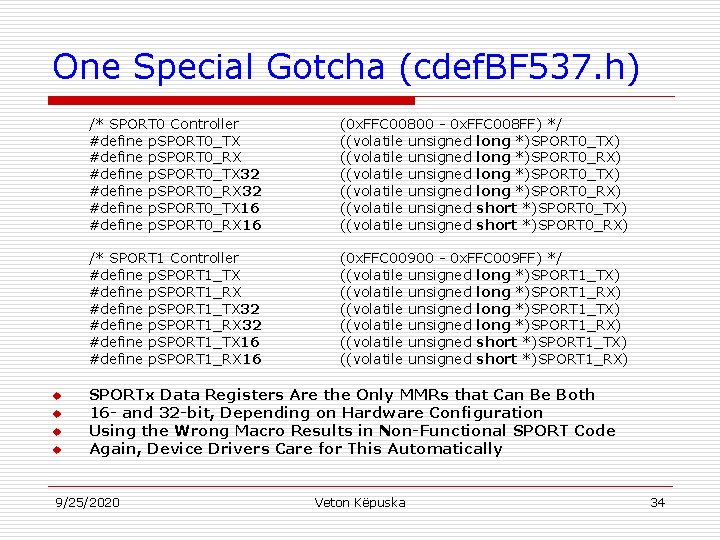

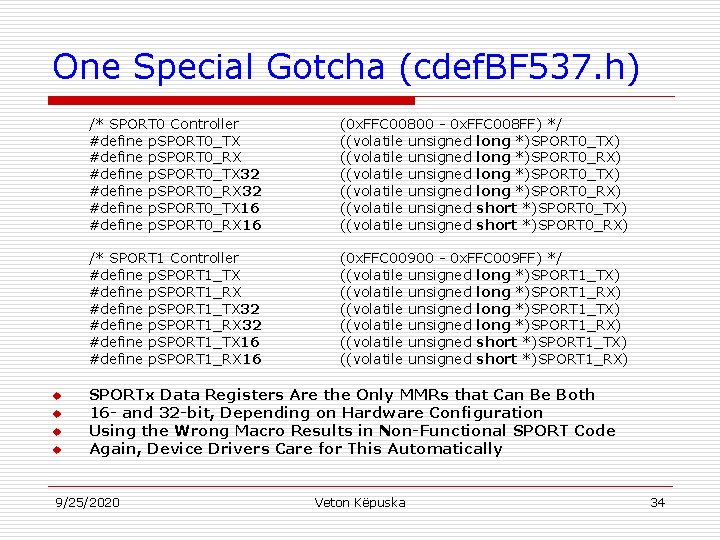

One Special Gotcha (cdef. BF 537. h) u u /* SPORT 0 Controller #define p. SPORT 0_TX #define p. SPORT 0_RX #define p. SPORT 0_TX 32 #define p. SPORT 0_RX 32 #define p. SPORT 0_TX 16 #define p. SPORT 0_RX 16 (0 x. FFC 00800 - 0 x. FFC 008 FF) */ ((volatile unsigned long *)SPORT 0_TX) ((volatile unsigned long *)SPORT 0_RX) ((volatile unsigned short *)SPORT 0_TX) ((volatile unsigned short *)SPORT 0_RX) /* SPORT 1 Controller #define p. SPORT 1_TX #define p. SPORT 1_RX #define p. SPORT 1_TX 32 #define p. SPORT 1_RX 32 #define p. SPORT 1_TX 16 #define p. SPORT 1_RX 16 (0 x. FFC 00900 - 0 x. FFC 009 FF) */ ((volatile unsigned long *)SPORT 1_TX) ((volatile unsigned long *)SPORT 1_RX) ((volatile unsigned short *)SPORT 1_TX) ((volatile unsigned short *)SPORT 1_RX) SPORTx Data Registers Are the Only MMRs that Can Be Both 16 - and 32 -bit, Depending on Hardware Configuration Using the Wrong Macro Results in Non-Functional SPORT Code Again, Device Drivers Care for This Automatically 9/25/2020 Veton Këpuska 34

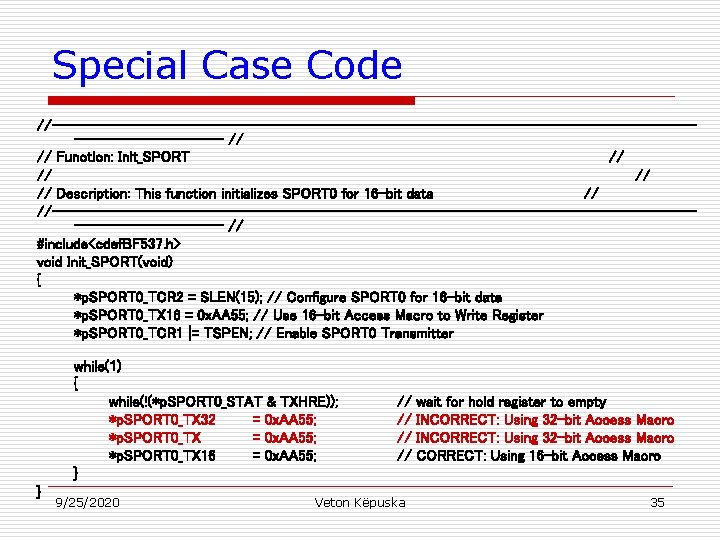

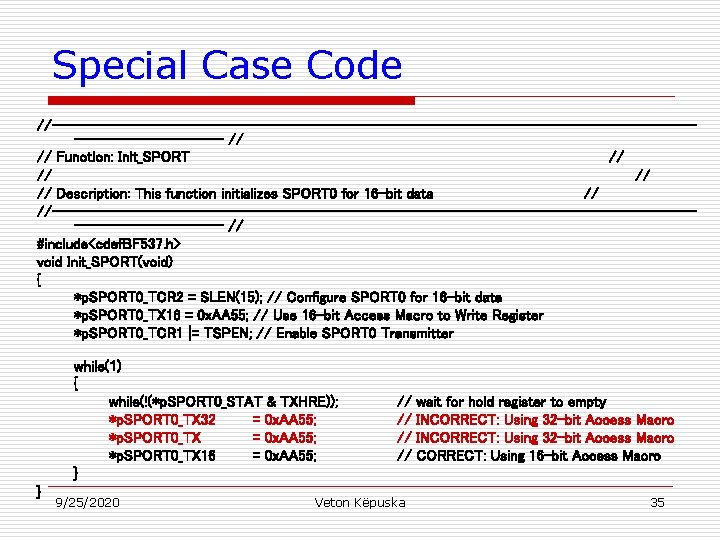

Special Case Code //----------------------------------------------------- // // Function: Init_SPORT // // Description: This function initializes SPORT 0 for 16 -bit data // //----------------------------------------------------- // #include<cdef. BF 537. h> void Init_SPORT(void) { *p. SPORT 0_TCR 2 = SLEN(15); // Configure SPORT 0 for 16 -bit data *p. SPORT 0_TX 16 = 0 x. AA 55; // Use 16 -bit Access Macro to Write Register *p. SPORT 0_TCR 1 |= TSPEN; // Enable SPORT 0 Transmitter while(1) { while(!(*p. SPORT 0_STAT & TXHRE)); *p. SPORT 0_TX 32 = 0 x. AA 55; *p. SPORT 0_TX 16 = 0 x. AA 55; } } 9/25/2020 // // Veton Këpuska wait for hold register to empty INCORRECT: Using 32 -bit Access Macro CORRECT: Using 16 -bit Access Macro 35

Creating Efficient C Code for Blackfin Veton Këpuska

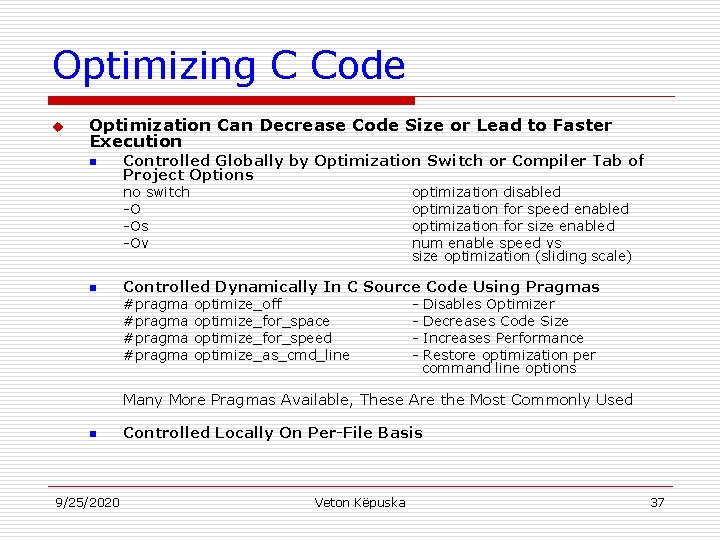

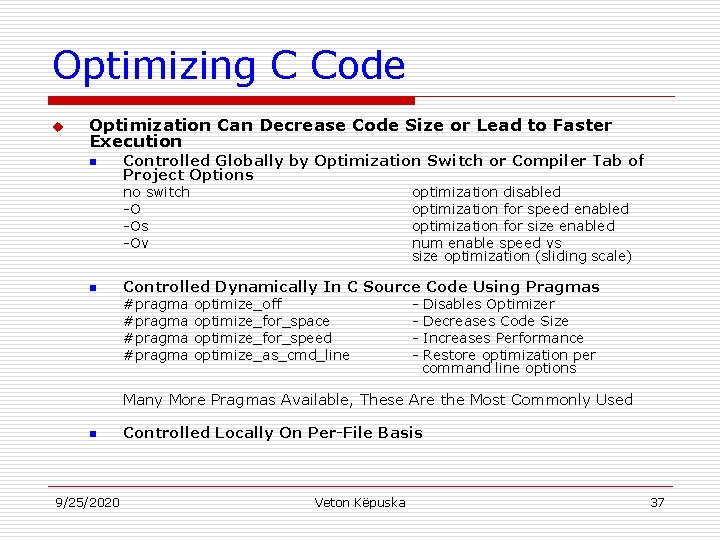

Optimizing C Code u Optimization Can Decrease Code Size or Lead to Faster Execution n Controlled Globally by Optimization Switch or Compiler Tab of Project Options no switch -O -Os -Ov n optimization disabled optimization for speed enabled optimization for size enabled num enable speed vs size optimization (sliding scale) Controlled Dynamically In C Source Code Using Pragmas #pragma optimize_off optimize_for_space optimize_for_speed optimize_as_cmd_line - Disables Optimizer Decreases Code Size Increases Performance Restore optimization per command line options Many More Pragmas Available, These Are the Most Commonly Used n 9/25/2020 Controlled Locally On Per-File Basis Veton Këpuska 37

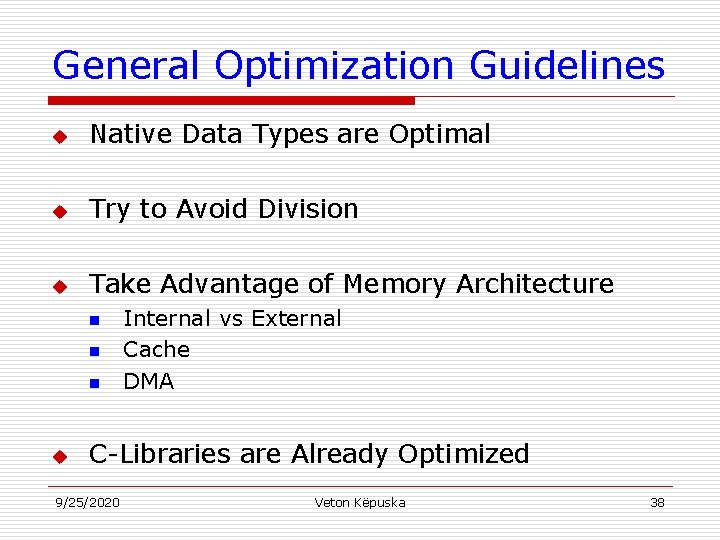

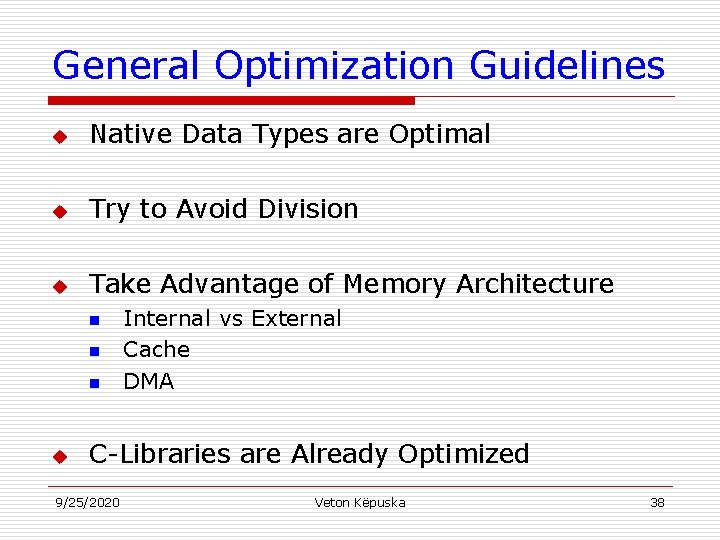

General Optimization Guidelines u Native Data Types are Optimal u Try to Avoid Division u Take Advantage of Memory Architecture n n n u Internal vs External Cache DMA C-Libraries are Already Optimized 9/25/2020 Veton Këpuska 38

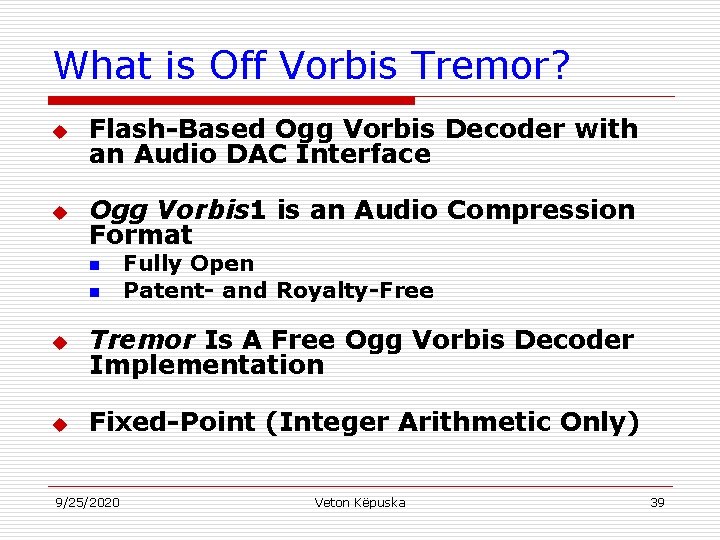

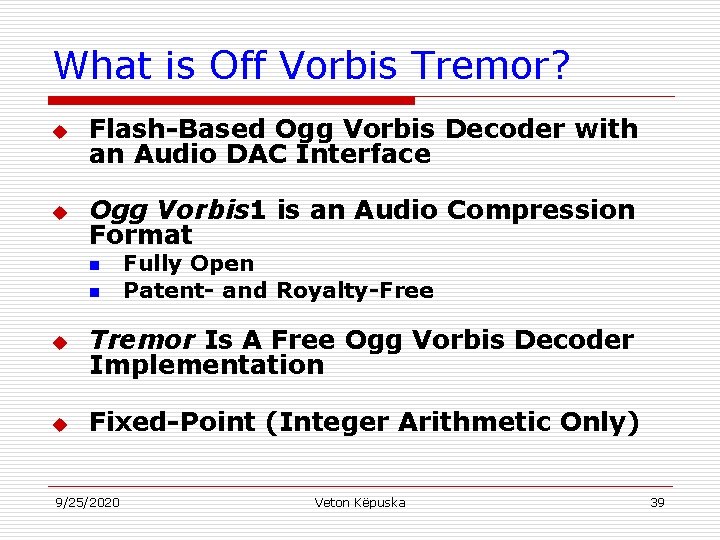

What is Off Vorbis Tremor? u Flash-Based Ogg Vorbis Decoder with an Audio DAC Interface u Ogg Vorbis 1 is an Audio Compression Format n n Fully Open Patent- and Royalty-Free u Tremor Is A Free Ogg Vorbis Decoder Implementation u Fixed-Point (Integer Arithmetic Only) 9/25/2020 Veton Këpuska 39

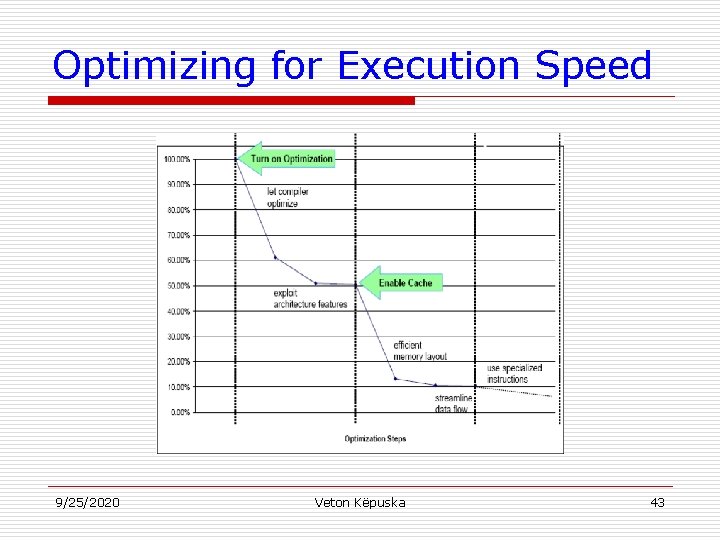

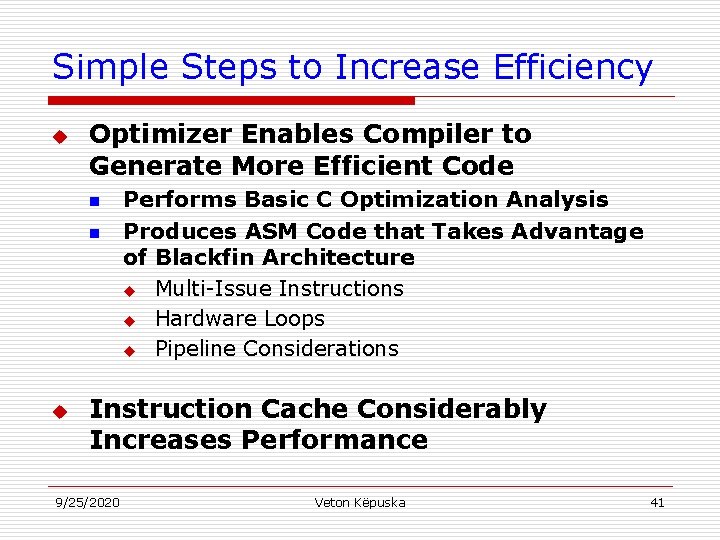

Ogg Vorbis Overview u source: http: //oggonachip. sourceforge. net Encoding Analysis Raw Music Data Block Switching MDCT Psychoacoustics Masking Decoding Synthesis Raw Music Data 9/25/2020 IMDC Coding Flooring Generation Channelcoupling/ Residue Generation Encoding (VQ) Decoding Recover Floor Recover Residue Channel Decoupling Signal Restauration Veton Këpuska Streaming Pack to Ogg Stream Ogg. Vorbis Stream Decompositio n Extract Vorbis Packet 40

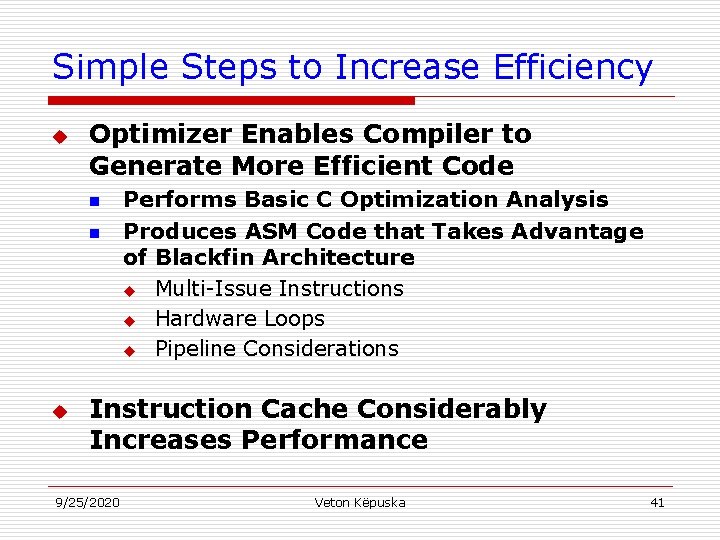

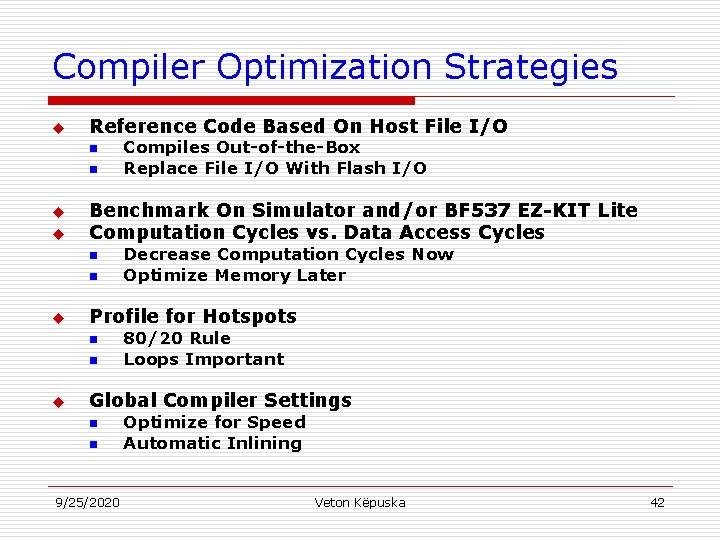

Simple Steps to Increase Efficiency u Optimizer Enables Compiler to Generate More Efficient Code n n u Performs Basic C Optimization Analysis Produces ASM Code that Takes Advantage of Blackfin Architecture u Multi-Issue Instructions u Hardware Loops u Pipeline Considerations Instruction Cache Considerably Increases Performance 9/25/2020 Veton Këpuska 41

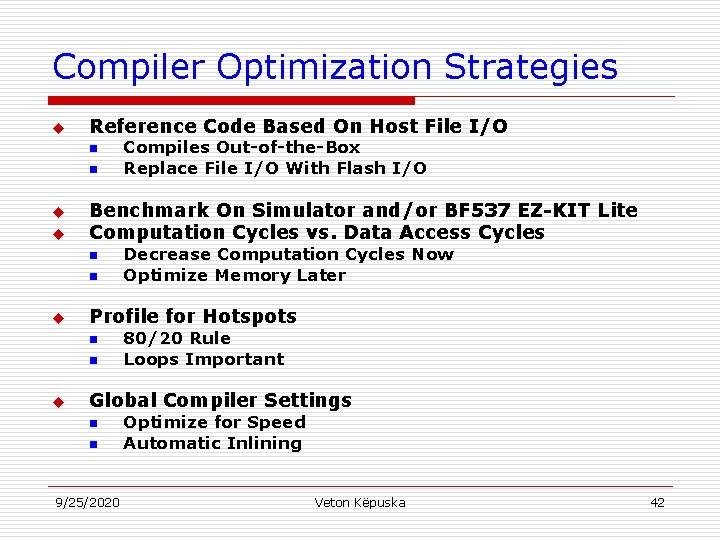

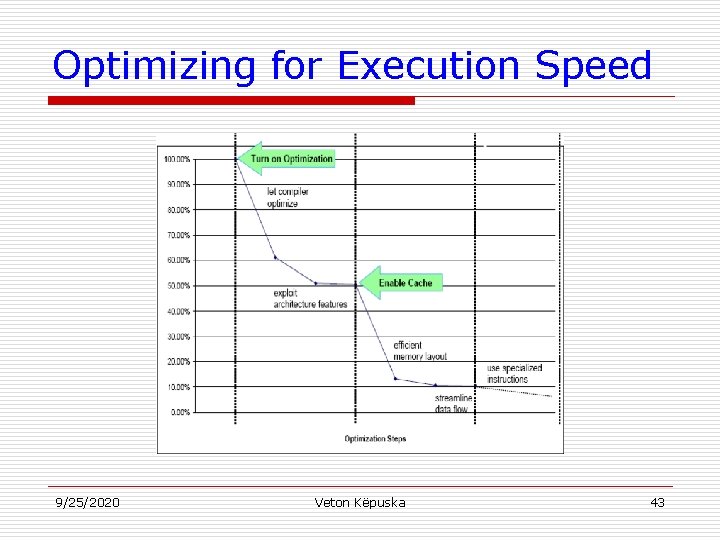

Compiler Optimization Strategies u Reference Code Based On Host File I/O n n u u Benchmark On Simulator and/or BF 537 EZ-KIT Lite Computation Cycles vs. Data Access Cycles n n u Decrease Computation Cycles Now Optimize Memory Later Profile for Hotspots n n u Compiles Out-of-the-Box Replace File I/O With Flash I/O 80/20 Rule Loops Important Global Compiler Settings n n 9/25/2020 Optimize for Speed Automatic Inlining Veton Këpuska 42

Optimizing for Execution Speed 9/25/2020 Veton Këpuska 43