Microarchitecture Microarchitecture also called computer organization and sometimes

- Slides: 10

Microarchitecture

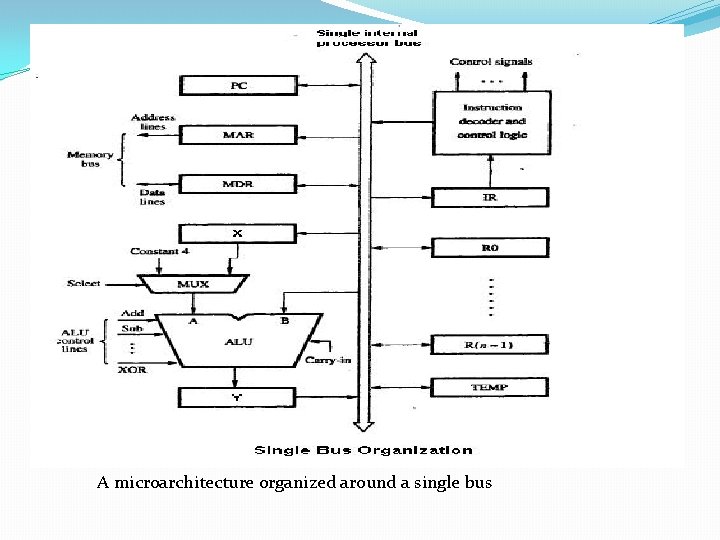

�Microarchitecture, also called computer organization and sometimes abbreviated as µarch or uarch, is the way a given instruction set architecture (ISA) is implemented in a particular processor. �The microarchitecture of a machine is usually represented as (more or less detailed) diagrams that describe the interconnections of the various microarchitectural elements of the machine, which may be everything from single gates and registers, to complete arithmetic logic units (ALUs) and even larger elements

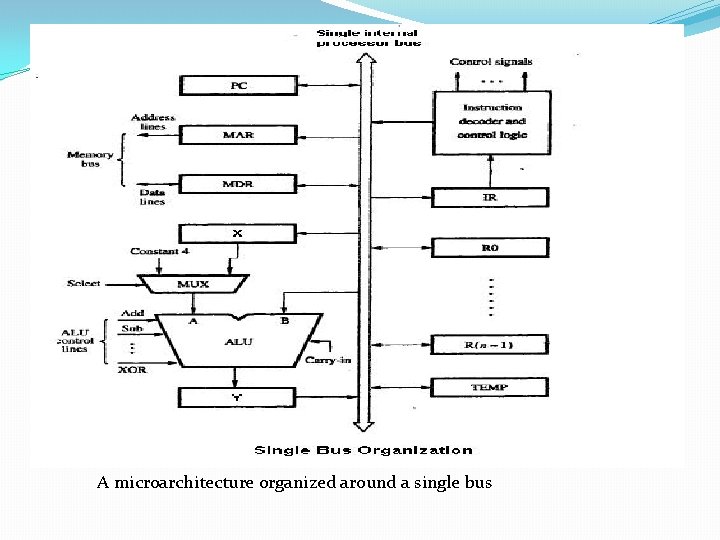

A microarchitecture organized around a single bus

The Microarchitecture of the Pentium 4 Processor(Net. Burst) • The Intel® Net. Burst microarchitecture of Intel’s new flagship Pentium® 4 processor. • The Pentium 4 processor provides a substantial performance gain for many key application areas where the end user can truly appreciate the difference. For example, it allows a much better user experience in areas such as Internet audio and streaming video, image processing, video content creation, speech recognition, 3 D applications and games, multi-media, and multi-tasking user environments. • The Pentium 4 processor enables real time MPEG 2 video encoding and near real-time MPEG 4 encoding, allowing efficient video editing and video conferencing.

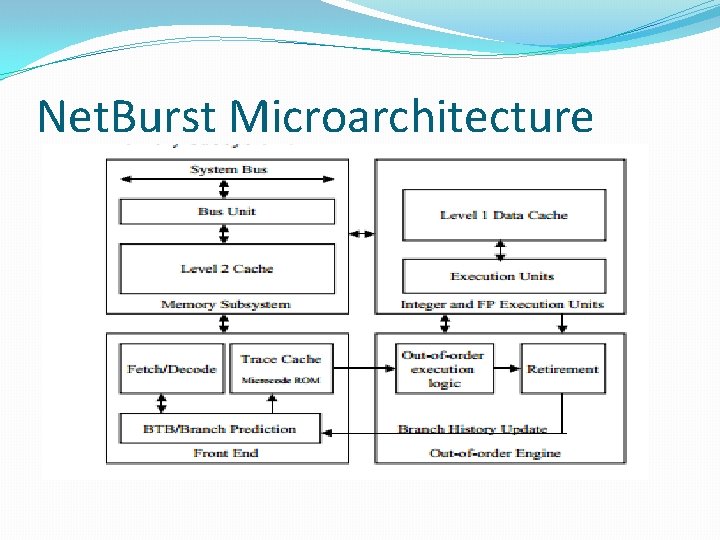

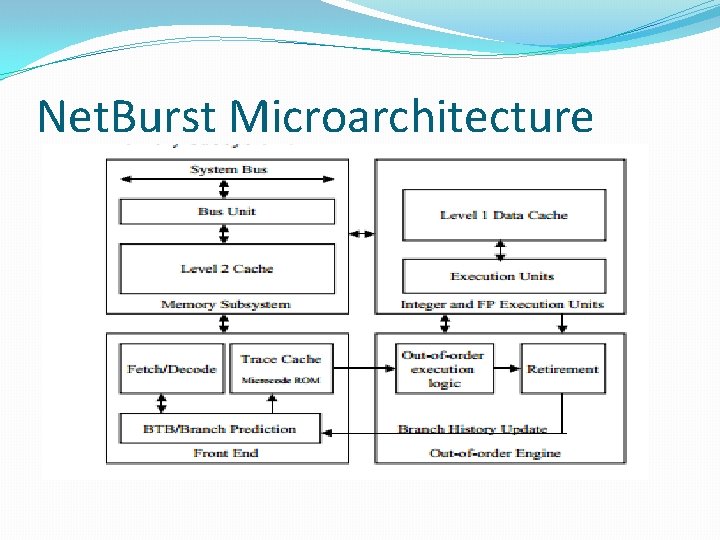

Net. Burst Microarchitecture

The in-order front end is the part of the machine that fetches the instructions to be executed next in the program and prepares them to be used later in the machine pipeline. The out-of-order execution logic has several buffers that it uses to smooth and re-order the flow of instructions to optimize performance as they go down the pipeline and get scheduled for execution. Out-of-order execution allows the execution resources such as the ALUs and the cache to be kept as busy as possible executing independent instructions that are ready to execute. The retirement logic is what reorders the instructions, executed in an out-oforder manner, back to the original program order Integer and Floating-Point Execution Units : The execution units are where the instructions are actually executed. This section includes the register files that store the integer and floating-point data operand values that the instructions need to execute. Memory Subsystem : This includes the L 2 cache and the system bus. The L 2 cache stores both instructions and data that cannot fit in the Execution Trace Cache and the L 1 data cache. The external system bus is connected to the backside of the second-level cache and is used to access main memory when the L 2 cache has a cache miss, and to access the system I/O resources.

Next generation processors architecture : *Cortex-A 15 Processor *Unified Processing Architecture

Cortex-A 15 Processor ARM Cortex-A 15 processor is the proven high-performance engine for highly connected devices, delivering unprecedented flexibility and processing capability. The processor is designed with advanced power reduction techniques as well as reliability features which make the Cortex-A 15 ideal for networking infrastructure and other enterprise applications. The Cortex-A 15 processor is supported by a suite of optimized IP targeted at high-end solutions bringing premium performance in a mobile power envelope. ARM Mali high-end graphics processors support advanced graphics performance, with the Mali-V 500 and Mali-DP 500 processors providing display and video capabilities respectively. The ARM interconnect and memory controller IP addresses the critical challenge of efficiently moving and storing data between multiple Cortex-A 15 processors, high-performance media processors and dynamic memories to optimize the system performance and power consumption of the So. C.

The Harmony Unified Processing Architecture are described as consisting of “the Multi-Thread Virtual Pipeline parallel computing core (MVP), an independent instruction set architecture, an optimizing compiler, and the Agile Switch dynamic load balancer. ” The chip uses both SMP (Symmetric Multi-Processing) and SMT (Simultaneous Multi. Threading).

Thank You