Microarchitecture is Dead AND We must have a

- Slides: 10

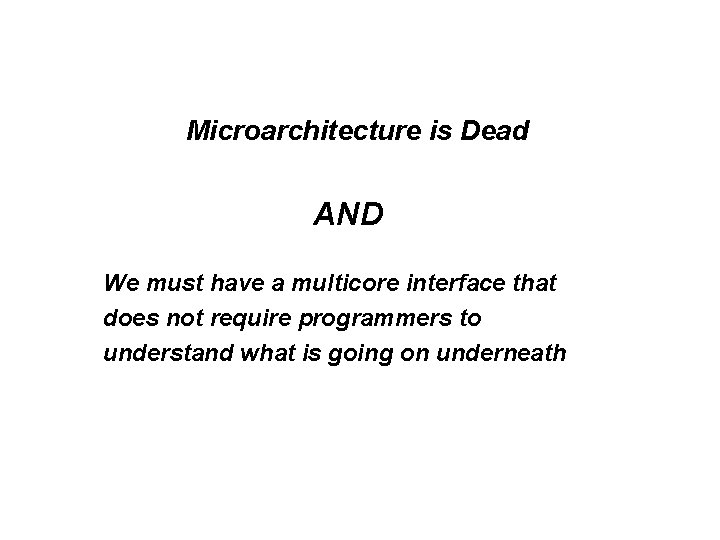

Microarchitecture is Dead AND We must have a multicore interface that does not require programmers to understand what is going on underneath

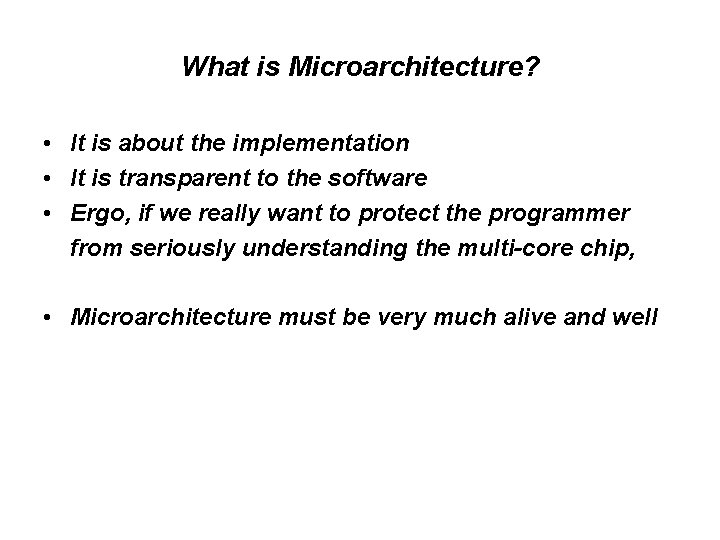

What is Microarchitecture? • It is about the implementation • It is transparent to the software • Ergo, if we really want to protect the programmer from seriously understanding the multi-core chip, • Microarchitecture must be very much alive and well

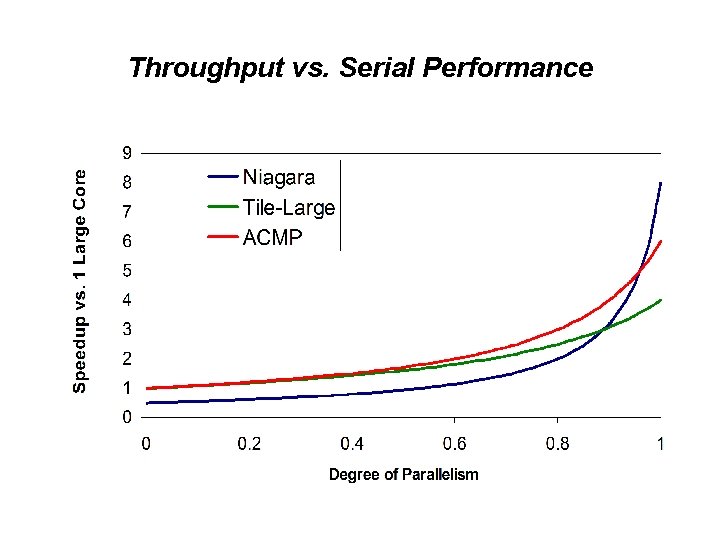

First, a few words about the multi-core chip: The following figure was first published in a UT Tech Report: “ACMP: Balancing Hardware Efficiency and Programmer Efficiency, ” TR-HPS-2007 -001, Feb, 2007 (Actually, it was first submitted to ISCA in June, 2006, and was rejected )

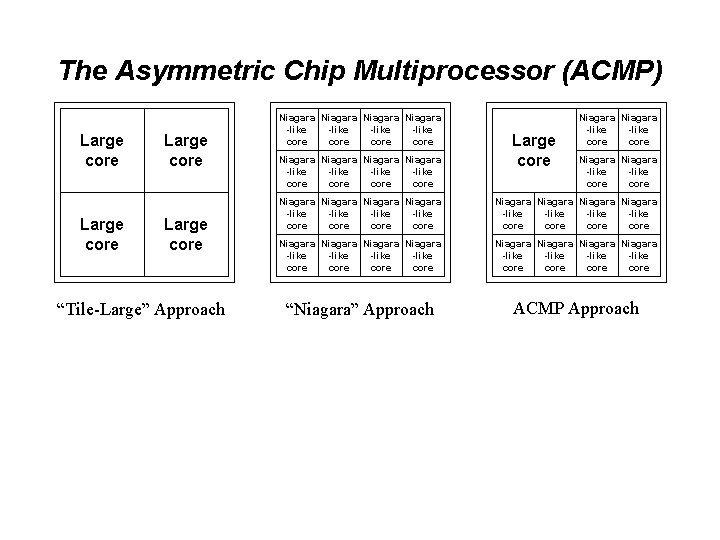

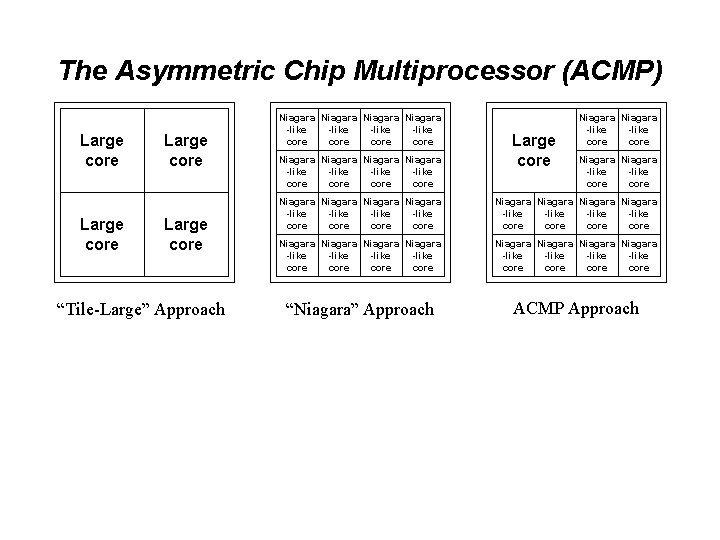

The Asymmetric Chip Multiprocessor (ACMP) Large core “Tile-Large” Approach Niagara Niagara -like -like core core Large core Niagara -like core core Niagara Niagara Niagara Niagara -like -like -like -like core core core “Niagara” Approach ACMP Approach

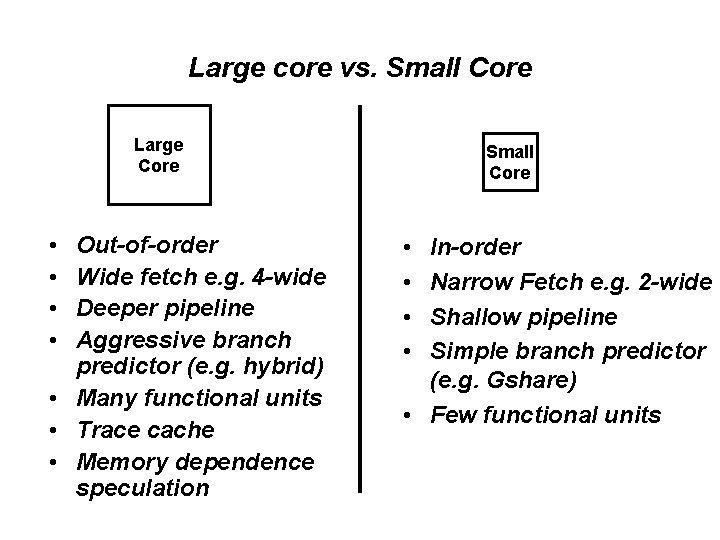

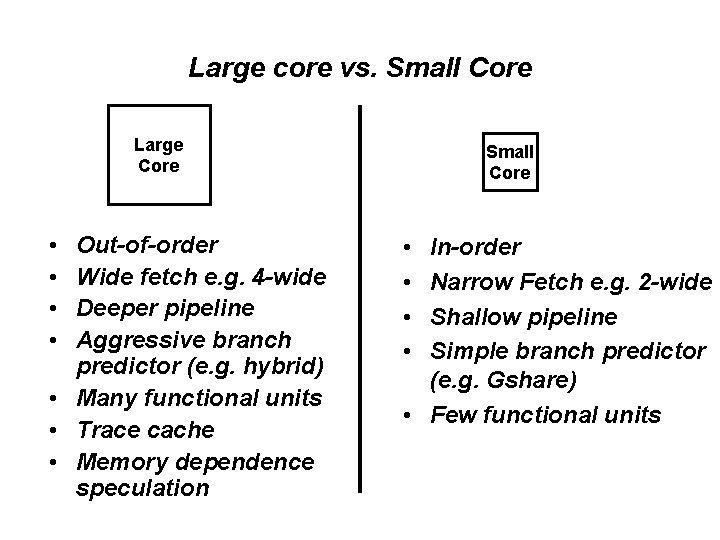

Large core vs. Small Core Large Core • • Out-of-order Wide fetch e. g. 4 -wide Deeper pipeline Aggressive branch predictor (e. g. hybrid) • Many functional units • Trace cache • Memory dependence speculation Small Core • • In-order Narrow Fetch e. g. 2 -wide Shallow pipeline Simple branch predictor (e. g. Gshare) • Few functional units

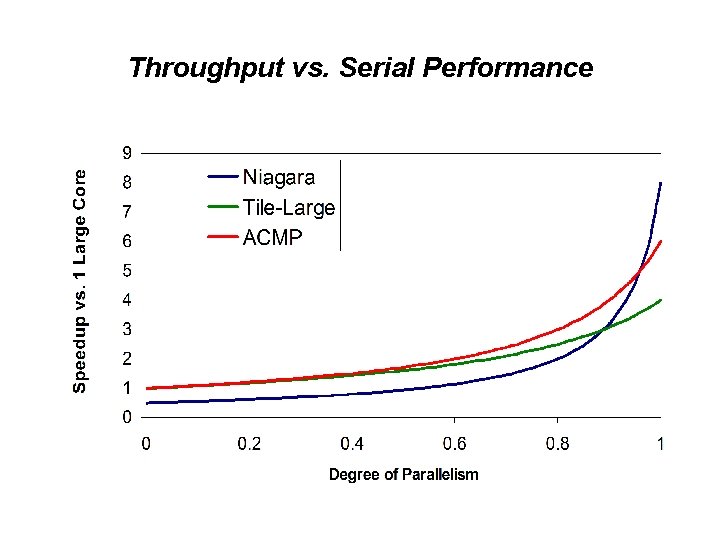

Throughput vs. Serial Performance

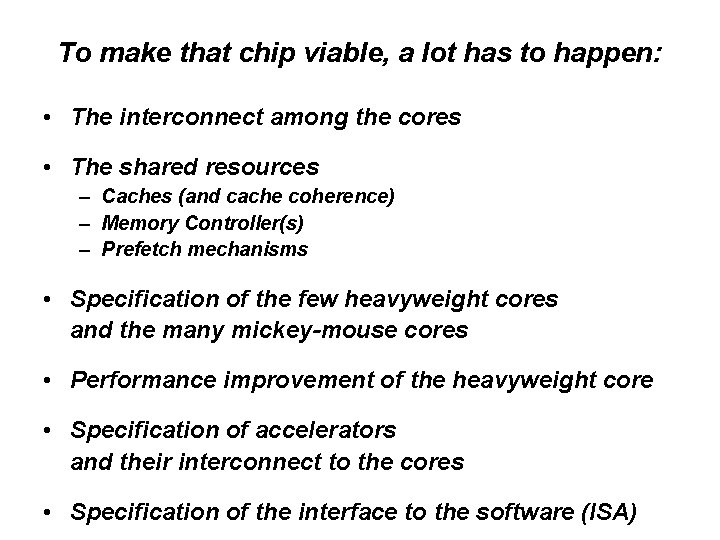

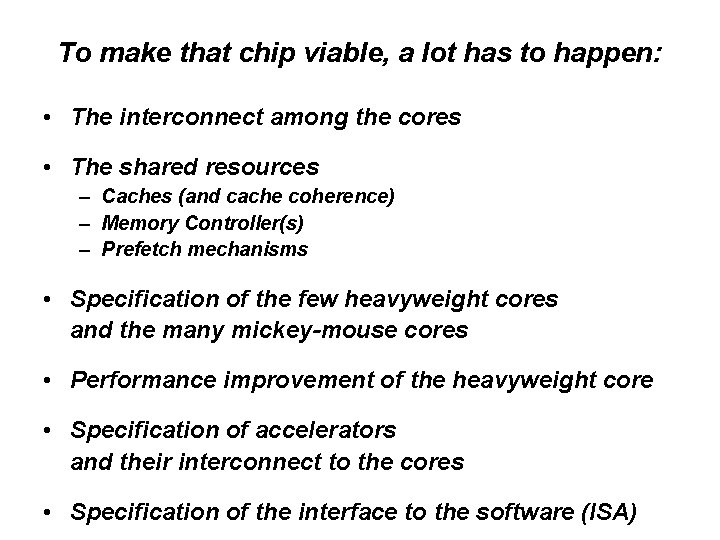

To make that chip viable, a lot has to happen: • The interconnect among the cores • The shared resources – Caches (and cache coherence) – Memory Controller(s) – Prefetch mechanisms • Specification of the few heavyweight cores and the many mickey-mouse cores • Performance improvement of the heavyweight core • Specification of accelerators and their interconnect to the cores • Specification of the interface to the software (ISA)

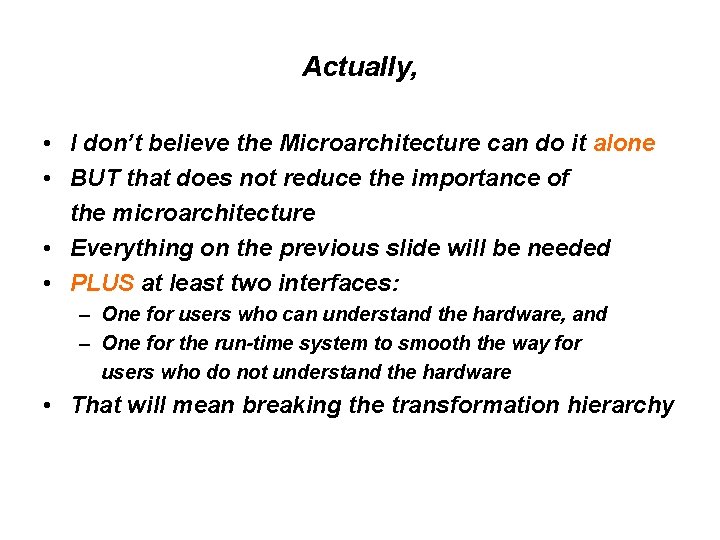

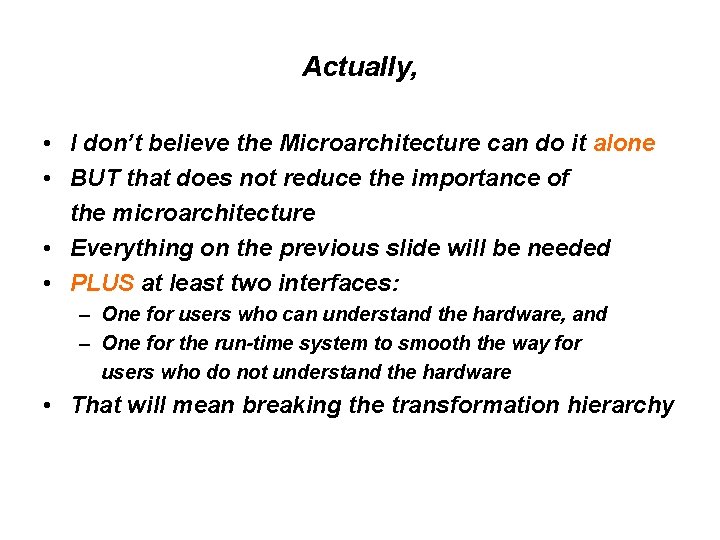

Actually, • I don’t believe the Microarchitecture can do it alone • BUT that does not reduce the importance of the microarchitecture • Everything on the previous slide will be needed • PLUS at least two interfaces: – One for users who can understand the hardware, and – One for the run-time system to smooth the way for users who do not understand the hardware • That will mean breaking the transformation hierarchy

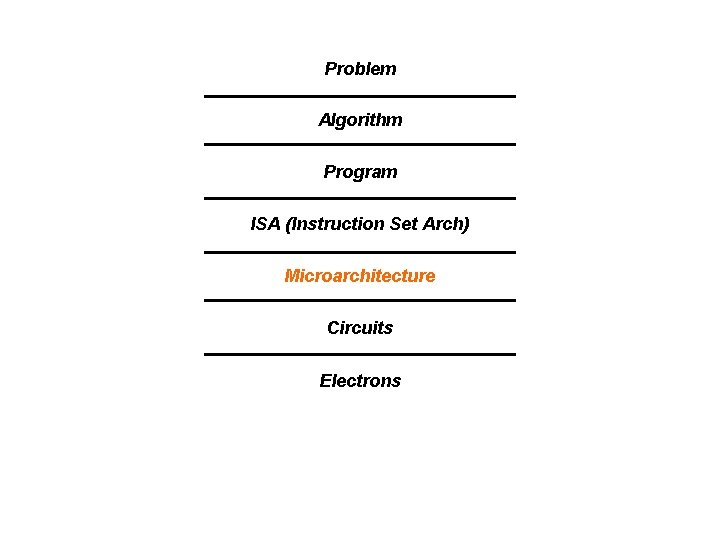

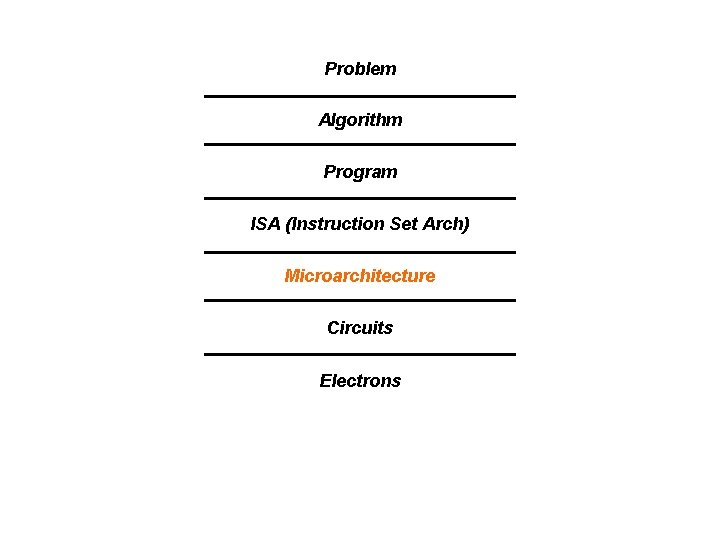

Problem Algorithm Program ISA (Instruction Set Arch) Microarchitecture Circuits Electrons

and that means (in my view) A vibrant future for Microarchitecture