Micro Baby ALU MB ALU o Constructed form

Micro. Baby ALU

MB ALU o Constructed form building block components n n n n o 8 -bit adder 4 -to-1 mux by 8 -bit 4 -to-1 mux 2 -to-1 mux by 8 -bit All 0’s detector Bus Driver – 8 -bit Register – 8 -bit The objective is to implement this in VHDL, verify the implementation, and then synthesize it in Quartis. 8/22/2012 – ECE 3561 Lect 2 Copyright 2012 - Joanne De. Groat, ECE, OSU 2

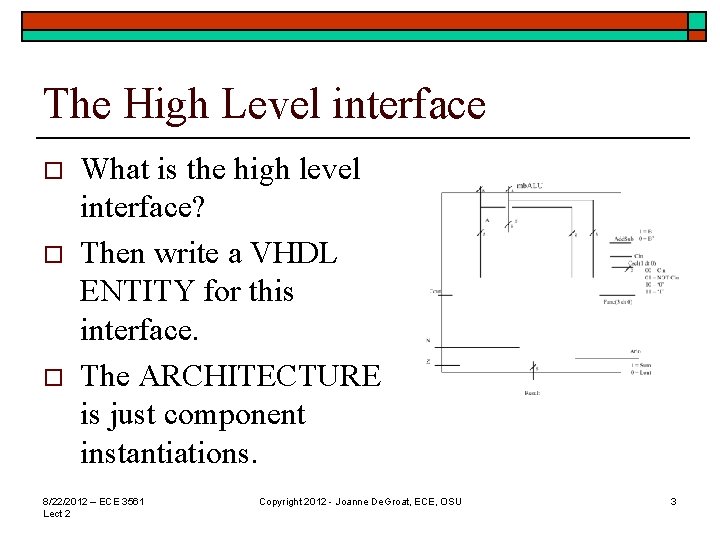

The High Level interface o o o What is the high level interface? Then write a VHDL ENTITY for this interface. The ARCHITECTURE is just component instantiations. 8/22/2012 – ECE 3561 Lect 2 Copyright 2012 - Joanne De. Groat, ECE, OSU 3

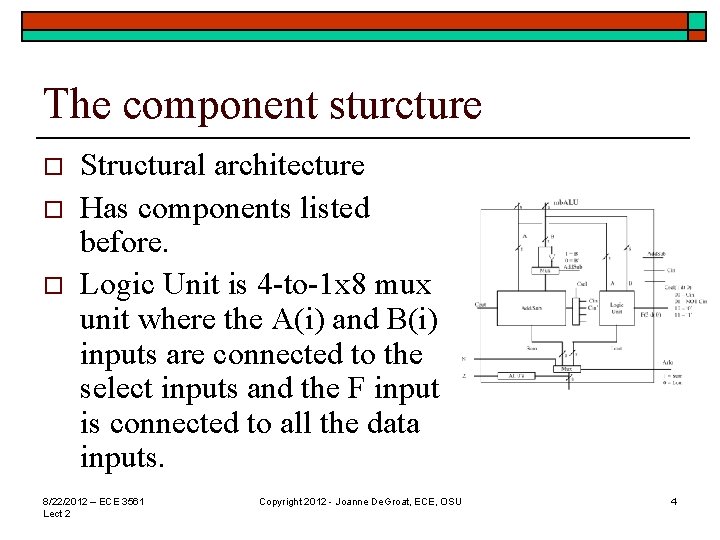

The component sturcture o o o Structural architecture Has components listed before. Logic Unit is 4 -to-1 x 8 mux unit where the A(i) and B(i) inputs are connected to the select inputs and the F input is connected to all the data inputs. 8/22/2012 – ECE 3561 Lect 2 Copyright 2012 - Joanne De. Groat, ECE, OSU 4

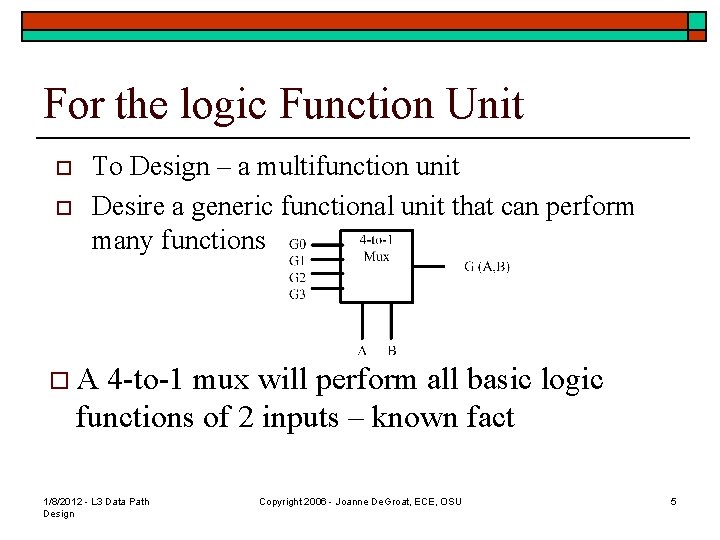

For the logic Function Unit o o To Design – a multifunction unit Desire a generic functional unit that can perform many functions o. A 4 -to-1 mux will perform all basic logic functions of 2 inputs – known fact 1/8/2012 - L 3 Data Path Design Copyright 2006 - Joanne De. Groat, ECE, OSU 5

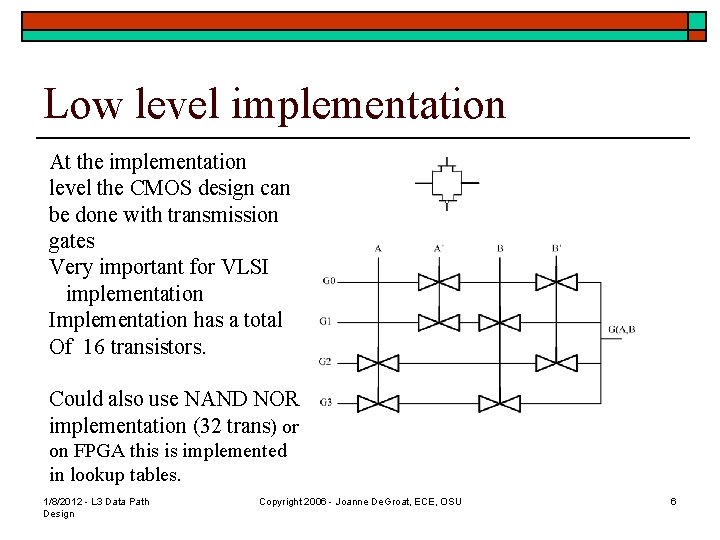

Low level implementation At the implementation level the CMOS design can be done with transmission gates Very important for VLSI implementation Implementation has a total Of 16 transistors. Could also use NAND NOR implementation (32 trans) or on FPGA this is implemented in lookup tables. 1/8/2012 - L 3 Data Path Design Copyright 2006 - Joanne De. Groat, ECE, OSU 6

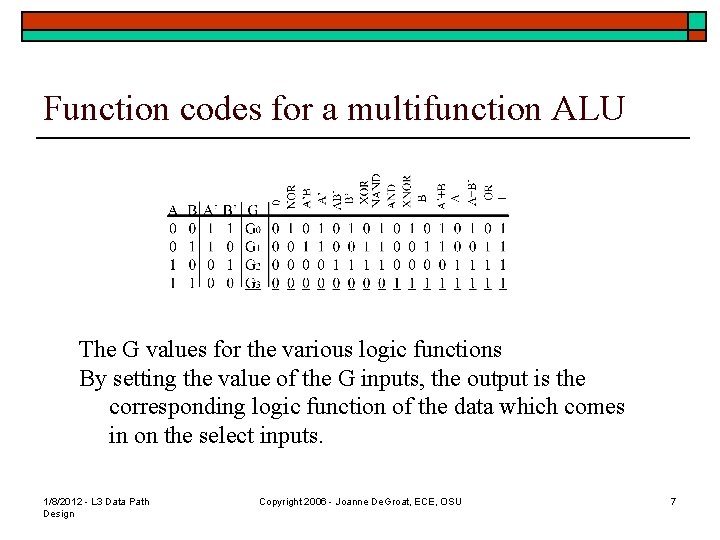

Function codes for a multifunction ALU The G values for the various logic functions By setting the value of the G inputs, the output is the corresponding logic function of the data which comes in on the select inputs. 1/8/2012 - L 3 Data Path Design Copyright 2006 - Joanne De. Groat, ECE, OSU 7

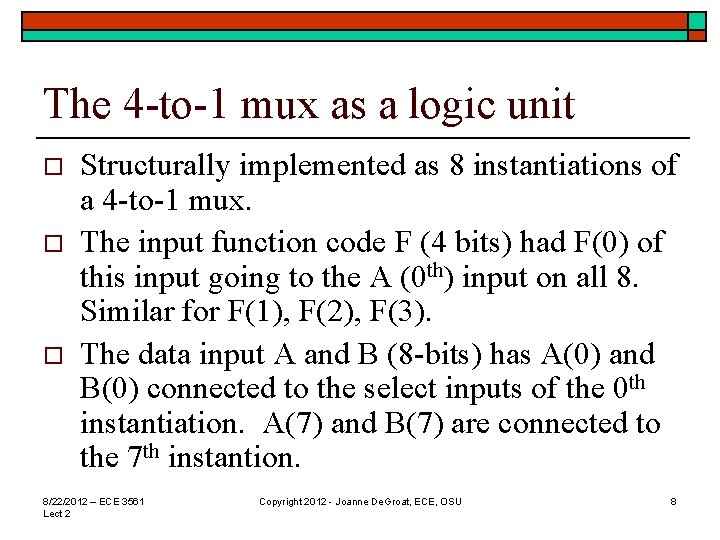

The 4 -to-1 mux as a logic unit o o o Structurally implemented as 8 instantiations of a 4 -to-1 mux. The input function code F (4 bits) had F(0) of this input going to the A (0 th) input on all 8. Similar for F(1), F(2), F(3). The data input A and B (8 -bits) has A(0) and B(0) connected to the select inputs of the 0 th instantiation. A(7) and B(7) are connected to the 7 th instantion. 8/22/2012 – ECE 3561 Lect 2 Copyright 2012 - Joanne De. Groat, ECE, OSU 8

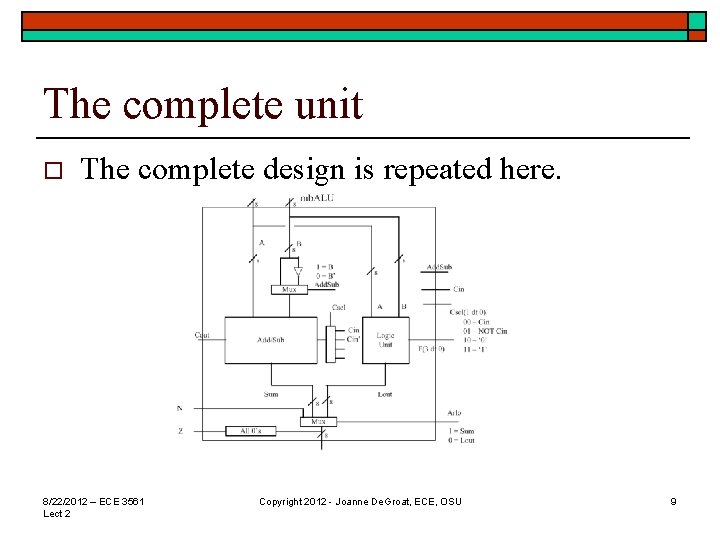

The complete unit o The complete design is repeated here. 8/22/2012 – ECE 3561 Lect 2 Copyright 2012 - Joanne De. Groat, ECE, OSU 9

Subtraction ability o o By suppling B and NOT B (1’s complement of B), subtraction is achieved by SUM = A + NOT B with the Cin complemented. 8/22/2012 – ECE 3561 Lect 2 Copyright 2012 - Joanne De. Groat, ECE, OSU 10

The Testbench o Testbench test vectors classes 8/22/2012 – ECE 3561 Lect 2 Copyright 2012 - Joanne De. Groat, ECE, OSU 11

- Slides: 11