MIC 7340 Introduction aux microcontrleurs Mounir Boukadoum Traduit

MIC 7340 Introduction aux microcontrôleurs Mounir Boukadoum Traduit et adapté de l’anglais

Comment additionne-t’on 147 et 332 ? 1. On écrit les deux nombres l’un au dessus de l’autre 2. On les additionne colonne par colonne avec les retenues 3. On note le résultat final Traduit et adapté de l’anglais

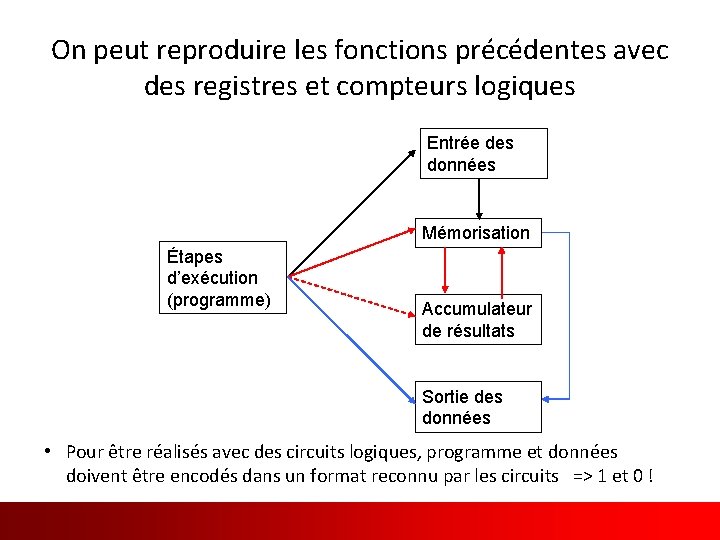

On peut reproduire les fonctions précédentes avec des registres et compteurs logiques Entrée des données Mémorisation Étapes d’exécution (programme) Accumulateur de résultats Sortie des données • Pour être réalisés avec des circuits logiques, programme et données doivent être encodés dans un format reconnu par les circuits => 1 et 0 ! Traduit et adapté de l’anglais

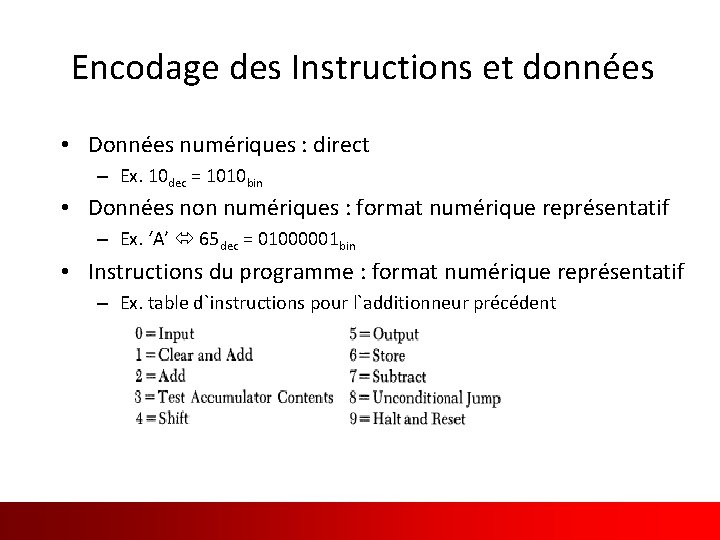

Encodage des Instructions et données • Données numériques : direct – Ex. 10 dec = 1010 bin • Données non numériques : format numérique représentatif – Ex. ‘A’ 65 dec = 01000001 bin • Instructions du programme : format numérique représentatif – Ex. table d`instructions pour l`additionneur précédent Traduit et adapté de l’anglais

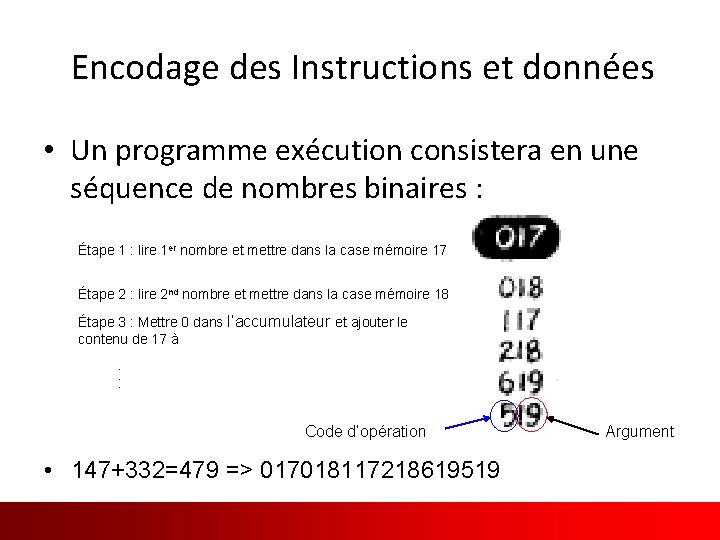

Encodage des Instructions et données • Un programme exécution consistera en une séquence de nombres binaires : Étape 1 : lire 1 nombre et mettre dans la case mémoire 17 er Étape 2 : lire 2 nd nombre et mettre dans la case mémoire 18 Étape 3 : Mettre 0 dans l’accumulateur et ajouter le contenu de 17 à . Code d’opération • 147+332=479 => 017018117218619519 Traduit et adapté de l’anglais Argument

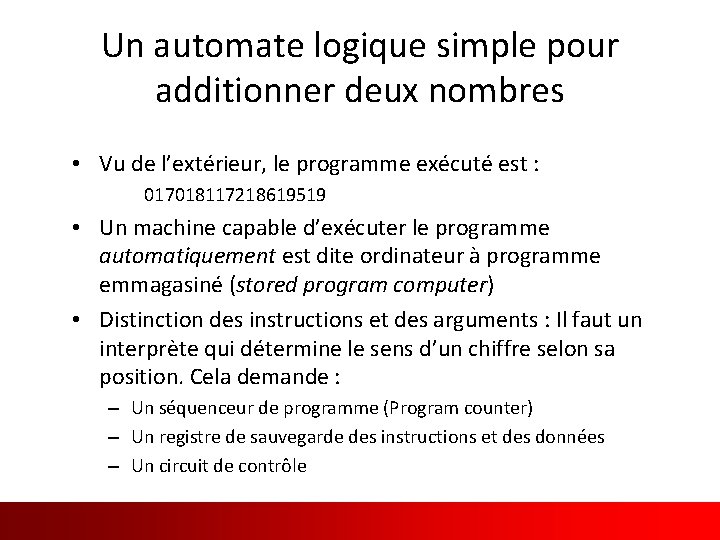

Un automate logique simple pour additionner deux nombres • Vu de l’extérieur, le programme exécuté est : 017018117218619519 • Un machine capable d’exécuter le programme automatiquement est dite ordinateur à programme emmagasiné (stored program computer) • Distinction des instructions et des arguments : Il faut un interprète qui détermine le sens d’un chiffre selon sa position. Cela demande : – Un séquenceur de programme (Program counter) – Un registre de sauvegarde des instructions et des données – Un circuit de contrôle Traduit et adapté de l’anglais

Ordinateur à programme emmagasiné • Peut itérer les instructions • Peut séparer les codes d’instructions des données • Sans entrées, sorties ou mémoire, c’est un microprocesseur (CPU) 1 2 Données 1 2 Commutateur : 1 : Lire entrée et mettre en mémoire 2 : Lire code d`instruction en mémoire Traduit et adapté de l’anglais Adresse en mémoire

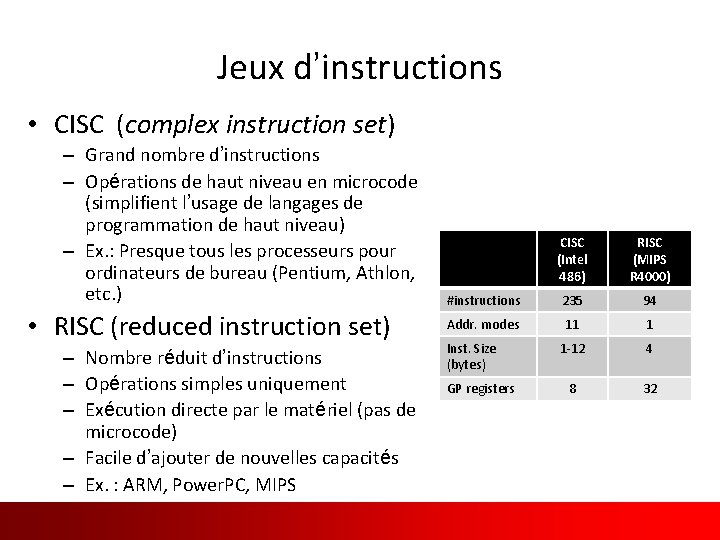

Jeux d’instructions • CISC (complex instruction set) – Grand nombre d’instructions – Opérations de haut niveau en microcode (simplifient l’usage de langages de programmation de haut niveau) – Ex. : Presque tous les processeurs pour ordinateurs de bureau (Pentium, Athlon, etc. ) • RISC (reduced instruction set) – Nombre réduit d’instructions – Opérations simples uniquement – Exécution directe par le matériel (pas de microcode) – Facile d’ajouter de nouvelles capacités – Ex. : ARM, Power. PC, MIPS Traduit et adapté de l’anglais CISC (Intel 486) RISC (MIPS R 4000) #instructions 235 94 Addr. modes 11 1 1 -12 4 8 32 Inst. Size (bytes) GP registers

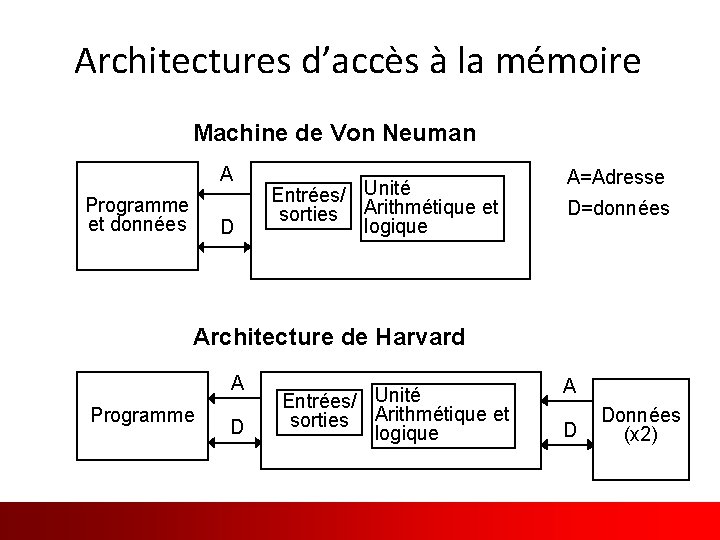

Architectures d’accès à la mémoire Machine de Von Neuman A Programme et données D Entrées/ Unité sorties Arithmétique et logique A=Adresse D=données Architecture de Harvard A Programme Traduit et adapté de l’anglais D Entrées/ Unité sorties Arithmétique et logique A D Données (x 2)

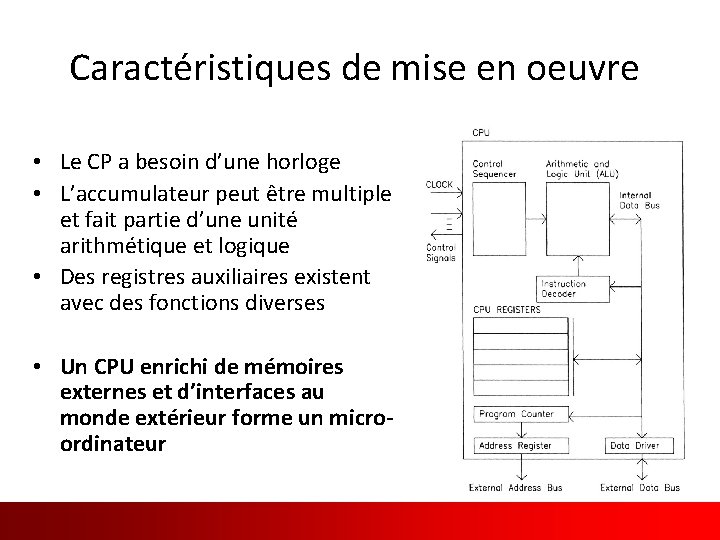

Caractéristiques de mise en oeuvre • Le CP a besoin d’une horloge • L’accumulateur peut être multiple et fait partie d’une unité arithmétique et logique • Des registres auxiliaires existent avec des fonctions diverses • Un CPU enrichi de mémoires externes et d’interfaces au monde extérieur forme un microordinateur Traduit et adapté de l’anglais

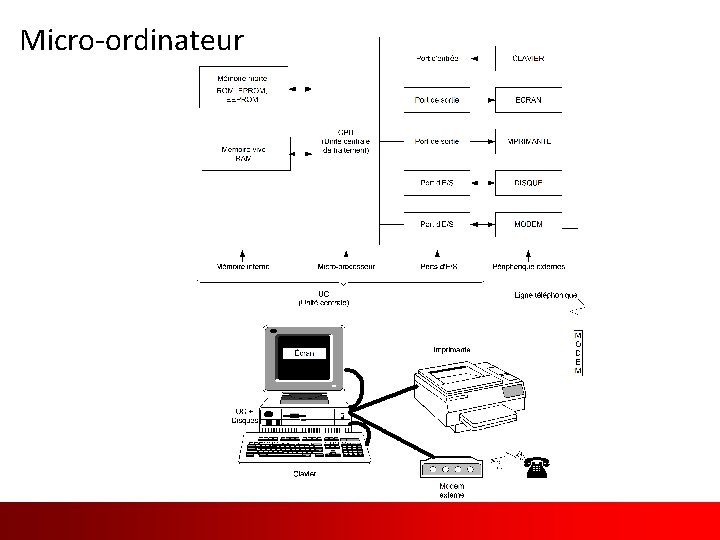

Micro-ordinateur Traduit et adapté de l’anglais

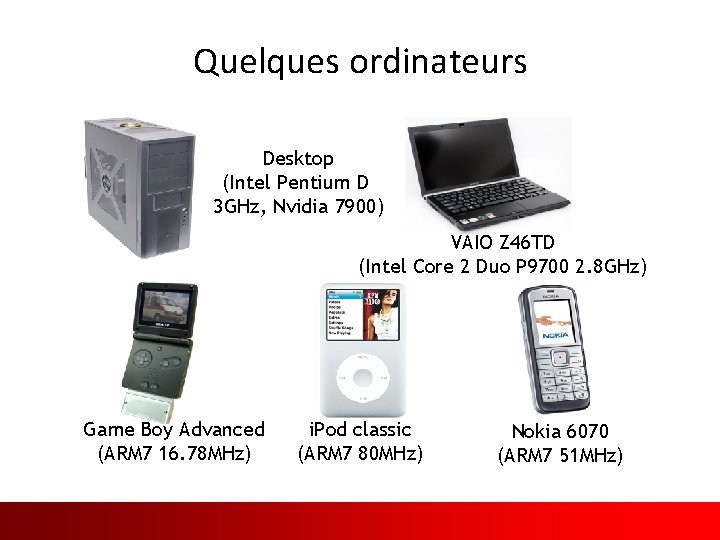

Quelques ordinateurs Desktop (Intel Pentium D 3 GHz, Nvidia 7900) VAIO Z 46 TD (Intel Core 2 Duo P 9700 2. 8 GHz) Game Boy Advanced (ARM 7 16. 78 MHz) Traduit et adapté de l’anglais i. Pod classic (ARM 7 80 MHz) Nokia 6070 (ARM 7 51 MHz)

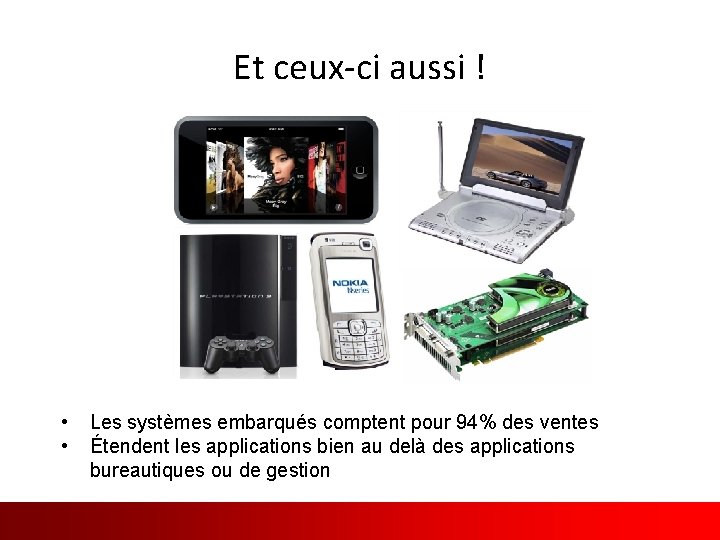

Et ceux-ci aussi ! • • Les systèmes embarqués comptent pour 94% des ventes Étendent les applications bien au delà des applications bureautiques ou de gestion Traduit et adapté de l’anglais

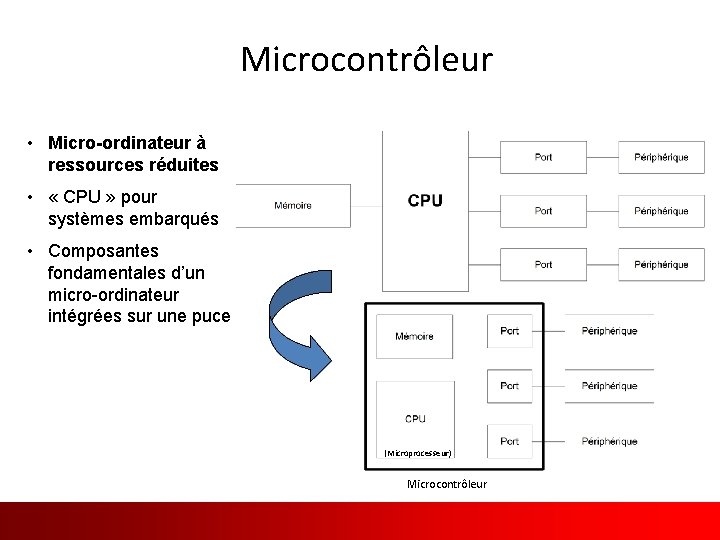

Microcontrôleur • Micro-ordinateur à ressources réduites • « CPU » pour systèmes embarqués • Composantes fondamentales d’un micro-ordinateur intégrées sur une puce (Microprocesseur) Microcontrôleur Traduit et adapté de l’anglais

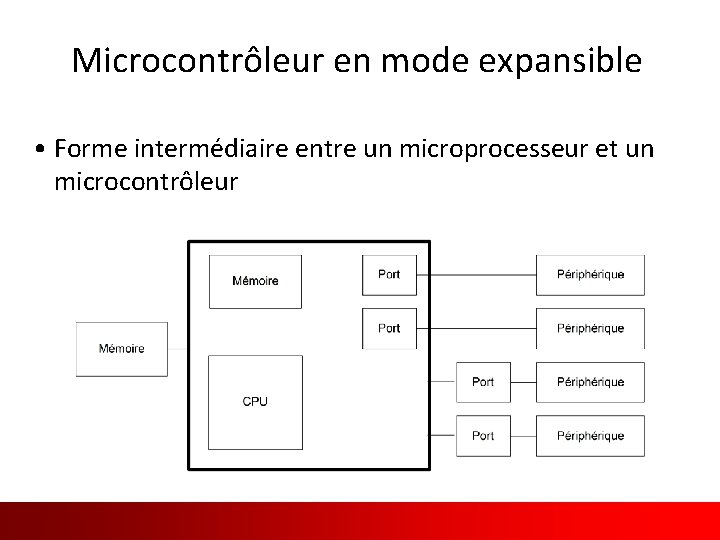

Microcontrôleur en mode expansible • Forme intermédiaire entre un microprocesseur et un microcontrôleur Traduit et adapté de l’anglais

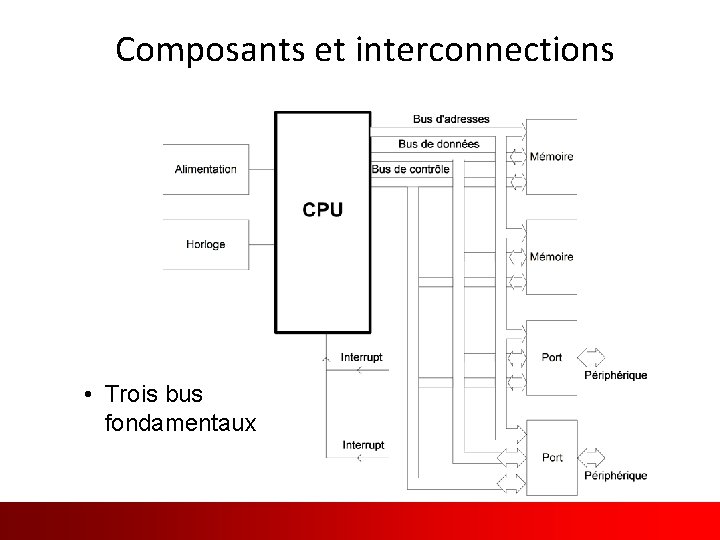

Composants et interconnections • Trois bus fondamentaux Traduit et adapté de l’anglais

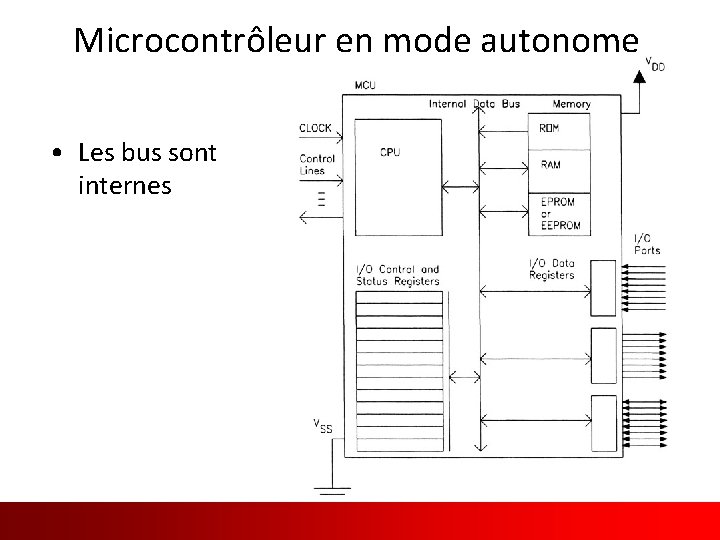

Microcontrôleur en mode autonome • Les bus sont internes Traduit et adapté de l’anglais

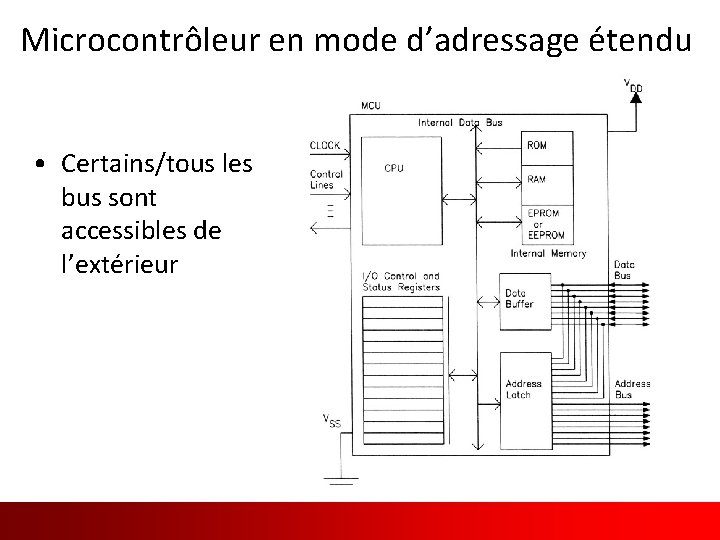

Microcontrôleur en mode d’adressage étendu • Certains/tous les bus sont accessibles de l’extérieur Traduit et adapté de l’anglais

TI Embedded Processors Microcontrollers (MCUs) 16 -bit ultralow power MCUs 32 -bit real-time MCUs 32 -bit ARM Cortex™-M 3 MCUs ARM Cortex-A 8 MPUs MSP 430™ C 2000™ Delfino™ Piccolo™ Stellaris® Sitara™ Up to 25 MHz 40 MHz to 300 MHz Digital Signal Processors (DSPs) ARM®-Based Processors ARM® Cortex™-M 3 Up to 100 MHz Flash, RAM Flash 1 KB to 256 KB 16 KB to 512 KB 8 KB to 256 KB USB, ENET Analog I/O, ADC PWM, ADC, MAC+PHY CAN, LCD, USB, RF CAN, SPI, I 2 C ADC, PWM, SPI ARM® Cortex™-A 8 & ARM 9 300 MHz to >1 GHz DSP+ARM C 6000™ Da. Vinci™ Multi-core DSP Ultra Low power DSP C 6000™ C 5000™ video processors OMAP™ 24. 000 MMACS Cache, RAM, ROM 300 MHz to >1 Ghz +Accelerator Cache RAM, ROM Up to 300 MHz +Accelerator Up to 320 KB RAM Up to 128 KB ROM USB, CAN, PCIe, EMAC USB, ENET, PCIe, SATA, SPI SRIO, EMAC DMA, PCIe USB, ADC Mc. BSP, SPI, I 2 C Measurement, Motor Control, Connectivity, Security, Industrial computing, Floating/Fixed Point Telecom test & meas, Audio, Voice Sensing, General Digital Power, Video, Audio, Voice, media gateways, Motion Control, HMI, POS & portable Medical, Biometrics Lighting, Ren. Enrgy. Industrial Automation Purpose base stations data terminals Security, Conferencing $0. 25 to $9. 00 $1. 50 to $20. 00 $1. 00 to $8. 00 $5. 00 to $200. 00 $40 to $200. 00 $3. 00 to $10. 00 Software & Dev. Tools Traduit et adapté de l’anglais 3 5 xx Gen Summary …

La famille MSP 430 : Architecture générale • Bus interne de données interne de 16 bits et externe de 8 bits • Jusqu’à 20 bits d’espace d’adressage • Site web de TI Traduit et adapté de l’anglais

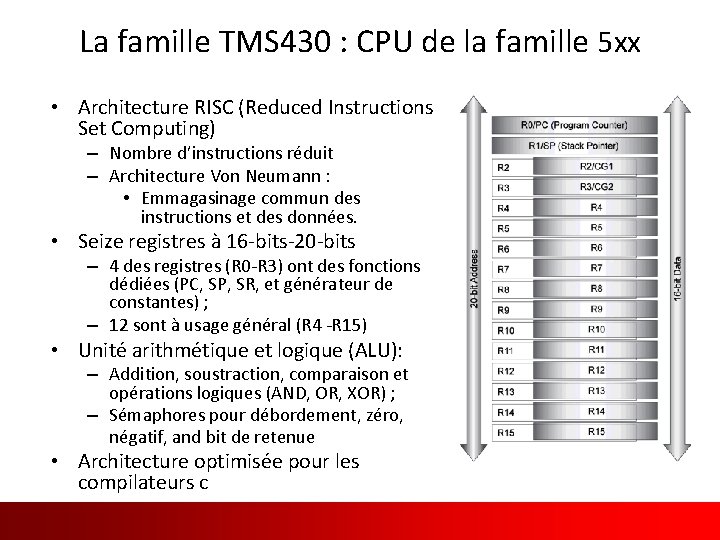

La famille TMS 430 : CPU de la famille 5 xx • Architecture RISC (Reduced Instructions Set Computing) – Nombre d’instructions réduit – Architecture Von Neumann : • Emmagasinage commun des instructions et des données. • Seize registres à 16 -bits-20 -bits – 4 des registres (R 0 -R 3) ont des fonctions dédiées (PC, SP, SR, et générateur de constantes) ; – 12 sont à usage général (R 4 -R 15) • Unité arithmétique et logique (ALU): – Addition, soustraction, comparaison et opérations logiques (AND, OR, XOR) ; – Sémaphores pour débordement, zéro, négatif, and bit de retenue • Architecture optimisée pour les compilateurs c Traduit et adapté de l’anglais

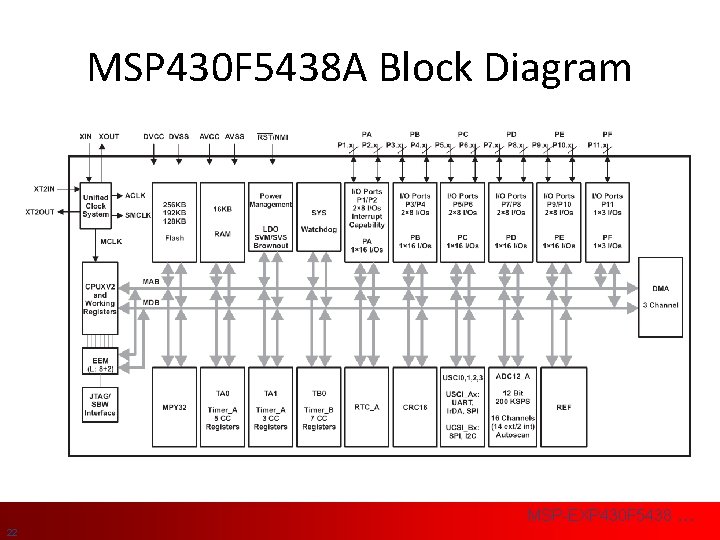

MSP 430 F 5438 A Block Diagram Traduit et adapté de l’anglais 22 MSP-EXP 430 F 5438 …

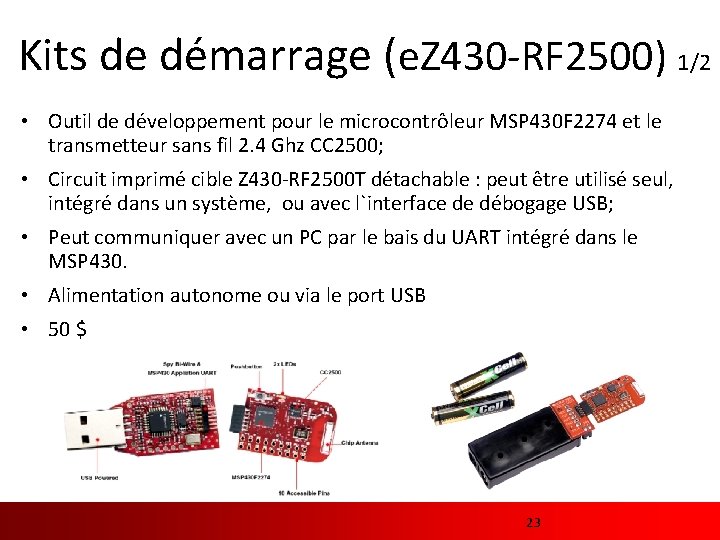

Kits de démarrage (e. Z 430 -RF 2500) 1/2 • Outil de développement pour le microcontrôleur MSP 430 F 2274 et le transmetteur sans fil 2. 4 Ghz CC 2500; • Circuit imprimé cible Z 430 -RF 2500 T détachable : peut être utilisé seul, intégré dans un système, ou avec l`interface de débogage USB; • Peut communiquer avec un PC par le bais du UART intégré dans le MSP 430. • Alimentation autonome ou via le port USB • 50 $ Traduit et adapté de l’anglais 23

Kit de démarrage e. Z 430 -RF 2500 : MSP 430 F 2274 et périphériques 2/2 • Performance de 16 -MIPS; • Convertisseur A-N à approximations successives avec 10 bits de résolution et fréquence d`échantillonnage jusqu’à 200 ke/s • Compteur/temporisateur de 16 bits • 2 amplificateur opérationnels intégrés • Compteur/temporisateur de 16 bits • Chien de garde ( « Watchdog timer » ) • Module sériel universel supportant UART/LIN, (2) SPI, I 2 C, or Ir. DA • Taux de transfert de données programmable jusqu’à 500 kb/s • 5 modes d’opération à faible courant (0. 7 μA en mode standby) • Transmetteur RF 2. 4 -GHz externe (CC 2500) Traduit et adapté de l’anglais 24

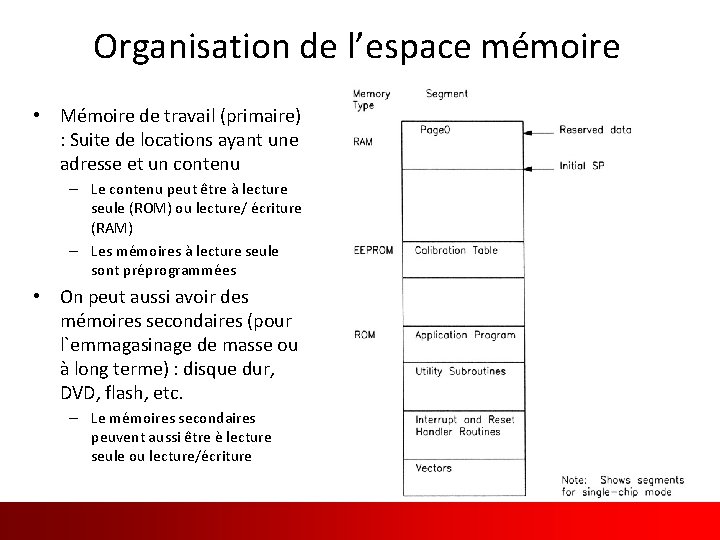

Organisation de l’espace mémoire • Mémoire de travail (primaire) : Suite de locations ayant une adresse et un contenu – Le contenu peut être à lecture seule (ROM) ou lecture/ écriture (RAM) – Les mémoires à lecture seule sont préprogrammées • On peut aussi avoir des mémoires secondaires (pour l`emmagasinage de masse ou à long terme) : disque dur, DVD, flash, etc. – Le mémoires secondaires peuvent aussi être è lecture seule ou lecture/écriture Traduit et adapté de l’anglais

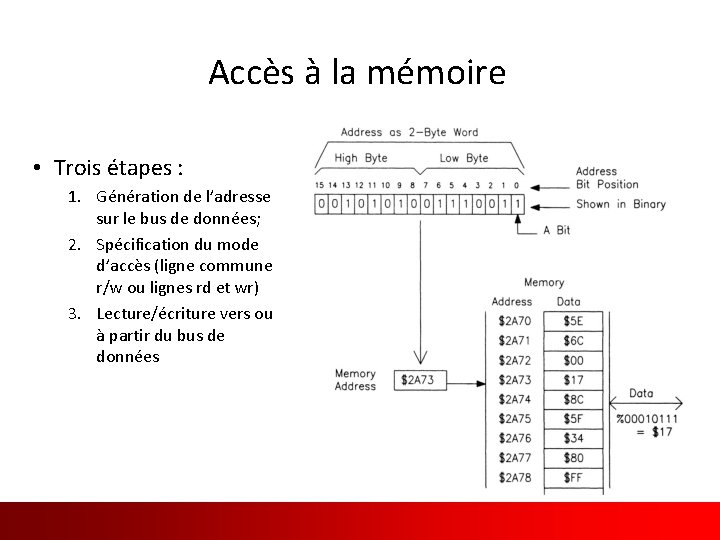

Accès à la mémoire • Trois étapes : 1. Génération de l’adresse sur le bus de données; 2. Spécification du mode d’accès (ligne commune r/w ou lignes rd et wr) 3. Lecture/écriture vers ou à partir du bus de données Traduit et adapté de l’anglais

Cycle de fonctionnement d’un CPU Traduit et adapté de l’anglais

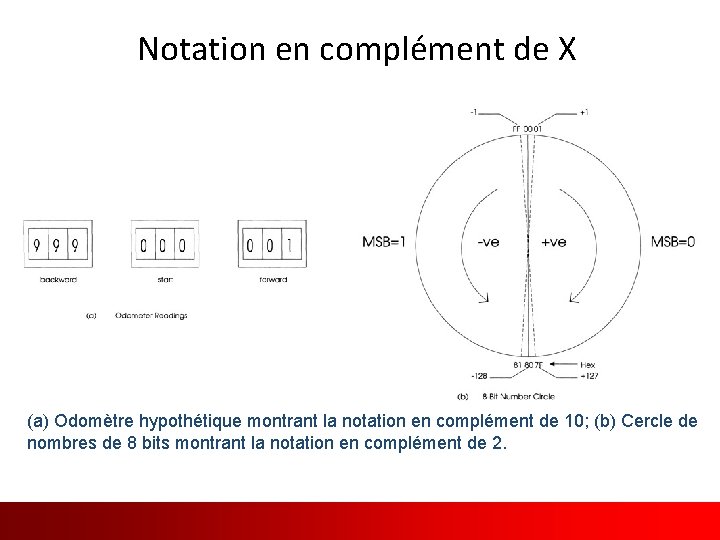

Notation en complément de X (a) Odomètre hypothétique montrant la notation en complément de 10; (b) Cercle de nombres de 8 bits montrant la notation en complément de 2. Traduit et adapté de l’anglais

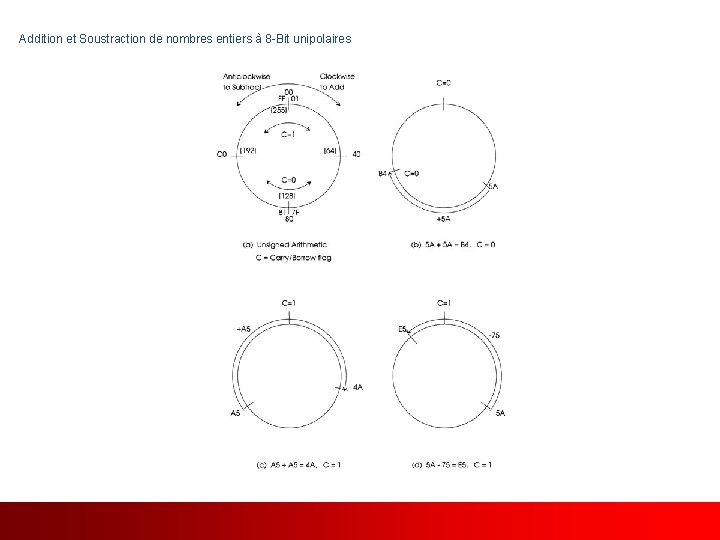

Addition et Soustraction de nombres entiers à 8 -Bit unipolaires Traduit et adapté de l’anglais

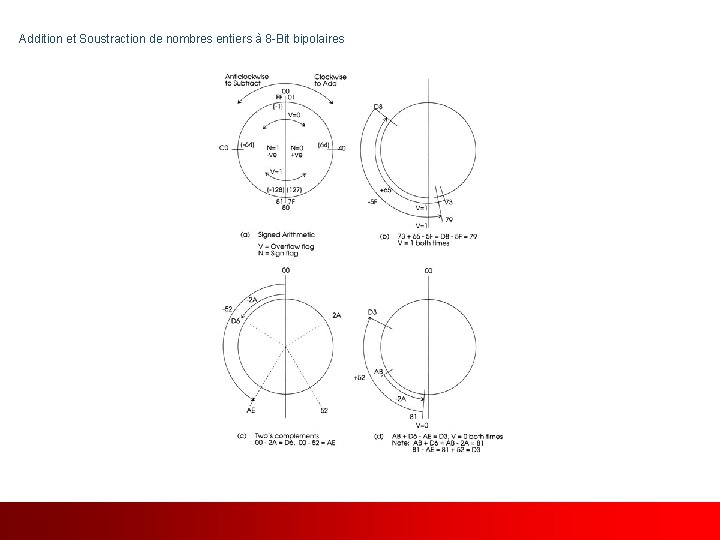

Addition et Soustraction de nombres entiers à 8 -Bit bipolaires Traduit et adapté de l’anglais

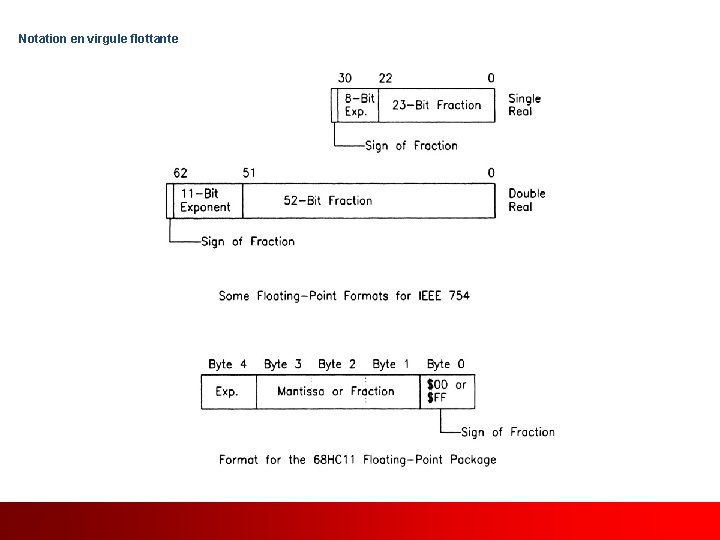

Notation en virgule flottante Traduit et adapté de l’anglais

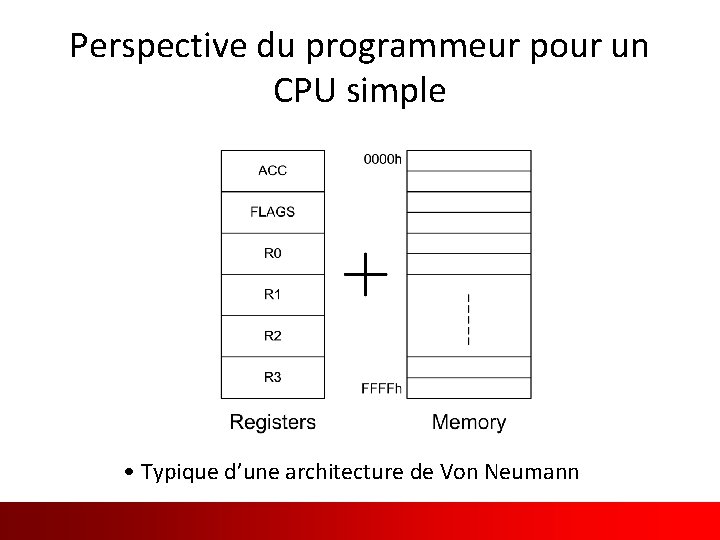

Perspective du programmeur pour un CPU simple • Typique d’une architecture de Von Neumann Traduit et adapté de l’anglais

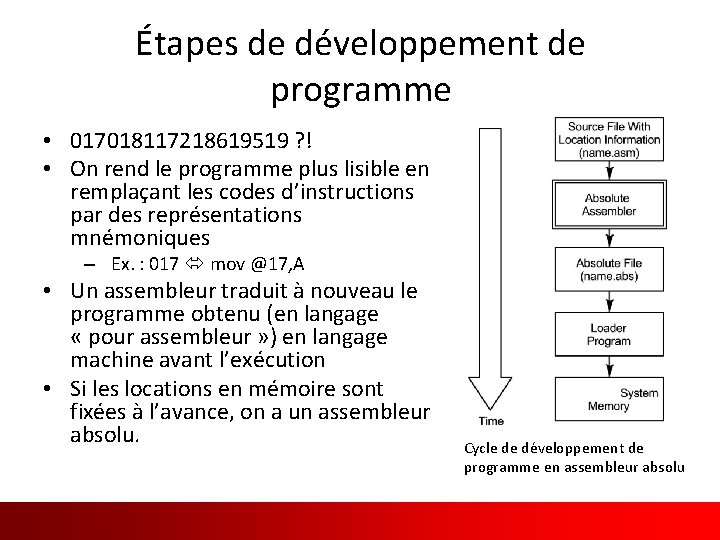

Étapes de développement de programme • 017018117218619519 ? ! • On rend le programme plus lisible en remplaçant les codes d’instructions par des représentations mnémoniques – Ex. : 017 mov @17, A • Un assembleur traduit à nouveau le programme obtenu (en langage « pour assembleur » ) en langage machine avant l’exécution • Si les locations en mémoire sont fixées à l’avance, on a un assembleur absolu. Traduit et adapté de l’anglais Cycle de développement de programme en assembleur absolu

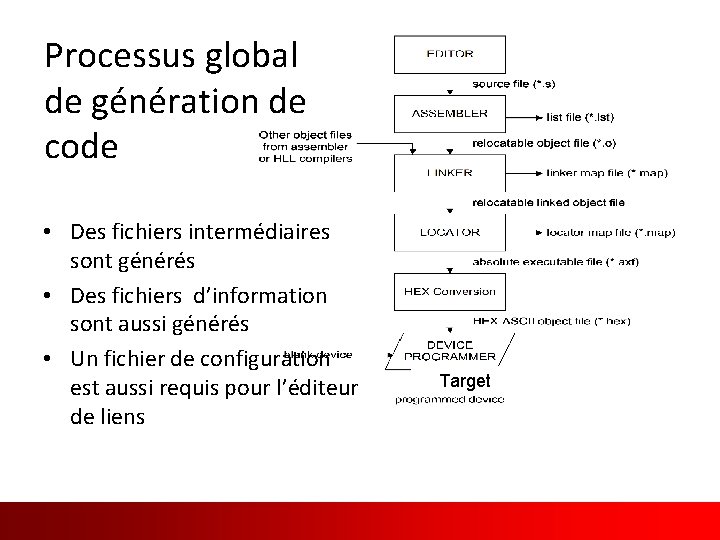

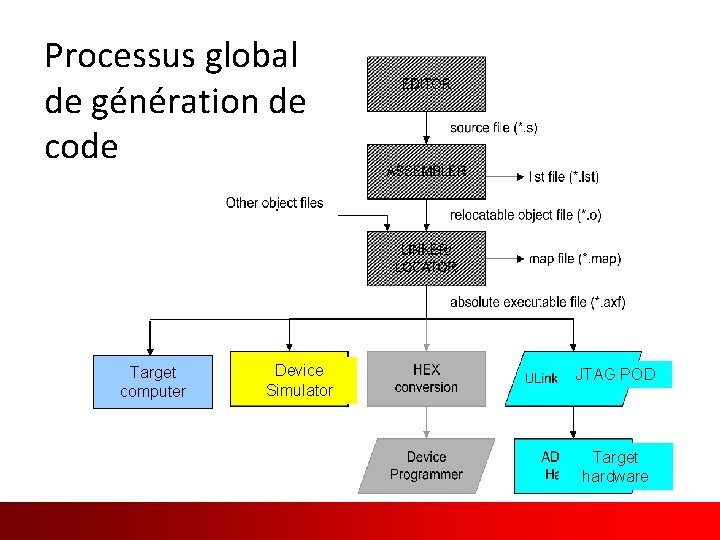

Processus global de génération de code • Des fichiers intermédiaires sont générés • Des fichiers d’information sont aussi générés • Un fichier de configuration est aussi requis pour l’éditeur de liens Traduit et adapté de l’anglais Target

Processus global de génération de code Target computer Device Simulator JTAG POD Target hardware Traduit et adapté de l’anglais

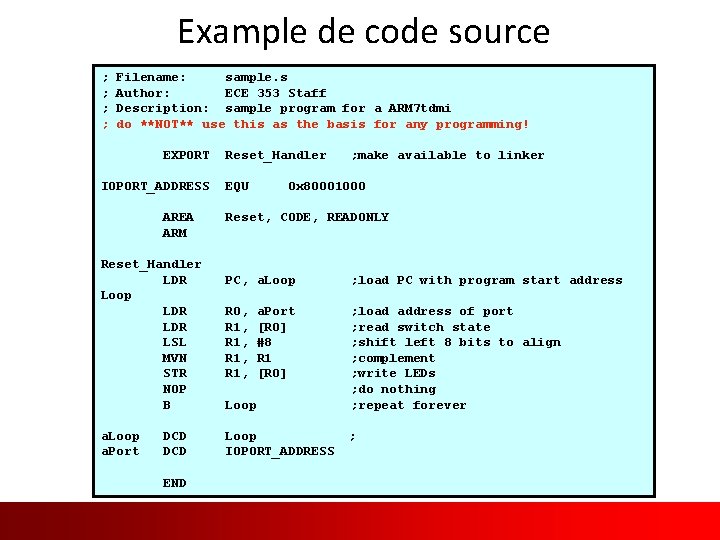

Example de code source ; ; Filename: sample. s Author: ECE 353 Staff Description: sample program for a ARM 7 tdmi do **NOT** use this as the basis for any programming! EXPORT IOPORT_ADDRESS AREA ARM Reset_Handler LDR Loop LDR LSL MVN STR NOP B a. Loop a. Port DCD END Traduit et adapté de l’anglais Reset_Handler EQU ; make available to linker 0 x 80001000 Reset, CODE, READONLY PC, a. Loop ; load PC with program start address R 0, R 1, ; load address of port ; read switch state ; shift left 8 bits to align ; complement ; write LEDs ; do nothing ; repeat forever a. Port [R 0] #8 R 1 [R 0] Loop IOPORT_ADDRESS ;

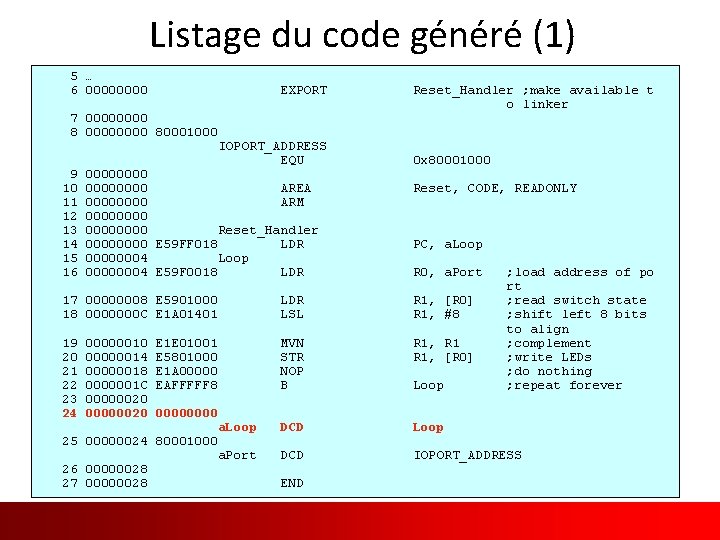

Listage du code généré (1) 5 … 6 0000 EXPORT 7 00000000 80001000 9 10 11 12 13 14 15 16 IOPORT_ADDRESS EQU 00000000 AREA 0000 ARM 00000000 Reset_Handler 0000 E 59 FF 018 LDR 00000004 Loop 00000004 E 59 F 0018 LDR Reset_Handler ; make available t o linker 0 x 80001000 Reset, CODE, READONLY PC, a. Loop R 0, a. Port ; load address of po rt ; read switch state ; shift left 8 bits to align ; complement ; write LEDs ; do nothing ; repeat forever 17 00000008 E 5901000 18 0000000 C E 1 A 01401 LDR LSL R 1, [R 0] R 1, #8 19 20 21 22 23 24 MVN STR NOP B R 1, [R 0] a. Loop DCD Loop a. Port DCD IOPORT_ADDRESS 00000010 00000014 00000018 0000001 C 00000020 E 1 E 01001 E 5801000 E 1 A 00000 EAFFFFF 8 0000 25 00000024 80001000 26 00000028 27 00000028 Traduit et adapté de l’anglais END Loop

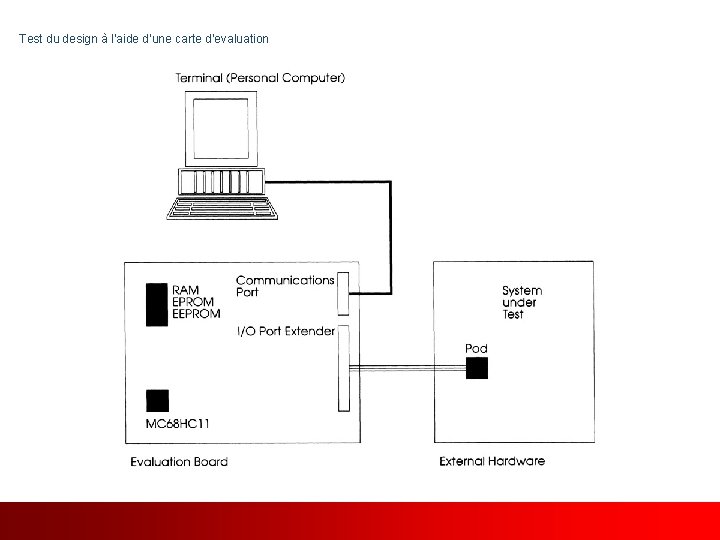

Test du design à l’aide d’une carte d’evaluation Traduit et adapté de l’anglais

Allure dans une fenêtre de desassemblage a. Loop a. Port 0 x 00080000 0 x 00080004 0 x 0008000 C 0 x 00080010 0 x 00080014 0 x 00080018 0 x 0008001 C 0 x 00080020 0 x 00080024 0 x 00080028 0 x 0008002 C 0 x 00080030 0 x 00080034 Adresses Traduit et adapté de l’anglais E 59 FF 018 E 59 F 0018 E 5901000 E 1 A 01401 E 1 E 01001 E 5801000 E 1 A 00000 EAFFFFF 8 00080004 80001000 00000000 Code machine DD LDR MOV MVN STR NOP B DD ANDHI ANDEQ 0 x. E 59 FF 018 R 0, [PC, #0 x 0018] R 1, [R 0] R 1, LSL #8 R 1, [R 0] ? 0 x 00080004 R 1, R 0, R 0 R 0, R 0 Code Assembleur equivalent

Débogage • Tout comme le génie, l’écriture de programmes exige 1% d’inspiration et 99% de transpiration – Un code source fonctionne rarement du premier coup ! – Une fois devenu fonctionnel, il doit être validé – Ensuite, il faut le maintenir • Un débogueur permet de : – – Charger un programme dans un environnement d’exécution contrôlé Exécuter le programme pas à pas Établir dynamiquement des points d’arrêt ( « breakpoints » ) Afficher/modifier des valeurs de registres ou locations en mémoire Traduit et adapté de l’anglais

Le cycle de programmation Traduit et adapté de l’anglais 41

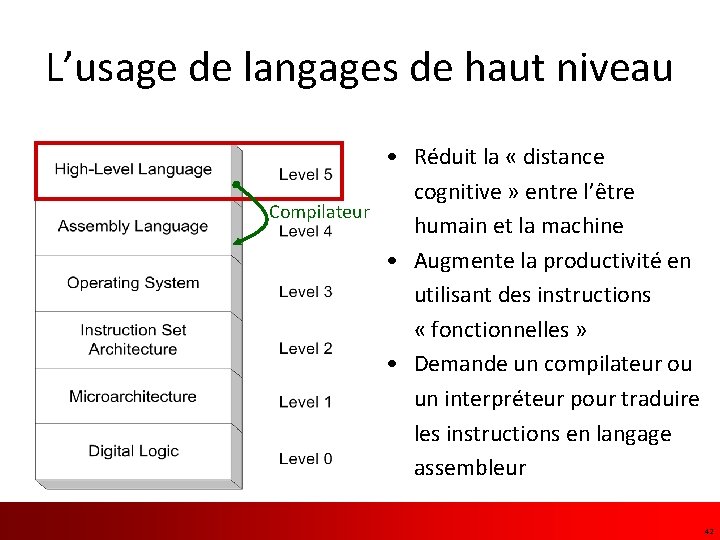

L’usage de langages de haut niveau • Réduit la « distance cognitive » entre l’être Compilateur humain et la machine • Augmente la productivité en utilisant des instructions « fonctionnelles » • Demande un compilateur ou un interpréteur pour traduire les instructions en langage assembleur Traduit et adapté de l’anglais 42

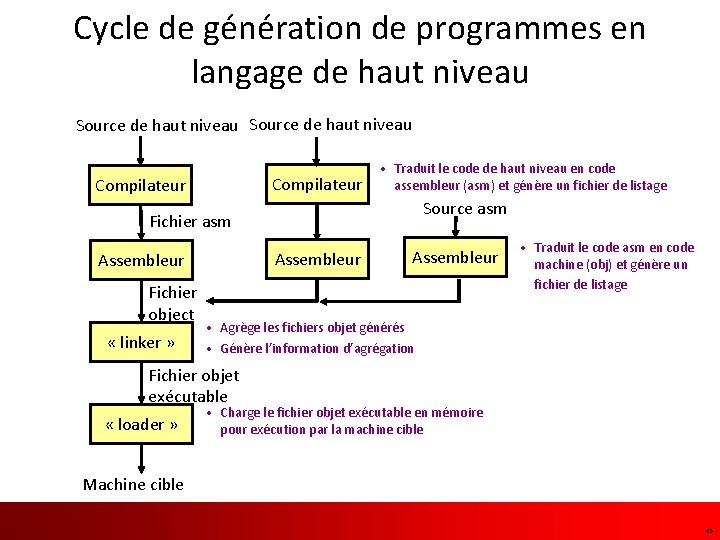

Cycle de génération de programmes en langage de haut niveau Source de haut niveau Compilateur • Traduit le code de haut niveau en code assembleur (asm) et génère un fichier de listage Source asm Fichier asm Assembleur Fichier object « linker » Assembleur • Traduit le code asm en code machine (obj) et génère un fichier de listage • Agrège les fichiers objet générés • Génère l’information d’agrégation Fichier objet exécutable « loader » • Charge le fichier objet exécutable en mémoire pour exécution par la machine cible Machine cible Traduit et adapté de l’anglais 43

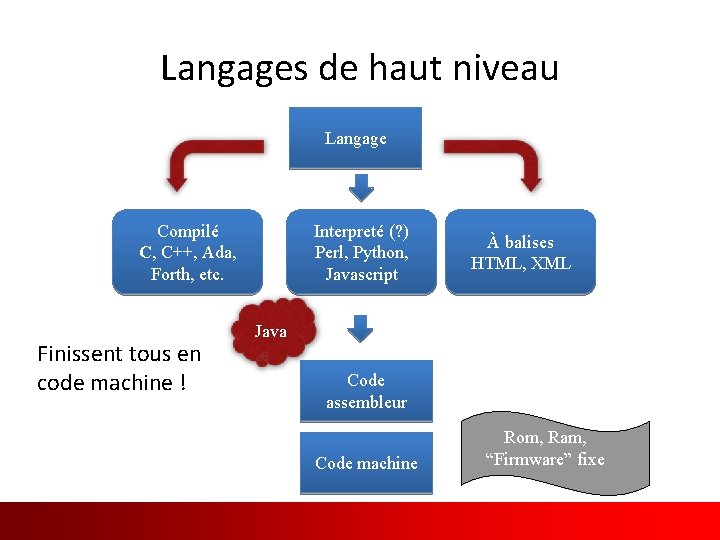

Langages de haut niveau Langage Compilé C, C++, Ada, Forth, etc. Finissent tous en code machine ! Interpreté (? ) Perl, Python, Javascript Java Code assembleur Code machine Traduit et adapté de l’anglais À balises HTML, XML Rom, Ram, “Firmware” fixe

Exigences pour le code d’un système embarqué • Densité • Rapidité • Accès direct au matériel (registres, bits, etc. ) • Robustesse (redondance ? ) Contraintes souvent contradictoires étant données les ressources Traduit et adapté de l’anglais

- Slides: 45