Metallization Contact to devices interconnections between devices and

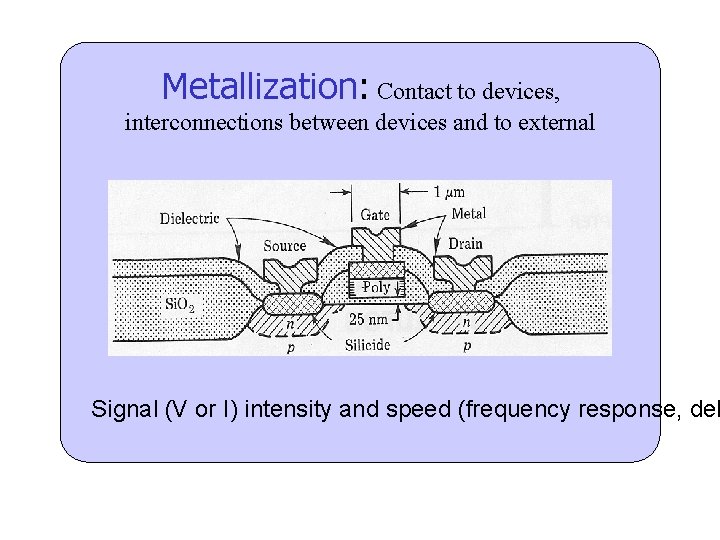

Metallization: Contact to devices, interconnections between devices and to external Signal (V or I) intensity and speed (frequency response, del

Issues in VLSI Metallization Ø Speed: switching speed, RC delay Ø Intensity: electromigration (I), electric breakdown (V) Ø Stability: contact interface, stable I-V characteristics Ø Voltage drop: IR drop reduces voltage on transistor Ø Area: connection wires have to be narrow

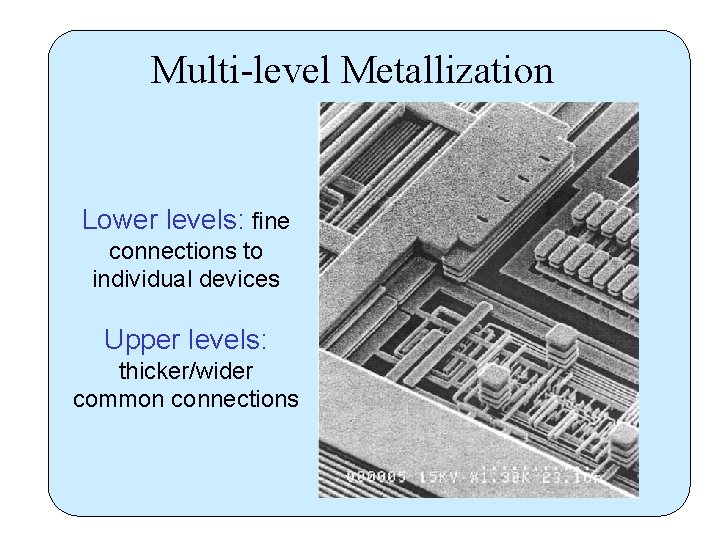

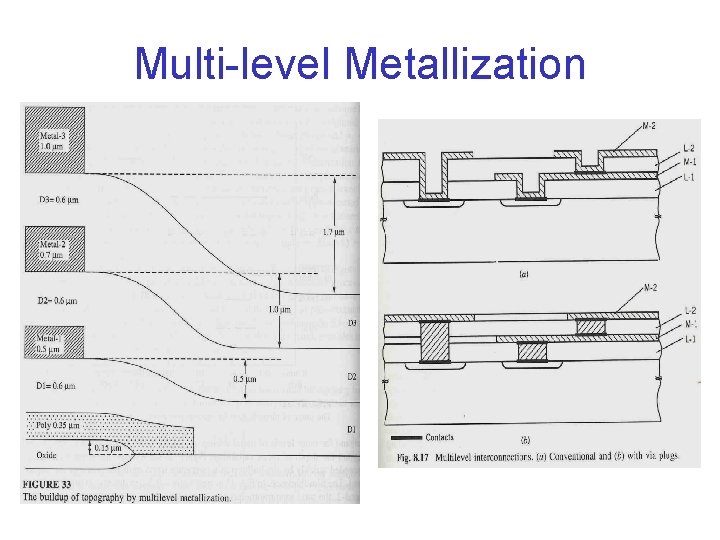

Multi-level Metallization Lower levels: fine connections to individual devices Upper levels: thicker/wider common connections

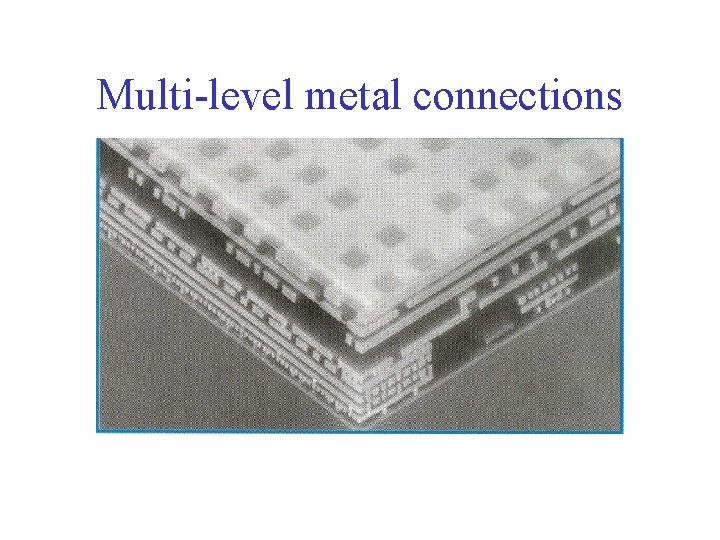

Multi-level metal connections

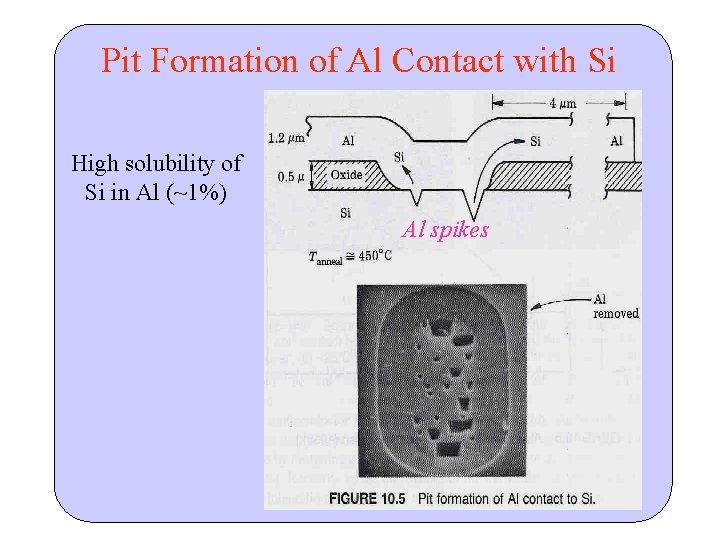

Pit Formation of Al Contact with Si High solubility of Si in Al (~1%) Al spikes

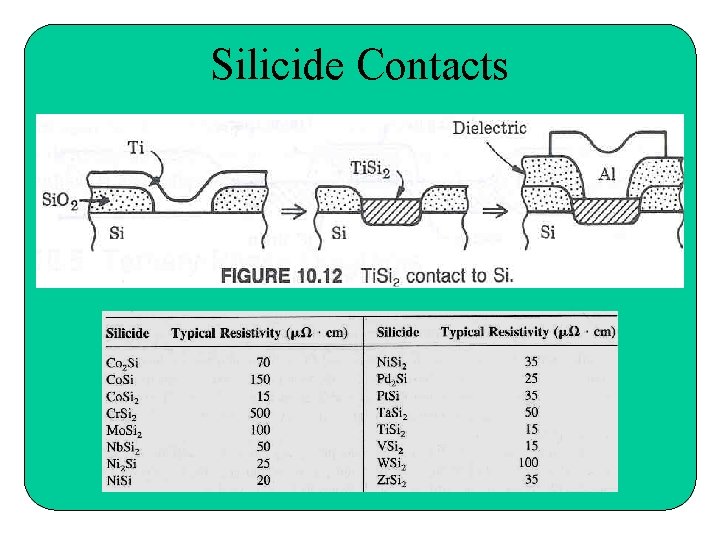

Silicide Contacts

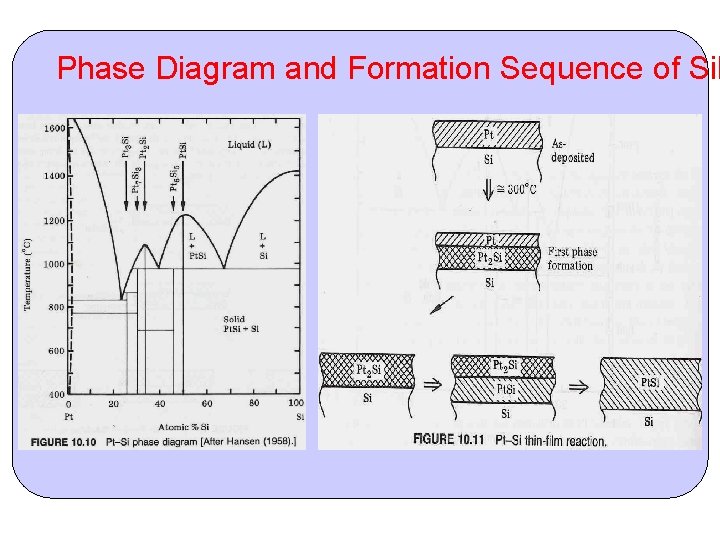

Phase Diagram and Formation Sequence of Sil

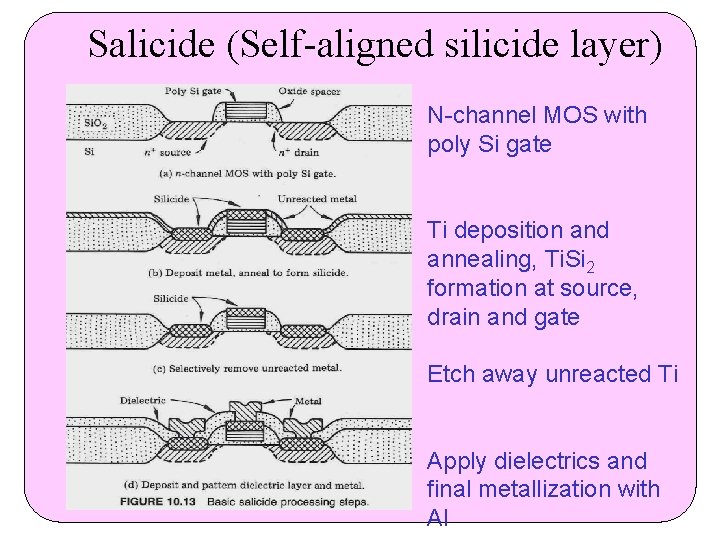

Salicide (Self-aligned silicide layer) N-channel MOS with poly Si gate Ti deposition and annealing, Ti. Si 2 formation at source, drain and gate Etch away unreacted Ti Apply dielectrics and final metallization with Al

Multi-level Metallization

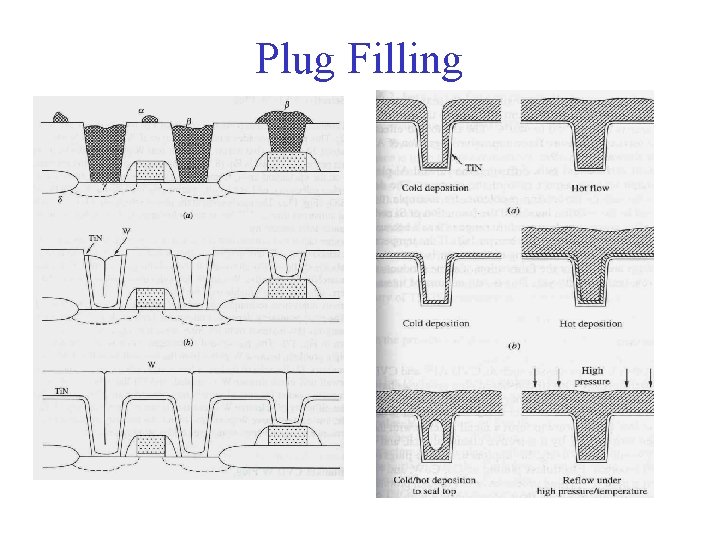

Plug Filling

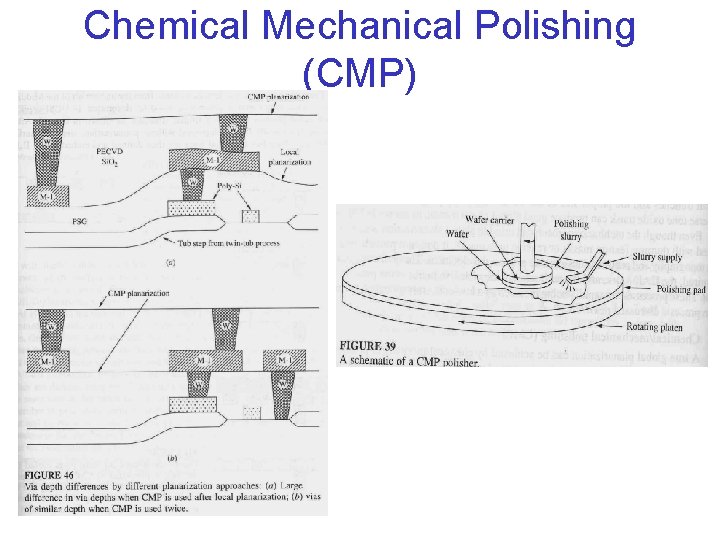

Chemical Mechanical Polishing (CMP)

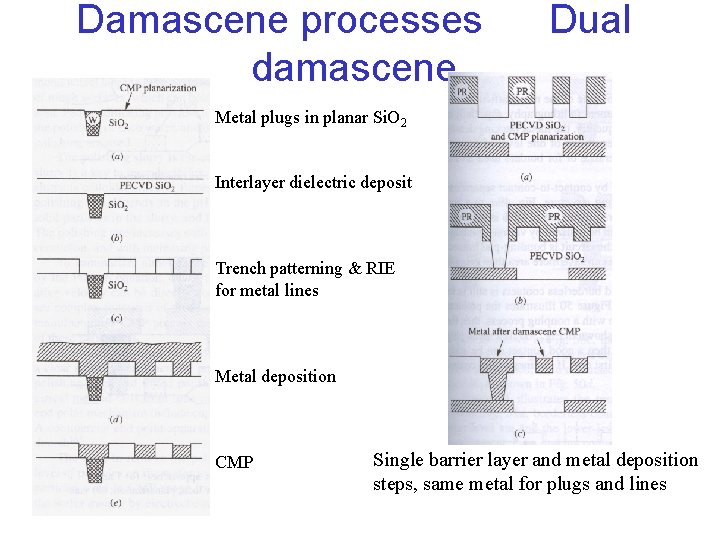

Damascene processes damascene Dual Metal plugs in planar Si. O 2 Interlayer dielectric deposit Trench patterning & RIE for metal lines Metal deposition CMP Single barrier layer and metal deposition steps, same metal for plugs and lines

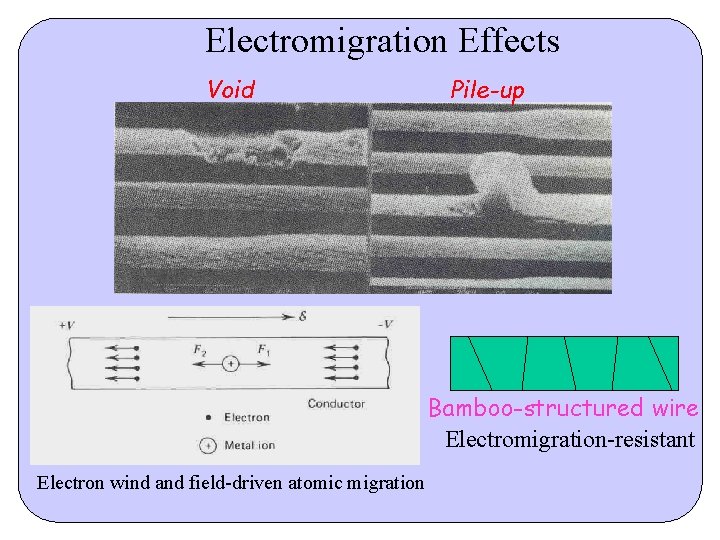

Electromigration Effects Void Pile-up Bamboo-structured wire Electromigration-resistant Electron wind and field-driven atomic migration

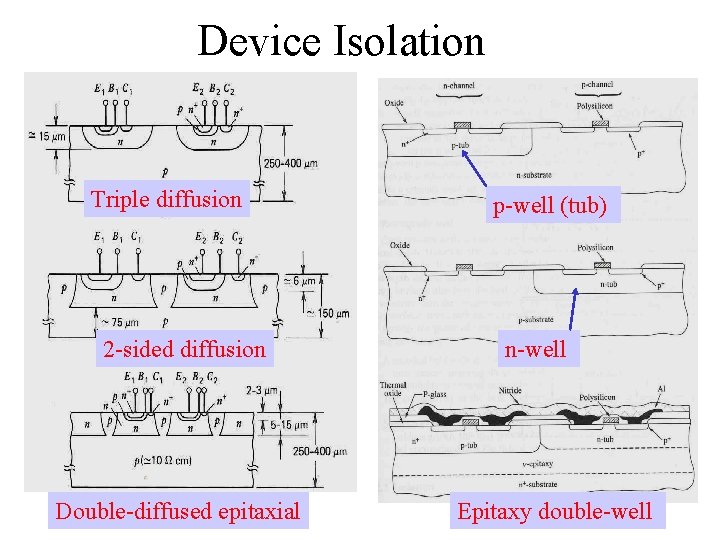

Device Isolation Triple diffusion 2 -sided diffusion Double-diffused epitaxial p-well (tub) n-well Epitaxy double-well

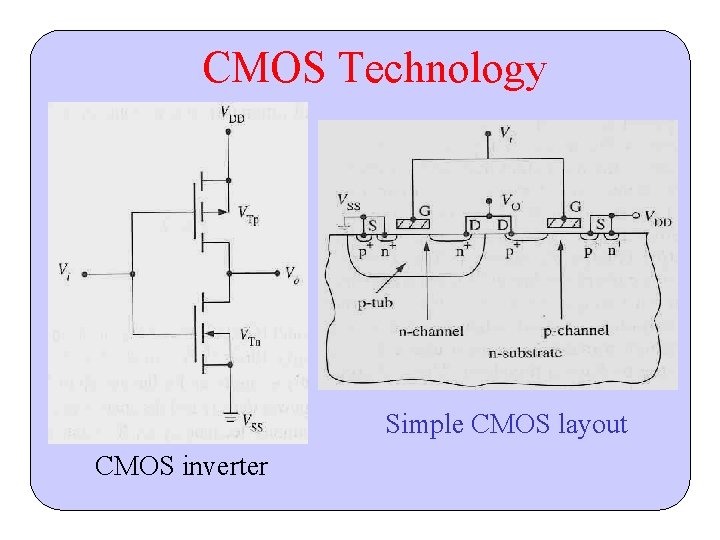

CMOS Technology Simple CMOS layout CMOS inverter

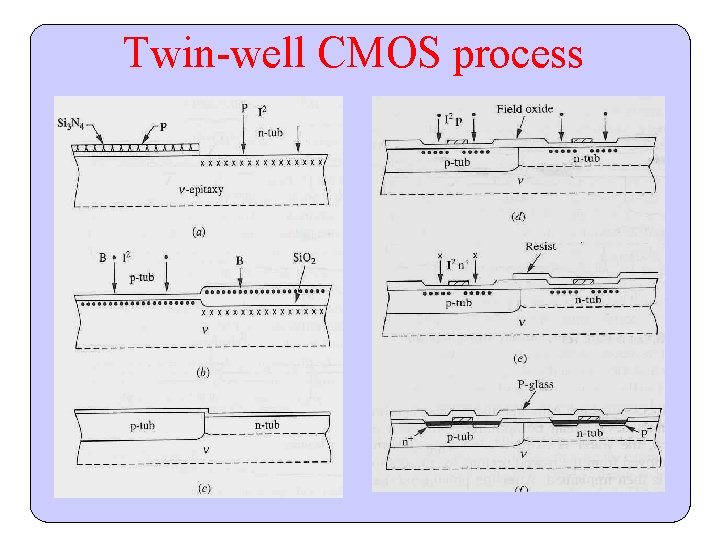

Twin-well CMOS process

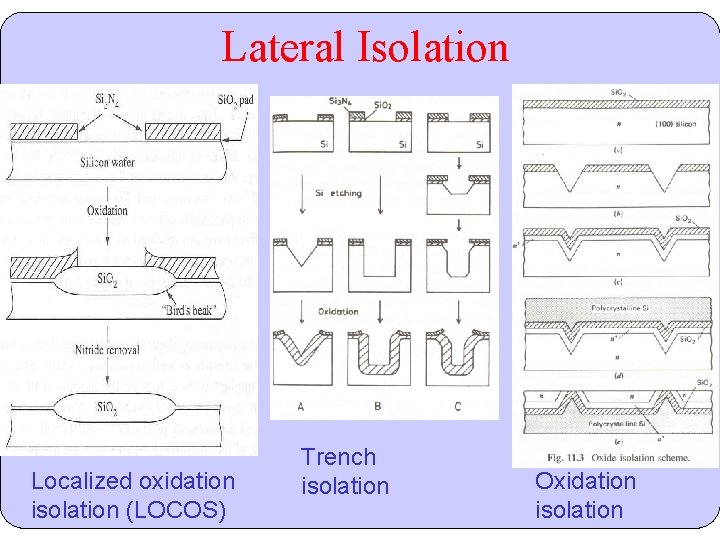

Lateral Isolation Localized oxidation isolation (LOCOS) Trench isolation Oxidation isolation

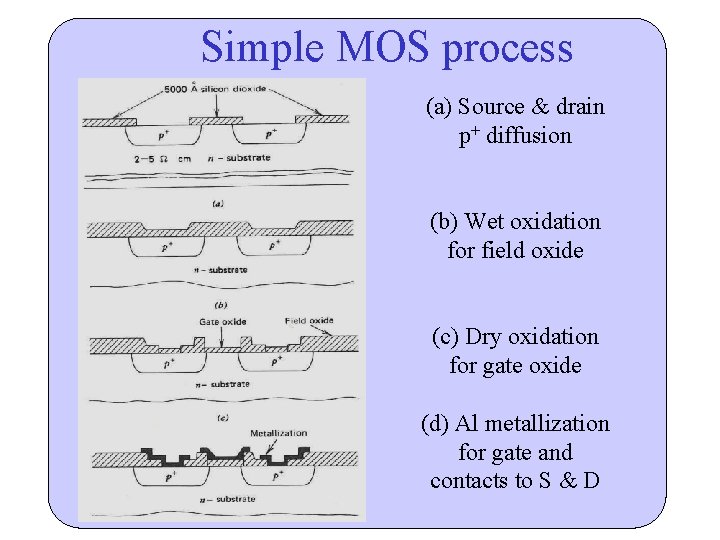

Simple MOS process (a) Source & drain p+ diffusion (b) Wet oxidation for field oxide (c) Dry oxidation for gate oxide (d) Al metallization for gate and contacts to S & D

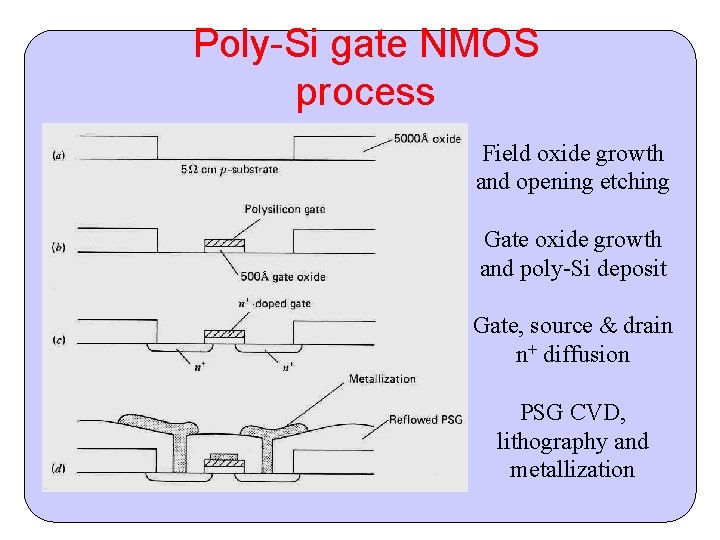

Poly-Si gate NMOS process Field oxide growth and opening etching Gate oxide growth and poly-Si deposit Gate, source & drain n+ diffusion PSG CVD, lithography and metallization

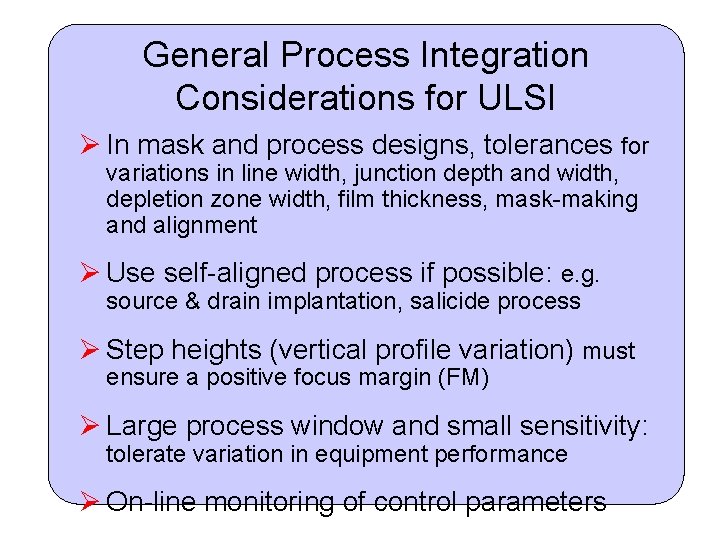

General Process Integration Considerations for ULSI Ø In mask and process designs, tolerances for variations in line width, junction depth and width, depletion zone width, film thickness, mask-making and alignment Ø Use self-aligned process if possible: e. g. source & drain implantation, salicide process Ø Step heights (vertical profile variation) must ensure a positive focus margin (FM) Ø Large process window and small sensitivity: tolerate variation in equipment performance Ø On-line monitoring of control parameters

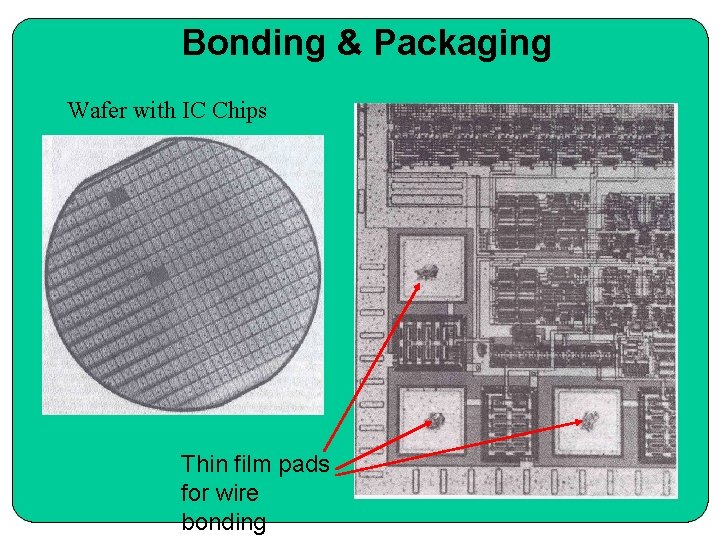

Bonding & Packaging Wafer with IC Chips Thin film pads for wire bonding

Plastic-encapsulated packag Back side of IC chip bond to a metallized ceramic substrate Au wires connecting the IC and pins

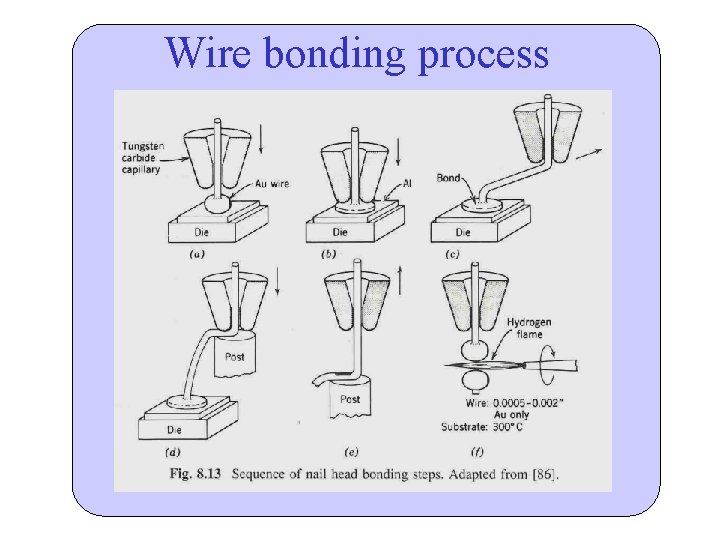

Wire bonding process

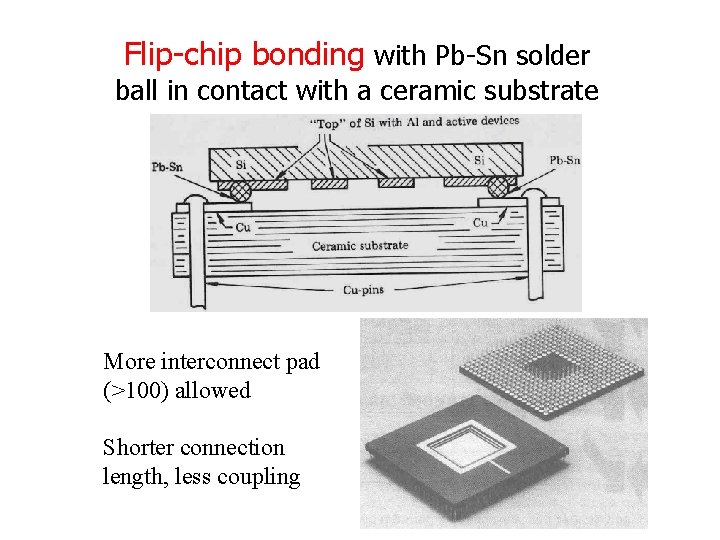

Flip-chip bonding with Pb-Sn solder ball in contact with a ceramic substrate More interconnect pad (>100) allowed Shorter connection length, less coupling

- Slides: 24