Memria CENTRO DE INFORMTICA UFPE GRECO Sistema Bsico

Memória CENTRO DE INFORMÁTICA - UFPE GRECO

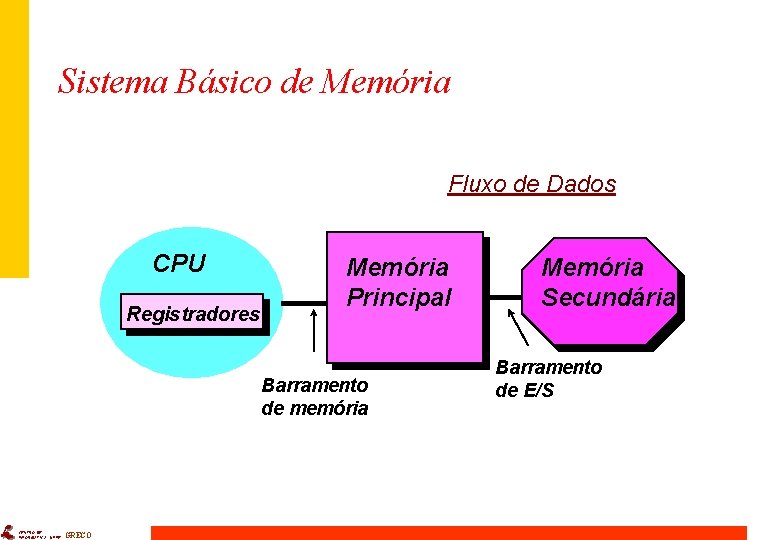

Sistema Básico de Memória Fluxo de Dados CPU Registradores Memória Principal Barramento de memória CENTRO DE INFORMÁTICA - UFPE GRECO Memória Secundária Barramento de E/S

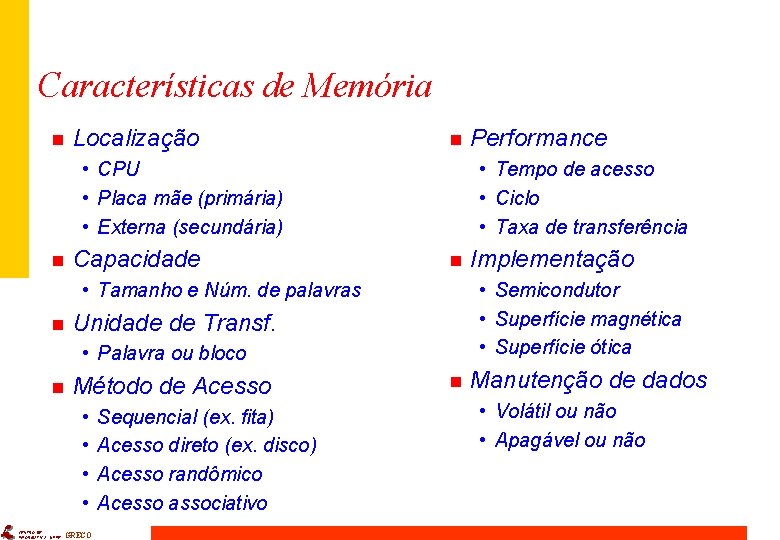

Características de Memória n Localização n • CPU • Placa mãe (primária) • Externa (secundária) n Capacidade • Tempo de acesso • Ciclo • Taxa de transferência n • Tamanho e Núm. de palavras n Unidade de Transf. Método de Acesso • • CENTRO DE INFORMÁTICA - UFPE GRECO Sequencial (ex. fita) Acesso direto (ex. disco) Acesso randômico Acesso associativo Implementação • Semicondutor • Superfície magnética • Superfície ótica • Palavra ou bloco n Performance n Manutenção de dados • Volátil ou não • Apagável ou não

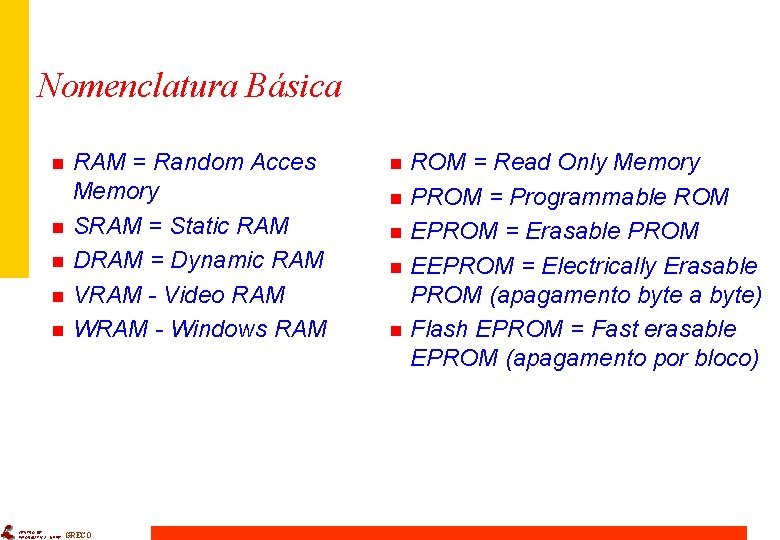

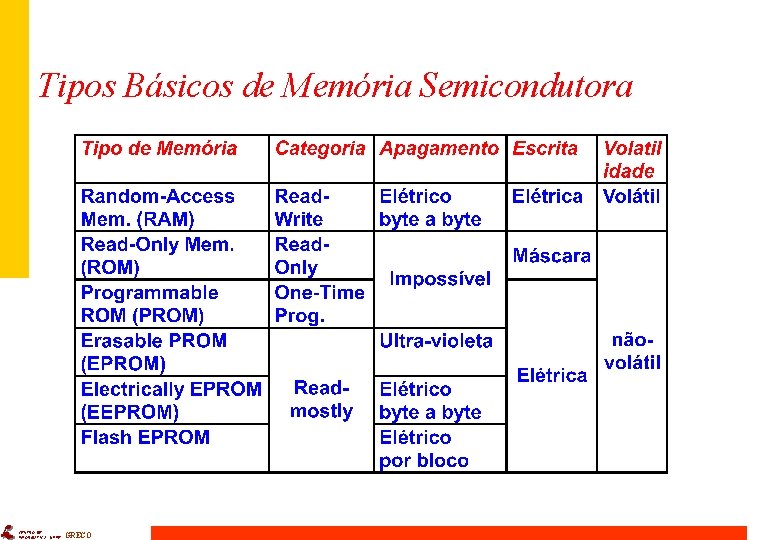

Nomenclatura Básica n n n CENTRO DE INFORMÁTICA - UFPE RAM = Random Acces Memory SRAM = Static RAM DRAM = Dynamic RAM VRAM - Video RAM WRAM - Windows RAM GRECO n n n ROM = Read Only Memory PROM = Programmable ROM EPROM = Erasable PROM EEPROM = Electrically Erasable PROM (apagamento byte a byte) Flash EPROM = Fast erasable EPROM (apagamento por bloco)

Tipos Básicos de Memória Semicondutora CENTRO DE INFORMÁTICA - UFPE GRECO

RAM Dinâmica vs. Estática n DRAM (Dynamic Random Acess Memory) • Grande capacidade de integração (baixo custo por bit) • Perda de informação após algum tempo: Necessidade de refreshing n SRAM (Static Random Acess Memory) • Pequeno tempo de acesso • Não existe necessidade de refreshing • Alto custo por bit (baixa integração) CENTRO DE INFORMÁTICA - UFPE GRECO

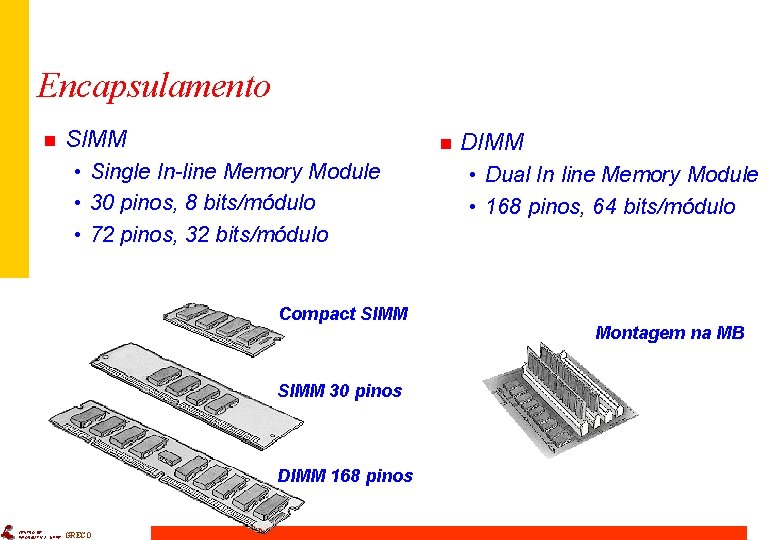

Encapsulamento n SIMM n • Single In-line Memory Module • 30 pinos, 8 bits/módulo • 72 pinos, 32 bits/módulo Compact SIMM 30 pinos DIMM 168 pinos CENTRO DE INFORMÁTICA - UFPE GRECO DIMM • Dual In line Memory Module • 168 pinos, 64 bits/módulo Montagem na MB

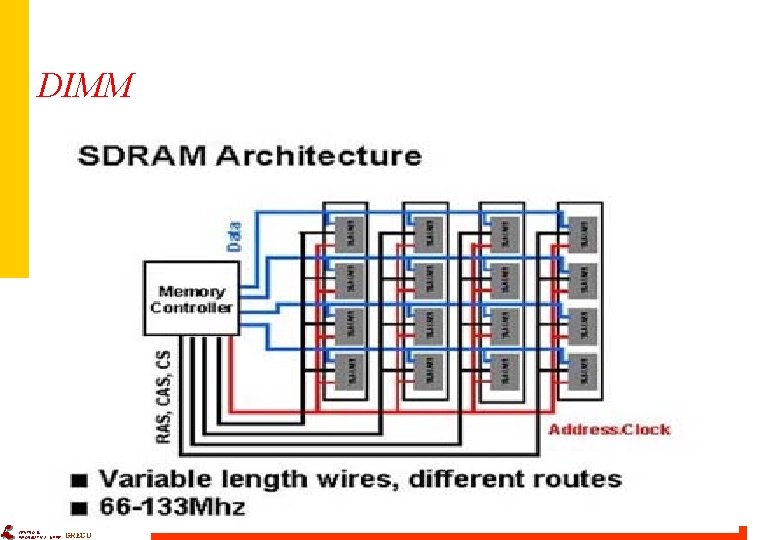

DIMM CENTRO DE INFORMÁTICA - UFPE GRECO

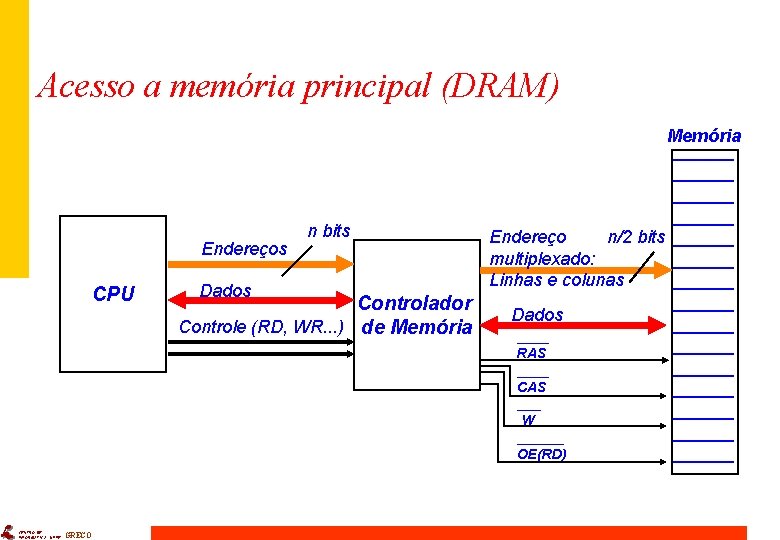

Acesso a memória principal (DRAM) CPU CENTRO DE INFORMÁTICA - UFPE GRECO Memória ______ n bits Endereço n/2 bits ______ Endereços multiplexado: ______ Linhas e colunas ______ Dados ______ Controlador Dados ______ Controle (RD, WR. . . ) de Memória ______ RAS ______ CAS ______ W ______ OE(RD) ______

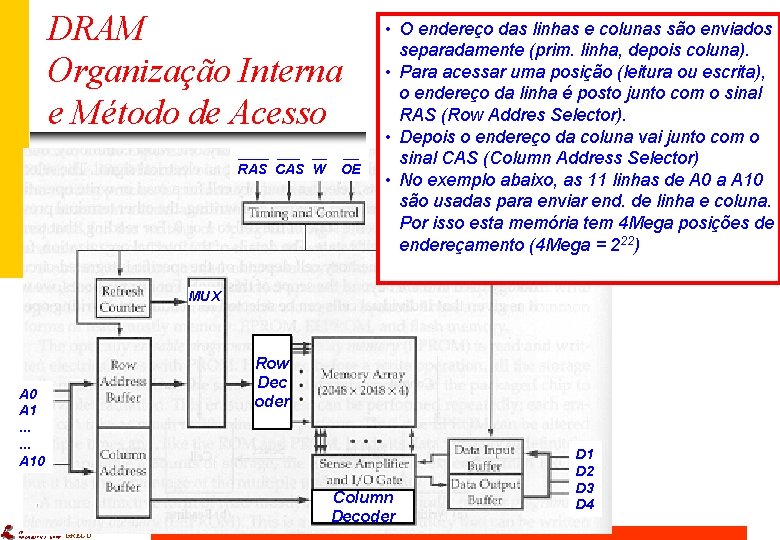

DRAM Organização Interna e Método de Acesso ____ __ __ RAS CAS W OE • O endereço das linhas e colunas são enviados separadamente (prim. linha, depois coluna). • Para acessar uma posição (leitura ou escrita), o endereço da linha é posto junto com o sinal RAS (Row Addres Selector). • Depois o endereço da coluna vai junto com o sinal CAS (Column Address Selector) • No exemplo abaixo, as 11 linhas de A 0 a A 10 são usadas para enviar end. de linha e coluna. Por isso esta memória tem 4 Mega posições de endereçamento (4 Mega = 222) MUX Row Dec oder A 0 A 1. . . A 10 Column Decoder CENTRO DE INFORMÁTICA - UFPE GRECO D 1 D 2 D 3 D 4

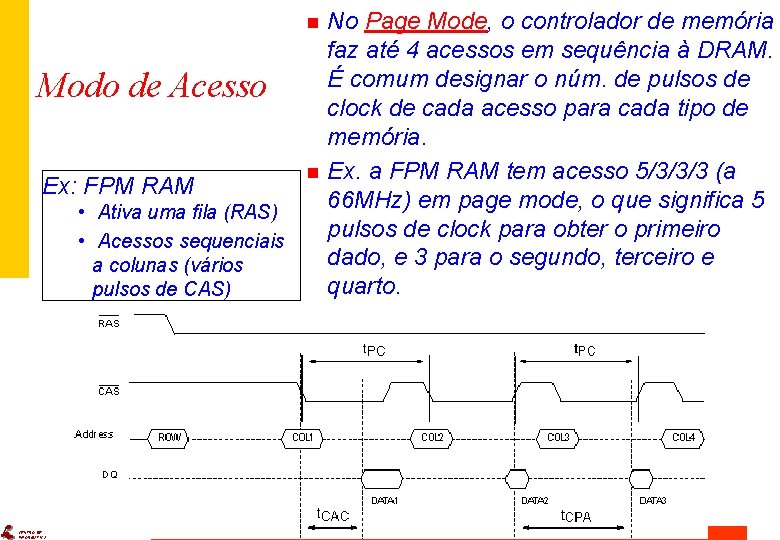

n Modo de Acesso Ex: FPM RAM • Ativa uma fila (RAS) • Acessos sequenciais a colunas (vários pulsos de CAS) CENTRO DE INFORMÁTICA - UFPE GRECO n No Page Mode, o controlador de memória faz até 4 acessos em sequência à DRAM. É comum designar o núm. de pulsos de clock de cada acesso para cada tipo de memória. Ex. a FPM RAM tem acesso 5/3/3/3 (a 66 MHz) em page mode, o que significa 5 pulsos de clock para obter o primeiro dado, e 3 para o segundo, terceiro e quarto.

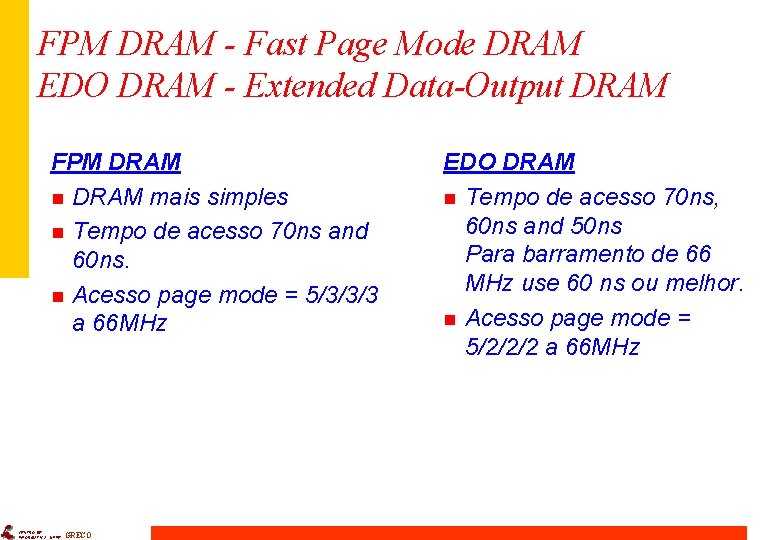

FPM DRAM - Fast Page Mode DRAM EDO DRAM - Extended Data-Output DRAM FPM DRAM n DRAM mais simples n Tempo de acesso 70 ns and 60 ns. n Acesso page mode = 5/3/3/3 a 66 MHz CENTRO DE INFORMÁTICA - UFPE GRECO EDO DRAM n Tempo de acesso 70 ns, 60 ns and 50 ns Para barramento de 66 MHz use 60 ns ou melhor. n Acesso page mode = 5/2/2/2 a 66 MHz

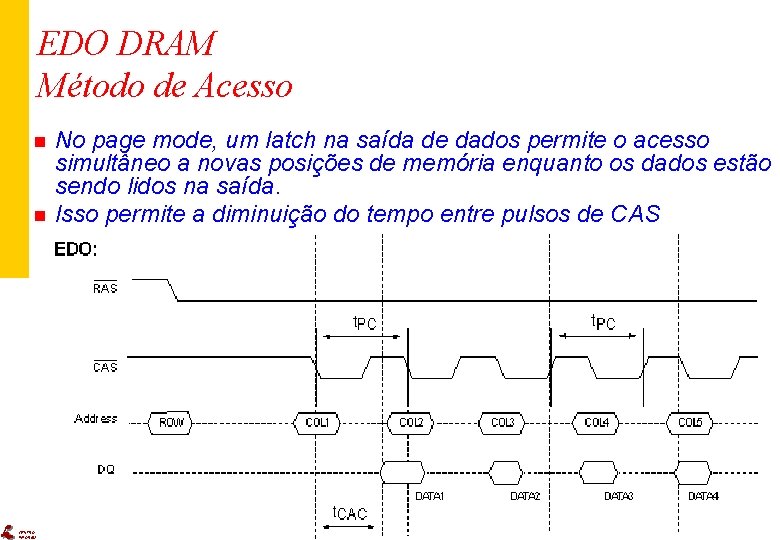

EDO DRAM Método de Acesso n n No page mode, um latch na saída de dados permite o acesso simultâneo a novas posições de memória enquanto os dados estão sendo lidos na saída. Isso permite a diminuição do tempo entre pulsos de CAS CENTRO DE INFORMÁTICA - UFPE GRECO

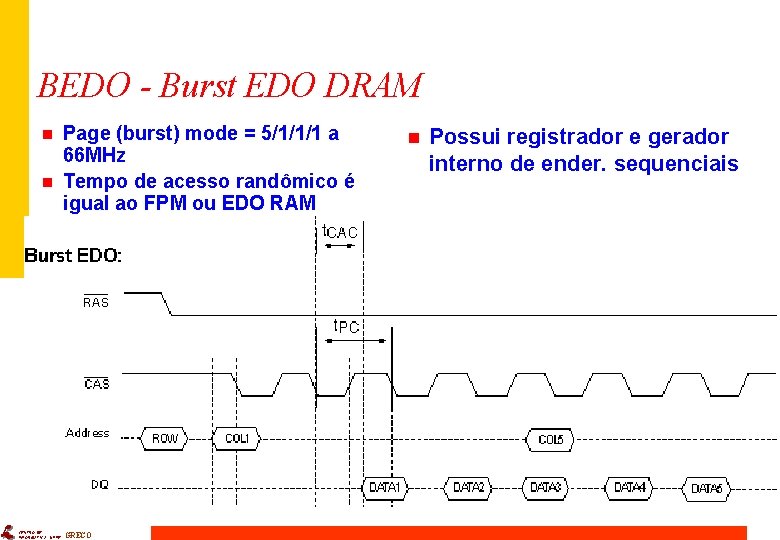

BEDO - Burst EDO DRAM n n CENTRO DE INFORMÁTICA - UFPE Page (burst) mode = 5/1/1/1 a 66 MHz Tempo de acesso randômico é igual ao FPM ou EDO RAM GRECO n Possui registrador e gerador interno de ender. sequenciais

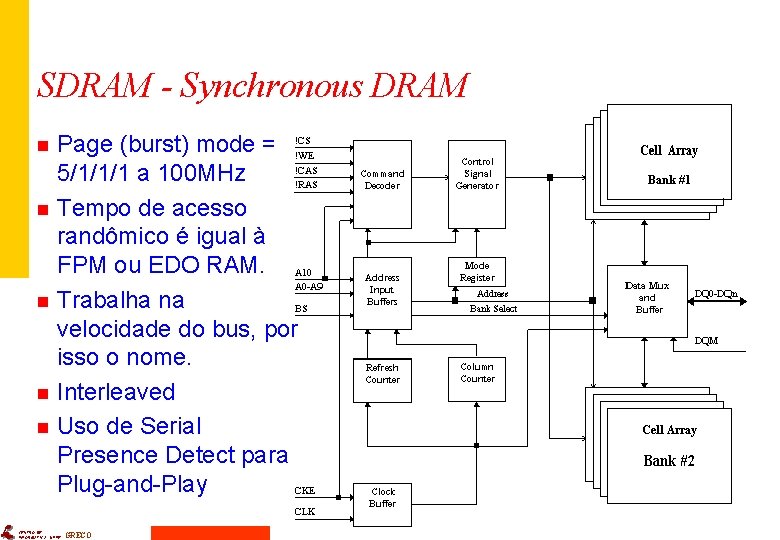

SDRAM - Synchronous DRAM n n n Page (burst) mode = 5/1/1/1 a 100 MHz Tempo de acesso randômico é igual à FPM ou EDO RAM. Trabalha na velocidade do bus, por isso o nome. Interleaved Uso de Serial Presence Detect para Plug-and-Play CENTRO DE INFORMÁTICA - UFPE GRECO

DDR SDRAM – Double Data Rate SDRAM n n Transfere dados na subida e descida do clock (compensa o uso de barramentos lentos) Uso de Serial Presence Detect para Plug-and-Play CENTRO DE INFORMÁTICA - UFPE GRECO

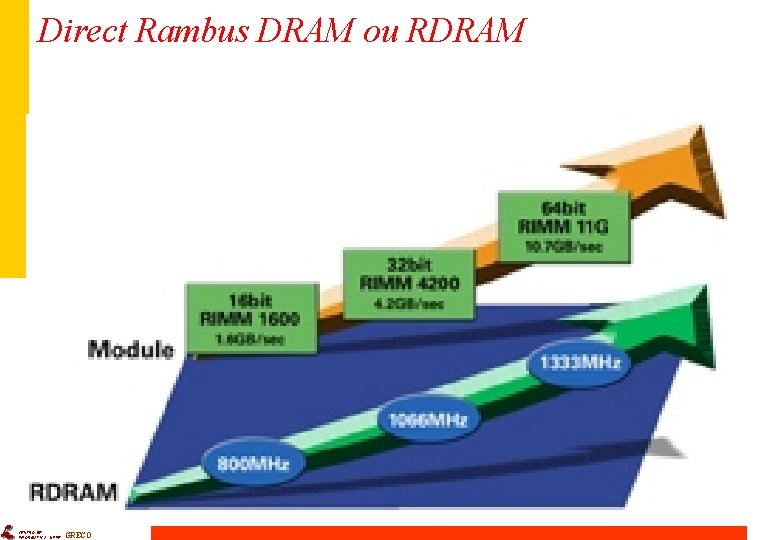

Direct Rambus DRAM ou RDRAM n n Padrão proprietário da Rambus Inc. Usa o Direct Rambus Channel – 400 MHz, 16 bits (o barramento estreito permite estas taxas altas) Transferência de dados na subida e descida do clock 1, 6 GByte/s Uso de Serial Presence Detect para Plug-and-Play CENTRO DE INFORMÁTICA - UFPE GRECO

Direct Rambus DRAM ou RDRAM CENTRO DE INFORMÁTICA - UFPE GRECO

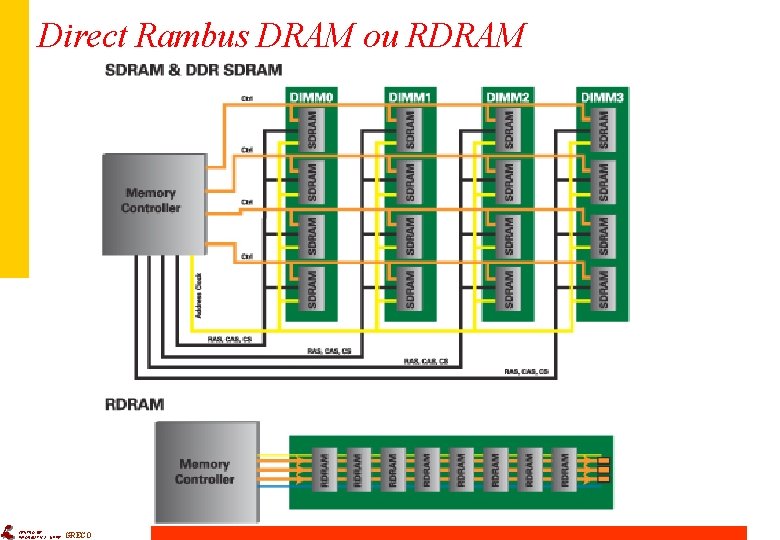

Direct Rambus DRAM ou RDRAM CENTRO DE INFORMÁTICA - UFPE GRECO

Synchronous Link DRAM - SLDRAM n n n Desenvolvido pelo SLDRAM Consortium (20 empresas) Uso de tecnologia mais comum: bus de 64 -bit a 200 MHz Transferência de dados na subida e descida do clock 3, 2 GByte/s CENTRO DE INFORMÁTICA - UFPE GRECO

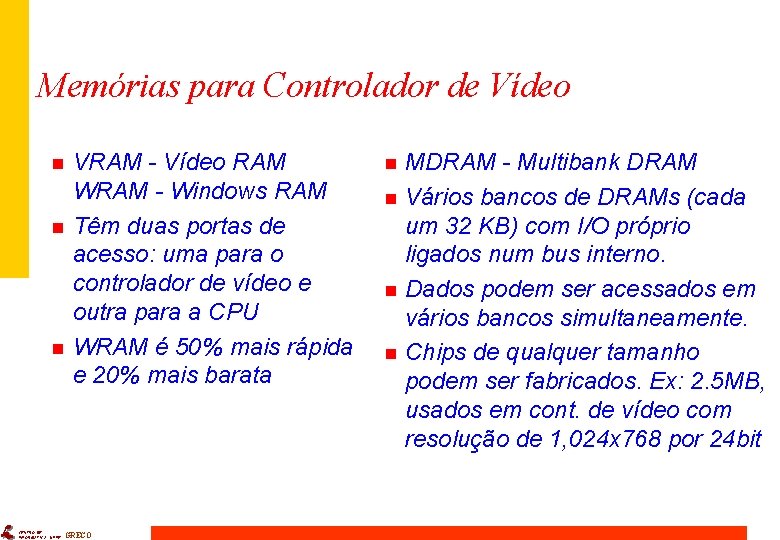

Memórias para Controlador de Vídeo n n n CENTRO DE INFORMÁTICA - UFPE VRAM - Vídeo RAM WRAM - Windows RAM Têm duas portas de acesso: uma para o controlador de vídeo e outra para a CPU WRAM é 50% mais rápida e 20% mais barata GRECO n n MDRAM - Multibank DRAM Vários bancos de DRAMs (cada um 32 KB) com I/O próprio ligados num bus interno. Dados podem ser acessados em vários bancos simultaneamente. Chips de qualquer tamanho podem ser fabricados. Ex: 2. 5 MB, usados em cont. de vídeo com resolução de 1, 024 x 768 por 24 bit

Memória Cache CENTRO DE INFORMÁTICA - UFPE GRECO

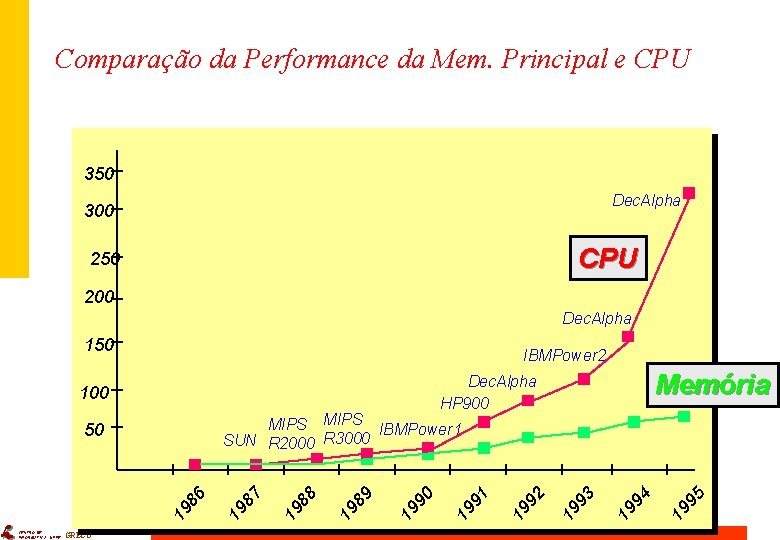

Comparação da Performance da Mem. Principal e CPU 350 Dec. Alpha 300 CPU 250 200 Dec. Alpha 150 IBMPower 2 95 19 94 19 93 19 92 19 91 19 90 19 89 19 88 19 19 86 19 GRECO 87 MIPS IBMPower 1 SUN R 2000 R 3000 50 CENTRO DE INFORMÁTICA - UFPE Memória Dec. Alpha HP 900 100

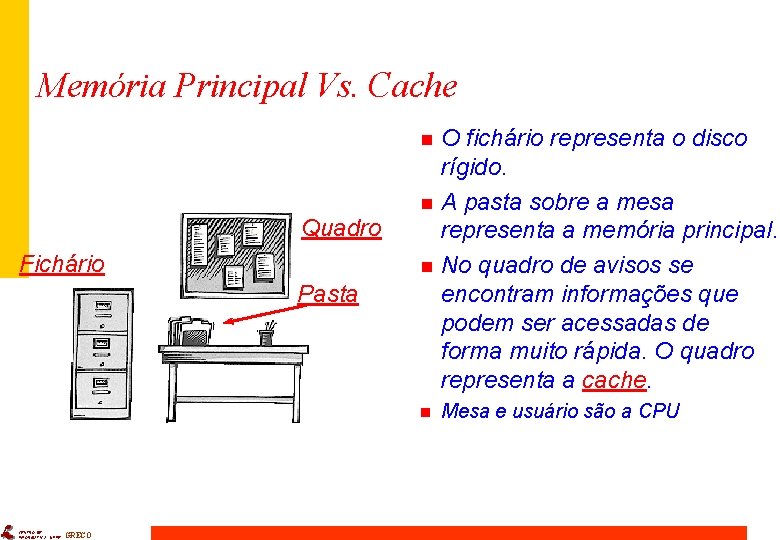

Memória Principal Vs. Cache n O fichário representa o disco rígido. A pasta sobre a mesa representa a memória principal. No quadro de avisos se encontram informações que podem ser acessadas de forma muito rápida. O quadro representa a cache. n Mesa e usuário são a CPU n n Quadro Fichário Pasta CENTRO DE INFORMÁTICA - UFPE GRECO

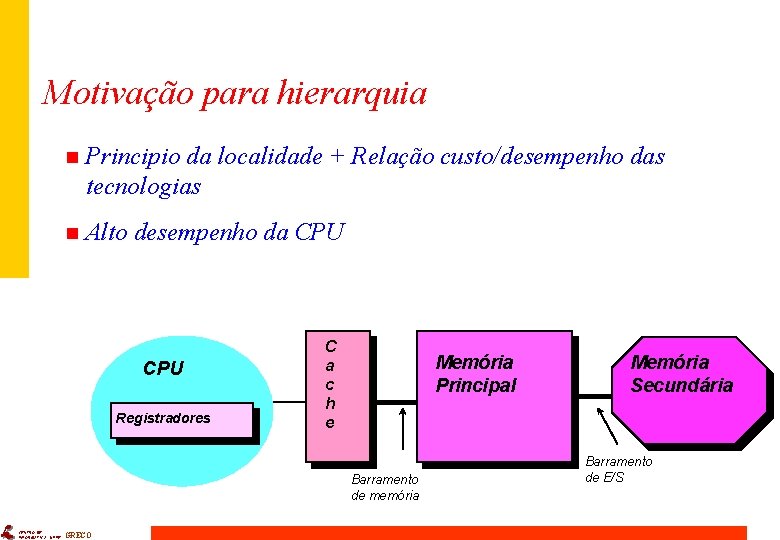

Motivação para hierarquia n Principio da localidade + Relação custo/desempenho das tecnologias n Alto desempenho da CPU Registradores C a c h e Memória Principal Barramento de memória CENTRO DE INFORMÁTICA - UFPE GRECO Memória Secundária Barramento de E/S

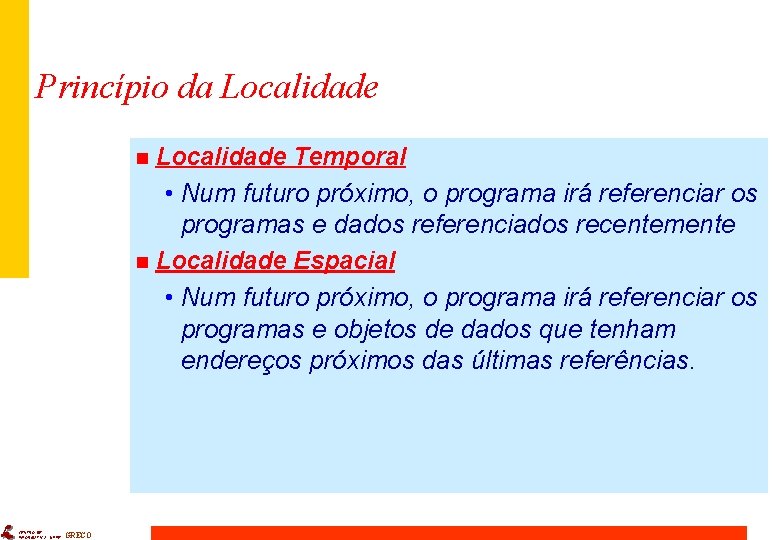

Princípio da Localidade Temporal • Num futuro próximo, o programa irá referenciar os programas e dados referenciados recentemente n Localidade Espacial • Num futuro próximo, o programa irá referenciar os programas e objetos de dados que tenham endereços próximos das últimas referências. n CENTRO DE INFORMÁTICA - UFPE GRECO

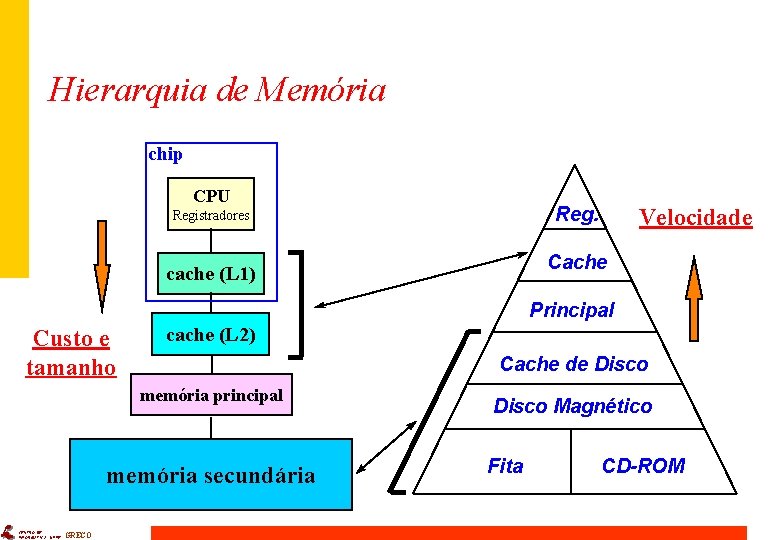

Hierarquia de Memória chip CPU Registradores Velocidade Cache cache (L 1) Principal Custo e tamanho cache (L 2) Cache de Disco memória principal memória secundária CENTRO DE INFORMÁTICA - UFPE GRECO Disco Magnético Fita CD-ROM

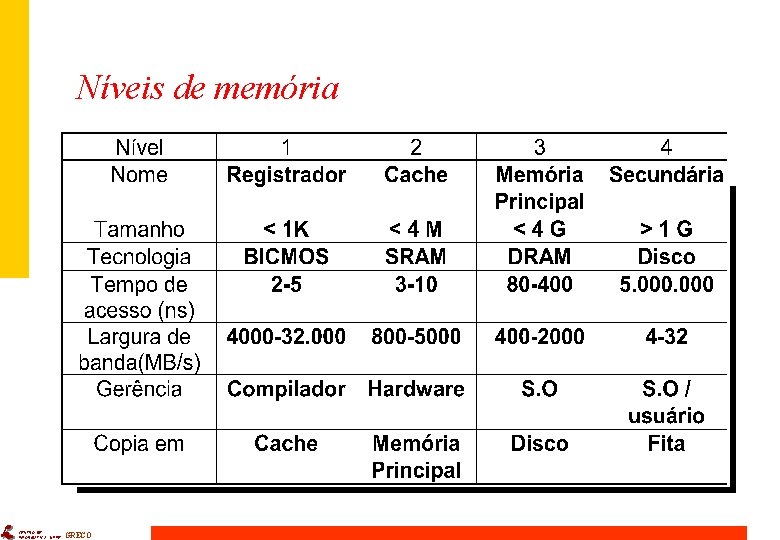

Níveis de memória CENTRO DE INFORMÁTICA - UFPE GRECO

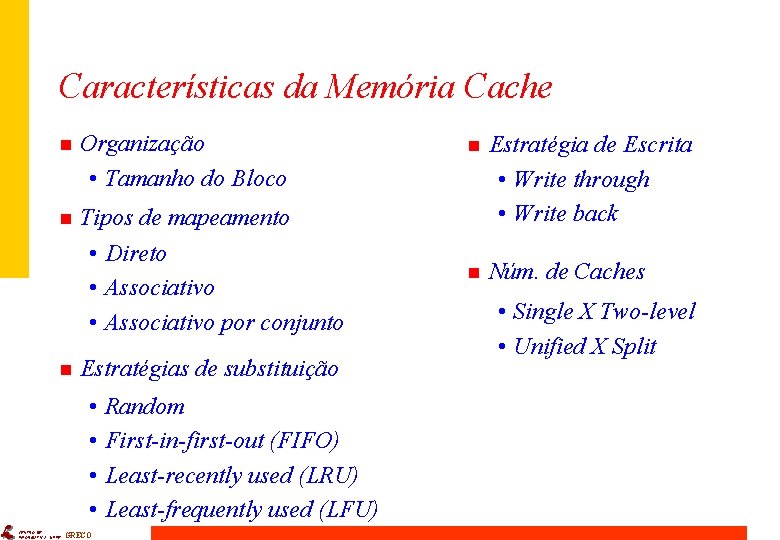

Características da Memória Cache n Organização • Tamanho do Bloco n Tipos de mapeamento • Direto • Associativo por conjunto n Estratégias de substituição • Random • First-in-first-out (FIFO) • Least-recently used (LRU) • Least-frequently used (LFU) CENTRO DE INFORMÁTICA - UFPE GRECO n Estratégia de Escrita • Write through • Write back n Núm. de Caches • Single X Two-level • Unified X Split

Avanços em implementação de caches n Sincronizada ao clock do sistema • Os sinais são sincronizados ao clock. • Simplifica o projeto da memória n Burst • Incorpora controle interno que permite acesso rápido a posições subsequentes (ex. reg. e gerador de endereços) n Pipelining • Usa registradores na entrada e/ou saída o que permite fornecer dados e acessar novos endereços em paralelo. CENTRO DE INFORMÁTICA - UFPE GRECO

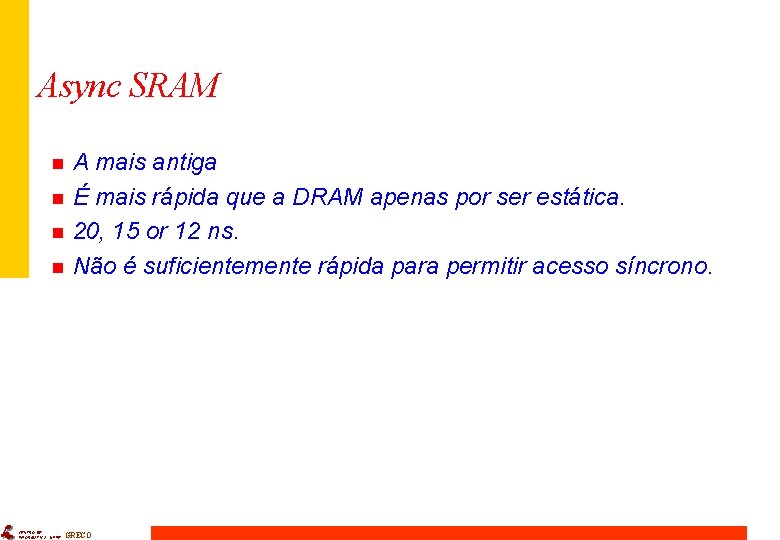

Async SRAM n n CENTRO DE INFORMÁTICA - UFPE A mais antiga É mais rápida que a DRAM apenas por ser estática. 20, 15 or 12 ns. Não é suficientemente rápida para permitir acesso síncrono. GRECO

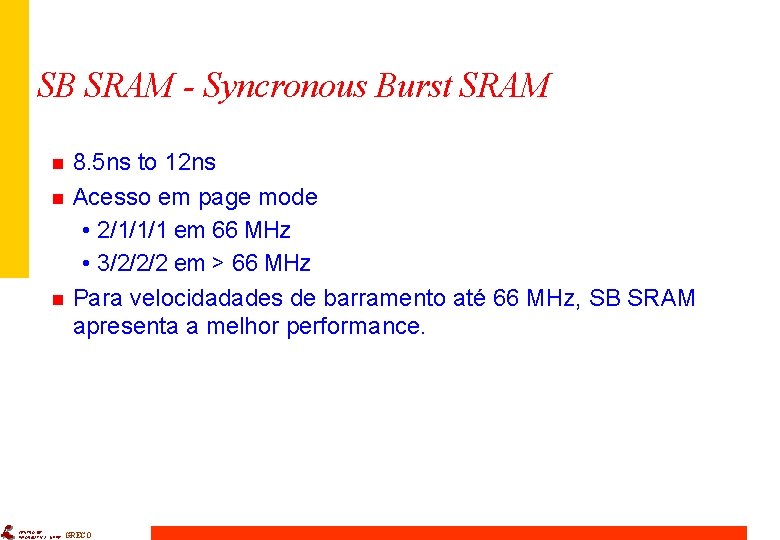

SB SRAM - Syncronous Burst SRAM n n n CENTRO DE INFORMÁTICA - UFPE 8. 5 ns to 12 ns Acesso em page mode • 2/1/1/1 em 66 MHz • 3/2/2/2 em > 66 MHz Para velocidadades de barramento até 66 MHz, SB SRAM apresenta a melhor performance. GRECO

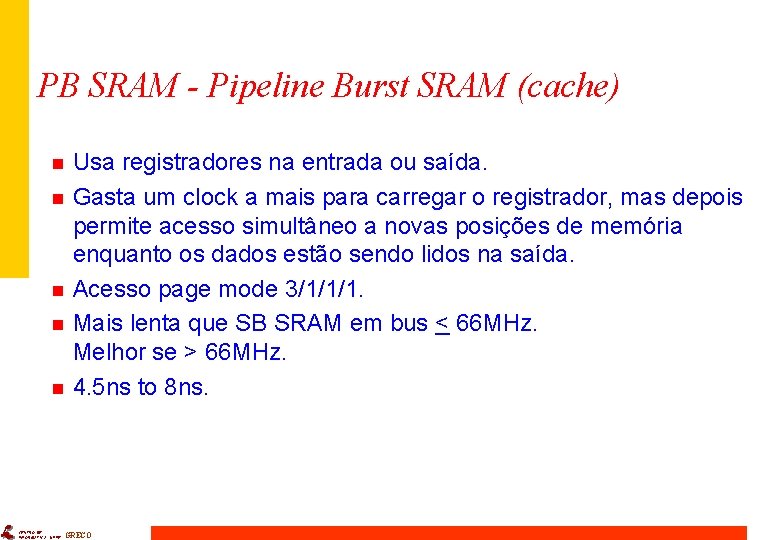

PB SRAM - Pipeline Burst SRAM (cache) n n n CENTRO DE INFORMÁTICA - UFPE Usa registradores na entrada ou saída. Gasta um clock a mais para carregar o registrador, mas depois permite acesso simultâneo a novas posições de memória enquanto os dados estão sendo lidos na saída. Acesso page mode 3/1/1/1. Mais lenta que SB SRAM em bus < 66 MHz. Melhor se > 66 MHz. 4. 5 ns to 8 ns. GRECO

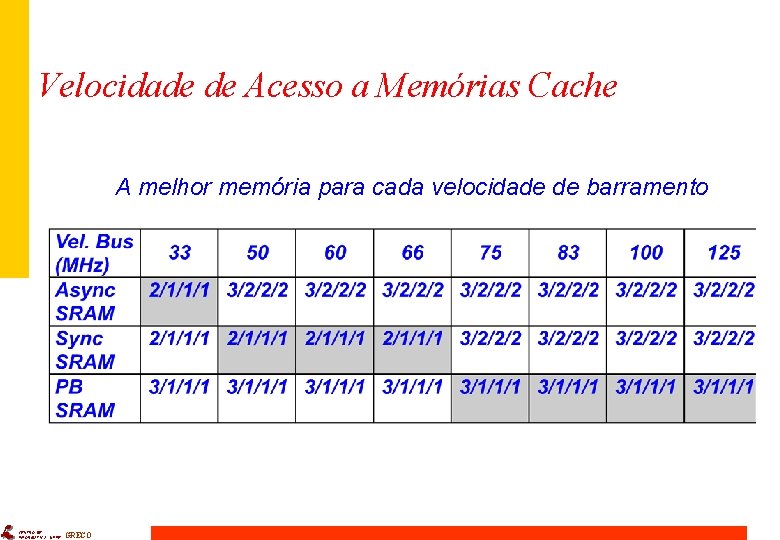

Velocidade de Acesso a Memórias Cache A melhor memória para cada velocidade de barramento CENTRO DE INFORMÁTICA - UFPE GRECO

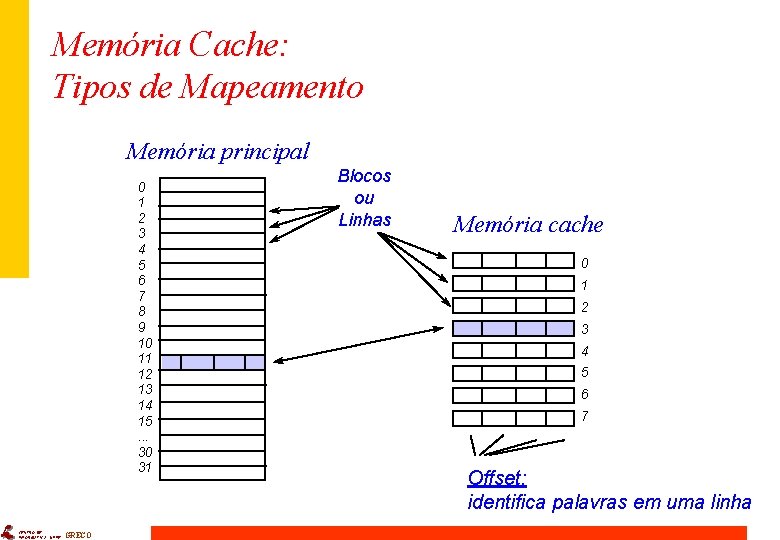

Memória Cache: Tipos de Mapeamento Memória principal 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15. . . 30 31 CENTRO DE INFORMÁTICA - UFPE GRECO Blocos ou Linhas Memória cache 0 1 2 3 4 5 6 7 Offset: identifica palavras em uma linha

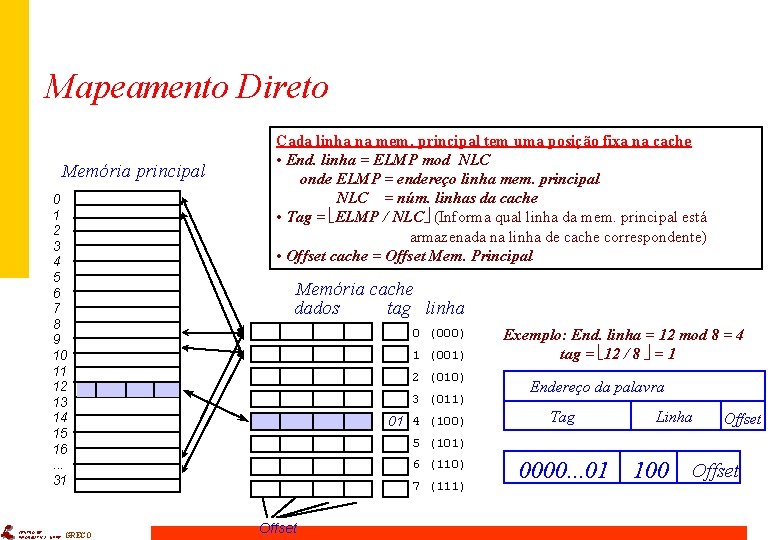

Mapeamento Direto Memória principal 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16. . . 31 CENTRO DE INFORMÁTICA - UFPE GRECO Cada linha na mem. principal tem uma posição fixa na cache • End. linha = ELMP mod NLC onde ELMP = endereço linha mem. principal NLC = núm. linhas da cache • Tag = ëELMP / NLCû (Informa qual linha da mem. principal está armazenada na linha de cache correspondente) • Offset cache = Offset Mem. Principal Memória cache dados tag linha 0 (000) 1 (001) 2 (010) 3 (011) 01 4 (100) Exemplo: End. linha = 12 mod 8 = 4 tag = ë 12 / 8 û = 1 Endereço da palavra Tag Linha Offset 5 (101) 6 (110) 7 (111) Offset 0000. . . 01 100 Offset

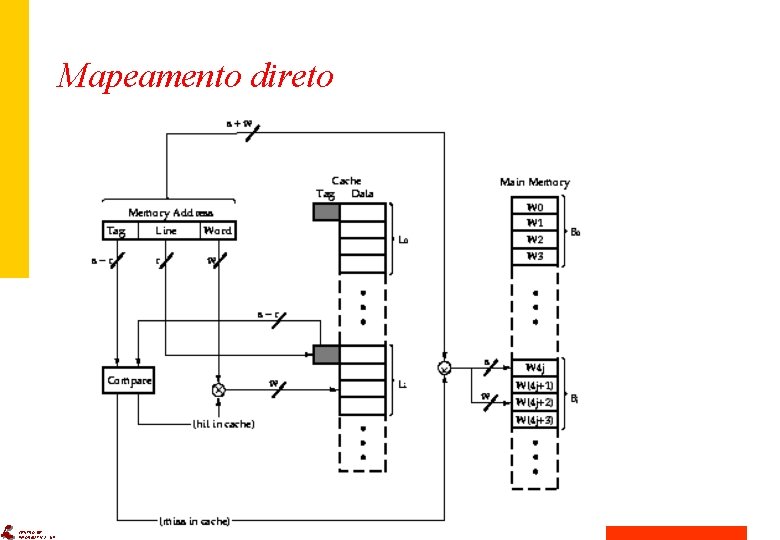

Mapeamento direto CENTRO DE INFORMÁTICA - UFPE GRECO

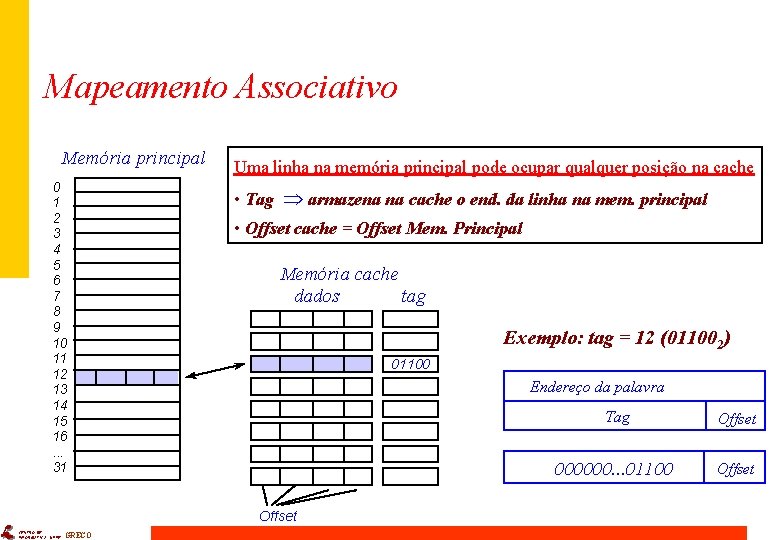

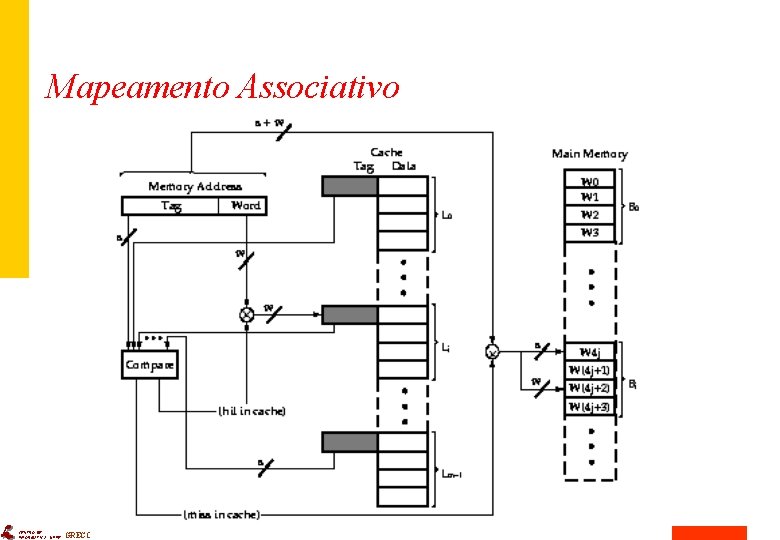

Mapeamento Associativo Memória principal 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16. . . 31 Uma linha na memória principal pode ocupar qualquer posição na cache • Tag Þ armazena na cache o end. da linha na mem. principal • Offset cache = Offset Mem. Principal Memória cache dados tag Exemplo: tag = 12 (011002) 01100 Endereço da palavra Offset CENTRO DE INFORMÁTICA - UFPE GRECO Tag Offset 000000. . . 01100 Offset

Mapeamento Associativo CENTRO DE INFORMÁTICA - UFPE GRECO

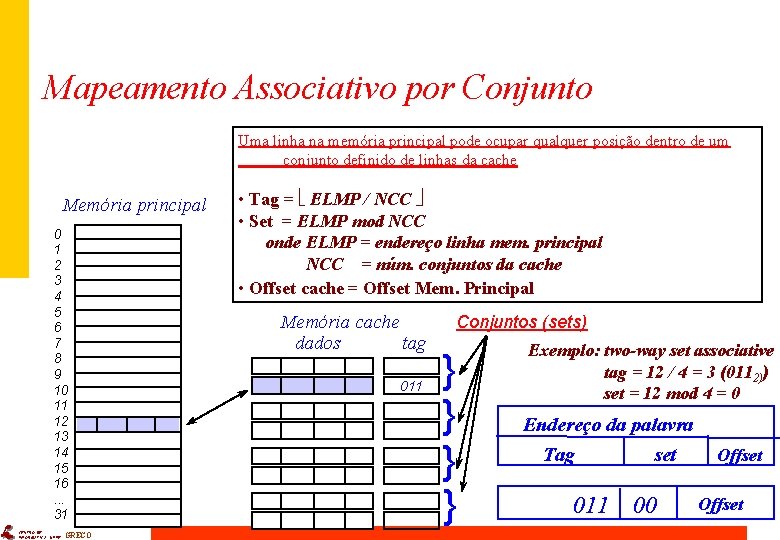

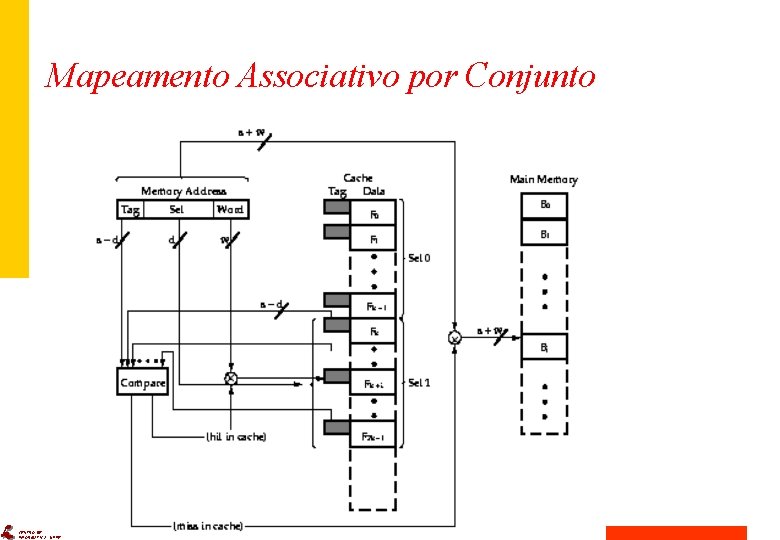

Mapeamento Associativo por Conjunto Uma linha na memória principal pode ocupar qualquer posição dentro de um conjunto definido de linhas da cache 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16. . . 31 CENTRO DE INFORMÁTICA - UFPE GRECO • Tag = ë ELMP / NCC û • Set = ELMP mod NCC onde ELMP = endereço linha mem. principal NCC = núm. conjuntos da cache • Offset cache = Offset Mem. Principal Memória cache dados tag 011 Conjuntos (sets) { { Memória principal Exemplo: two-way set associative tag = 12 / 4 = 3 (0112)) set = 12 mod 4 = 0 Endereço da palavra Tag set 011 00 Offset

Mapeamento Associativo por Conjunto CENTRO DE INFORMÁTICA - UFPE GRECO

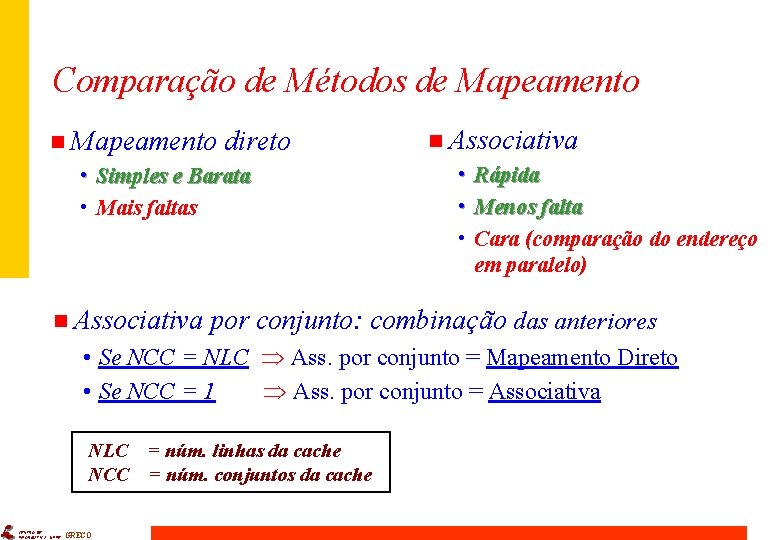

Comparação de Métodos de Mapeamento n Mapeamento direto • Simples e Barata • Mais faltas n Associativa • Rápida • Menos falta • Cara (comparação do endereço em paralelo) por conjunto: combinação das anteriores • Se NCC = NLC Þ Ass. por conjunto = Mapeamento Direto • Se NCC = 1 Þ Ass. por conjunto = Associativa NLC = núm. linhas da cache NCC = núm. conjuntos da cache CENTRO DE INFORMÁTICA - UFPE GRECO

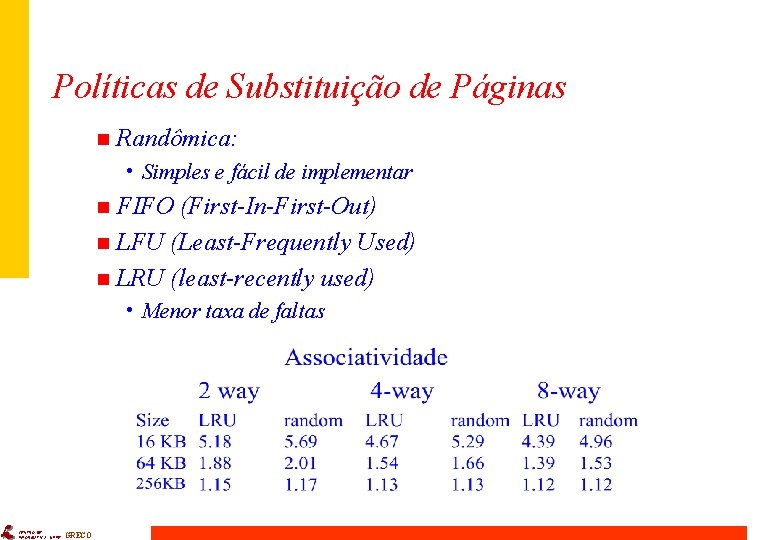

Políticas de Substituição de Páginas n Randômica: • Simples e fácil de implementar FIFO (First-In-First-Out) n LFU (Least-Frequently Used) n LRU (least-recently used) n • Menor taxa de faltas CENTRO DE INFORMÁTICA - UFPE GRECO

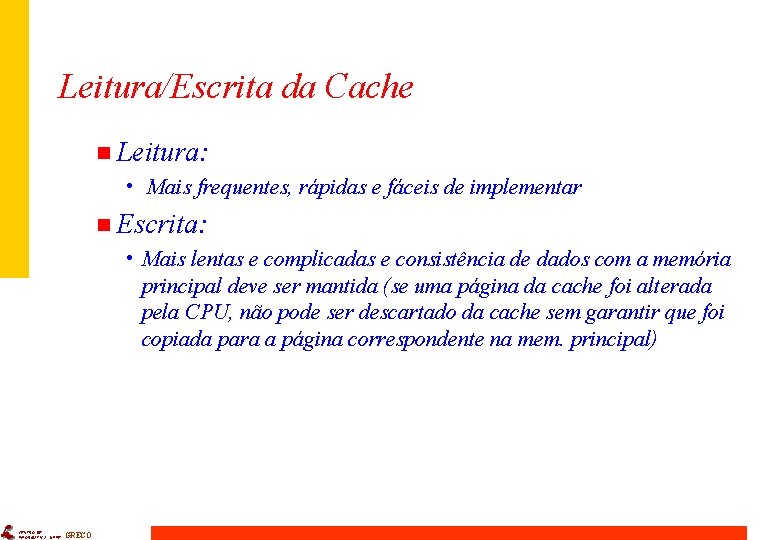

Leitura/Escrita da Cache n Leitura: • Mais frequentes, rápidas e fáceis de implementar n Escrita: • Mais lentas e complicadas e consistência de dados com a memória principal deve ser mantida (se uma página da cache foi alterada pela CPU, não pode ser descartado da cache sem garantir que foi copiada para a página correspondente na mem. principal) CENTRO DE INFORMÁTICA - UFPE GRECO

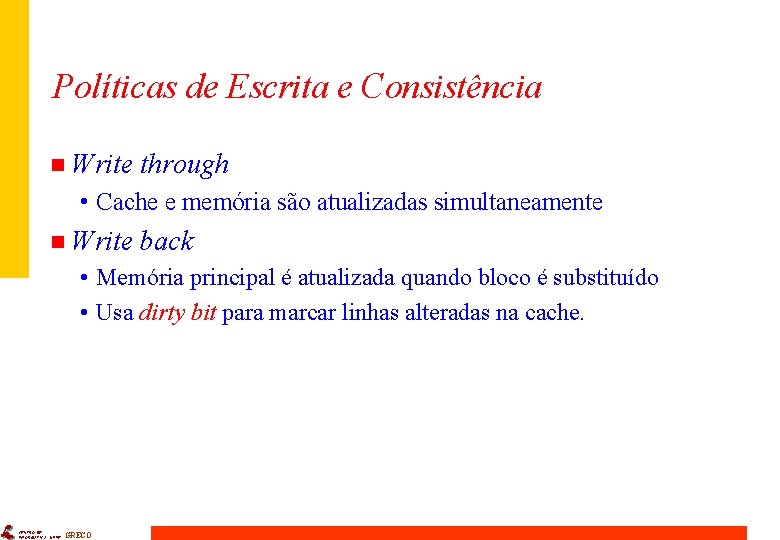

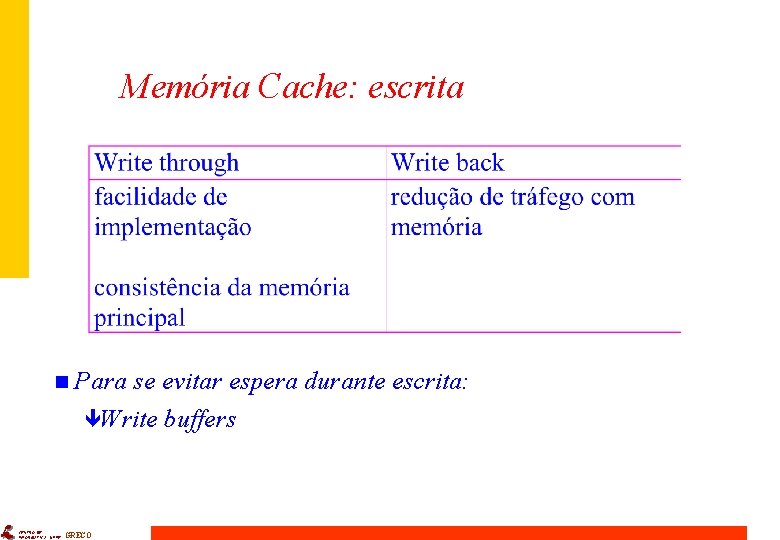

Políticas de Escrita e Consistência n Write through • Cache e memória são atualizadas simultaneamente n Write back • Memória principal é atualizada quando bloco é substituído • Usa dirty bit para marcar linhas alteradas na cache. CENTRO DE INFORMÁTICA - UFPE GRECO

Memória Cache: escrita n CENTRO DE INFORMÁTICA - UFPE Para se evitar espera durante escrita: êWrite buffers GRECO

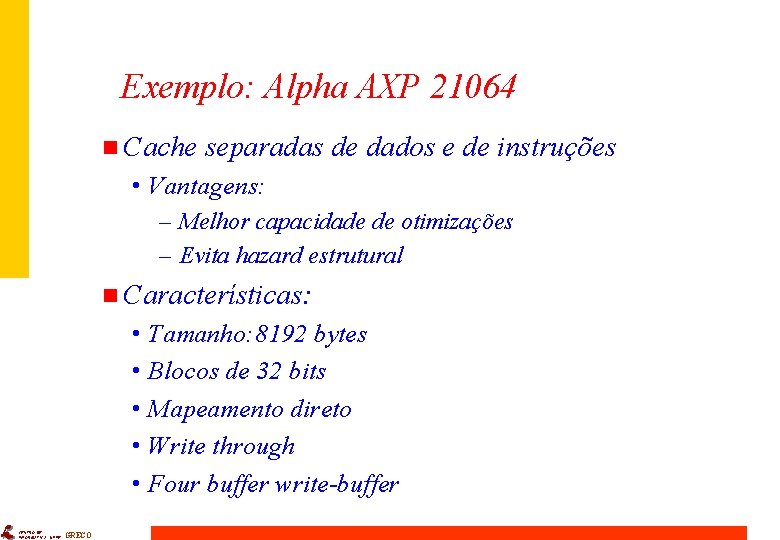

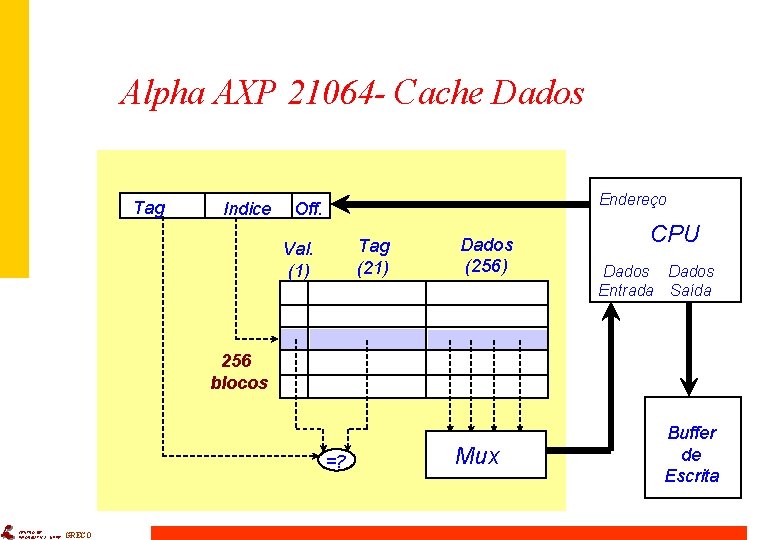

Exemplo: Alpha AXP 21064 n Cache separadas de dados e de instruções • Vantagens: – Melhor capacidade de otimizações – Evita hazard estrutural n Características: • Tamanho: 8192 bytes • Blocos de 32 bits • Mapeamento direto • Write through • Four buffer write-buffer CENTRO DE INFORMÁTICA - UFPE GRECO

Alpha AXP 21064 - Cache Dados Tag Indice Endereço Off. Tag (21) Val. (1) Dados (256) CPU Dados Entrada Saída 256 blocos =? CENTRO DE INFORMÁTICA - UFPE GRECO Mux Buffer de Escrita

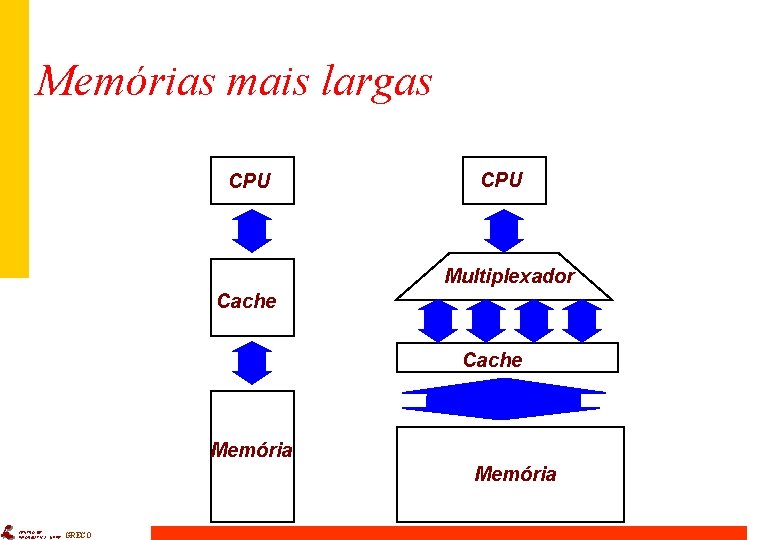

Memórias mais largas CPU Multiplexador Cache Memória CENTRO DE INFORMÁTICA - UFPE GRECO

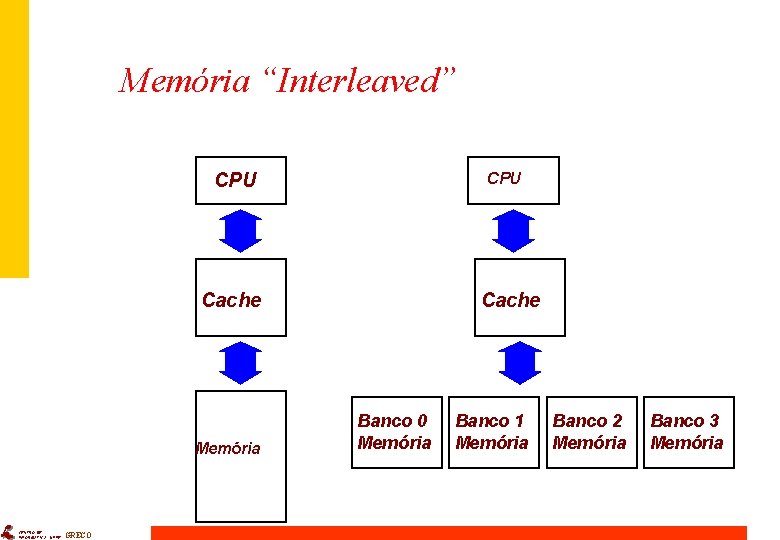

Memória “Interleaved” CPU Cache Memória CENTRO DE INFORMÁTICA - UFPE GRECO Cache Banco 0 Memória Banco 1 Memória Banco 2 Memória Banco 3 Memória

Memória Interleaved Bancos de memória para escrita/leitura de múltiplas palavras n Reduz penalidade n Necessita pouco hardware adicional n CENTRO DE INFORMÁTICA - UFPE GRECO

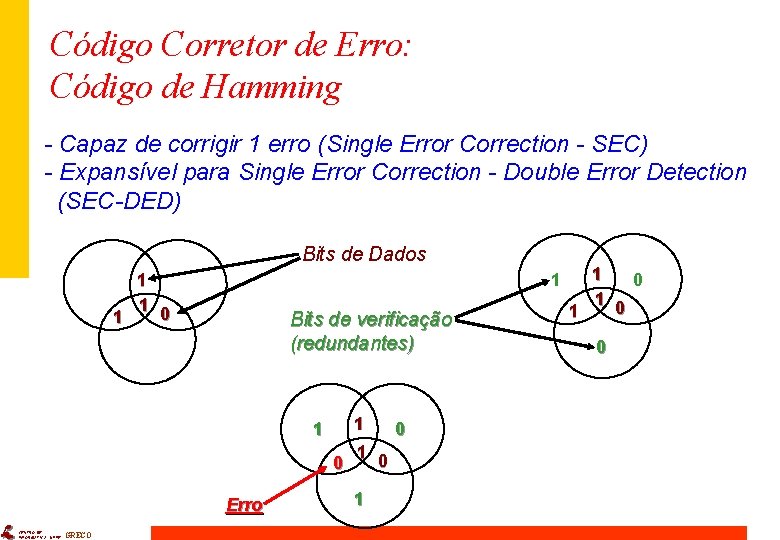

Código Corretor de Erro: Código de Hamming - Capaz de corrigir 1 erro (Single Error Correction - SEC) - Expansível para Single Error Correction - Double Error Detection (SEC-DED) Bits de Dados 1 1 1 0 1 Bits de verificação (redundantes) 1 1 0 Erro CENTRO DE INFORMÁTICA - UFPE GRECO 1 0 1 0 1 0

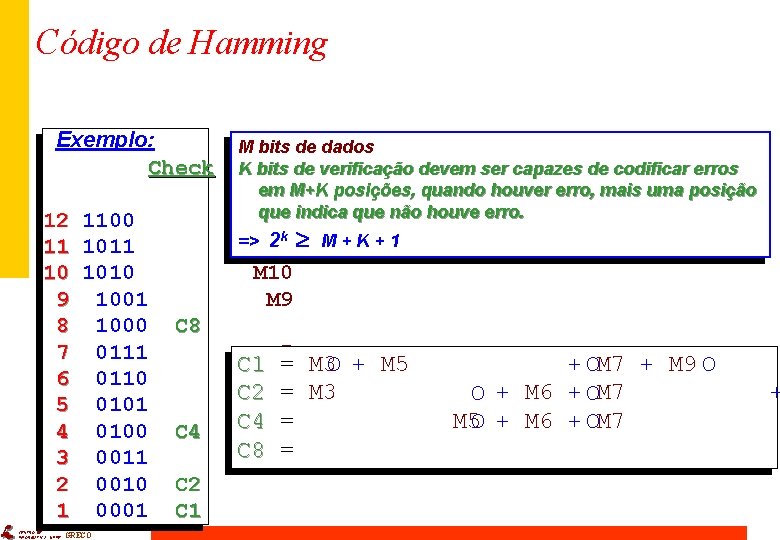

Código de Hamming Exemplo: Check 12 1100 11 10 1010 9 1001 8 1000 7 0111 6 0110 5 0101 4 0100 3 0011 2 0010 1 0001 CENTRO DE INFORMÁTICA - UFPE GRECO M bits de dados K Data bits de verificação devem ser capazes de codificar erros posições, quando houver erro, mais uma posição bitem M+K bit que indica que não houve erro. M 12 =>M 11 2 k ³ M + K + 1 M 10 M 9 C 8 M 7 C 4 C 2 C 1 = M 3 O + M 5 M 6 C 2 M 5 = M 3 C 4 = C 8 M 3 = + OM 7 + M 9 O O + M 6 + OM 7 M 5 O + M 6 + OM 7 +

- Slides: 53