MemoryEfficient and Scalable Virtual Routers Using FPGA Authors

Memory-Efficient and Scalable Virtual Routers Using FPGA Authors: Hoang Le, Thilan Ganegedara and Viktor K. Prasanna. Publisher: 2011 19 th ACM/SIGDA international symposium on Field programmable gate arrays (FPGA) Presenter: Chun-Yu, Li Date: 2015/11/4 Department of Computer Science and Information Engineering, National Cheng Kung University, Tainan, Taiwan, R. O. C.

Outline l Introduction l IP Lookup Algorithm for Virtual Router l Architecture l Performance Evaluation • Network Virtulization • Set-Bounded Leaf-Pushing Algorithm (SBLP) • Overall Architecture • Memory Management • Virtual Routing Table Update • Experimental Setup • Performance Comparison Computer & Internet Architecture Lab CSIE NCKU 2

Network Virtulization (1/2) l The main goal of virtualization is to make efficient use of the networking resources. l It allows multiple virtual router instances to run on a common physical router platform. Computer & Internet Architecture Lab CSIE NCKU 3

Network Virtulization (2/2) l A simple merging algorithm for IP lookup in virtual router that achieves high throughput and supports quick update. l Using FPGA along with external SRAM, the proposed architecture can support up to 16 M IPv 4 and 880 K IPv 6 prefixes. Computer & Internet Architecture Lab CSIE NCKU 4

Outline l Introduction l IP Lookup Algorithm for Virtual Router l Architecture l Performance Evaluation • Network Virtulization • Set-Bounded Leaf-Pushing Algorithm (SBLP) • Overall Architecture • Memory Management • Virtual Routing Table Update • Experimental Setup • Performance Comparison Computer & Internet Architecture Lab CSIE NCKU 5

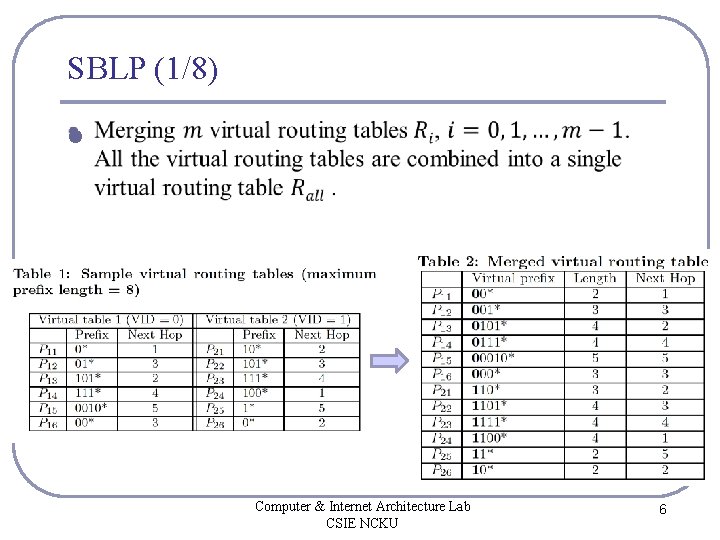

SBLP (1/8) l Computer & Internet Architecture Lab CSIE NCKU 6

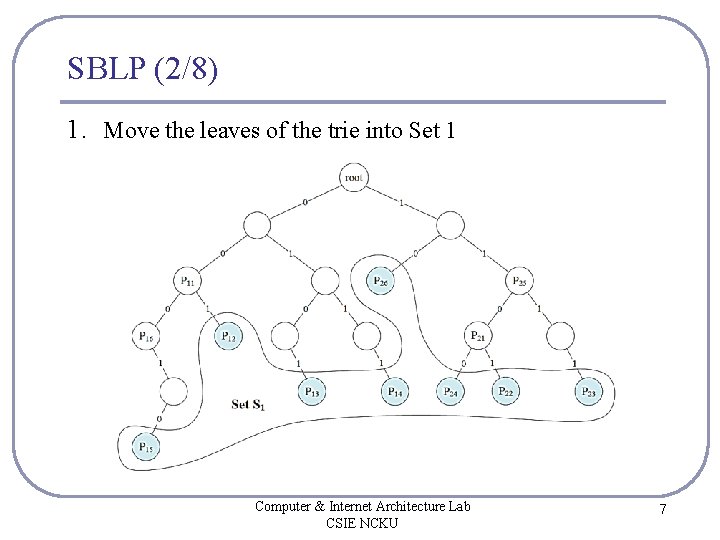

SBLP (2/8) 1. Move the leaves of the trie into Set 1 Computer & Internet Architecture Lab CSIE NCKU 7

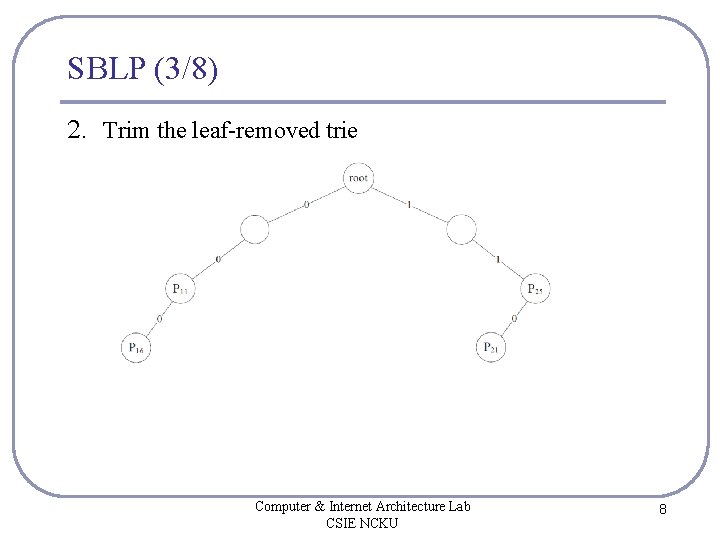

SBLP (3/8) 2. Trim the leaf-removed trie Computer & Internet Architecture Lab CSIE NCKU 8

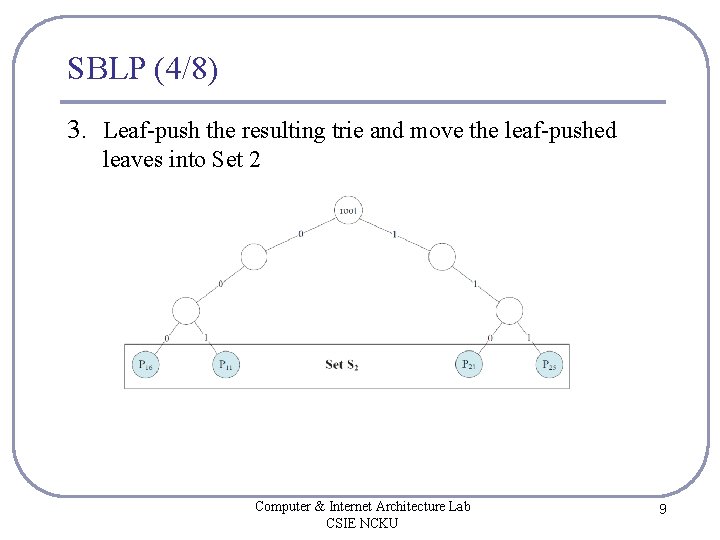

SBLP (4/8) 3. Leaf-push the resulting trie and move the leaf-pushed leaves into Set 2 Computer & Internet Architecture Lab CSIE NCKU 9

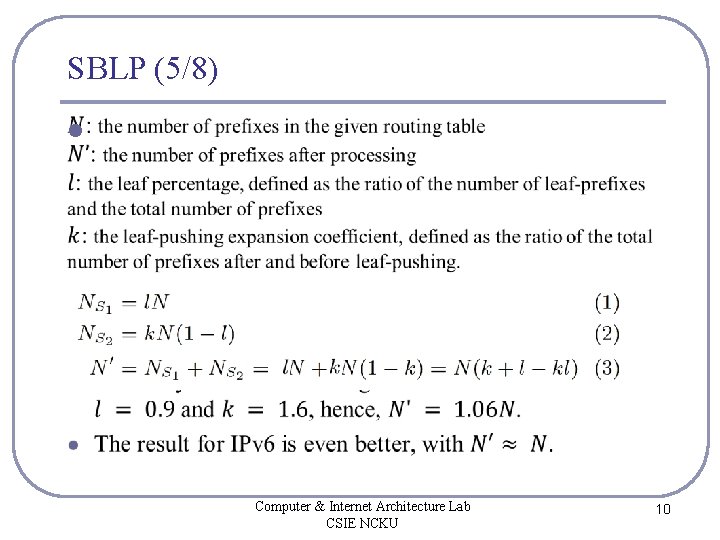

SBLP (5/8) l Computer & Internet Architecture Lab CSIE NCKU 10

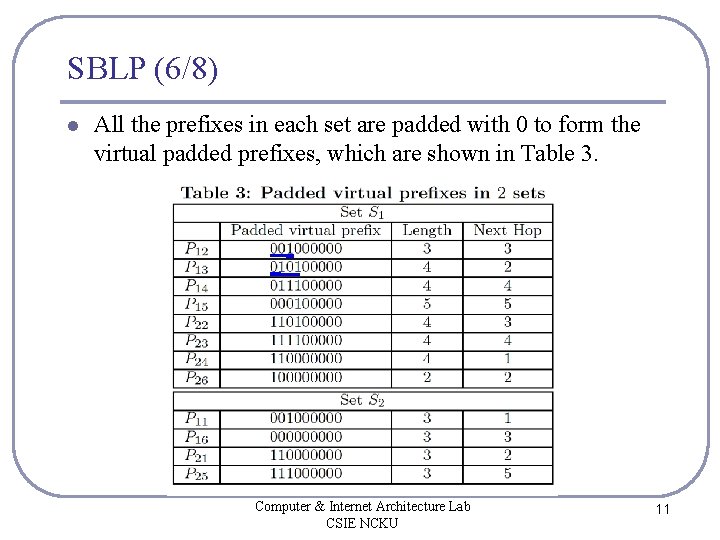

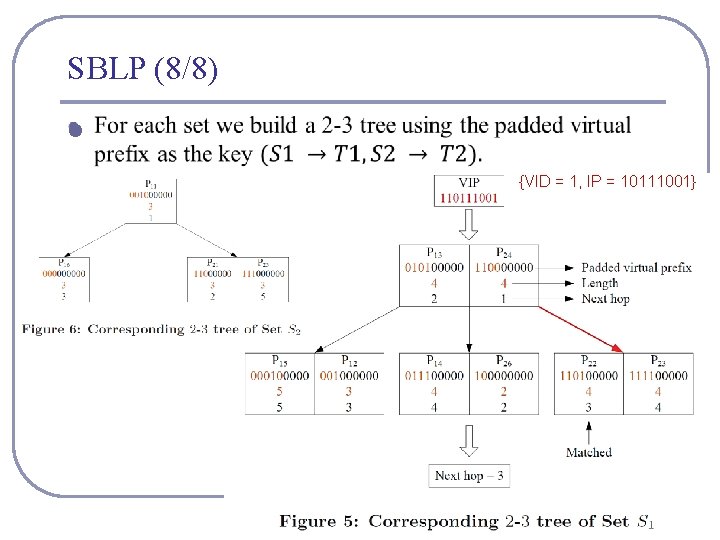

SBLP (6/8) l All the prefixes in each set are padded with 0 to form the virtual padded prefixes, which are shown in Table 3. Computer & Internet Architecture Lab CSIE NCKU 11

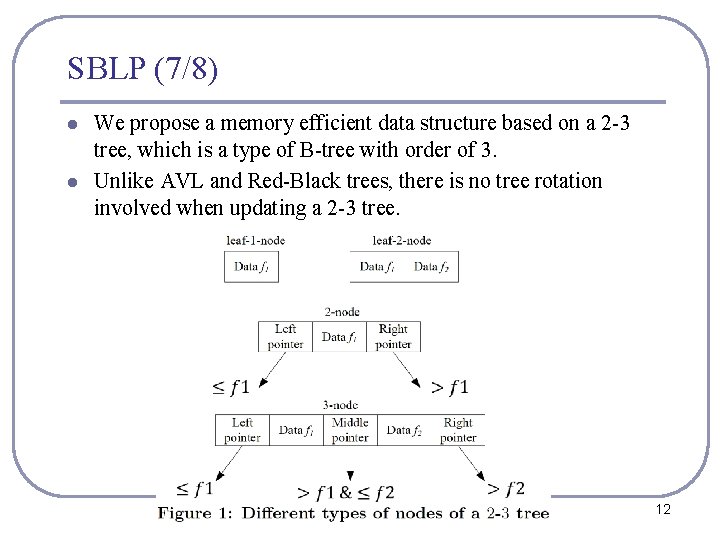

SBLP (7/8) l l We propose a memory efficient data structure based on a 2 -3 tree, which is a type of B-tree with order of 3. Unlike AVL and Red-Black trees, there is no tree rotation involved when updating a 2 -3 tree. Computer & Internet Architecture Lab CSIE NCKU 12

SBLP (8/8) l {VID = 1, IP = 10111001} Computer & Internet Architecture Lab CSIE NCKU 13

Outline l Introduction l IP Lookup Algorithm for Virtual Router l Architecture l Performance Evaluation • Network Virtulization • Set-Bounded Leaf-Pushing Algorithm (SBLP) • Overall Architecture • Memory Management • Virtual Routing Table Update • Experimental Setup • Performance Comparison Computer & Internet Architecture Lab CSIE NCKU 14

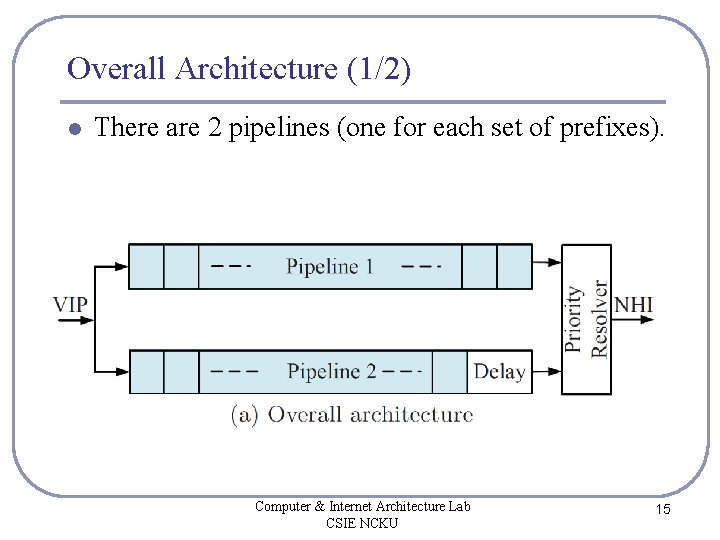

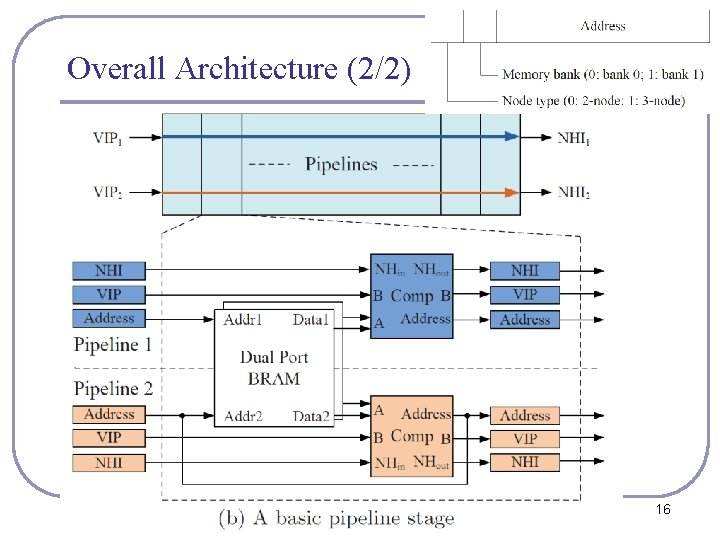

Overall Architecture (1/2) l There are 2 pipelines (one for each set of prefixes). Computer & Internet Architecture Lab CSIE NCKU 15

Overall Architecture (2/2) Computer & Internet Architecture Lab CSIE NCKU 16

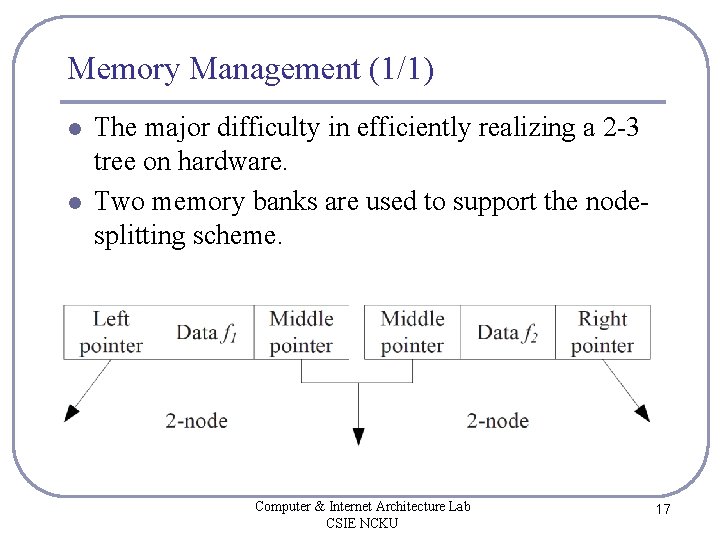

Memory Management (1/1) l l The major difficulty in efficiently realizing a 2 -3 tree on hardware. Two memory banks are used to support the nodesplitting scheme. Computer & Internet Architecture Lab CSIE NCKU 17

Virtual Routing Table Update (1/3) l A virtual routing table update can be any of three operations: • Modification of an existing prefix (i. e. change of • • the next hop information). Deletion of an existing prefix. Insertion of a new prefix. Computer & Internet Architecture Lab CSIE NCKU 18

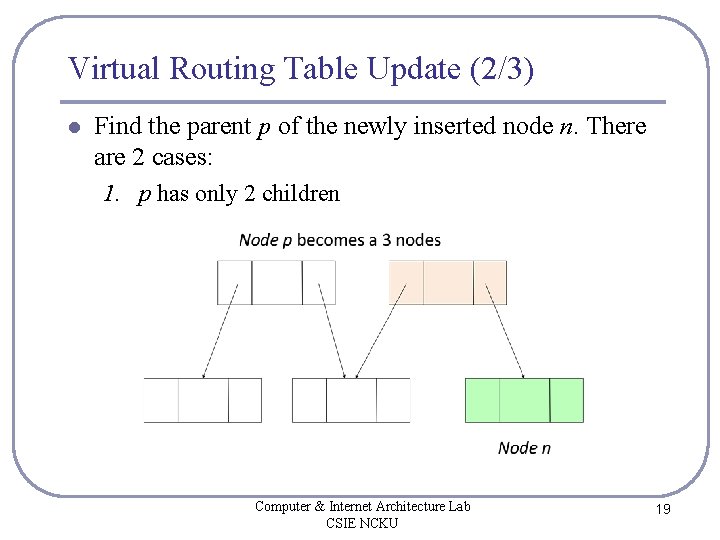

Virtual Routing Table Update (2/3) l Find the parent p of the newly inserted node n. There are 2 cases: 1. p has only 2 children Computer & Internet Architecture Lab CSIE NCKU 19

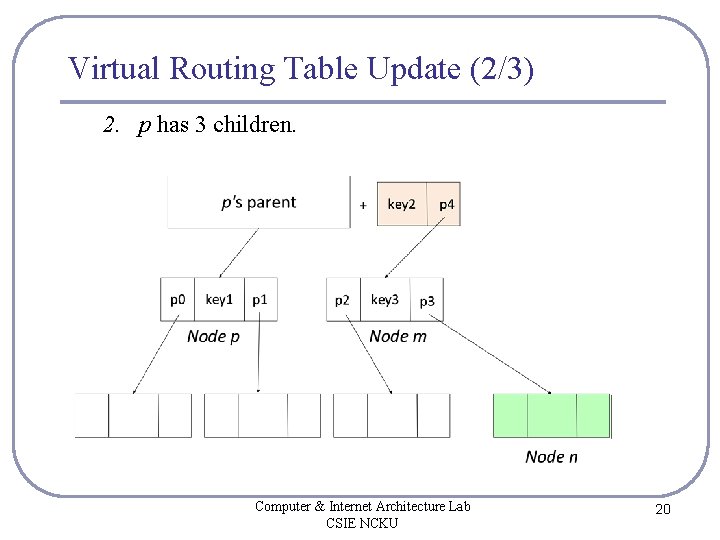

Virtual Routing Table Update (2/3) 2. p has 3 children. Computer & Internet Architecture Lab CSIE NCKU 20

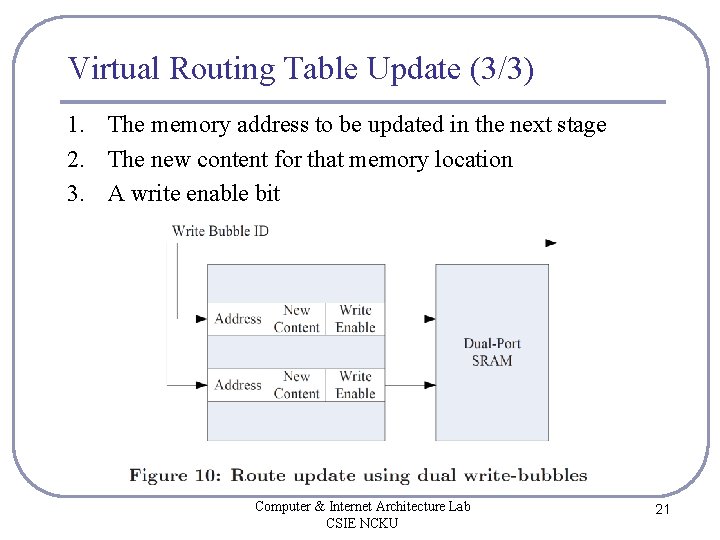

Virtual Routing Table Update (3/3) 1. The memory address to be updated in the next stage 2. The new content for that memory location 3. A write enable bit Computer & Internet Architecture Lab CSIE NCKU 21

Outline l Introduction l IP Lookup Algorithm for Virtual Router l Architecture l Performance Evaluation • Network Virtulization • Set-Bounded Leaf-Pushing Algorithm (SBLP) • Overall Architecture • Memory Management • Virtual Routing Table Update • Experimental Setup • Performance Comparison Computer & Internet Architecture Lab CSIE NCKU 22

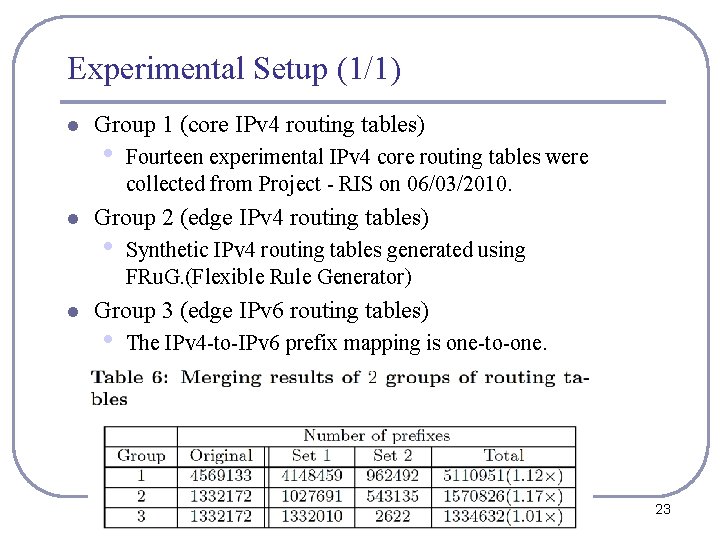

Experimental Setup (1/1) l l l Group 1 (core IPv 4 routing tables) • Fourteen experimental IPv 4 core routing tables were collected from Project - RIS on 06/03/2010. Group 2 (edge IPv 4 routing tables) • Synthetic IPv 4 routing tables generated using FRu. G. (Flexible Rule Generator) Group 3 (edge IPv 6 routing tables) • The IPv 4 -to-IPv 6 prefix mapping is one-to-one. Computer & Internet Architecture Lab CSIE NCKU 23

Performance Comparison (1/2) l Scheme A 1 (Trie-overlapping '08) • It is occasionally required to reconstruct the entire lookup data structure for optimal lookup efficiency. l Scheme A 2 (Trie braiding '10) • It is also required to be recomputed over a longer period of time in order to minimize the trie size. l Proposed Approach • New prefix can quickly be merged using our simple • merging algorithm New prefix can be inserted into the tree by injecting the update bubbles into the traffic stream. Computer & Internet Architecture Lab CSIE NCKU 24

Performance Comparison (2/2) l l We cannot directly compare throughput with the other 2 schemes as they were not implemented on hardware. Implementation on FPGA with Virtex-6 XC 6 VSX 475 T as the target. • 10% of the on-chip logic resource. • Throughput of 128 Gbps. • Maximum frequency of 200 MHz. Computer & Internet Architecture Lab CSIE NCKU 25

- Slides: 25