Memory Mapping Techniques CAO Lect 29 Outline Memory

- Slides: 18

Memory Mapping Techniques CAO Lect. #29

Outline � Memory Mapping Techniques � Direct Mapping � Fully-Associative Mapping � Set-Associative Mapping � Summary of Memory Mapping Techniques � Low-Power Off-Chip Memory Design for Video Decoder Using Embedded Bus-Invert Coding

Memory Mapping Techniques

Memory Mapping Techniques � There are three main types of memory mapping techniques: 1. Direct Mapping 2. Fully-Associative Mapping 3. Set-Associative Mapping � For the coming explanations, let us assume 1 GB main memory, 128 KB Cache Memory and Cache Line Size 32 B

Direct Mapping

Direct Mapping � Each block of main memory maps to only one cache line � i. e. if a block is in cache, it must be in one specific place � Address is in two parts � Least Significant w bits identify unique word/byte � Most Significant s bits specify one memory block � The MSBs are split into a cache line field r and a tag of s-r (most significant)

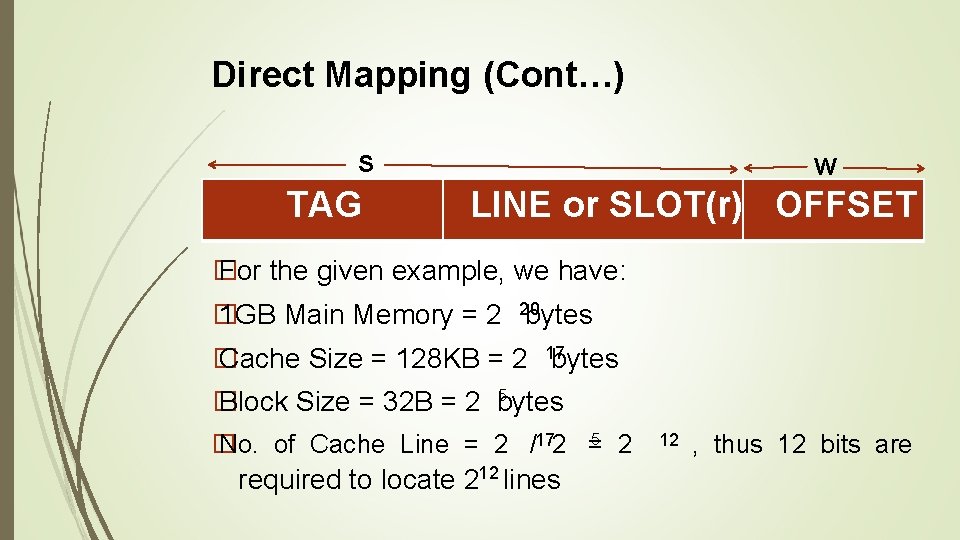

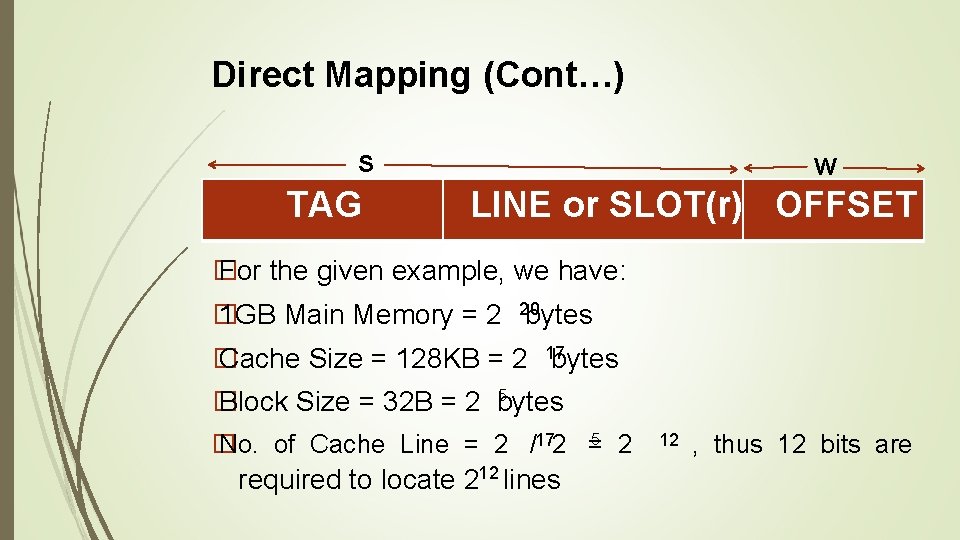

Direct Mapping (Cont…) S TAG W LINE or SLOT(r) OFFSET � For the given example, we have: � 1 GB Main Memory = 2 20 bytes � Cache Size = 128 KB = 2 17 bytes 5 � Block Size = 32 B = 2 bytes � No. of Cache Line = 2 /172 =5 2 required to locate 212 lines 12 , thus 12 bits are

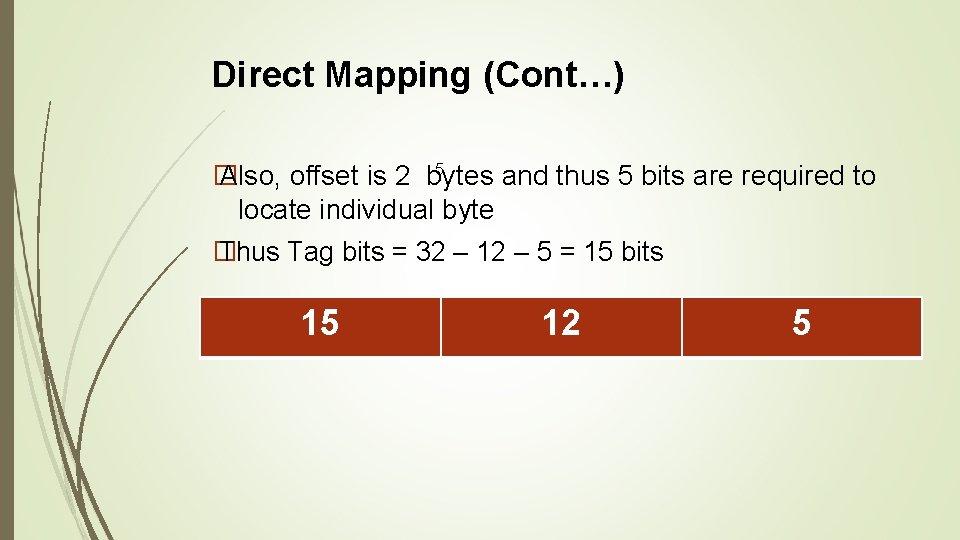

Direct Mapping (Cont…) 5 � Also, offset is 2 bytes and thus 5 bits are required to locate individual byte � Thus Tag bits = 32 – 12 – 5 = 15 bits 15 12 5

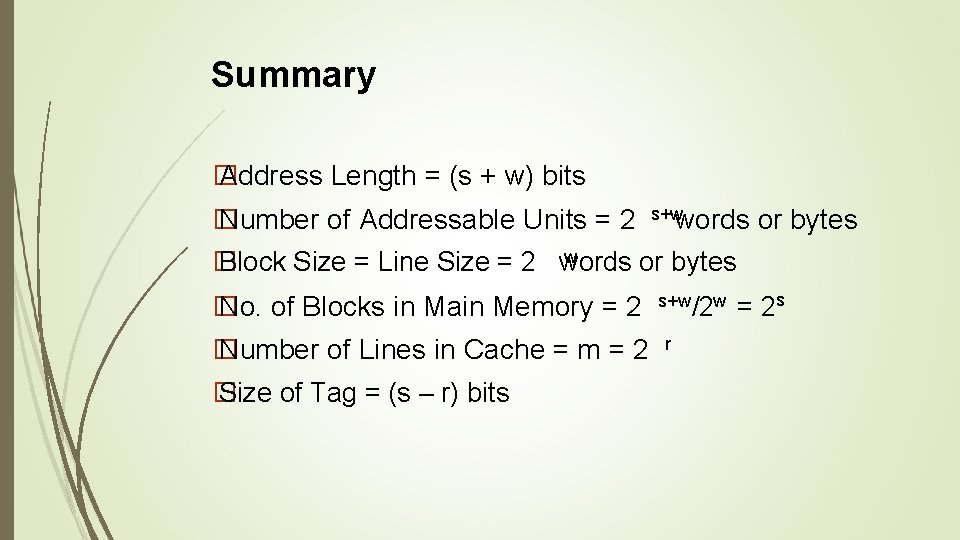

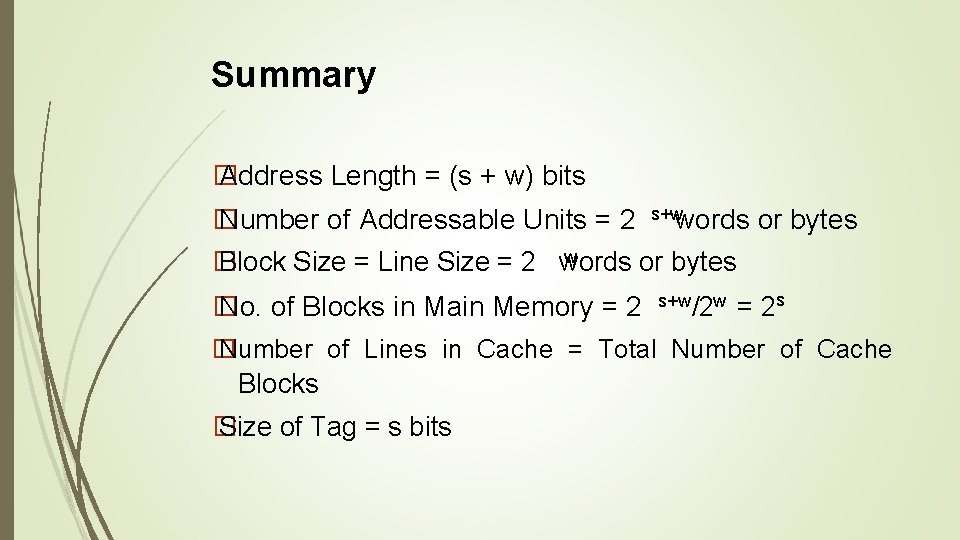

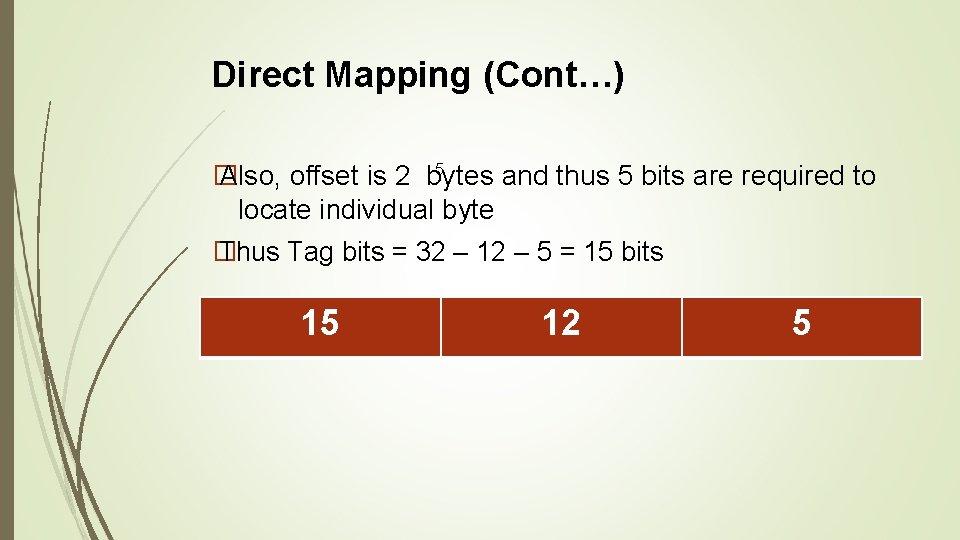

Summary � Address Length = (s + w) bits � Number of Addressable Units = 2 s+wwords or bytes w � Block Size = Line Size = 2 words or bytes � No. of Blocks in Main Memory = 2 � Number of Lines in Cache = m = 2 � Size of Tag = (s – r) bits s+w/2 w r = 2 s

Fully-Associative Mapping

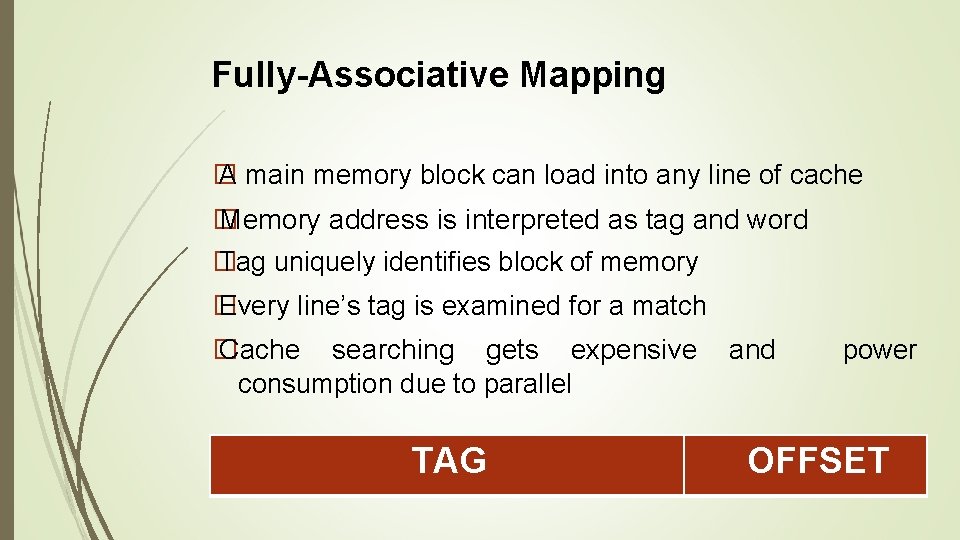

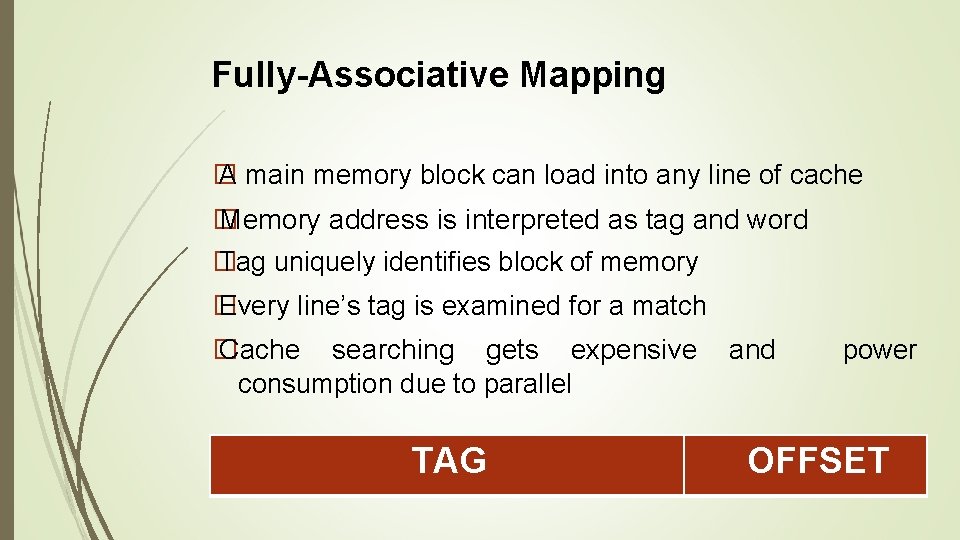

Fully-Associative Mapping � A main memory block can load into any line of cache � Memory address is interpreted as tag and word � Tag uniquely identifies block of memory � Every line’s tag is examined for a match � Cache searching gets expensive consumption due to parallel TAG and power OFFSET

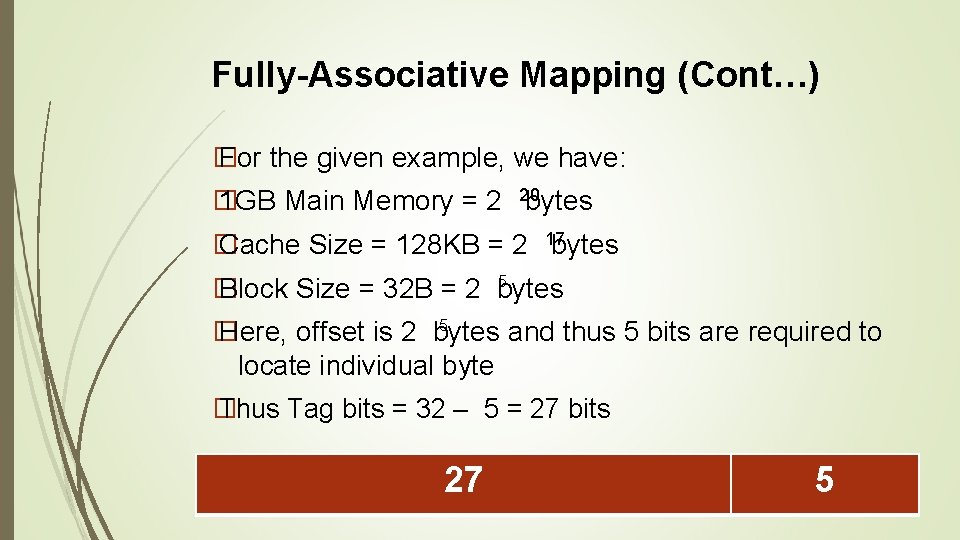

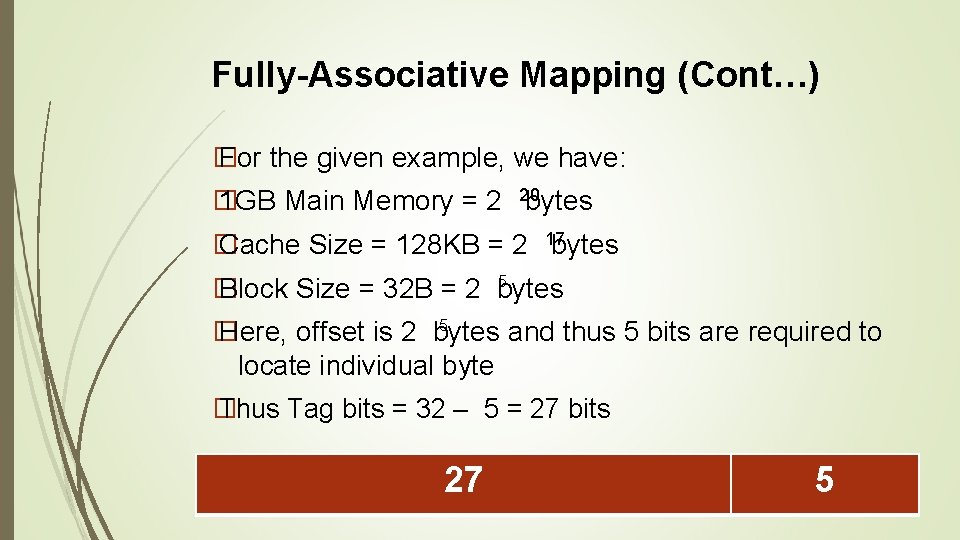

Fully-Associative Mapping (Cont…) � For the given example, we have: � 1 GB Main Memory = 2 20 bytes � Cache Size = 128 KB = 2 17 bytes 5 � Block Size = 32 B = 2 bytes 5 � Here, offset is 2 bytes and thus 5 bits are required to locate individual byte � Thus Tag bits = 32 – 5 = 27 bits 27 5

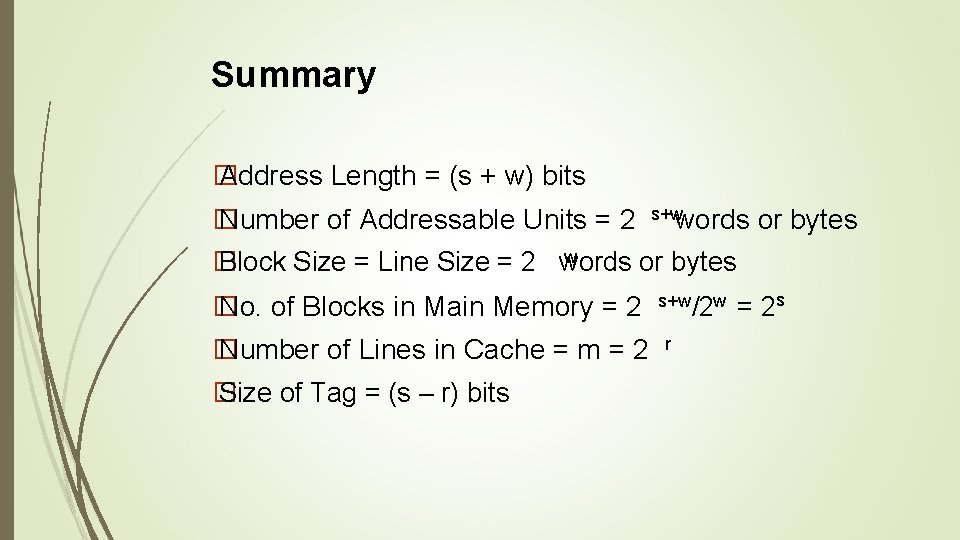

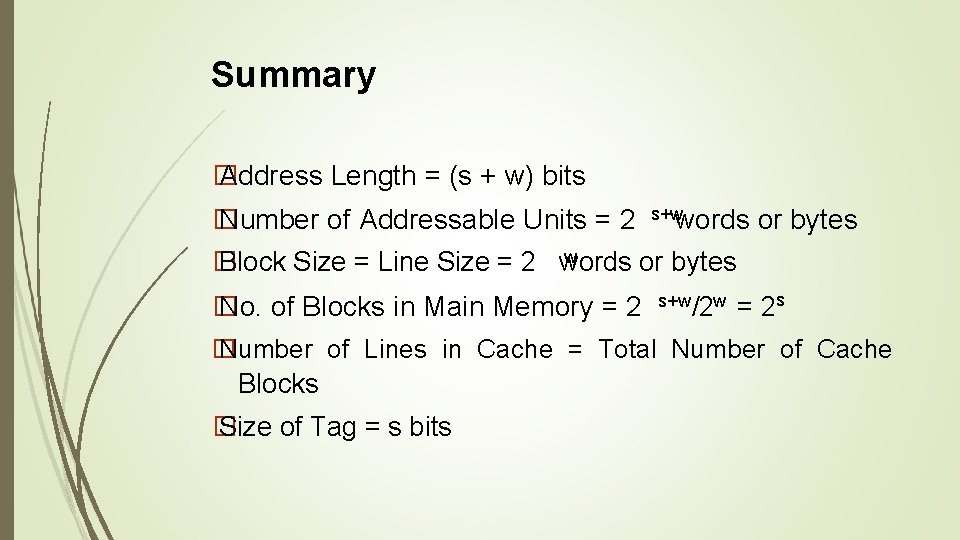

Summary � Address Length = (s + w) bits � Number of Addressable Units = 2 s+wwords or bytes w � Block Size = Line Size = 2 words or bytes � No. of Blocks in Main Memory = 2 s+w/2 w = 2 s � Number of Lines in Cache = Total Number of Cache Blocks � Size of Tag = s bits

Set-Associative Mapping

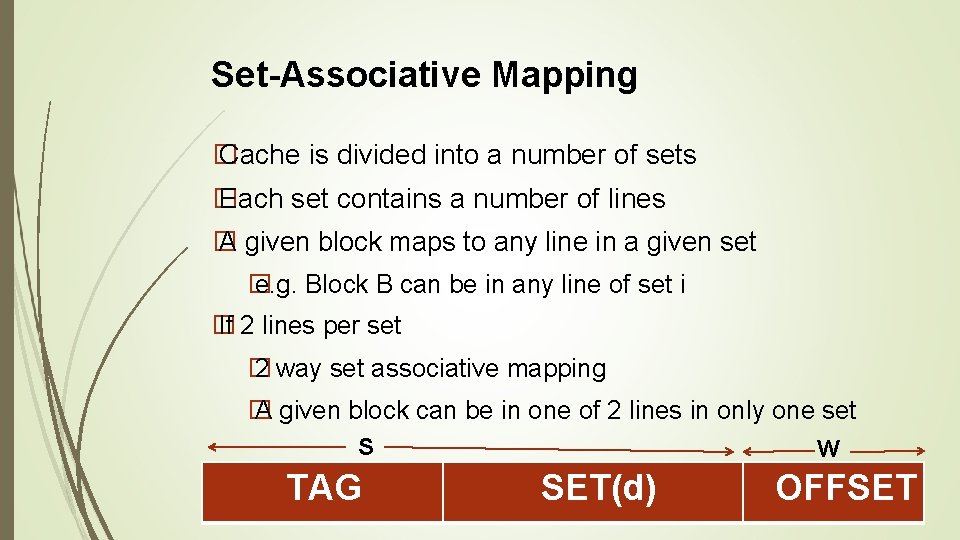

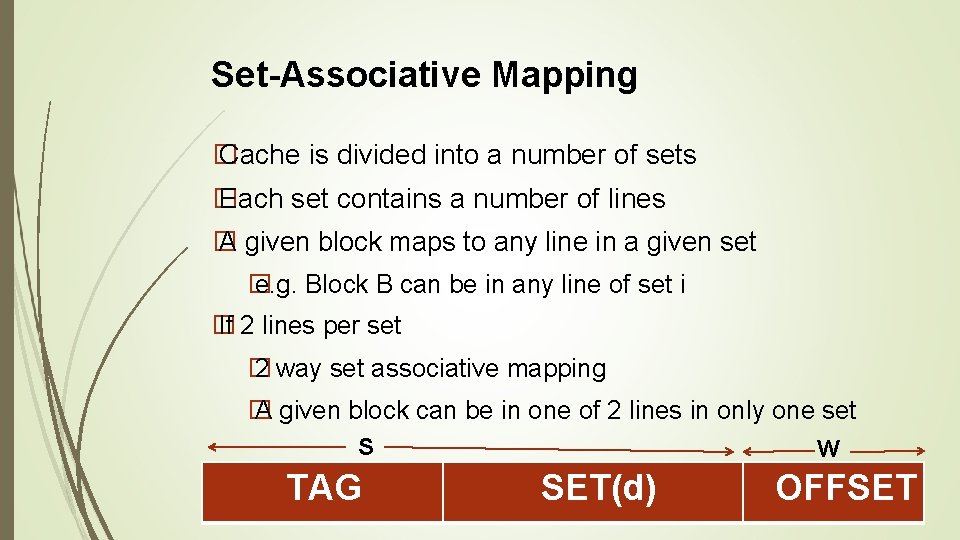

Set-Associative Mapping � Cache is divided into a number of sets � Each set contains a number of lines � A given block maps to any line in a given set � e. g. Block B can be in any line of set i � If 2 lines per set � 2 way set associative mapping � A given block can be in one of 2 lines in only one set S TAG W SET(d) OFFSET

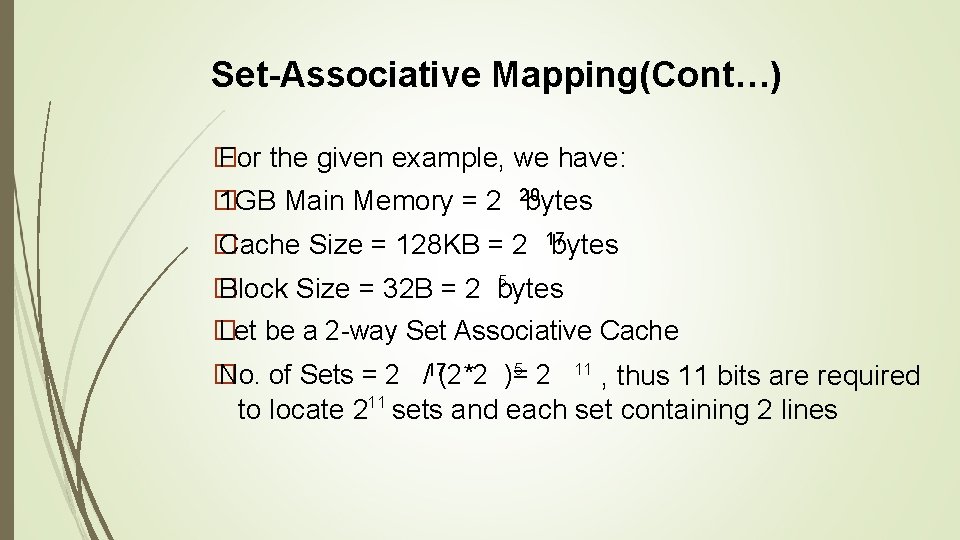

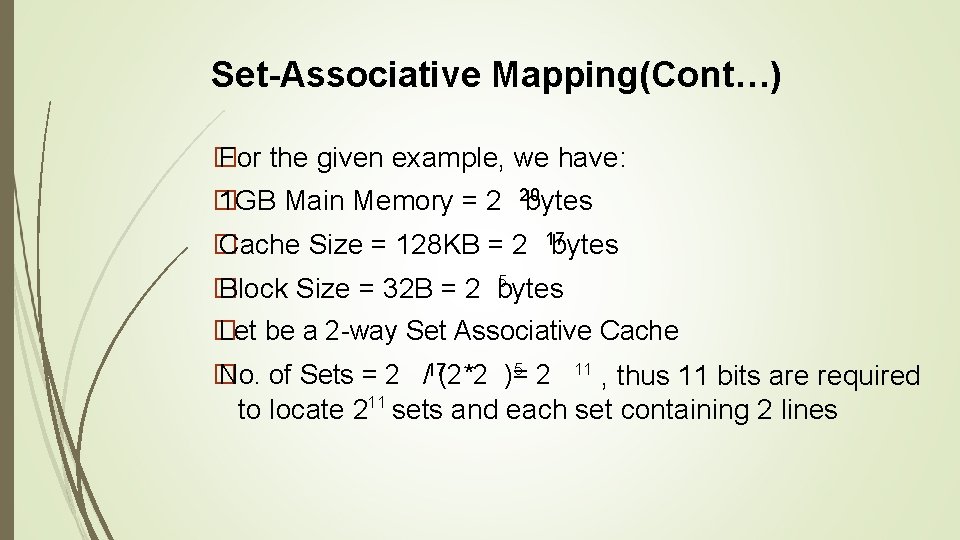

Set-Associative Mapping(Cont…) � For the given example, we have: � 1 GB Main Memory = 2 20 bytes � Cache Size = 128 KB = 2 17 bytes 5 � Block Size = 32 B = 2 bytes � Let be a 2 -way Set Associative Cache 5 � No. of Sets = 2 /17(2*2 )= 2 11 , thus 11 bits are required to locate 211 sets and each set containing 2 lines

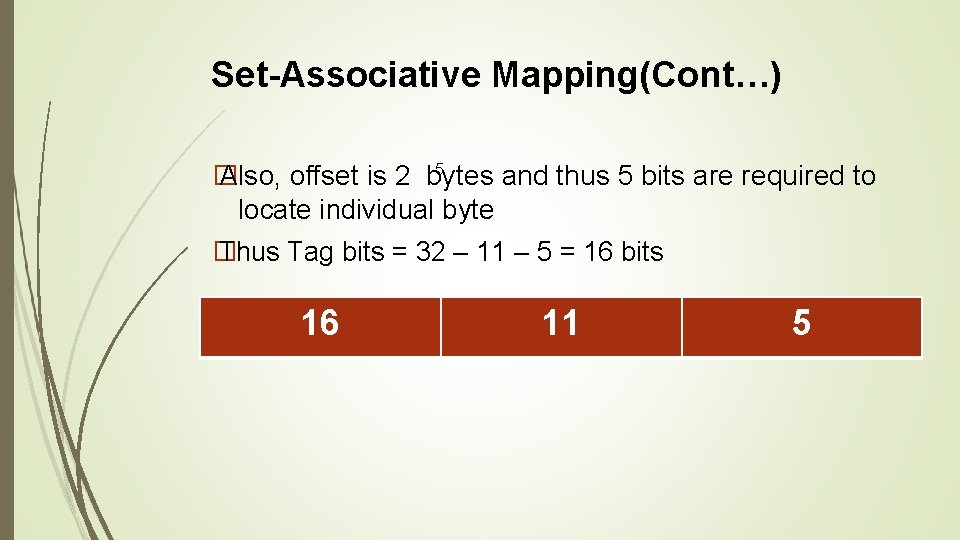

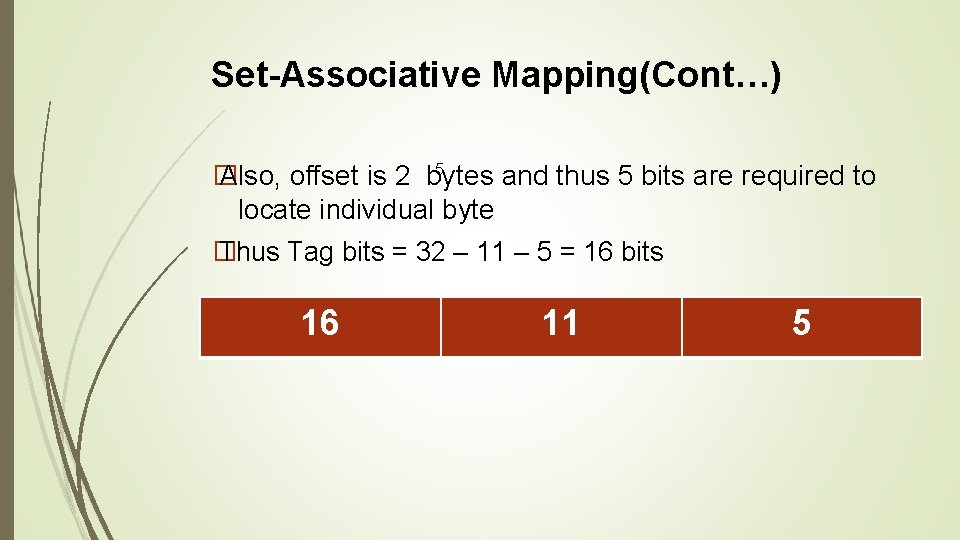

Set-Associative Mapping(Cont…) 5 � Also, offset is 2 bytes and thus 5 bits are required to locate individual byte � Thus Tag bits = 32 – 11 – 5 = 16 bits 16 11 5

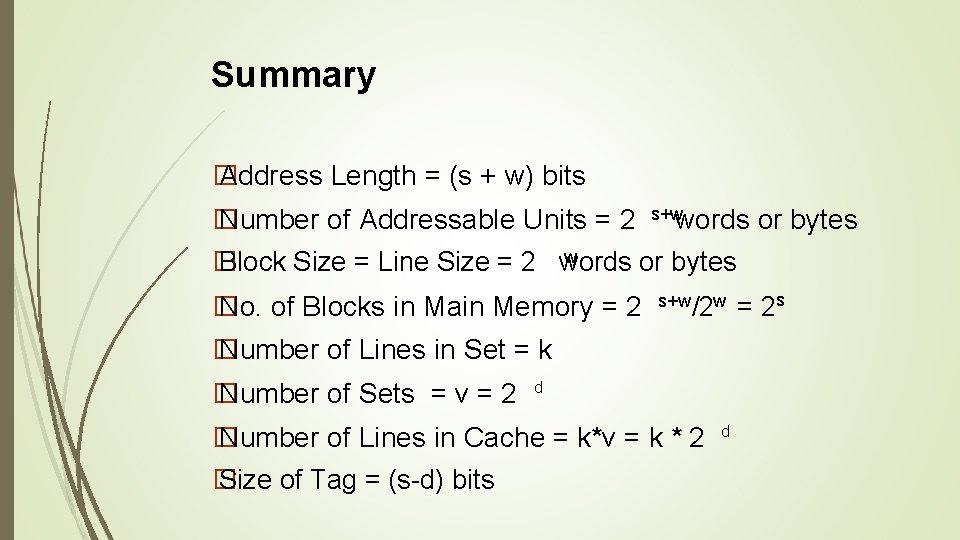

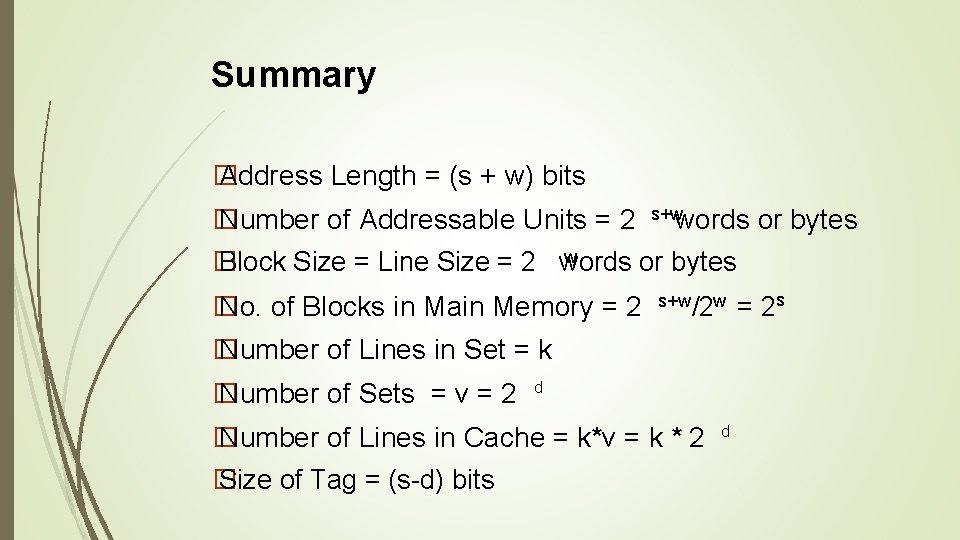

Summary � Address Length = (s + w) bits � Number of Addressable Units = 2 s+wwords or bytes w � Block Size = Line Size = 2 words or bytes � No. of Blocks in Main Memory = 2 s+w/2 w � Number of Lines in Set = k � Number of Sets = v = 2 d � Number of Lines in Cache = k*v = k * 2 � Size of Tag = (s-d) bits d = 2 s