MEMORIA RAM PARTES O ELEMENTOS CONCEPTOS Capacidad de

- Slides: 38

MEMORIA RAM

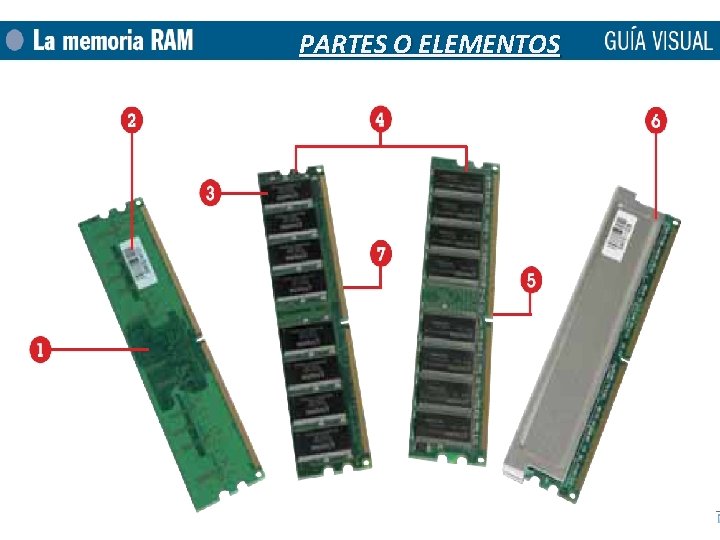

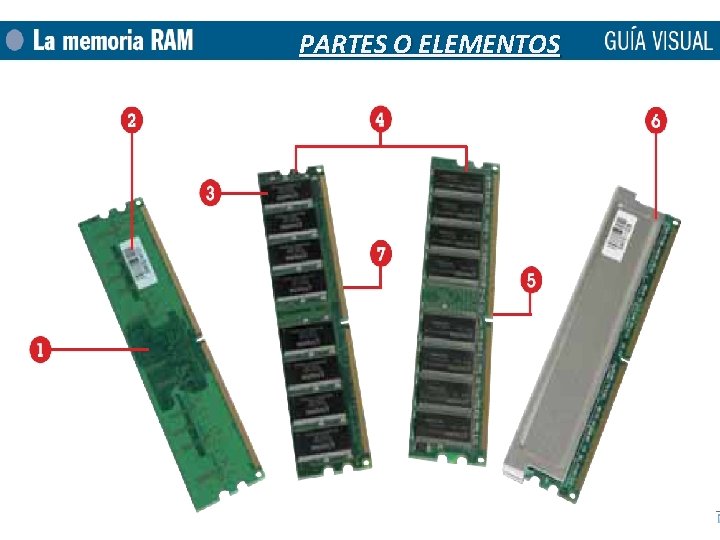

PARTES O ELEMENTOS

CONCEPTOS • Capacidad de almacenamiento: representa el volumen global de información (en bits) que la memoria puede almacenar. Actualmente se mide en gigabytes. • Tiempo de acceso: corresponde al intervalo de tiempo entre la solicitud de lectura/ escritura de un dato y la disponibilidad de los datos en cuestión. Cuanto menor es este tiempo, más eficiente es la memoria. Se mide en ns (nanosegundos).

CONCEPTOS • Tiempo de ciclo: representa el intervalo de tiempo mínimo entre dos accesos sucesivos. Es decir, este concepto hace referencia al tiempo entre ciclos de reloj. • Rendimiento: define el volumen de información intercambiado por unidad de tiempo, expresado en bits por segundo.

PREGUNTAS: 1. -¿De dónde viene la palabra RAM? 2. -¿Explica porque se dice que es de acceso aleatorio? 3. -¿Qué significa que sea volátil? 4. - ¿Qué se ejecuta en la memoria RAM? 5. - ¿Qué función realiza el controlador de la memoria y para que la realiza? 6. - ¿Por qué se dice que es una memoria dinámica? 7. - Dentro de las características de la Memoria RAM se habla de 4 aspectos: Capacidad de almacenamiento, Tiempo de acceso, Tiempo de ciclo y Rendimiento. ¿Qué significa cada uno?

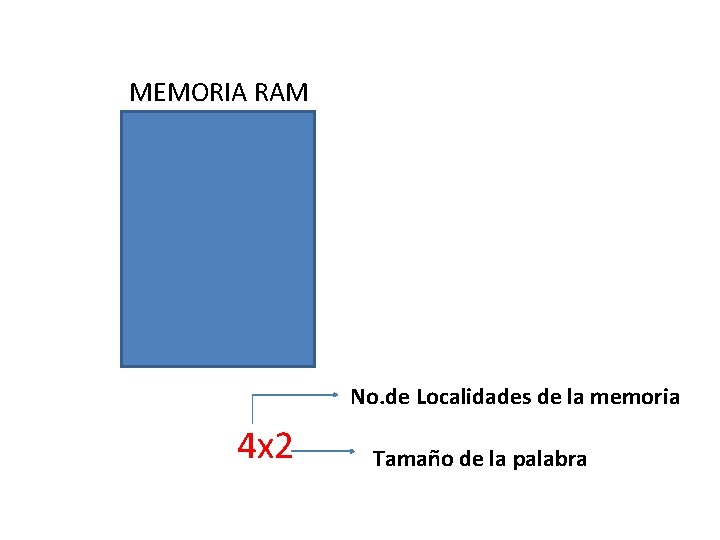

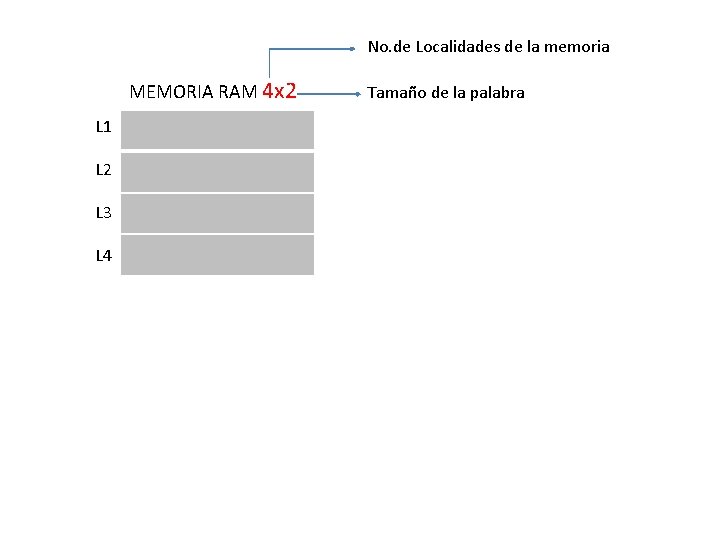

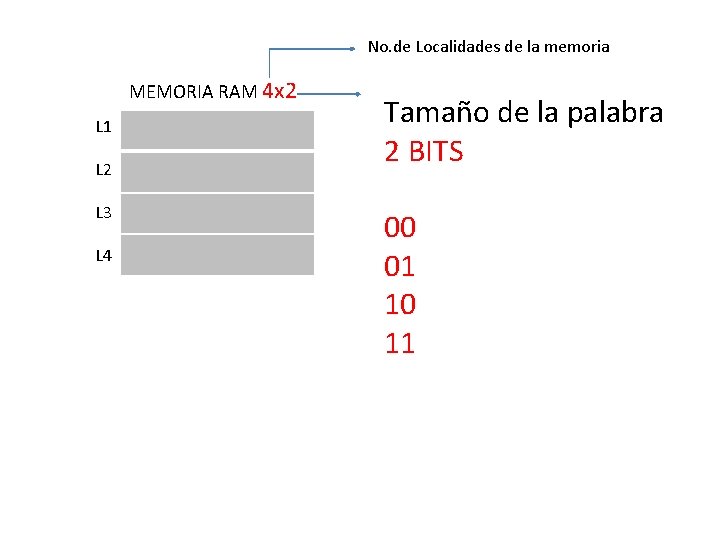

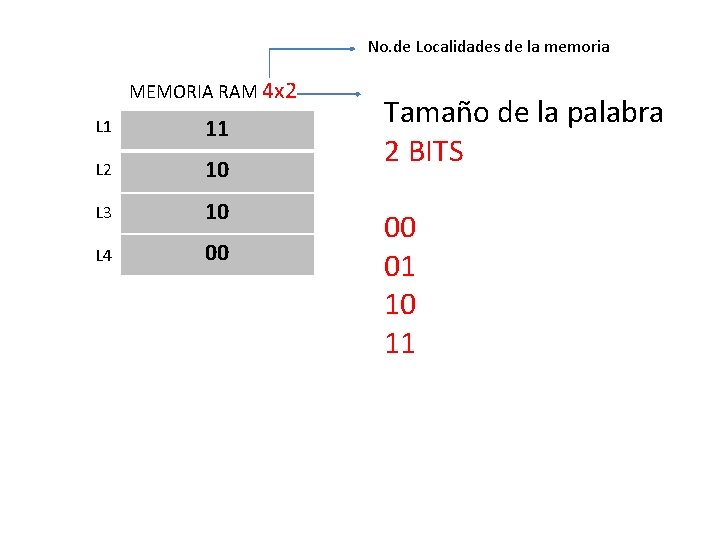

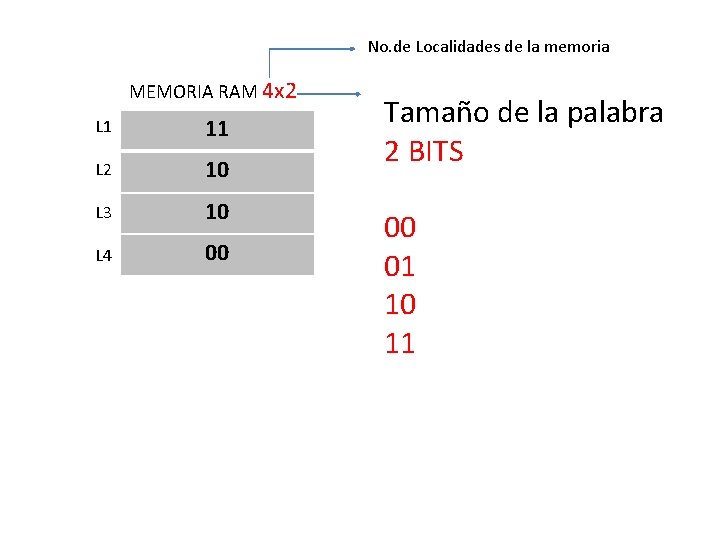

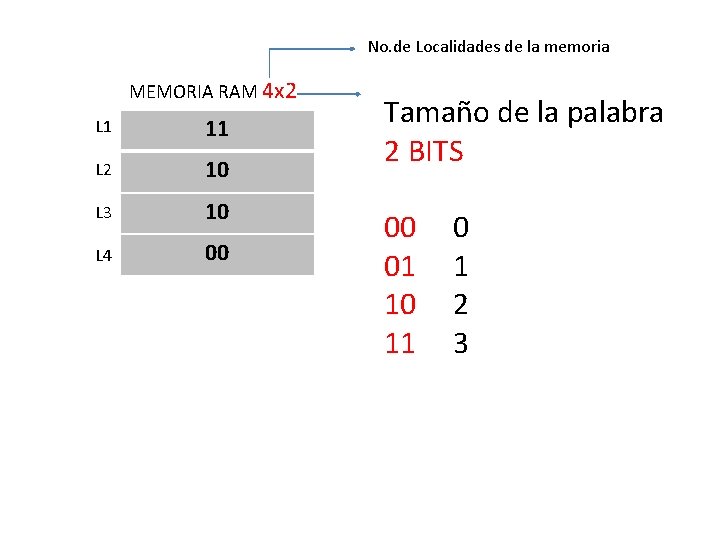

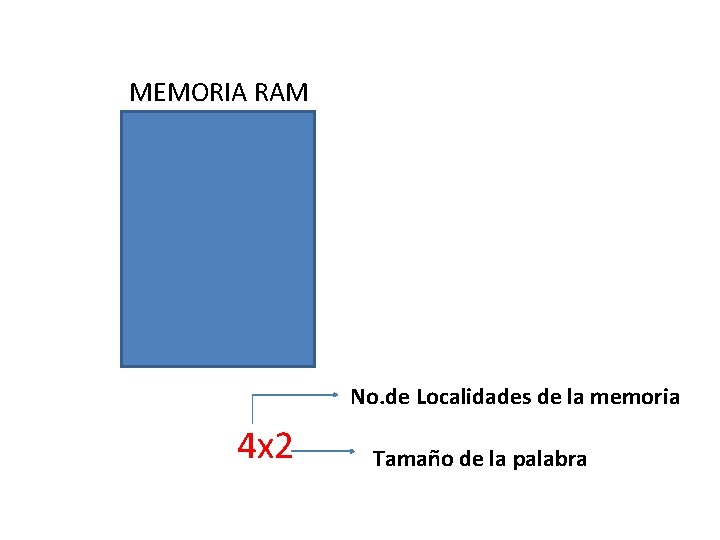

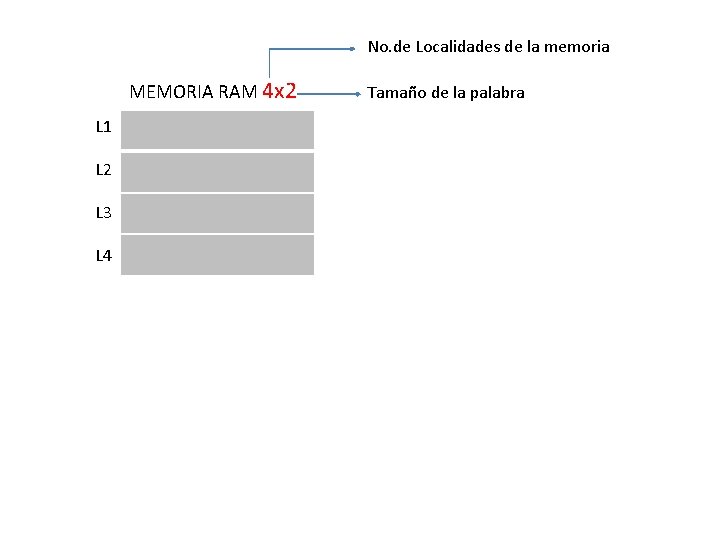

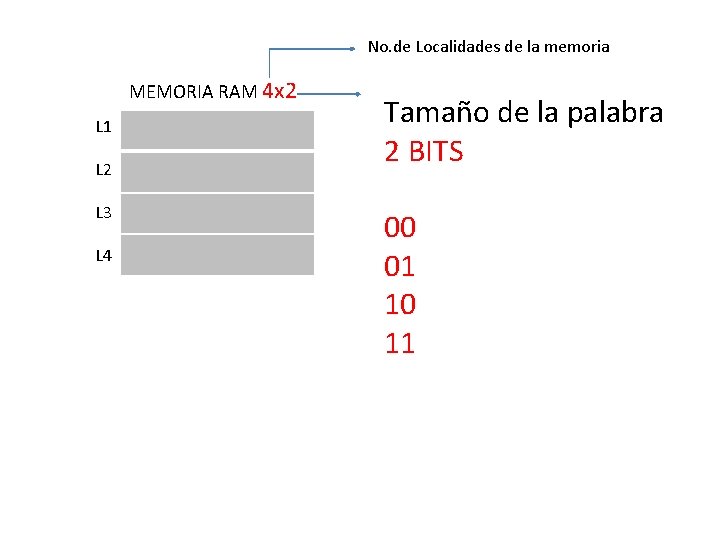

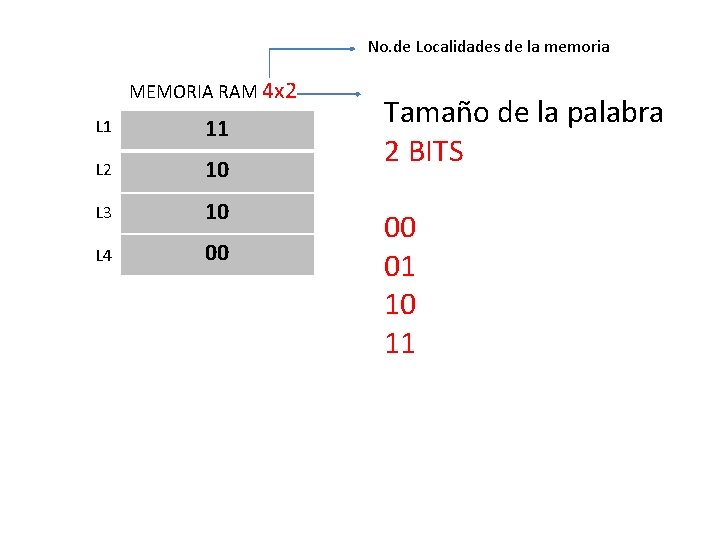

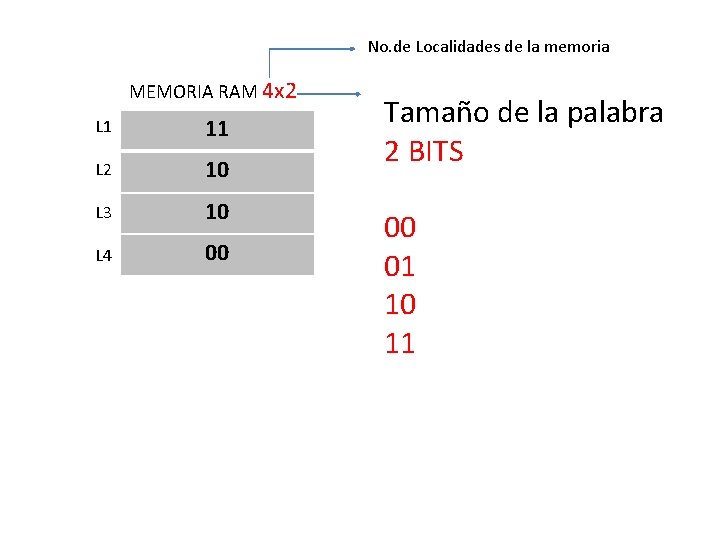

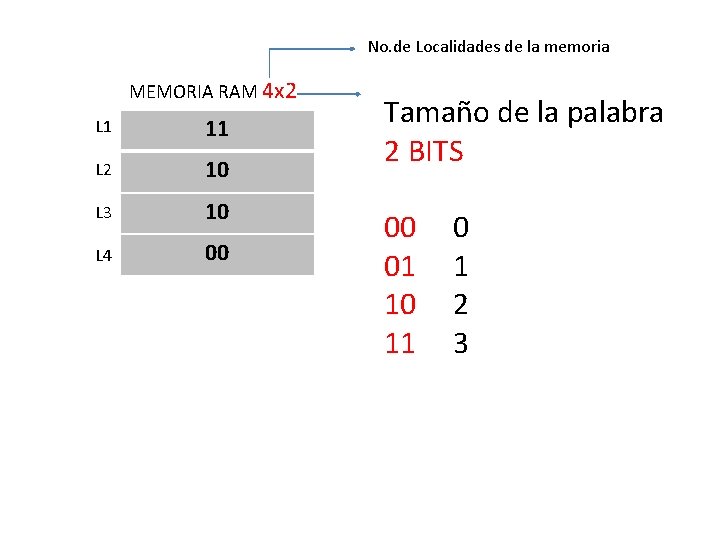

MEMORIA RAM No. de Localidades de la memoria 4 x 2 Tamaño de la palabra

No. de Localidades de la memoria MEMORIA RAM 4 x 2 L 1 L 2 L 3 L 4 Tamaño de la palabra

No. de Localidades de la memoria MEMORIA RAM 4 x 2 L 1 L 2 L 3 L 4 Tamaño de la palabra

No. de Localidades de la memoria MEMORIA RAM 4 x 2 L 1 L 2 L 3 L 4 Tamaño de la palabra 2 BITS 00 01 10 11

No. de Localidades de la memoria MEMORIA RAM 4 x 2 L 1 11 L 2 10 L 3 10 L 4 00 Tamaño de la palabra 2 BITS 00 01 10 11

No. de Localidades de la memoria MEMORIA RAM 4 x 2 L 1 11 L 2 10 L 3 10 L 4 00 Tamaño de la palabra 2 BITS 00 01 10 11

No. de Localidades de la memoria MEMORIA RAM 4 x 2 L 1 11 L 2 10 L 3 10 L 4 00 Tamaño de la palabra 2 BITS 00 01 10 11 0 1 2 3

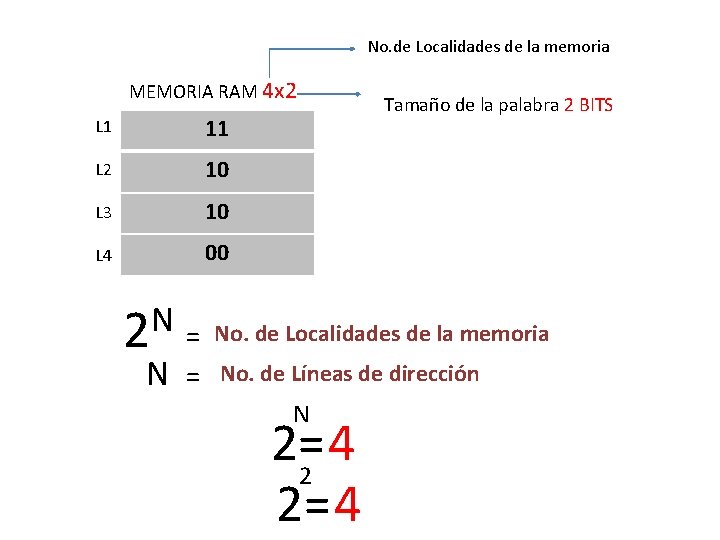

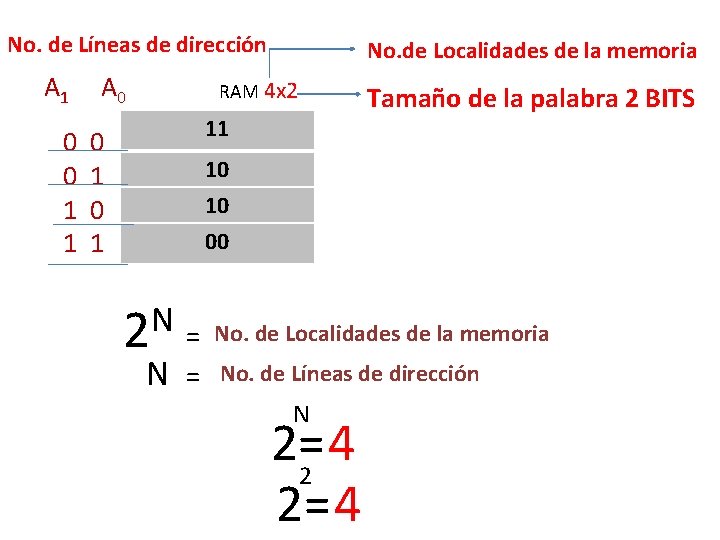

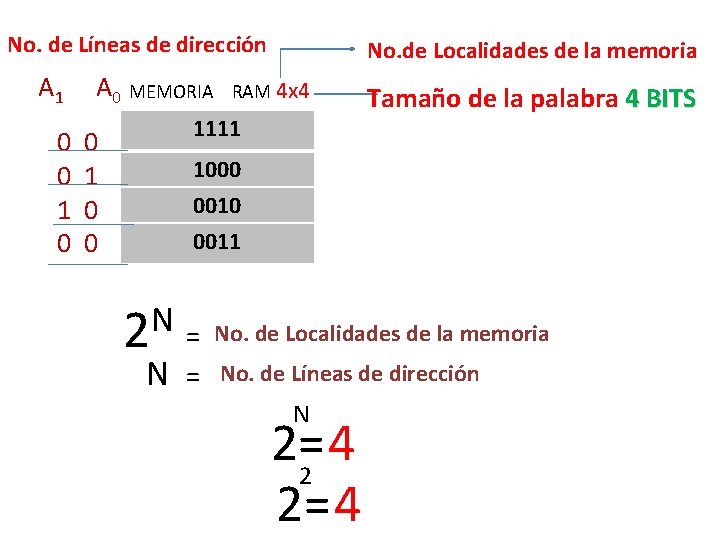

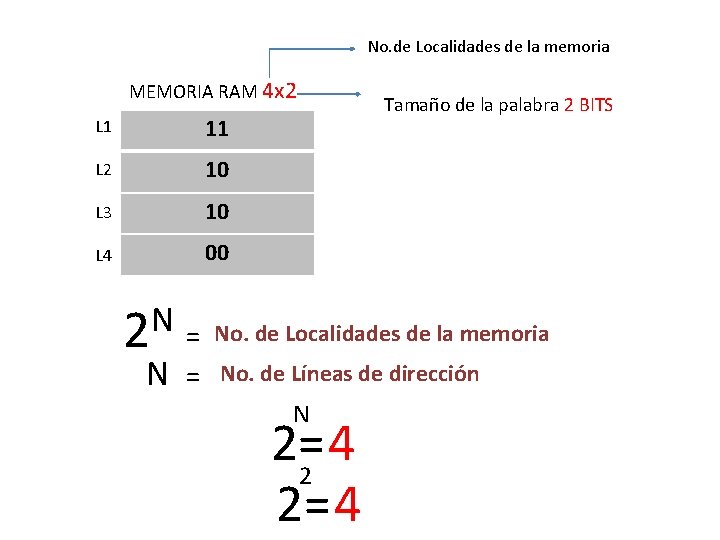

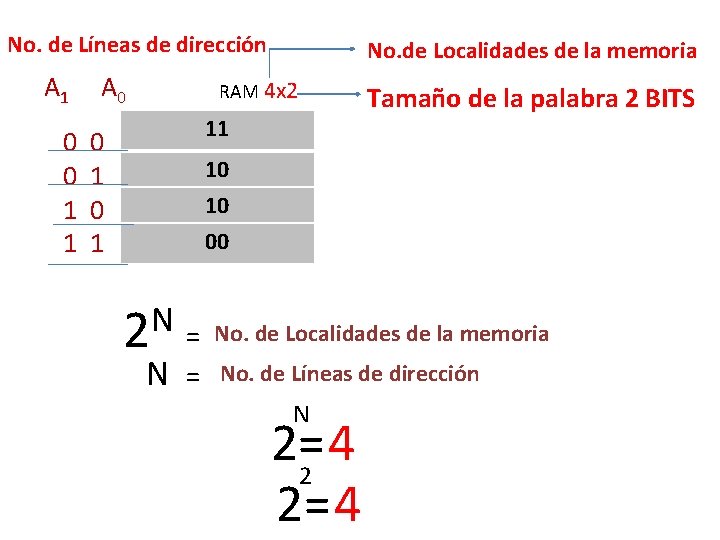

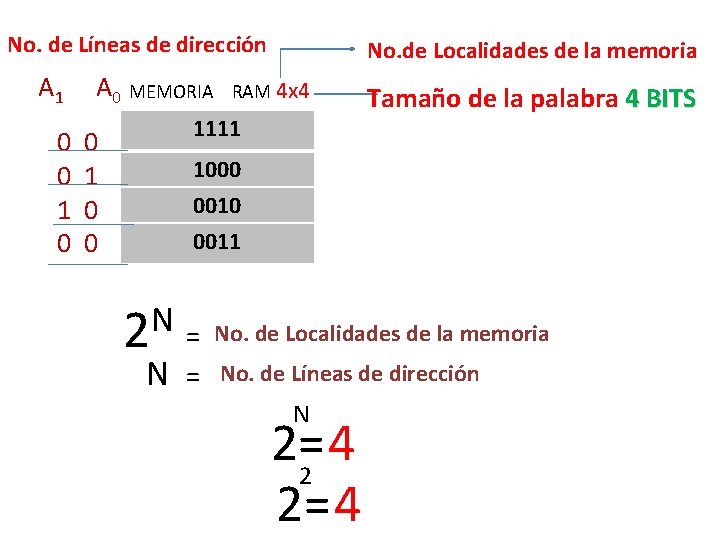

No. de Localidades de la memoria MEMORIA RAM 4 x 2 L 1 11 L 2 10 L 3 10 L 4 00 N 2 N Tamaño de la palabra 2 BITS = No. de Localidades de la memoria = No. de Líneas de dirección N 2=4 2 2=4

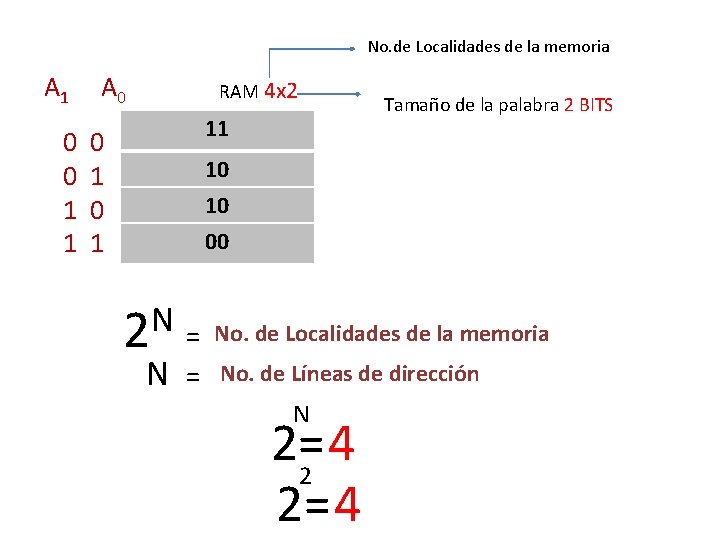

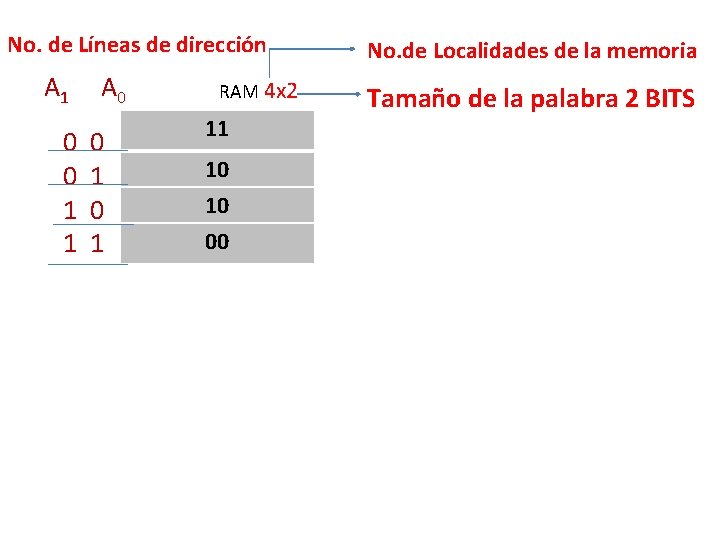

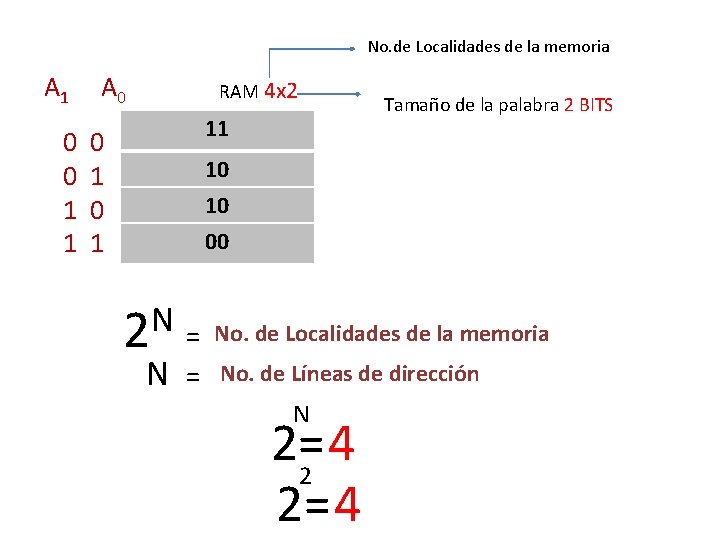

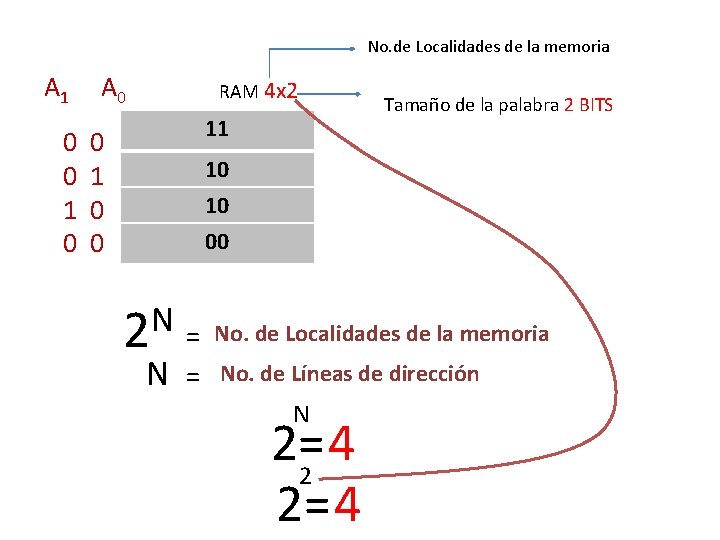

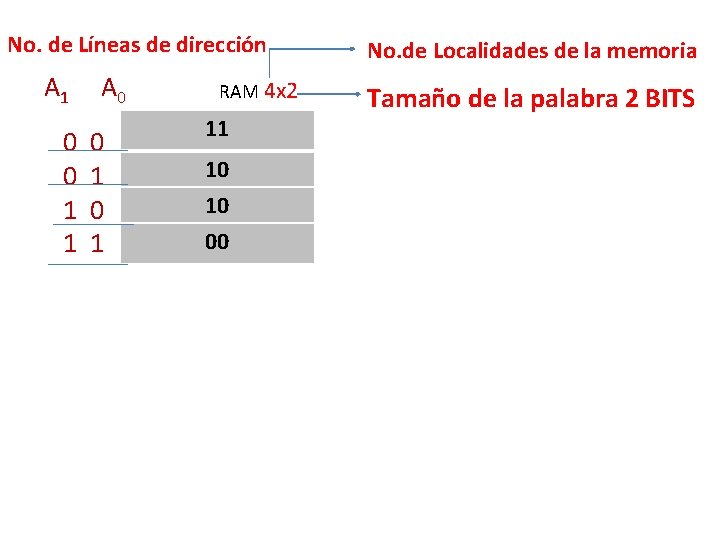

No. de Localidades de la memoria A 1 0 0 1 1 A 0 RAM 4 x 2 11 0 1 Tamaño de la palabra 2 BITS 10 10 00 N 2 N = No. de Localidades de la memoria = No. de Líneas de dirección N 2=4 2 2=4

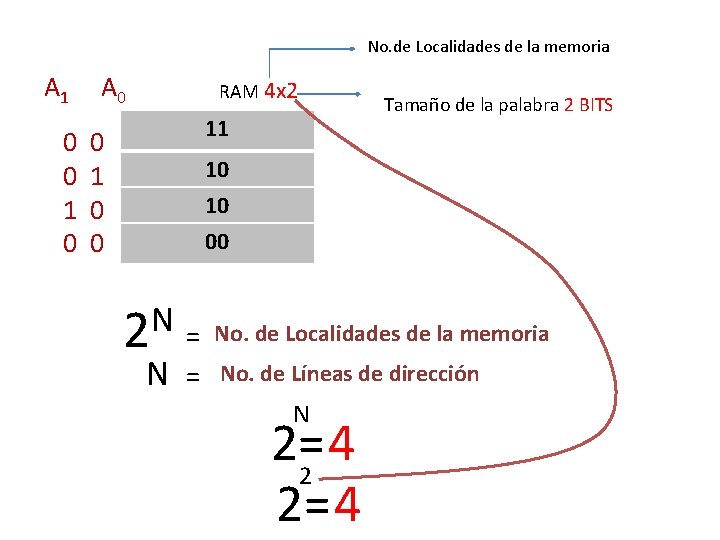

No. de Localidades de la memoria A 1 0 0 1 0 A 0 RAM 4 x 2 11 0 0 Tamaño de la palabra 2 BITS 10 10 00 N 2 N = No. de Localidades de la memoria = No. de Líneas de dirección N 2=4 2 2=4

No. de Líneas de dirección A 1 0 0 1 1 A 0 0 1 RAM 4 x 2 11 10 10 00 No. de Localidades de la memoria Tamaño de la palabra 2 BITS

No. de Líneas de dirección A 1 0 0 1 1 A 0 No. de Localidades de la memoria RAM 4 x 2 11 0 1 Tamaño de la palabra 2 BITS 10 10 00 N 2 N = No. de Localidades de la memoria = No. de Líneas de dirección N 2=4 2 2=4

MEMORIA RAM 8 x 4

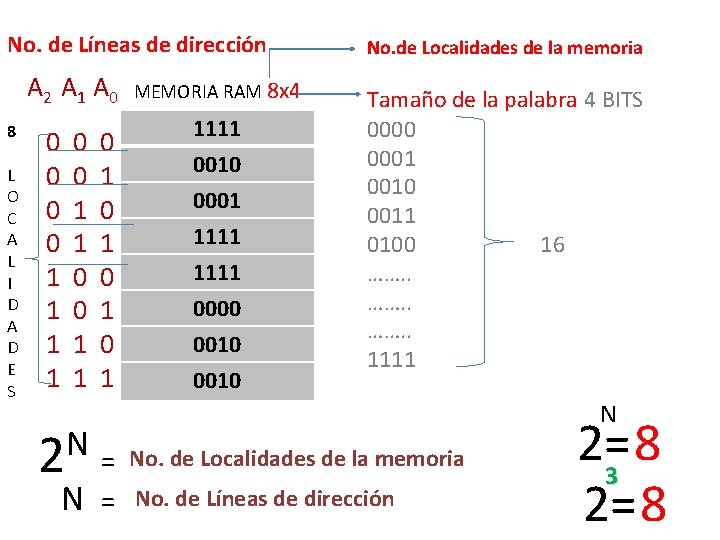

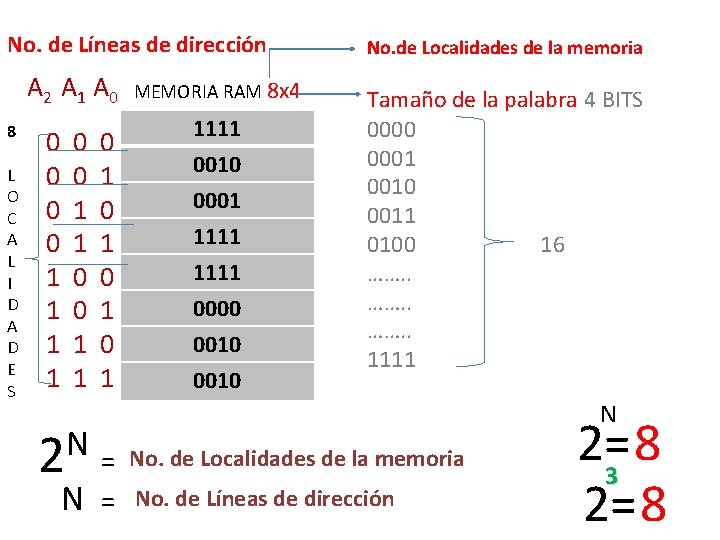

No. de Líneas de dirección A 2 A 1 A 0 8 L O C A L I D A D E S 0 0 1 1 N 2 N 0 1 0 1 MEMORIA RAM 8 x 4 1111 0010 0001 1111 0000 0010 No. de Localidades de la memoria Tamaño de la palabra 4 BITS 0000 0001 0010 0011 0100 16 ……. . 1111 N = No. de Localidades de la memoria = No. de Líneas de dirección 2=8 3 2=8

Buses de comunicación Las unidades que integran el ordenador se comunican a través de los buses; son las líneas eléctricas u ópticas a través de las cuales se comunican las distintas unidades de un ordenador. Los buses son cables por los que circula la información en forma de bits.

Distinguimos tres tipos de buses: Bus de datos. Permite establecer el intercambio de datos entre la CPU y el resto de unidades. Cada instrucción de un programa y cada byte de datos viaja por este bus. El intercambio de datos se realiza a través de un conjunto de líneas eléctricas, una por cada bit, y se transmiten todos a la vez de forma paralela. La velocidad del bus de datos se mide en megahercios (MHz) o gigahercios (GHz).

Bus de datos. Otra de las características de la CPU es el número de bits que transfiere simultáneamente a través de este bus. El tamaño del bus se mide en bits. Las CPU de los primeros PC tenían un bus de 8 bits y solo podían transferir un byte por cada ciclo de reloj. Los actuales micros tienen un bus de datos de 64 bits, con lo que pueden transferir en un ciclo de reloj hasta 8 bytes.

Bus de direcciones. Transmite direcciones entre la CPU y la memoria. El bus de direcciones funciona sincronizado con el de datos. Es el empleado por la CPU para seleccionar la dirección de memoria o el dispositivo de entrada/salida con el cual va a intercambiar información. El bus de direcciones es necesario para conocer las direcciones de los datos que se envían a (o que se reciben desde) la CPU por el bus de datos. .

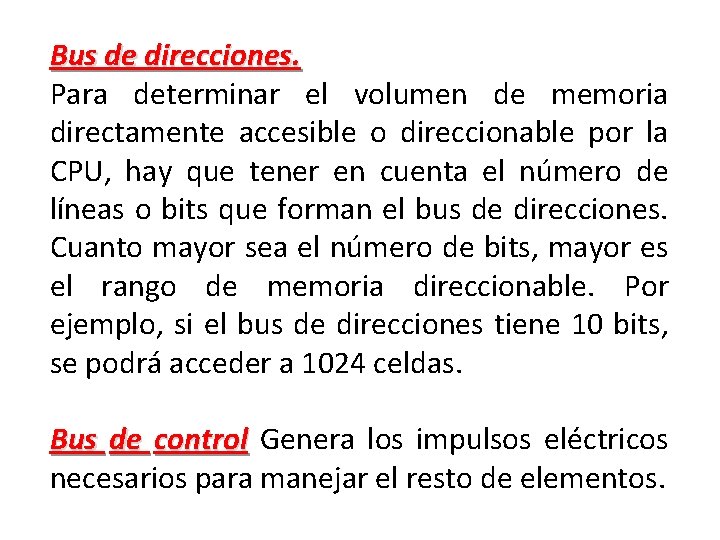

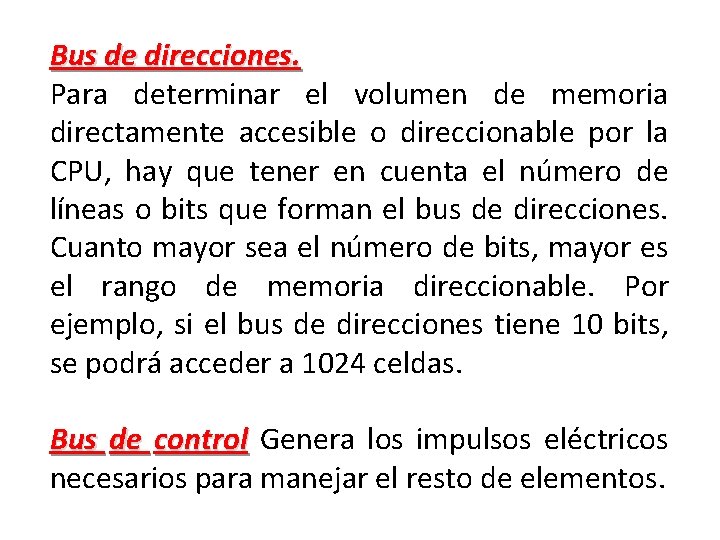

Bus de direcciones. Para determinar el volumen de memoria directamente accesible o direccionable por la CPU, hay que tener en cuenta el número de líneas o bits que forman el bus de direcciones. Cuanto mayor sea el número de bits, mayor es el rango de memoria direccionable. Por ejemplo, si el bus de direcciones tiene 10 bits, se podrá acceder a 1024 celdas. Bus de control Genera los impulsos eléctricos necesarios para manejar el resto de elementos.

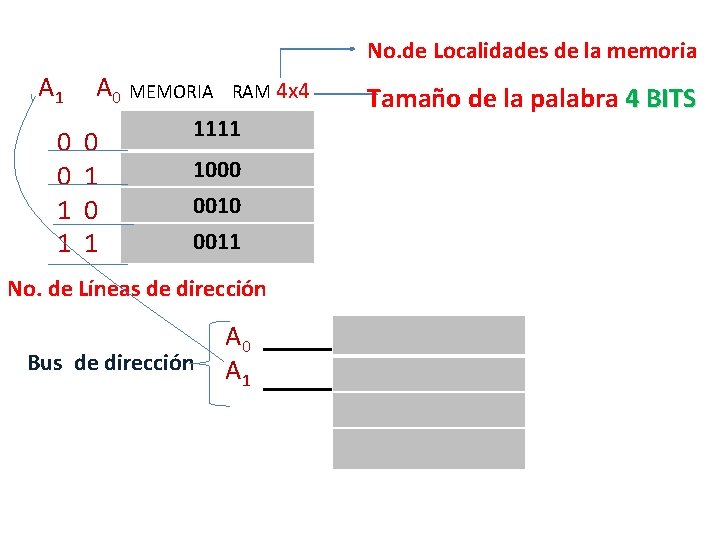

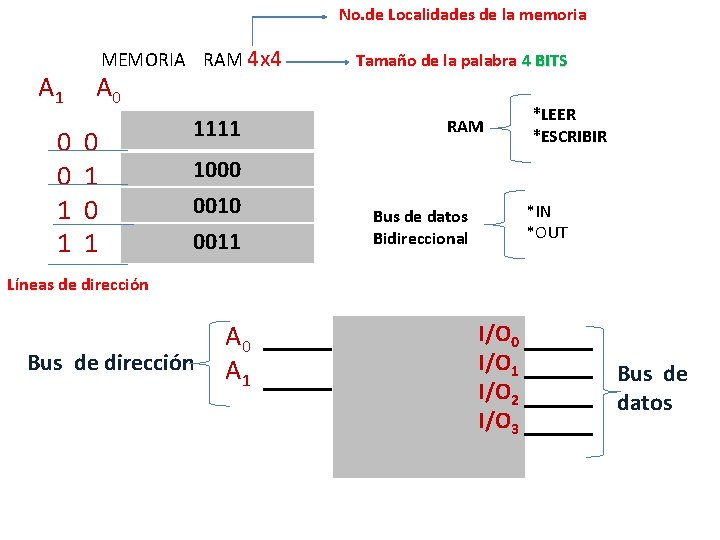

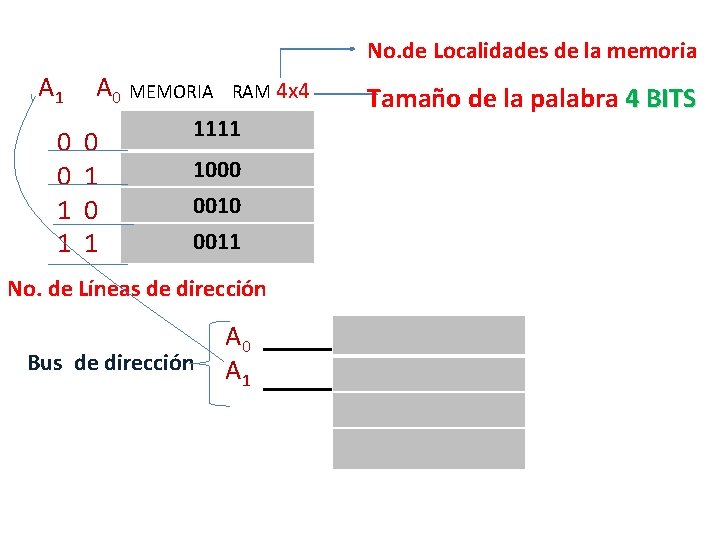

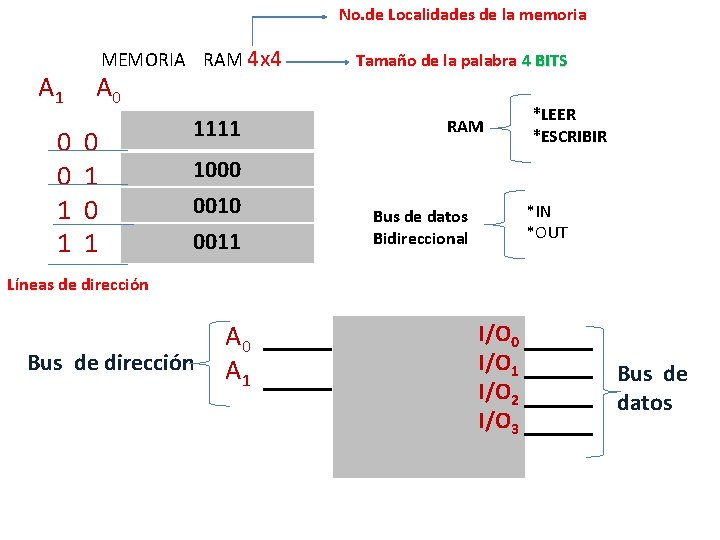

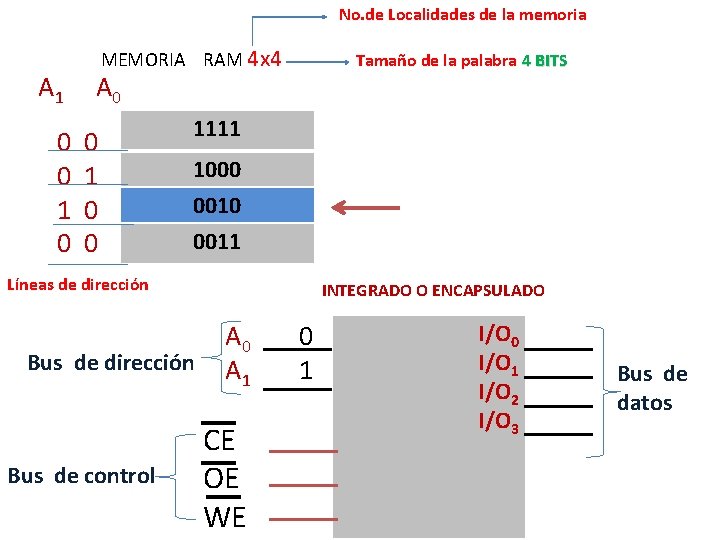

No. de Líneas de dirección A 1 0 0 1 0 A 0 MEMORIA No. de Localidades de la memoria RAM 4 x 4 1111 0 0 Tamaño de la palabra 4 BITS 1000 0011 N 2 N = No. de Localidades de la memoria = No. de Líneas de dirección N 2=4 2 2=4

No. de Localidades de la memoria A 1 0 0 1 1 A 0 MEMORIA 0 1 RAM 4 x 4 1111 1000 0011 No. de Líneas de dirección Bus de dirección A 0 A 1 Tamaño de la palabra 4 BITS

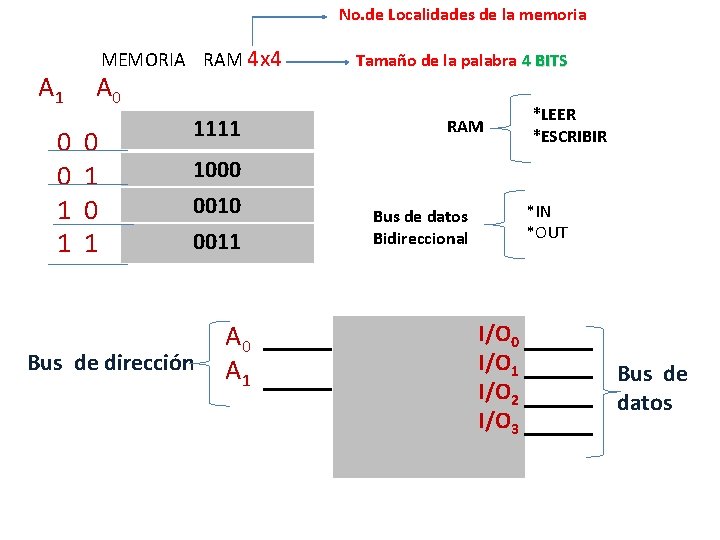

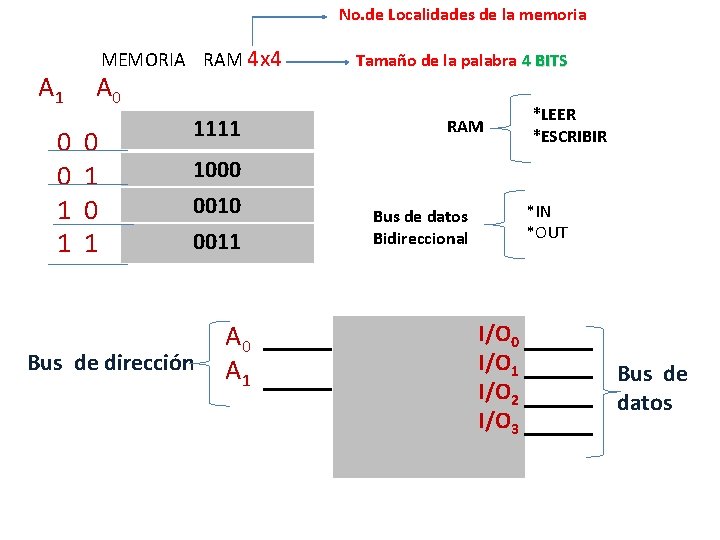

No. de Localidades de la memoria A 1 0 0 1 1 MEMORIA RAM 4 x 4 A 0 0 1 1111 Tamaño de la palabra 4 BITS RAM *LEER *ESCRIBIR 1000 0011 Bus de dirección A 0 A 1 *IN *OUT Bus de datos Bidireccional I/O 0 I/O 1 I/O 2 I/O 3 Bus de datos

No. de Localidades de la memoria A 1 0 0 1 1 MEMORIA RAM 4 x 4 A 0 0 1 1111 Tamaño de la palabra 4 BITS RAM *LEER *ESCRIBIR 1000 0011 *IN *OUT Bus de datos Bidireccional Líneas de dirección Bus de dirección A 0 A 1 I/O 0 I/O 1 I/O 2 I/O 3 Bus de datos

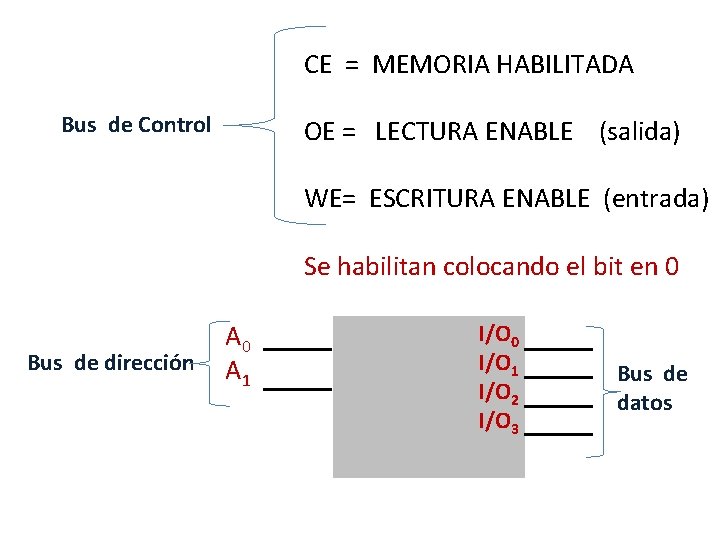

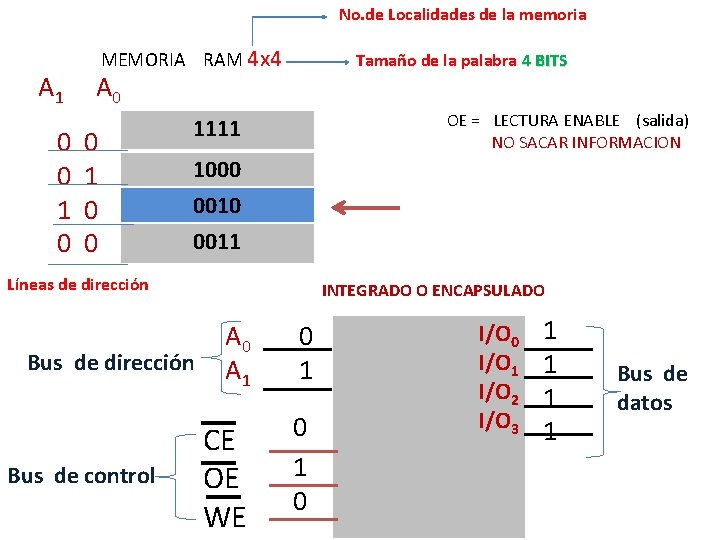

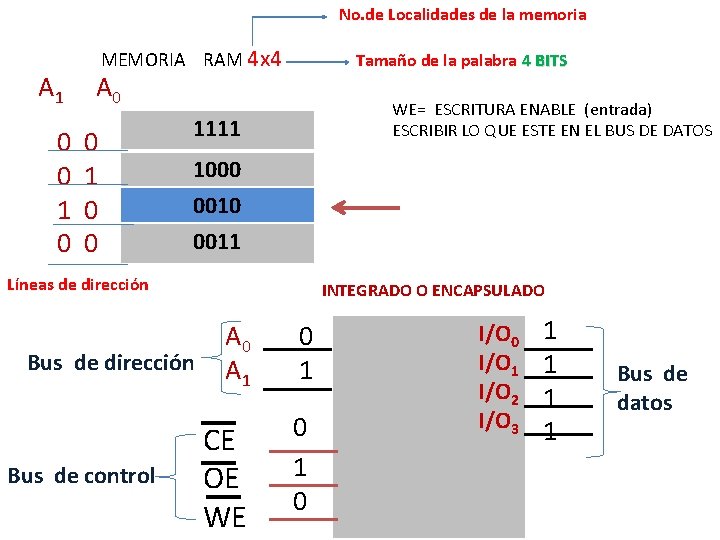

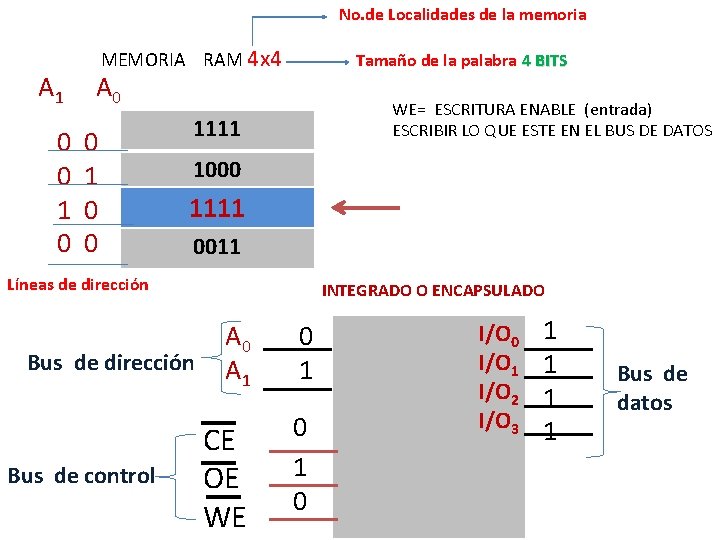

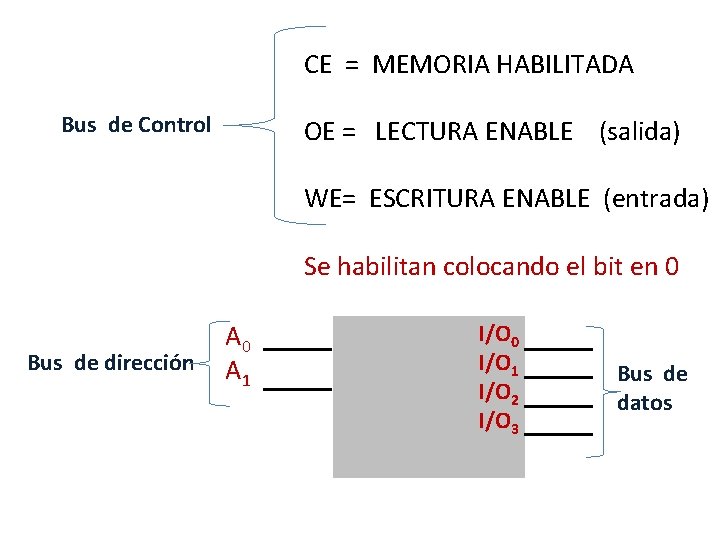

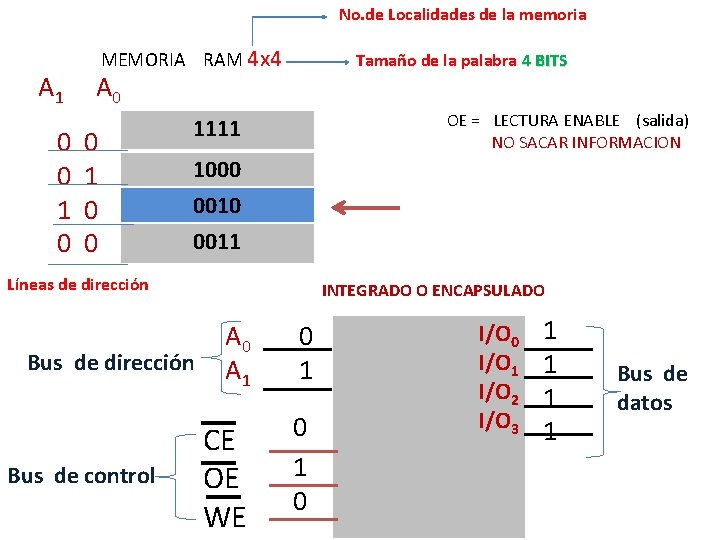

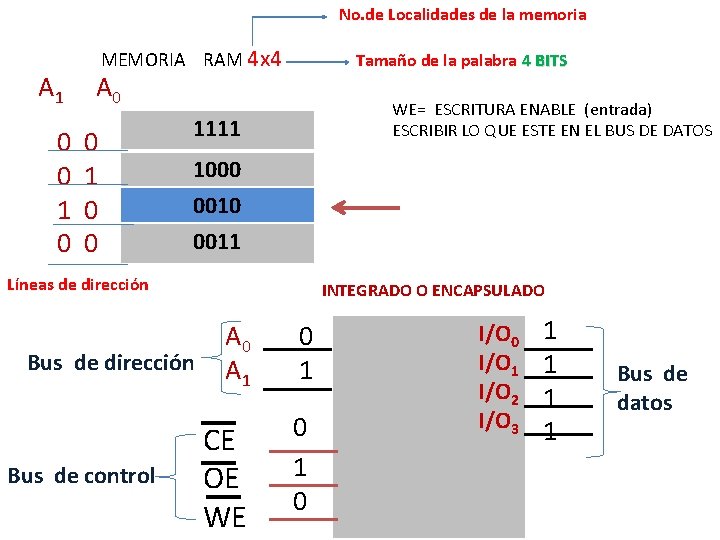

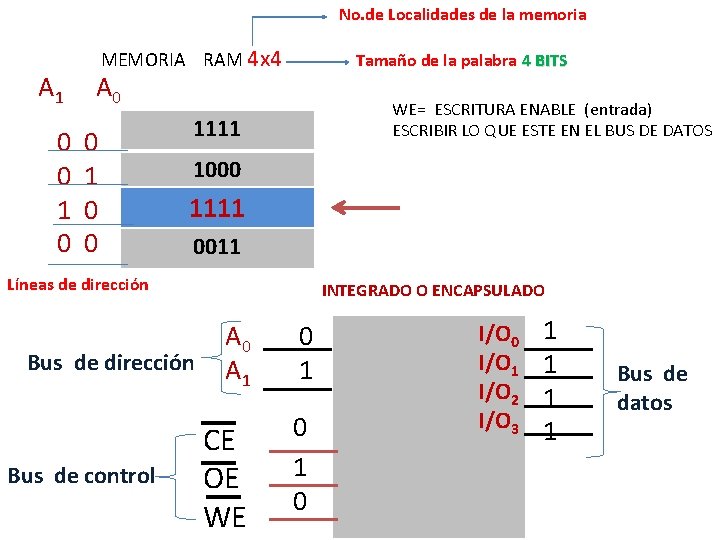

CE = MEMORIA HABILITADA Bus de Control OE = LECTURA ENABLE (salida) WE= ESCRITURA ENABLE (entrada) Se habilitan colocando el bit en 0 Bus de dirección A 0 A 1 I/O 0 I/O 1 I/O 2 I/O 3 Bus de datos

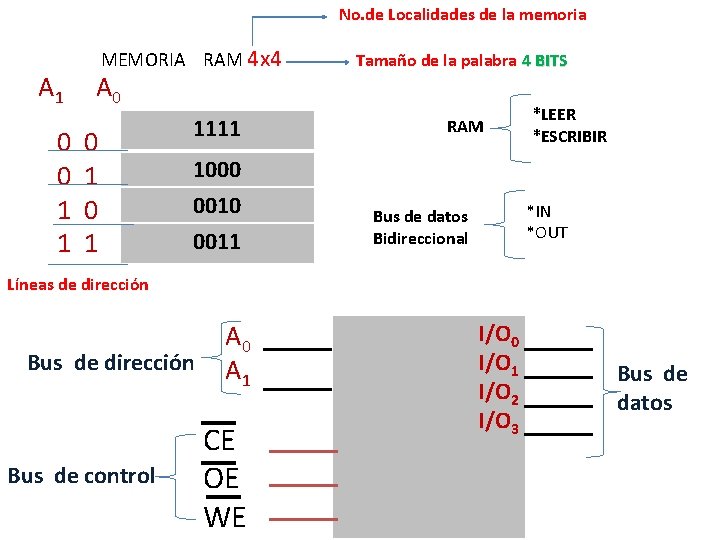

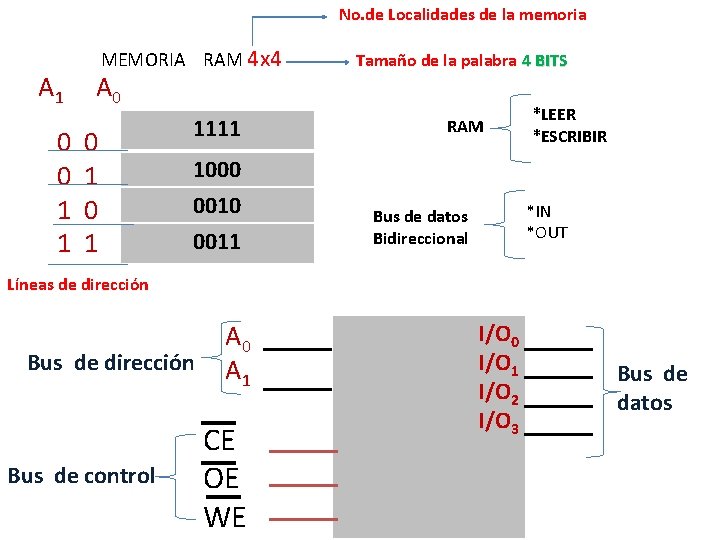

No. de Localidades de la memoria A 1 0 0 1 1 MEMORIA RAM 4 x 4 A 0 0 1 1111 Tamaño de la palabra 4 BITS RAM *LEER *ESCRIBIR 1000 0011 *IN *OUT Bus de datos Bidireccional Líneas de dirección Bus de control A 0 A 1 CE OE WE I/O 0 I/O 1 I/O 2 I/O 3 Bus de datos

No. de Localidades de la memoria A 1 0 0 1 0 MEMORIA RAM 4 x 4 Tamaño de la palabra 4 BITS A 0 0 1111 1000 0011 Líneas de dirección Bus de control INTEGRADO O ENCAPSULADO A 0 A 1 CE OE WE 0 1 I/O 0 I/O 1 I/O 2 I/O 3 Bus de datos

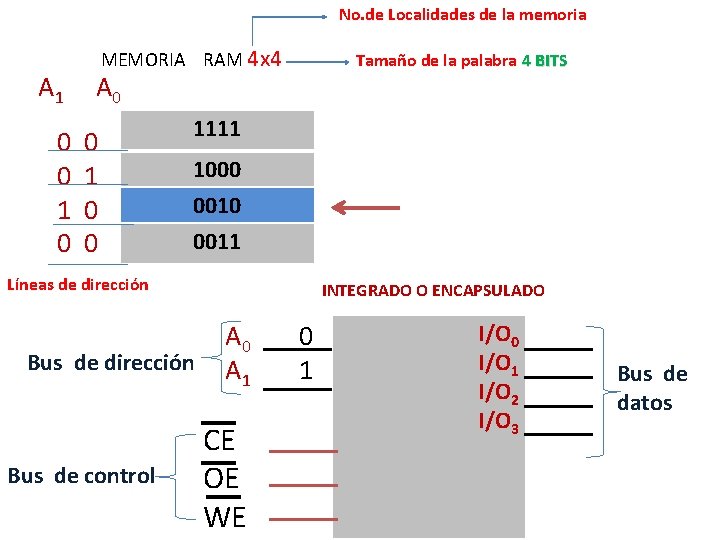

No. de Localidades de la memoria A 1 0 0 1 0 MEMORIA RAM 4 x 4 Tamaño de la palabra 4 BITS A 0 0 1 0 0 OE = LECTURA ENABLE (salida) NO SACAR INFORMACION 1111 1000 0011 Líneas de dirección Bus de control INTEGRADO O ENCAPSULADO A 0 A 1 0 1 CE OE WE 0 1 0 I/O 0 1 I/O 1 1 I/O 2 1 I/O 3 1 Bus de datos

No. de Localidades de la memoria A 1 0 0 1 0 MEMORIA RAM 4 x 4 Tamaño de la palabra 4 BITS A 0 0 1 0 0 WE= ESCRITURA ENABLE (entrada) ESCRIBIR LO QUE ESTE EN EL BUS DE DATOS 1111 1000 0011 Líneas de dirección Bus de control INTEGRADO O ENCAPSULADO A 0 A 1 0 1 CE OE WE 0 1 0 I/O 0 1 I/O 1 1 I/O 2 1 I/O 3 1 Bus de datos

No. de Localidades de la memoria A 1 0 0 1 0 MEMORIA RAM 4 x 4 Tamaño de la palabra 4 BITS A 0 0 1 0 0 WE= ESCRITURA ENABLE (entrada) ESCRIBIR LO QUE ESTE EN EL BUS DE DATOS 1111 1000 1111 0011 Líneas de dirección Bus de control INTEGRADO O ENCAPSULADO A 0 A 1 0 1 CE OE WE 0 1 0 I/O 0 1 I/O 1 1 I/O 2 1 I/O 3 1 Bus de datos

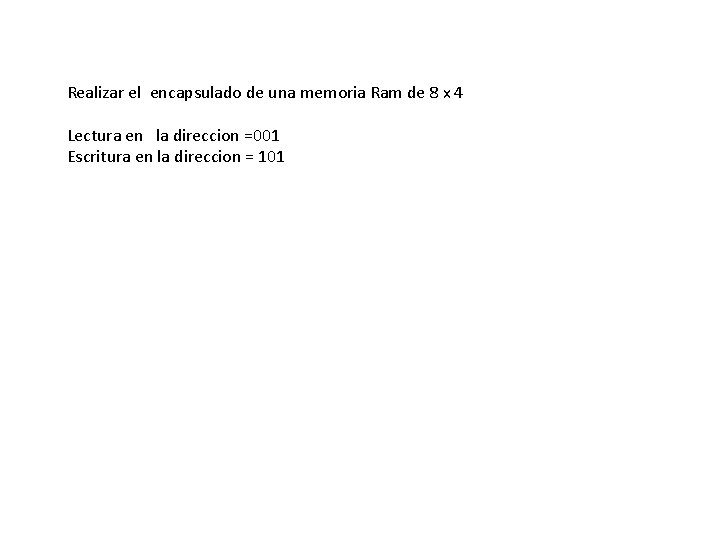

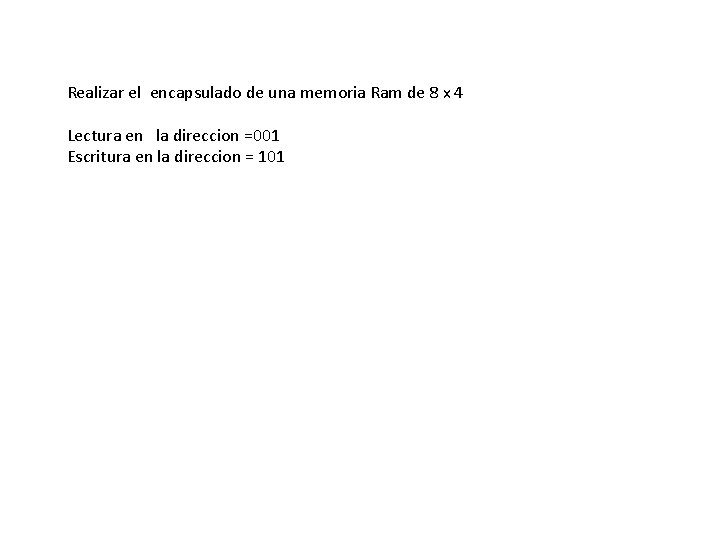

Realizar el encapsulado de una memoria Ram de 8 x 4 Lectura en la direccion =001 Escritura en la direccion = 101