MEMORI INTERNAL Karakteristik Sistem Memori Lokasi Kapasitas Satuan

- Slides: 43

MEMORI INTERNAL

Karakteristik Sistem Memori Lokasi Kapasitas Satuan transfer Metode pengaksesan Unjuk kerja Karakteristik fisik

Karakteristik: Lokasi Memori Eksternal n Terdiri dari perangkat storage peripheral yang dapat diakses oleh CPU melalui modul I/O Memori Internal n Terdiri dari Register, Cache Memory, ROM dan RAM

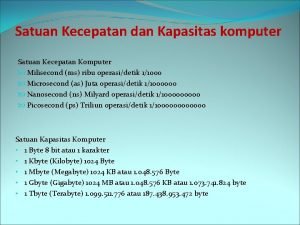

Karakterisitik: Kapasitas Memori internal biasanya dinyatakan dalam byte atau word n n 1 byte = 8 bit 1 word = 8, 16, atau 32 bit Memori eksternal biasanya dinyatakan dalam byte

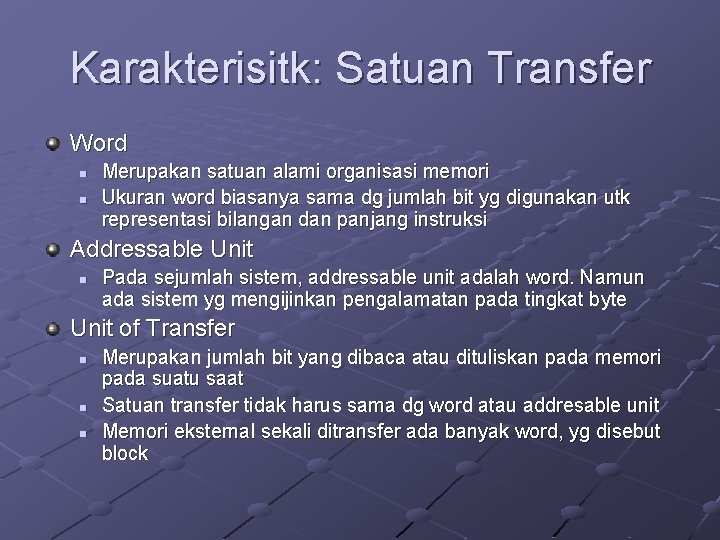

Karakterisitk: Satuan Transfer Word n n Merupakan satuan alami organisasi memori Ukuran word biasanya sama dg jumlah bit yg digunakan utk representasi bilangan dan panjang instruksi Addressable Unit n Pada sejumlah sistem, addressable unit adalah word. Namun ada sistem yg mengijinkan pengalamatan pada tingkat byte Unit of Transfer n n n Merupakan jumlah bit yang dibaca atau dituliskan pada memori pada suatu saat Satuan transfer tidak harus sama dg word atau addresable unit Memori eksternal sekali ditransfer ada banyak word, yg disebut block

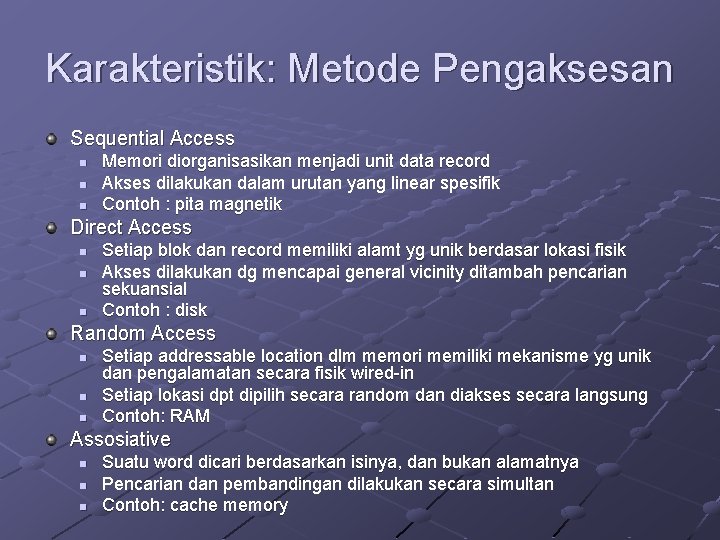

Karakteristik: Metode Pengaksesan Sequential Access n n n Memori diorganisasikan menjadi unit data record Akses dilakukan dalam urutan yang linear spesifik Contoh : pita magnetik Direct Access n n n Setiap blok dan record memiliki alamt yg unik berdasar lokasi fisik Akses dilakukan dg mencapai general vicinity ditambah pencarian sekuansial Contoh : disk Random Access n n n Setiap addressable location dlm memori memiliki mekanisme yg unik dan pengalamatan secara fisik wired-in Setiap lokasi dpt dipilih secara random dan diakses secara langsung Contoh: RAM Assosiative n n n Suatu word dicari berdasarkan isinya, dan bukan alamatnya Pencarian dan pembandingan dilakukan secara simultan Contoh: cache memory

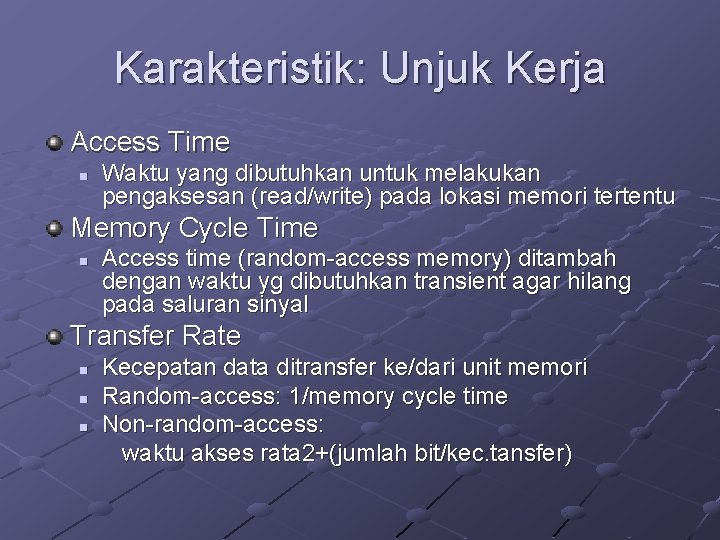

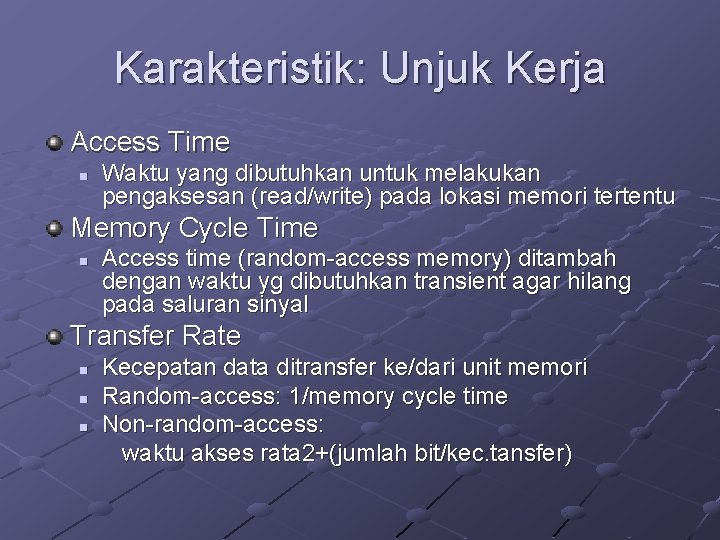

Karakteristik: Unjuk Kerja Access Time n Waktu yang dibutuhkan untuk melakukan pengaksesan (read/write) pada lokasi memori tertentu Memory Cycle Time n Access time (random-access memory) ditambah dengan waktu yg dibutuhkan transient agar hilang pada saluran sinyal Transfer Rate n n n Kecepatan data ditransfer ke/dari unit memori Random-access: 1/memory cycle time Non-random-access: waktu akses rata 2+(jumlah bit/kec. tansfer)

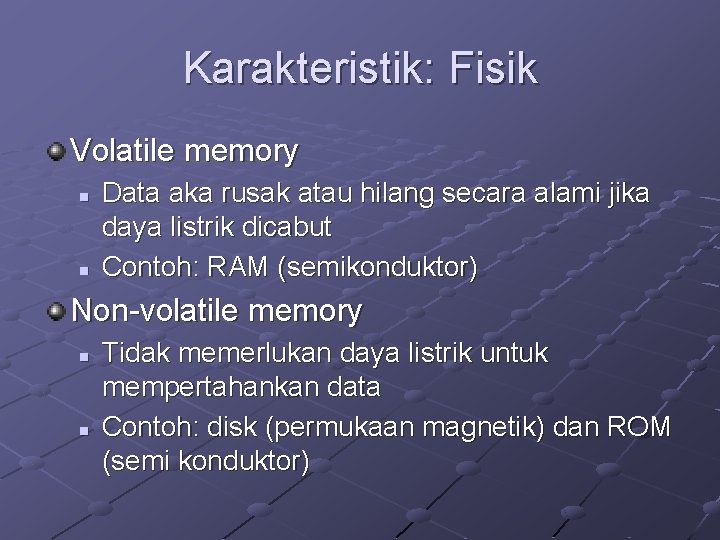

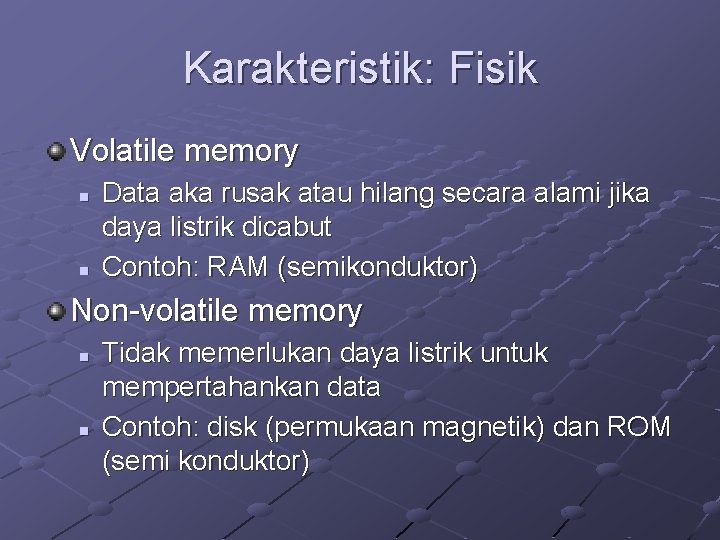

Karakteristik: Fisik Volatile memory n n Data aka rusak atau hilang secara alami jika daya listrik dicabut Contoh: RAM (semikonduktor) Non-volatile memory n n Tidak memerlukan daya listrik untuk mempertahankan data Contoh: disk (permukaan magnetik) dan ROM (semi konduktor)

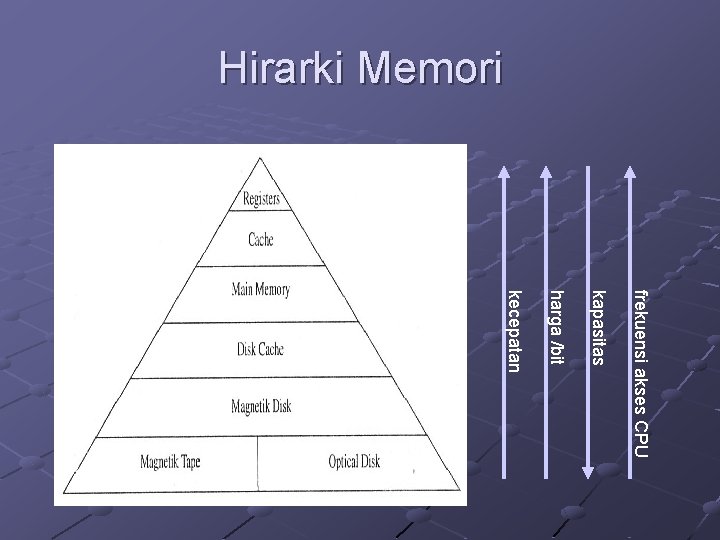

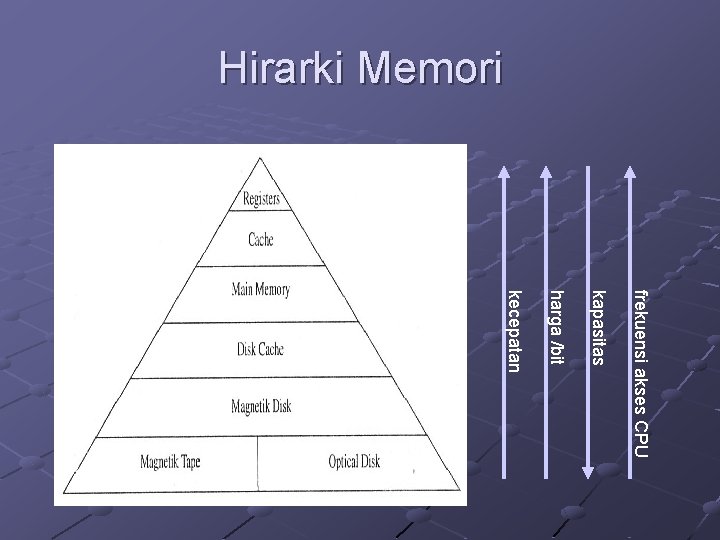

Hirarki Memori frekuensi akses CPU kapasitas harga /bit kecepatan

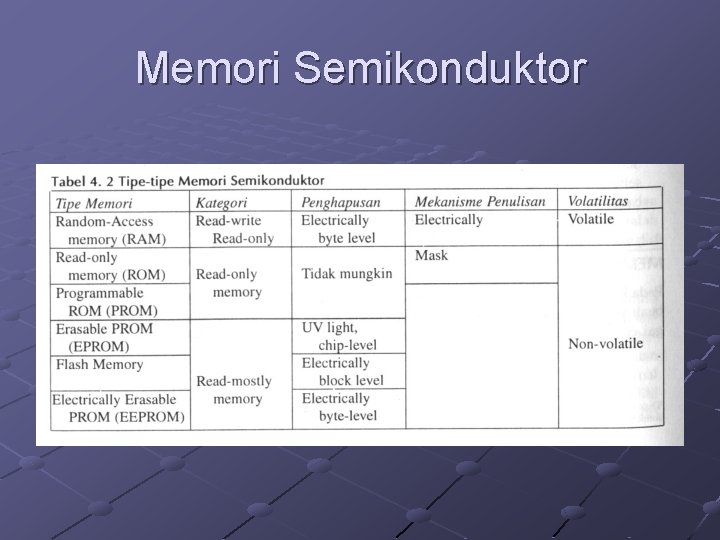

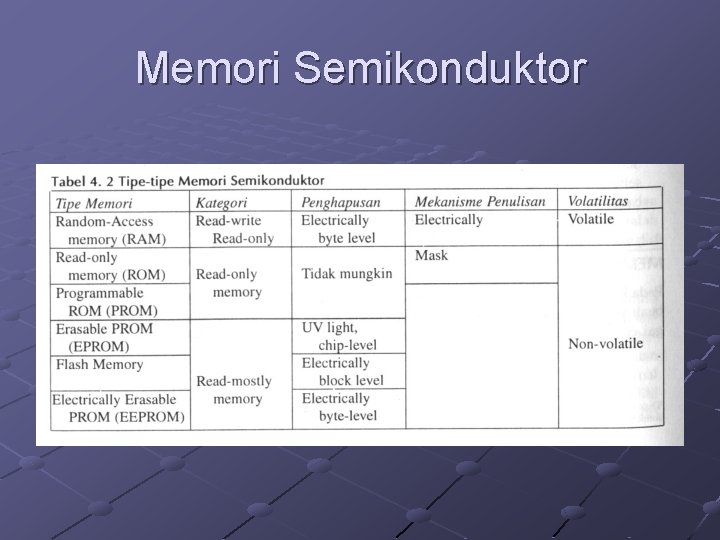

Memori Semikonduktor

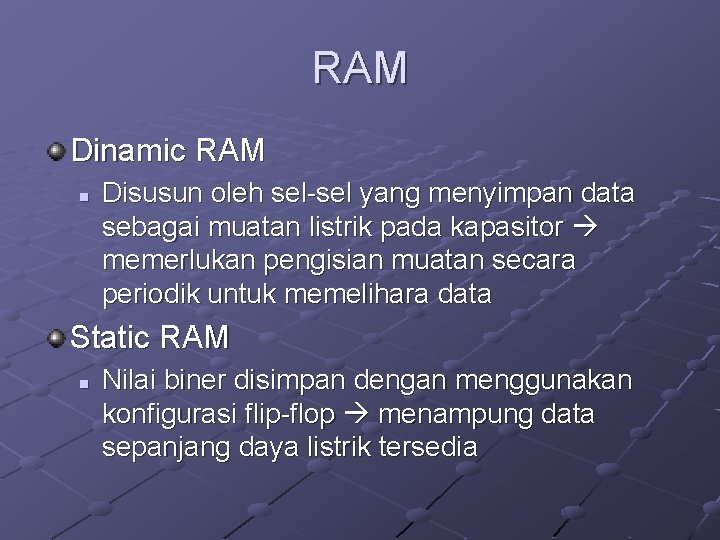

RAM Dinamic RAM n Disusun oleh sel-sel yang menyimpan data sebagai muatan listrik pada kapasitor memerlukan pengisian muatan secara periodik untuk memelihara data Static RAM n Nilai biner disimpan dengan menggunakan konfigurasi flip-flop menampung data sepanjang daya listrik tersedia

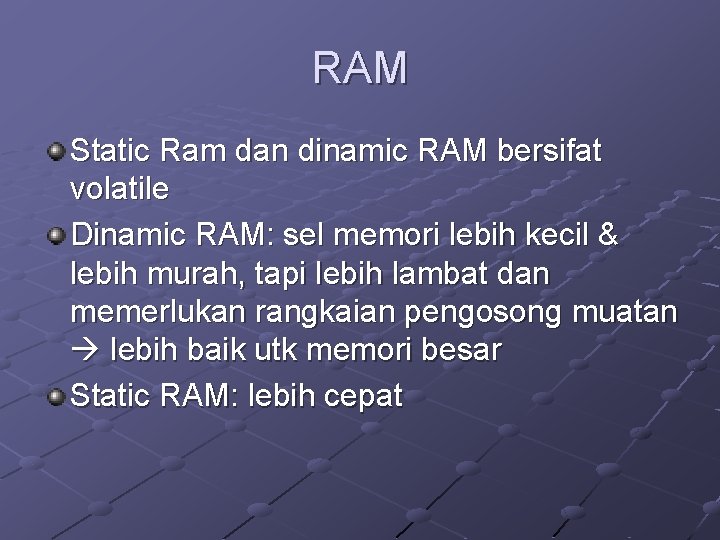

RAM Static Ram dan dinamic RAM bersifat volatile Dinamic RAM: sel memori lebih kecil & lebih murah, tapi lebih lambat dan memerlukan rangkaian pengosong muatan lebih baik utk memori besar Static RAM: lebih cepat

ROM Berisi data permanen yang tidak dapat diubah Biasanya diisi library subroutines yg sering digunakan dan program sistem Keuntungan ROM adalah data atau program secara permanen ada di memori utama dan tidak perlu dimuat ke penyimpan sekunder

Jenis ROM n Isi dibuat oleh pabrik PROM (Programmable ROM) n n Dapat ditulisi satu kali Pengguna dapat melakukan proses penulisan secara elektris dengan peralatan khusus EPROM (Erasable Programmable ROM) n Dapat ditulisi secara elektris dan dihapus (kosong) dengan radiasi sinar ultra violet dapat berulang kali EEPROM (Electrically Erasable Programmable ROM) n ROM yg dapat ditulisi kapan saja tanpa menghapus isi sebelumnya (hanya byte tertentu yg du-update)

Flash Memory bersifat non-volatile dapat dihapus dan diisi ulang secara cepat dimungkinkan penghapusan blok memori, tetapi tidak sampai tingkat byte banyak digunakan untuk USB flash disk, memori pada kamera digital dan handphone

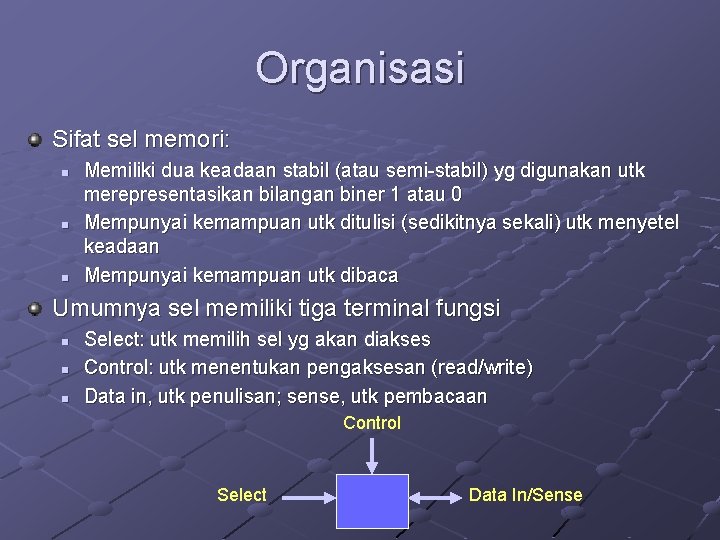

Organisasi Sifat sel memori: n n n Memiliki dua keadaan stabil (atau semi-stabil) yg digunakan utk merepresentasikan bilangan biner 1 atau 0 Mempunyai kemampuan utk ditulisi (sedikitnya sekali) utk menyetel keadaan Mempunyai kemampuan utk dibaca Umumnya sel memiliki tiga terminal fungsi n n n Select: utk memilih sel yg akan diakses Control: utk menentukan pengaksesan (read/write) Data in, utk penulisan; sense, utk pembacaan Control Select Data In/Sense

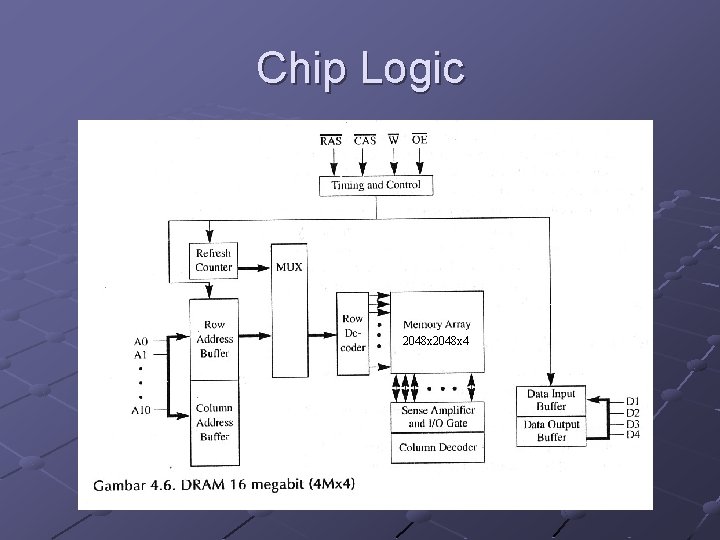

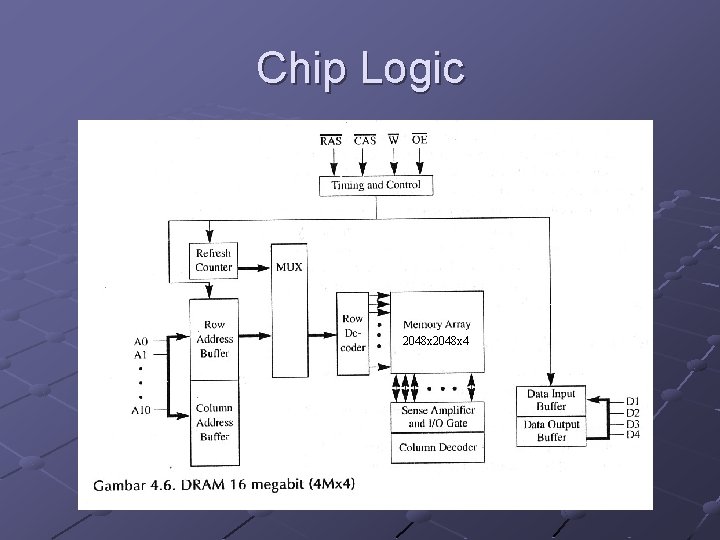

Chip Logic 2048 x 4

Chip Logic Elemen-elemen array dihubungkan dg saluran horizontal (baris) dan vertikal (kolom). Setiap saluran vertikal terhubung ke terminal Data-In/Sense Saluran alamat memberikan alamat word yg dipilih. Diperlukan 11 saluran utk memilih salah satu dr 2048 (=211) baris. 11 saluran lain utk menentukan kolom (4 -bit per kolom). Penggunaan alamat utk baris dan kolom ditentukan dg mengatur sinyal RAS (Row Address Select) dan CAS (Column Address Select) 4 saluran data digunakan utk input dan output 4 -bit ke/dari buffer hrs ada beberapa DRAM utk baca/tulis word

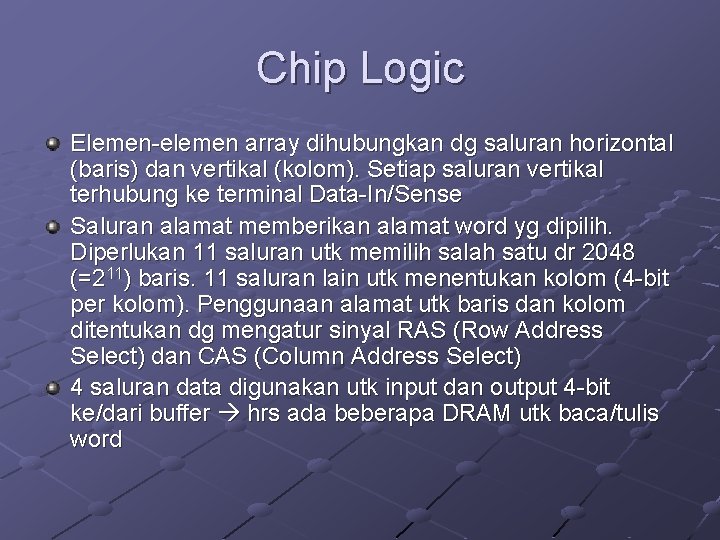

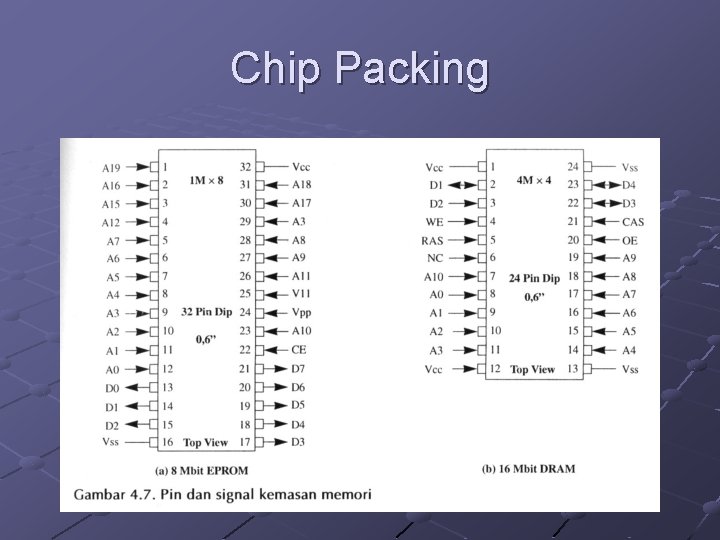

Chip Packing

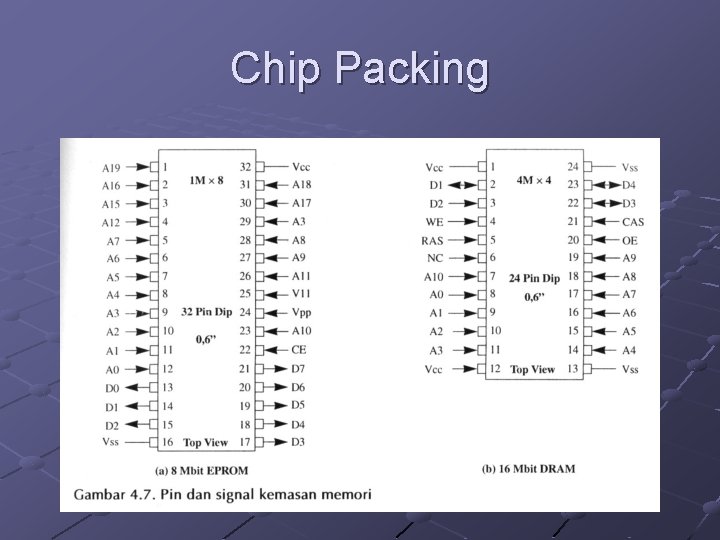

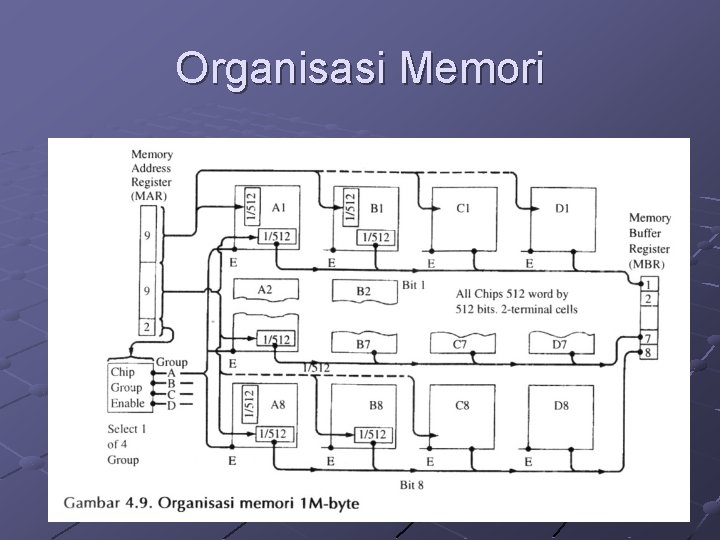

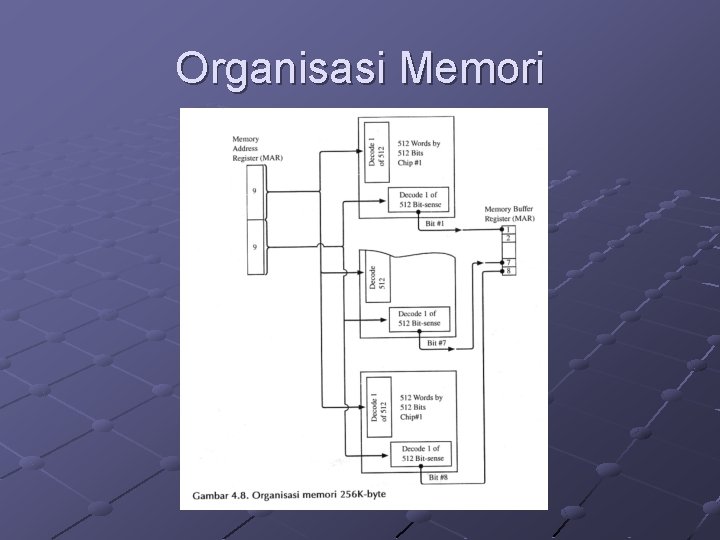

Organisasi Memori

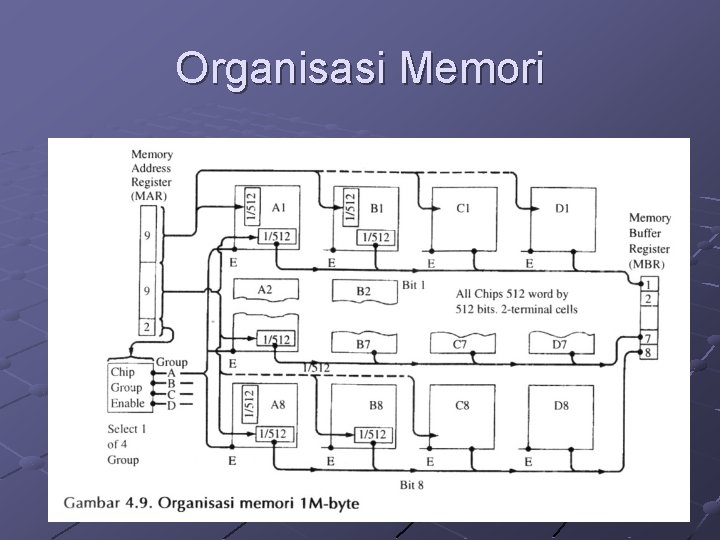

Organisasi Memori

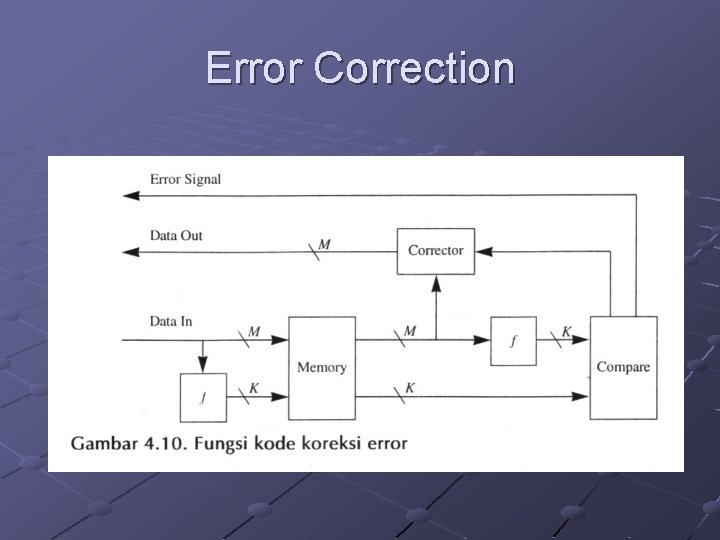

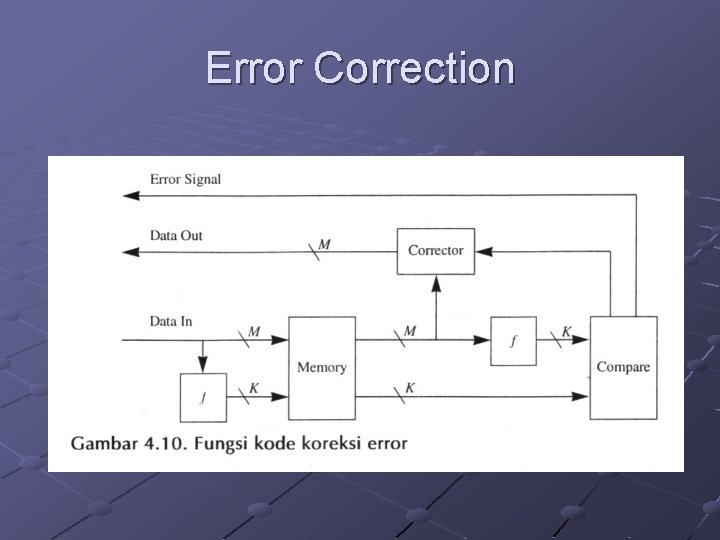

Error Correction

CACHE MEMORY

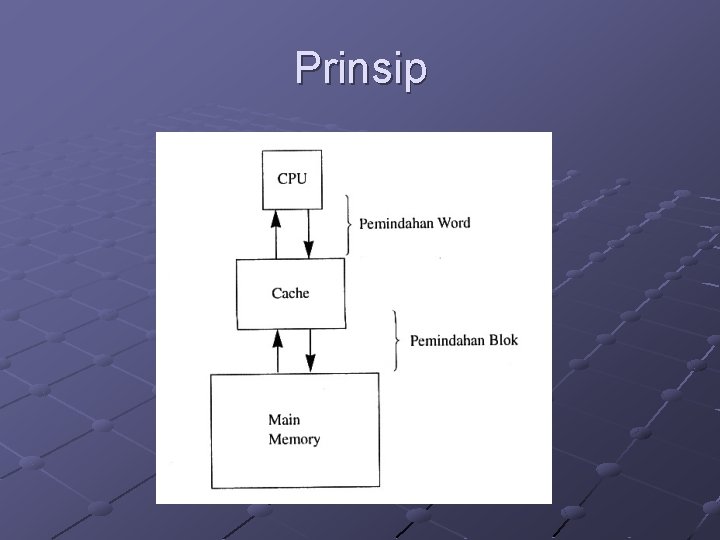

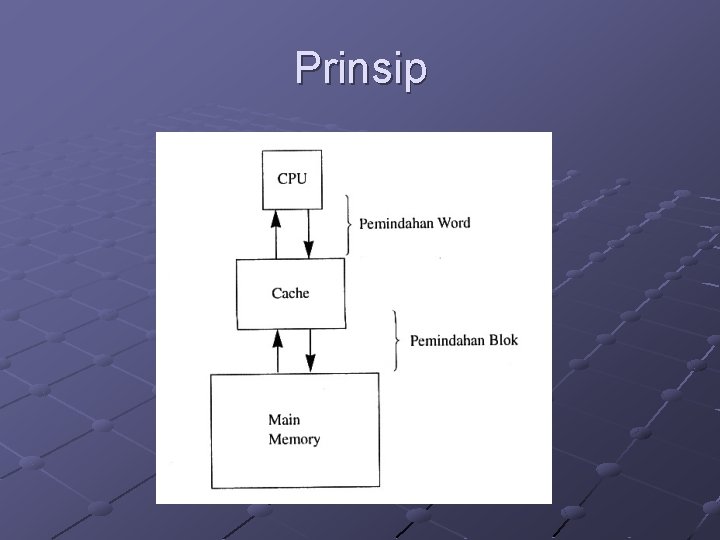

Prinsip Cache Memory Cache memory ditujukan utk memberikan kecepatan memori yg mendekati kecepatan memori tercepat yg bisa diperoleh, sekaligus memberi ukuran memori yg besar dg harga yg lebih murah berfingsi untuk menjembatani perbedaan kecepatan yang besar antara main memory dan CPU mengurangi idle time CPU Cache memory berada diantara CPU dan memori utama (RAM), baik posisi, kecepatan dan ukurannya Cache berisi salinan sebagian memori utama (data dari main memory dipindah per blok)

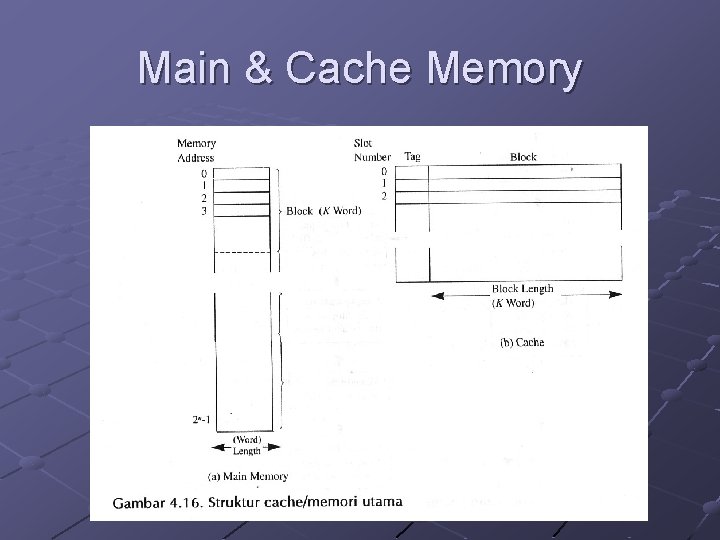

Prinsip Cache Memory (cont. ) Saat CPU akan membaca sebuah word, maka diperiksa apakah ada di cache. Bila sudah ada langsung diambil, jika belum ada maka beberapa word (dlm jumlah yg tetap) diambil dr memori utama ke cache dan kemudian dikirimkan ke CPU Fenomena lokalitas referensi: ketika sebuah blok data diambil ke cache utk memenuhi referensi memori tunggal, terdapat kemungkinan bahwa referensi berikutnya adalah blok-blok lain dlm blok tersebut Cache terdiri dari beberapa slot; tiap slot terdiri dari beberapa word (1 blok)

Prinsip

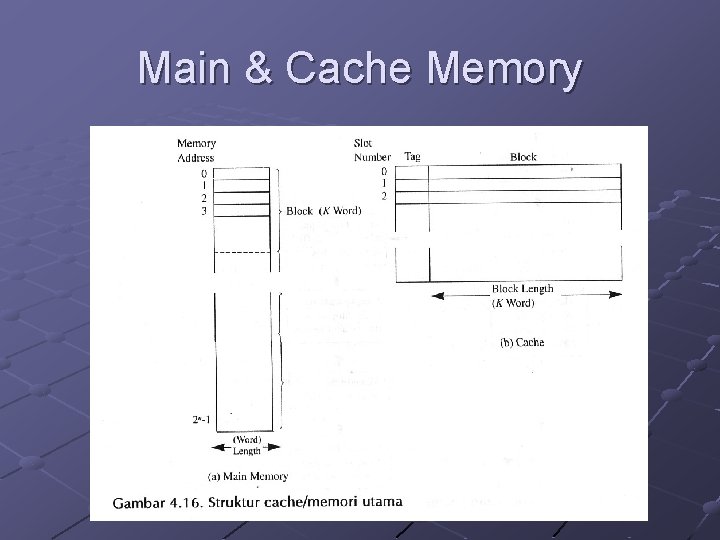

Main & Cache Memory

Cache Memory Semakin besar ukuran cache, maka semakin banyak jumlah gerbang yang dibutuhkan dalam pengalamatan cache yang terlalu besar cenderung lebih lambat dicari ukuran yang optimal

Fungsi Pemetaan (Mapping) Saluran cache lebih sedikit dibanding dengan blok memori utama Ada 3 buah teknik pemetaan: n n n Pemetaan Langsung (Direct Mapping) Pemetaan Asosiatif (Associative Mapping) Pemetaan Asosiatif Set (Set Associative Mapping)

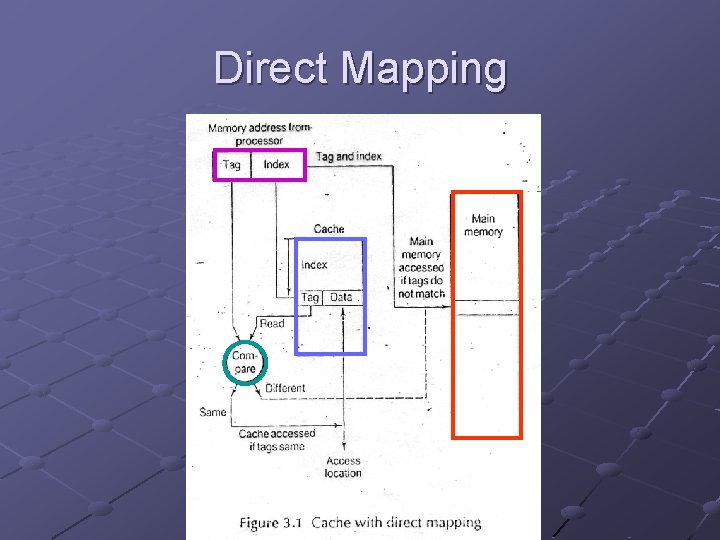

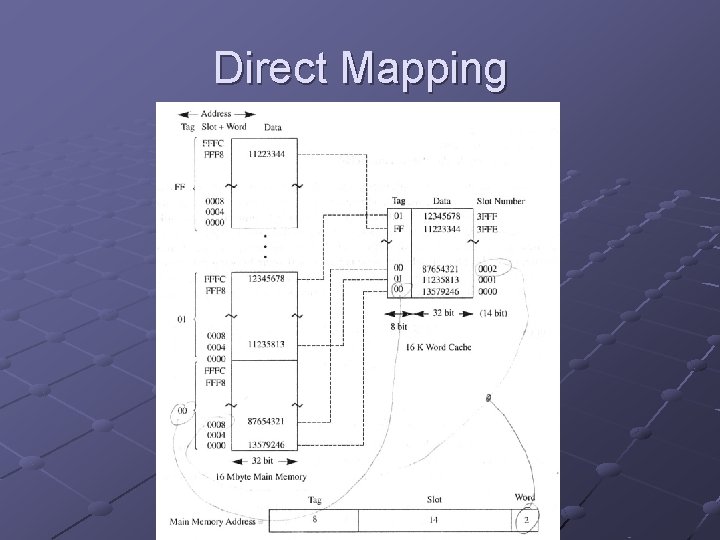

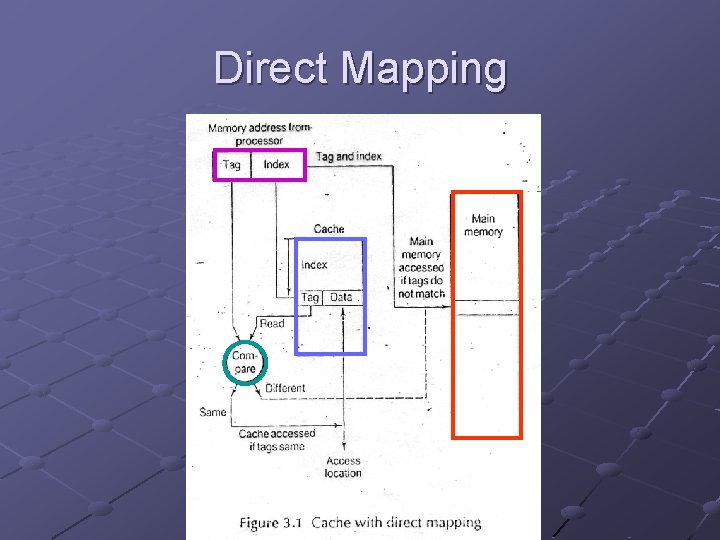

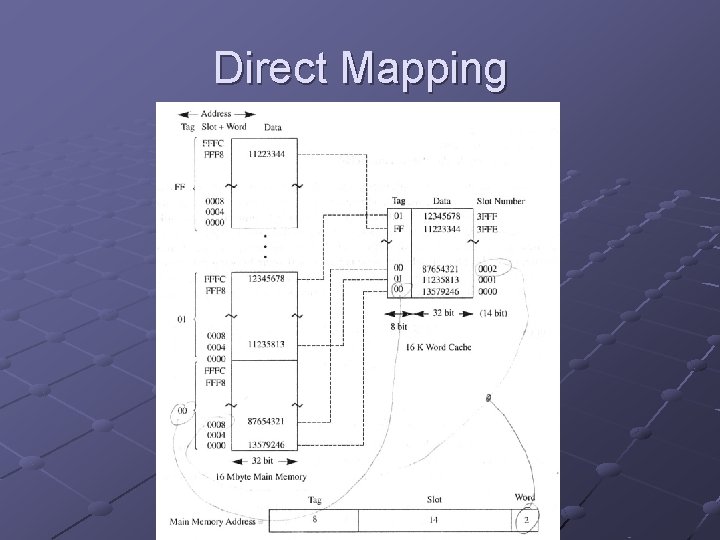

Direct Mapping memetakan masing-masing blok memori utama hanya ke sebuah saluran cache saja teknik ini sederhana dan murah untuk diimplementasikan kelemahan: terdapat lokasi cache yang tetap bagi sembarang blok-blok yang diketahui

Direct Mapping

Direct Mapping

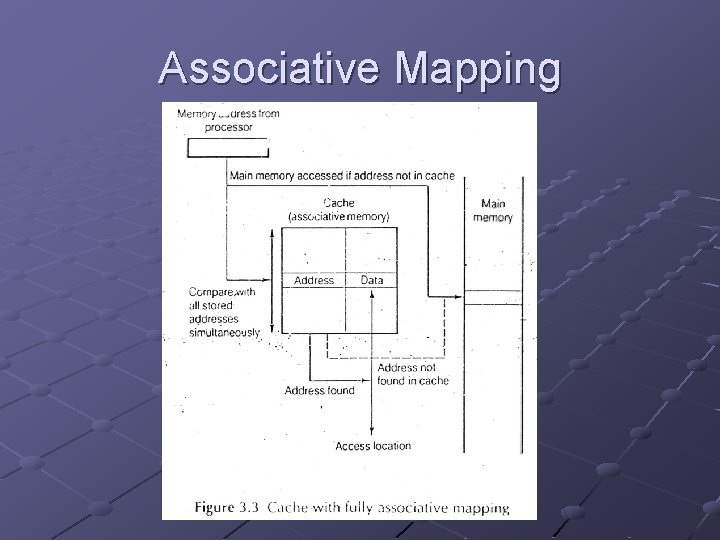

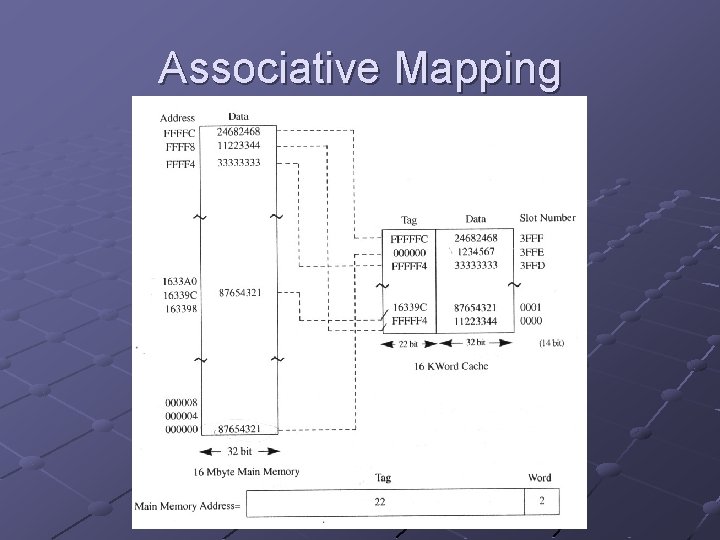

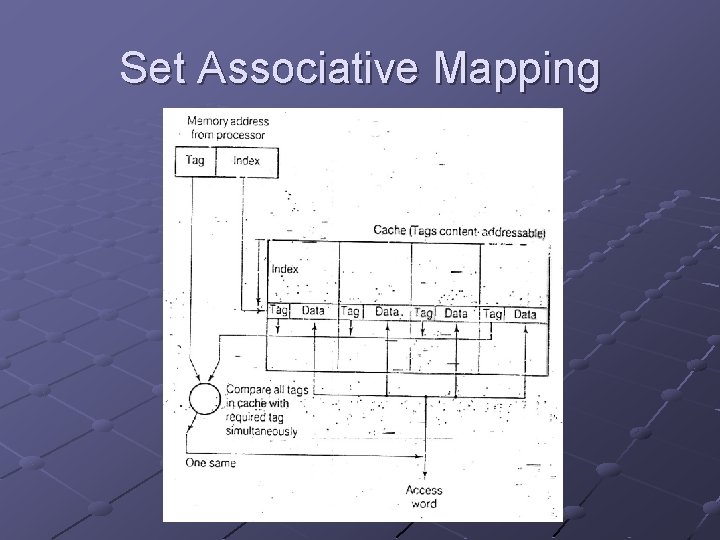

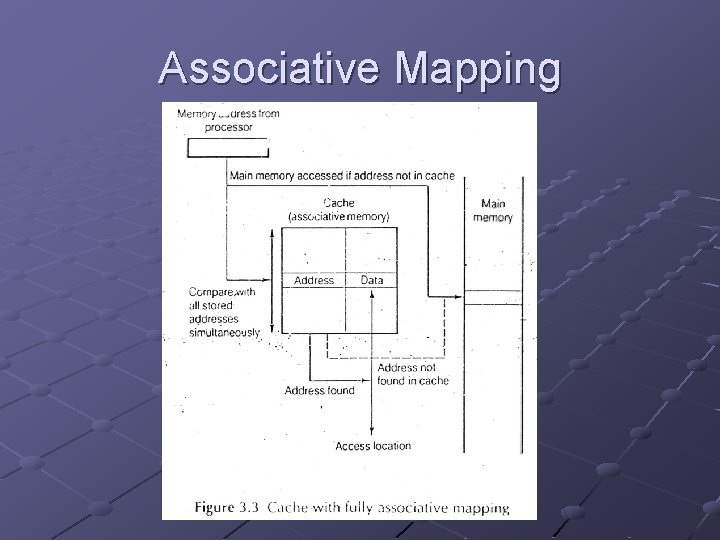

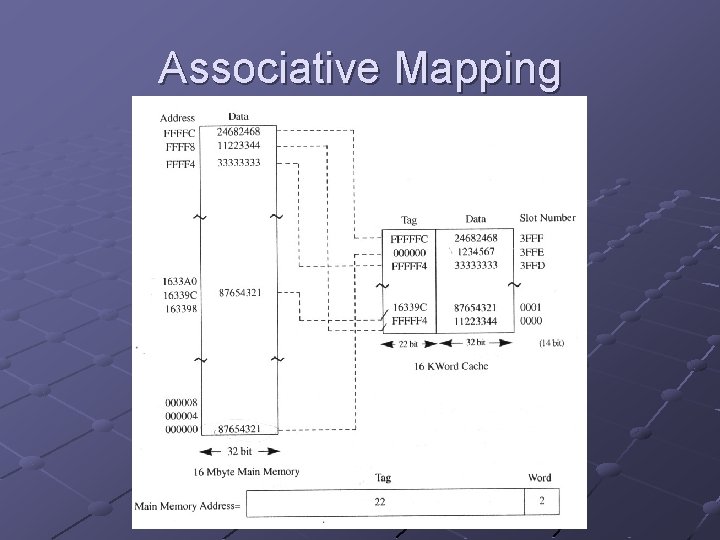

Associative Mapping mengijinkan setiap blok memori utama untuk dimuatkan ke sembarang saluran cache untuk menentukan apakah suatu blok berada di cache, maka cache control logic harus secara simultan memeriksa setiap tag saluran yang sesuai terdapat fleksibilitas penggantian blok kelemahan: kompleksitas rangkaian yang diperlukan untuk menguji tag seluruh saluran cache secara paralel

Associative Mapping

Associative Mapping

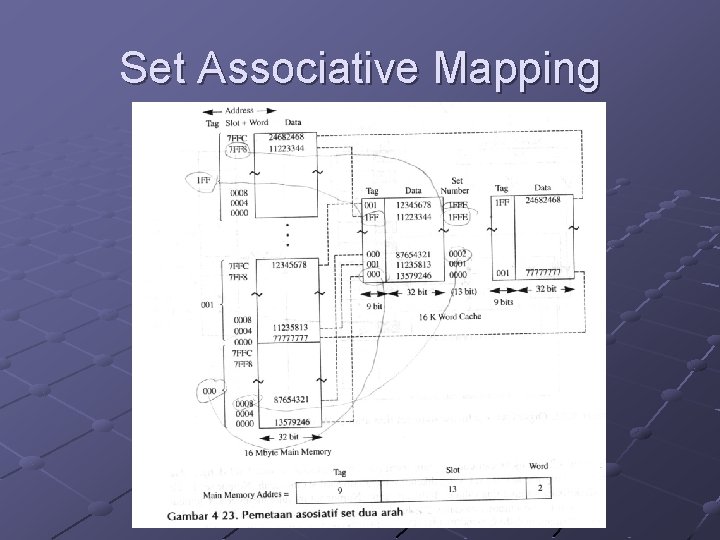

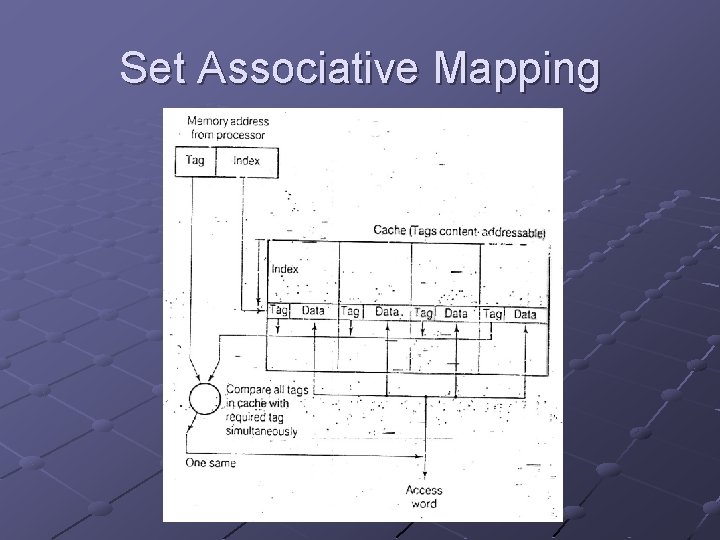

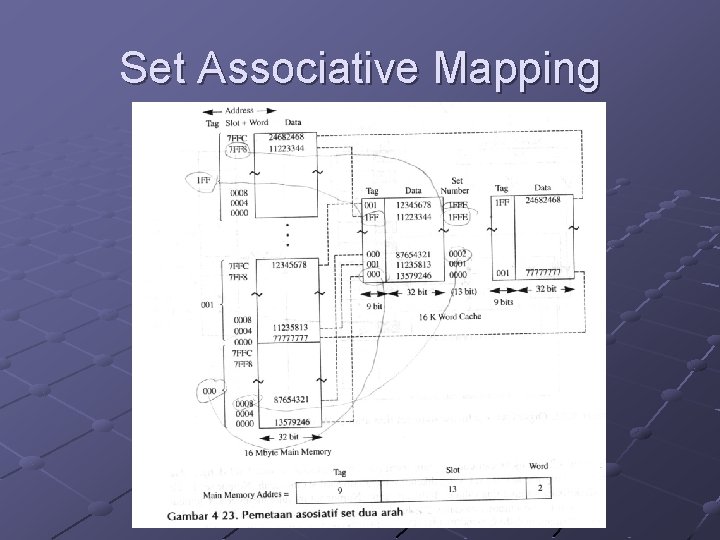

Set Associative Mapping merupakan penggabungan pemetaan langsung dan pemetaan asosiatif blok dapat dipetakan ke sembarang saluran

Set Associative Mapping

Set Associative Mapping

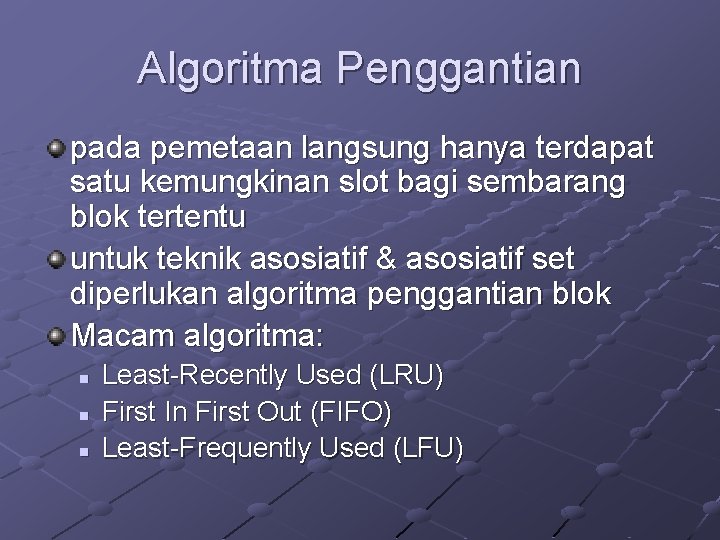

Algoritma Penggantian pada pemetaan langsung hanya terdapat satu kemungkinan slot bagi sembarang blok tertentu untuk teknik asosiatif & asosiatif set diperlukan algoritma penggantian blok Macam algoritma: n n n Least-Recently Used (LRU) First In First Out (FIFO) Least-Frequently Used (LFU)

Algoritma Penggantian Least-Recently Used (LRU) n n mengganti blok yang berada dalam set yang telah paling lama tidak diakses hit ratio terbaik diperlukan LRU, karena lokasi memori yang lebih sering dipakai akan lebih lama di cache First In First Out (FIFO) n mengganti blok yang paling lama berada di cache Least-Frequently Used (LFU) n n mengganti blok yang paling jarang diakses terdapat sebuah counter pada masing-masing slot

Write Policy jika nilai blok di dalam cache diubah, maka nilai blok di dalam main memory tidak valid lagi untuk menjaga validitas, ada beberapa teknik: n Write Through operasi write dilakukan pada cache dan main memory lalulintas memori menjadi sibuk terjadi bottle neck n Write Back meminimalisasi penulisan memori dengan hanya mengupdate cache dan memberi tanda pada bit UPDATE, lalu main memory di-update saat blok tersebut diganti akses oleh modul I/O hanya diijinkan lewat cache

Jumlah Cache Ada 2 jenis cache: n on-chip cache mengurangi aktivitas bus eksternal meningkatkan kinerja sistem diakses oleh CPU dengan sangat cepat ditempatkan pada keping yang sama dengan CPU n off-chip cache ditempatkan pada keping yang berbeda dengan CPU

Cache 2 Tingkat saat ini banyak komputer menggunakan cache 2 tingkat: n n L 1 cache (internal cache) L 2 cache (external cache) jika tidak ada L 2 cache, jika lokasi memori tidak berada di L 1 cache, maka CPU harus mengakses memori RAM/ROM melalui bus lambat dengan adanya SRAM L 2 cache, maka informasi dapat diberikan secepatnya zero wait state

Alat penyimpanan memori utama disebut juga dengan

Alat penyimpanan memori utama disebut juga dengan Satuan kapasitas memori komputer

Satuan kapasitas memori komputer Satuan alami organisasi memori adalah

Satuan alami organisasi memori adalah Karakteristik sistem memori ram

Karakteristik sistem memori ram Persamaan kapasitas efektif dan kapasitas desain

Persamaan kapasitas efektif dan kapasitas desain Karakteristik memori internal

Karakteristik memori internal Kapasitas register memori lokal dinyatakan dalam

Kapasitas register memori lokal dinyatakan dalam Kapasitas memori otak manusia

Kapasitas memori otak manusia Tingkatan satuan memori

Tingkatan satuan memori Satuan kecepatan kinerja komputer

Satuan kecepatan kinerja komputer Satuan besaran pokok sisi kubus

Satuan besaran pokok sisi kubus Dua satuan segitiga sama dengan ... satuan persegi

Dua satuan segitiga sama dengan ... satuan persegi 450 g dalam satuan si

450 g dalam satuan si Lll adalah

Lll adalah Apa karakteristik dari memori virtual

Apa karakteristik dari memori virtual Karakteristik memori virtual

Karakteristik memori virtual Karakteristik memori

Karakteristik memori Materi memori internal

Materi memori internal Alamat tabel sebuah page dalam memori ditunjukkan oleh

Alamat tabel sebuah page dalam memori ditunjukkan oleh Alokasi memori pada sistem multiprogramming

Alokasi memori pada sistem multiprogramming Sekumpulan komputer

Sekumpulan komputer Definisi sistem informasi manajemen

Definisi sistem informasi manajemen Karakteristik sistem

Karakteristik sistem Sistem informasi manajemen perkantoran

Sistem informasi manajemen perkantoran Pengantar sistem cerdas

Pengantar sistem cerdas Karakteristik sistem operasi jaringan

Karakteristik sistem operasi jaringan Karakteristik evaluasi strategi

Karakteristik evaluasi strategi System of internal controls

System of internal controls Right of auditor

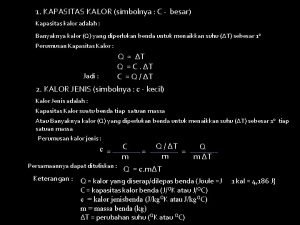

Right of auditor Mencari kapasitas kalor

Mencari kapasitas kalor Contoh desain proses

Contoh desain proses Kapasitas kerja adalah

Kapasitas kerja adalah Perencanaan agregat

Perencanaan agregat Kapasitas kalor

Kapasitas kalor Kapasitas kanal transmisi

Kapasitas kanal transmisi Cp-cv=r/m

Cp-cv=r/m Tiga buah kapasitor dihubungkan secara seri dan paralel

Tiga buah kapasitor dihubungkan secara seri dan paralel Suatu kapasitor keping sejenis mempunyai kapasitas 5

Suatu kapasitor keping sejenis mempunyai kapasitas 5 Kapasitas sesungguhnya adalah

Kapasitas sesungguhnya adalah Kapasitas sesungguhnya yang diharapkan adalah

Kapasitas sesungguhnya yang diharapkan adalah Kapasitas lapang

Kapasitas lapang Sebutkan kata lain dari biaya overhead

Sebutkan kata lain dari biaya overhead Satuan energi gibbs

Satuan energi gibbs Simbol komponen pneumatic

Simbol komponen pneumatic