Medipix 2 Parallel Readout System V Fanti R

- Slides: 32

Medipix 2 Parallel Readout System V. Fanti, R. Marzeddu, P. Randaccio Dipartamento di Fisica e Sezione INFN Cagliari 4 -th IWORID Amsterdam 8 – 12 September 2002 IWORID 2002 - P. Randaccio

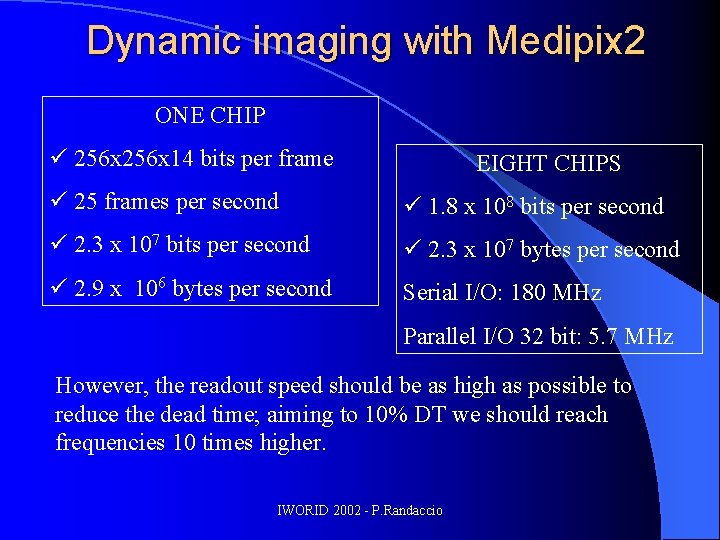

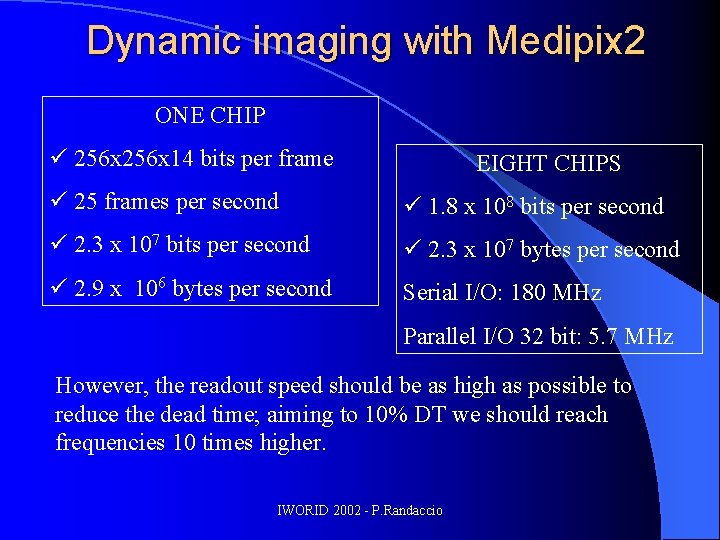

Dynamic imaging with Medipix 2 ONE CHIP ü 256 x 14 bits per frame EIGHT CHIPS ü 25 frames per second ü 1. 8 x 108 bits per second ü 2. 3 x 107 bytes per second ü 2. 9 x 106 bytes per second Serial I/O: 180 MHz Parallel I/O 32 bit: 5. 7 MHz However, the readout speed should be as high as possible to reduce the dead time; aiming to 10% DT we should reach frequencies 10 times higher. IWORID 2002 - P. Randaccio

The PC platform as acquisition system Actually the PC is the best solution for: • Acquisition • Processing • Visualization • Storage in imaging systems. IWORID 2002 - P. Randaccio

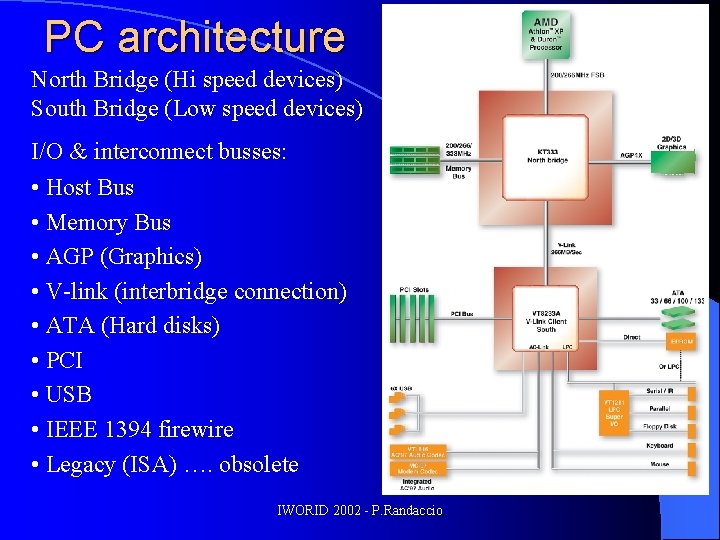

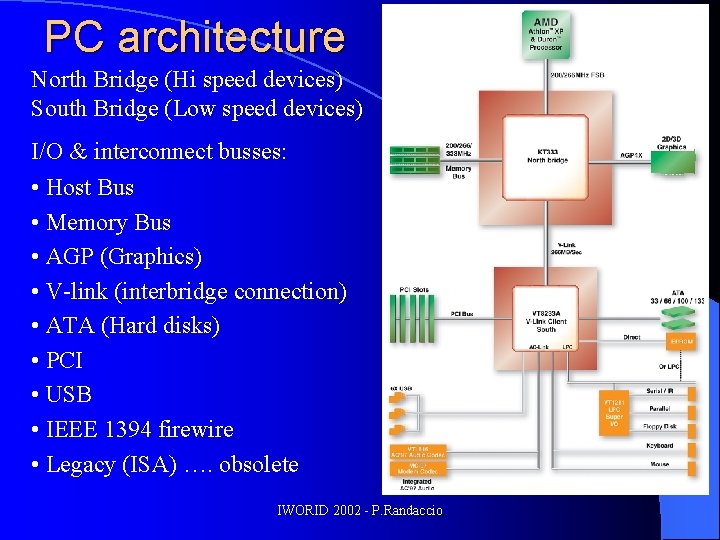

PC architecture North Bridge (Hi speed devices) South Bridge (Low speed devices) I/O & interconnect busses: • Host Bus • Memory Bus • AGP (Graphics) • V-link (interbridge connection) • ATA (Hard disks) • PCI • USB • IEEE 1394 firewire • Legacy (ISA) …. obsolete IWORID 2002 - P. Randaccio

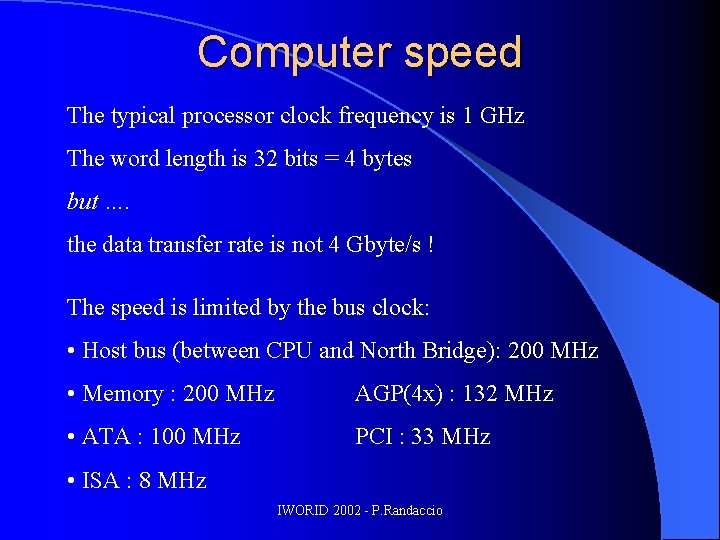

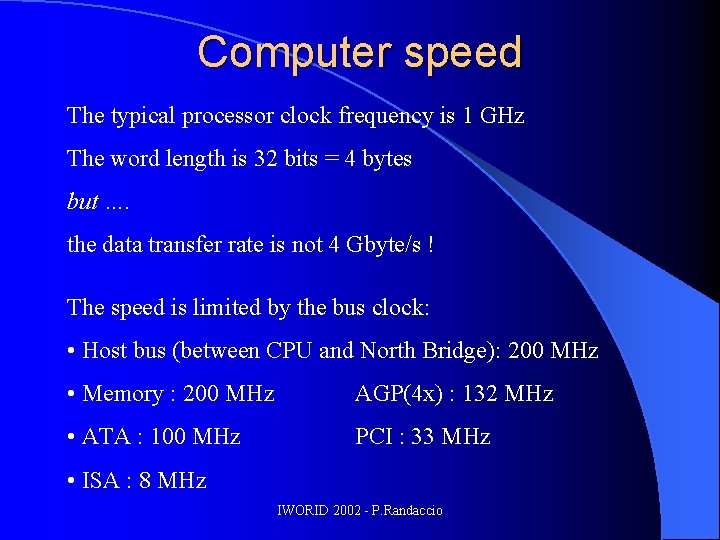

Computer speed The typical processor clock frequency is 1 GHz The word length is 32 bits = 4 bytes but …. the data transfer rate is not 4 Gbyte/s ! The speed is limited by the bus clock: • Host bus (between CPU and North Bridge): 200 MHz • Memory : 200 MHz AGP(4 x) : 132 MHz • ATA : 100 MHz PCI : 33 MHz • ISA : 8 MHz IWORID 2002 - P. Randaccio

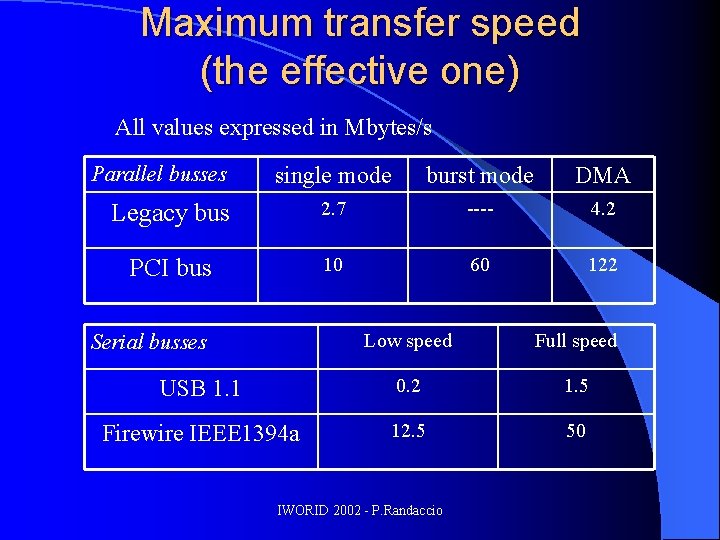

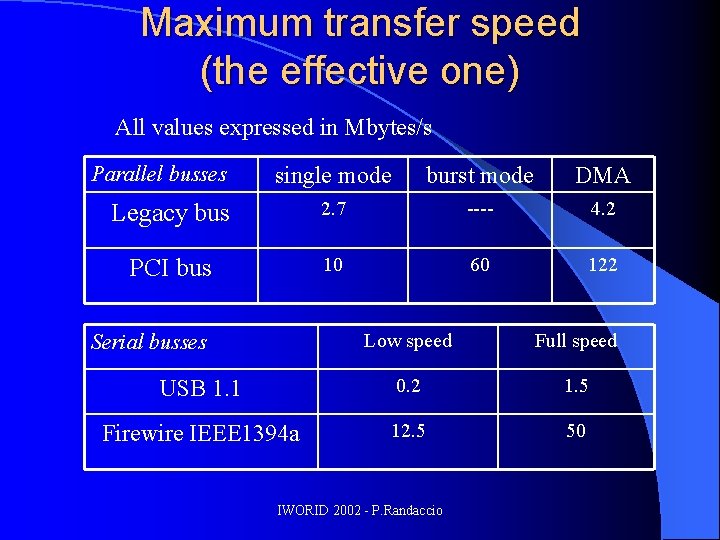

Maximum transfer speed (the effective one) All values expressed in Mbytes/s Parallel busses single mode burst mode DMA Legacy bus 2. 7 ---- 4. 2 PCI bus 10 60 122 Low speed Full speed USB 1. 1 0. 2 1. 5 Firewire IEEE 1394 a 12. 5 50 Serial busses IWORID 2002 - P. Randaccio

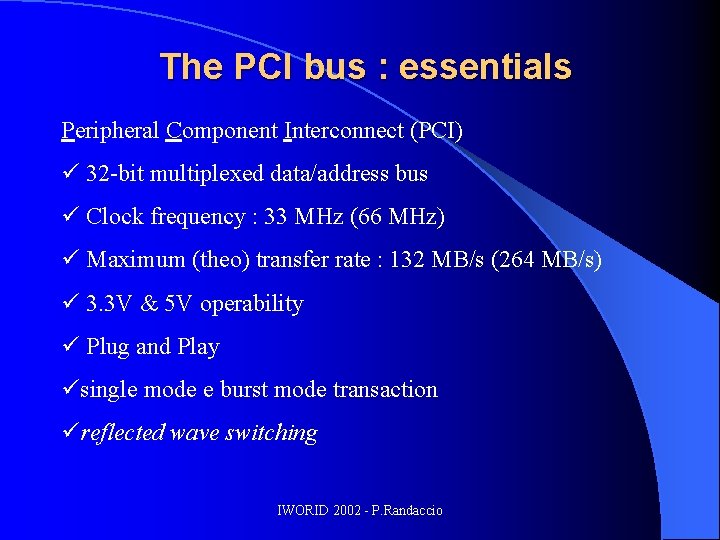

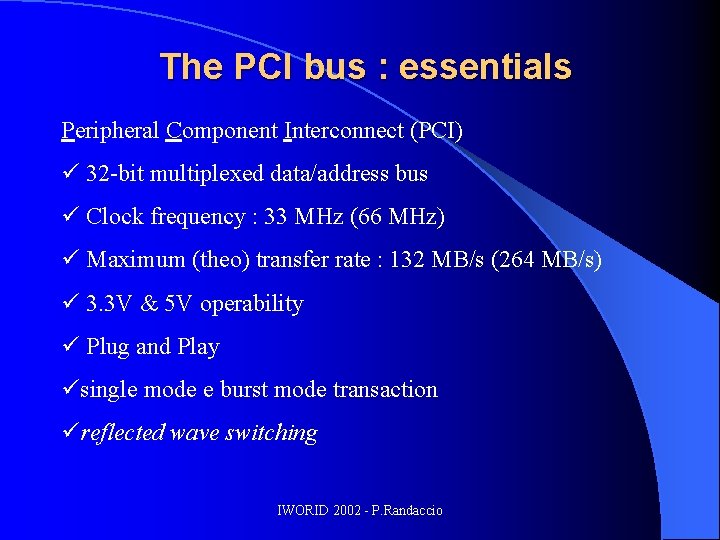

The PCI bus : essentials Peripheral Component Interconnect (PCI) ü 32 -bit multiplexed data/address bus ü Clock frequency : 33 MHz (66 MHz) ü Maximum (theo) transfer rate : 132 MB/s (264 MB/s) ü 3. 3 V & 5 V operability ü Plug and Play üsingle mode e burst mode transaction üreflected wave switching IWORID 2002 - P. Randaccio

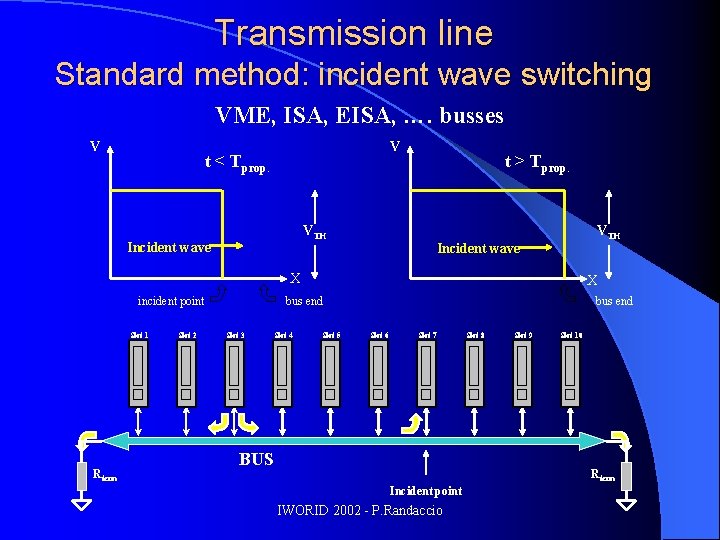

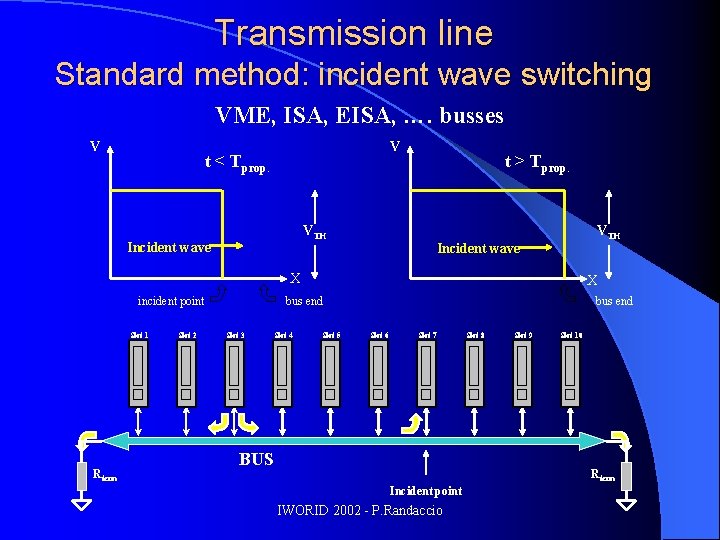

Transmission line Standard method: incident wave switching VME, ISA, EISA, …. busses V V t < Tprop. t > Tprop. VTH Incident wave X incident point Slot 1 Rterm Slot 2 X bus end Slot 3 Slot 4 Slot 5 bus end Slot 6 Slot 7 BUS Slot 8 Slot 9 Slot 10 Rterm Incident point IWORID 2002 - P. Randaccio

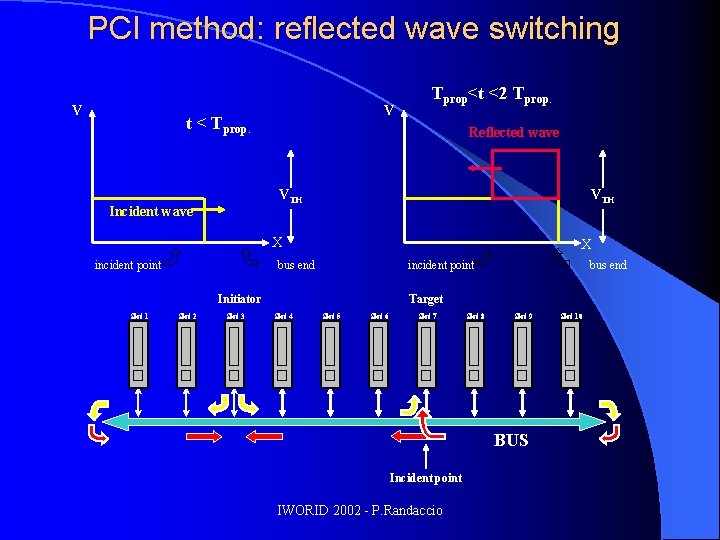

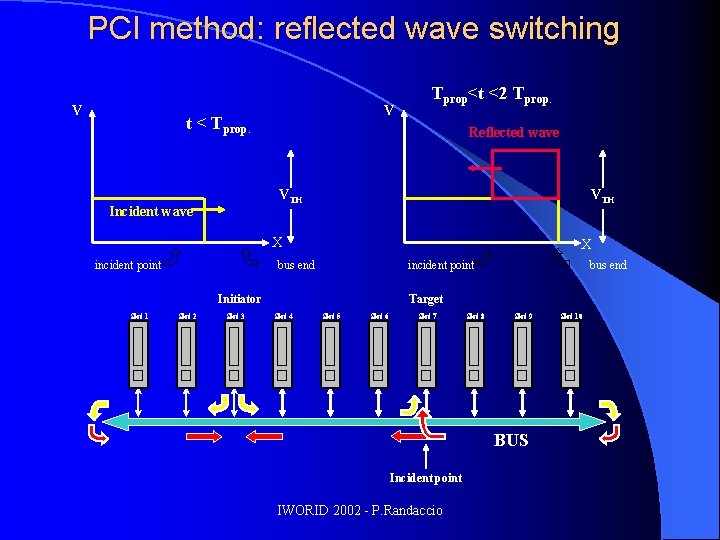

PCI method: reflected wave switching V V t < Tprop<t <2 Tprop. Reflected wave VTH Incident wave VTH X incident point bus end Initiator Slot 1 Slot 2 Slot 3 bus end Target Slot 4 Slot 5 Slot 6 Slot 7 Slot 8 Slot 9 BUS Incident point IWORID 2002 - P. Randaccio Slot 10

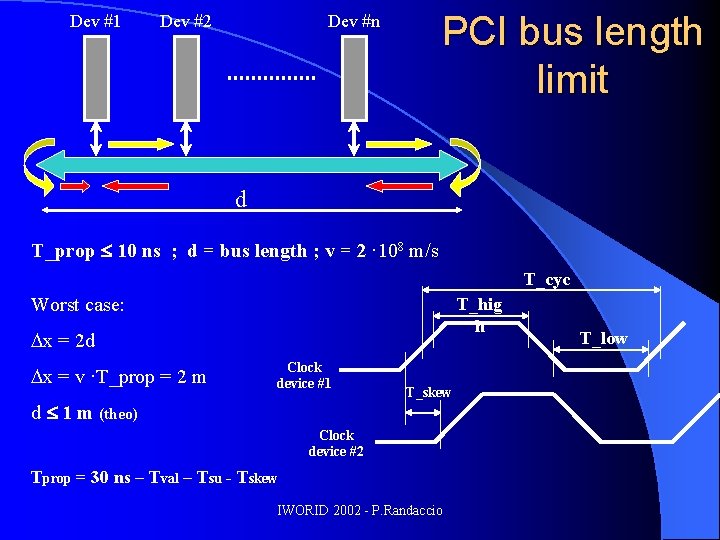

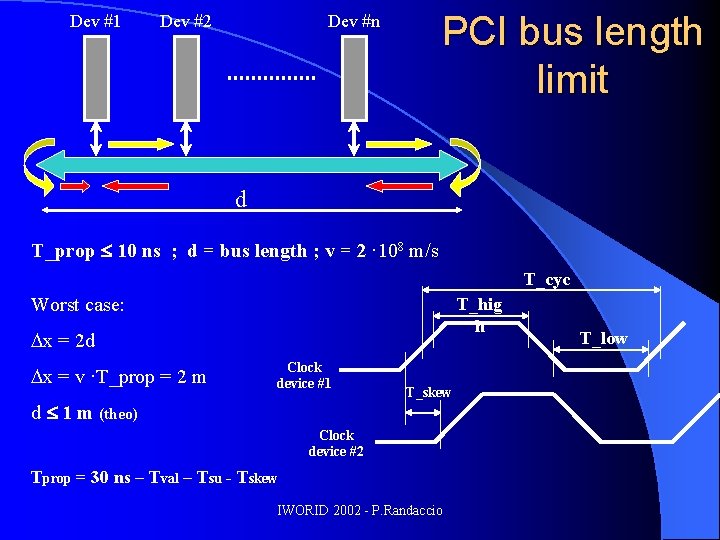

Dev #1 Dev #2 PCI bus length limit Dev #n d T_prop 10 ns ; d = bus length ; v = 2 · 108 m/s T_cyc Worst case: T_hig h x = 2 d x = v ·T_prop = 2 m Clock device #1 d 1 m (theo) T_skew Clock device #2 Tprop = 30 ns – Tval – Tsu - Tskew IWORID 2002 - P. Randaccio T_low

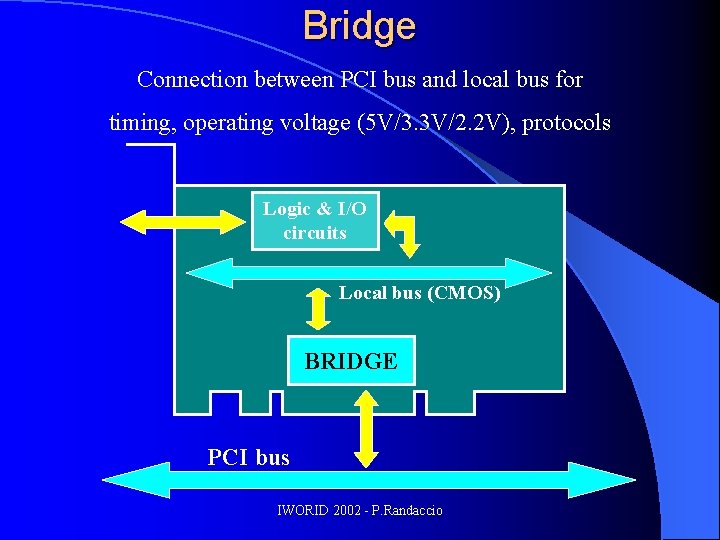

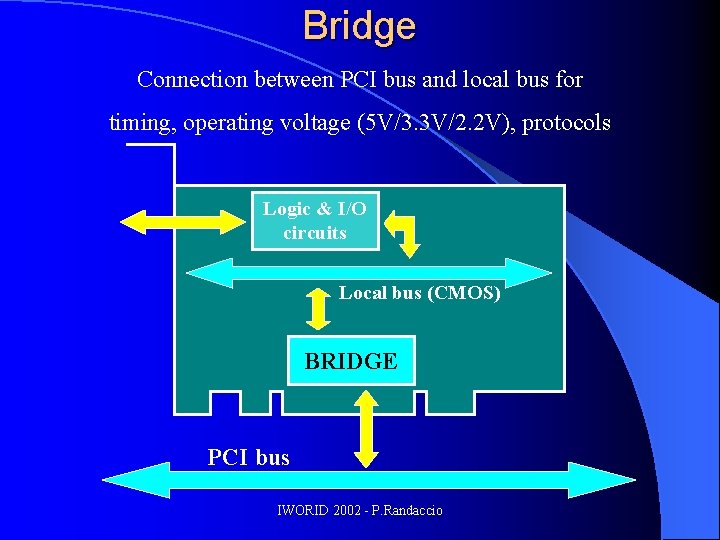

Bridge Connection between PCI bus and local bus for timing, operating voltage (5 V/3. 3 V/2. 2 V), protocols Logic & I/O circuits Local bus (CMOS) BRIDGE PCI bus IWORID 2002 - P. Randaccio

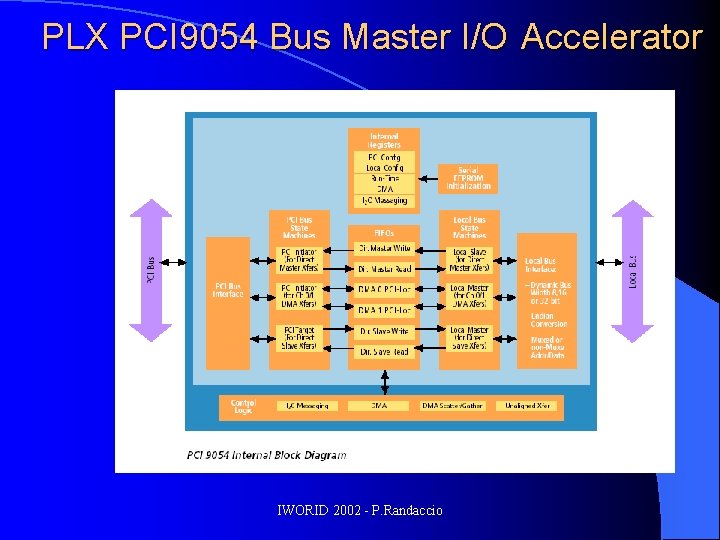

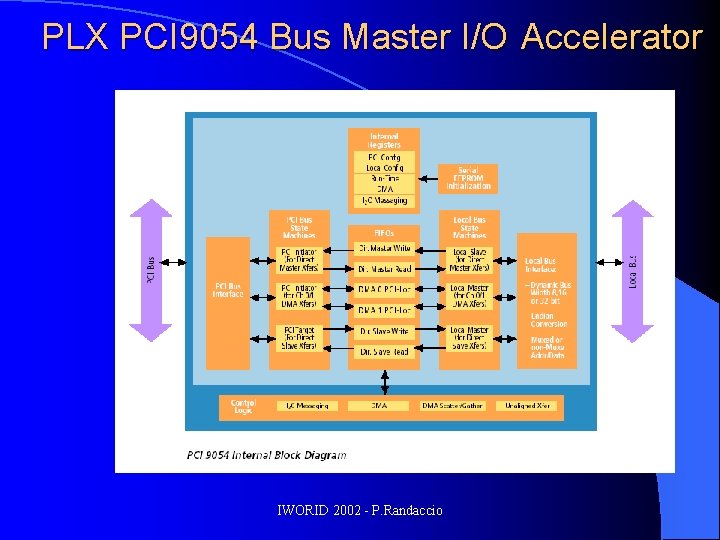

PLX PCI 9054 Bus Master I/O Accelerator IWORID 2002 - P. Randaccio

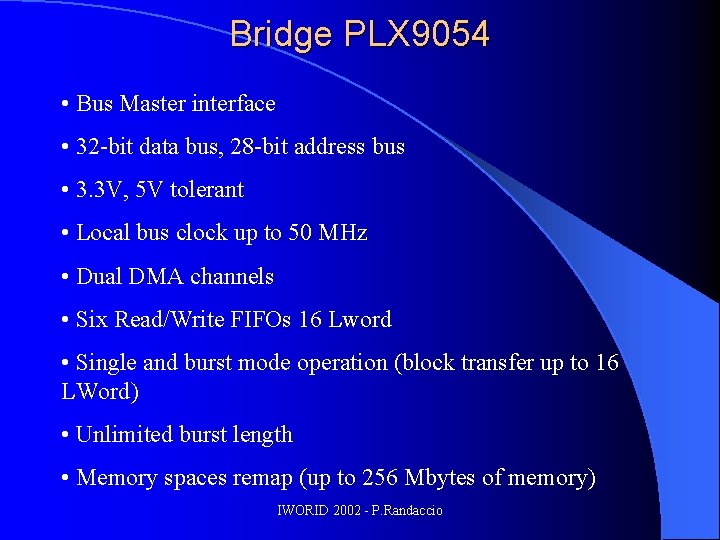

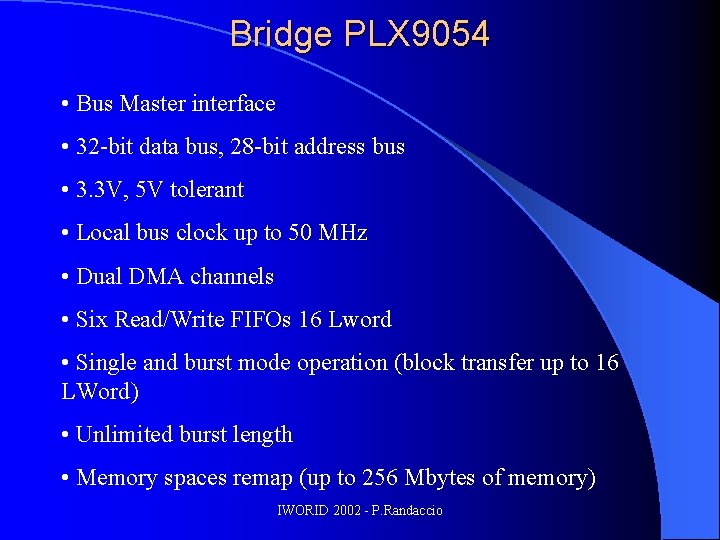

Bridge PLX 9054 • Bus Master interface • 32 -bit data bus, 28 -bit address bus • 3. 3 V, 5 V tolerant • Local bus clock up to 50 MHz • Dual DMA channels • Six Read/Write FIFOs 16 Lword • Single and burst mode operation (block transfer up to 16 LWord) • Unlimited burst length • Memory spaces remap (up to 256 Mbytes of memory) IWORID 2002 - P. Randaccio

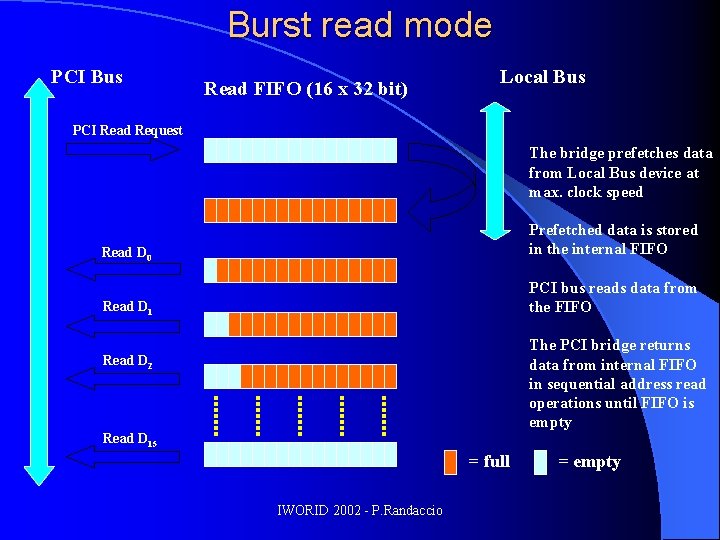

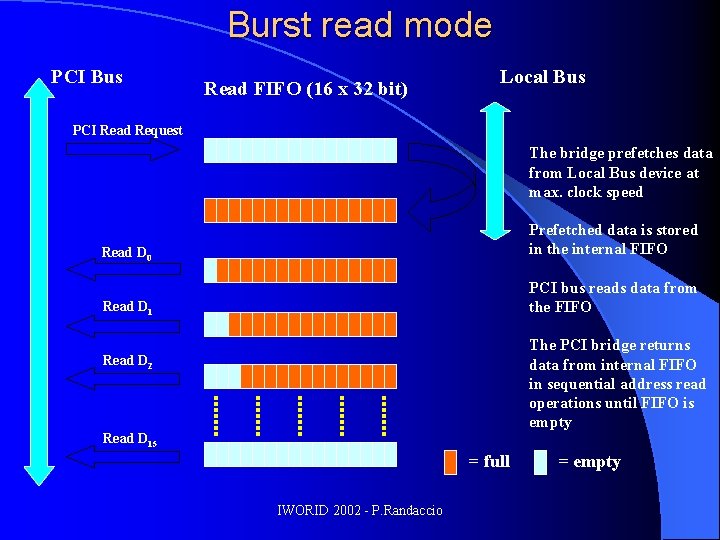

Burst read mode PCI Bus Read FIFO (16 x 32 bit) Local Bus PCI Read Request The bridge prefetches data from Local Bus device at max. clock speed Read D 0 Prefetched data is stored in the internal FIFO Read D 1 PCI bus reads data from the FIFO The PCI bridge returns data from internal FIFO in sequential address read operations until FIFO is empty Read D 2 Read D 15 = full IWORID 2002 - P. Randaccio = empty

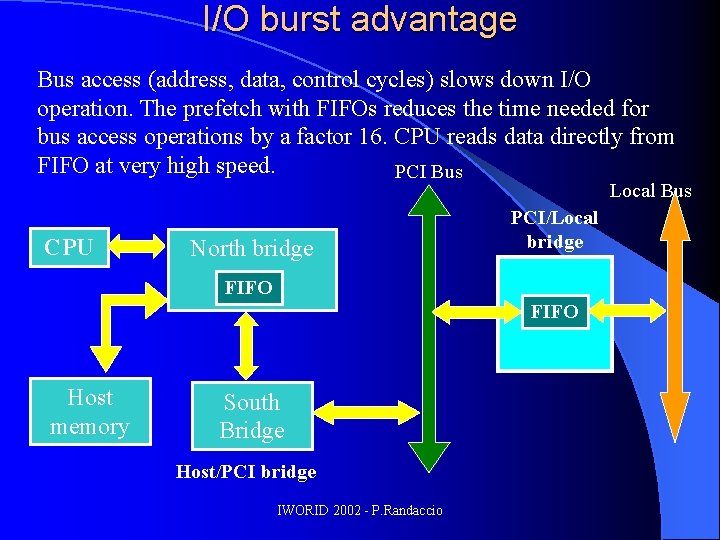

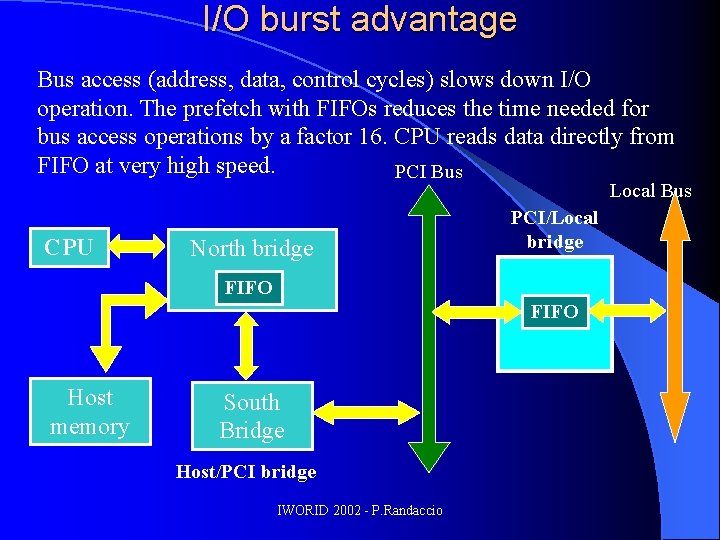

I/O burst advantage Bus access (address, data, control cycles) slows down I/O operation. The prefetch with FIFOs reduces the time needed for bus access operations by a factor 16. CPU reads data directly from FIFO at very high speed. PCI Bus Local Bus CPU North bridge PCI/Local bridge FIFO Host memory South Bridge Host/PCI bridge IWORID 2002 - P. Randaccio

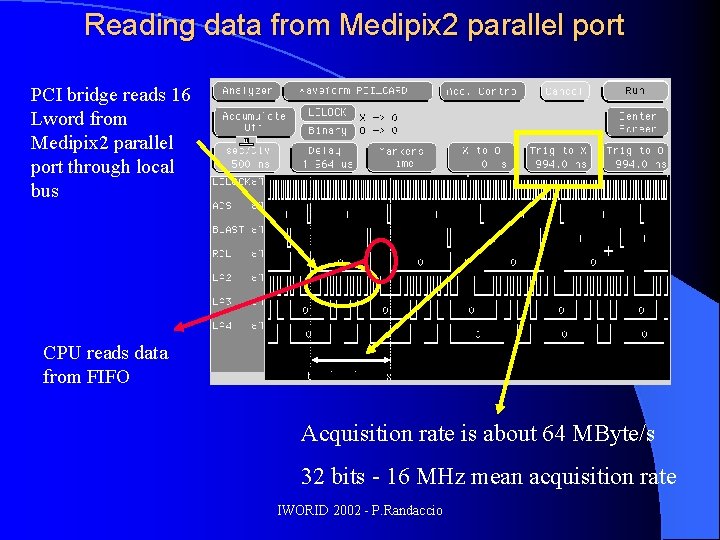

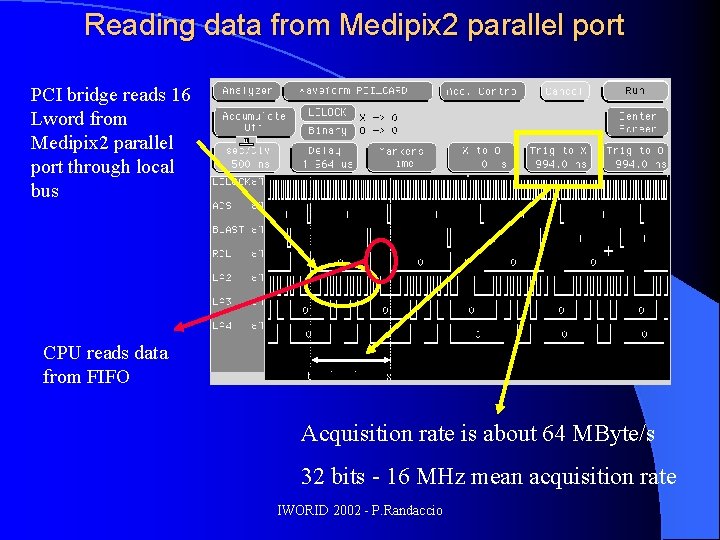

Reading data from Medipix 2 parallel port PCI bridge reads 16 Lword from Medipix 2 parallel port through local bus CPU reads data from FIFO Acquisition rate is about 64 MByte/s 32 bits - 16 MHz mean acquisition rate IWORID 2002 - P. Randaccio

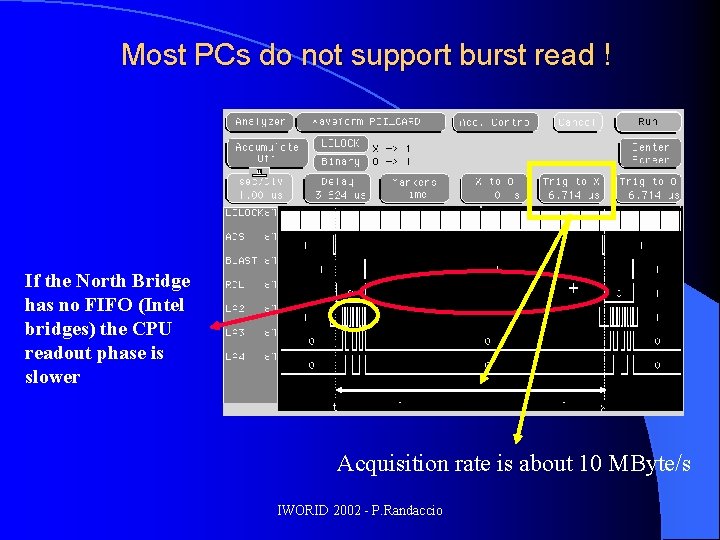

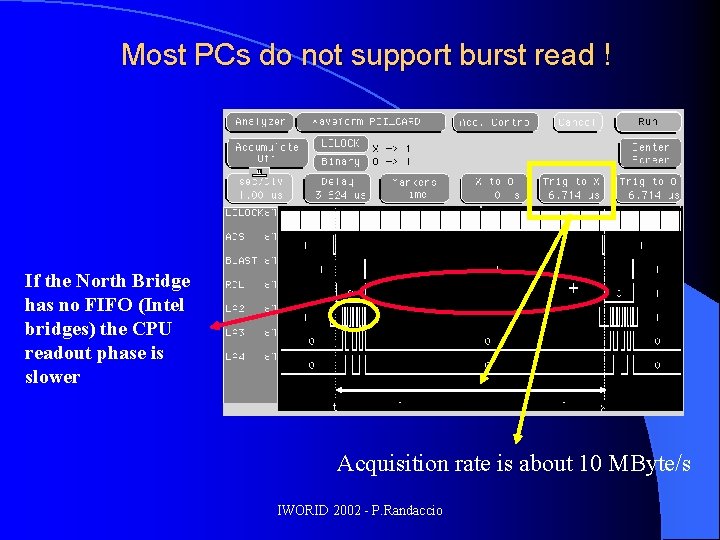

Most PCs do not support burst read ! If the North Bridge has no FIFO (Intel bridges) the CPU readout phase is slower Acquisition rate is about 10 MByte/s IWORID 2002 - P. Randaccio

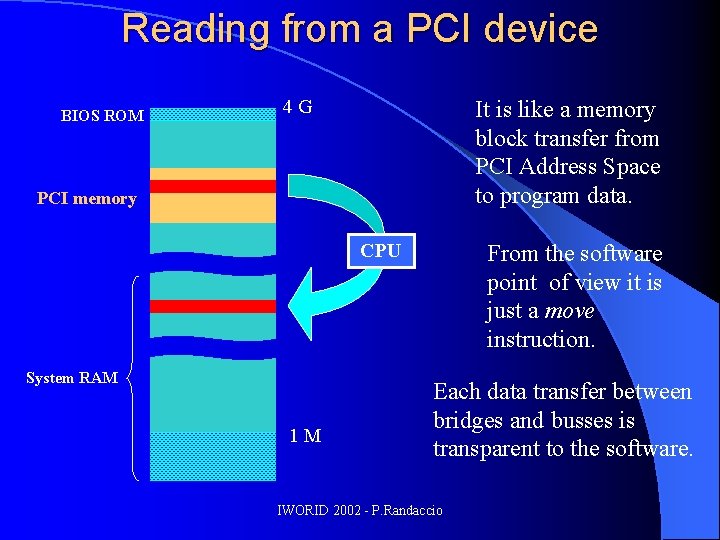

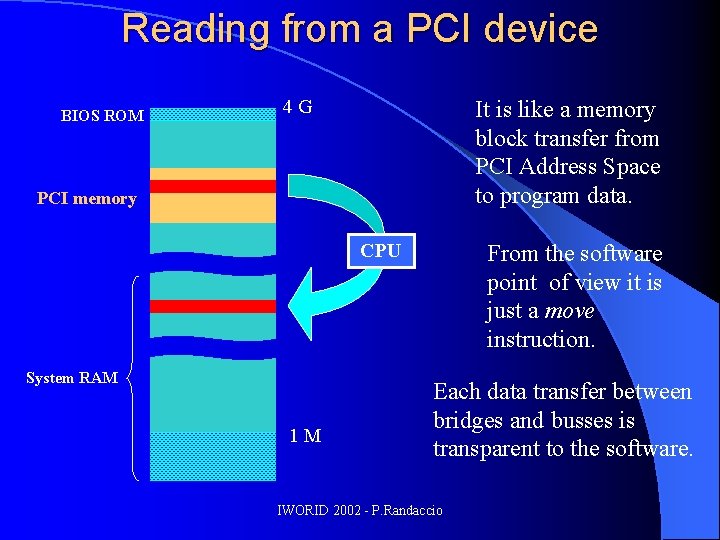

Reading from a PCI device BIOS ROM 4 G It is like a memory block transfer from PCI Address Space to program data. PCI memory CPU System RAM 1 M From the software point of view it is just a move instruction. Each data transfer between bridges and busses is transparent to the software. IWORID 2002 - P. Randaccio

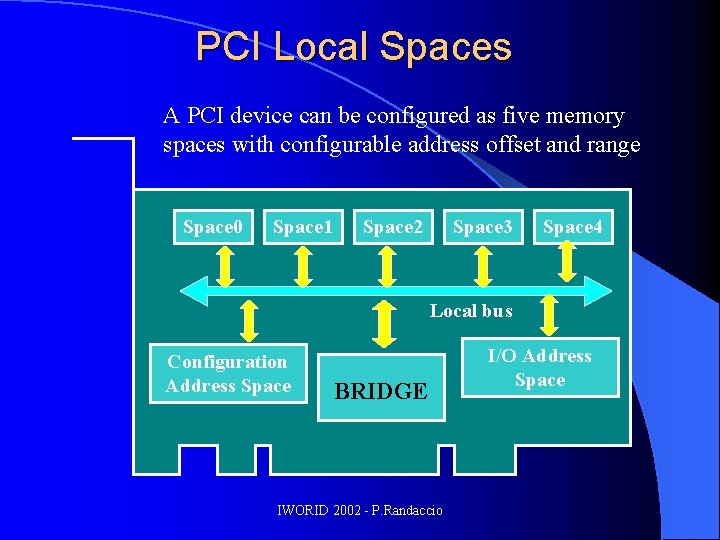

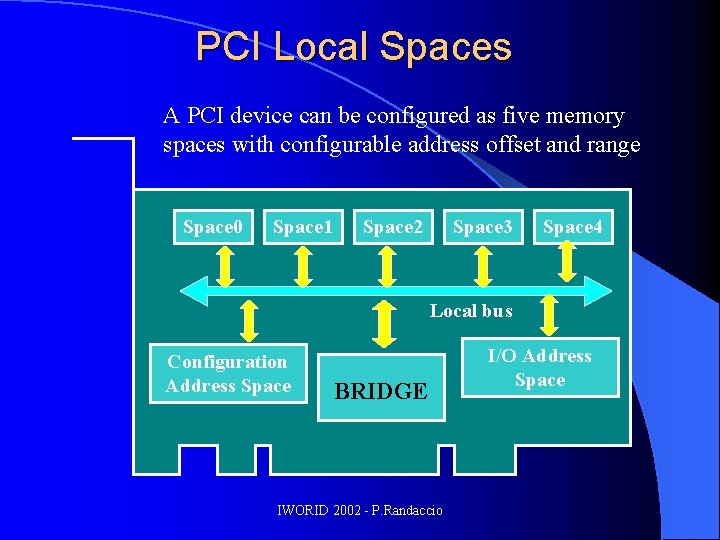

PCI Local Spaces A PCI device can be configured as five memory spaces with configurable address offset and range Space 0 Space 1 Space 2 Space 3 Space 4 Local bus Configuration Address Space BRIDGE IWORID 2002 - P. Randaccio I/O Address Space

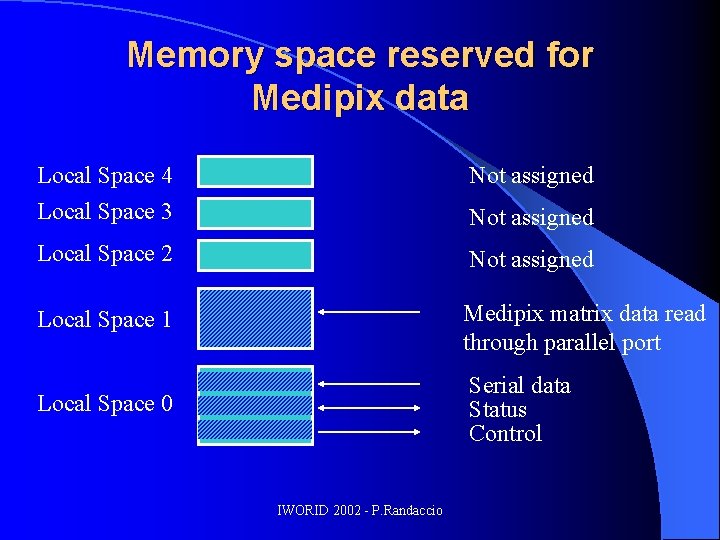

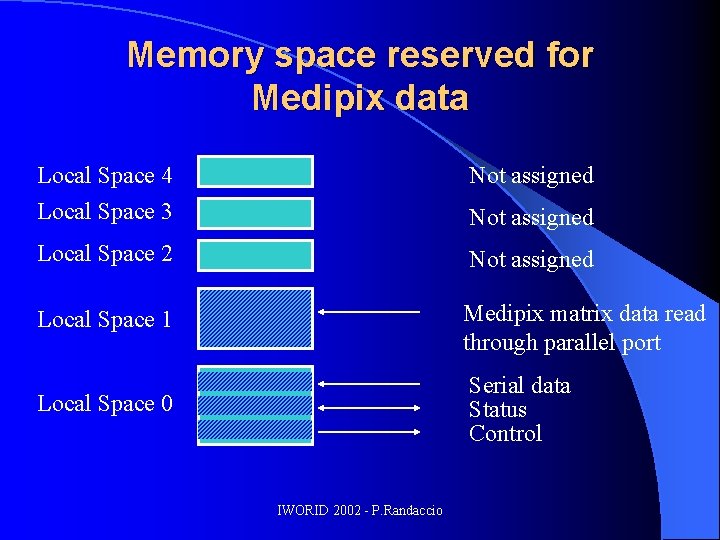

Memory space reserved for Medipix data Local Space 4 Local Space 3 Not assigned Local Space 2 Not assigned Local Space 1 Medipix matrix data read through parallel port Local Space 0 Serial data Status Control Not assigned IWORID 2002 - P. Randaccio

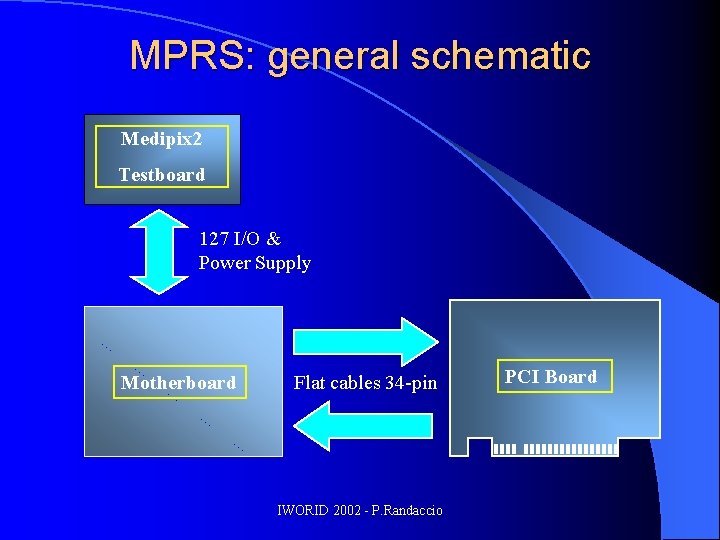

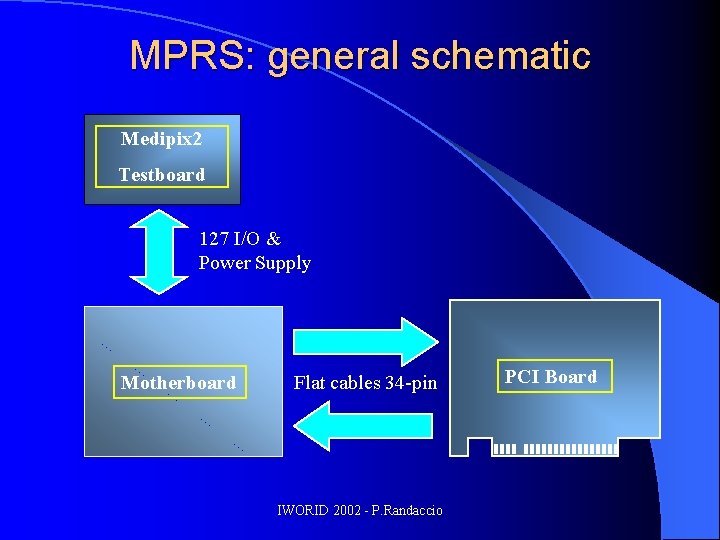

MPRS: general schematic Medipix 2 Testboard 127 I/O & Power Supply Motherboard Flat cables 34 -pin IWORID 2002 - P. Randaccio PCI Board

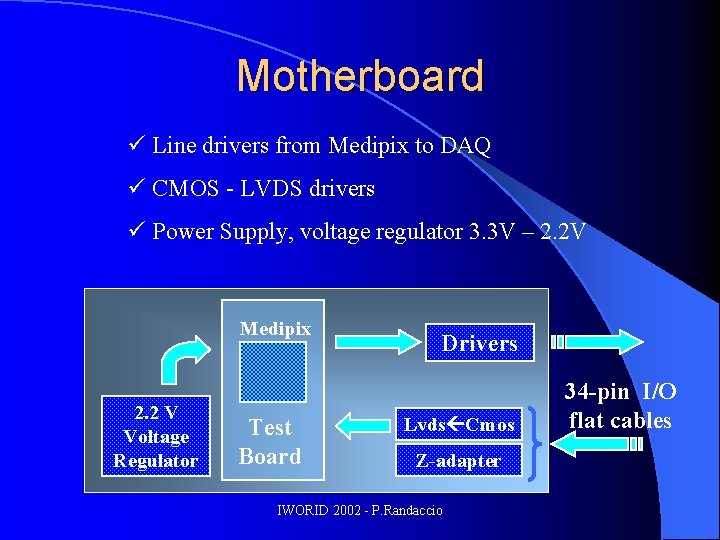

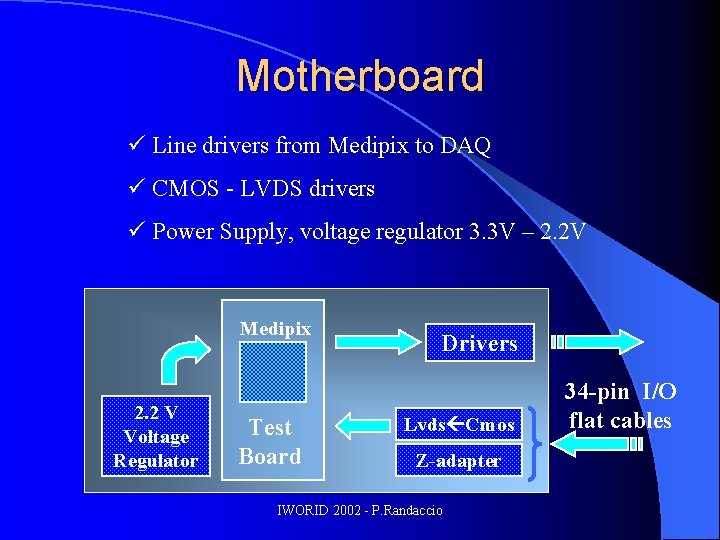

Motherboard ü Line drivers from Medipix to DAQ ü CMOS - LVDS drivers ü Power Supply, voltage regulator 3. 3 V – 2. 2 V Medipix 2. 2 V Voltage Regulator Test Board Drivers Lvds Cmos Z-adapter IWORID 2002 - P. Randaccio 34 -pin I/O flat cables

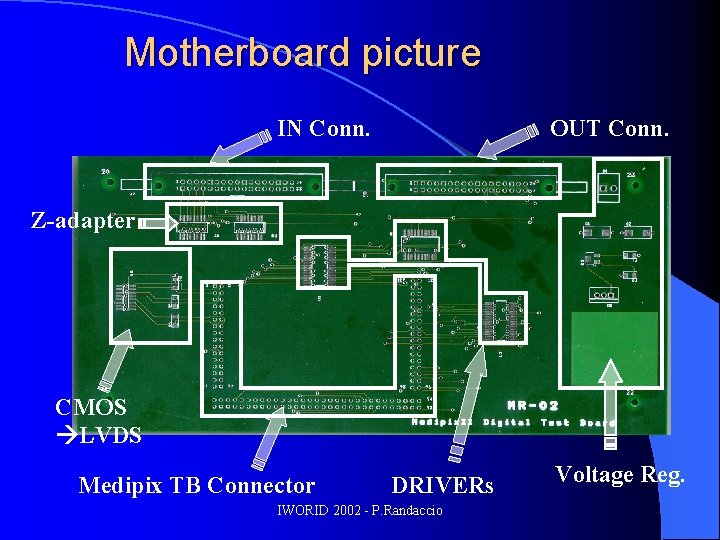

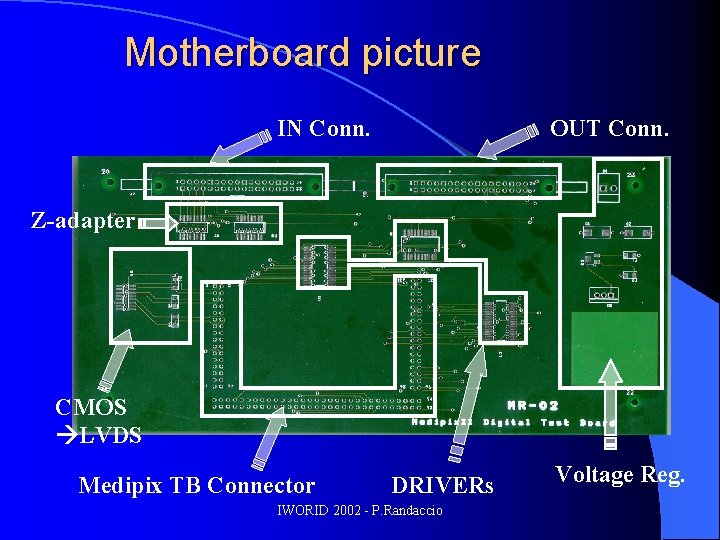

Motherboard picture IN Conn. OUT Conn. Z-adapter CMOS LVDS Medipix TB Connector DRIVERs IWORID 2002 - P. Randaccio Voltage Reg.

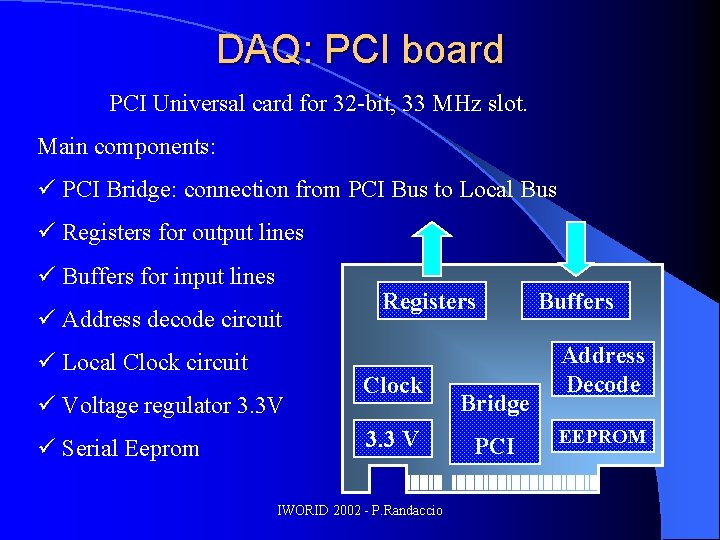

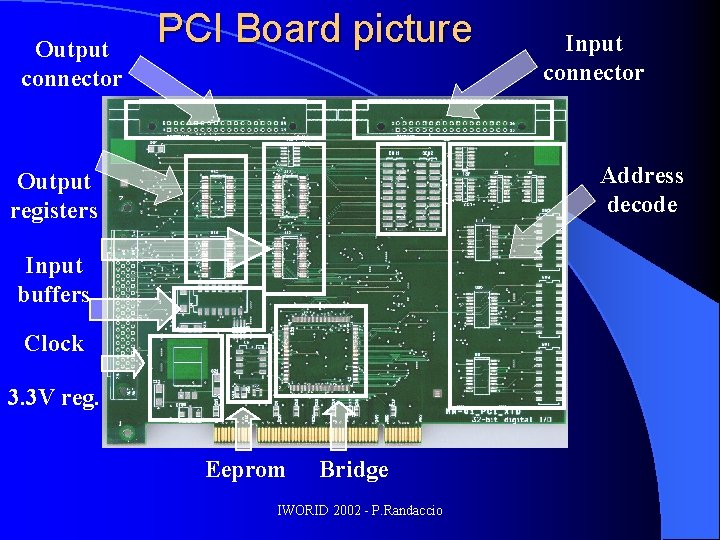

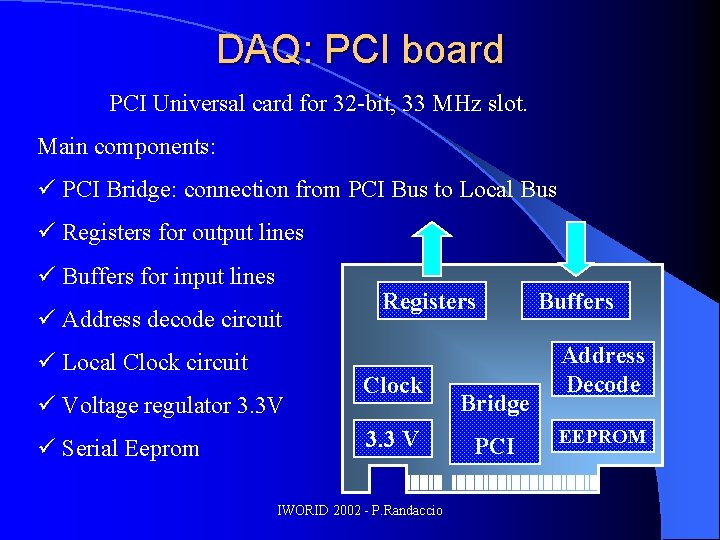

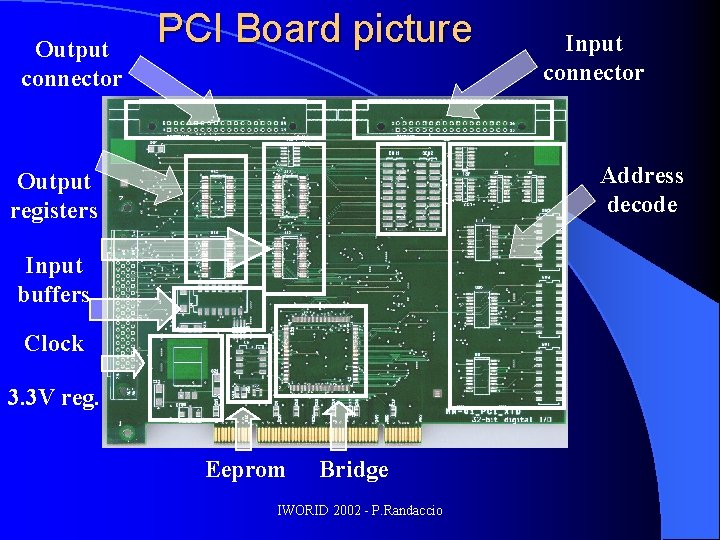

DAQ: PCI board PCI Universal card for 32 -bit, 33 MHz slot. Main components: ü PCI Bridge: connection from PCI Bus to Local Bus ü Registers for output lines ü Buffers for input lines ü Address decode circuit ü Local Clock circuit ü Voltage regulator 3. 3 V ü Serial Eeprom Registers Clock 3. 3 V IWORID 2002 - P. Randaccio Bridge PCI Buffers Address Decode EEPROM

Output connector PCI Board picture Input connector Address decode Output registers Input buffers Clock 3. 3 V reg. Eeprom Bridge IWORID 2002 - P. Randaccio

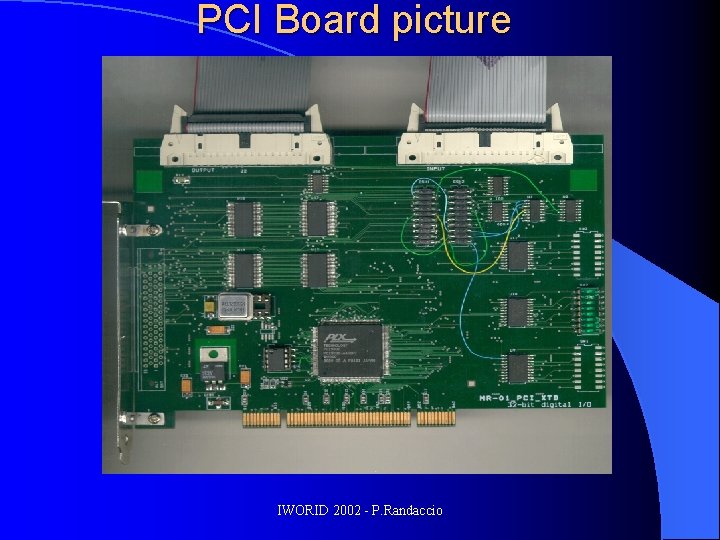

PCI Board picture IWORID 2002 - P. Randaccio

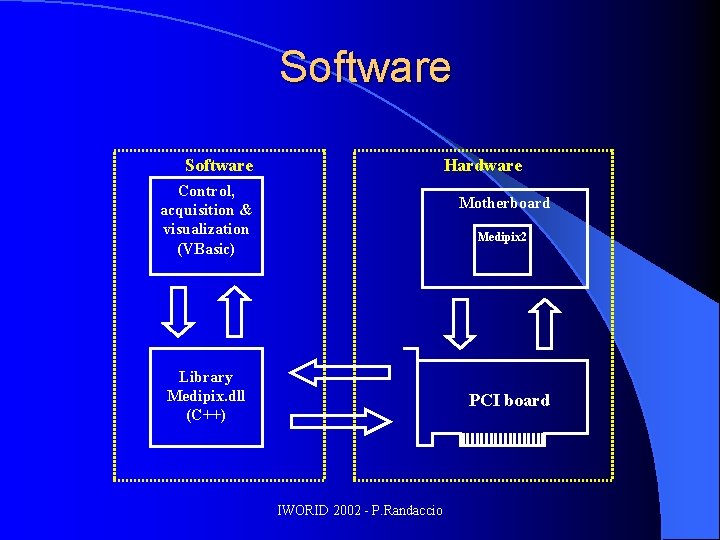

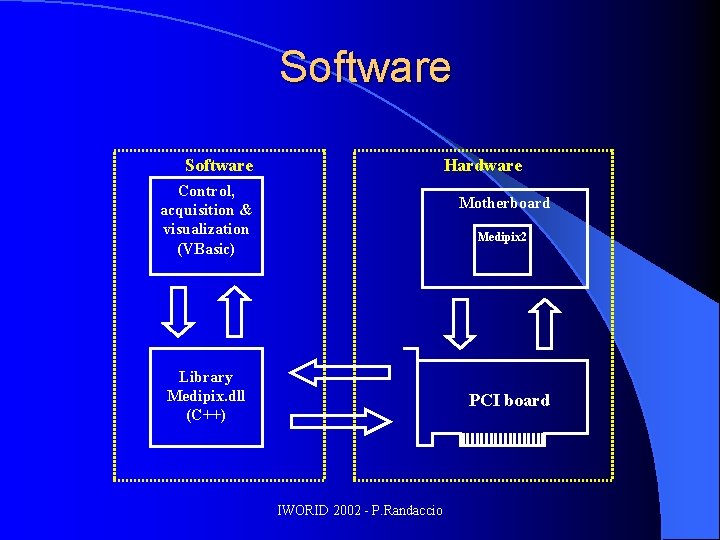

Software Hardware Control, acquisition & visualization (VBasic) Motherboard Medipix 2 Library Medipix. dll (C++) PCI board IWORID 2002 - P. Randaccio

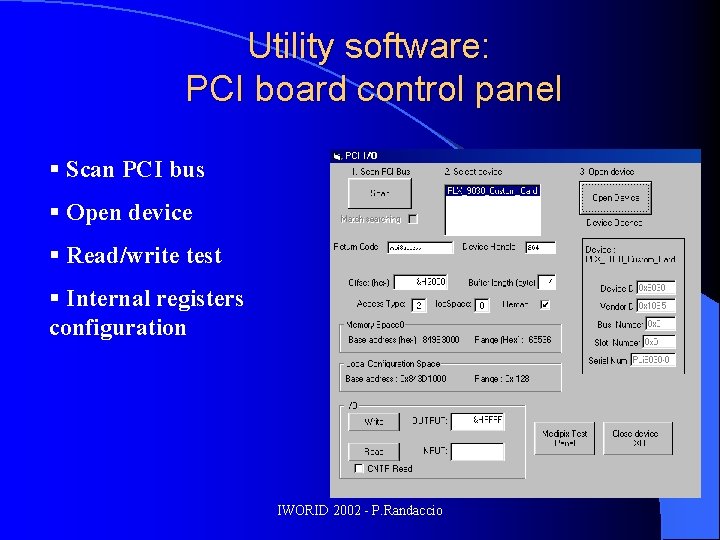

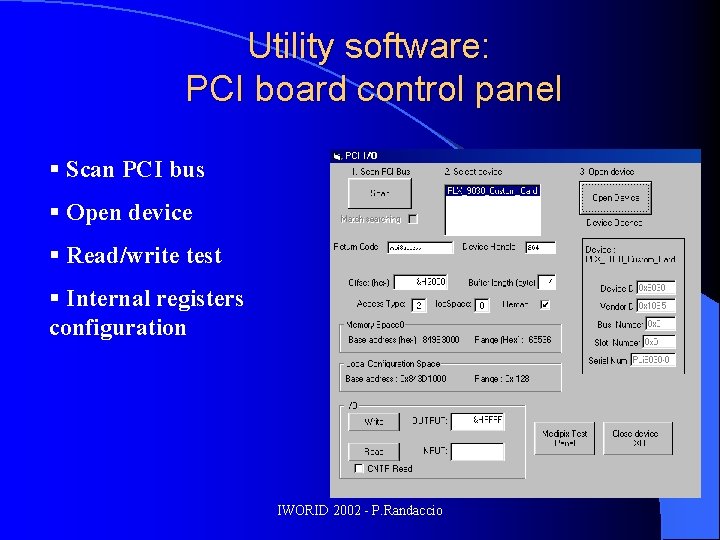

Utility software: PCI board control panel § Scan PCI bus § Open device § Read/write test § Internal registers configuration IWORID 2002 - P. Randaccio

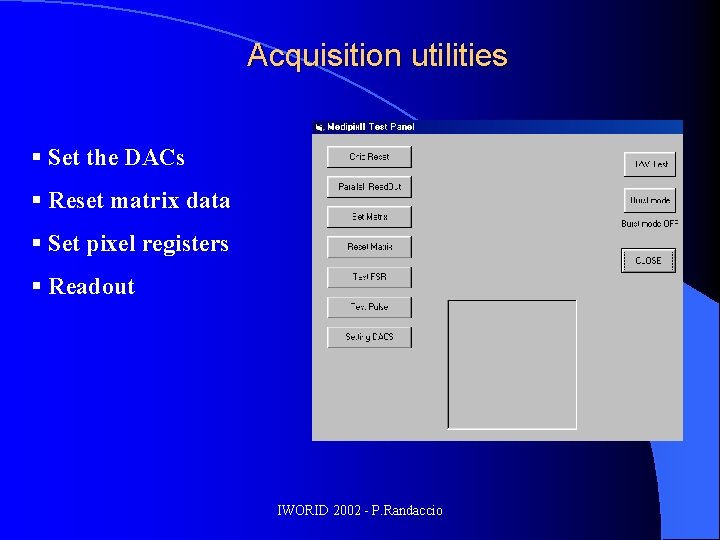

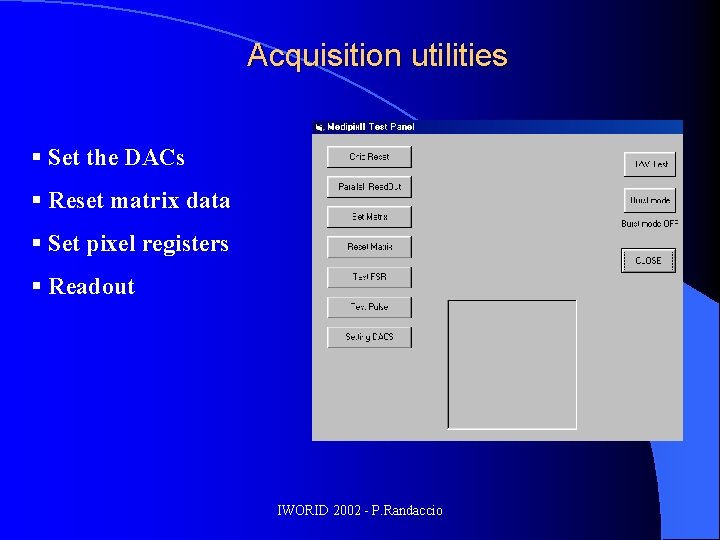

Acquisition utilities § Set the DACs § Reset matrix data § Set pixel registers § Readout IWORID 2002 - P. Randaccio

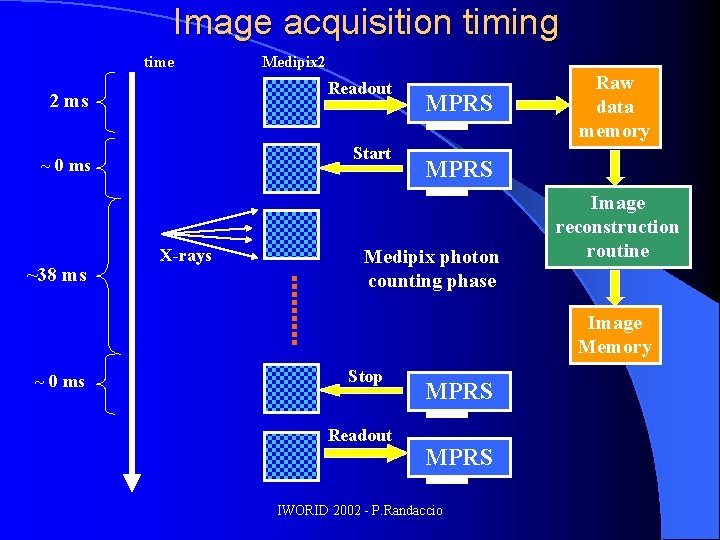

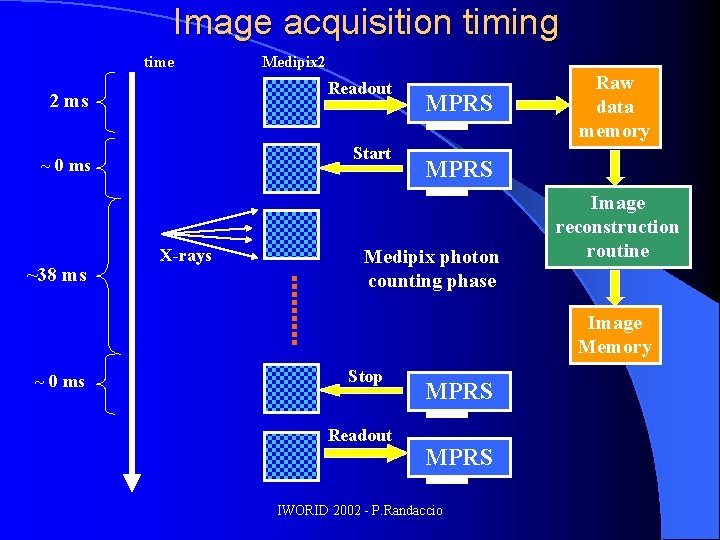

Image acquisition timing time Readout 2 ms Start ~ 0 ms ~38 ms Medipix 2 X-rays MPRS Raw data memory MPRS Medipix photon counting phase Image reconstruction routine Image Memory ~ 0 ms Stop Readout MPRS IWORID 2002 - P. Randaccio

Image reconstruction Any image processing is made by software after the acquisition, in particular: ü Image reconstruction with deserialization and derandomization The total time is : 256 x 8 x 14 x 32 x. Ts = 917504 x. Ts where Ts is the period of the inner software loop. The reconstruction time depends on CPU speed: however with a normal PC it lasts no more than 10 ms The software does the reconstruction during the Medipix 2 photon counting phase, so it does not slow down the process. IWORID 2002 - P. Randaccio

Conclusions • Parallel readout seems to be appropriate for the Medipix 2 dynamic imaging acquisition. • Actual PCs are convenient platforms for the image acquisition, processing, storage and visualization. • Interfaces based on PCI bus are easy to develop and fast enough for our purposes. • The hardware complexity is transparent for the software thanks to the bridges. • Image reconstruction made by software simplifies MPRS hardware design. IWORID 2002 - P. Randaccio