MDR IR BUF ALU FLAG PC LOGIC ACC

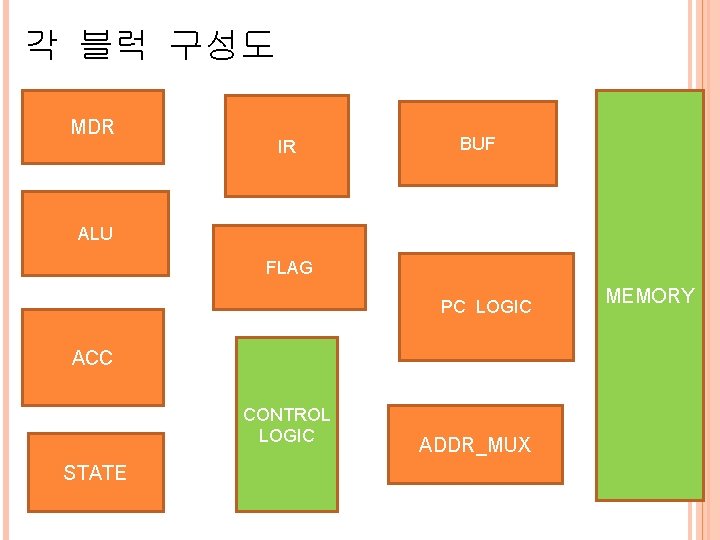

각 블럭 구성도 MDR IR BUF ALU FLAG PC LOGIC ACC CONTROL LOGIC STATE ADDR_MUX MEMORY

<my_acc> entity my_acc is Port ( acc_in : in STD_LOGIC_VECTOR (7 downto 0); clk : in STD_LOGIC; ld_acc : in STD_LOGIC; reset : in STD_LOGIC; acc_out : out STD_LOGIC_VECTOR (7 downto 0)); end my_acc; architecture Behavioral of my_acc is begin process(acc_in, clk, ld_acc, reset) begin if reset='1' then acc_out <="0000"; else if ld_acc='1' then if clk'event and clk='1' then acc_out <=acc_in; end if; end process; end Behavioral;

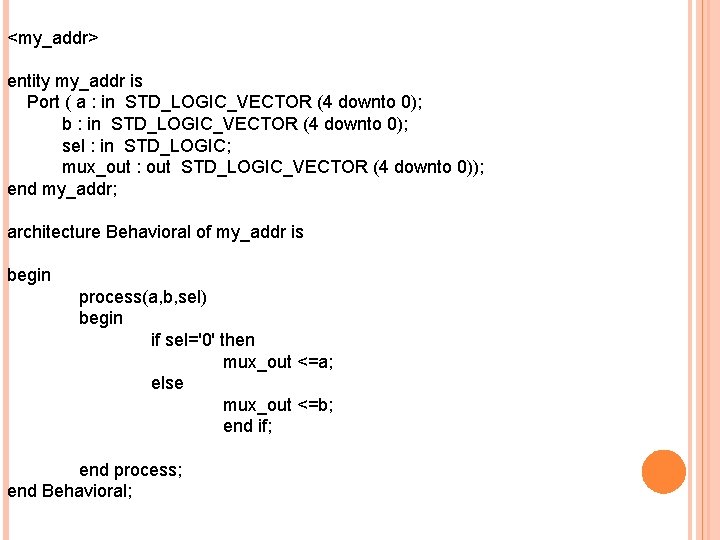

<my_addr> entity my_addr is Port ( a : in STD_LOGIC_VECTOR (4 downto 0); b : in STD_LOGIC_VECTOR (4 downto 0); sel : in STD_LOGIC; mux_out : out STD_LOGIC_VECTOR (4 downto 0)); end my_addr; architecture Behavioral of my_addr is begin process(a, b, sel) begin if sel='0' then mux_out <=a; else mux_out <=b; end if; end process; end Behavioral;

<my_alu> entity my_alu is Port ( a : in STD_LOGIC_VECTOR (7 downto 0); b : in STD_LOGIC_VECTOR (7 downto 0); op : in STD_LOGIC_VECTOR (2 downto 0); alu_out : out STD_LOGIC_VECTOR (7 downto 0)); end my_alu; architecture Behavioral of my_alu is begin process(a, b, op) begin if op="010" then alu_out<=a+b; elsif op="011" then alu_out<=a and b; elsif op="100" then alu_out<=a xor b; elsif op="101" then alu_out<=b; end if; end process; end Behavioral;

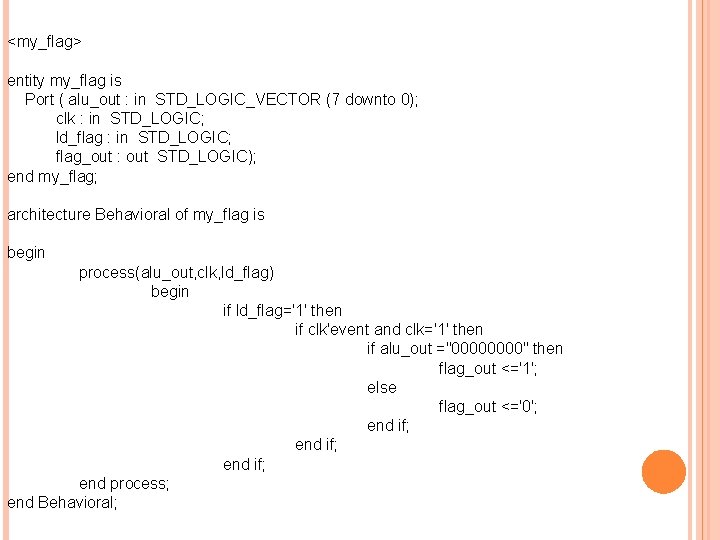

<my_flag> entity my_flag is Port ( alu_out : in STD_LOGIC_VECTOR (7 downto 0); clk : in STD_LOGIC; ld_flag : in STD_LOGIC; flag_out : out STD_LOGIC); end my_flag; architecture Behavioral of my_flag is begin process(alu_out, clk, ld_flag) begin if ld_flag='1' then if clk'event and clk='1' then if alu_out ="0000" then flag_out <='1'; else flag_out <='0'; end if; end process; end Behavioral;

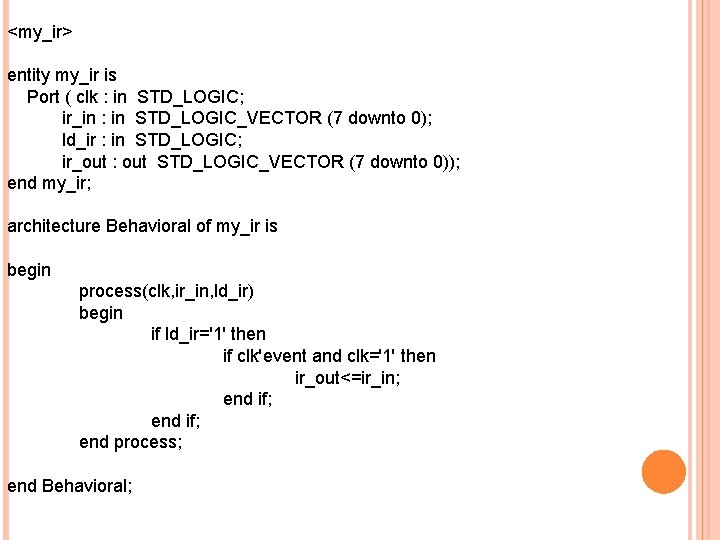

<my_ir> entity my_ir is Port ( clk : in STD_LOGIC; ir_in : in STD_LOGIC_VECTOR (7 downto 0); ld_ir : in STD_LOGIC; ir_out : out STD_LOGIC_VECTOR (7 downto 0)); end my_ir; architecture Behavioral of my_ir is begin process(clk, ir_in, ld_ir) begin if ld_ir='1' then if clk'event and clk='1' then ir_out<=ir_in; end if; end process; end Behavioral;

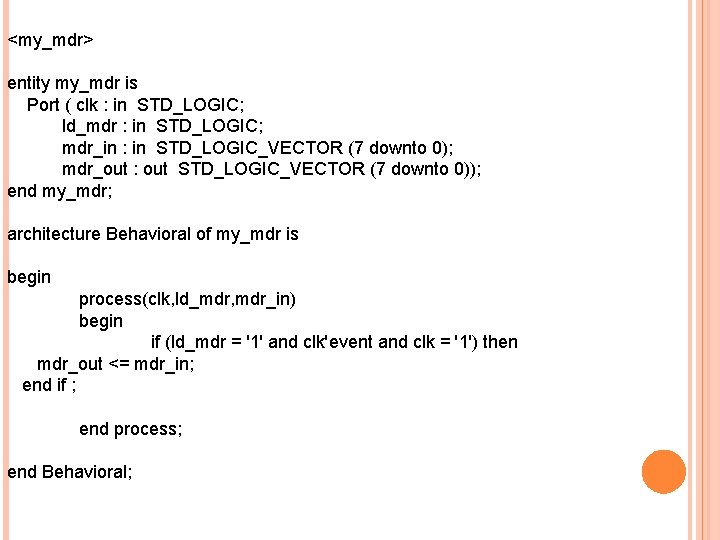

<my_mdr> entity my_mdr is Port ( clk : in STD_LOGIC; ld_mdr : in STD_LOGIC; mdr_in : in STD_LOGIC_VECTOR (7 downto 0); mdr_out : out STD_LOGIC_VECTOR (7 downto 0)); end my_mdr; architecture Behavioral of my_mdr is begin process(clk, ld_mdr, mdr_in) begin if (ld_mdr = '1' and clk'event and clk = '1') then mdr_out <= mdr_in; end if ; end process; end Behavioral;

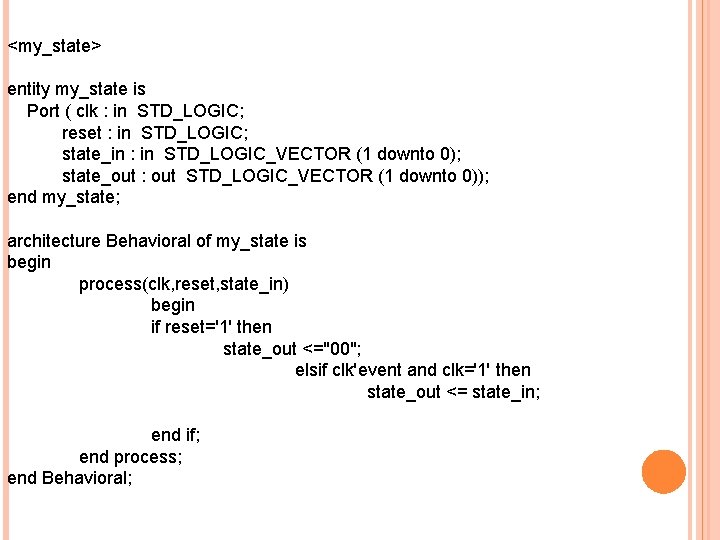

<my_state> entity my_state is Port ( clk : in STD_LOGIC; reset : in STD_LOGIC; state_in : in STD_LOGIC_VECTOR (1 downto 0); state_out : out STD_LOGIC_VECTOR (1 downto 0)); end my_state; architecture Behavioral of my_state is begin process(clk, reset, state_in) begin if reset='1' then state_out <="00"; elsif clk'event and clk='1' then state_out <= state_in; end if; end process; end Behavioral;

<mybi_buf> entity mybi_buf is Port ( buf_in : in STD_LOGIC_VECTOR (7 downto 0); dout : in STD_LOGIC_VECTOR (7 downto 0); en : in STD_LOGIC; din : out STD_LOGIC_VECTOR (7 downto 0); buf_out : out STD_LOGIC_VECTOR (7 downto 0)); end mybi_buf; architecture Behavioral of mybi_buf is begin process(buf_in, dout, en) begin if en='1' then din<=buf_in; else buf_out<=dout; end if; end process; end Behavioral;

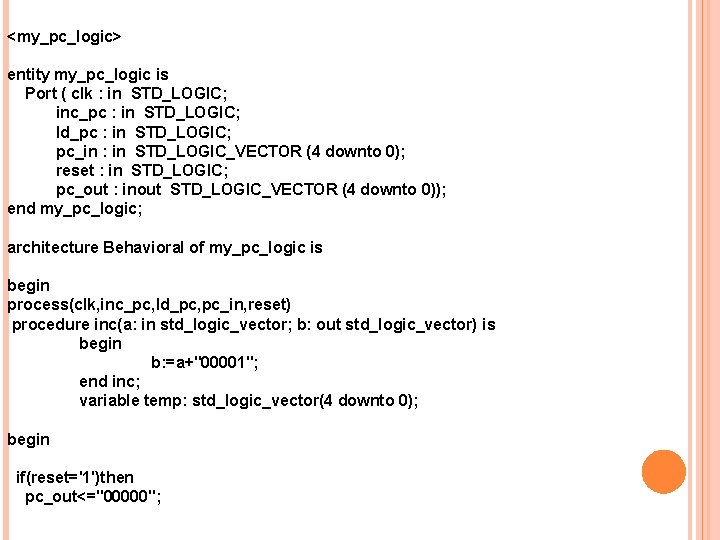

<my_pc_logic> entity my_pc_logic is Port ( clk : in STD_LOGIC; inc_pc : in STD_LOGIC; ld_pc : in STD_LOGIC; pc_in : in STD_LOGIC_VECTOR (4 downto 0); reset : in STD_LOGIC; pc_out : inout STD_LOGIC_VECTOR (4 downto 0)); end my_pc_logic; architecture Behavioral of my_pc_logic is begin process(clk, inc_pc, ld_pc, pc_in, reset) procedure inc(a: in std_logic_vector; b: out std_logic_vector) is begin b: =a+"00001"; end inc; variable temp: std_logic_vector(4 downto 0); begin if(reset='1')then pc_out<="00000";

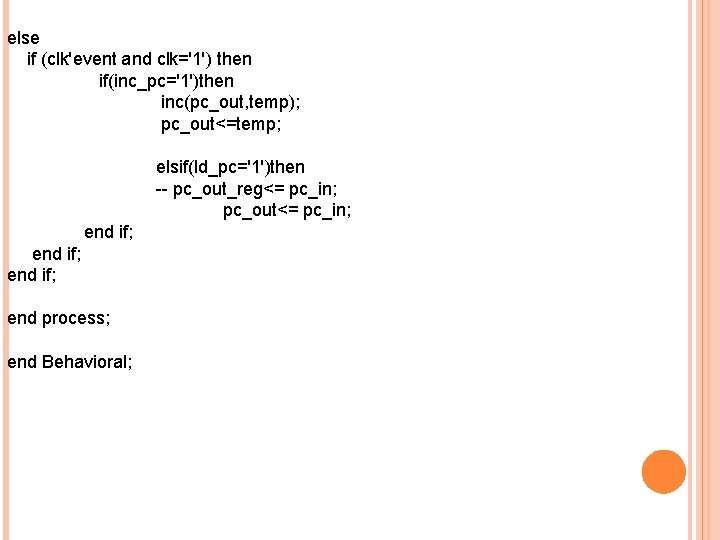

else if (clk'event and clk='1') then if(inc_pc='1')then inc(pc_out, temp); pc_out<=temp; elsif(ld_pc='1')then -- pc_out_reg<= pc_in; pc_out<= pc_in; end if; end process; end Behavioral;

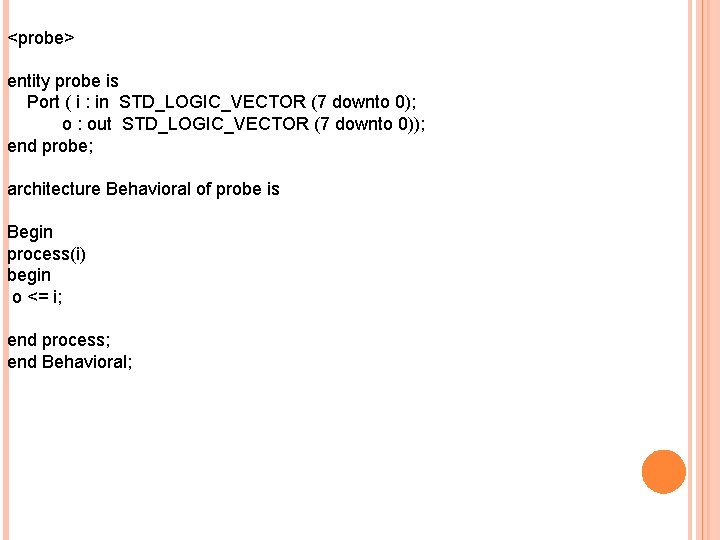

<probe> entity probe is Port ( i : in STD_LOGIC_VECTOR (7 downto 0); o : out STD_LOGIC_VECTOR (7 downto 0)); end probe; architecture Behavioral of probe is Begin process(i) begin o <= i; end process; end Behavioral;

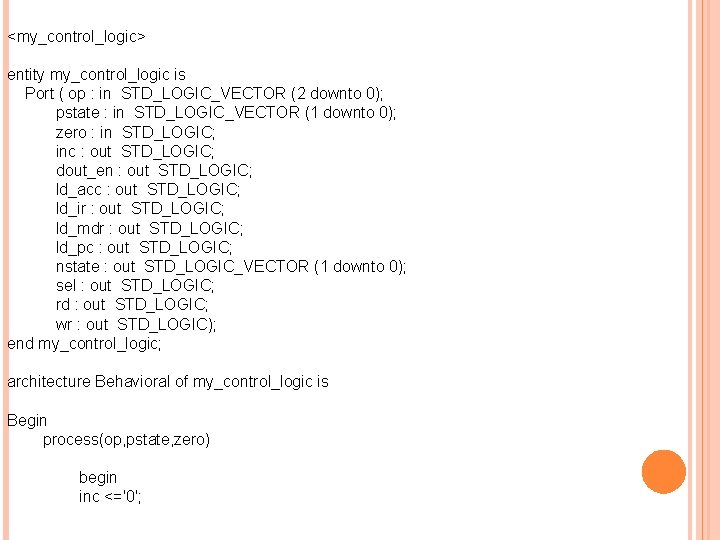

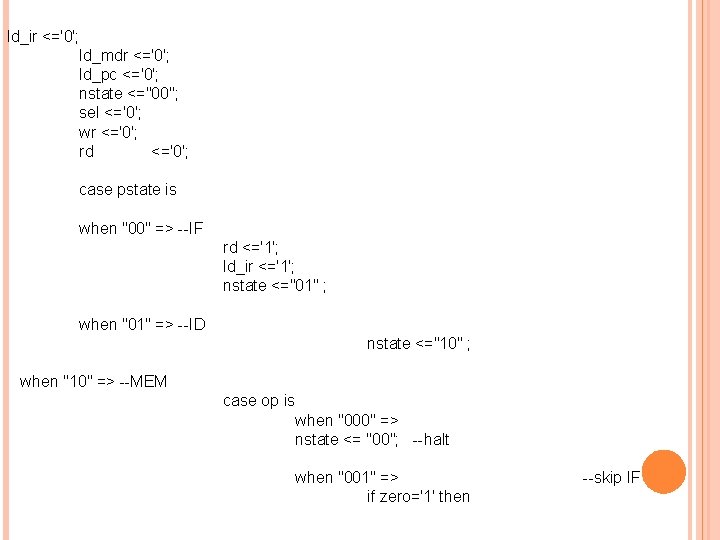

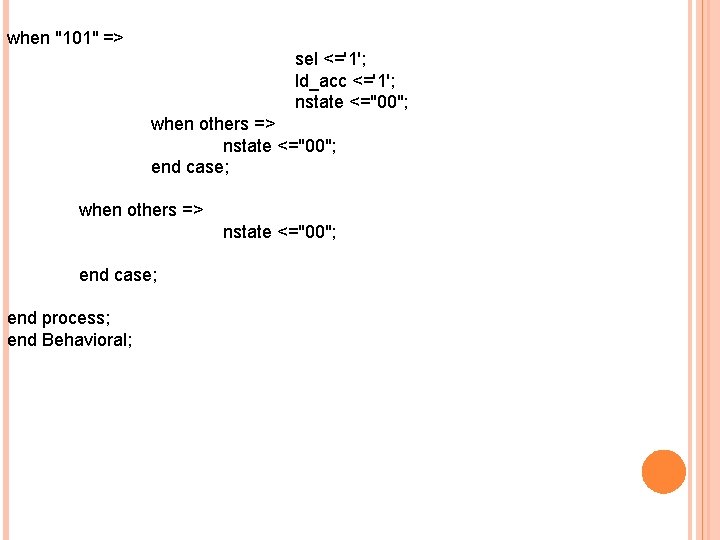

<my_control_logic> entity my_control_logic is Port ( op : in STD_LOGIC_VECTOR (2 downto 0); pstate : in STD_LOGIC_VECTOR (1 downto 0); zero : in STD_LOGIC; inc : out STD_LOGIC; dout_en : out STD_LOGIC; ld_acc : out STD_LOGIC; ld_ir : out STD_LOGIC; ld_mdr : out STD_LOGIC; ld_pc : out STD_LOGIC; nstate : out STD_LOGIC_VECTOR (1 downto 0); sel : out STD_LOGIC; rd : out STD_LOGIC; wr : out STD_LOGIC); end my_control_logic; architecture Behavioral of my_control_logic is Begin process(op, pstate, zero) begin inc <='0';

ld_ir <='0'; ld_mdr <='0'; ld_pc <='0'; nstate <="00"; sel <='0'; wr <='0'; rd <='0'; case pstate is when "00" => --IF rd <='1'; ld_ir <='1'; nstate <="01" ; when "01" => --ID nstate <="10" ; when "10" => --MEM case op is when "000" => nstate <= "00"; --halt when "001" => if zero='1' then --skip IF

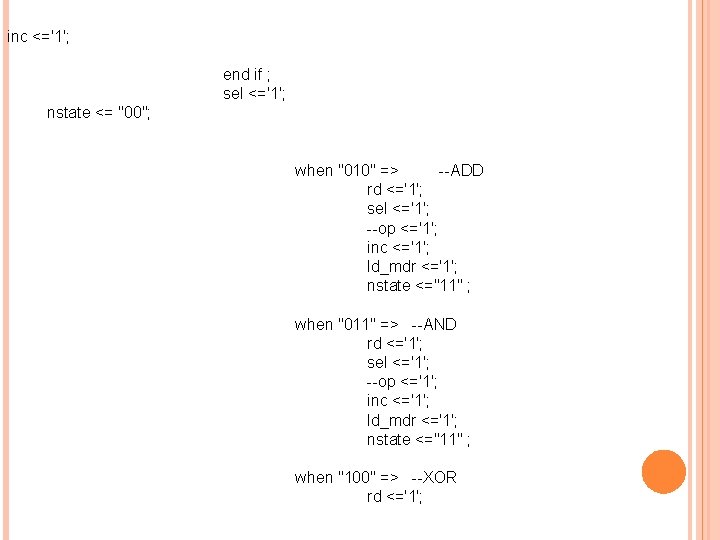

inc <='1'; end if ; sel <='1'; nstate <= "00"; when "010" => --ADD rd <='1'; sel <='1'; --op <='1'; inc <='1'; ld_mdr <='1'; nstate <="11" ; when "011" => --AND rd <='1'; sel <='1'; --op <='1'; inc <='1'; ld_mdr <='1'; nstate <="11" ; when "100" => --XOR rd <='1';

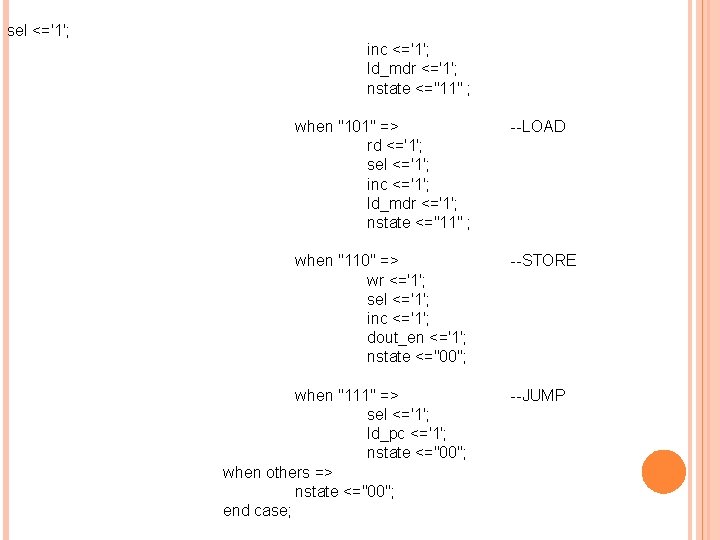

sel <='1'; inc <='1'; ld_mdr <='1'; nstate <="11" ; when "101" => rd <='1'; sel <='1'; inc <='1'; ld_mdr <='1'; nstate <="11" ; --LOAD when "110" => wr <='1'; sel <='1'; inc <='1'; dout_en <='1'; nstate <="00"; --STORE when "111" => sel <='1'; ld_pc <='1'; nstate <="00"; when others => nstate <="00"; end case; --JUMP

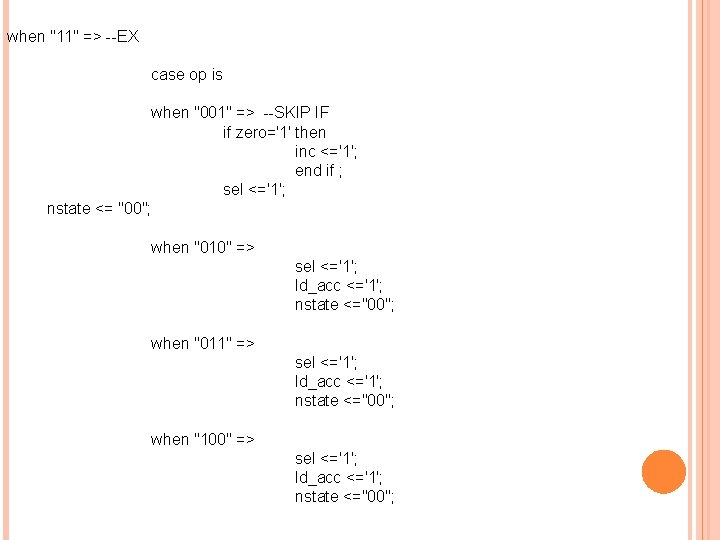

when "11" => --EX case op is when "001" => --SKIP IF if zero='1' then inc <='1'; end if ; sel <='1'; nstate <= "00"; when "010" => sel <='1'; ld_acc <='1'; nstate <="00"; when "011" => sel <='1'; ld_acc <='1'; nstate <="00"; when "100" => sel <='1'; ld_acc <='1'; nstate <="00";

when "101" => sel <='1'; ld_acc <='1'; nstate <="00"; when others => nstate <="00"; end case; end process; end Behavioral;

<clk_inv> entity clk_inv is Port ( a : in STD_LOGIC; b : out STD_LOGIC); end clk_inv; architecture Behavioral of clk_inv is begin b <= not(a); end Behavioral;

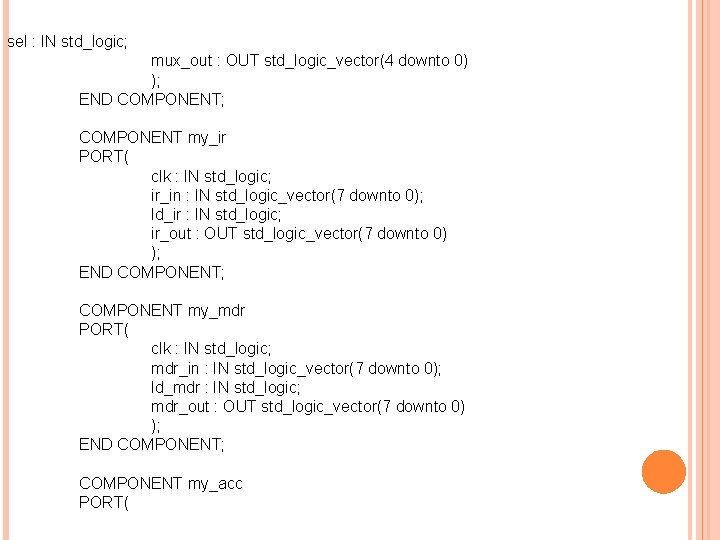

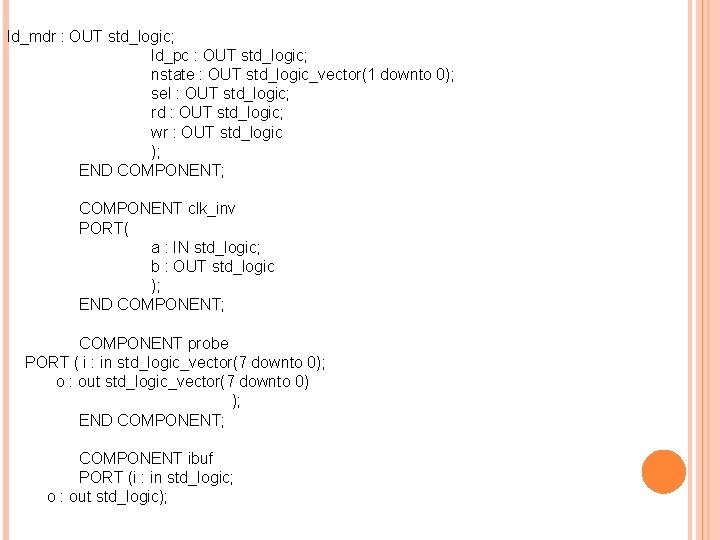

<mycisc> library IEEE; library UNISIM; use IEEE. STD_LOGIC_1164. ALL; use IEEE. std_logic_signed. all; --tmp use IEEE. STD_LOGIC_ARITH. ALL; use IEEE. STD_LOGIC_UNSIGNED. ALL; use UNISIM. VCOMPONENTS. ALL; entity mycisc is Port ( reset_reset : in STD_LOGIC; clk_clk : in STD_LOGIC; digita : out std_logic_vector(6 downto 1); didi : out std_logic_vector(7 downto 0); probe_out : out std_logic_vector(7 downto 0)); end mycisc; architecture Behavioral of mycisc is COMPONENT my_addr PORT( a : IN std_logic_vector(4 downto 0); b : IN std_logic_vector(4 downto 0);

sel : IN std_logic; mux_out : OUT std_logic_vector(4 downto 0) ); END COMPONENT; COMPONENT my_ir PORT( clk : IN std_logic; ir_in : IN std_logic_vector(7 downto 0); ld_ir : IN std_logic; ir_out : OUT std_logic_vector(7 downto 0) ); END COMPONENT; COMPONENT my_mdr PORT( clk : IN std_logic; mdr_in : IN std_logic_vector(7 downto 0); ld_mdr : IN std_logic; mdr_out : OUT std_logic_vector(7 downto 0) ); END COMPONENT; COMPONENT my_acc PORT(

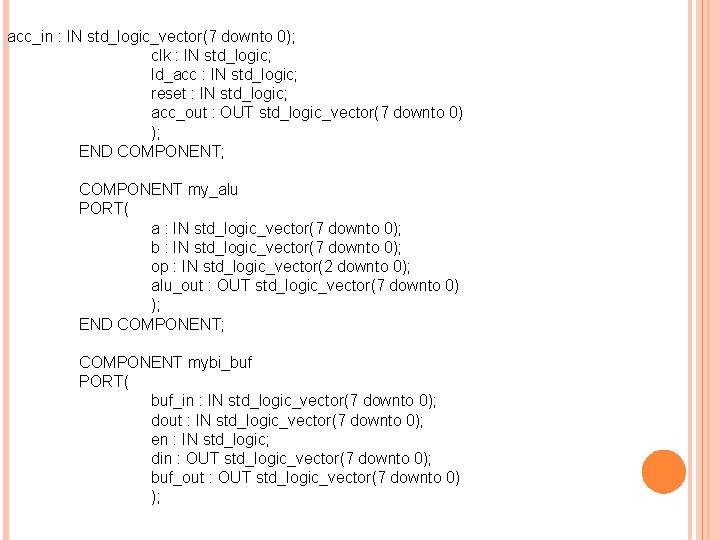

acc_in : IN std_logic_vector(7 downto 0); clk : IN std_logic; ld_acc : IN std_logic; reset : IN std_logic; acc_out : OUT std_logic_vector(7 downto 0) ); END COMPONENT; COMPONENT my_alu PORT( a : IN std_logic_vector(7 downto 0); b : IN std_logic_vector(7 downto 0); op : IN std_logic_vector(2 downto 0); alu_out : OUT std_logic_vector(7 downto 0) ); END COMPONENT; COMPONENT mybi_buf PORT( buf_in : IN std_logic_vector(7 downto 0); dout : IN std_logic_vector(7 downto 0); en : IN std_logic; din : OUT std_logic_vector(7 downto 0); buf_out : OUT std_logic_vector(7 downto 0) );

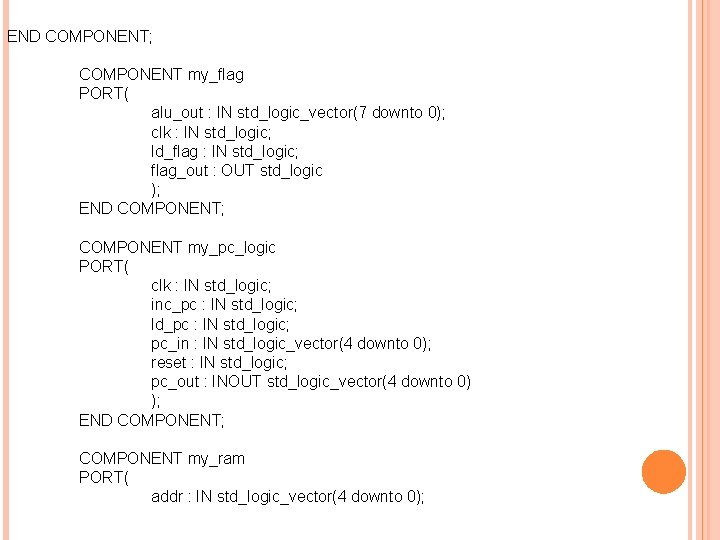

END COMPONENT; COMPONENT my_flag PORT( alu_out : IN std_logic_vector(7 downto 0); clk : IN std_logic; ld_flag : IN std_logic; flag_out : OUT std_logic ); END COMPONENT; COMPONENT my_pc_logic PORT( clk : IN std_logic; inc_pc : IN std_logic; ld_pc : IN std_logic; pc_in : IN std_logic_vector(4 downto 0); reset : IN std_logic; pc_out : INOUT std_logic_vector(4 downto 0) ); END COMPONENT; COMPONENT my_ram PORT( addr : IN std_logic_vector(4 downto 0);

clk : IN std_logic; din : IN std_logic_vector(7 downto 0); we : IN std_logic; dout : OUT std_logic_vector(7 downto 0) ); END COMPONENT; COMPONENT my_state PORT( clk : IN std_logic; reset : IN std_logic; state_in : IN std_logic_vector(1 downto 0); state_out : OUT std_logic_vector(1 downto 0) ); END COMPONENT; COMPONENT my_control_logic PORT( pstate : IN std_logic_vector(1 downto 0); op : IN std_logic_vector(2 downto 0); zero : IN std_logic; inc : OUT std_logic; dout_en : OUT std_logic; ld_acc : OUT std_logic; ld_ir : OUT std_logic;

ld_mdr : OUT std_logic; ld_pc : OUT std_logic; nstate : OUT std_logic_vector(1 downto 0); sel : OUT std_logic; rd : OUT std_logic; wr : OUT std_logic ); END COMPONENT; COMPONENT clk_inv PORT( a : IN std_logic; b : OUT std_logic ); END COMPONENT; COMPONENT probe PORT ( i : in std_logic_vector(7 downto 0); o : out std_logic_vector(7 downto 0) ); END COMPONENT; COMPONENT ibuf PORT (i : in std_logic; o : out std_logic);

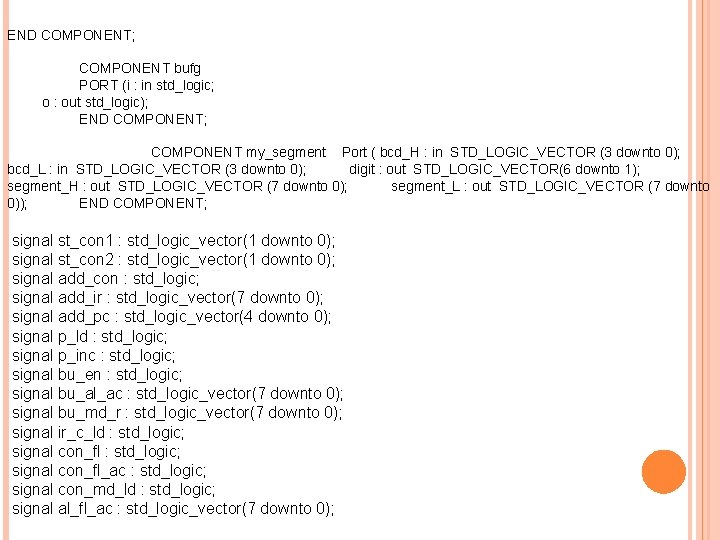

END COMPONENT; COMPONENT bufg PORT (i : in std_logic; o : out std_logic); END COMPONENT; COMPONENT my_segment Port ( bcd_H : in STD_LOGIC_VECTOR (3 downto 0); bcd_L : in STD_LOGIC_VECTOR (3 downto 0); digit : out STD_LOGIC_VECTOR(6 downto 1); segment_H : out STD_LOGIC_VECTOR (7 downto 0); segment_L : out STD_LOGIC_VECTOR (7 downto 0)); END COMPONENT; signal st_con 1 : std_logic_vector(1 downto 0); signal st_con 2 : std_logic_vector(1 downto 0); signal add_con : std_logic; signal add_ir : std_logic_vector(7 downto 0); signal add_pc : std_logic_vector(4 downto 0); signal p_ld : std_logic; signal p_inc : std_logic; signal bu_en : std_logic; signal bu_al_ac : std_logic_vector(7 downto 0); signal bu_md_r : std_logic_vector(7 downto 0); signal ir_c_ld : std_logic; signal con_fl_ac : std_logic; signal con_md_ld : std_logic; signal al_fl_ac : std_logic_vector(7 downto 0);

signal al_md : std_logic_vector(7 downto 0); signal ad_m : std_logic_vector(4 downto 0); signal wrwr : std_logic; signal rdrd : std_logic; signal m_in : std_logic_vector(7 downto 0); signal m_out : std_logic_vector(7 downto 0); signal my_clk : std_logic; signal rclk_clk : std_logic; signal tmp_clk : std_logic; signal int_mem_bus: std_logic_vector (7 downto 0); signal as: std_logic_vector (7 downto 0); begin u 1: my_addr port map(sel=>add_con, b=>add_ir(4 downto 0), a=>add_pc, mux_out=>ad_m); u 2: my_ir port map(clk=>rclk_clk, ir_in=>bu_md_r, ld_ir=>ir_c_ld, ir_out=>add_ir); u 3: my_mdr port map(mdr_out=>al_md, mdr_in=>bu_md_r, ld_mdr=>con_md_ld, clk=>rclk_clk); u 4: my_acc port map(acc_in=>al_fl_ac, ld_acc=>con_fl_ac, reset=>reset_reset, clk=>rclk_clk, acc_out=>bu_al_ac); u 5: my_alu port map(a=>bu_al_ac, b=>al_md, op=>add_ir(7 downto 5), alu_out=>al_fl_ac); u 6: mybi_buf port map(en=>bu_en, buf_in=>bu_al_ac, buf_out=>bu_md_r, din=>m_in, dout=>m_out); u 7: my_flag port map(alu_out=>al_fl_ac, ld_flag=>con_fl_ac, clk=>rclk_clk, flag_out=>con_fl);

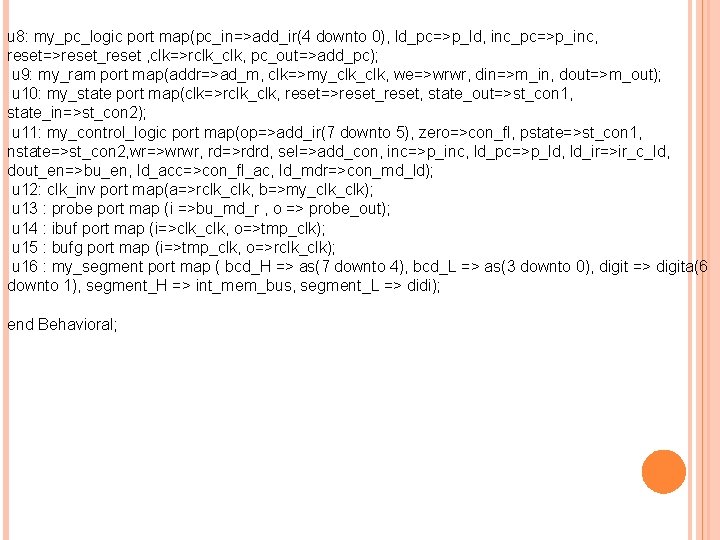

u 8: my_pc_logic port map(pc_in=>add_ir(4 downto 0), ld_pc=>p_ld, inc_pc=>p_inc, reset=>reset_reset , clk=>rclk_clk, pc_out=>add_pc); u 9: my_ram port map(addr=>ad_m, clk=>my_clk, we=>wrwr, din=>m_in, dout=>m_out); u 10: my_state port map(clk=>rclk_clk, reset=>reset_reset, state_out=>st_con 1, state_in=>st_con 2); u 11: my_control_logic port map(op=>add_ir(7 downto 5), zero=>con_fl, pstate=>st_con 1, nstate=>st_con 2, wr=>wrwr, rd=>rdrd, sel=>add_con, inc=>p_inc, ld_pc=>p_ld, ld_ir=>ir_c_ld, dout_en=>bu_en, ld_acc=>con_fl_ac, ld_mdr=>con_md_ld); u 12: clk_inv port map(a=>rclk_clk, b=>my_clk); u 13 : probe port map (i =>bu_md_r , o => probe_out); u 14 : ibuf port map (i=>clk_clk, o=>tmp_clk); u 15 : bufg port map (i=>tmp_clk, o=>rclk_clk); u 16 : my_segment port map ( bcd_H => as(7 downto 4), bcd_L => as(3 downto 0), digit => digita(6 downto 1), segment_H => int_mem_bus, segment_L => didi); end Behavioral;

- Slides: 41