MCPPMT test bench at LAL D Breton L

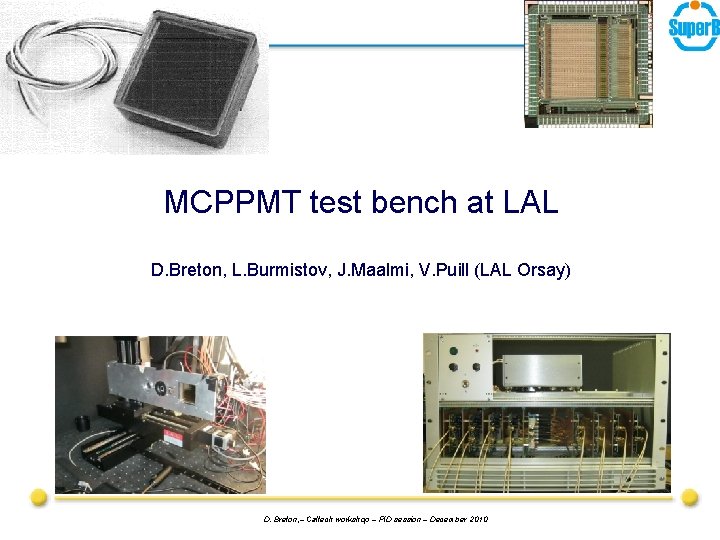

MCPPMT test bench at LAL D. Breton, L. Burmistov, J. Maalmi, V. Puill (LAL Orsay) D. Breton, – Caltech workshop – PID session – December 2010

Introduction • In view between others of Super. B PID TOF, we decided to mount a high speed PMT/Si. PM test facility at LAL. • Therefore we built a second 16 -channel acquisition crate identical to that used at SLAC on the CRT for the two bars – Same features except that the Wave. Catcher boards have an internal gain of 10 and AC coupling => idea is to avoid buying amplifiers (6 k€) – We also kept boards with DC coupling and gain 1 which allowed us to perform thorough time measurements which we had no time to perform before leaving for SLAC – Almost no difference was seen in time performance between gain 1 and gain 10 boards because all the elements implied therein are located behind where the gain is applied to the signal • This crate will first be used to read out 16 channels of MCPPMT (BURLE 85012 - 25µ) D. Breton, – Caltech workshop – PID session – December 2010

Introduction Reminder of the technical challenge for the electronics: to keep the 10 ps precision at the crate level … The crate is based on 8 two-channel Wave. Catcher V 5 boards: 1. The system works with a common synchronous clock § There we take benefit of the external clock input of the Wave. Catcher V 5 2. It is self-triggered but it also has to be synchronized with its environment § Rate is low thus computer time tagging of events is adequate 3. Like the Wave. Catcher, data acquisition is based on 480 Mbits/s USB. D. Breton, – Caltech workshop – PID session – December 2010

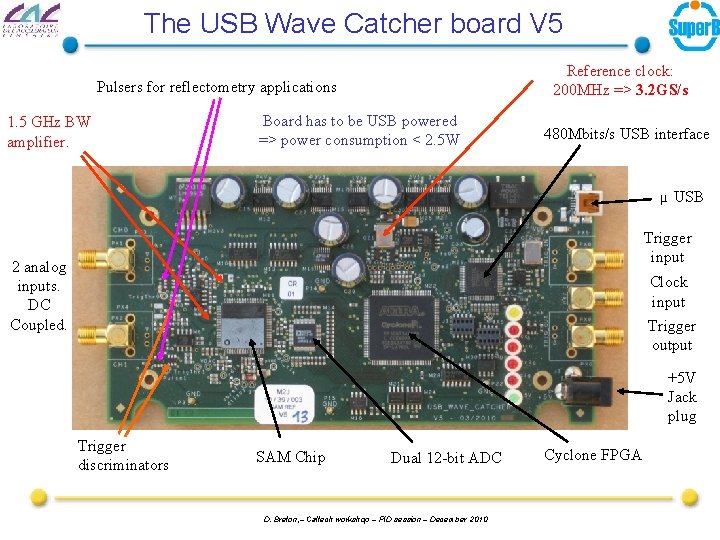

The USB Wave Catcher board V 5 Reference clock: 200 MHz => 3. 2 GS/s Pulsers for reflectometry applications 1. 5 GHz BW amplifier. Board has to be USB powered => power consumption < 2. 5 W 480 Mbits/s USB interface µ USB Trigger input 2 analog inputs. DC Coupled. Clock input Trigger output +5 V Jack plug Trigger discriminators SAM Chip Dual 12 -bit ADC D. Breton, – Caltech workshop – PID session – December 2010 Cyclone FPGA

Clock and control board (1) From Wave. Catchers To Wave. Catchers From Laser Trigger is done in coincidence mode : when the controller board detects a coincidence between an external trigger from laser and a hit in one of the sixteen channels D. Breton, – Caltech workshop – PID session – December 2010

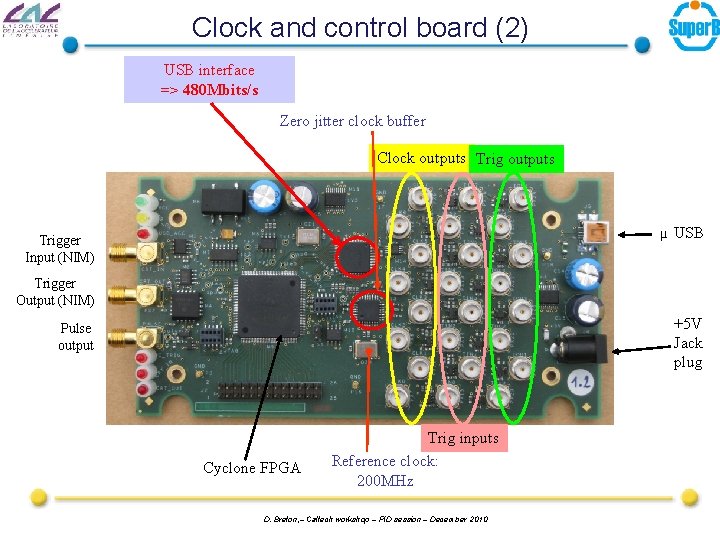

Clock and control board (2) USB interface => 480 Mbits/s Zero jitter clock buffer Clock outputs Trig outputs µ USB Trigger Input (NIM) Trigger Output (NIM) +5 V Jack plug Pulse output Cyclone FPGA Trig inputs Reference clock: 200 MHz D. Breton, – Caltech workshop – PID session – December 2010

Full crate D. Breton, – Caltech workshop – PID session – December 2010

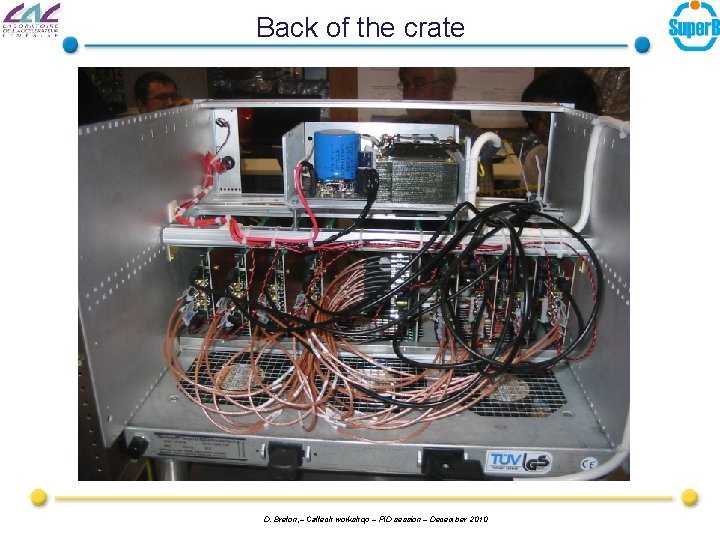

Back of the crate D. Breton, – Caltech workshop – PID session – December 2010

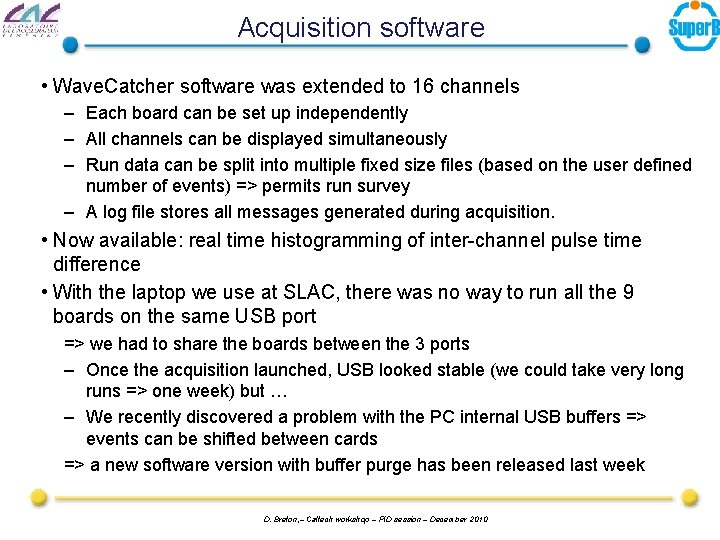

Acquisition software • Wave. Catcher software was extended to 16 channels – Each board can be set up independently – All channels can be displayed simultaneously – Run data can be split into multiple fixed size files (based on the user defined number of events) => permits run survey – A log file stores all messages generated during acquisition. • Now available: real time histogramming of inter-channel pulse time difference • With the laptop we use at SLAC, there was no way to run all the 9 boards on the same USB port => we had to share the boards between the 3 ports – Once the acquisition launched, USB looked stable (we could take very long runs => one week) but … – We recently discovered a problem with the PC internal USB buffers => events can be shifted between cards => a new software version with buffer purge has been released last week D. Breton, – Caltech workshop – PID session – December 2010

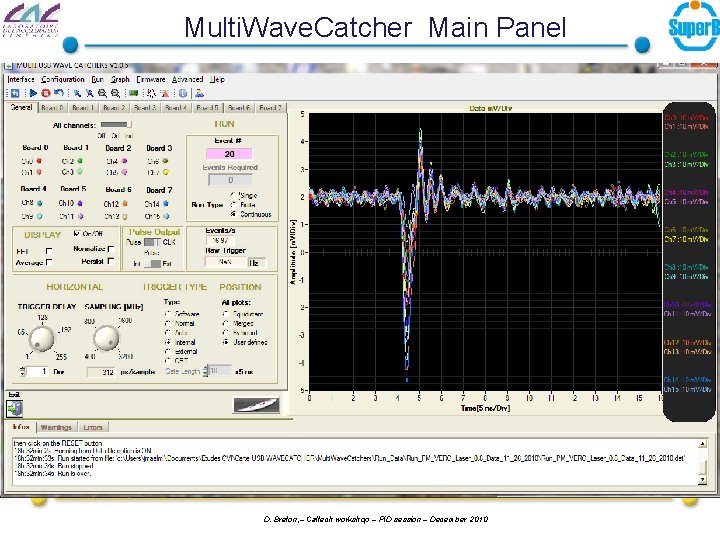

Multi. Wave. Catcher Main Panel D. Breton, – Caltech workshop – PID session – December 2010

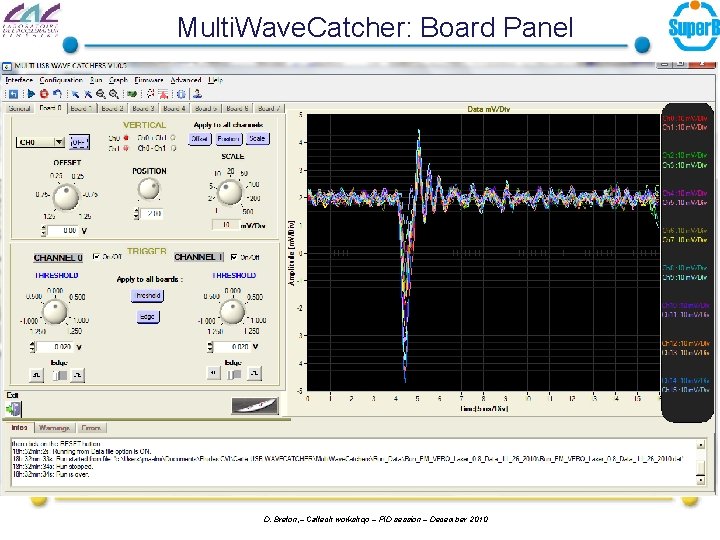

Multi. Wave. Catcher: Board Panel D. Breton, – Caltech workshop – PID session – December 2010

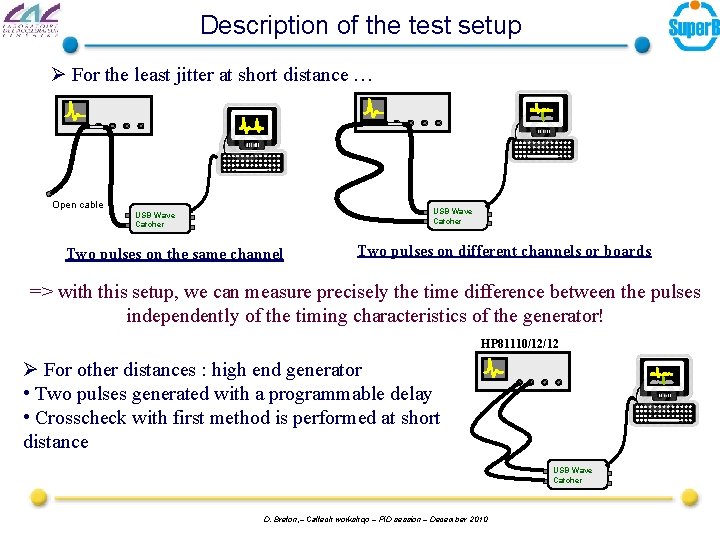

Description of the test setup Ø For the least jitter at short distance … Open cable USB Wave Catcher Two pulses on the same channel Two pulses on different channels or boards => with this setup, we can measure precisely the time difference between the pulses independently of the timing characteristics of the generator! HP 81110/12/12 Ø For other distances : high end generator • Two pulses generated with a programmable delay • Crosscheck with first method is performed at short distance USB Wave Catcher D. Breton, – Caltech workshop – PID session – December 2010

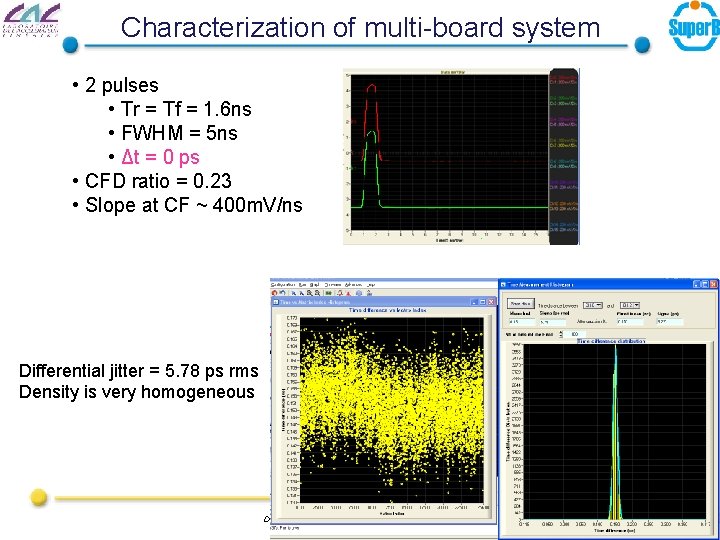

Characterization of multi-board system • 2 pulses • Tr = Tf = 1. 6 ns • FWHM = 5 ns • Δt = 0 ps • CFD ratio = 0. 23 • Slope at CF ~ 400 m. V/ns Differential jitter = 5. 78 ps rms Density is very homogeneous D. Breton, – Caltech workshop – PID session – December 2010

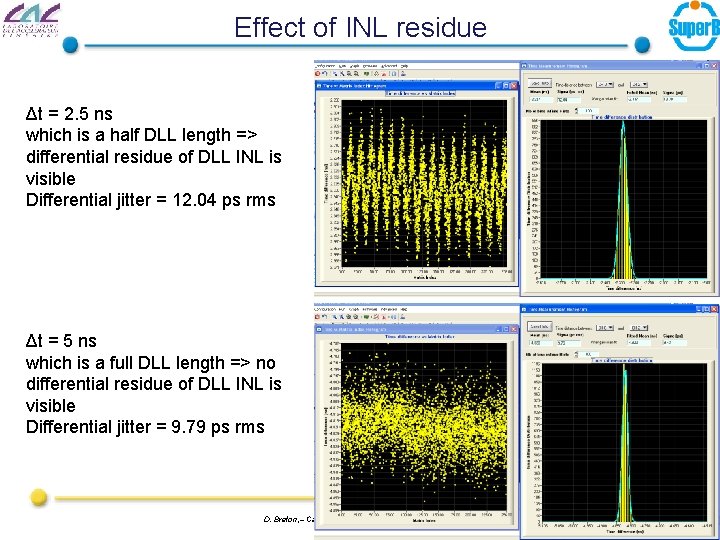

Effect of INL residue Δt = 2. 5 ns which is a half DLL length => differential residue of DLL INL is visible Differential jitter = 12. 04 ps rms Δt = 5 ns which is a full DLL length => no differential residue of DLL INL is visible Differential jitter = 9. 79 ps rms D. Breton, – Caltech workshop – PID session – December 2010

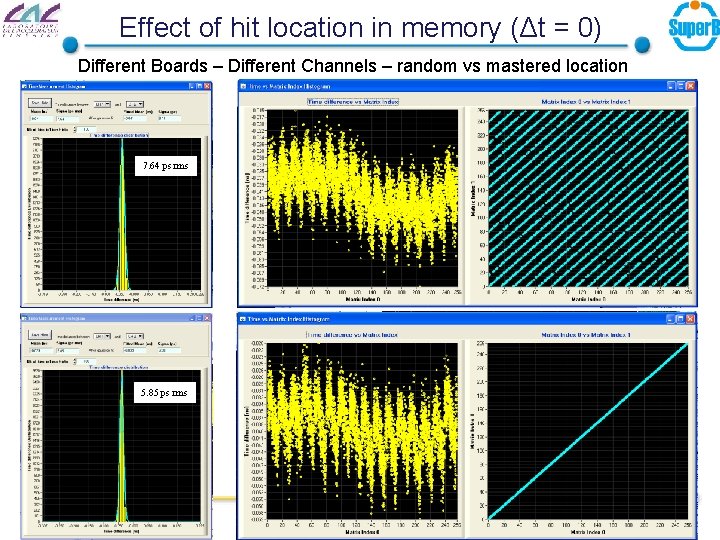

Effect of hit location in memory (Δt = 0) Different Boards – Different Channels – random vs mastered location 7. 64 ps rms 5. 85 ps rms D. Breton, – Caltech workshop – PID session – December 2010

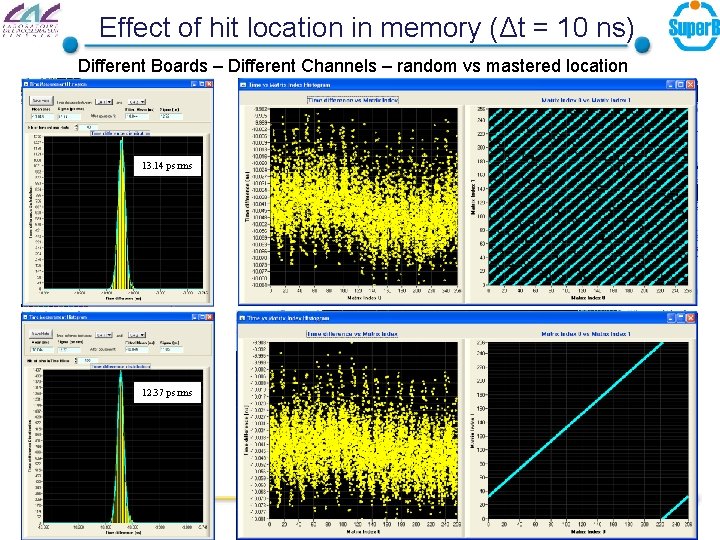

Effect of hit location in memory (Δt = 10 ns) Different Boards – Different Channels – random vs mastered location 13. 14 ps rms 12. 37 ps rms D. Breton, – Caltech workshop – PID session – December 2010

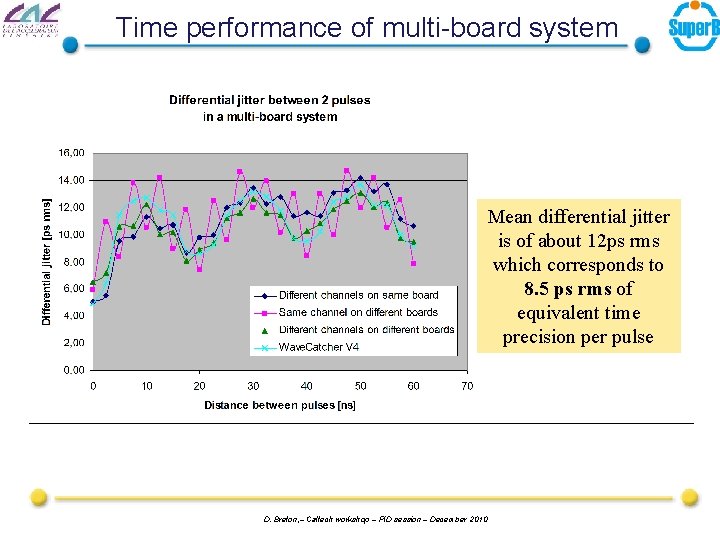

Time performance of multi-board system Mean differential jitter is of about 12 ps rms which corresponds to 8. 5 ps rms of equivalent time precision per pulse D. Breton, – Caltech workshop – PID session – December 2010

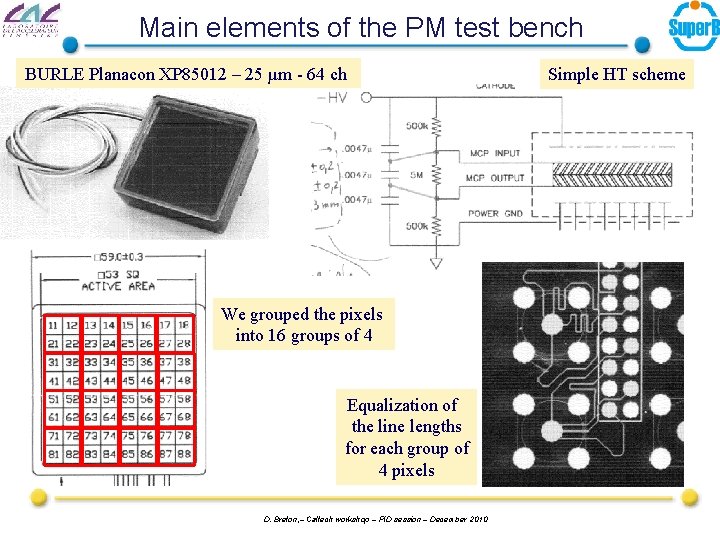

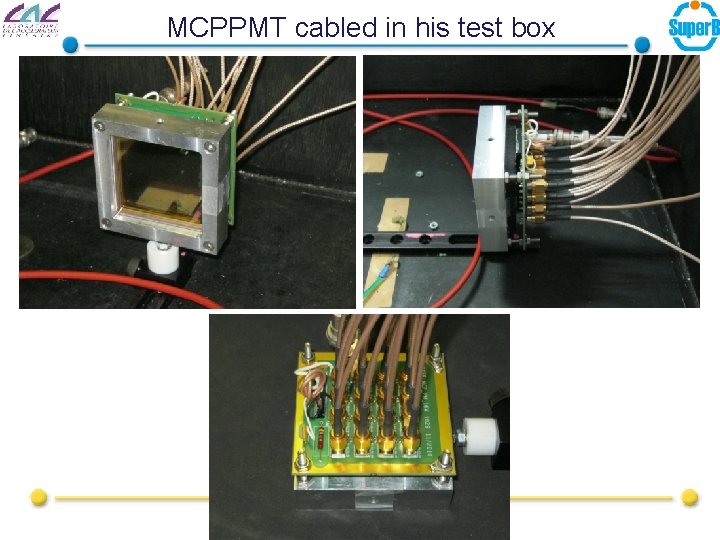

Main elements of the PM test bench BURLE Planacon XP 85012 – 25 µm - 64 ch We grouped the pixels into 16 groups of 4 Equalization of the line lengths for each group of 4 pixels D. Breton, – Caltech workshop – PID session – December 2010 Simple HT scheme

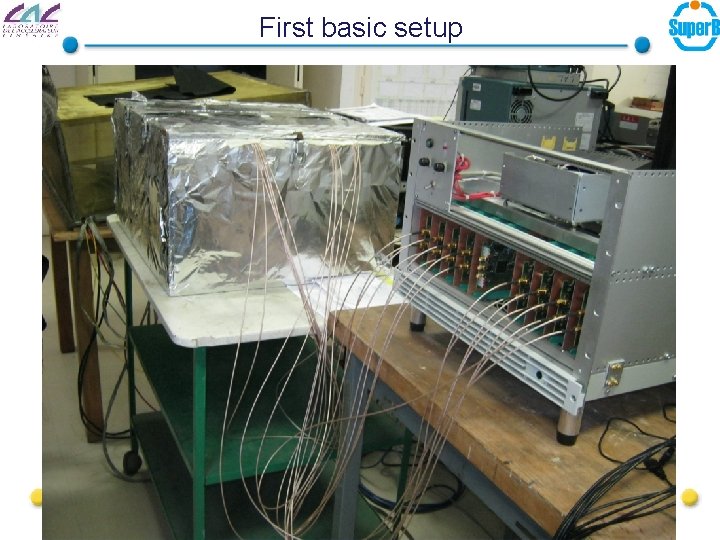

First basic setup D. Breton, – Caltech workshop – PID session – December 2010

MCPPMT cabled in his test box D. Breton, – Caltech workshop – PID session – December 2010

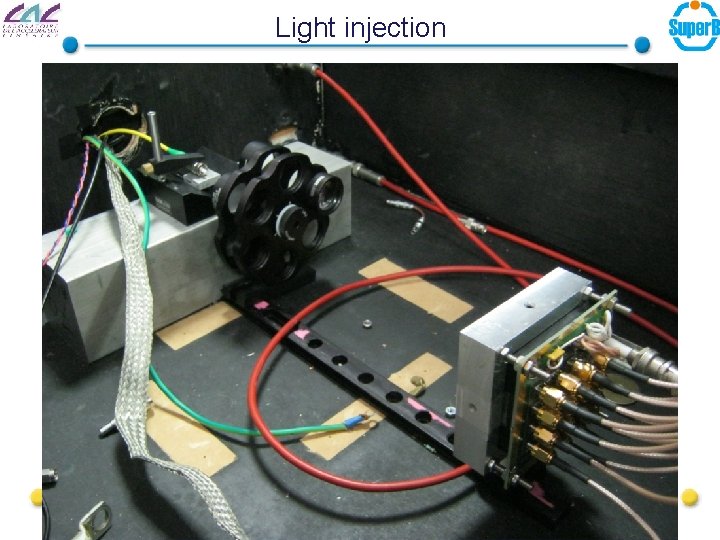

Light injection D. Breton, – Caltech workshop – PID session – December 2010

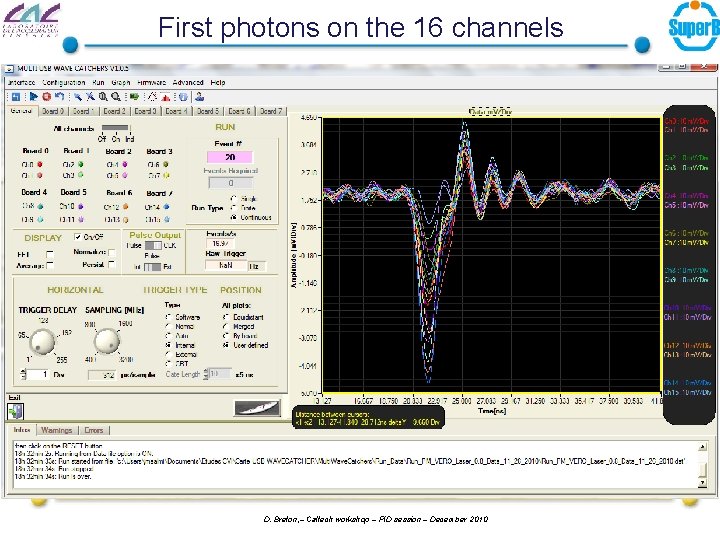

First photons on the 16 channels D. Breton, – Caltech workshop – PID session – December 2010

Moving toward the scanning setup (1) D. Breton, – Caltech workshop – PID session – December 2010

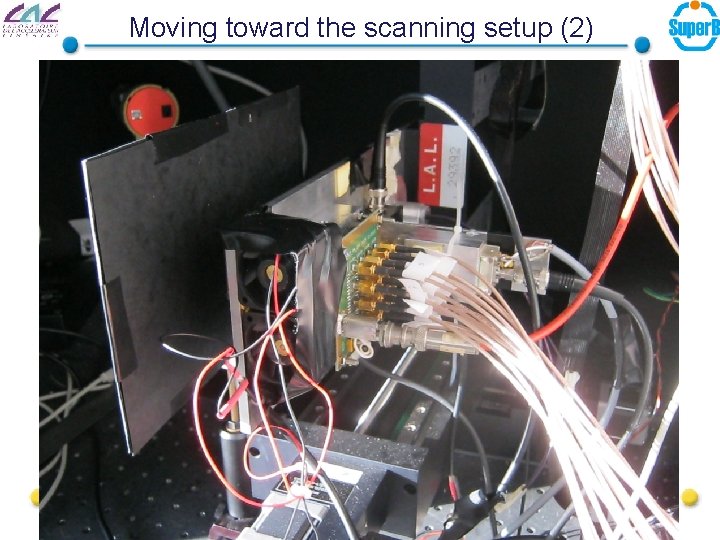

Moving toward the scanning setup (2) D. Breton, – Caltech workshop – PID session – December 2010

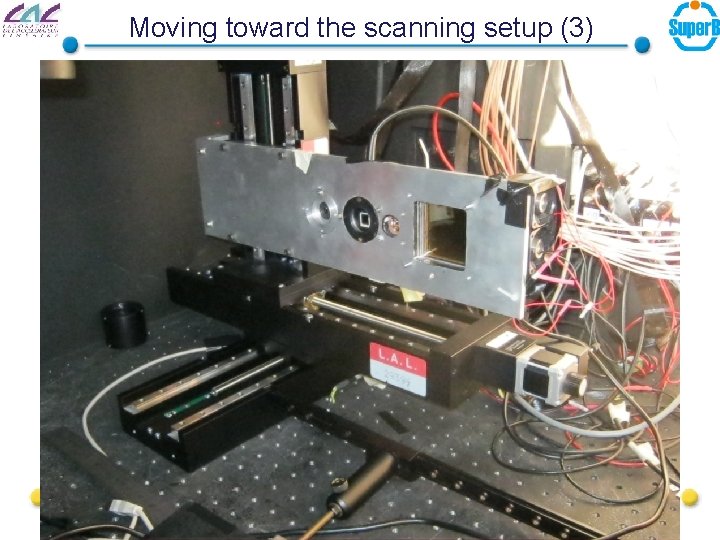

Moving toward the scanning setup (3) D. Breton, – Caltech workshop – PID session – December 2010

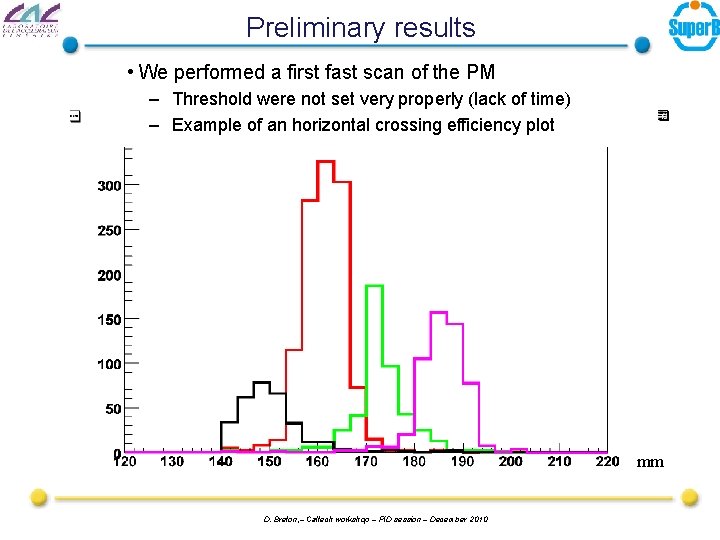

Preliminary results • We performed a first fast scan of the PM – Threshold were not set very properly (lack of time) – Example of an horizontal crossing efficiency plot Plot de Leonid mm D. Breton, – Caltech workshop – PID session – December 2010

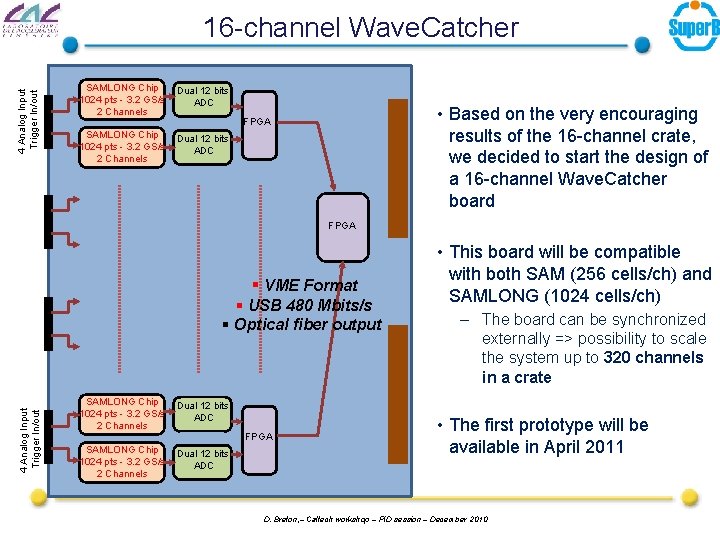

4 Analog Input Trigger In/out 16 -channel Wave. Catcher SAMLONG Chip 1024 pts - 3. 2 GS/s 2 Channels Dual 12 bits ADC • Based on the very encouraging results of the 16 -channel crate, we decided to start the design of a 16 -channel Wave. Catcher board FPGA § VME Format 4 Analog Input Trigger In/out § USB 480 Mbits/s § Optical fiber output SAMLONG Chip 1024 pts - 3. 2 GS/s 2 Channels Dual 12 bits ADC FPGA • This board will be compatible with both SAM (256 cells/ch) and SAMLONG (1024 cells/ch) – The board can be synchronized externally => possibility to scale the system up to 320 channels in a crate • The first prototype will be available in April 2011 D. Breton, – Caltech workshop – PID session – December 2010

Conclusion • We built a second 16 -channel USB Wave Catcher crate for our new MCPPMT/Si. PM scanning setup at LAL. • This allowed us to perform thorough measurements on the electronics, which we had no time to do before the first crate left for SLAC in September • Timing measurements showed a stable single pulse resolution < 10 ps rms • The crate has been associated to a BURLE 25µ MCPPMT and mounted on the scanning setup • This allowed us to solve a serious USB buffer problem inside the PC which was a source of desynchronization of the events between the boards • First results look promising • Preliminary map has been produced • Bench still has to be optimized • Is a gain 10 sufficient ? D. Breton, – Caltech workshop – PID session – December 2010

- Slides: 28