mc Mikrocomputertechnik Kapitel 4 Herzlich Willkommen Prof Jrgen

- Slides: 31

mc Mikrocomputertechnik - Kapitel 4 Herzlich Willkommen Prof. Jürgen Walter Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 1

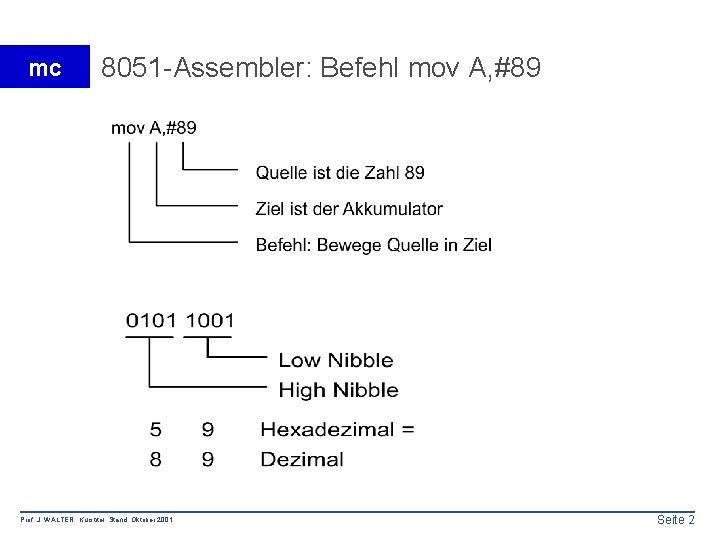

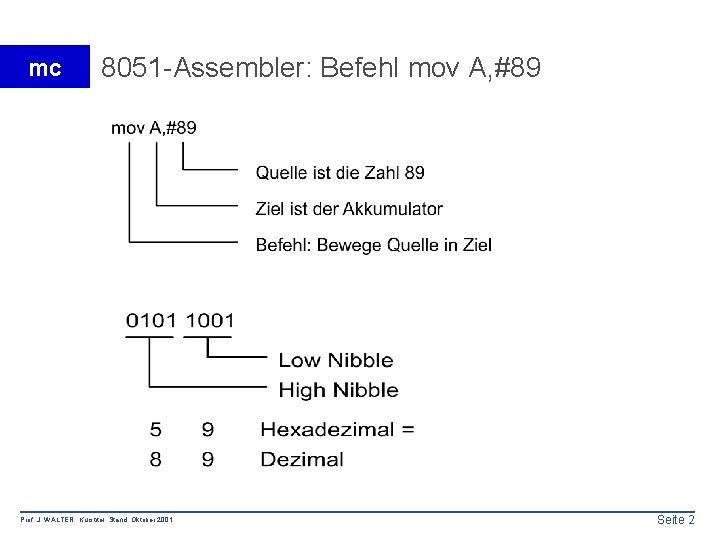

mc 8051 -Assembler: Befehl mov A, #89 Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 2

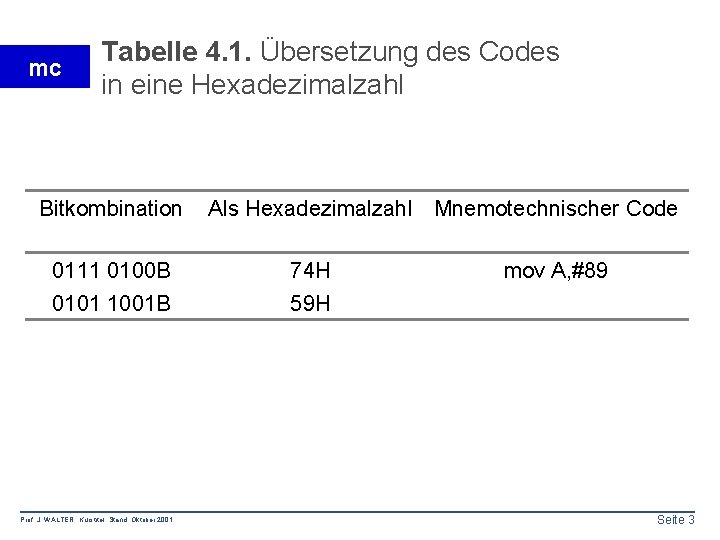

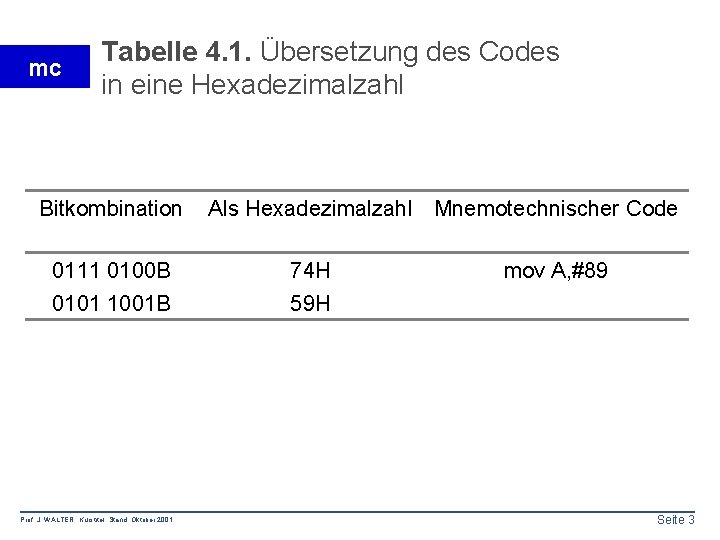

mc Tabelle 4. 1. Übersetzung des Codes in eine Hexadezimalzahl Bitkombination Als Hexadezimalzahl Mnemotechnischer Code 0111 0100 B 74 H 0101 1001 B 59 H Prof. J. WALTER Kurstitel Stand: Oktober 2001 mov A, #89 Seite 3

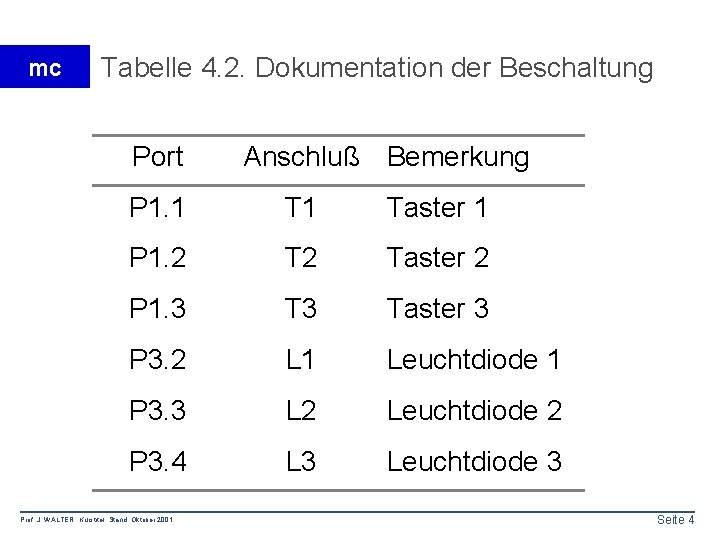

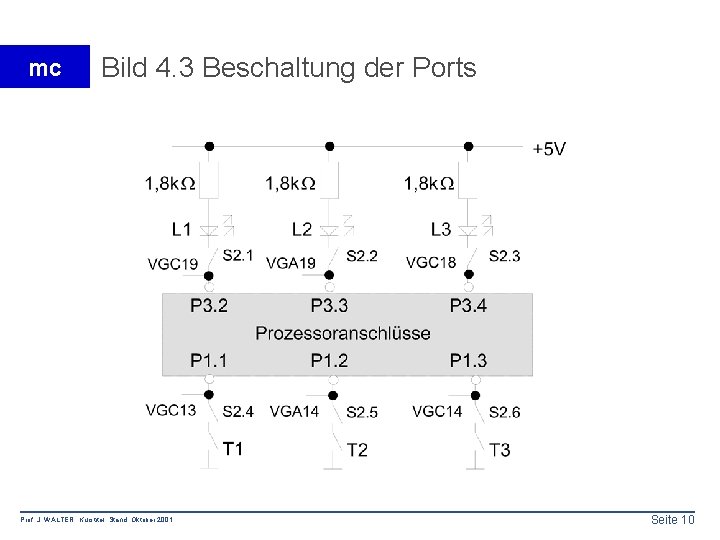

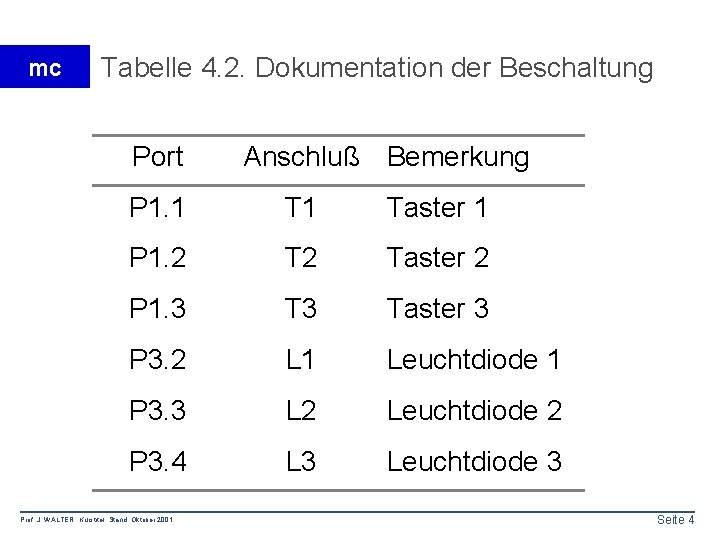

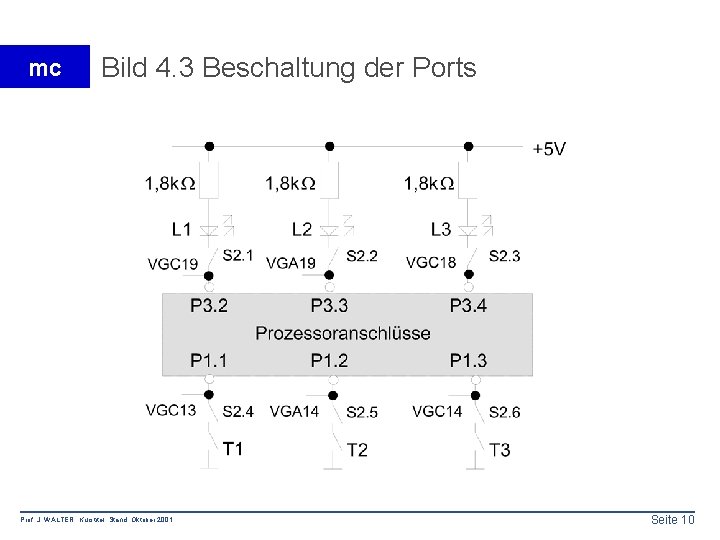

mc Tabelle 4. 2. Dokumentation der Beschaltung Port Anschluß Bemerkung P 1. 1 Taster 1 P 1. 2 Taster 2 P 1. 3 Taster 3 P 3. 2 L 1 Leuchtdiode 1 P 3. 3 L 2 Leuchtdiode 2 P 3. 4 L 3 Leuchtdiode 3 Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 4

mc Bild 4. 4. Struktogramm: EIN_AUS. ASM Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 5

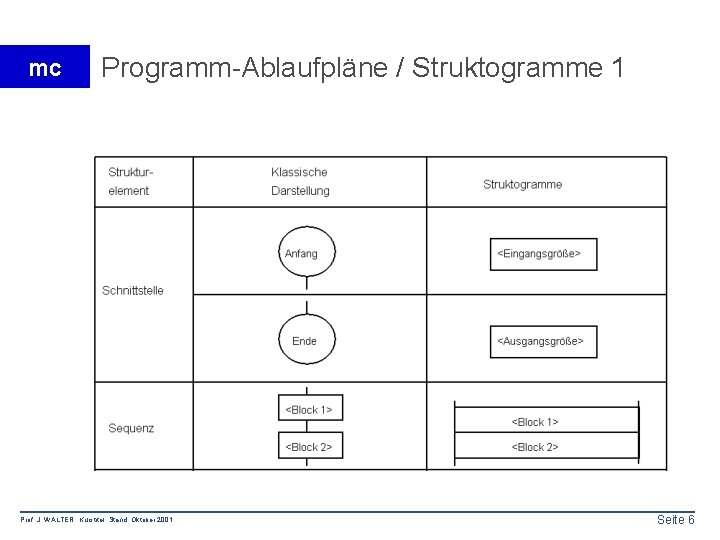

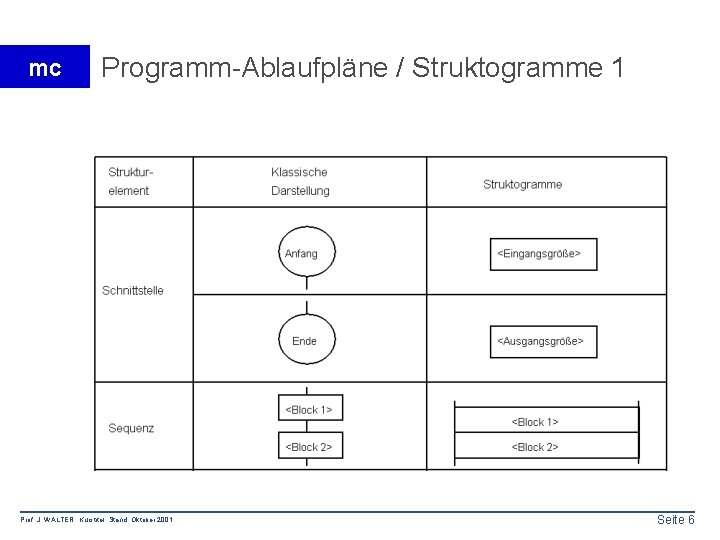

mc Programm-Ablaufpläne / Struktogramme 1 Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 6

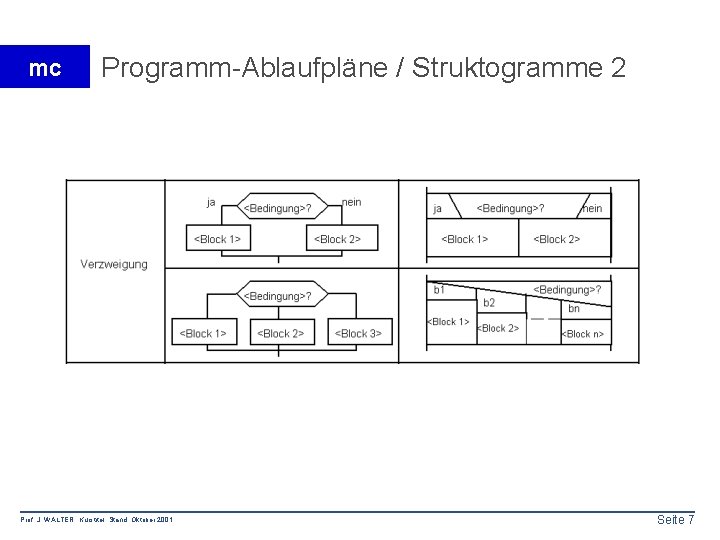

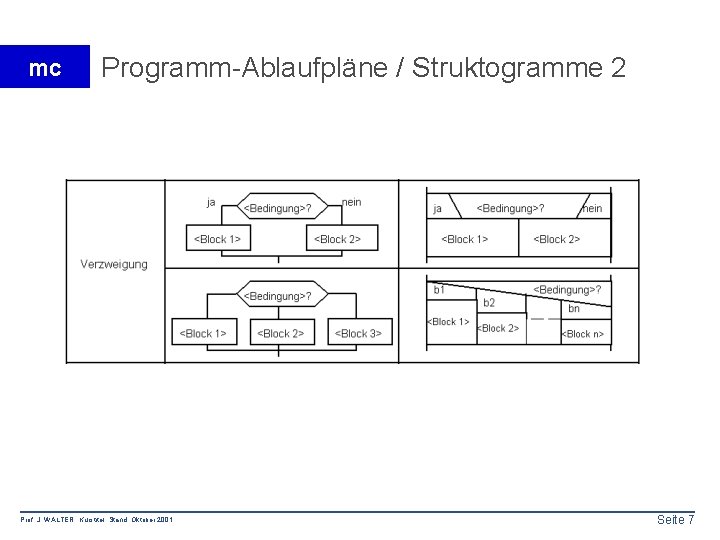

mc Programm-Ablaufpläne / Struktogramme 2 Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 7

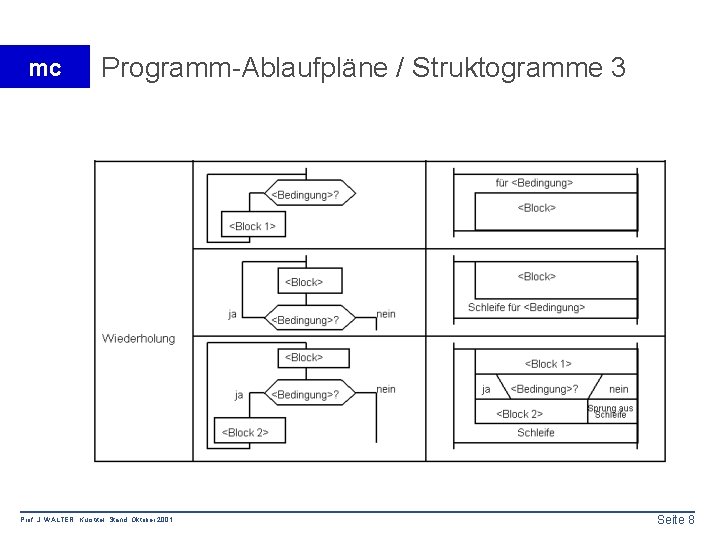

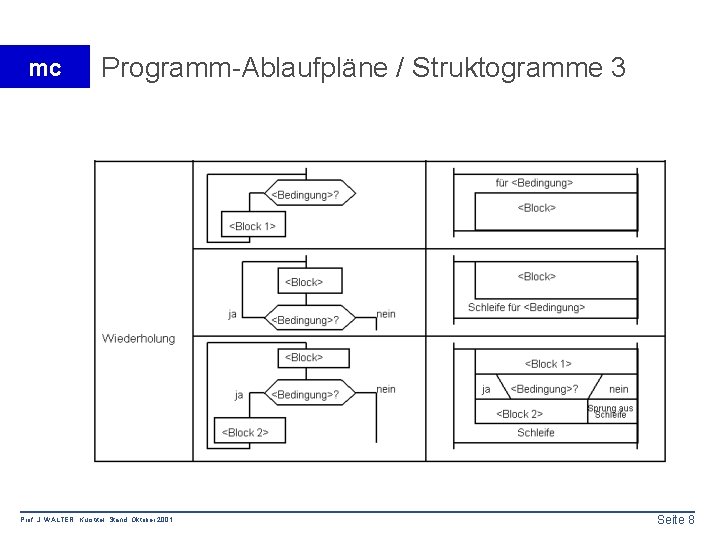

mc Programm-Ablaufpläne / Struktogramme 3 Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 8

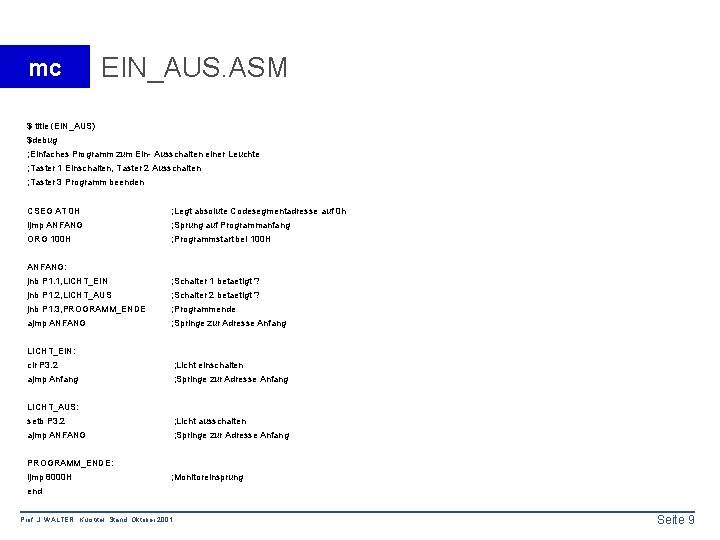

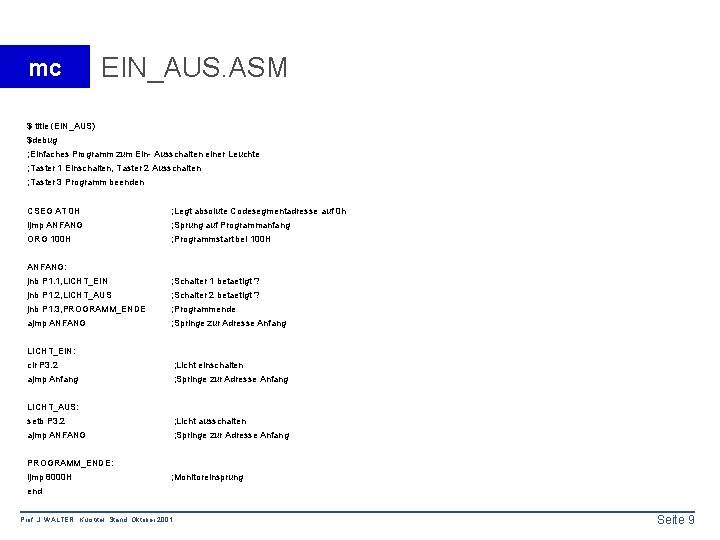

mc EIN_AUS. ASM $ title (EIN_AUS) $debug ; Einfaches Programm zum Ein- Ausschalten einer Leuchte ; Taster 1 Einschalten, Taster 2 Ausschalten ; Taster 3 Programm beenden CSEG AT 0 H ; Legt absolute Codesegmentadresse auf 0 h ljmp ANFANG ; Sprung auf Programmanfang ORG 100 H ; Programmstart bei 100 H ANFANG: jnb P 1. 1, LICHT_EIN ; Schalter 1 betaetigt ? jnb P 1. 2, LICHT_AUS ; Schalter 2 betaetigt ? jnb P 1. 3, PROGRAMM_ENDE ; Programmende ajmp ANFANG ; Springe zur Adresse Anfang LICHT_EIN: clr P 3. 2 ; Licht einschalten ajmp Anfang ; Springe zur Adresse Anfang LICHT_AUS: setb P 3. 2 ; Licht ausschalten ajmp ANFANG ; Springe zur Adresse Anfang PROGRAMM_ENDE: ljmp 8000 H ; Monitoreinsprung end Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 9

mc Bild 4. 3 Beschaltung der Ports Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 10

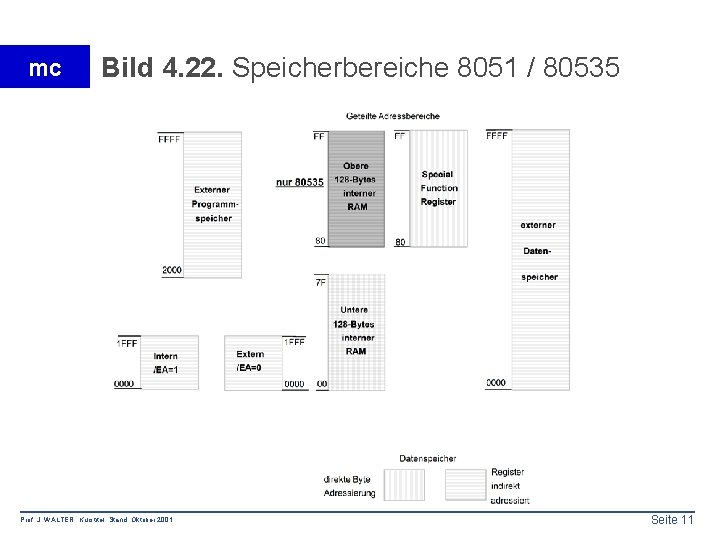

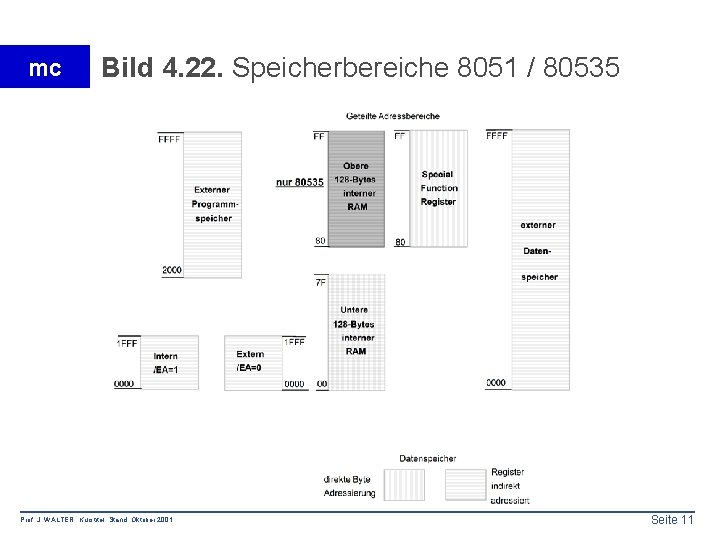

mc Bild 4. 22. Speicherbereiche 8051 / 80535 Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 11

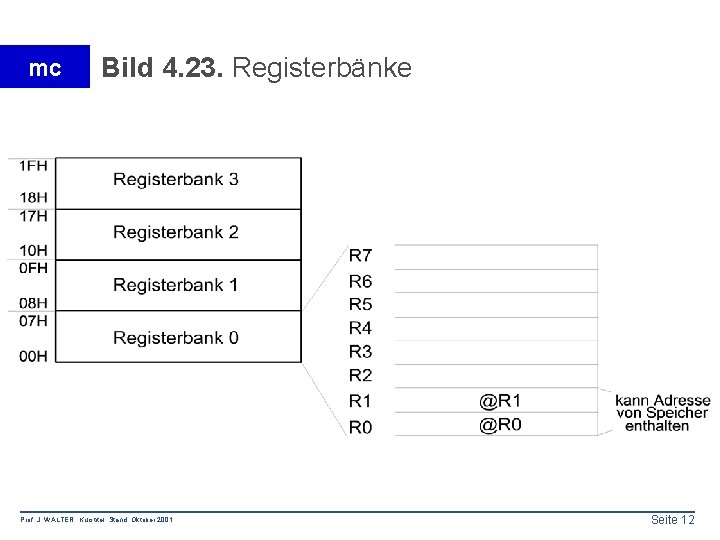

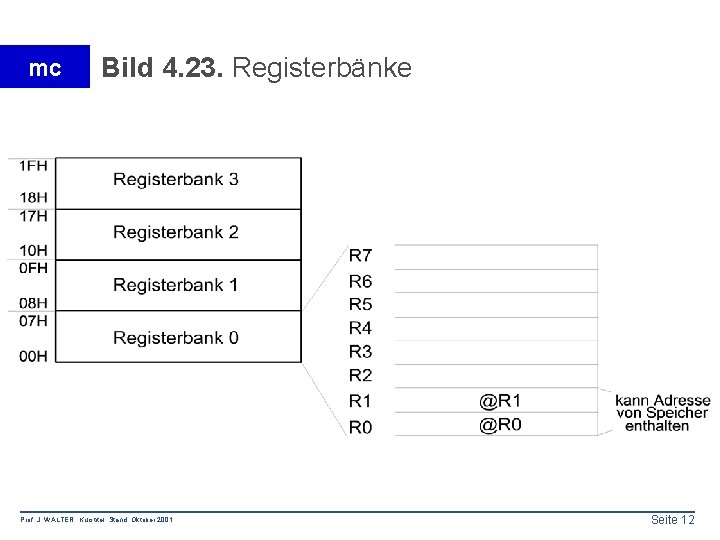

mc Bild 4. 23. Registerbänke Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 12

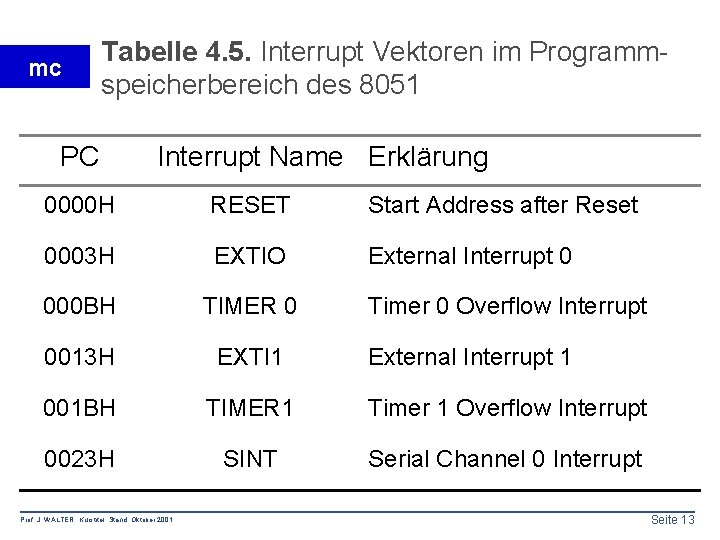

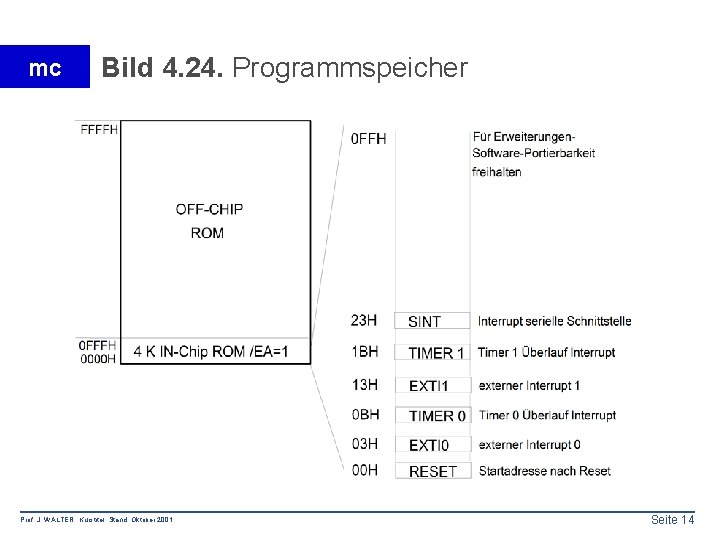

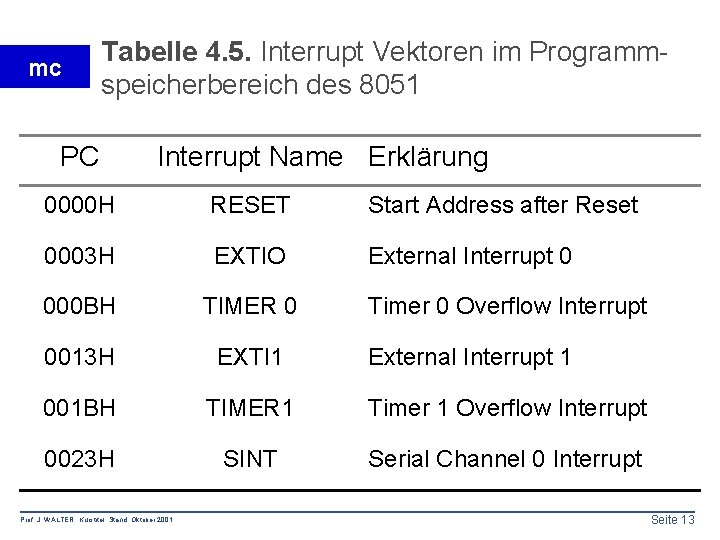

mc Tabelle 4. 5. Interrupt Vektoren im Programmspeicherbereich des 8051 PC Interrupt Name Erklärung 0000 H RESET Start Address after Reset 0003 H EXTIO External Interrupt 0 000 BH TIMER 0 0013 H EXTI 1 001 BH TIMER 1 Timer 1 Overflow Interrupt 0023 H SINT Serial Channel 0 Interrupt Prof. J. WALTER Kurstitel Stand: Oktober 2001 Timer 0 Overflow Interrupt External Interrupt 1 Seite 13

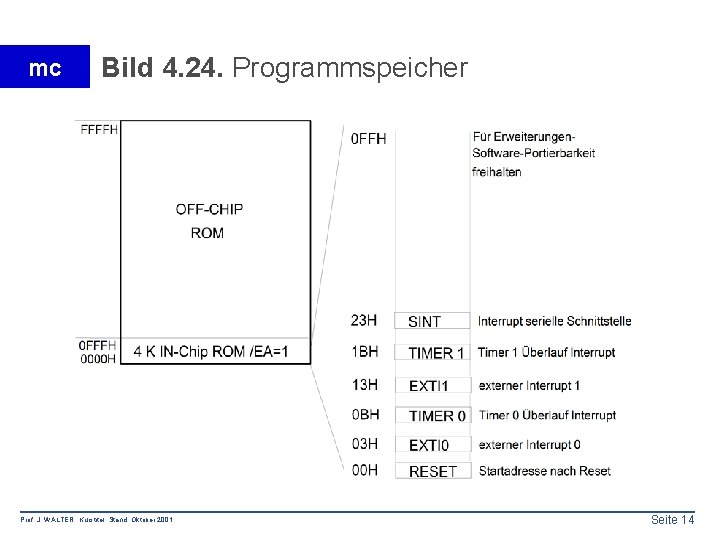

mc Bild 4. 24. Programmspeicher Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 14

mc Bild 4. 25. Interner Datenspeicher Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 15

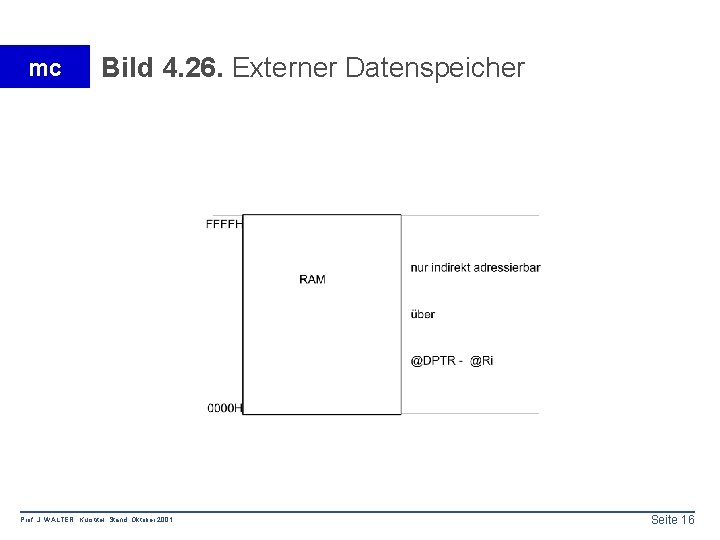

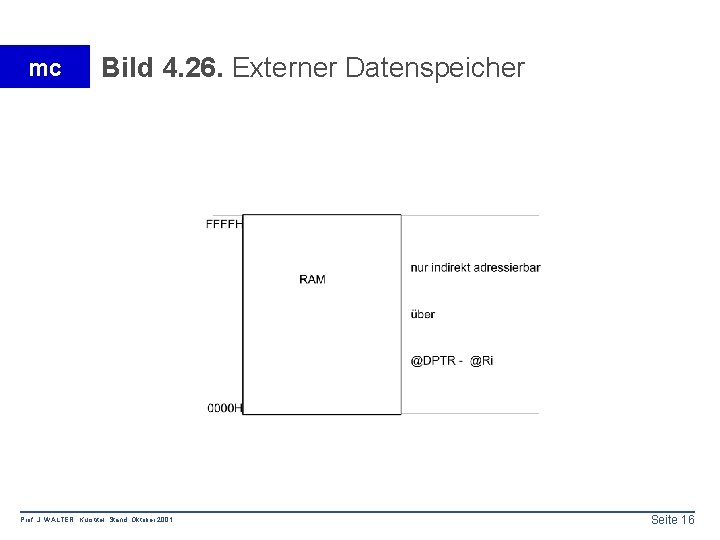

mc Bild 4. 26. Externer Datenspeicher Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 16

mc Bild 4. 27. Bitadressierbarer RAM-Bereich Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 17

mc Bild 4. 28. Speicherbereiche - Segmente Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 18

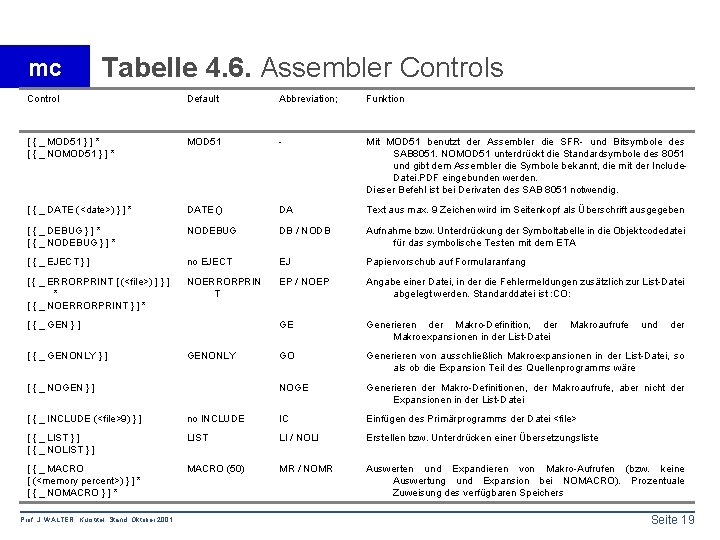

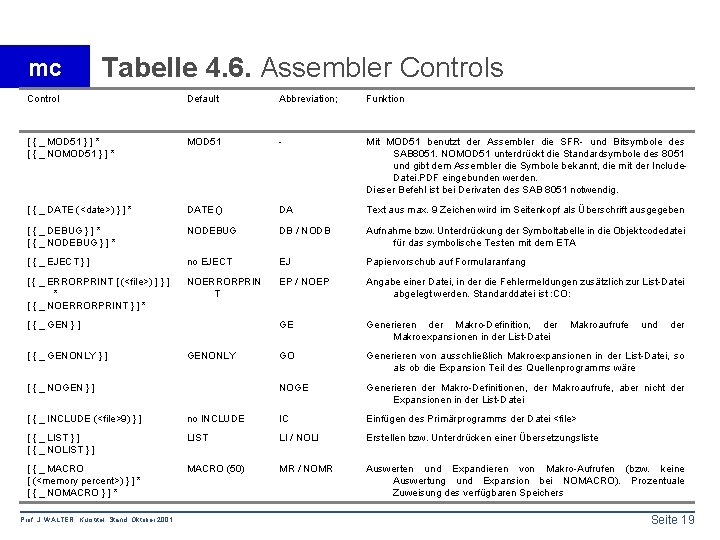

mc Tabelle 4. 6. Assembler Controls Control Default Abbreviation; Funktion [ { _ MOD 51 } ] * [ { _ NOMOD 51 } ] * MOD 51 - Mit MOD 51 benutzt der Assembler die SFR- und Bitsymbole des SAB 8051. NOMOD 51 unterdrückt die Standardsymbole des 8051 und gibt dem Assembler die Symbole bekannt, die mit der Include. Datei. PDF eingebunden werden. Dieser Befehl ist bei Derivaten des SAB 8051 notwendig. [ { _ DATE (<date>) } ] * DATE () DA Text aus max. 9 Zeichen wird im Seitenkopf als Überschrift ausgegeben [ { _ DEBUG } ] * [ { _ NODEBUG } ] * NODEBUG DB / NODB Aufnahme bzw. Unterdrückung der Symboltabelle in die Objektcodedatei für das symbolische Testen mit dem ETA [ { _ EJECT } ] no EJECT EJ Papiervorschub auf Formularanfang [ { _ ERRORPRINT [ (<file>) ] } ] * [ { _ NOERRORPRINT } ] * NOERRORPRIN T EP / NOEP Angabe einer Datei, in der die Fehlermeldungen zusätzlich zur List-Datei abgelegt werden. Standarddatei ist : CO: GE Generieren der Makro-Definition, der Makroexpansionen in der List-Datei GO Generieren von ausschließlich Makroexpansionen in der List-Datei, so als ob die Expansion Teil des Quellenprogramms wäre NOGE Generieren der Makro-Definitionen, der Makroaufrufe, aber nicht der Expansionen in der List-Datei [ { _ GEN } ] [ { _ GENONLY } ] GENONLY [ { _ NOGEN } ] Makroaufrufe und der [ { _ INCLUDE (<file>9) } ] no INCLUDE IC Einfügen des Primärprogramms der Datei <file> [ { _ LIST } ] [ { _ NOLIST } ] LIST LI / NOLI Erstellen bzw. Unterdrücken einer Übersetzungsliste [ { _ MACRO [ (<memory percent>) } ] * [ { _ NOMACRO } ] * MACRO (50) MR / NOMR Auswerten und Expandieren von Makro-Aufrufen (bzw. keine Auswertung und Expansion bei NOMACRO). Prozentuale Zuweisung des verfügbaren Speichers Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 19

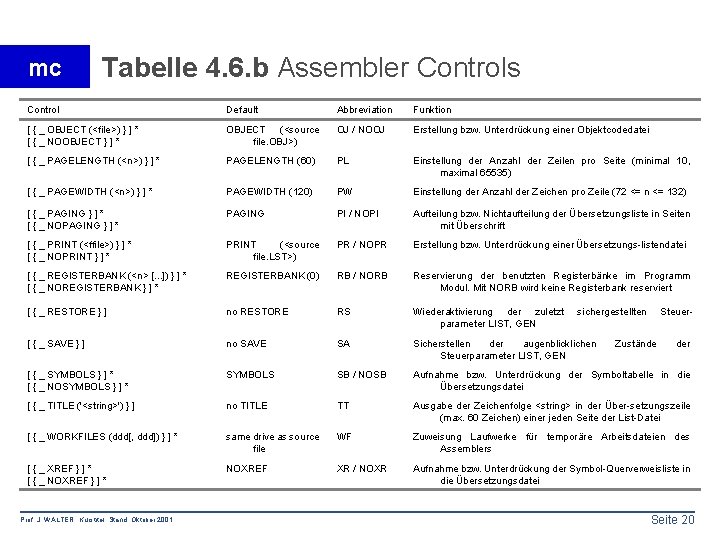

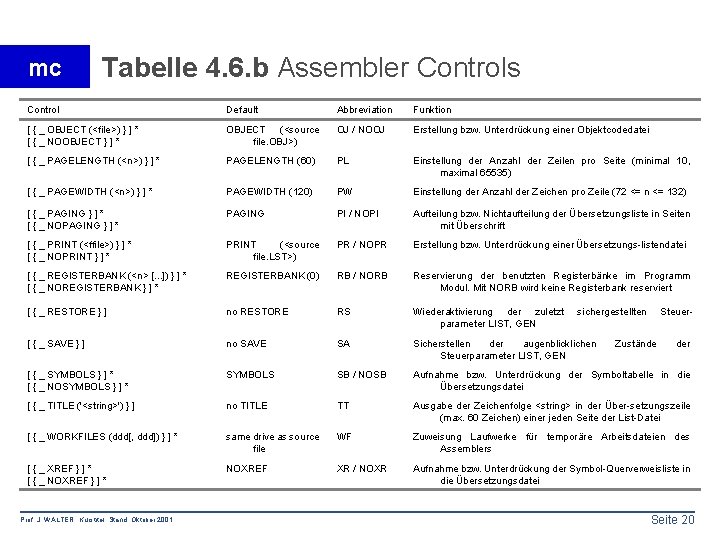

mc Tabelle 4. 6. b Assembler Controls Control Default Abbreviation Funktion [ { _ OBJECT (<file>) } ] * [ { _ NOOBJECT } ] * OBJECT (<source file. OBJ>) OJ / NOOJ Erstellung bzw. Unterdrückung einer Objektcodedatei [ { _ PAGELENGTH (<n>) } ] * PAGELENGTH (60) PL Einstellung der Anzahl der Zeilen pro Seite (minimal 10, maximal 65535) [ { _ PAGEWIDTH (<n>) } ] * PAGEWIDTH (120) PW Einstellung der Anzahl der Zeichen pro Zeile (72 <= n <= 132) [ { _ PAGING } ] * [ { _ NOPAGING } ] * PAGING PI / NOPI Aufteilung bzw. Nichtaufteilung der Übersetzungsliste in Seiten mit Überschrift [ { _ PRINT (<ffile>) } ] * [ { _ NOPRINT } ] * PRINT (<source file. LST>) PR / NOPR Erstellung bzw. Unterdrückung einer Übersetzungs-listendatei [ { _ REGISTERBANK (<n> [. . . ]) } ] * [ { _ NOREGISTERBANK } ] * REGISTERBANK (0) RB / NORB Reservierung der benutzten Registerbänke im Programm Modul. Mit NORB wird keine Registerbank reserviert [ { _ RESTORE } ] no RESTORE RS Wiederaktivierung der zuletzt parameter LIST, GEN [ { _ SAVE } ] no SAVE SA Sicherstellen der augenblicklichen Steuerparameter LIST, GEN [ { _ SYMBOLS } ] * [ { _ NOSYMBOLS } ] * SYMBOLS SB / NOSB Aufnahme bzw. Unterdrückung der Symboltabelle in die Übersetzungsdatei [ { _ TITLE ('<string>') } ] no TITLE TT Ausgabe der Zeichenfolge <string> in der Über-setzungszeile (max. 60 Zeichen) einer jeden Seite der List-Datei [ { _ WORKFILES (ddd[, ddd]) } ] * same drive as source file WF Zuweisung Laufwerke für temporäre Arbeitsdateien des Assemblers [ { _ XREF } ] * [ { _ NOXREF } ] * NOXREF XR / NOXR Aufnahme bzw. Unterdrückung der Symbol-Querverweisliste in die Übersetzungsdatei Prof. J. WALTER Kurstitel Stand: Oktober 2001 sichergestellten Steuer- Zustände der Seite 20

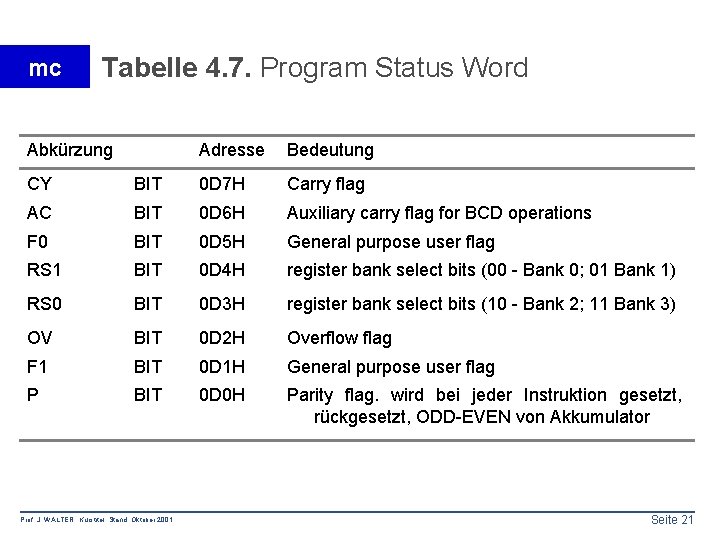

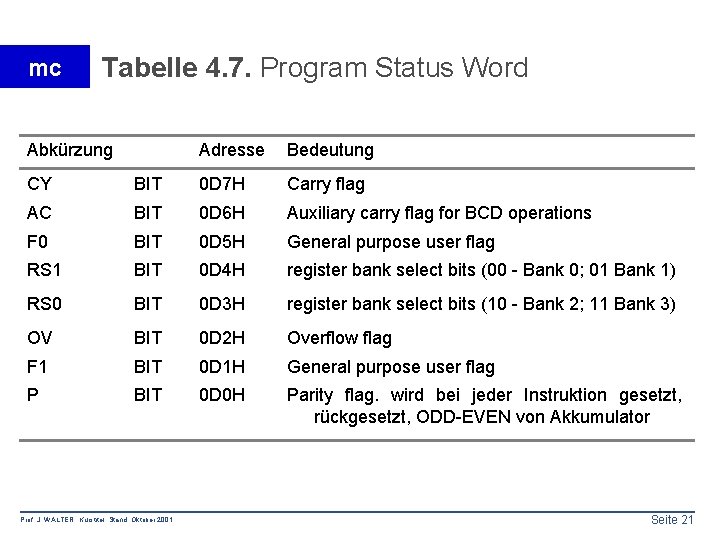

mc Tabelle 4. 7. Program Status Word Abkürzung Adresse Bedeutung CY BIT 0 D 7 H Carry flag AC BIT 0 D 6 H Auxiliary carry flag for BCD operations F 0 BIT 0 D 5 H General purpose user flag RS 1 BIT 0 D 4 H register bank select bits (00 - Bank 0; 01 Bank 1) RS 0 BIT 0 D 3 H register bank select bits (10 - Bank 2; 11 Bank 3) OV BIT 0 D 2 H Overflow flag F 1 BIT 0 D 1 H General purpose user flag P BIT 0 D 0 H Parity flag. wird bei jeder Instruktion gesetzt, rückgesetzt, ODD-EVEN von Akkumulator Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 21

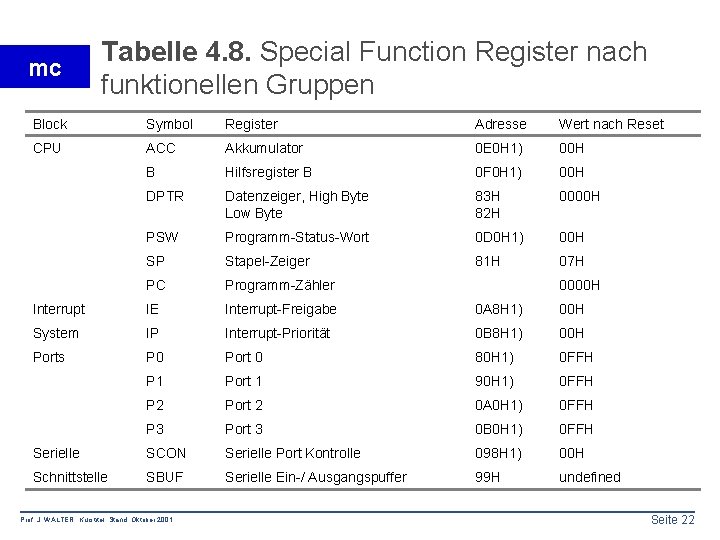

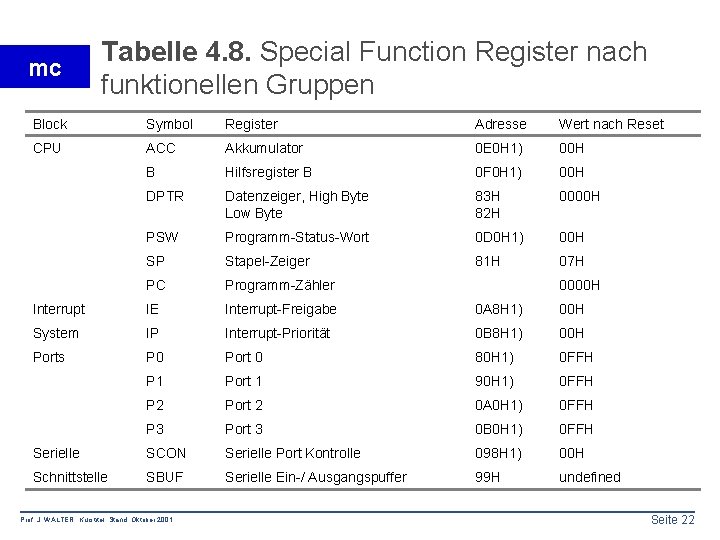

mc Tabelle 4. 8. Special Function Register nach funktionellen Gruppen Block Symbol Register Adresse Wert nach Reset CPU ACC Akkumulator 0 E 0 H 1) 00 H B Hilfsregister B 0 F 0 H 1) 00 H DPTR Datenzeiger, High Byte Low Byte 83 H 82 H 0000 H PSW Programm-Status-Wort 0 D 0 H 1) 00 H SP Stapel-Zeiger 81 H 07 H PC Programm-Zähler Interrupt IE Interrupt-Freigabe 0 A 8 H 1) 00 H System IP Interrupt-Priorität 0 B 8 H 1) 00 H Ports P 0 Port 0 80 H 1) 0 FFH P 1 Port 1 90 H 1) 0 FFH P 2 Port 2 0 A 0 H 1) 0 FFH P 3 Port 3 0 B 0 H 1) 0 FFH Serielle SCON Serielle Port Kontrolle 098 H 1) 00 H Schnittstelle SBUF Serielle Ein-/ Ausgangspuffer 99 H undefined Prof. J. WALTER Kurstitel Stand: Oktober 2001 0000 H Seite 22

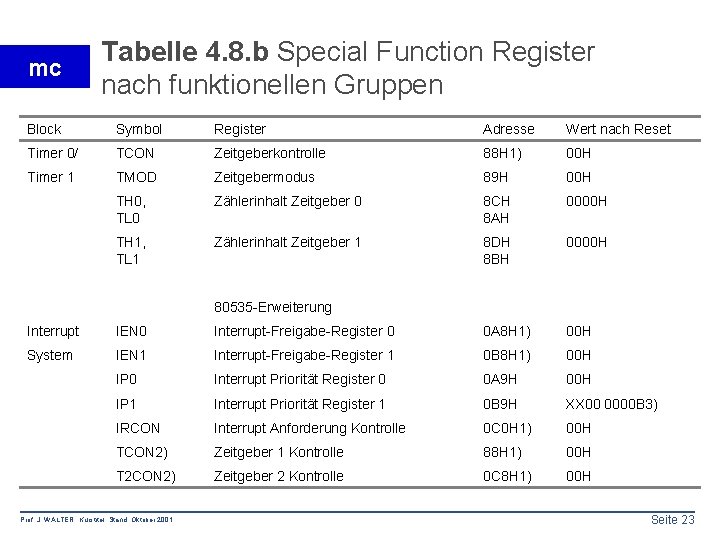

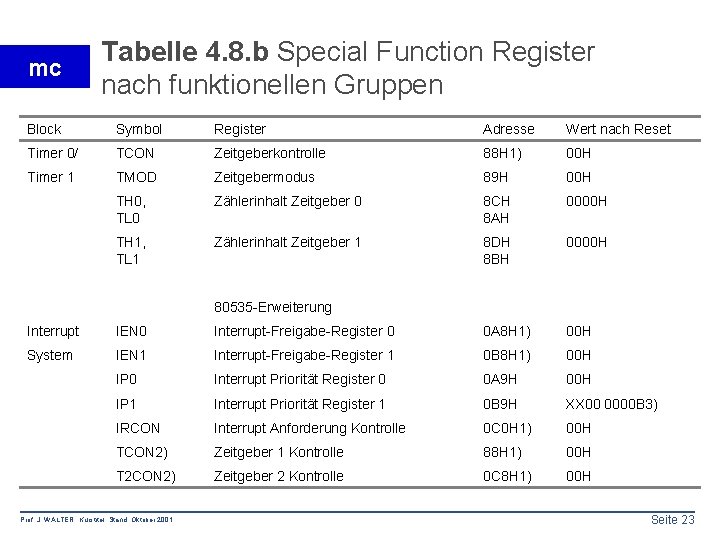

mc Tabelle 4. 8. b Special Function Register nach funktionellen Gruppen Block Symbol Register Adresse Wert nach Reset Timer 0/ TCON Zeitgeberkontrolle 88 H 1) 00 H Timer 1 TMOD Zeitgebermodus 89 H 00 H TH 0, TL 0 Zählerinhalt Zeitgeber 0 8 CH 8 AH 0000 H TH 1, TL 1 Zählerinhalt Zeitgeber 1 8 DH 8 BH 0000 H 80535 -Erweiterung Interrupt IEN 0 Interrupt-Freigabe-Register 0 0 A 8 H 1) 00 H System IEN 1 Interrupt-Freigabe-Register 1 0 B 8 H 1) 00 H IP 0 Interrupt Priorität Register 0 0 A 9 H 00 H IP 1 Interrupt Priorität Register 1 0 B 9 H XX 00 0000 B 3) IRCON Interrupt Anforderung Kontrolle 0 C 0 H 1) 00 H TCON 2) Zeitgeber 1 Kontrolle 88 H 1) 00 H T 2 CON 2) Zeitgeber 2 Kontrolle 0 C 8 H 1) 00 H Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 23

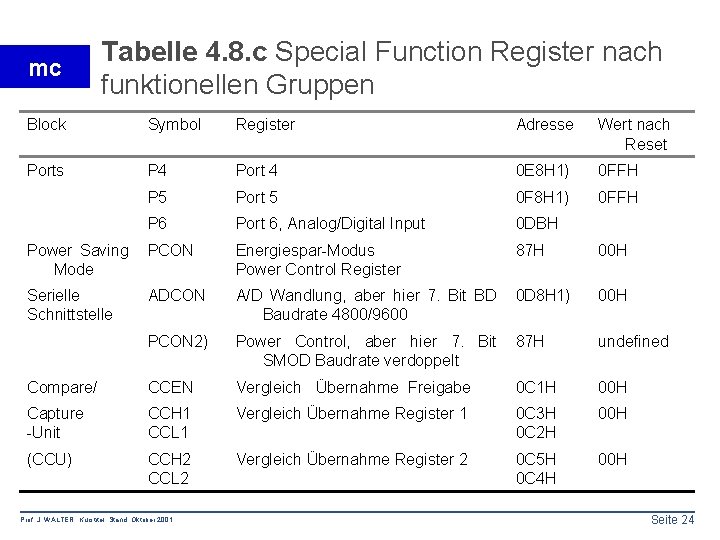

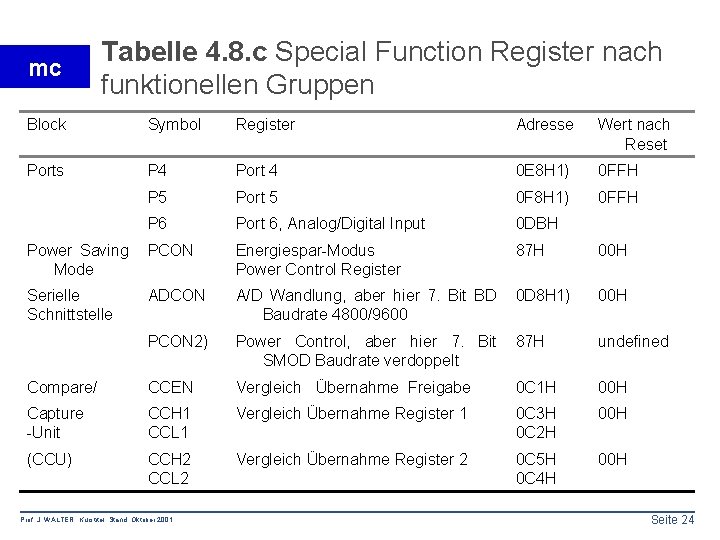

mc Tabelle 4. 8. c Special Function Register nach funktionellen Gruppen Block Symbol Register Adresse Wert nach Reset Ports P 4 Port 4 0 E 8 H 1) 0 FFH P 5 Port 5 0 F 8 H 1) 0 FFH P 6 Port 6, Analog/Digital Input 0 DBH Power Saving Mode PCON Energiespar-Modus Power Control Register 87 H 00 H Serielle Schnittstelle ADCON A/D Wandlung, aber hier 7. Bit BD Baudrate 4800/9600 0 D 8 H 1) 00 H PCON 2) Power Control, aber hier 7. Bit SMOD Baudrate verdoppelt 87 H undefined Compare/ CCEN Vergleich Übernahme Freigabe 0 C 1 H 00 H Capture -Unit CCH 1 CCL 1 Vergleich Übernahme Register 1 0 C 3 H 0 C 2 H 00 H (CCU) CCH 2 CCL 2 Vergleich Übernahme Register 2 0 C 5 H 0 C 4 H 00 H Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 24

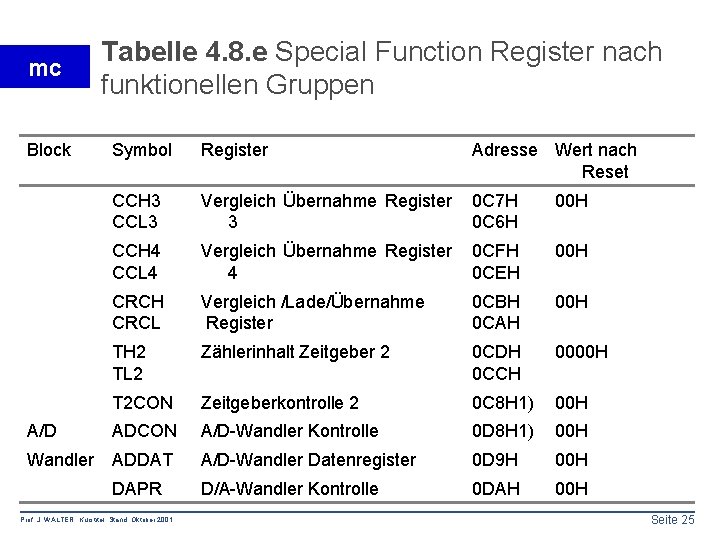

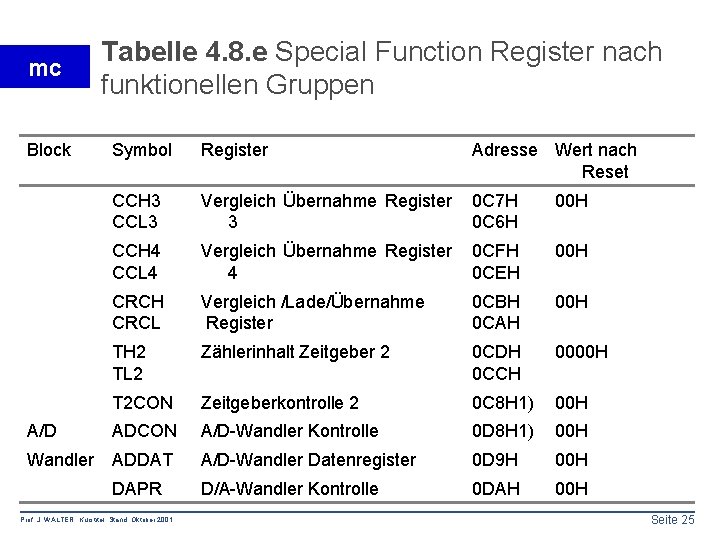

mc Block Tabelle 4. 8. e Special Function Register nach funktionellen Gruppen Symbol Register Adresse Wert nach Reset CCH 3 CCL 3 Vergleich Übernahme Register 3 0 C 7 H 0 C 6 H 00 H CCH 4 CCL 4 Vergleich Übernahme Register 4 0 CFH 0 CEH 00 H CRCL Vergleich /Lade/Übernahme Register 0 CBH 0 CAH 00 H TH 2 TL 2 Zählerinhalt Zeitgeber 2 0 CDH 0 CCH 0000 H T 2 CON Zeitgeberkontrolle 2 0 C 8 H 1) 00 H A/D ADCON A/D-Wandler Kontrolle 0 D 8 H 1) 00 H Wandler ADDAT A/D-Wandler Datenregister 0 D 9 H 00 H DAPR D/A-Wandler Kontrolle 0 DAH 00 H Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 25

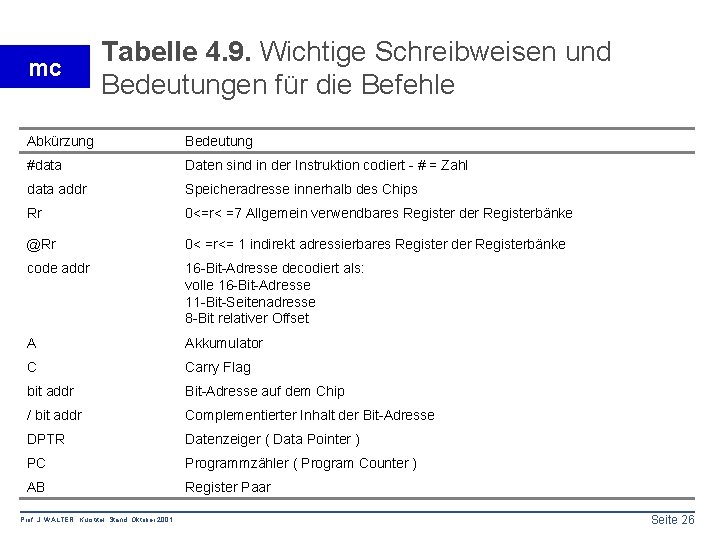

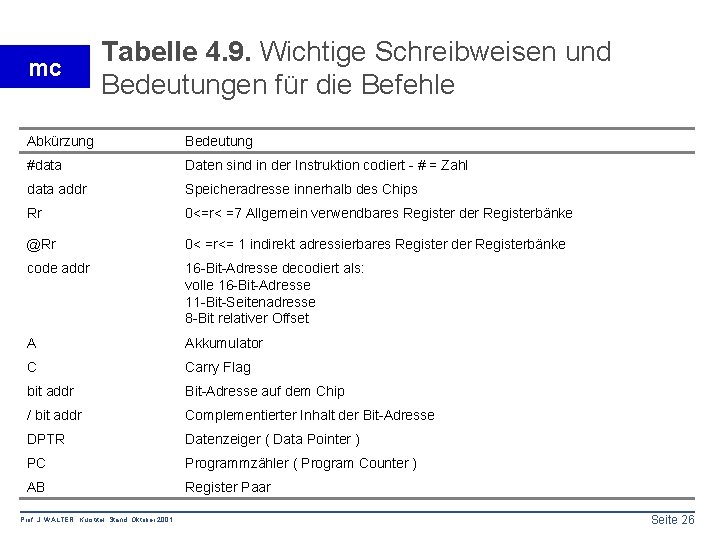

mc Tabelle 4. 9. Wichtige Schreibweisen und Bedeutungen für die Befehle Abkürzung Bedeutung #data Daten sind in der Instruktion codiert - # = Zahl data addr Speicheradresse innerhalb des Chips Rr 0<=r< =7 Allgemein verwendbares Register der Registerbänke @Rr 0< =r<= 1 indirekt adressierbares Register der Registerbänke code addr 16 -Bit-Adresse decodiert als: volle 16 -Bit-Adresse 11 -Bit-Seitenadresse 8 -Bit relativer Offset A Akkumulator C Carry Flag bit addr Bit-Adresse auf dem Chip / bit addr Complementierter Inhalt der Bit-Adresse DPTR Datenzeiger ( Data Pointer ) PC Programmzähler ( Program Counter ) AB Register Paar Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 26

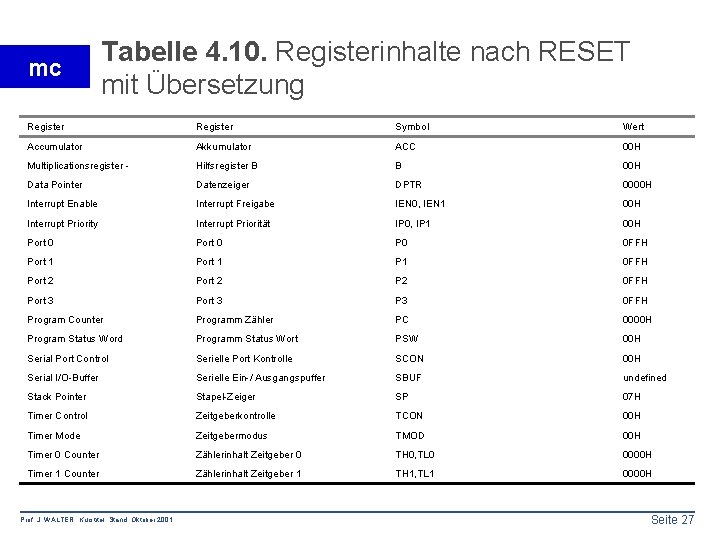

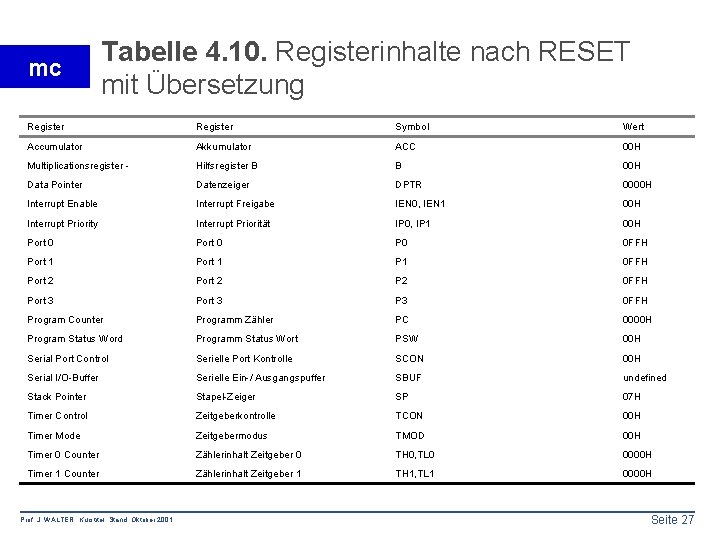

mc Tabelle 4. 10. Registerinhalte nach RESET mit Übersetzung Register Symbol Wert Accumulator Akkumulator ACC 00 H Multiplicationsregister - Hilfsregister B B 00 H Data Pointer Datenzeiger DPTR 0000 H Interrupt Enable Interrupt Freigabe IEN 0, IEN 1 00 H Interrupt Priority Interrupt Priorität IP 0, IP 1 00 H Port 0 P 0 0 FFH Port 1 P 1 0 FFH Port 2 P 2 0 FFH Port 3 P 3 0 FFH Program Counter Programm Zähler PC 0000 H Program Status Word Programm Status Wort PSW 00 H Serial Port Control Serielle Port Kontrolle SCON 00 H Serial I/O-Buffer Serielle Ein-/ Ausgangspuffer SBUF undefined Stack Pointer Stapel-Zeiger SP 07 H Timer Control Zeitgeberkontrolle TCON 00 H Timer Mode Zeitgebermodus TMOD 00 H Timer 0 Counter Zählerinhalt Zeitgeber 0 TH 0, TL 0 0000 H Timer 1 Counter Zählerinhalt Zeitgeber 1 TH 1, TL 1 0000 H Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 27

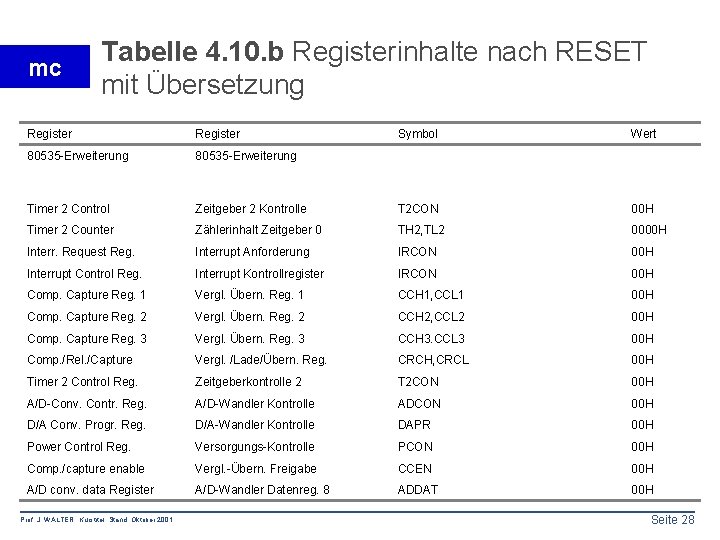

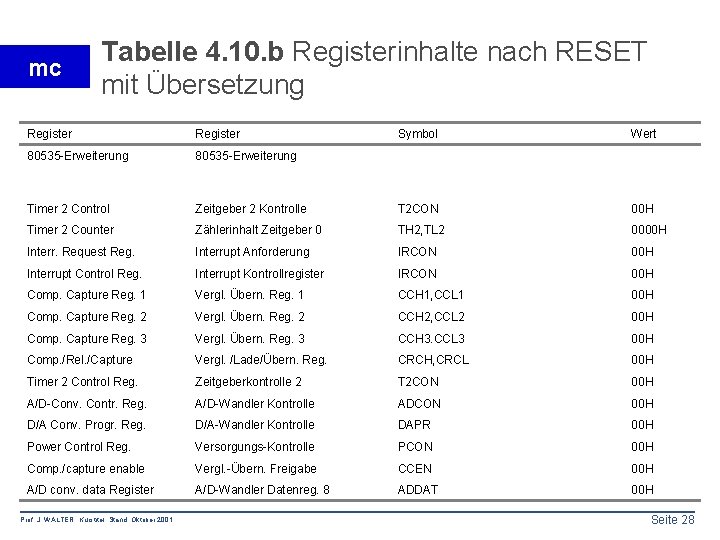

mc Tabelle 4. 10. b Registerinhalte nach RESET mit Übersetzung Register Symbol Wert 80535 -Erweiterung Timer 2 Control Zeitgeber 2 Kontrolle T 2 CON 00 H Timer 2 Counter Zählerinhalt Zeitgeber 0 TH 2, TL 2 0000 H Interr. Request Reg. Interrupt Anforderung IRCON 00 H Interrupt Control Reg. Interrupt Kontrollregister IRCON 00 H Comp. Capture Reg. 1 Vergl. Übern. Reg. 1 CCH 1, CCL 1 00 H Comp. Capture Reg. 2 Vergl. Übern. Reg. 2 CCH 2, CCL 2 00 H Comp. Capture Reg. 3 Vergl. Übern. Reg. 3 CCH 3. CCL 3 00 H Comp. /Rel. /Capture Vergl. /Lade/Übern. Reg. CRCH, CRCL 00 H Timer 2 Control Reg. Zeitgeberkontrolle 2 T 2 CON 00 H A/D-Conv. Contr. Reg. A/D-Wandler Kontrolle ADCON 00 H D/A Conv. Progr. Reg. D/A-Wandler Kontrolle DAPR 00 H Power Control Reg. Versorgungs-Kontrolle PCON 00 H Comp. /capture enable Vergl. -Übern. Freigabe CCEN 00 H A/D conv. data Register A/D-Wandler Datenreg. 8 ADDAT 00 H Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 28

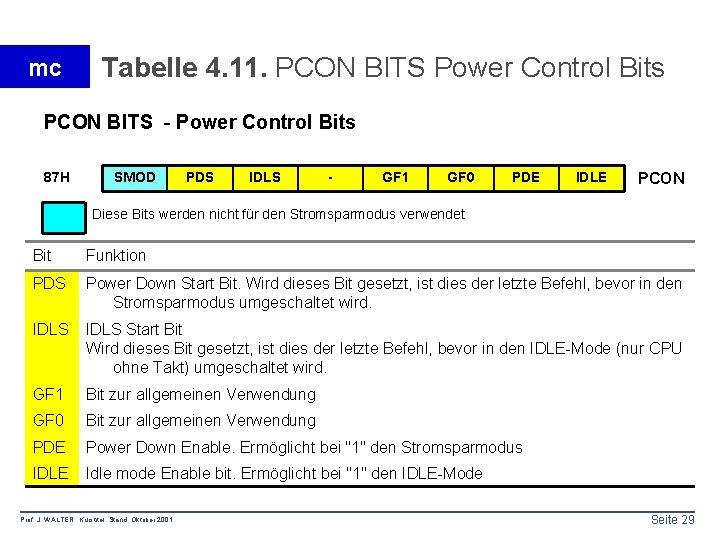

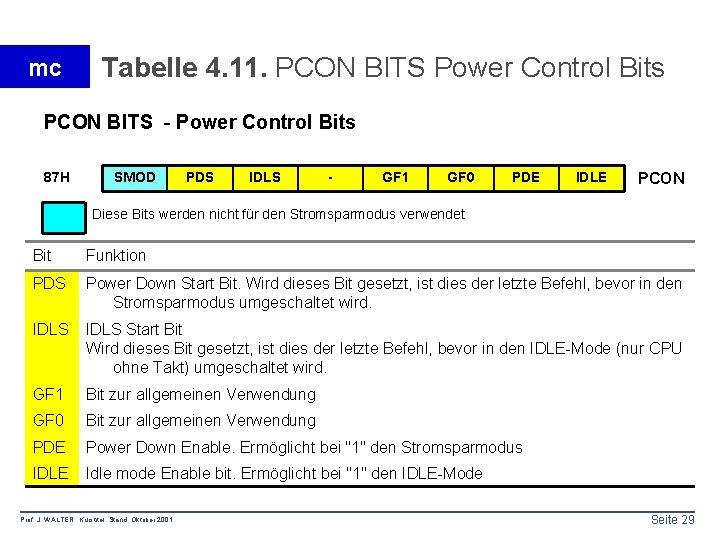

mc Tabelle 4. 11. PCON BITS Power Control Bits PCON BITS - Power Control Bits 87 H SMOD PDS IDLS - GF 1 GF 0 PDE IDLE PCON Diese Bits werden nicht für den Stromsparmodus verwendet Bit Funktion PDS Power Down Start Bit. Wird dieses Bit gesetzt, ist dies der letzte Befehl, bevor in den Stromsparmodus umgeschaltet wird. IDLS Start Bit Wird dieses Bit gesetzt, ist dies der letzte Befehl, bevor in den IDLE-Mode (nur CPU ohne Takt) umgeschaltet wird. GF 1 Bit zur allgemeinen Verwendung GF 0 Bit zur allgemeinen Verwendung PDE Power Down Enable. Ermöglicht bei "1" den Stromsparmodus IDLE Idle mode Enable bit. Ermöglicht bei "1" den IDLE-Mode Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 29

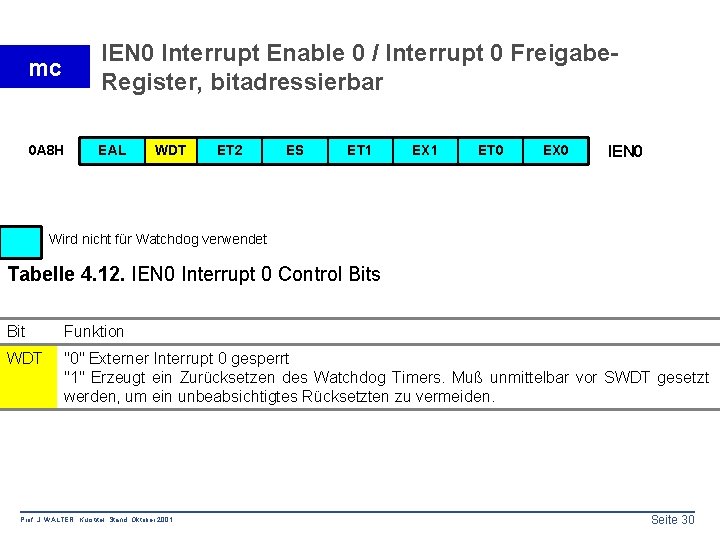

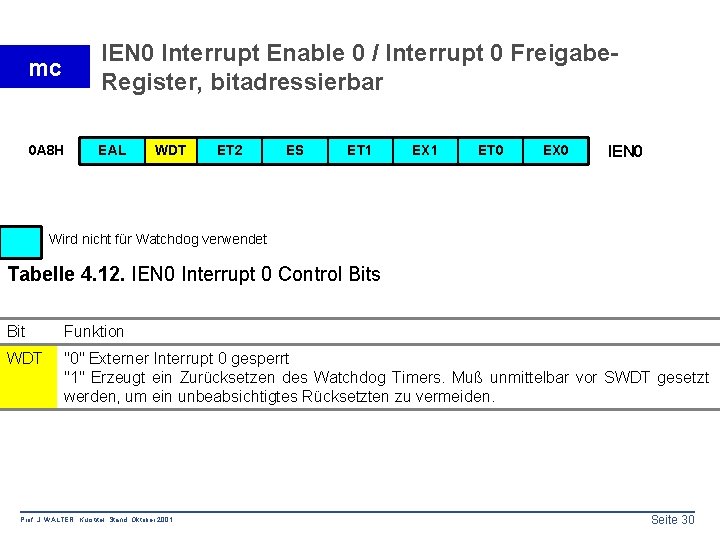

mc IEN 0 Interrupt Enable 0 / Interrupt 0 Freigabe. Register, bitadressierbar 0 A 8 H EAL WDT ET 2 ES ET 1 EX 1 ET 0 EX 0 IEN 0 Wird nicht für Watchdog verwendet Tabelle 4. 12. IEN 0 Interrupt 0 Control Bits Bit Funktion WDT "0" Externer Interrupt 0 gesperrt "1" Erzeugt ein Zurücksetzen des Watchdog Timers. Muß unmittelbar vor SWDT gesetzt werden, um ein unbeabsichtigtes Rücksetzten zu vermeiden. Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 30

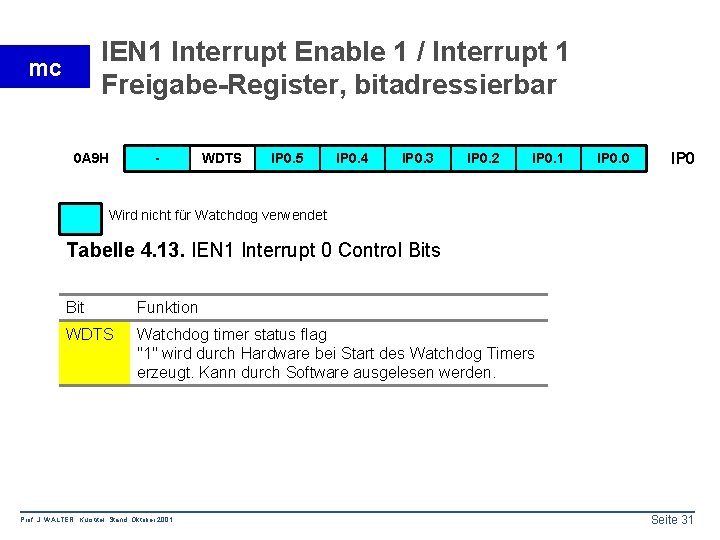

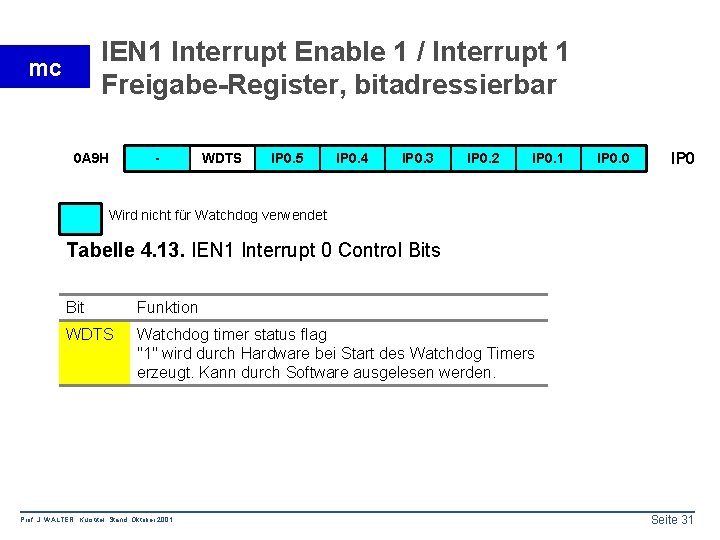

IEN 1 Interrupt Enable 1 / Interrupt 1 Freigabe-Register, bitadressierbar mc 0 A 9 H - WDTS IP 0. 5 IP 0. 4 IP 0. 3 IP 0. 2 IP 0. 1 IP 0. 0 IP 0 Wird nicht für Watchdog verwendet Tabelle 4. 13. IEN 1 Interrupt 0 Control Bits Bit Funktion WDTS Watchdog timer status flag "1" wird durch Hardware bei Start des Watchdog Timers erzeugt. Kann durch Software ausgelesen werden. Prof. J. WALTER Kurstitel Stand: Oktober 2001 Seite 31