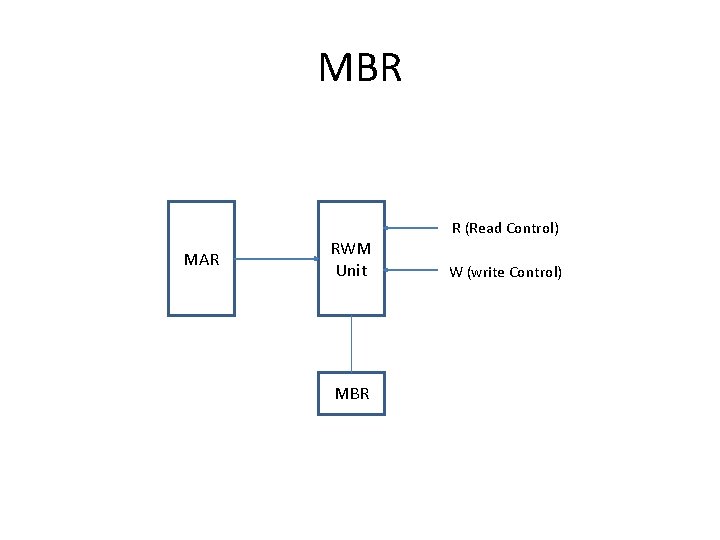

MBR MAR RWM Unit MBR R Read Control

MBR MAR RWM Unit MBR R (Read Control) W (write Control)

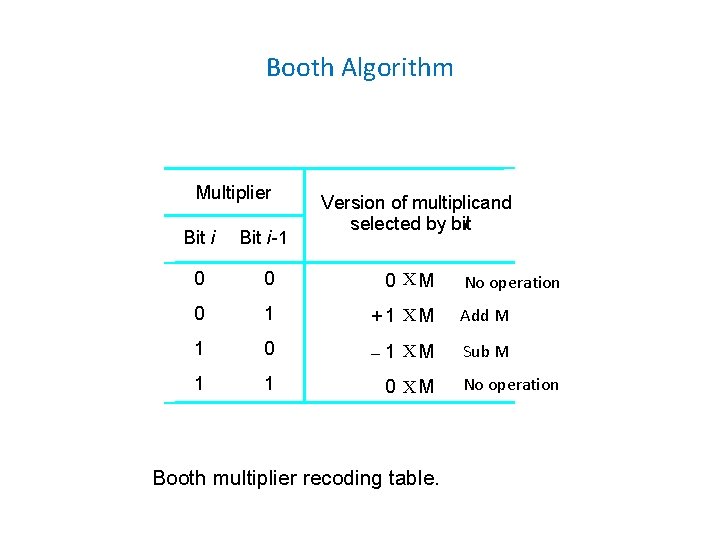

Booth Algorithm Multiplier Version of multiplicand selected by biti Bit i -1 0 0 0 XM 0 1 +1 XM Add M 1 0 1 XM Sub M 1 1 0 XM Booth multiplier recoding table. No operation

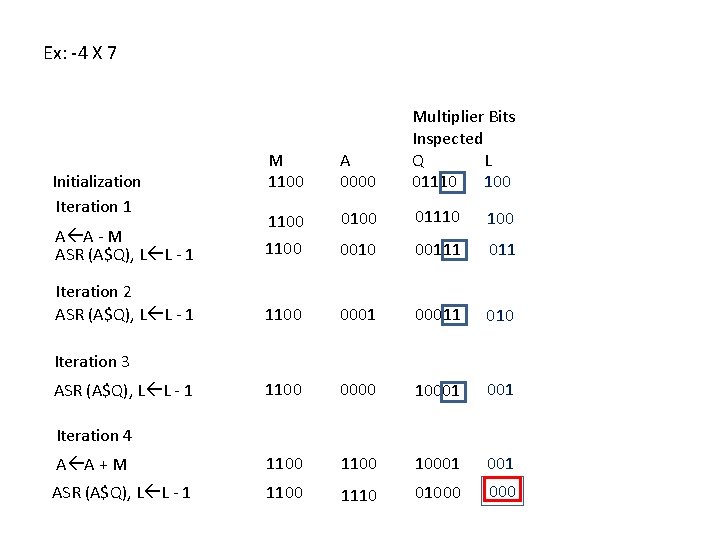

Ex: -4 X 7 M 1100 A 0000 Multiplier Bits Inspected Q L 01110 100 A A - M ASR (A$Q), L L - 1 1100 01110 100 1100 00111 011 Iteration 2 ASR (A$Q), L L - 1 1100 00011 010 1100 0000 10001 A A + M 1100 10001 ASR (A$Q), L L - 1 1100 1110 01000 Initialization Iteration 1 Iteration 3 ASR (A$Q), L L - 1 Iteration 4

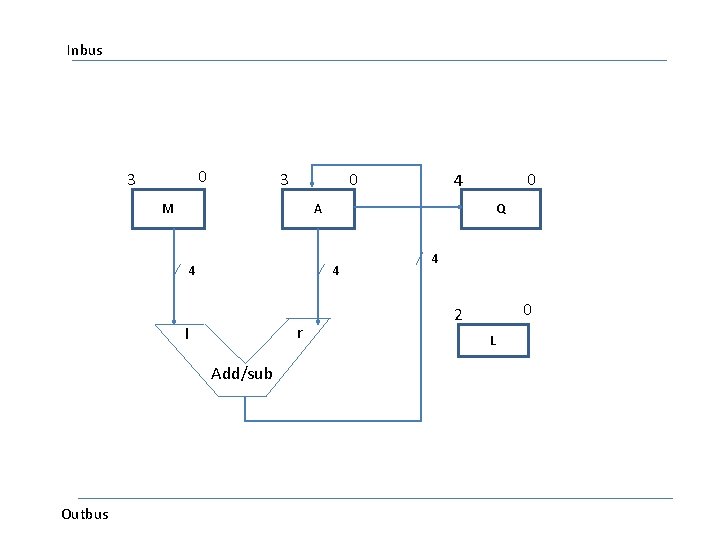

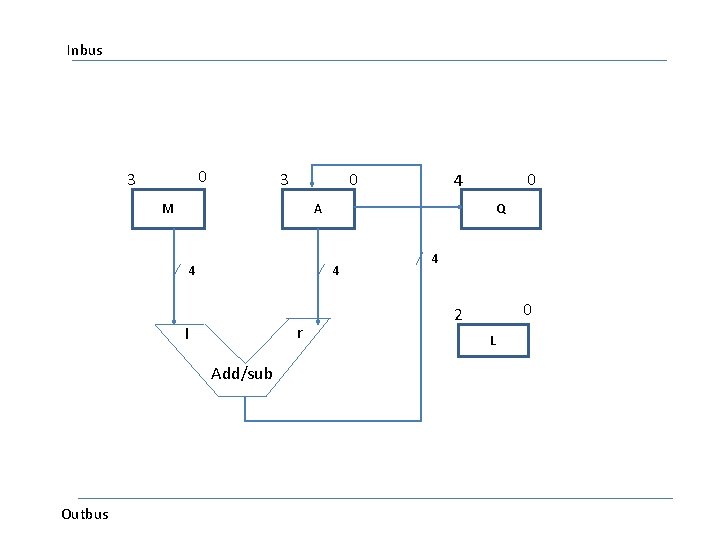

Inbus 0 3 3 0 M A 4 r Add/sub Outbus Q 4 I 0 4 4 0 2 L

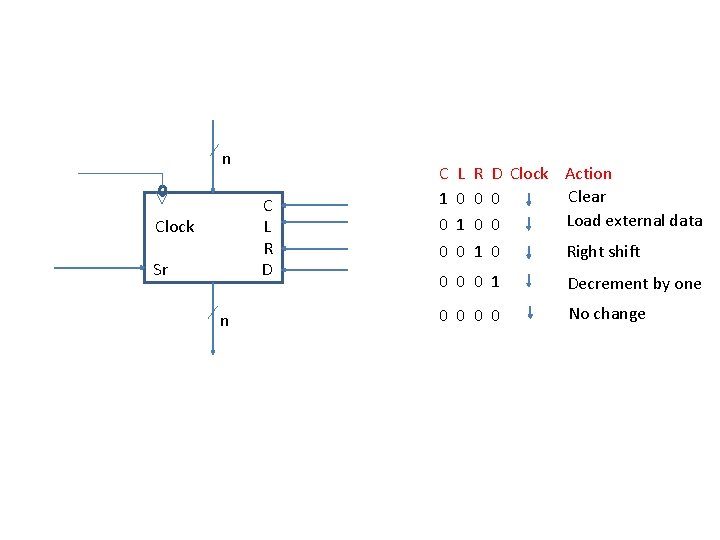

n C L R D Clock Sr n C L R D Clock Action Clear 1 0 0 0 Load external data 0 1 0 0 Right shift 0 0 1 Decrement by one 0 0 No change

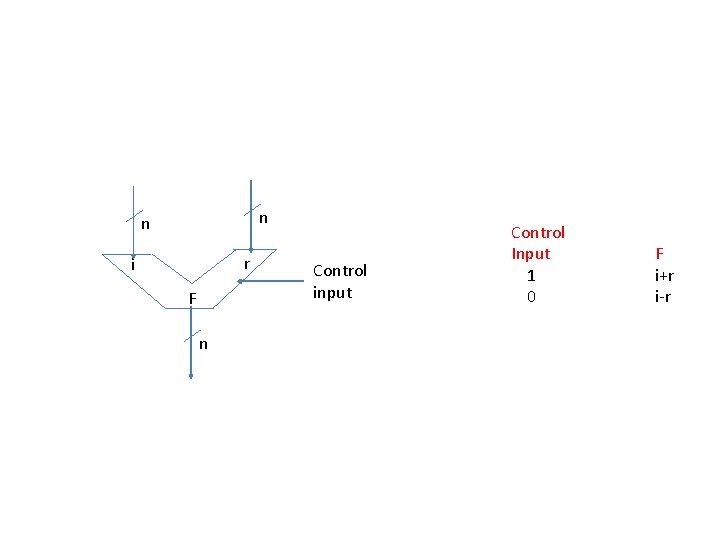

n n r i F n Control input Control Input 1 0 F i+r i-r

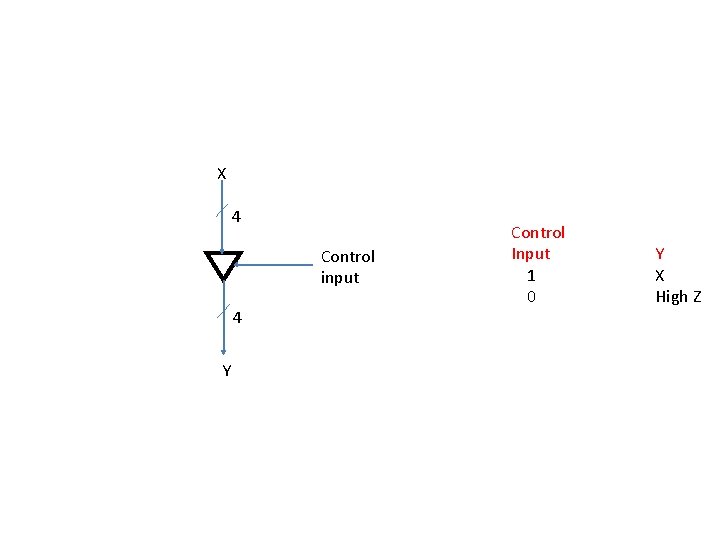

X 4 Control input 4 Y Control Input 1 0 Y X High Z

![Register Transfer Description of Booth’s Multiplication Procedure Declare registers A[4], M[4], Q[5], L[3]; Declare Register Transfer Description of Booth’s Multiplication Procedure Declare registers A[4], M[4], Q[5], L[3]; Declare](http://slidetodoc.com/presentation_image_h/17f0d091b0012dc9777de6f54aca6126/image-8.jpg)

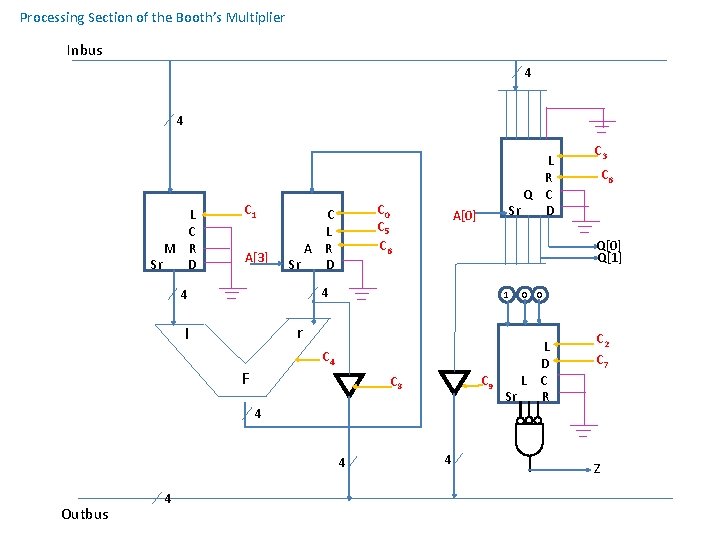

Register Transfer Description of Booth’s Multiplication Procedure Declare registers A[4], M[4], Q[5], L[3]; Declare buses Inbus[4], Outbus[4] Start: A 0, M Inbus, L 4; clear A and transfer M Q[4: 1] Inbus, Q[0] 0; transfer Q Loop: if Q[1: 0] = 01 then go to Add; if Q[1: 0] = 10 then go to Sub; Go to Rshift, Add: A A+M Go to Rshift Sub: A A-M Rshift: ASR(AQ), L L-1; If L<>0 then go to Loop Outbus = A Outbus = Q[4: 1}; Halt: Go to Halt

Inbus 0 3 3 0 M A 4 r Add/sub Outbus Q 4 I 0 4 4 0 2 L

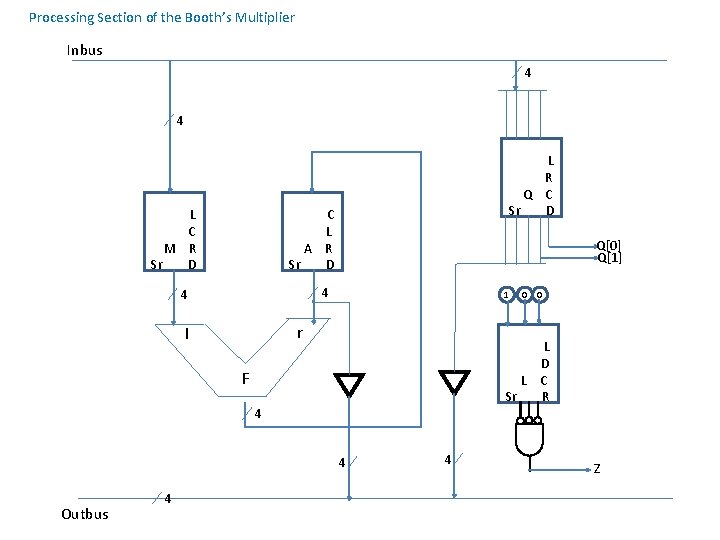

Processing Section of the Booth’s Multiplier Inbus 4 4 L C M R Sr D L R Q C Sr D C L A R Sr D Q[0] Q[1] 4 4 1 r I 0 0 L D L C Sr R F 4 4 Outbus 4 4 Z

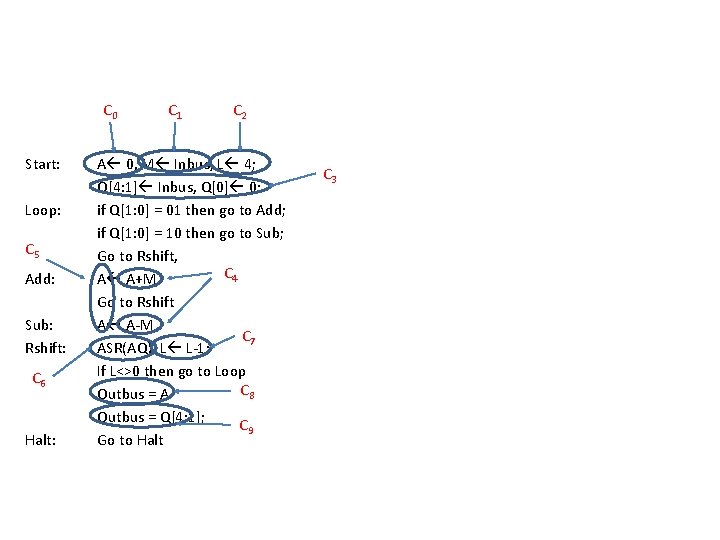

C 0 Start: Loop: C 5 Add: Sub: Rshift: C 6 Halt: C 1 C 2 A 0, M Inbus, L 4; Q[4: 1] Inbus, Q[0] 0; if Q[1: 0] = 01 then go to Add; if Q[1: 0] = 10 then go to Sub; Go to Rshift, C 4 A A+M Go to Rshift A A-M C 7 ASR(AQ), L L-1; If L<>0 then go to Loop C 8 Outbus = A Outbus = Q[4: 1]; C 9 Go to Halt C 3

Processing Section of the Booth’s Multiplier Inbus 4 4 L C M R Sr D C 1 A[3] C 0 C 5 C 6 C L A R Sr D L R Q C Sr D A[0] 1 r I C 4 F C 6 Q[0] Q[1] 4 4 C 3 C 9 C 8 0 0 L D L C Sr R C 2 C 7 4 4 Outbus 4 4 Z

![C 0 C 1 C 2 Reset Q[1] Q[0] CONTROLLER Z Clock . . C 0 C 1 C 2 Reset Q[1] Q[0] CONTROLLER Z Clock . .](http://slidetodoc.com/presentation_image_h/17f0d091b0012dc9777de6f54aca6126/image-13.jpg)

C 0 C 1 C 2 Reset Q[1] Q[0] CONTROLLER Z Clock . . . C 3 C 4 C 9

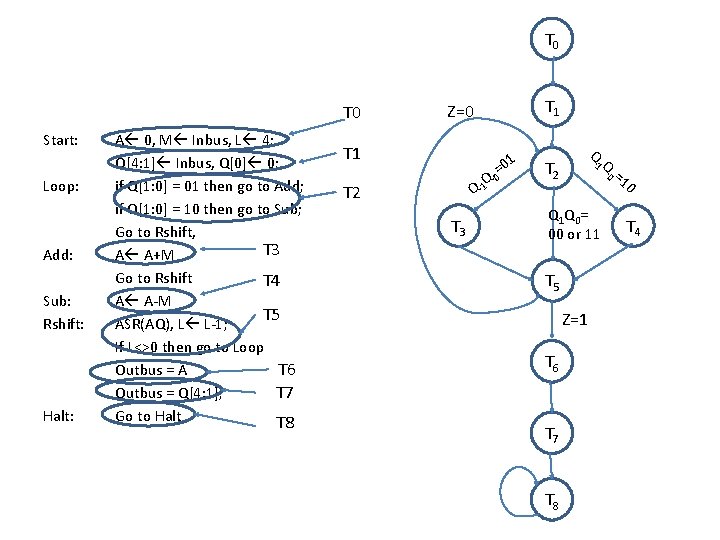

T 0 Start: Loop: Add: Sub: Rshift: Halt: A 0, M Inbus, L 4; Q[4: 1] Inbus, Q[0] 0; if Q[1: 0] = 01 then go to Add; if Q[1: 0] = 10 then go to Sub; Go to Rshift, T 3 A A+M Go to Rshift T 4 A A-M T 5 ASR(AQ), L L-1; If L<>0 then go to Loop Outbus = A T 6 Outbus = Q[4: 1}; T 7 Go to Halt T 8 T 1 Z=0 T 1 1 =0 Q 1 T 2 T 3 Q 1 Q 0= T 2 10 Q 1 Q 0 = 00 or 11 T 5 Z=1 T 6 T 7 T 8 T 4

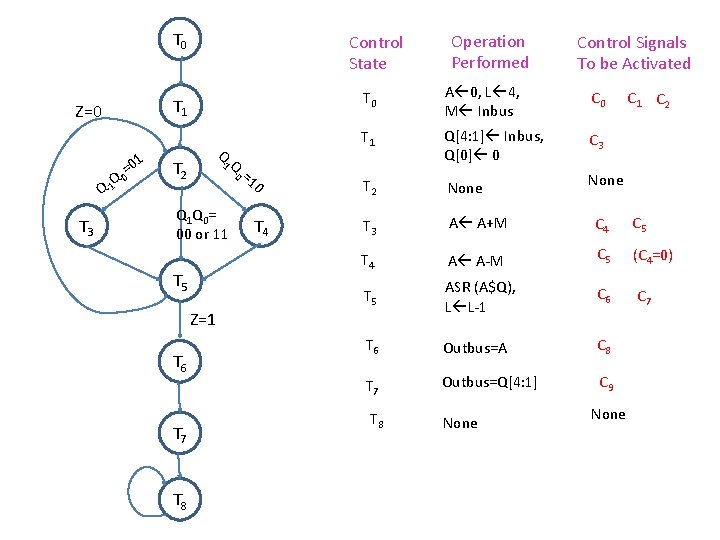

T 0 T 1 Z=0 Q Q 1 T 3 Control State =0 0 1 Q 1 Q 0= T 2 10 Q 1 Q 0 = 00 or 11 T 5 T 4 T 7 T 8 Control Signals To be Activated T 0 A 0, L 4, M Inbus C 0 T 1 Q[4: 1] Inbus, Q[0] 0 C 3 T 2 None T 3 A A+M C 4 C 5 T 4 A A-M C 5 (C 4=0) T 5 ASR (A$Q), L L-1 C 6 C 7 T 6 Outbus=A C 8 T 7 Outbus=Q[4: 1] C 9 T 8 None Z=1 T 6 Operation Performed None C 1 C 2

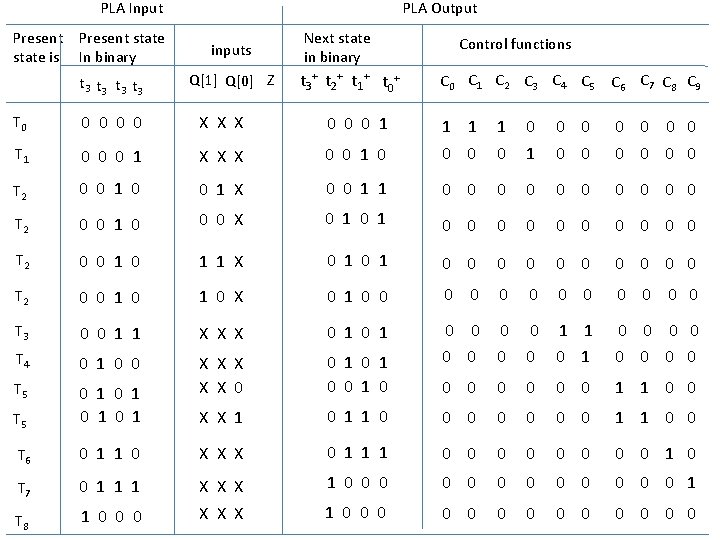

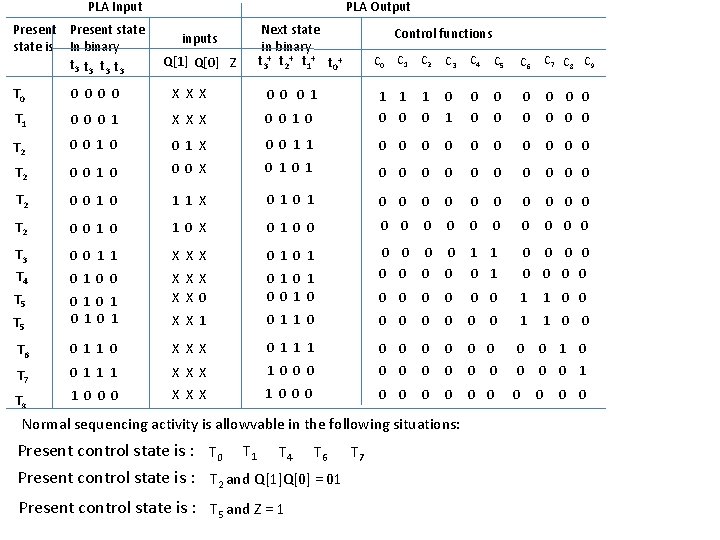

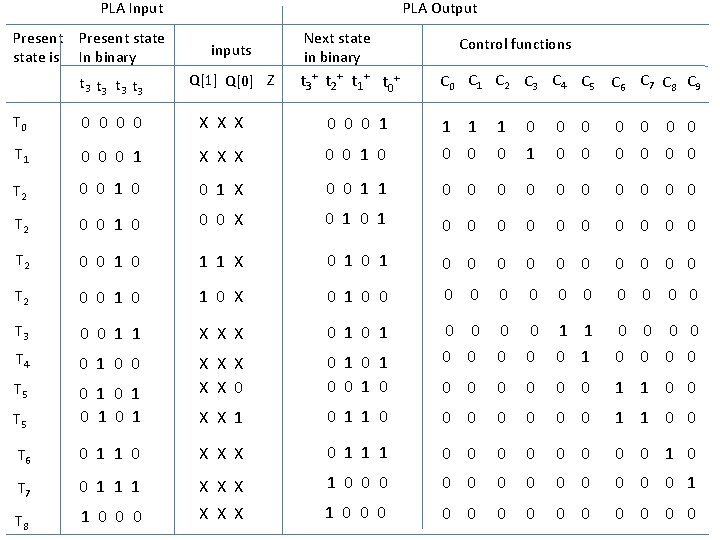

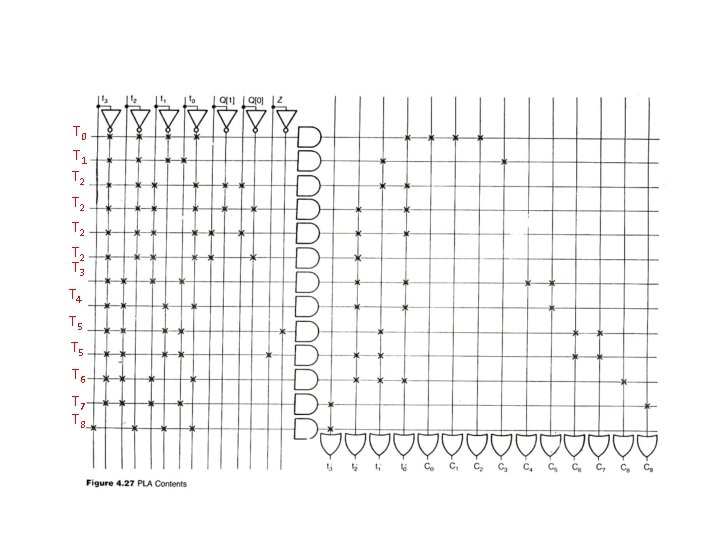

PLA Input Present state is Present state In binary t 3 t 3 PLA Output inputs Q[1] Q[0] Z Next state in binary t 3+ t 2+ t 1+ t 0+ Control functions C 0 C 1 C 2 C 3 C 4 C 5 C 6 C 7 C 8 C 9 T 0 0 0 X X X 0 0 0 1 1 0 0 0 0 T 1 0 0 0 1 X X X 0 0 1 0 0 0 0 T 2 0 0 1 X 0 0 1 1 0 0 0 0 0 T 2 0 0 1 0 0 0 X 0 1 0 0 0 0 0 T 2 0 0 1 1 X 0 1 0 0 0 0 0 T 2 0 0 1 0 X 0 1 0 0 0 T 3 0 0 1 1 X X X 0 1 T 4 0 1 0 0 0 0 1 1 0 0 T 5 0 1 0 1 0 1 0 0 0 0 0 T 5 X X X 0 0 0 1 1 0 0 0 1 X X 1 0 1 1 0 0 0 0 1 1 0 0 T 6 0 1 1 0 X X X 0 1 1 1 0 0 0 0 1 0 T 7 0 1 1 1 X X X 1 0 0 0 1 T 8 1 0 0 0 X X X 1 0 0 0 0

PLA Input Present state is In binary t 3 t 3 PLA Output inputs Q[1] Q[0] Z Next state in binary t 3+ t 2+ t 1+ t 0+ Control functions C 0 C 1 C 2 C 3 C 4 C 5 C 6 C 7 C 8 C 9 T 0 0 0 X X X 0 0 0 1 1 0 0 0 0 T 1 0 0 0 1 X X X 0 0 1 0 0 0 0 T 2 0 0 1 X 0 0 1 1 0 0 0 0 0 T 2 0 0 1 0 0 0 X 0 1 0 0 0 0 0 T 2 0 0 1 1 X 0 1 0 0 0 0 0 T 2 0 0 1 0 X 0 1 0 0 0 T 3 0 0 1 1 X X X 0 1 T 4 0 1 0 0 0 0 1 1 0 0 T 5 0 1 0 1 0 1 0 0 1 1 0 1 T 5 X X X 0 0 0 0 0 X X 1 0 1 1 0 0 0 0 1 1 0 0 T 6 0 1 1 0 X X X 0 1 1 1 0 0 0 0 1 0 T 7 0 1 1 1 X X X 1 0 0 0 1 T 8 1 0 0 0 X X X 1 0 0 0 Normal sequencing activity is allowvable in the following situations: Present control state is : T 0 T 1 T 4 T 6 T 7 Present control state is : T 2 and Q[1]Q[0] = 01 Present control state is : T 5 and Z = 1 0 0

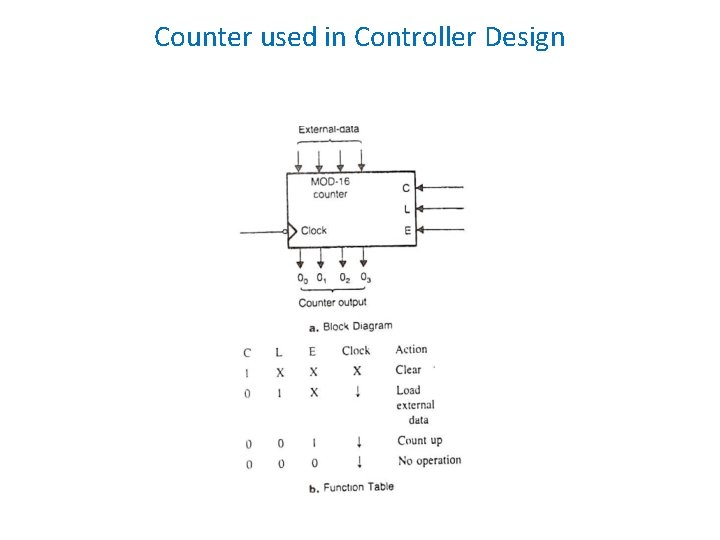

Counter used in Controller Design

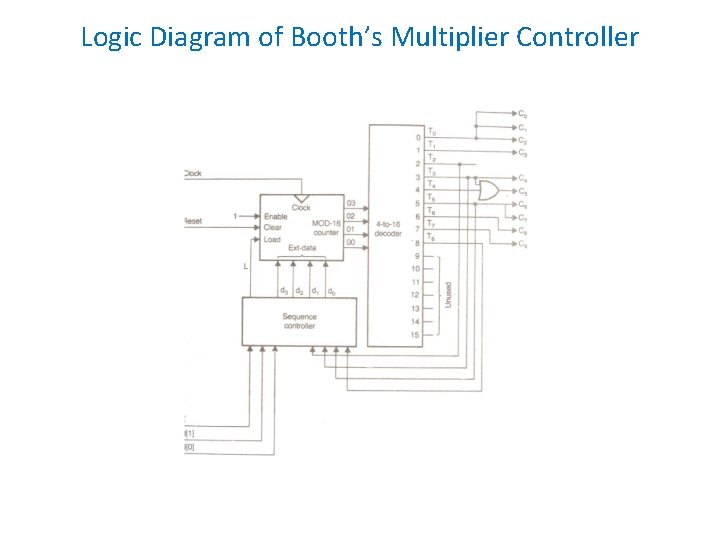

Logic Diagram of Booth’s Multiplier Controller

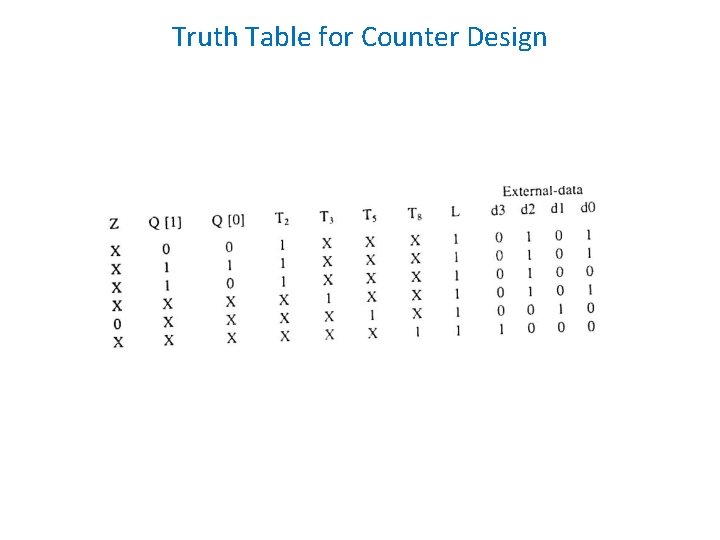

Truth Table for Counter Design

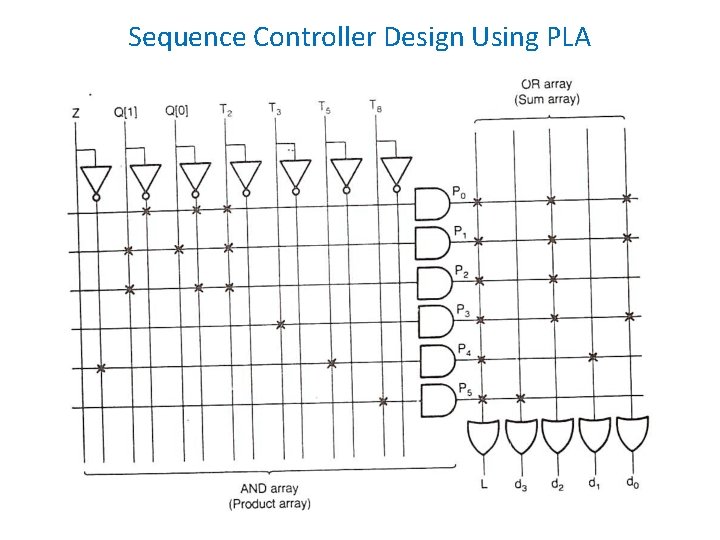

Sequence Controller Design Using PLA

PLA Input Present state is Present state In binary t 3 t 3 PLA Output inputs Q[1] Q[0] Z Next state in binary t 3+ t 2+ t 1+ t 0+ Control functions C 0 C 1 C 2 C 3 C 4 C 5 C 6 C 7 C 8 C 9 T 0 0 0 X X X 0 0 0 1 1 0 0 0 0 T 1 0 0 0 1 X X X 0 0 1 0 0 0 0 T 2 0 0 1 X 0 0 1 1 0 0 0 0 0 T 2 0 0 1 0 0 0 X 0 1 0 0 0 0 0 T 2 0 0 1 1 X 0 1 0 0 0 0 0 T 2 0 0 1 0 X 0 1 0 0 0 T 3 0 0 1 1 X X X 0 1 T 4 0 1 0 0 0 0 1 1 0 0 T 5 0 1 0 1 0 1 0 0 0 0 0 T 5 X X X 0 0 0 1 1 0 0 0 1 X X 1 0 1 1 0 0 0 0 1 1 0 0 T 6 0 1 1 0 X X X 0 1 1 1 0 0 0 0 1 0 T 7 0 1 1 1 X X X 1 0 0 0 1 T 8 1 0 0 0 X X X 1 0 0 0 0

T 0 T 1 T 2 T 2 T 3 T 4 T 5 T 6 T 7 T 8

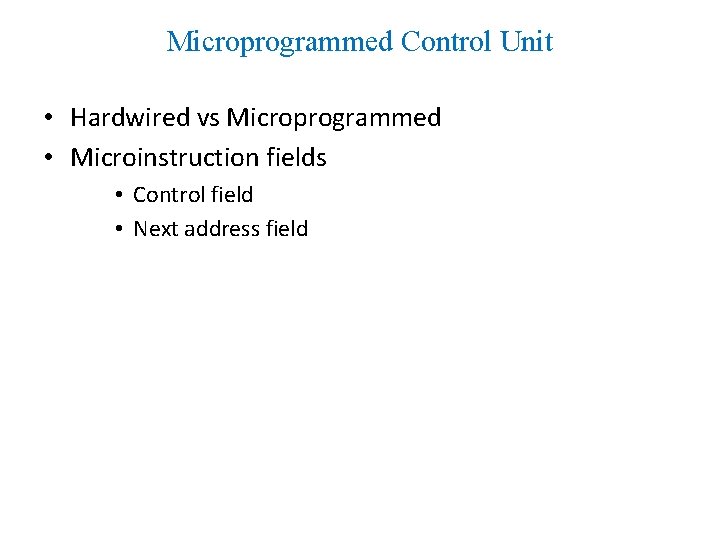

Microprogrammed Control Unit • Hardwired vs Microprogrammed • Microinstruction fields • Control field • Next address field

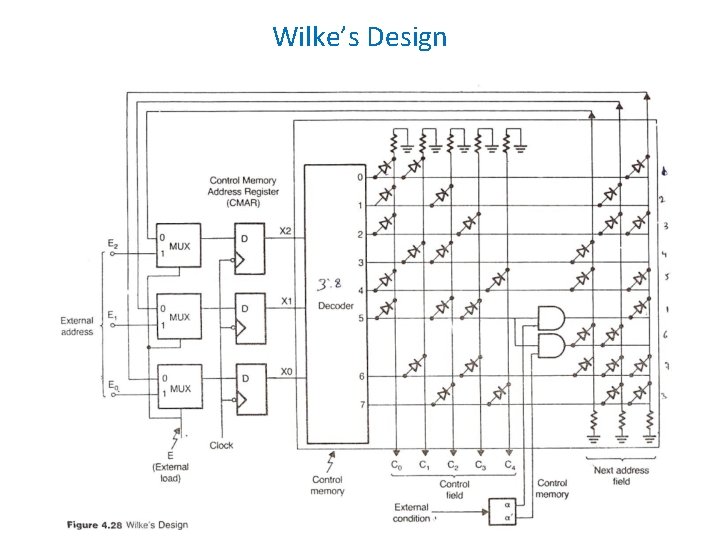

Wilke’s Design

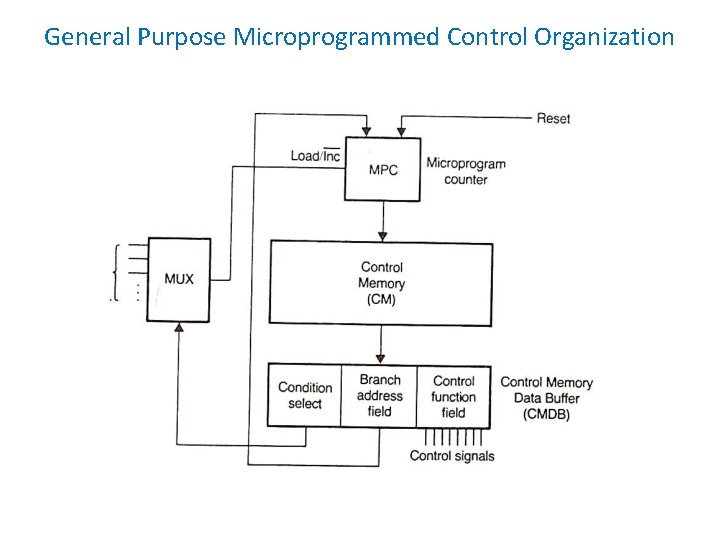

General Purpose Microprogrammed Control Organization

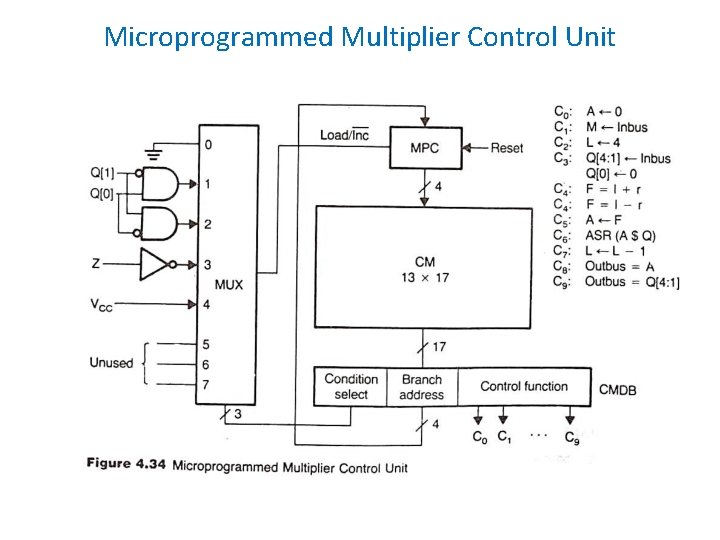

Microprogrammed Multiplier Control Unit

- Slides: 28