Math Coprocessor Also called Floating Point Unit FPU

- Slides: 20

Math Coprocessor Also called Floating Point Unit FPU 11/23/2020 TUC-N dr. Emil CEBUC

Outline l l l Math Coprocessor Operation Math Coprocessor Structure Data Types Representation error Instructions 11/23/2020 TUC-N dr. Emil CEBUC

Math Coprocessor Operation l l l Shares the same Data, Address and Control BUS as the main processor Two different chips for old processors On the same silicon die starting with 486 DX Instructions preceded by an ESC sequence Operates in parallel with main processor Coprocessor may overtake BUS for longer periods if more data is needed 11/23/2020 TUC-N dr. Emil CEBUC

Math Coprocessor Operation l l l Coprocessor has no access to registers But can use registers for addressing All addressing modes are available except immediate addressing Uses special synchronization signals to cooperate Instructions take tens to hundreds of cycles to complete 11/23/2020 TUC-N dr. Emil CEBUC

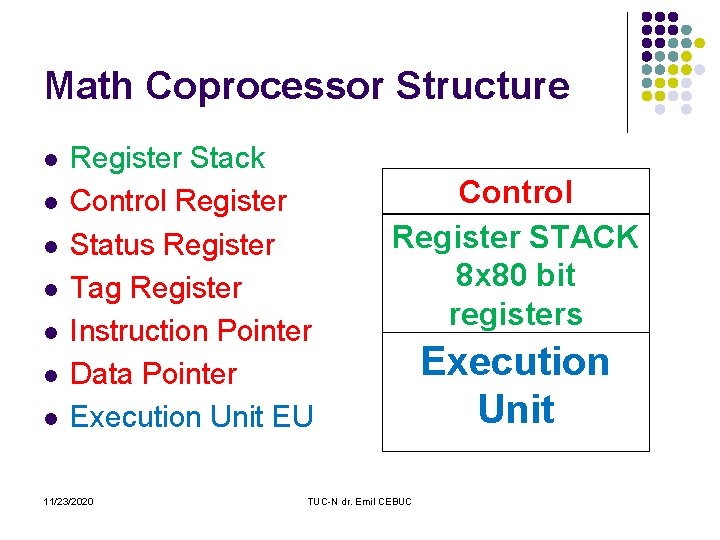

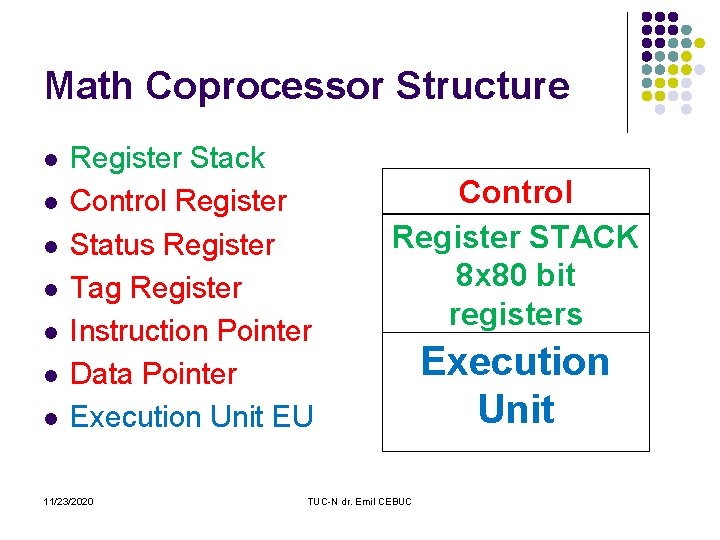

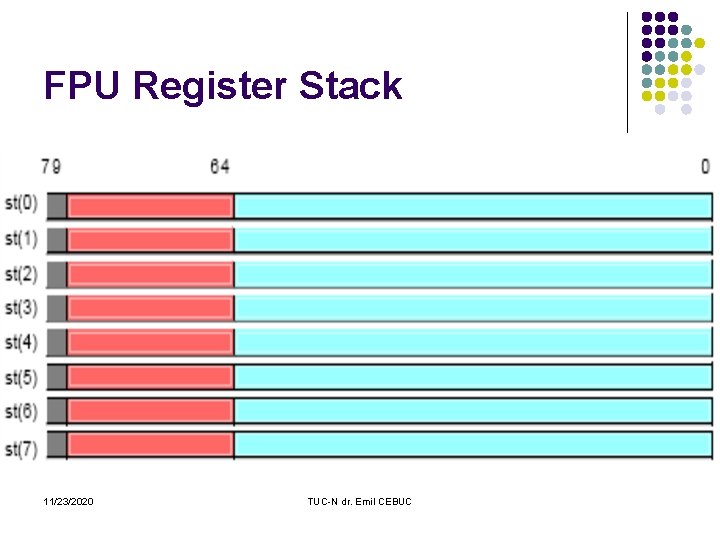

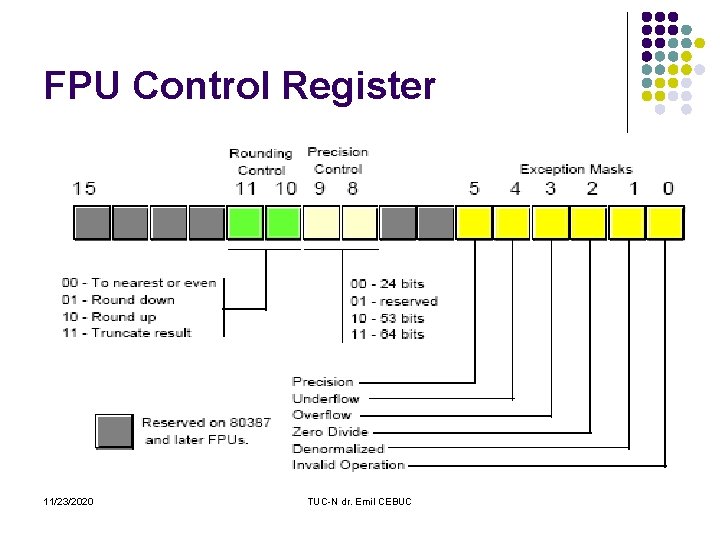

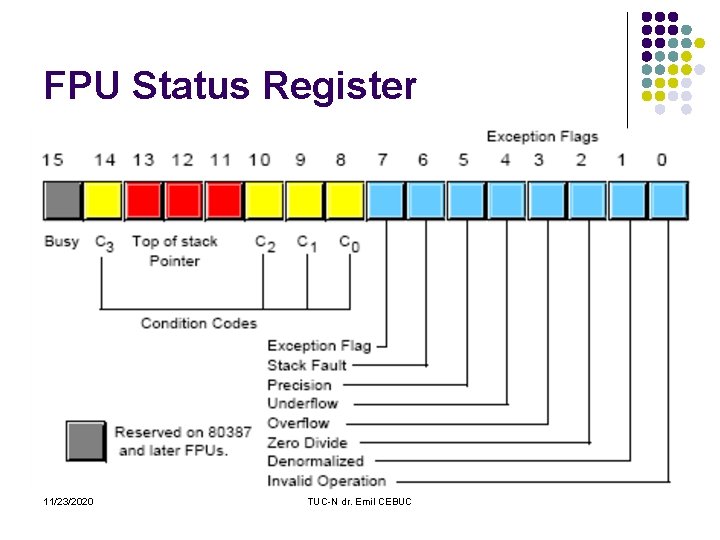

Math Coprocessor Structure l l l l Register Stack Control Register Status Register Tag Register Instruction Pointer Data Pointer Execution Unit EU 11/23/2020 Control Register STACK 8 x 80 bit registers TUC-N dr. Emil CEBUC Execution Unit

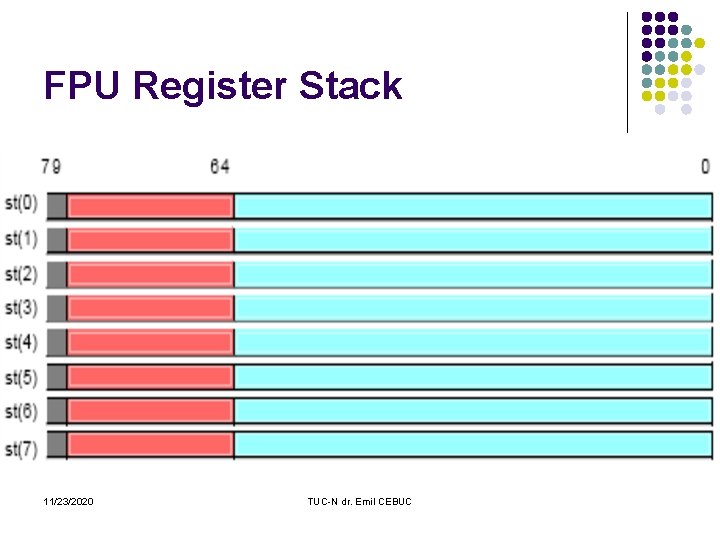

FPU Register Stack 11/23/2020 TUC-N dr. Emil CEBUC

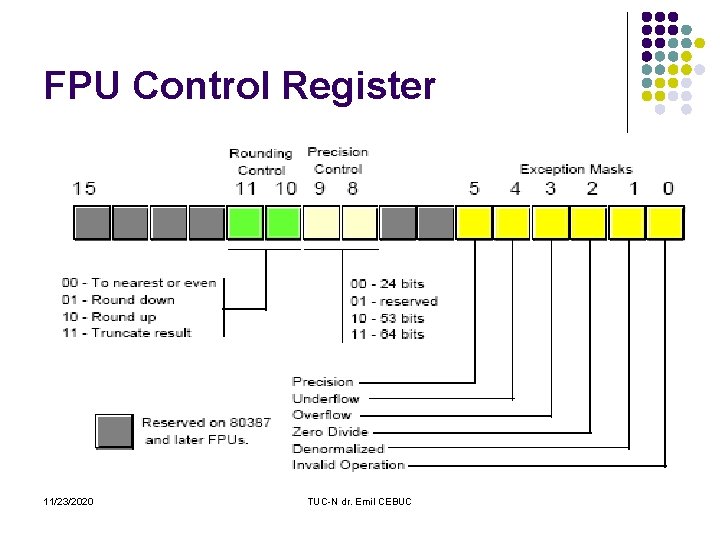

FPU Control Register 11/23/2020 TUC-N dr. Emil CEBUC

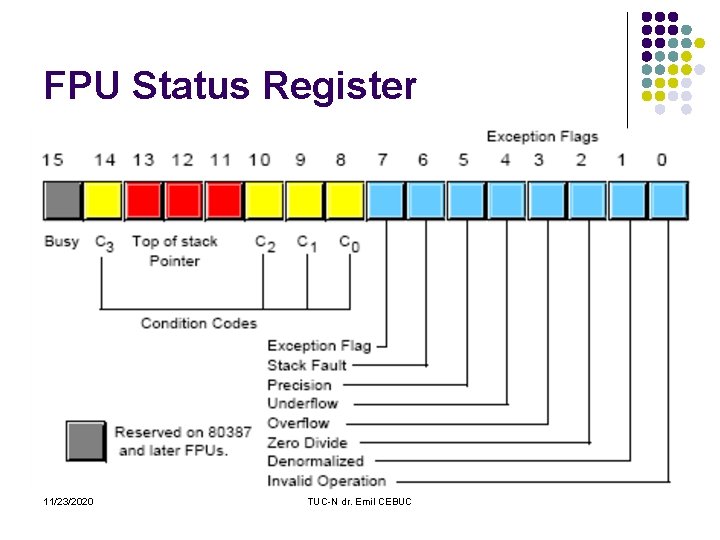

FPU Status Register 11/23/2020 TUC-N dr. Emil CEBUC

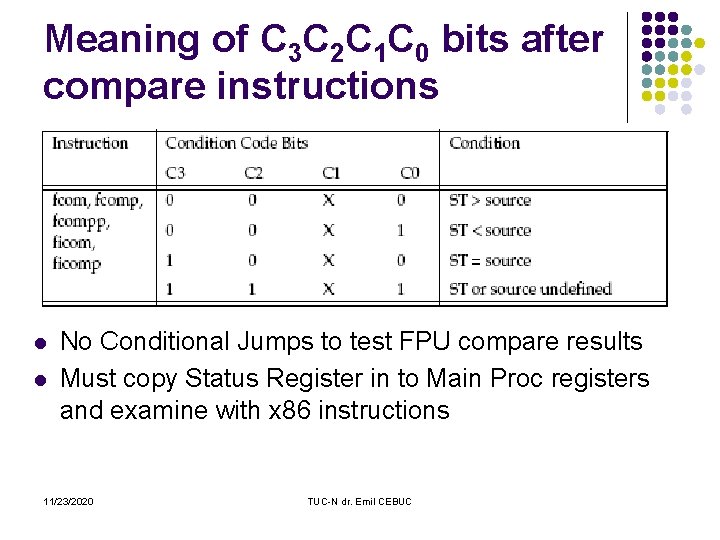

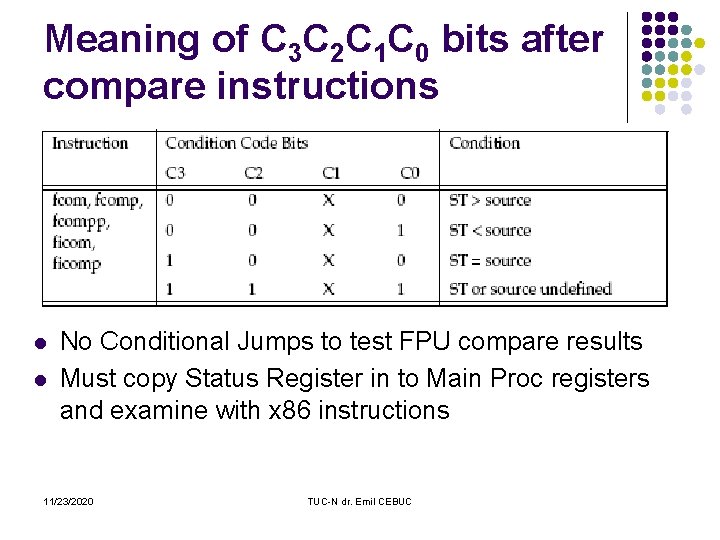

Meaning of C 3 C 2 C 1 C 0 bits after compare instructions l l No Conditional Jumps to test FPU compare results Must copy Status Register in to Main Proc registers and examine with x 86 instructions 11/23/2020 TUC-N dr. Emil CEBUC

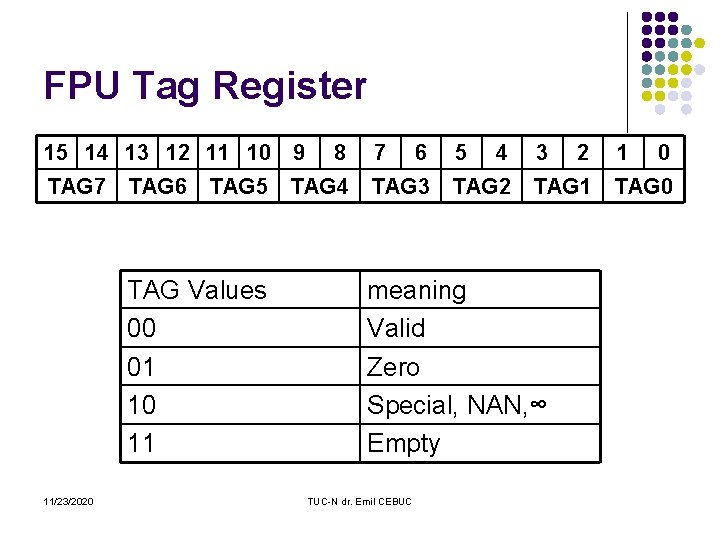

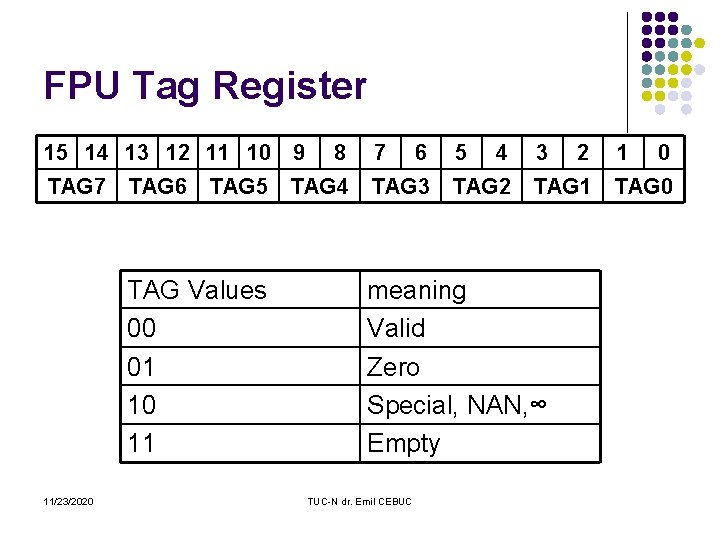

FPU Tag Register 15 14 13 12 11 10 9 TAG 7 TAG 4 TAG 6 TAG 5 TAG Values 00 01 10 11 11/23/2020 8 7 6 TAG 3 5 4 TAG 2 3 TAG 1 meaning Valid Zero Special, NAN, ∞ Empty TUC-N dr. Emil CEBUC 2 1 0 TAG 0

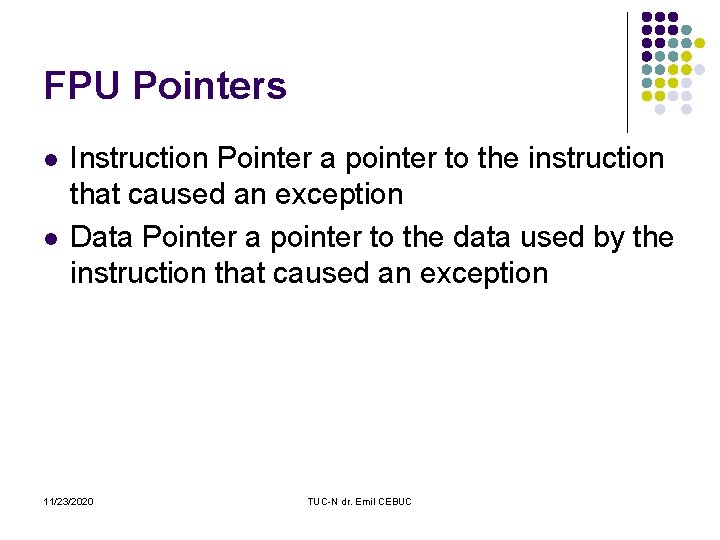

FPU Pointers l l Instruction Pointer a pointer to the instruction that caused an exception Data Pointer a pointer to the data used by the instruction that caused an exception 11/23/2020 TUC-N dr. Emil CEBUC

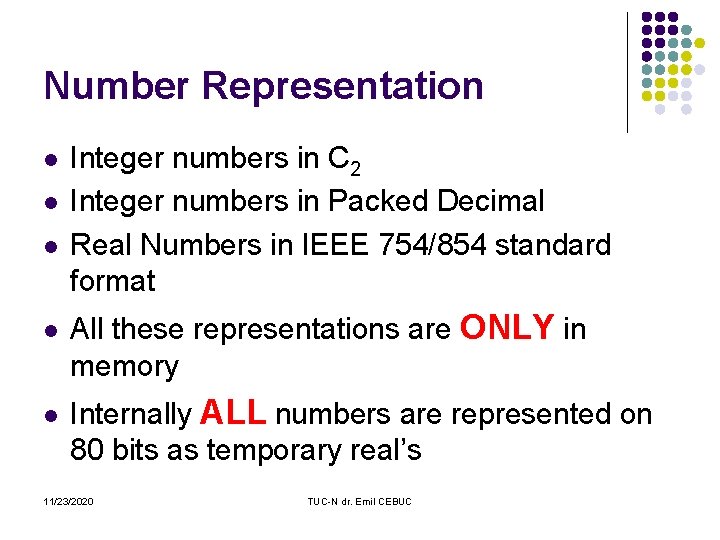

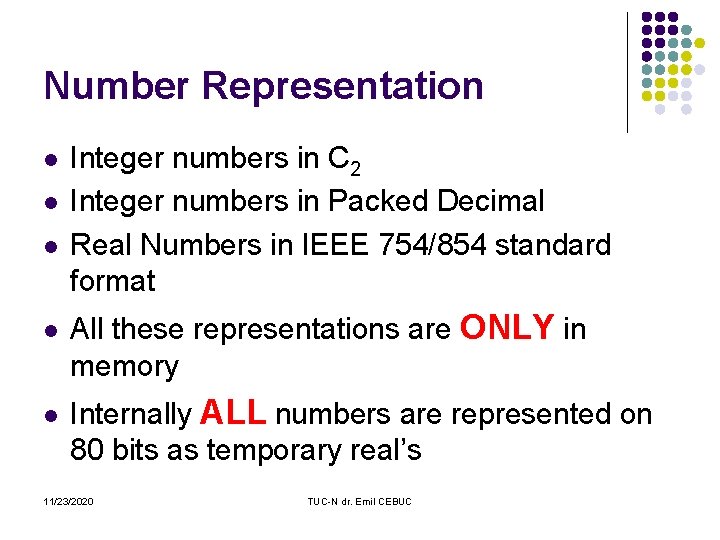

Number Representation l l l Integer numbers in C 2 Integer numbers in Packed Decimal Real Numbers in IEEE 754/854 standard format All these representations are ONLY in memory Internally ALL numbers are represented on 80 bits as temporary real’s 11/23/2020 TUC-N dr. Emil CEBUC

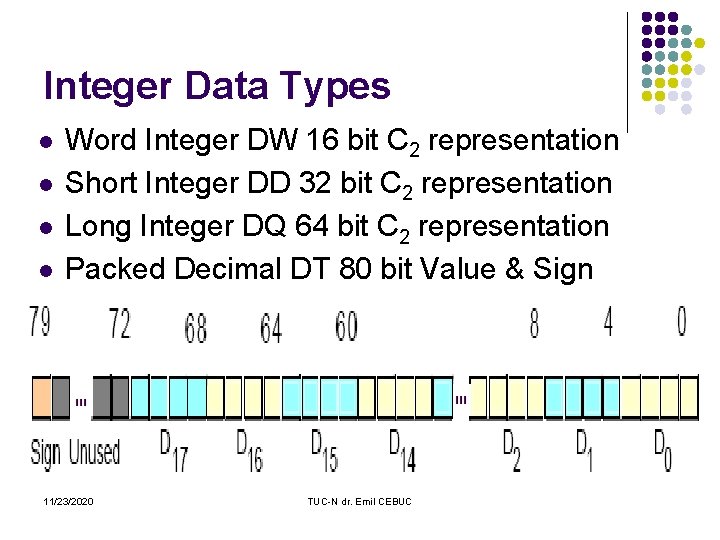

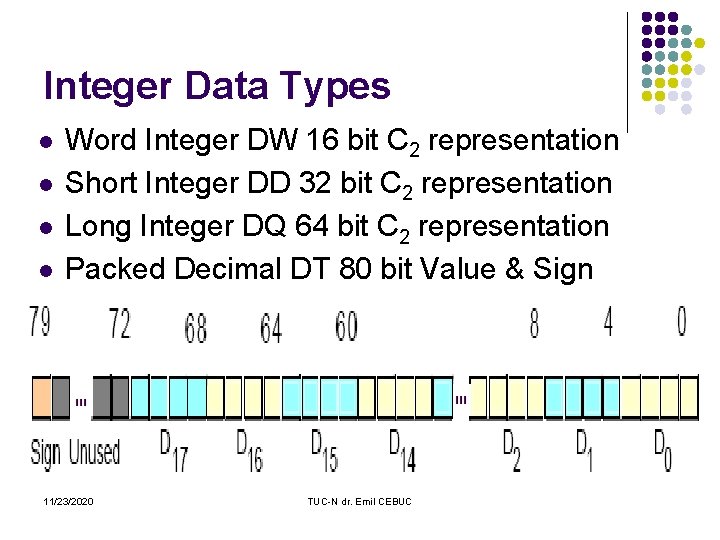

Integer Data Types l l Word Integer DW 16 bit C 2 representation Short Integer DD 32 bit C 2 representation Long Integer DQ 64 bit C 2 representation Packed Decimal DT 80 bit Value & Sign 11/23/2020 TUC-N dr. Emil CEBUC

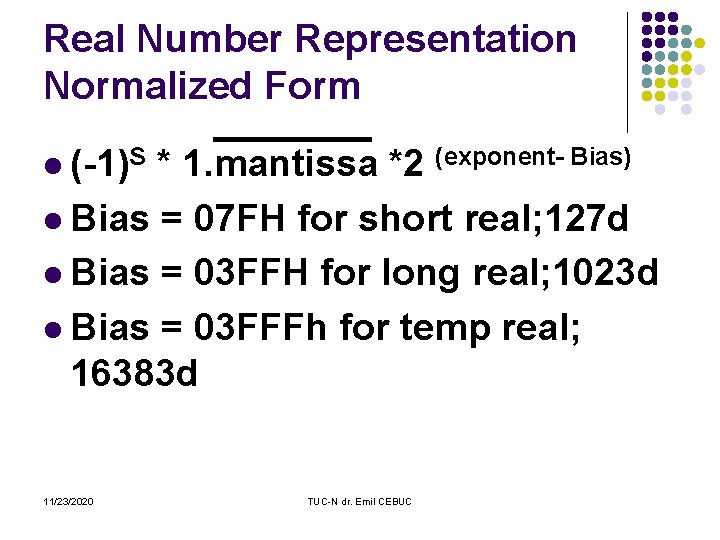

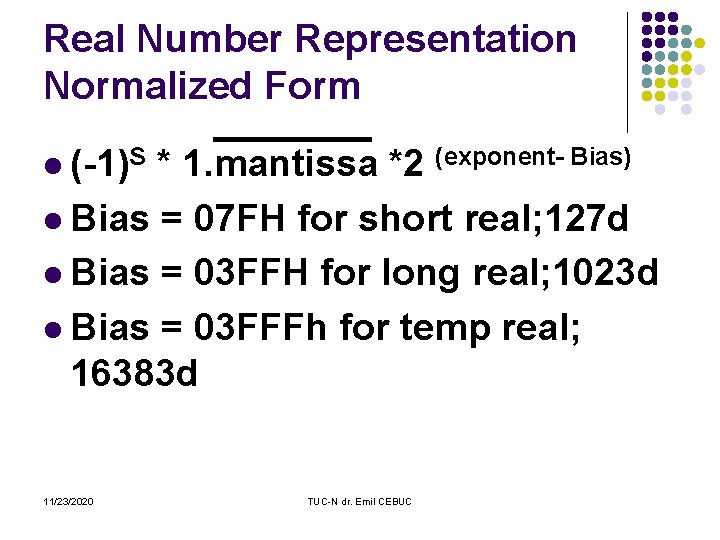

Real Number Representation Normalized Form l (-1)S * 1. mantissa *2 (exponent- Bias) l Bias = 07 FH for short real; 127 d l Bias = 03 FFH for long real; 1023 d l Bias = 03 FFFh for temp real; 16383 d 11/23/2020 TUC-N dr. Emil CEBUC

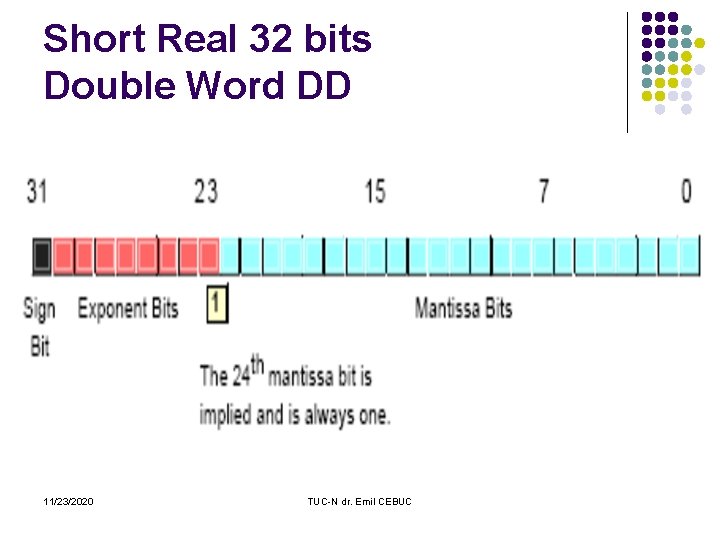

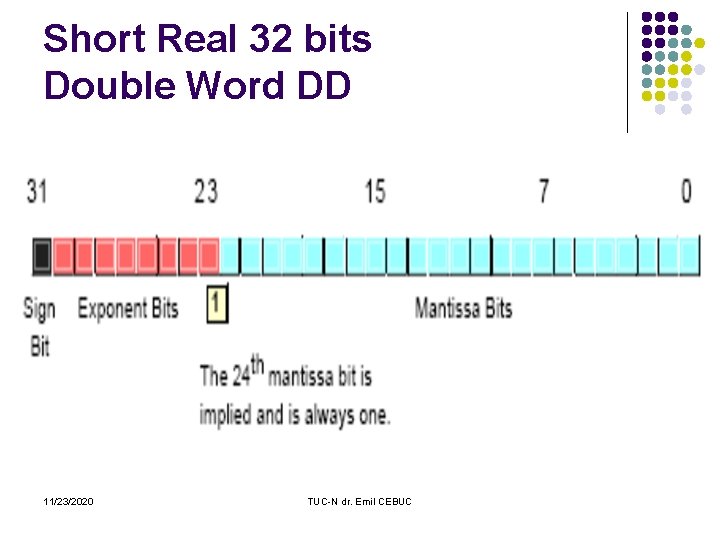

Short Real 32 bits Double Word DD 11/23/2020 TUC-N dr. Emil CEBUC

Long Real 64 bits Quad Word DQ 11/23/2020 TUC-N dr. Emil CEBUC

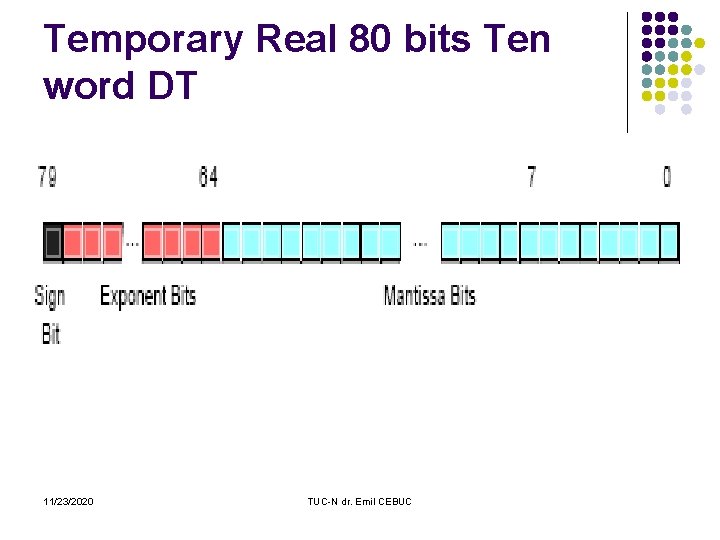

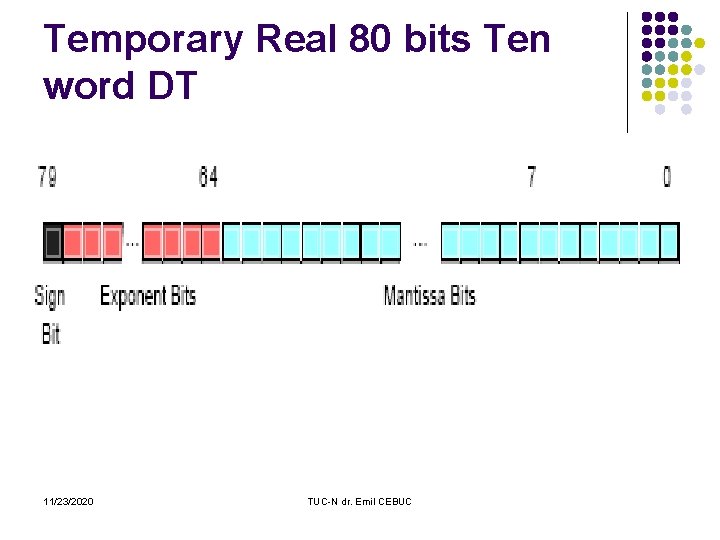

Temporary Real 80 bits Ten word DT 11/23/2020 TUC-N dr. Emil CEBUC

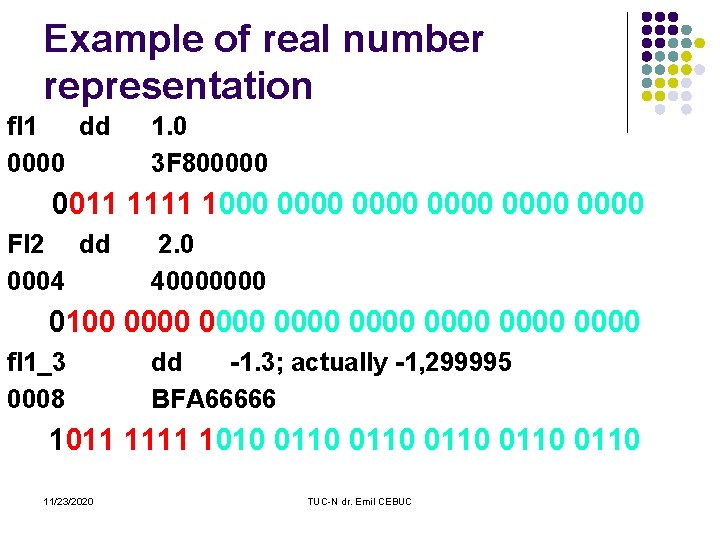

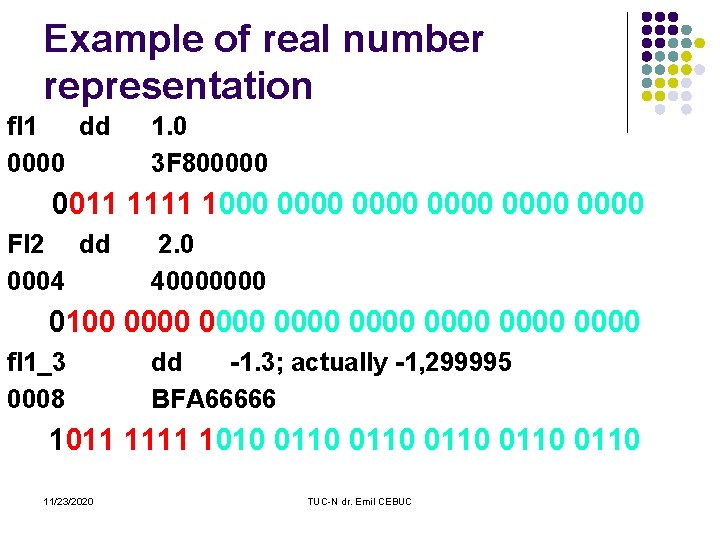

Example of real number representation fl 1 dd 0000 1. 0 3 F 800000 0011 1111 1000 0000 0000 Fl 2 dd 0004 2. 0 40000000 0100 0000 0000 fl 1_3 0008 dd -1. 3; actually -1, 299995 BFA 66666 1011 1111 1010 0110 0110 11/23/2020 TUC-N dr. Emil CEBUC

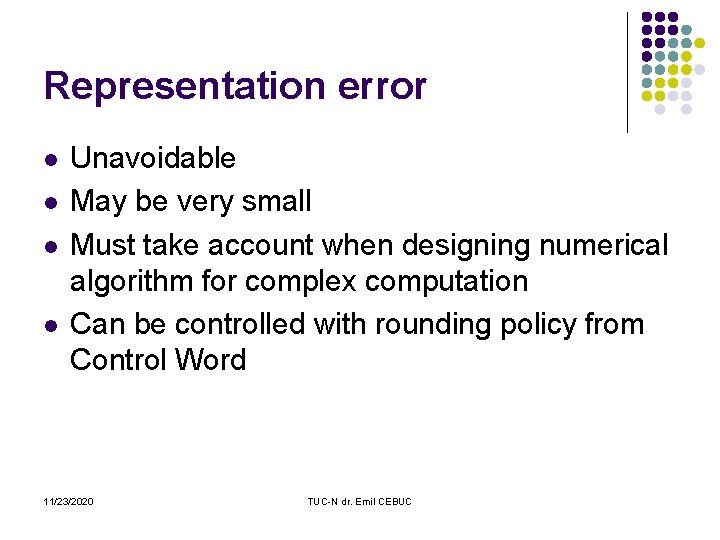

Representation error l l Unavoidable May be very small Must take account when designing numerical algorithm for complex computation Can be controlled with rounding policy from Control Word 11/23/2020 TUC-N dr. Emil CEBUC

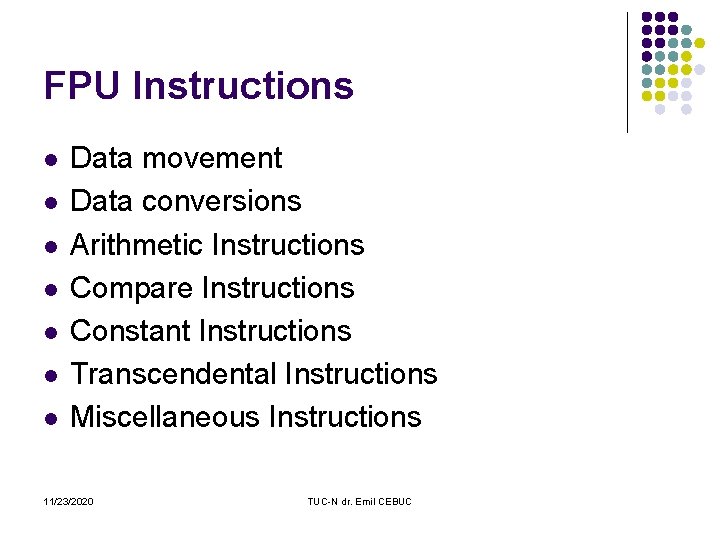

FPU Instructions l l l l Data movement Data conversions Arithmetic Instructions Compare Instructions Constant Instructions Transcendental Instructions Miscellaneous Instructions 11/23/2020 TUC-N dr. Emil CEBUC