Master en Ingeniera de Sistemas Empotrados UPV EHU

- Slides: 14

Master en Ingeniería de Sistemas Empotrados UPV / EHU MOISE Departamento de Arquitectura y Tecnología de Computadores Universidad del País Vasco / Euskal Herriko Unibertsitatea Introducción al tiempo real en sistemas empotrados Konputagailuen Arkitektura eta Teknologia Saila Departamento de Arquitectura y Tecnología de Computadores 1

Contenido UPV / EHU MOISE • • • Introducción Soporte de interrupciones Conceptos de sistemas operativos Planificación en sistemas de tiempo real Mecanismos de sincronización y comunicación Planificación de tiempo real con recursos compartidos Konputagailuen Arkitektura eta Teknologia Saila Departamento de Arquitectura y Tecnología de Computadores 2

Soporte de interrupciones CONTENIDO UPV / EHU MOISE • • • Introducción Interrupciones y excepciones Controladores de interrupciones Manejadores de interrupciones Mecanismo de ejecución de interrupciones y excepciones BIBLIOGRAFIA • Q. Li: Real-Time concepts for embedded systems. CMP Books, 2003. Capítulo 10. Konputagailuen Arkitektura eta Teknologia Saila Departamento de Arquitectura y Tecnología de Computadores 3

Introducción UPV / EHU MOISE • El hardware del sistema está compuesto de sensores, actuadores y recursos de cómputo (procesador, memoria). • Interfaz hardware para el programador: – – – Instrucciones del lenguaje máquina Espacio de direcciones de memoria Espacio de direcciones de entrada/salida Vectores de interrupciones … • Un sistema operativo (o componentes del SO), que se instala sobre esta interfaz permite compartir y gestionar el hardware de forma más sencilla. Konputagailuen Arkitektura eta Teknologia Saila Departamento de Arquitectura y Tecnología de Computadores 4

Interrupciones y excepciones • Excepción: UPV / EHU MOISE Evento que, producido durante la ejecución de un programa, provoca que el procesador ejecute un código especial para tratarla. – También llamadas interrupciones internas. • Interrupción: Condición asíncrona provocada por un dispositivo externo. – También llamadas excepciones asíncronas. – Se tratan de la misma forma que las excepciones. Konputagailuen Arkitektura eta Teknologia Saila Departamento de Arquitectura y Tecnología de Computadores 5

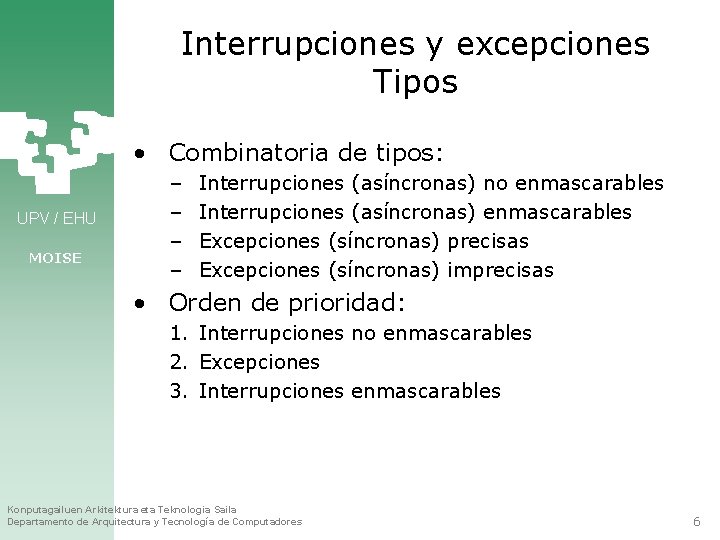

Interrupciones y excepciones Tipos • Combinatoria de tipos: UPV / EHU MOISE – – Interrupciones (asíncronas) no enmascarables Interrupciones (asíncronas) enmascarables Excepciones (síncronas) precisas Excepciones (síncronas) imprecisas • Orden de prioridad: 1. Interrupciones no enmascarables 2. Excepciones 3. Interrupciones enmascarables Konputagailuen Arkitektura eta Teknologia Saila Departamento de Arquitectura y Tecnología de Computadores 6

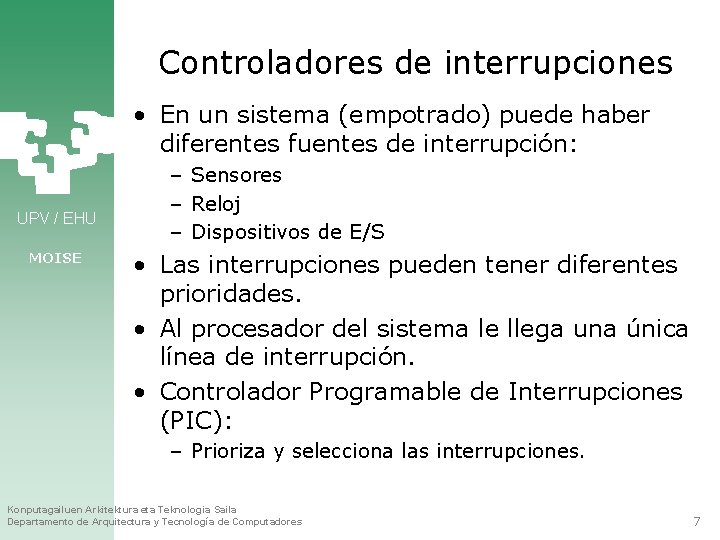

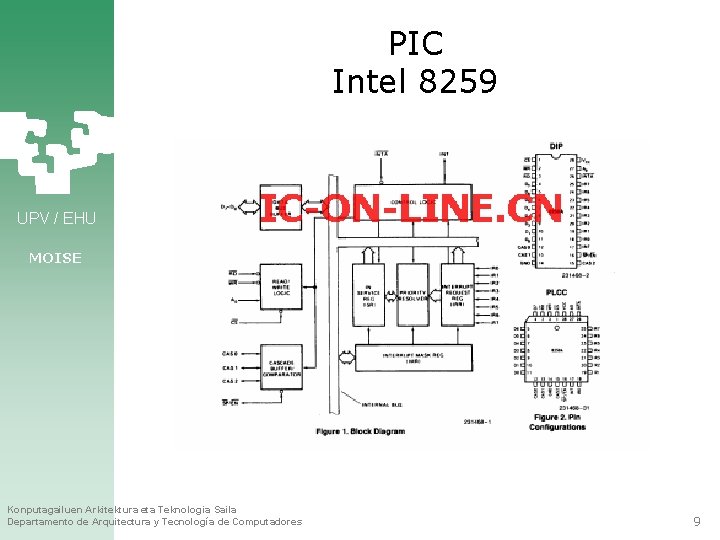

Controladores de interrupciones • En un sistema (empotrado) puede haber diferentes fuentes de interrupción: UPV / EHU MOISE – Sensores – Reloj – Dispositivos de E/S • Las interrupciones pueden tener diferentes prioridades. • Al procesador del sistema le llega una única línea de interrupción. • Controlador Programable de Interrupciones (PIC): – Prioriza y selecciona las interrupciones. Konputagailuen Arkitektura eta Teknologia Saila Departamento de Arquitectura y Tecnología de Computadores 7

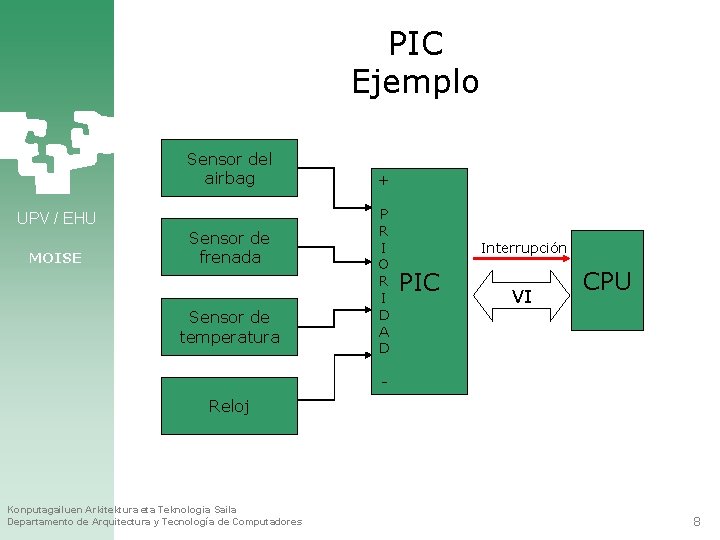

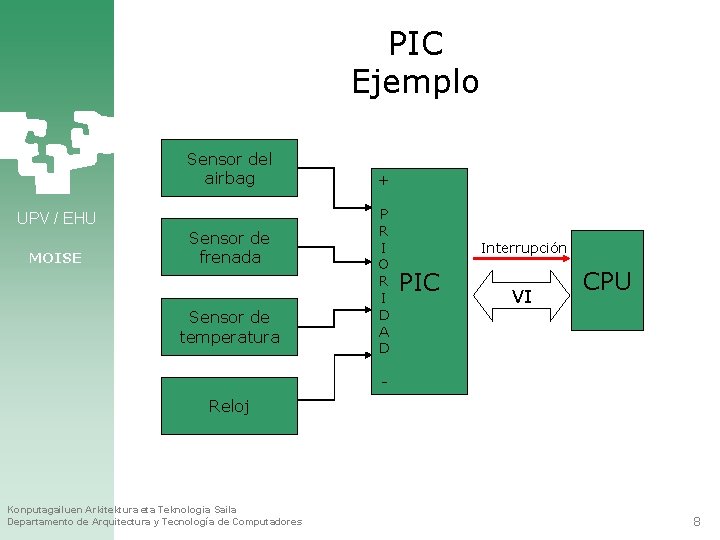

PIC Ejemplo Sensor del airbag UPV / EHU MOISE Sensor de frenada Sensor de temperatura + P R I O R I D A D Interrupción PIC VI CPU - Reloj Konputagailuen Arkitektura eta Teknologia Saila Departamento de Arquitectura y Tecnología de Computadores 8

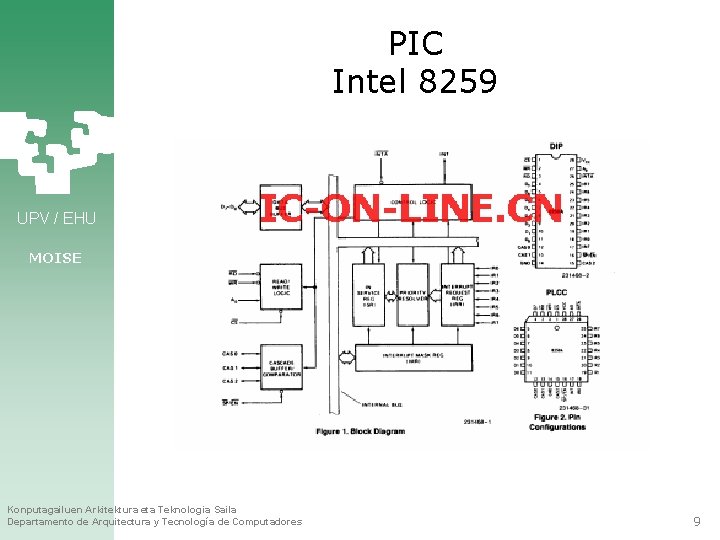

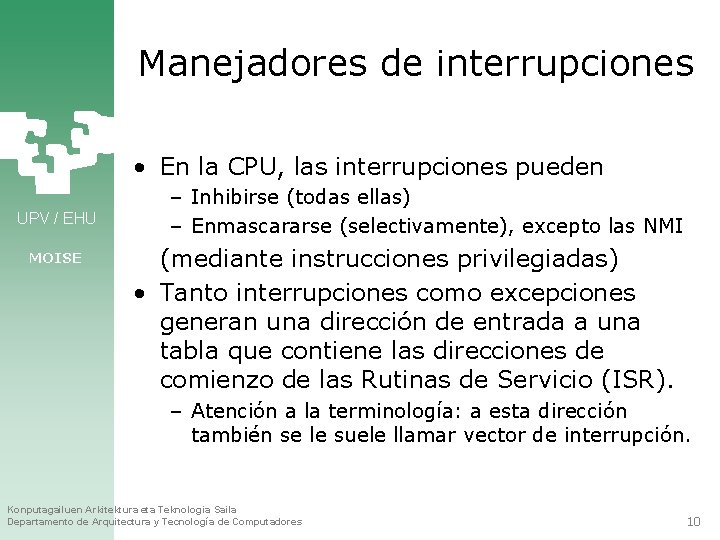

PIC Intel 8259 UPV / EHU MOISE Konputagailuen Arkitektura eta Teknologia Saila Departamento de Arquitectura y Tecnología de Computadores 9

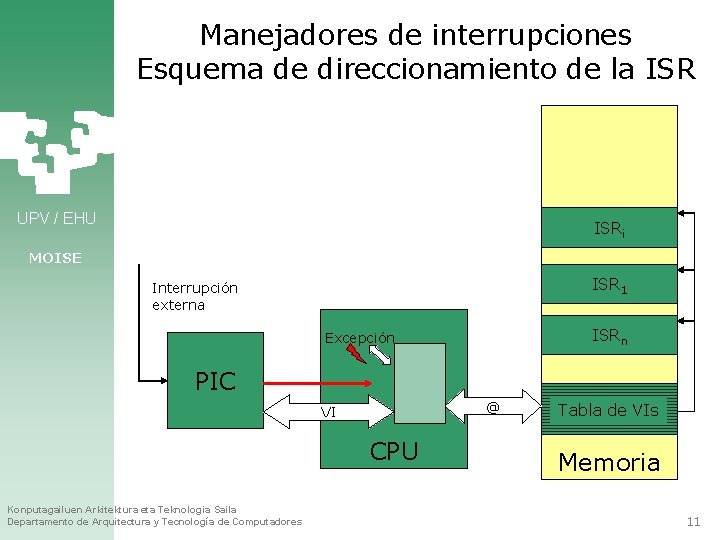

Manejadores de interrupciones • En la CPU, las interrupciones pueden UPV / EHU MOISE – Inhibirse (todas ellas) – Enmascararse (selectivamente), excepto las NMI (mediante instrucciones privilegiadas) • Tanto interrupciones como excepciones generan una dirección de entrada a una tabla que contiene las direcciones de comienzo de las Rutinas de Servicio (ISR). – Atención a la terminología: a esta dirección también se le suele llamar vector de interrupción. Konputagailuen Arkitektura eta Teknologia Saila Departamento de Arquitectura y Tecnología de Computadores 10

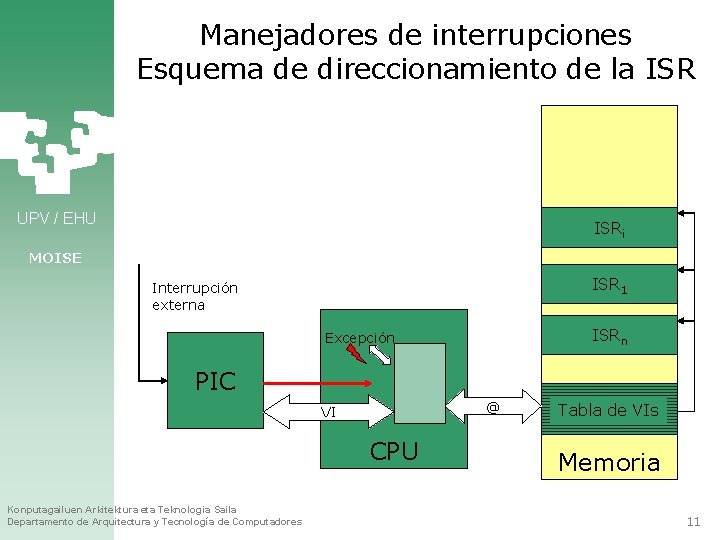

Manejadores de interrupciones Esquema de direccionamiento de la ISR UPV / EHU ISRi MOISE ISR 1 Interrupción externa ISRn Excepción PIC @ VI CPU Konputagailuen Arkitektura eta Teknologia Saila Departamento de Arquitectura y Tecnología de Computadores Tabla de VIs Memoria 11

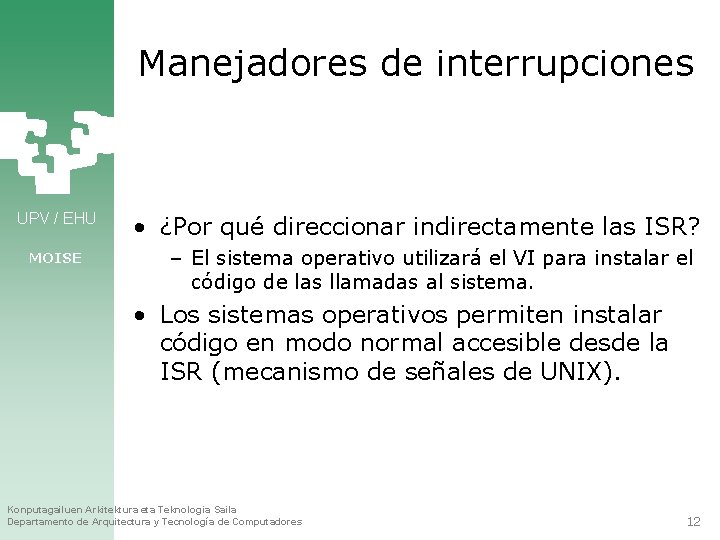

Manejadores de interrupciones UPV / EHU MOISE • ¿Por qué direccionar indirectamente las ISR? – El sistema operativo utilizará el VI para instalar el código de las llamadas al sistema. • Los sistemas operativos permiten instalar código en modo normal accesible desde la ISR (mecanismo de señales de UNIX). Konputagailuen Arkitektura eta Teknologia Saila Departamento de Arquitectura y Tecnología de Computadores 12

Mecanismo de ejecución UPV / EHU MOISE • La interrupción/excepción requiere su propio contexto de ejecución (pila). • Debe guardarse el contexto del programa que se está ejecutando para recuperarlo tras la ejecución. Konputagailuen Arkitektura eta Teknologia Saila Departamento de Arquitectura y Tecnología de Computadores 13

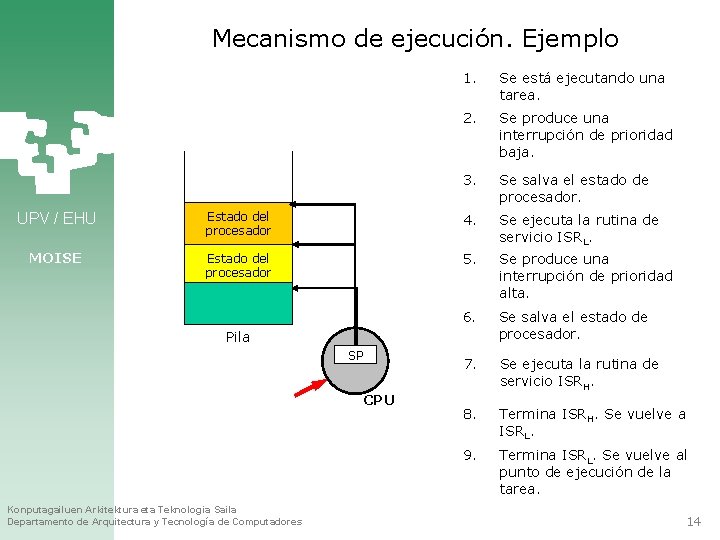

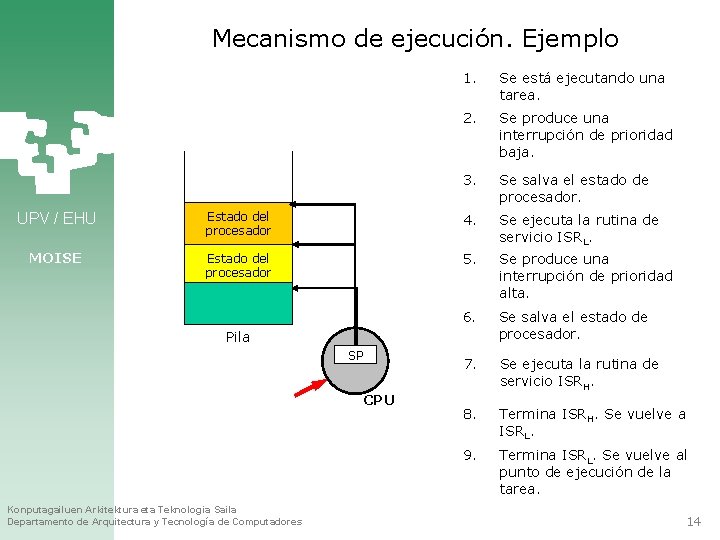

Mecanismo de ejecución. Ejemplo 1. Se está ejecutando una tarea. 2. Se produce una interrupción de prioridad baja. 3. Se salva el estado de procesador. UPV / EHU Estado del procesador 4. Se ejecuta la rutina de servicio ISRL. MOISE Estado del procesador 5. Se produce una interrupción de prioridad alta. 6. Se salva el estado de procesador. 7. Se ejecuta la rutina de servicio ISRH. 8. Termina ISRH. Se vuelve a ISRL. 9. Termina ISRL. Se vuelve al punto de ejecución de la tarea. Pila SP CPU Konputagailuen Arkitektura eta Teknologia Saila Departamento de Arquitectura y Tecnología de Computadores 14