Mapping Algorithm for Largescale Field Programmable Analog Array

Mapping Algorithm for Large-scale Field Programmable Analog Array (FPAA) Faik Baskaya, Sasank Reddy, Sung Kyu Lim, Tyson Hall, and David Anderson School of Electrical and Computer Engineering Georgia Institute of Technology Atlanta, GA 30332 {baskaya, sreddy, limsk, tyson, dva}@ece. gatech. edu ISPD’ 2005, San Francisco April 5, 2005

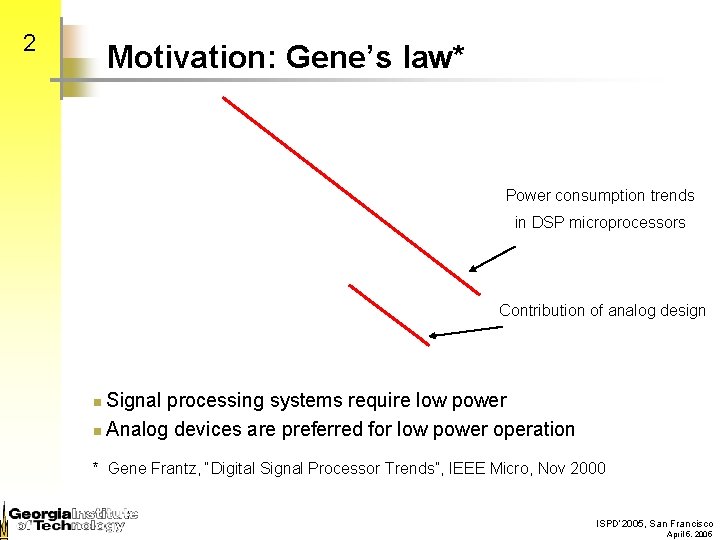

2 Motivation: Gene’s law* Power consumption trends in DSP microprocessors Contribution of analog design Signal processing systems require low power n Analog devices are preferred for low power operation n * Gene Frantz, “Digital Signal Processor Trends”, IEEE Micro, Nov 2000 ISPD’ 2005, San Francisco April 5, 2005

3 Field Programmable Analog Arrays (FPAA) n Array of Computational Analog Blocks (CAB) n Discrete time and continuous time versions n Not LUT based => heterogeneous resources n n Interconnect lines not segmented => less routing options Device/interconnect constraints different from FPGA => existing methods do not easily apply! ISPD’ 2005, San Francisco April 5, 2005

4 Previous Work n Discrete Time (switched capacitor based) FPAA n n n Continuous Time CMOS/Bipolar FPAA n n Former IMP EPAC: 150 k. Hz Former Motorola MPAA *: 200 k. Hz Lee-Gulak’ 1995: 125 k. Hz Fast Analog Solutions TRAC: 4 MHz Floating-gate based RASP: 11 MHz CAD tools n n Ganesan-Vemuri: DAC’ 2001 Wang-Vrudhula: Mixed Design of Integrated Circuits and Systems, 2001 *Now distributed by Anadigm ISPD’ 2005, San Francisco April 5, 2005

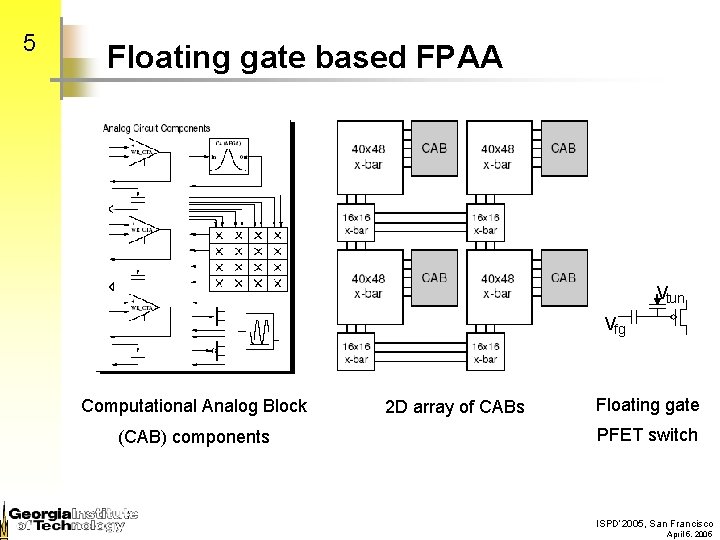

5 Floating gate based FPAA Vtun Vfg Computational Analog Block (CAB) components 2 D array of CABs Floating gate PFET switch ISPD’ 2005, San Francisco April 5, 2005

6 Interconnect Analysis n Three types of interconnects: n n n type 1: intra-CAB type 2: inter-CAB, intra-column type 3: inter-CAB, inter-column Clustering determines type 1 vs. types 2&3 Clustering maximizes type 1 use Vertical/horizontal wires are not segmented (unlike FPGA) R ~ 10 k. W (switch on resistance) Cx = S (all switch C’s on a line) ISPD’ 2005, San Francisco April 5, 2005

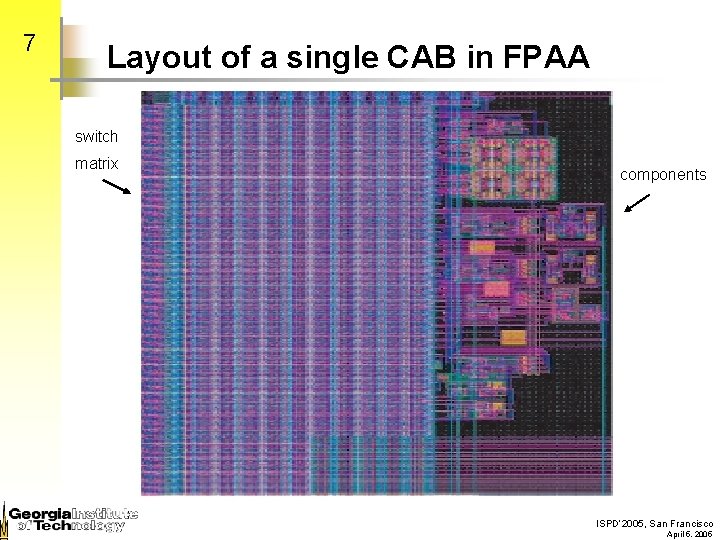

7 Layout of a single CAB in FPAA switch matrix components ISPD’ 2005, San Francisco April 5, 2005

8 Advantages of floating-gate based FPAA n Larger scale More components per CAB n More CABs per chip n More component variety n n Floating gate PFET switch technology Non-volatile memory unit n Programmable on resistance n Linear Voltage-Current characteristics n ISPD’ 2005, San Francisco April 5, 2005

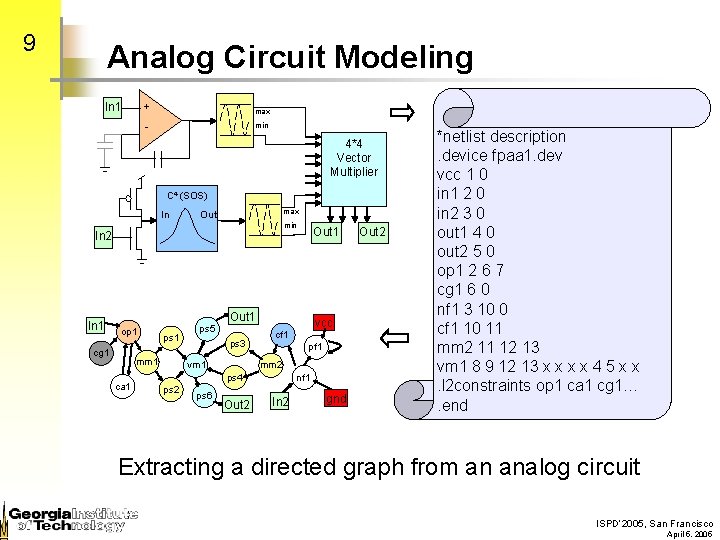

9 Analog Circuit Modeling In 1 + max - min 4*4 Vector Multiplier C 4 (SOS) In max Out min In 2 In 1 op 1 cg 1 ps 1 mm 1 ca 1 ps 5 Out 1 ps 3 pf 1 ps 4 ps 6 vcc cf 1 mm 2 vm 1 ps 2 Out 1 Out 2 nf 1 In 2 gnd Out 2 *netlist description. device fpaa 1. dev vcc 1 0 in 1 2 0 in 2 3 0 out 1 4 0 out 2 5 0 op 1 2 6 7 cg 1 6 0 nf 1 3 10 0 cf 1 10 11 mm 2 11 12 13 vm 1 8 9 12 13 x x 4 5 x x. l 2 constraints op 1 ca 1 cg 1…. end Extracting a directed graph from an analog circuit ISPD’ 2005, San Francisco April 5, 2005

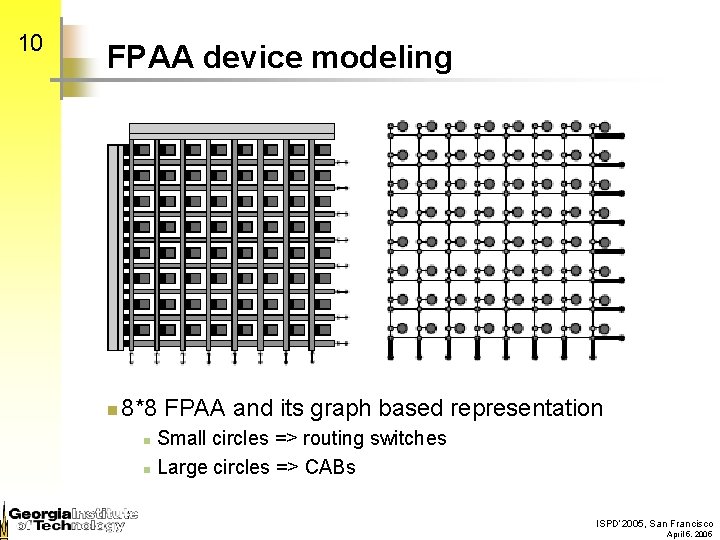

10 FPAA device modeling n 8*8 FPAA and its graph based representation Small circles => routing switches n Large circles => CABs n ISPD’ 2005, San Francisco April 5, 2005

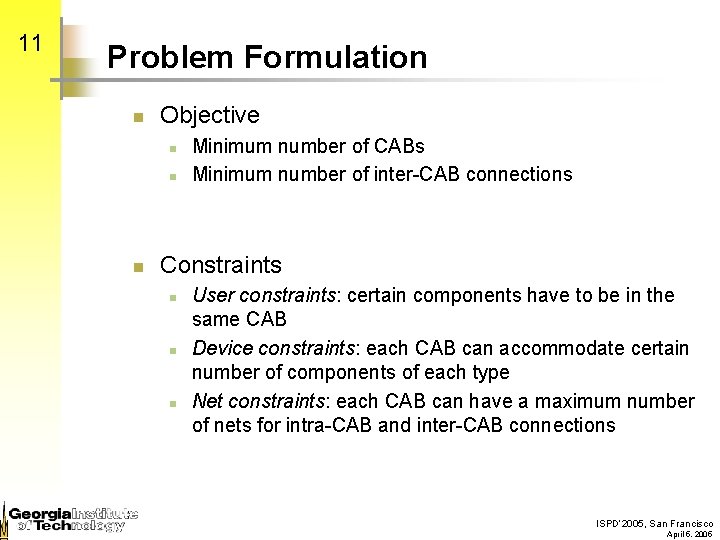

11 Problem Formulation n Objective n n n Minimum number of CABs Minimum number of inter-CAB connections Constraints n n n User constraints: certain components have to be in the same CAB Device constraints: each CAB can accommodate certain number of components of each type Net constraints: each CAB can have a maximum number of nets for intra-CAB and inter-CAB connections ISPD’ 2005, San Francisco April 5, 2005

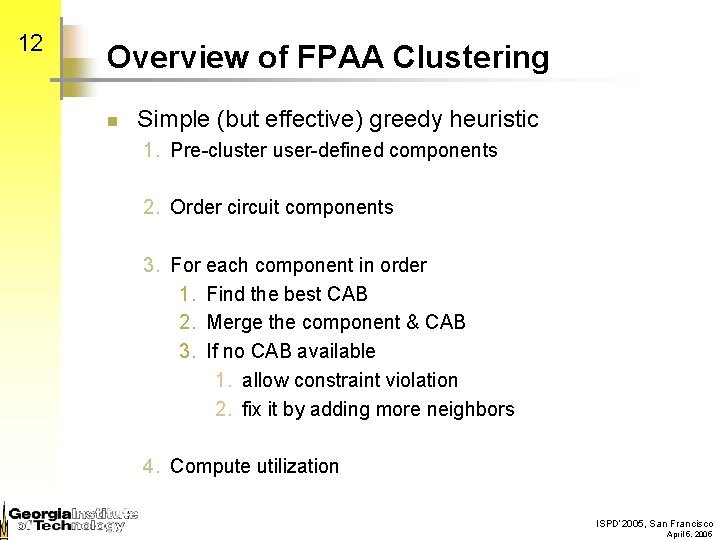

12 Overview of FPAA Clustering n Simple (but effective) greedy heuristic 1. Pre-cluster user-defined components 2. Order circuit components 3. For each component in order 1. Find the best CAB 2. Merge the component & CAB 3. If no CAB available 1. allow constraint violation 2. fix it by adding more neighbors 4. Compute utilization ISPD’ 2005, San Francisco April 5, 2005

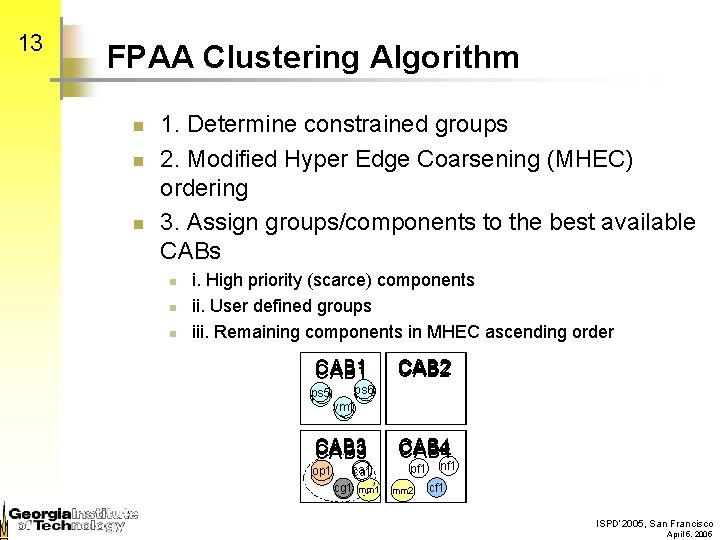

13 FPAA Clustering Algorithm n n n 1. Determine constrained groups 2. Modified Hyper Edge Coarsening (MHEC) ordering 3. Assign groups/components to the best available CABs n n n i. High priority (scarce) components ii. User defined groups iii. Remaining components in MHEC ascending order CAB 1 ps 5 ps 6 vm 1 CAB 3 op 1 CAB 2 CAB 4 pf 1 nf 1 ca 1 cg 1 mm 2 cf 1 ISPD’ 2005, San Francisco April 5, 2005

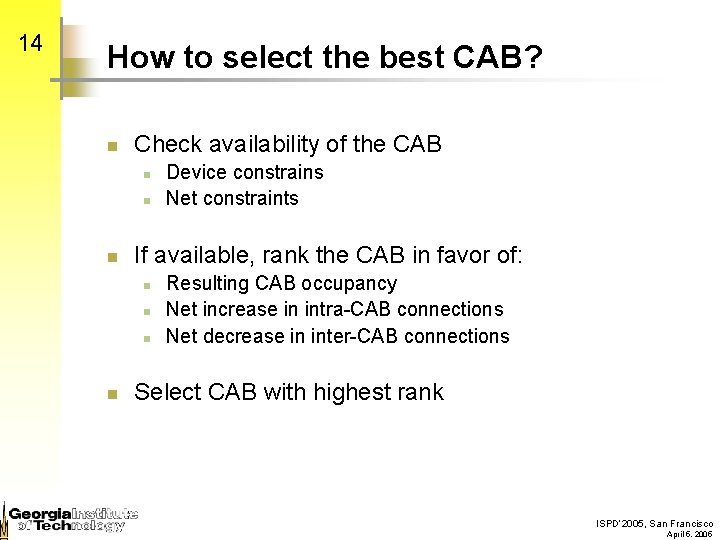

14 How to select the best CAB? n Check availability of the CAB n n n If available, rank the CAB in favor of: n n Device constrains Net constraints Resulting CAB occupancy Net increase in intra-CAB connections Net decrease in inter-CAB connections Select CAB with highest rank ISPD’ 2005, San Francisco April 5, 2005

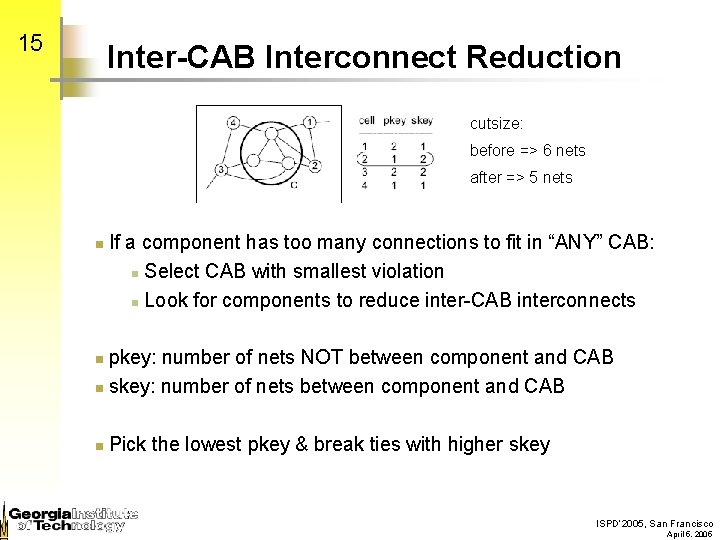

15 Inter-CAB Interconnect Reduction cutsize: before => 6 nets after => 5 nets n If a component has too many connections to fit in “ANY” CAB: n Select CAB with smallest violation n Look for components to reduce inter-CAB interconnects pkey: number of nets NOT between component and CAB n skey: number of nets between component and CAB n n Pick the lowest pkey & break ties with higher skey ISPD’ 2005, San Francisco April 5, 2005

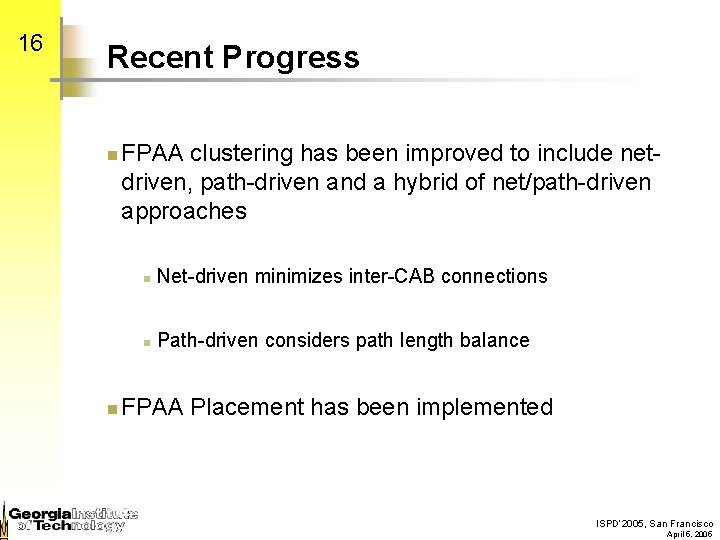

16 Recent Progress n n FPAA clustering has been improved to include netdriven, path-driven and a hybrid of net/path-driven approaches n Net-driven minimizes inter-CAB connections n Path-driven considers path length balance FPAA Placement has been implemented ISPD’ 2005, San Francisco April 5, 2005

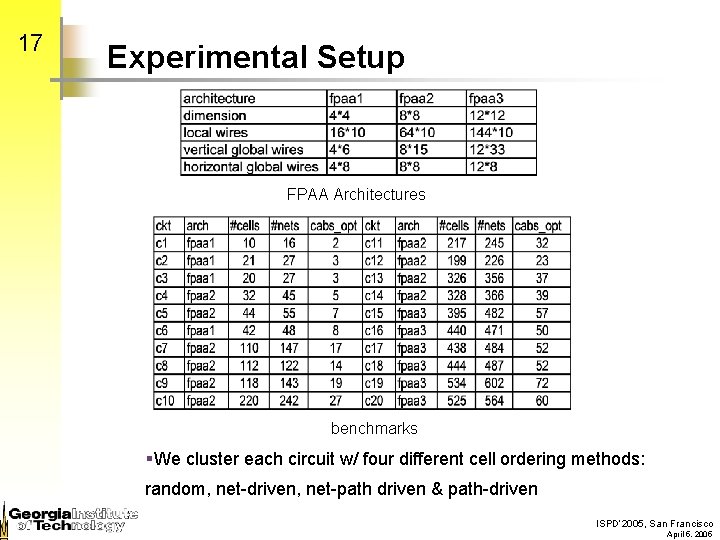

17 Experimental Setup FPAA Architectures benchmarks §We cluster each circuit w/ four different cell ordering methods: random, net-driven, net-path driven & path-driven ISPD’ 2005, San Francisco April 5, 2005

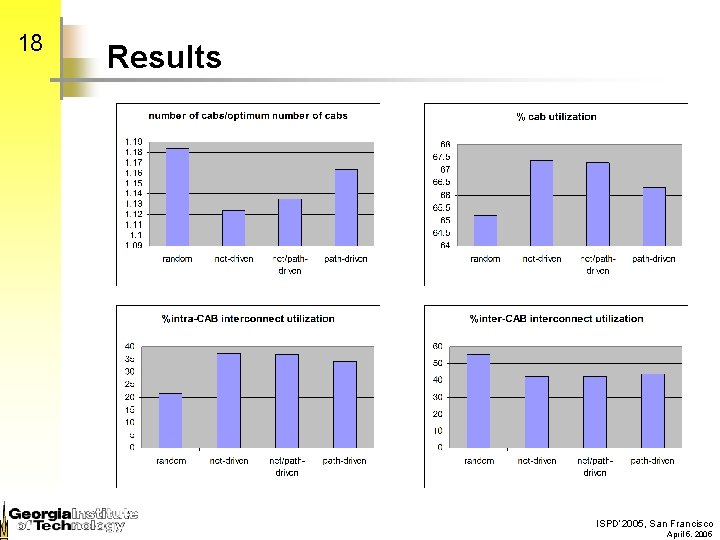

18 Results ISPD’ 2005, San Francisco April 5, 2005

19 Conclusion n We require low power reconfigurable analog devices for signal processing applications Floating gate based FPAA provides a large-scale solution We developed an algorithm for clustering targeting floating gate based FPAA ISPD’ 2005, San Francisco April 5, 2005

20 Future Work n Complete FPAA Physical Synthesis Tool including: n n n Clustering Placement Routing n Synthesize circuits => measurements n Elaborate FPAA switch vs wire analysis n Optimal FPAA Architecture Selection ISPD’ 2005, San Francisco April 5, 2005

21 Thank you ISPD’ 2005, San Francisco April 5, 2005

- Slides: 21