Manufacturing Testing Manufacturing Testing What is testing Apply

- Slides: 45

Manufacturing Testing

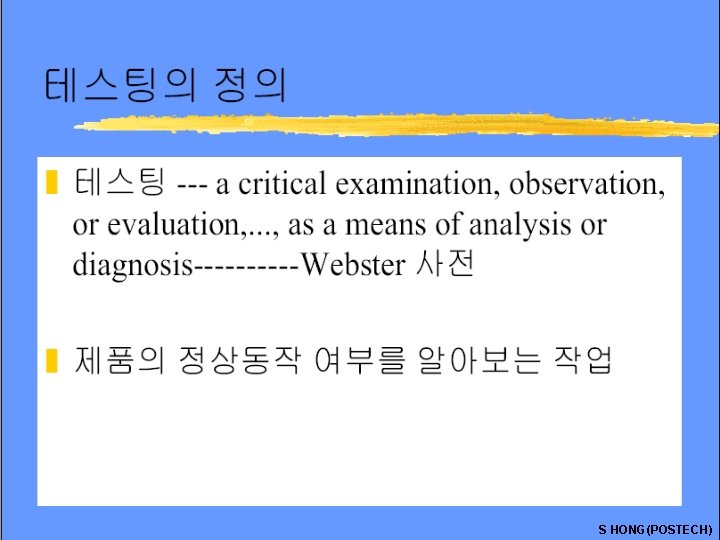

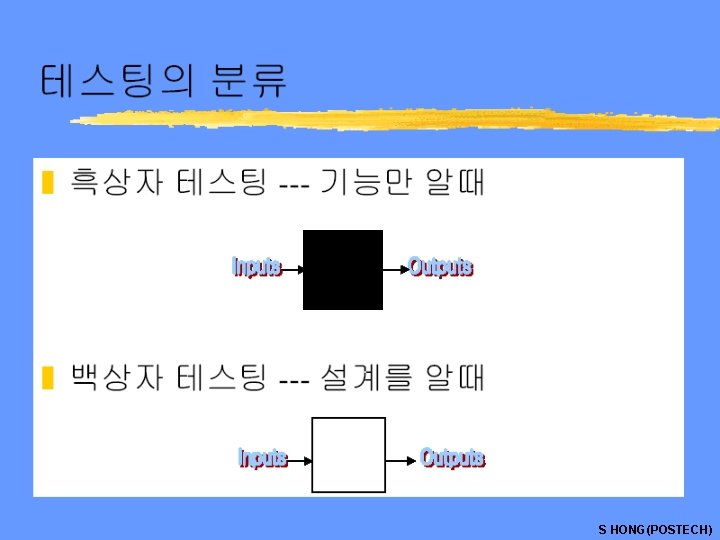

Manufacturing Testing • What is testing? – Apply the input stimuli, test vector, to DUT – Observe the response from DUT, and compare with expected results • How? – Fast and exact – Automation

S HONG(POSTECH)

S HONG(POSTECH)

S HONG(POSTECH)

S HONG(POSTECH)

S HONG(POSTECH)

S HONG(POSTECH)

S HONG(POSTECH)

S HONG(POSTECH)

S HONG(POSTECH)

S HONG(POSTECH)

S HONG(POSTECH)

S HONG(POSTECH)

S HONG(POSTECH)

S HONG(POSTECH)

S HONG(POSTECH)

S HONG(POSTECH)

S HONG(POSTECH)

S HONG(POSTECH)

S HONG(POSTECH)

S HONG(POSTECH)

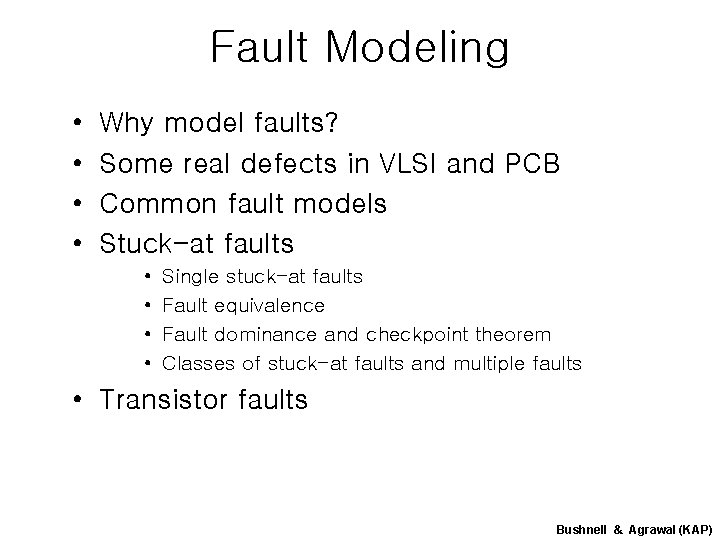

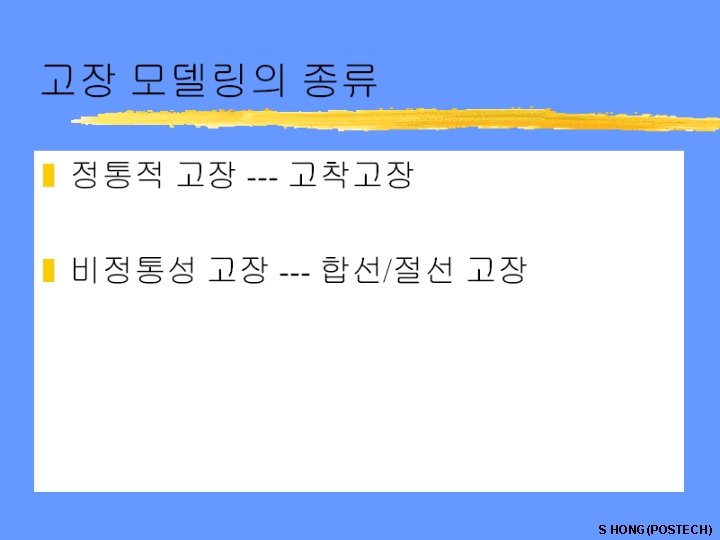

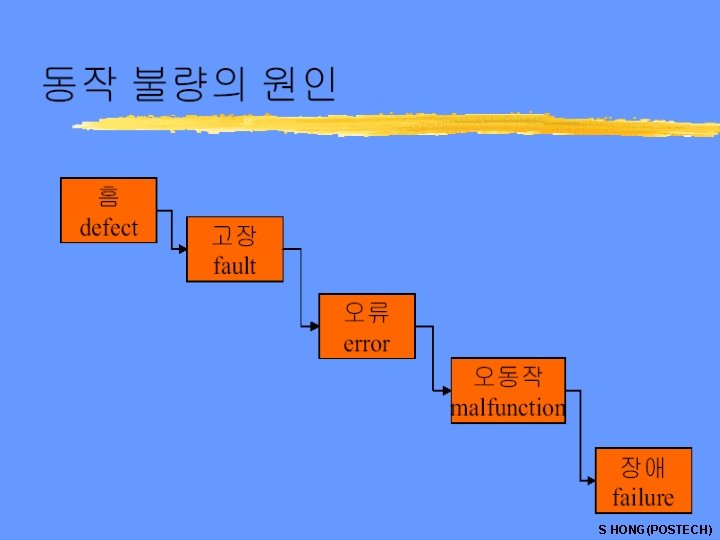

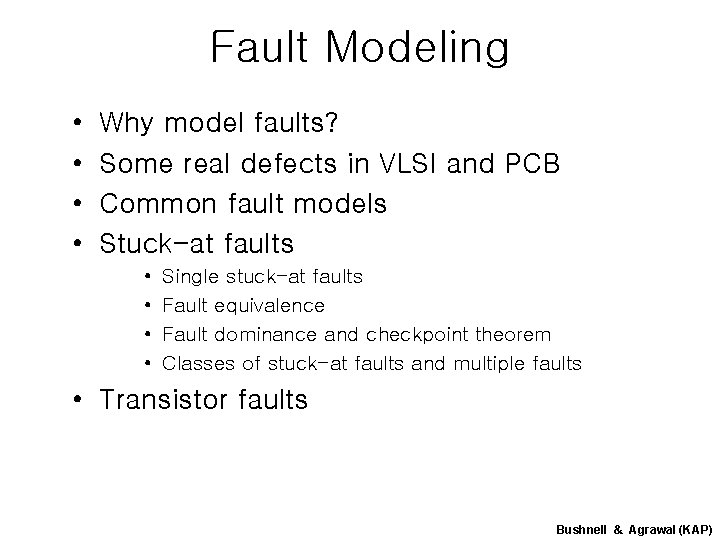

Fault Modeling • • Why model faults? Some real defects in VLSI and PCB Common fault models Stuck-at faults • • Single stuck-at faults Fault equivalence Fault dominance and checkpoint theorem Classes of stuck-at faults and multiple faults • Transistor faults Bushnell & Agrawal (KAP)

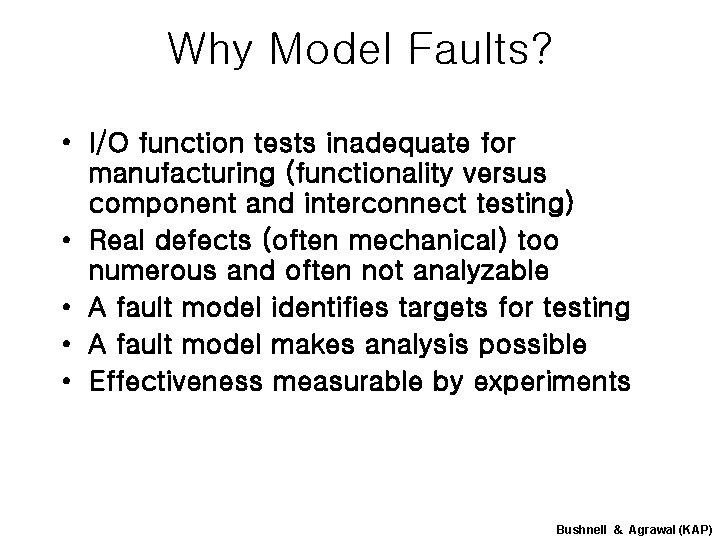

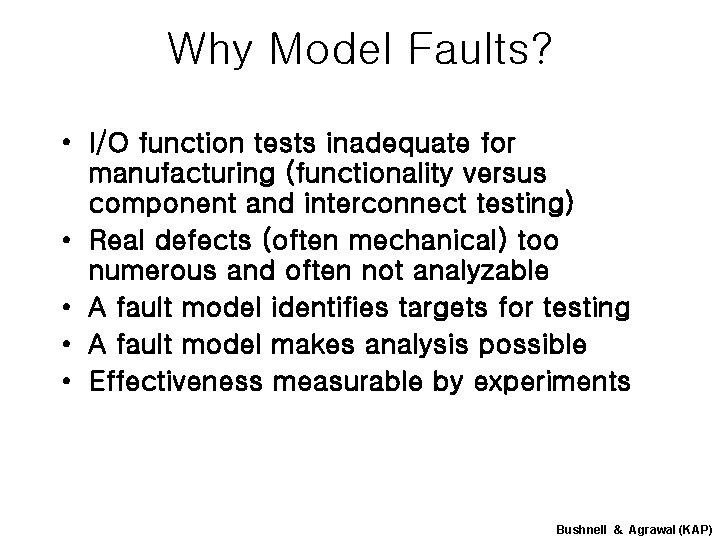

Why Model Faults? • I/O function tests inadequate for manufacturing (functionality versus component and interconnect testing) • Real defects (often mechanical) too numerous and often not analyzable • A fault model identifies targets for testing • A fault model makes analysis possible • Effectiveness measurable by experiments Bushnell & Agrawal (KAP)

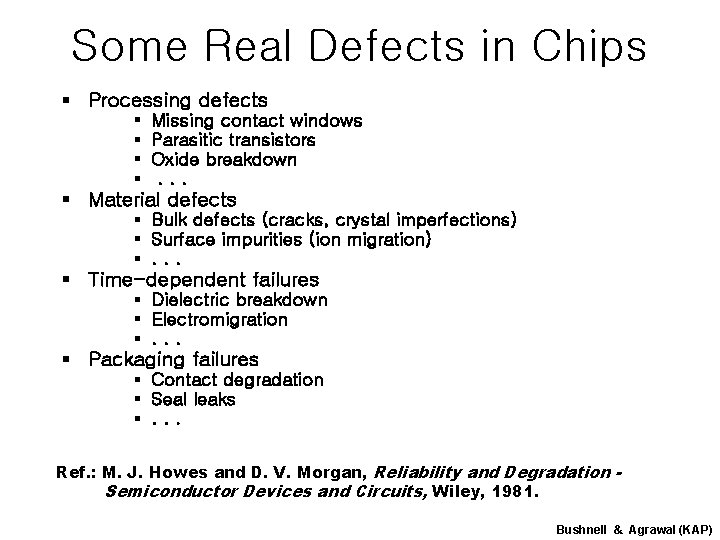

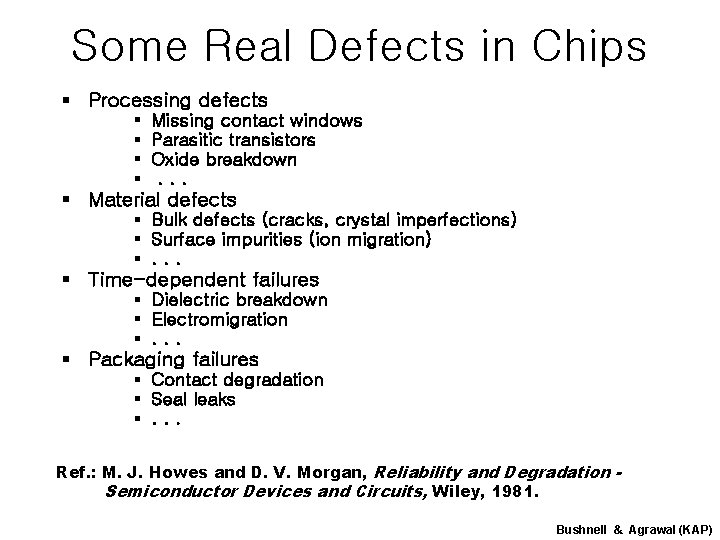

Some Real Defects in Chips § Processing defects § § Missing contact windows Parasitic transistors Oxide breakdown. . . § Material defects § Bulk defects (cracks, crystal imperfections) § Surface impurities (ion migration) §. . . § Time-dependent failures § Dielectric breakdown § Electromigration §. . . § Packaging failures § Contact degradation § Seal leaks §. . . Ref. : M. J. Howes and D. V. Morgan, Reliability and Degradation Semiconductor Devices and Circuits, Wiley, 1981. Bushnell & Agrawal (KAP)

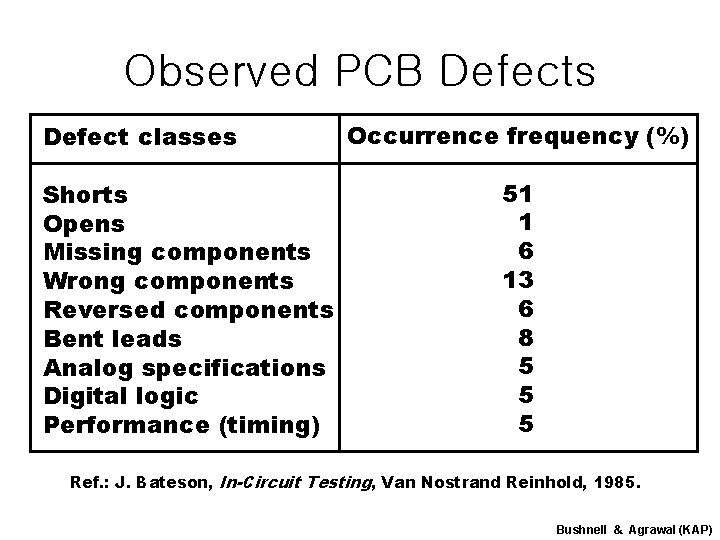

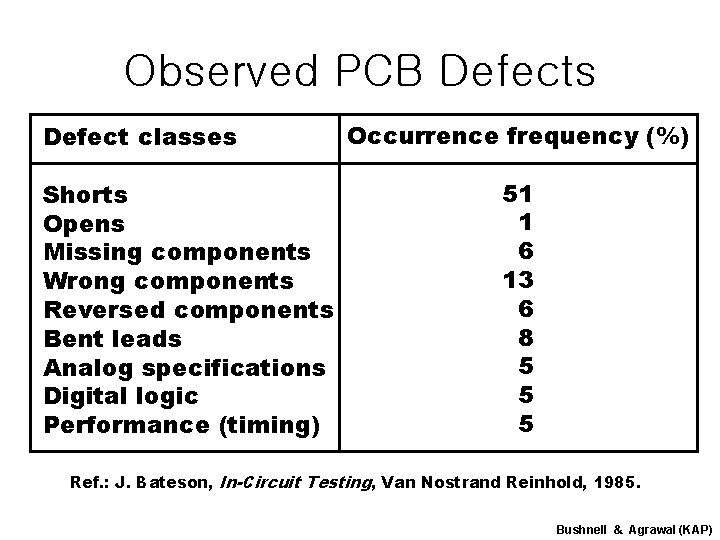

Observed PCB Defects Defect classes Shorts Opens Missing components Wrong components Reversed components Bent leads Analog specifications Digital logic Performance (timing) Occurrence frequency (%) 51 1 6 13 6 8 5 5 5 Ref. : J. Bateson, In-Circuit Testing, Van Nostrand Reinhold, 1985. Bushnell & Agrawal (KAP)

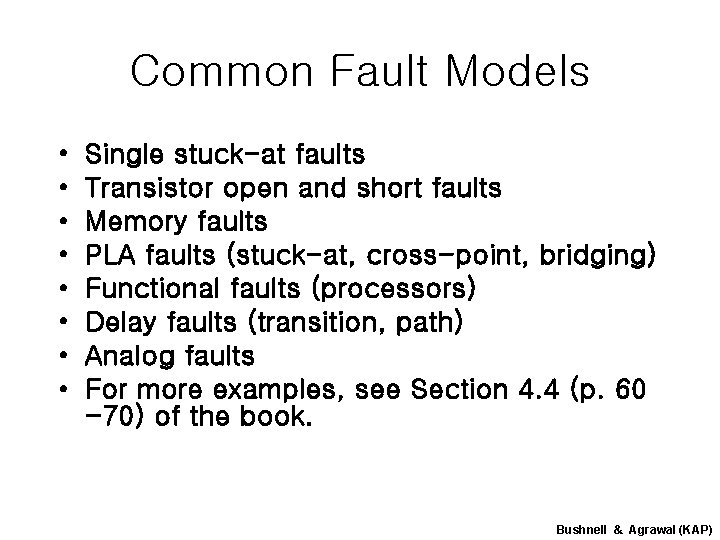

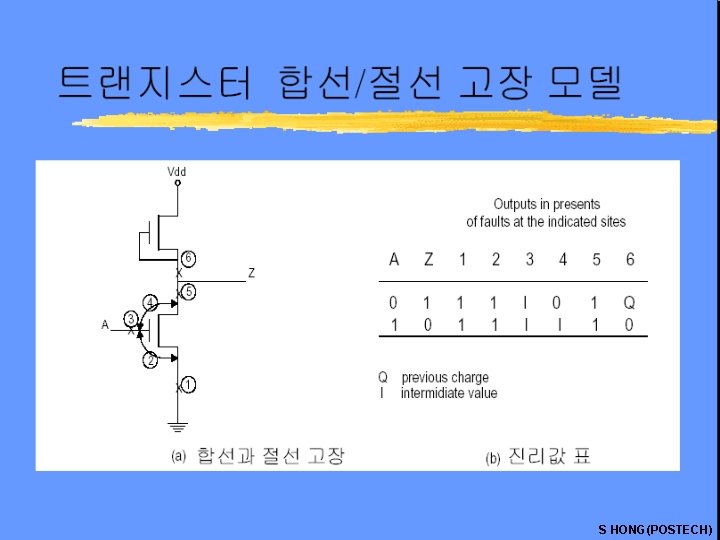

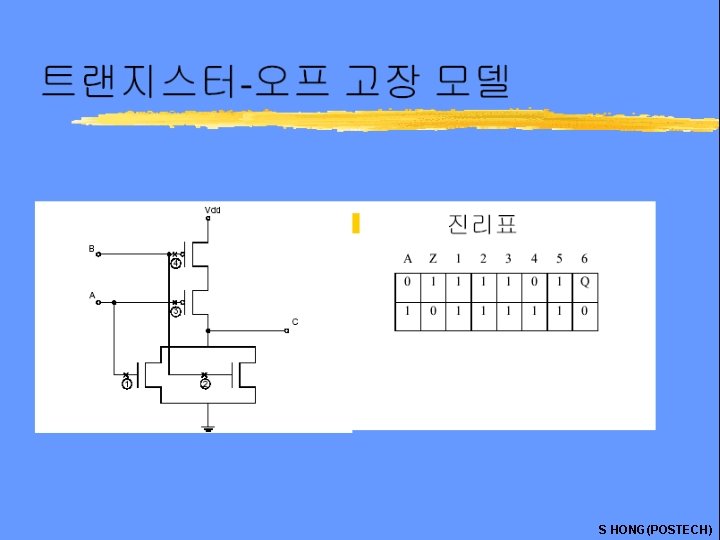

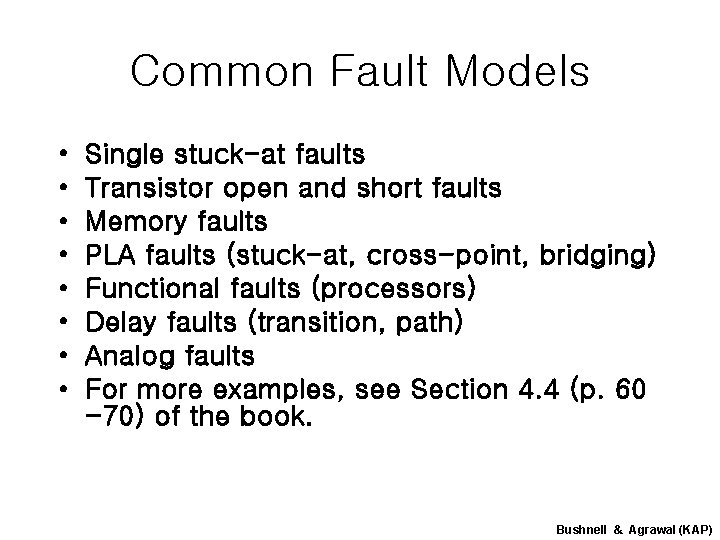

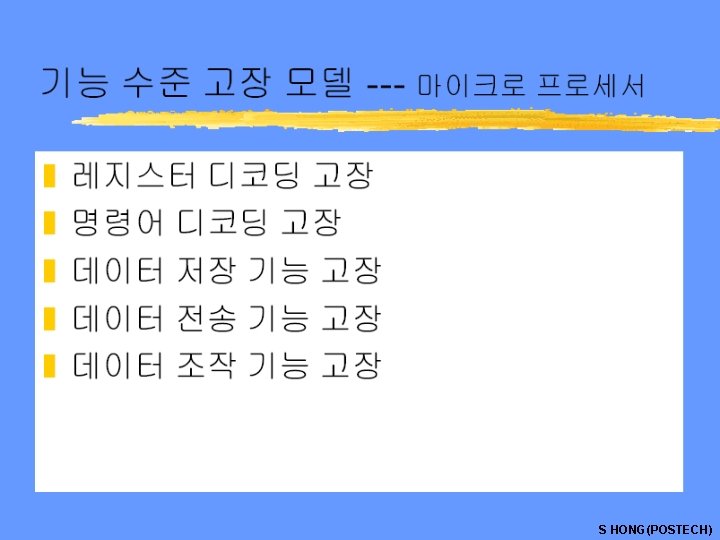

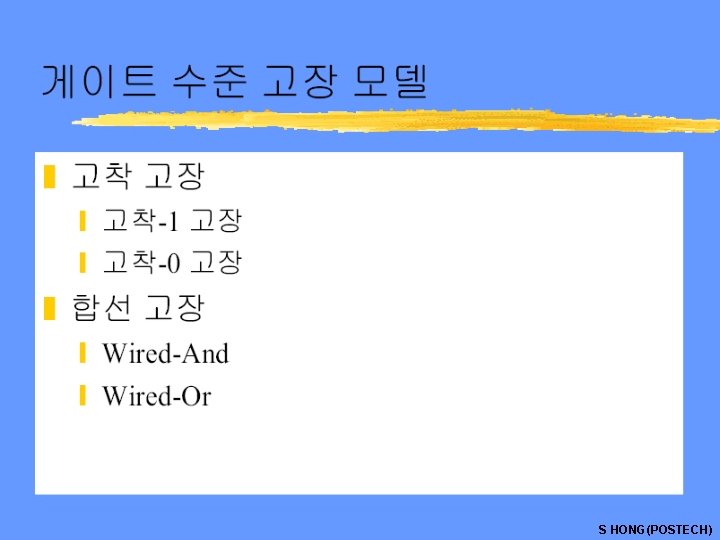

Common Fault Models • • Single stuck-at faults Transistor open and short faults Memory faults PLA faults (stuck-at, cross-point, bridging) Functional faults (processors) Delay faults (transition, path) Analog faults For more examples, see Section 4. 4 (p. 60 -70) of the book. Bushnell & Agrawal (KAP)

S HONG(POSTECH)

S HONG(POSTECH)

S HONG(POSTECH)

S HONG(POSTECH)

S HONG(POSTECH)

S HONG(POSTECH)

S HONG(POSTECH)

S HONG(POSTECH)

S HONG(POSTECH)

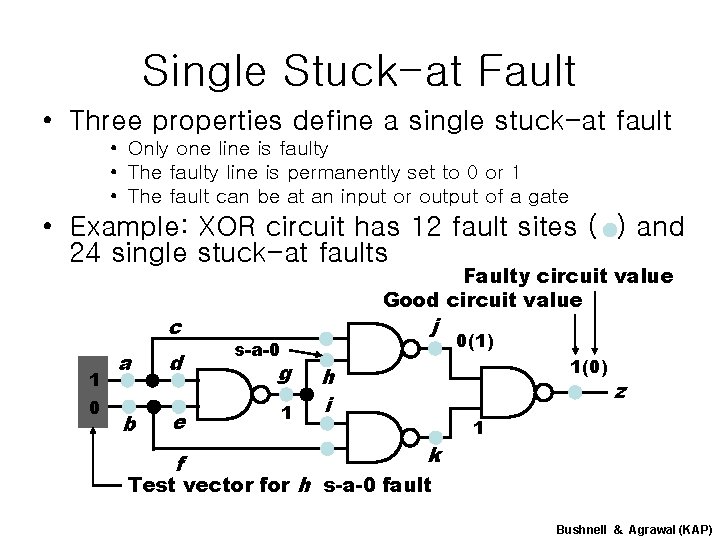

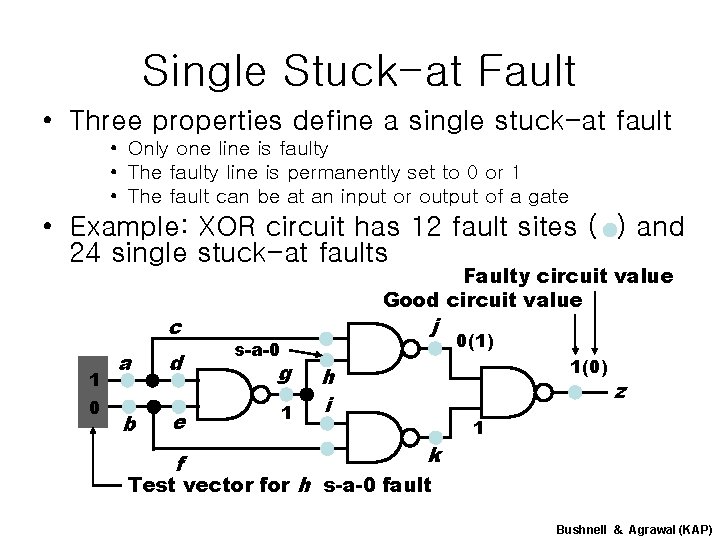

Single Stuck-at Fault • Three properties define a single stuck-at fault • Only one line is faulty • The faulty line is permanently set to 0 or 1 • The fault can be at an input or output of a gate • Example: XOR circuit has 12 fault sites ( ) and 24 single stuck-at faults c 1 0 a d b e f Faulty circuit value Good circuit value j s-a-0 g 1 0(1) 1(0) h i k z 1 Test vector for h s-a-0 fault Bushnell & Agrawal (KAP)

S HONG(POSTECH)

S HONG(POSTECH)

S HONG(POSTECH)

S HONG(POSTECH)

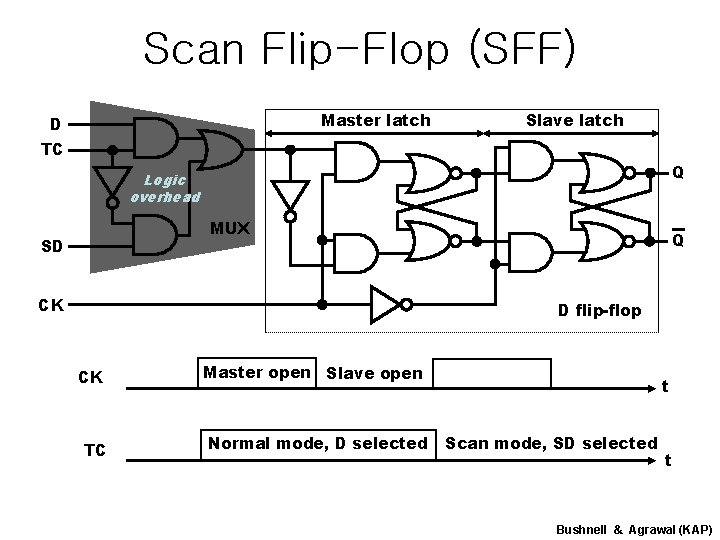

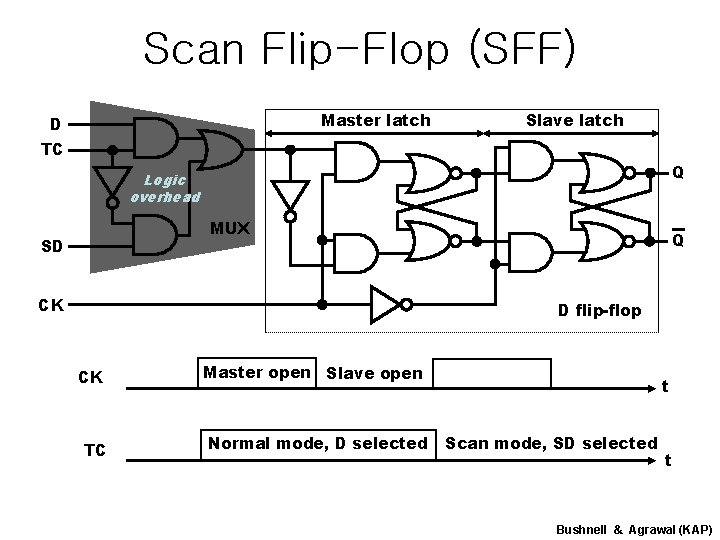

Scan Flip-Flop (SFF) Master latch D Slave latch TC Q Logic overhead MUX SD CK Q D flip-flop CK TC Master open Slave open Normal mode, D selected t Scan mode, SD selected t Bushnell & Agrawal (KAP)

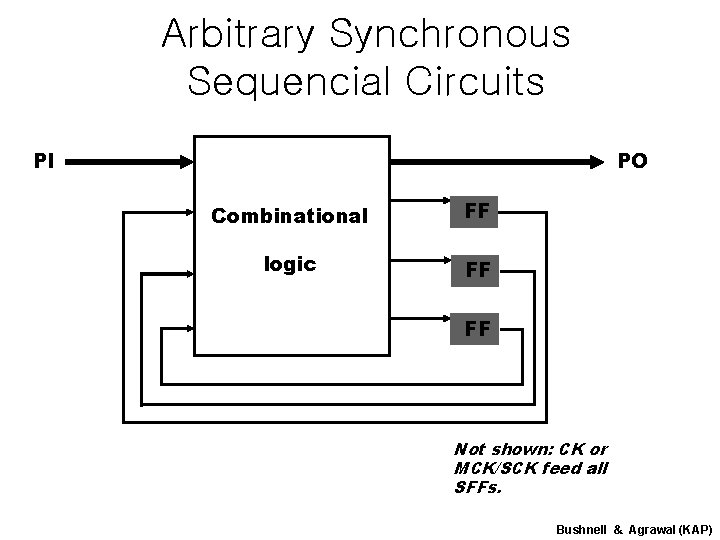

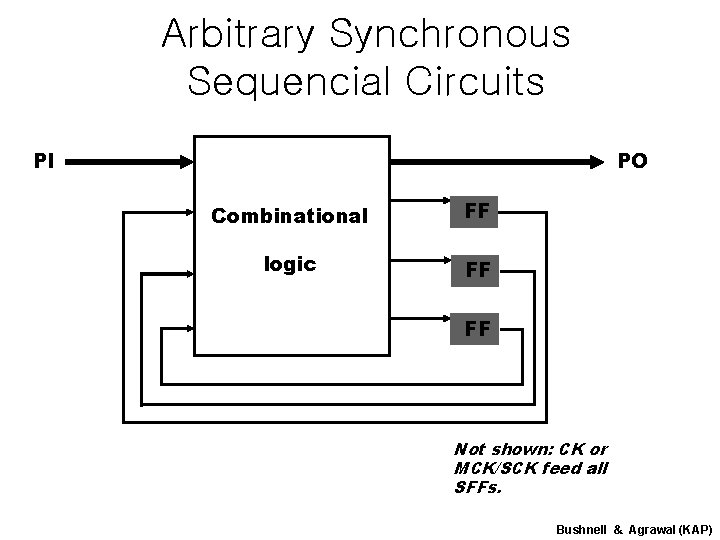

Arbitrary Synchronous Sequencial Circuits PI PO Combinational FF logic FF FF Not shown: CK or MCK/SCK feed all SFFs. Bushnell & Agrawal (KAP)

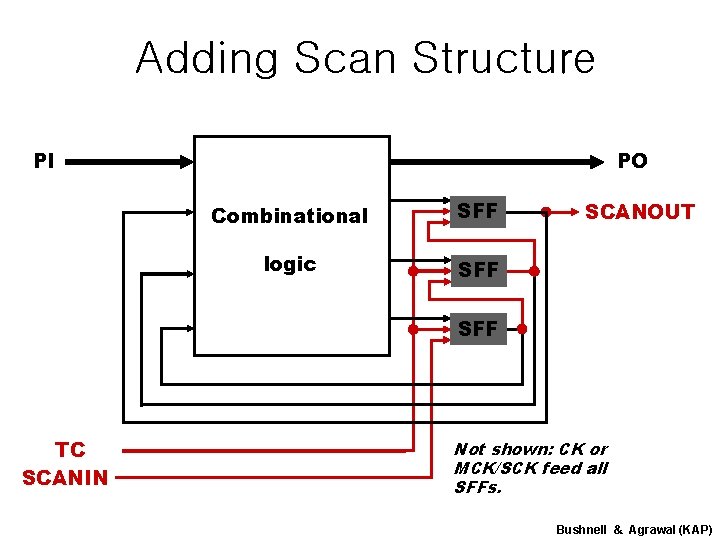

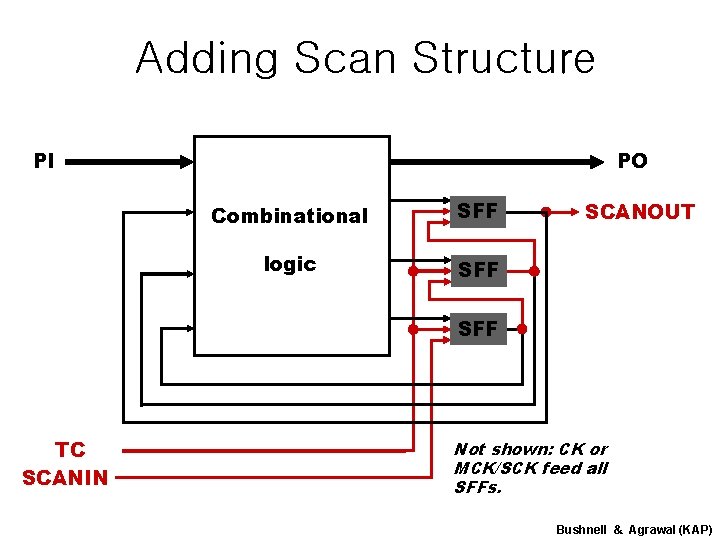

Adding Scan Structure PI PO Combinational SFF logic SFF SCANOUT SFF TC SCANIN Not shown: CK or MCK/SCK feed all SFFs. Bushnell & Agrawal (KAP)

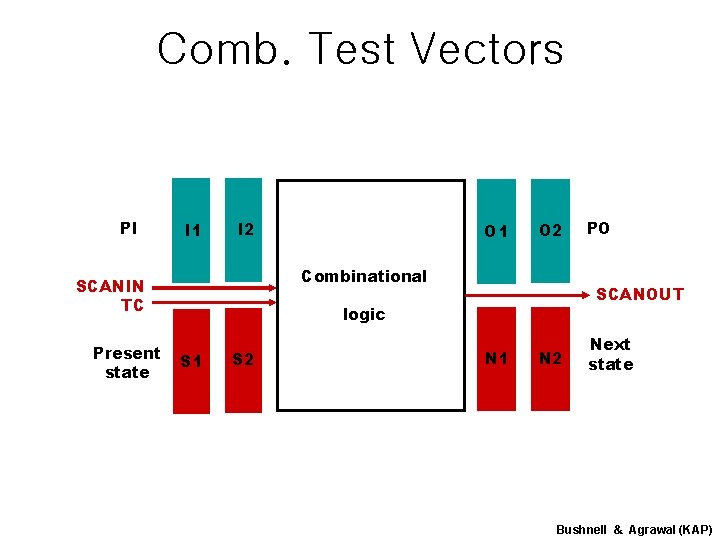

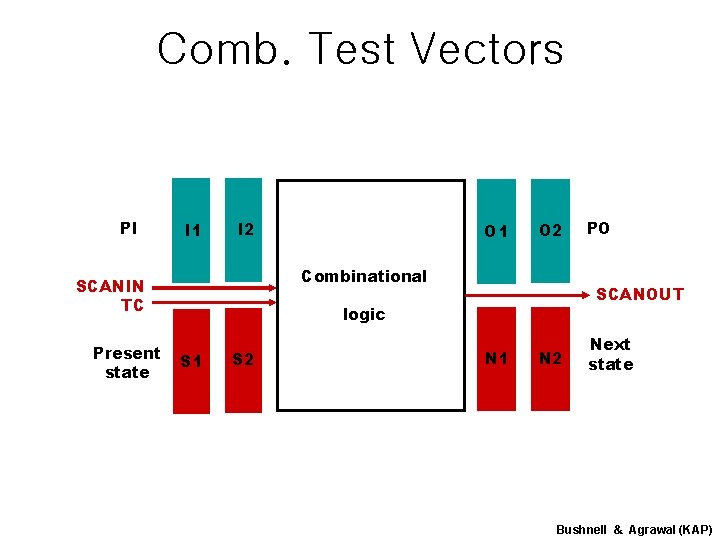

Comb. Test Vectors PI I 1 I 2 O 2 Combinational SCANIN TC Present state O 1 SCANOUT logic S 1 S 2 PO N 1 N 2 Next state Bushnell & Agrawal (KAP)