Making a Computer Binary number system Boolean functions

Making a Computer • • Binary number system → Boolean functions → Combinational circuits → Sequential circuits Sequential/Combinational circuits → Functional units • Functional units → Computer architecture CSC 321

Defining a Computer • Computer Architecture – Bus – Register transfer language – Microoperations – Instruction set – Timing and control CSC 321

Instruction Set • Instruction (Assembly language statement) – Binary code – Consists of an operation code and operand(s) – Specifies a sequence of microoperations to be executed • One high level language (e. g. C++/Java) statement specifies a sequence of instructions – Stored in memory – Note that we are talking about a level higher than RTL but lower than Java, C++, etc. CSC 321

Exercise • Start Visual Studio. NET • Select “New Project” – Visual C++ Projects • Win 32 Console Application – Type in a project name (e. g. Assembly. Example) – Browse to a directory (e. g. Desktop) – Press “OK” – Press “Finish” CSC 321

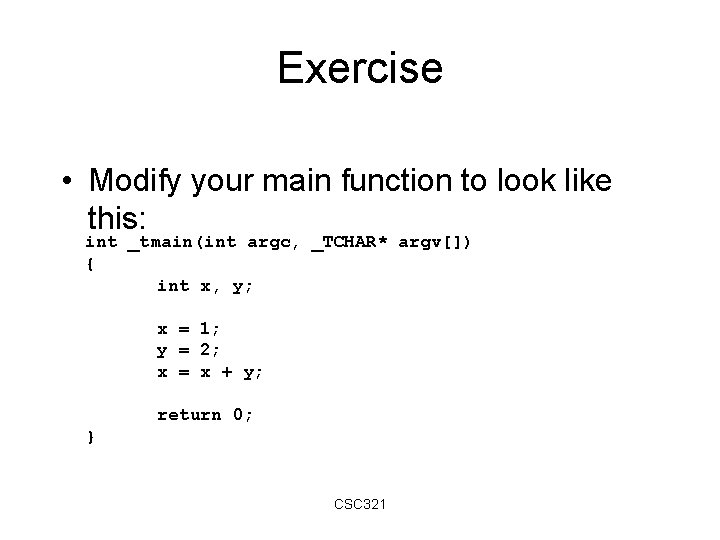

Exercise • Modify your main function to look like this: int _tmain(int argc, _TCHAR* argv[]) { int x, y; x = 1; y = 2; x = x + y; return 0; } CSC 321

Exercise • Set a break-point on the “int x, y; ” line by clicking on that line and pressing F 9 – A red circle should appear to the left of the line • Run the program by pressing F 5 and answering “yes” to the question • Open the Debug menu – Select Windows → Disassembly – Select Windows → Registers CSC 321

Exercise • In the Watch 1 window (lower left) select an empty line (turns blue) and type &x • In the Watch 1 window (lower left) select an empty line (turns blue) and type &y • In the Memory 1 window (select tab) enter the smaller of the two hexadecimal numbers next to the &x and &y into the Address field • If you want to see the binary (hex) codes for the instructions type an instruction address (next to an assembly language instruction) into the Memory 1 window’s address field – Notice that instructions are of varying lengths CSC 321

Exercise • Note the value of the EIP register in the Registers window – it matches the value next to the yellow arrow at the left of the assembly code • Press F 10 and watch the Memory 1 window • Press F 10 again and watch the EAX register • Press F 10 again and watch the Memory 1 window CSC 321

Exercise • What you witnessed was the modification of Pentium processor registers and memory as it executed individual assembly language instructions • Note that the Pentium assembly language is extremely complex as it is a powerful processor • If you want to learn more, manuals can be downloaded from http: //developer. intel. com/design/pentium 4/manuals/253665. ht m CSC 321

Basic Computer • The following discussions are based on a fictitious computer called “Basic Computer” by the author of the textbook • It’s a much better way to learn computer architecture concepts than trying to understand the Intel Pentium architecture

Assembly Language • Every computer architecture (or family of architectures) has its own unique assembly language • Unlike Java, you should not learn assembly language syntax, data types, etc. • You should learn to program/think at the assembly language level – It’s a way of thinking that requires intimate knowledge of the underlying hardware architecture

Assembly Language Instructions • Each instruction has two basic parts – Operation code (opcode) • What the instruction wants the processor to do – Operand(s) (registers, memory addresses) • Data location that the instruction wants the processor to manipulated • Some operands will be explicit while others will be implicit (implied by the opcode)

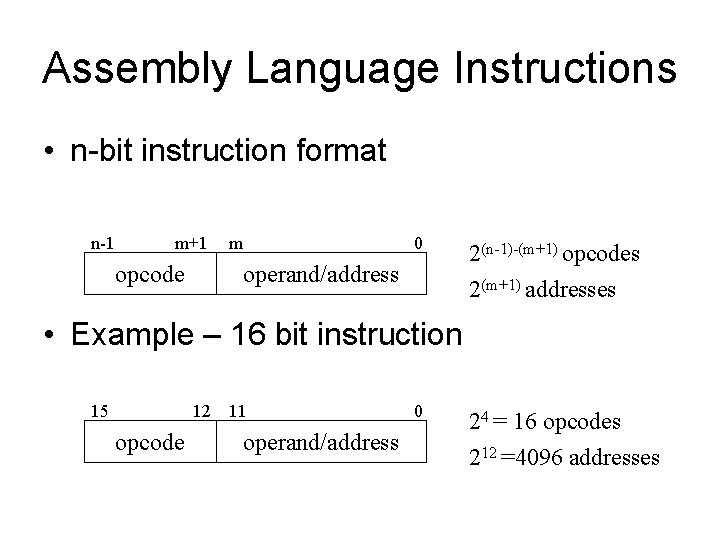

Assembly Language Instructions • n-bit instruction format n-1 m+1 opcode m 0 operand/address 2(n-1)-(m+1) opcodes 2(m+1) addresses • Example – 16 bit instruction 15 12 opcode 11 operand/address 0 24 = 16 opcodes 212 =4096 addresses

Assembly Language Instructions • Instructions within the same Assembly language may be of differing lengths – i. e. not all instructions utilize the same number of bits as we saw with the Pentium

Internal Operation • To execute an assembly language instruction the processor goes through 4 steps – – Fetch an instruction from memory Decode the instruction Read the operands from memory/registers Execute the instruction • This is often referred to as the Fetch-Execute cycle or the Instruction cycle • To execute a program the processor repeats this cycle until a halt instruction is reached

Internal Operation • All this is under the control of the Control Unit • This is the component that decodes the instruction and sends out microoperations to the rest of the hardware – The control unit can be hardwired • Made up entirely of sequential circuits designed to do precisely the fetch-execute steps – fixed instruction set – The control unit can be microprogrammed • A small programmable processor within the processor – programmable instruction set • More on this later

Addressing Modes • In designing a computer architecture the designer must specify the instruction set – Opcode/operand pairs • In specifying operands there a number of alternatives – Immediate instructions – Direct address operands – Indirect address operands

Immediate Instruction • The 2 nd part of the instruction is the operand (rather than the address of the operand) • An example might be an instruction that adds a constant to a register add 3 – The “ 3” is the value we want to add, not an address in memory

Direct Address Instruction • The 2 nd part of the instruction is the memory address of operand • An example might be an instruction that adds a value in memory to a register add 0 x 30213 – The “ 0 x 30213” is the memory address of the value that we want to add

Indirect Address Instruction • The 2 nd part of the instruction is the memory address of the location that holds the memory address of the operand • An example might be an instruction that adds a value in memory to a register add 0 x 30213 – The “ 0 x 30213” is a memory address that holds the memory address of the value that we want to add

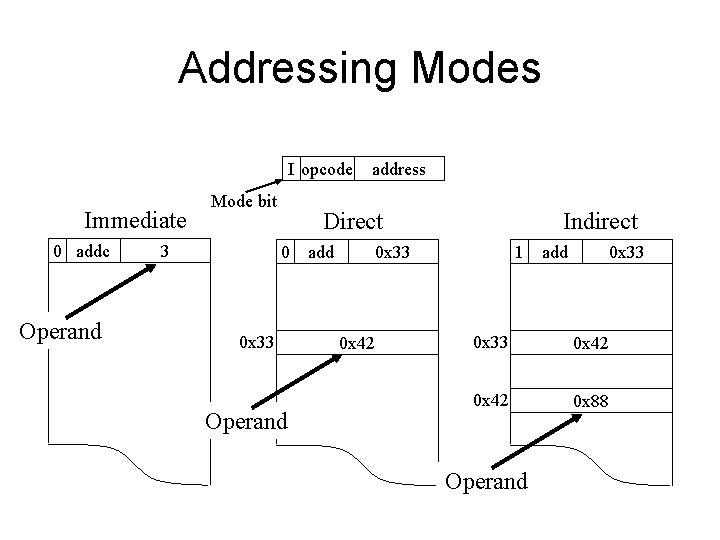

Addressing Modes I opcode Immediate 0 addc Operand Mode bit 3 address Direct 0 0 x 33 Operand add Indirect 0 x 33 0 x 42 1 add 0 x 33 0 x 42 0 x 88 Operand

Addressing Modes • The term effective address refers to the actual address of the operand – For the previous example • Immediate address mode – Effective address is the instruction itself • Direct address mode – Effective address is the memory location 0 x 33 • Indirect addressing mode – Effective address is the memory location 0 x 42

Addressing Modes • Something in the instruction word will specify which addressing mode is applicable – The operand itself (for immediate instructions) – A designated bit (for direct vs. indirect address instructions)

Addressing Modes • Indirect addressing is a convenient way to implement arrays (which are nothing more than pointers to blocks of contiguous memory) • Some architectures define additional modes such as “read location then increment” – These are all derivations of the three defined here

Registers • In designing a computer architecture the designer must specify the register set • There are essentially two categories – Special purpose registers – General purpose registers

Special Purpose Registers • Program Counter (PC) – Holds the memory address of the next instruction of our program • Memory Address Register (AR) – Holds the address of a location in memory that we want to access (read/write) • The size of (number of bits in) these two registers is determined by the number of memory addresses in our architecture

Special Purpose Registers • Instruction Register (IR) – Holds the instruction (opcode/operand) we are about to execute • Data Register (DR) – Holds the operand read from memory to be sent to the ALU • Accumulator (AC) – Holds an input to the ALU and the output from the ALU

Special Purpose Registers • Input Register (INPR) – Holds data received from a specified external device • Output Register (OUTR) – Holds data to be sent to a specified external device

General Purpose Registers • Temporary Register (TR) – For general usage either by our program or the architecture

Registers • These registers (shown previously) are specified for the fictitious architecture given in the textbook • All architectures will have these in some form • Most architectures will have more than just these – – – – More general purpose registers Stack pointers Interrupts Program status bits Multiple I/O ports Timers etc. • To effectively program the architecture (in assembly language) you need to be aware of all the available registers and their usage • High level language compilers possess this knowledge

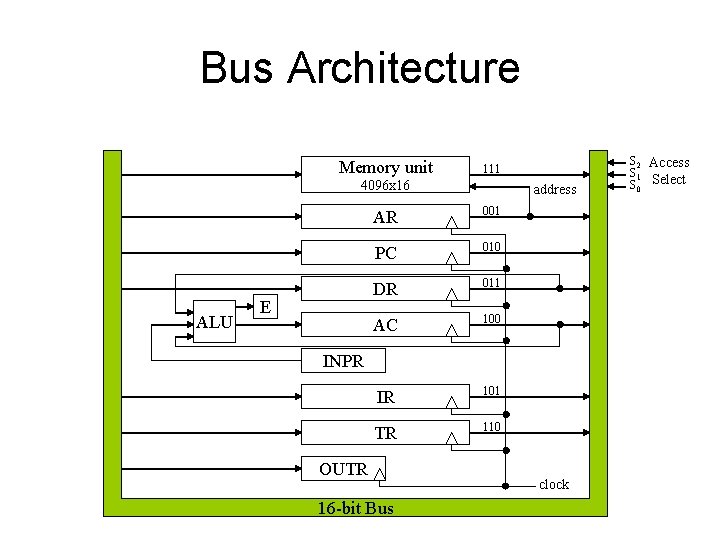

Bus • In designing a computer architecture the designer must specify the bus layout – The size of the bus (in bits) – What is connected to the bus – Access control to the bus • Recall that a bus is an efficient alternative to lots of wires when it comes to transferring data between registers, control units, and memory locations

Bus Architecture Memory unit 111 4096 x 16 ALU E address AR 001 PC 010 DR 011 AC 100 IR 101 TR 110 INPR OUTR 16 -bit Bus clock S 2 Access S 1 S 0 Select

- Slides: 32