Major Advances in Computers1 The family concept IBM

Major Advances in Computers(1) • The family concept – IBM System/360 1964 – DEC PDP-8 – Separates architecture from implementation • Microporgrammed control unit – Idea by Wilkes 1951 – Produced by IBM S/360 1964 • Cache memory – IBM S/360 model 85 1969

Major Advances in Computers(2) • Pipelining – Introduces parallelism into fetch execute cycle • Multiple processors

The Next Step - RISC • Reduced Instruction Set Computer • Key features – Large number of general purpose registers – or use of compiler technology to optimize register use – Limited and simple instruction set – Emphasis on optimising the instruction pipeline

Driving force for CISC • • Software costs far exceed hardware costs Increasingly complex high level languages Semantic gap Leads to: – Large instruction sets – More addressing modes – Hardware implementations of HLL statements • e. g. CASE (switch) on VAX

Intention of CISC • Ease compiler writing • Improve execution efficiency – Complex operations in microcode • Support more complex HLLs

CISC Characteristics A large no of instructions A large variety of addressing modes Variable length instruction formats Instructions that manipulate operands in memory • Some instructions that perform specialized tasks and are used infrequently • •

• Faster programs – More complex control unit – Microprogram control • Ease of writing programs

RISC Characteristics • • Few instructions Register to register operations Few, simple addressing modes Few, simple instruction formats Hardwired design (no microcode) Fixed instruction format One instruction per clock cycle More compile time/effort

• Large no. of CPU registers • Use of overlapped register windows • Efficient instruction pipeline

RISC v CISC • Not clear cut • Many designs borrow from both philosophies • e. g. Power. PC and Pentium II

Overlapped Register Windows – Procedure Calls • When a procedure is called – Save register values – Pass parameters – Execute the procedure – Restore the register values – Pass results to the calling programs • All these are time consuming operations

• Some computers provide register banks • Each procedure is allocated its own bank of registers – Eliminates the need for saving and restoring register values • Each procedure call results in the activation of a new window consisting of a set of registers for use by the new procedure • Each procedure call activates a new register window by incrementing a pointer and the return statement decrements the pointer activating the previous window • Only one register window is activated at any given time.

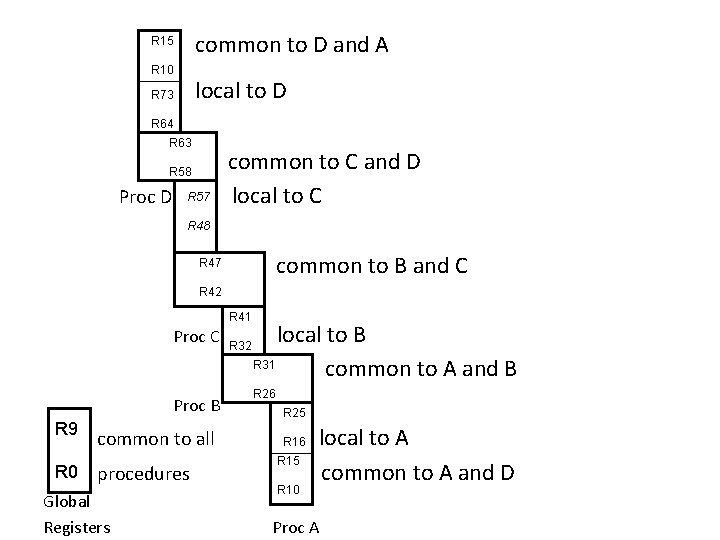

common to D and A R 15 R 10 local to D R 73 R 64 R 63 R 58 Proc D R 57 common to C and D local to C R 48 common to B and C R 47 R 42 R 41 Proc C Proc B R 9 common to all R 0 procedures Global Registers R 32 local to B R 31 common to A and B R 26 R 25 R 16 R 15 R 10 local to A common to A and D Proc A

• In general the organization of register window will have the following relationships • No. of global registers = G • No. of local registers in each window = L • No. of registers common to two windows = C • No. of windows = W • No. of registers available for each window = window size = L + 2 C + G • Total no of registers needed in the procedure is register file = (L+C)W +G G = 10, L = 10, C = 6 and W = 4 The window size is 32 registers Register file = 74 registers

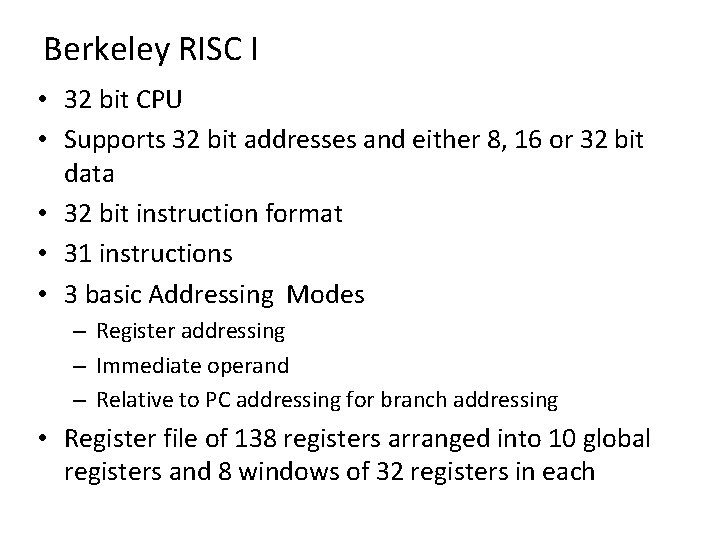

Berkeley RISC I • 32 bit CPU • Supports 32 bit addresses and either 8, 16 or 32 bit data • 32 bit instruction format • 31 instructions • 3 basic Addressing Modes – Register addressing – Immediate operand – Relative to PC addressing for branch addressing • Register file of 138 registers arranged into 10 global registers and 8 windows of 32 registers in each

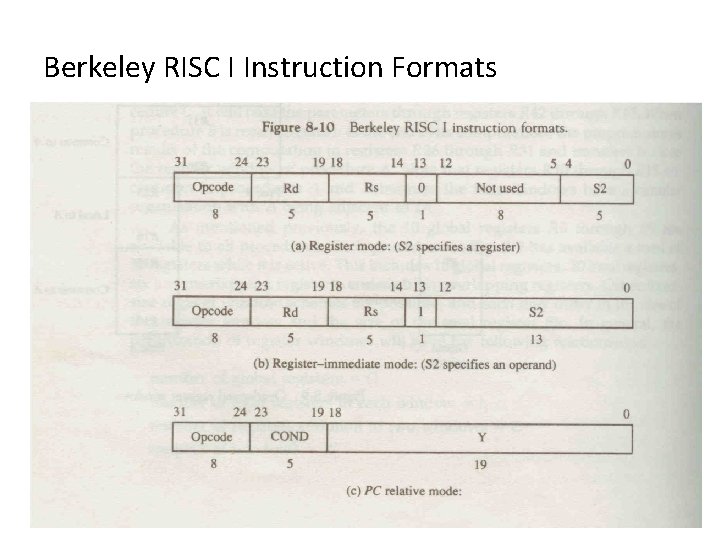

Berkeley RISC I Instruction Formats

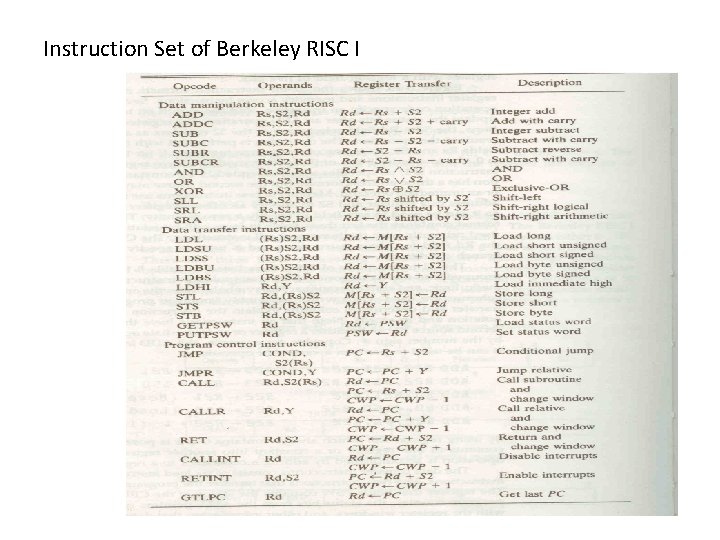

Instruction Set of Berkeley RISC I

- Slides: 17