Main Memory cslabntua 2017 2018 1 Memory Systems

Κύρια Μνήμη (Main Memory) cslab@ntua 2017 -2018 1

Πηγές/Βιβλιογραφία • “Memory Systems: Cache, DRAM, Disk”, Bruce Jacob, Spencer W. Ng, David T. Wang, Morgan Kaufmann Publishers, 2008 • Onur Mutlu, “Main Memory & DRAM Fundamentals”, Computer Architecture Lecture 4 – ETH, 2017 (slides & video) – https: //safari. ethz. ch/architecture/fall 2017/lib/exe/fetch. php? media=onur-comparchfall 2017 -lecture 4 -mainmemoryanddramfundamentals-afterlecture. pdf – https: //www. youtube. com/watch? v=s. Zj. SBFce. V_o cslab@ntua 2017 -2018 2

Η μνήμη για τον προγραμματιστή LOAD MEMORY STORE cslab@ntua 2017 -2018 3

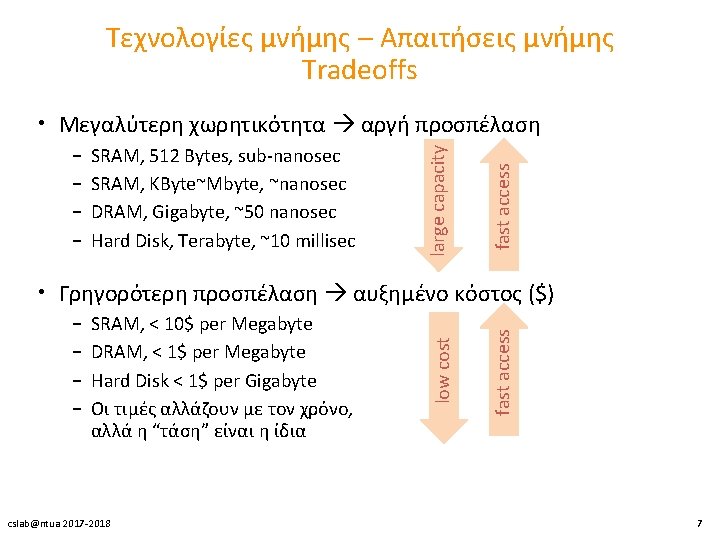

Τεχνολογίες μνήμης – Aπαιτήσεις μνήμης Tradeoffs SRAM, 512 Bytes, sub-nanosec SRAM, KByte~Mbyte, ~nanosec DRAM, Gigabyte, ~50 nanosec Hard Disk, Terabyte, ~10 millisec fast access – – large capacity • Μεγαλύτερη χωρητικότητα αργή προσπέλαση SRAM, < 10$ per Megabyte DRAM, < 1$ per Megabyte Hard Disk < 1$ per Gigabyte Οι τιμές αλλάζουν με τον χρόνο, αλλά η “τάση” είναι η ίδια cslab@ntua 2017 -2018 fast access – – low cost • Γρηγορότερη προσπέλαση αυξημένο κόστος ($) 7

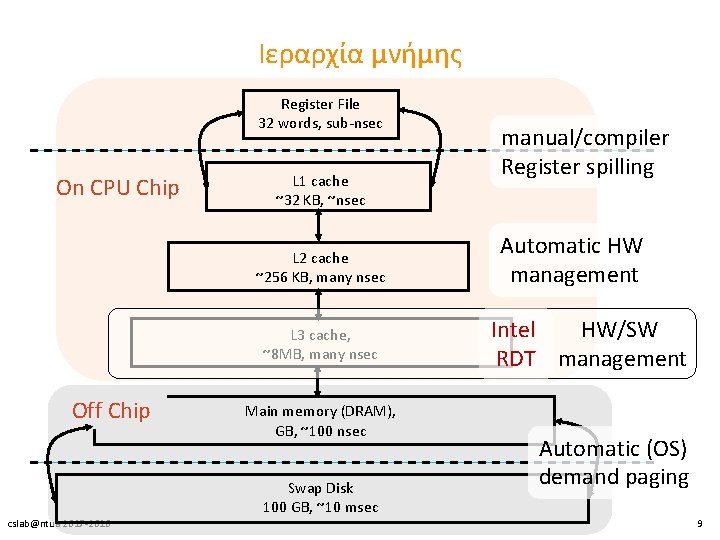

Ιεραρχία μνήμης Register File 32 words, sub-nsec On CPU Chip L 1 cache ~32 KB, ~nsec L 2 cache ~256 KB, many nsec L 3 cache, ~8 MB, many nsec Off Chip cslab@ntua 2017 -2018 Main memory (DRAM), GB, ~100 nsec Swap Disk 100 GB, ~10 msec manual/compiler Register spilling Automatic HW management HW/SW Intel RDT management Automatic (OS) demand paging 9

![H μνήμη σε ένα σύγχρονο σύστημα Intel Broadwell-E Core i 7 [2016] cslab@ntua 2017 H μνήμη σε ένα σύγχρονο σύστημα Intel Broadwell-E Core i 7 [2016] cslab@ntua 2017](http://slidetodoc.com/presentation_image_h2/654771f360f6442bfe018bd9fd192c2a/image-10.jpg)

H μνήμη σε ένα σύγχρονο σύστημα Intel Broadwell-E Core i 7 [2016] cslab@ntua 2017 -2018 10

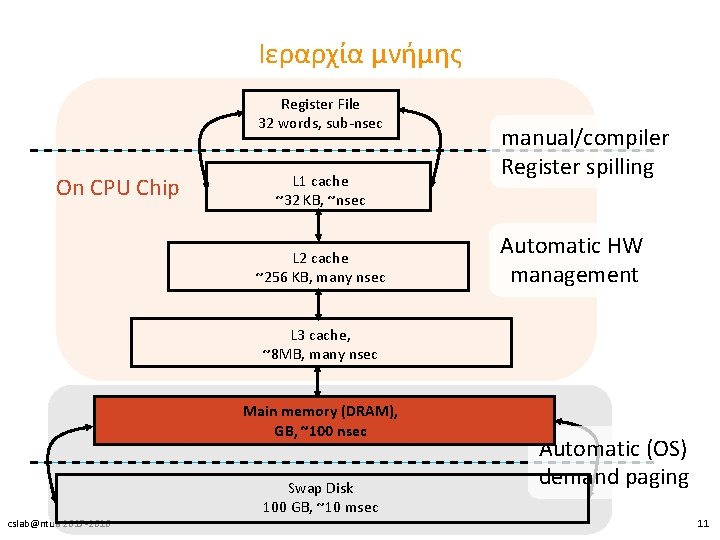

Ιεραρχία μνήμης Register File 32 words, sub-nsec On CPU Chip L 1 cache ~32 KB, ~nsec L 2 cache ~256 KB, many nsec manual/compiler Register spilling Automatic HW management L 3 cache, ~8 MB, many nsec Main memory (DRAM), GB, ~100 nsec cslab@ntua 2017 -2018 Swap Disk 100 GB, ~10 msec Automatic (OS) demand paging 11

Επίδοση cslab@ntua 2017 -2018 15

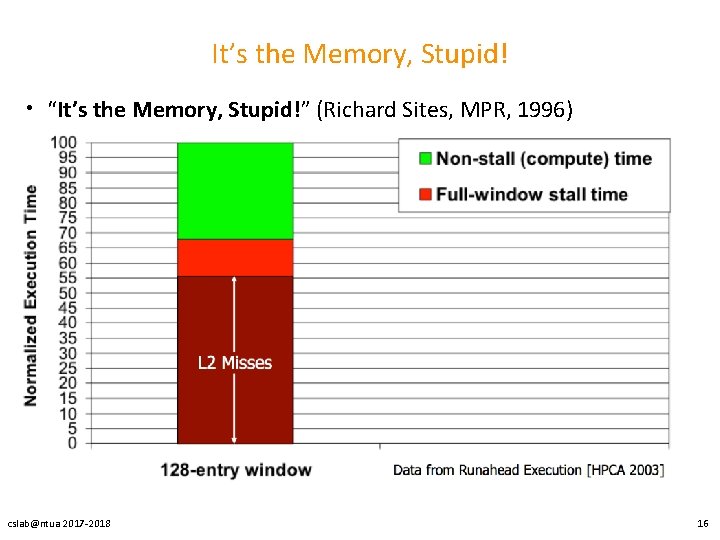

It’s the Memory, Stupid! • “It’s the Memory, Stupid!” (Richard Sites, MPR, 1996) cslab@ntua 2017 -2018 16

Ενέργεια cslab@ntua 2017 -2018 17

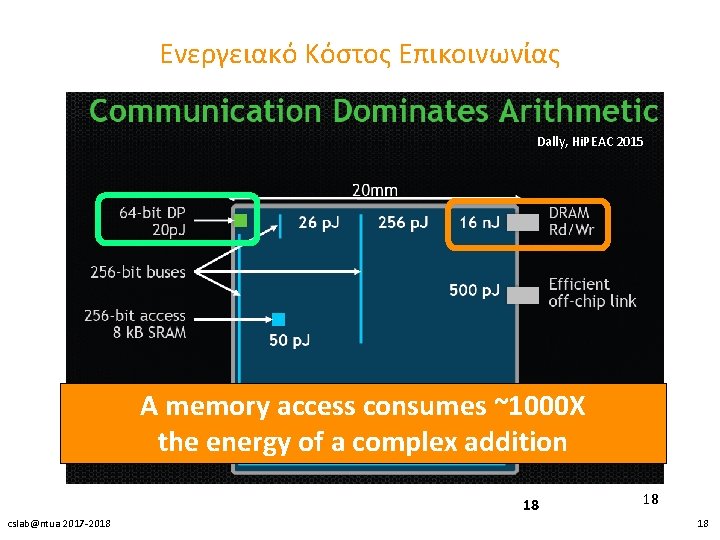

Ενεργειακό Κόστος Επικοινωνίας Dally, Hi. PEAC 2015 A memory access consumes ~1000 X the energy of a complex addition 18 cslab@ntua 2017 -2018 18 18

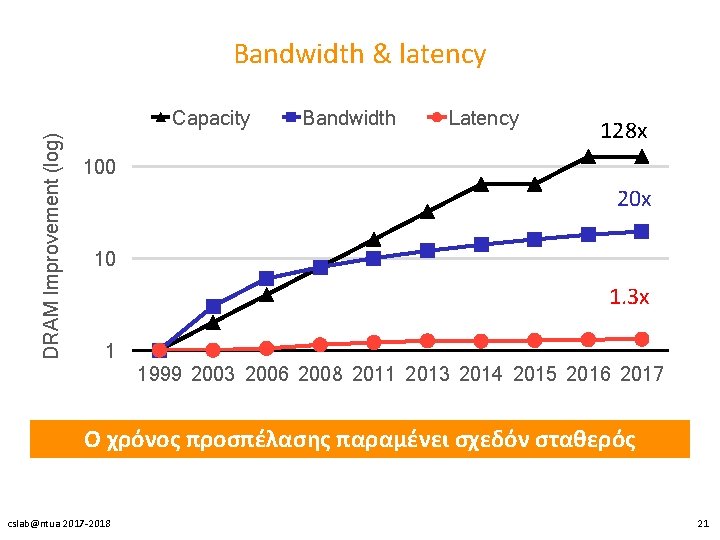

Bandwidth & latency DRAM Improvement (log) Capacity Bandwidth Latency 128 x 100 20 x 10 1. 3 x 1 1999 2003 2006 2008 2011 2013 2014 2015 2016 2017 O χρόνος προσπέλασης παραμένει σχεδόν σταθερός cslab@ntua 2017 -2018 21

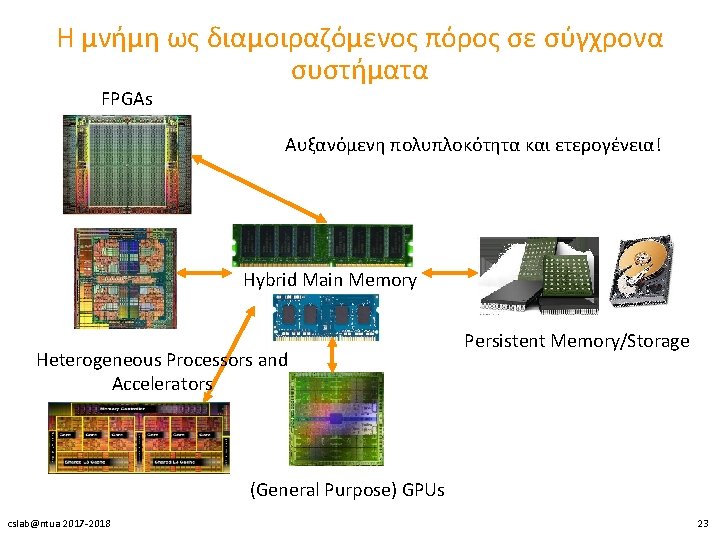

Η μνήμη ως διαμοιραζόμενος πόρος σε σύγχρονα συστήματα FPGAs Αυξανόμενη πολυπλοκότητα και ετερογένεια! Hybrid Main Memory Heterogeneous Processors and Accelerators Persistent Memory/Storage (General Purpose) GPUs cslab@ntua 2017 -2018 23

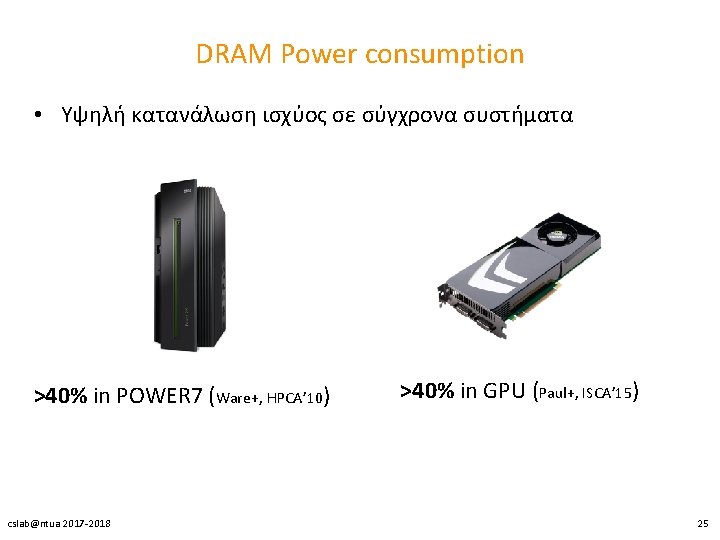

DRAM Power consumption • Υψηλή κατανάλωση ισχύος σε σύγχρονα συστήματα >40% in POWER 7 (Ware+, HPCA’ 10) cslab@ntua 2017 -2018 >40% in GPU (Paul+, ISCA’ 15) 25

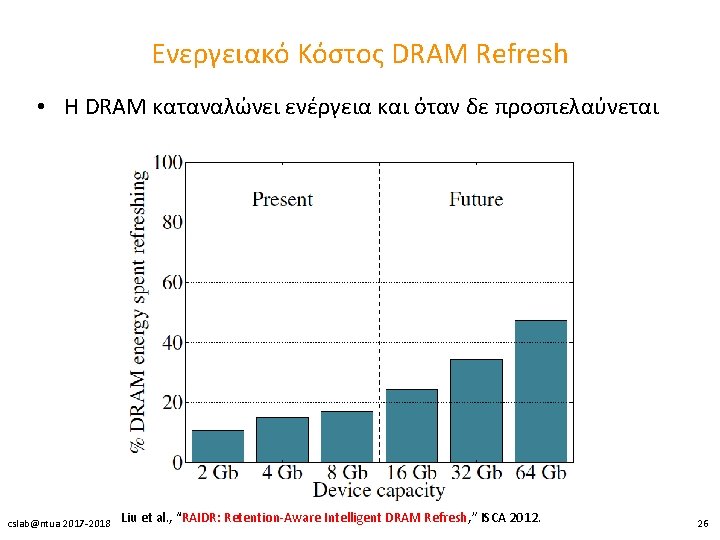

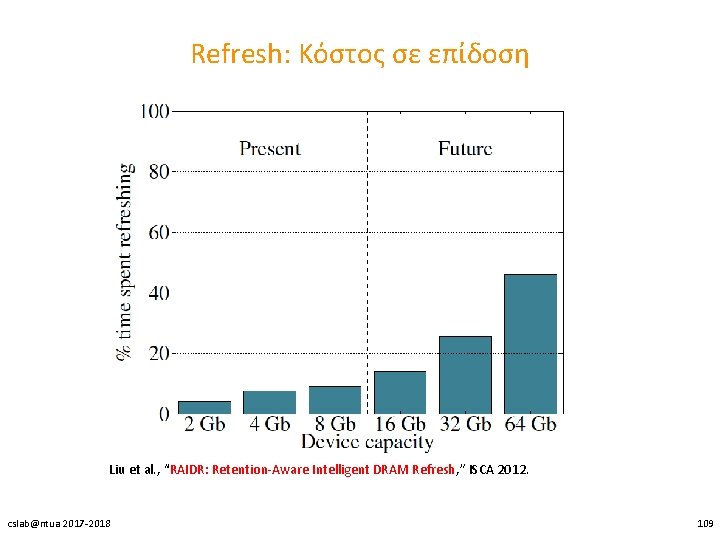

Ενεργειακό Κόστος DRAM Refresh • H DRAM καταναλώνει ενέργεια και όταν δε προσπελαύνεται cslab@ntua 2017 -2018 Liu et al. , “RAIDR: Retention-Aware Intelligent DRAM Refresh, ” ISCA 2012. 26

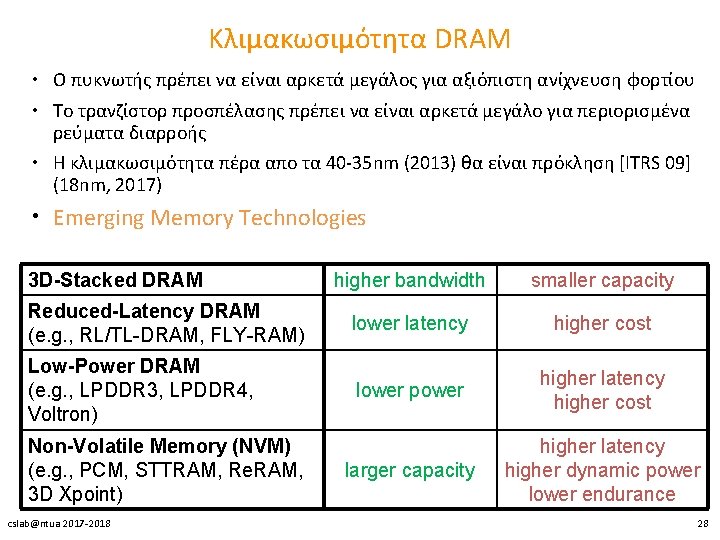

Κλιμακωσιμότητα DRAM • O πυκνωτής πρέπει να είναι αρκετά μεγάλος για αξιόπιστη ανίχνευση φορτίου • Το τρανζίστορ προσπέλασης πρέπει να είναι αρκετά μεγάλο για περιορισμένα ρεύματα διαρροής • Η κλιμακωσιμότητα πέρα απο τα 40 -35 nm (2013) θα είναι πρόκληση [ITRS 09] (18 nm, 2017) • Emerging Memory Technologies 3 D-Stacked DRAM higher bandwidth smaller capacity Reduced-Latency DRAM (e. g. , RL/TL-DRAM, FLY-RAM) lower latency higher cost Low-Power DRAM (e. g. , LPDDR 3, LPDDR 4, Voltron) lower power higher latency higher cost larger capacity higher latency higher dynamic power lower endurance Non-Volatile Memory (NVM) (e. g. , PCM, STTRAM, Re. RAM, 3 D Xpoint) cslab@ntua 2017 -2018 28

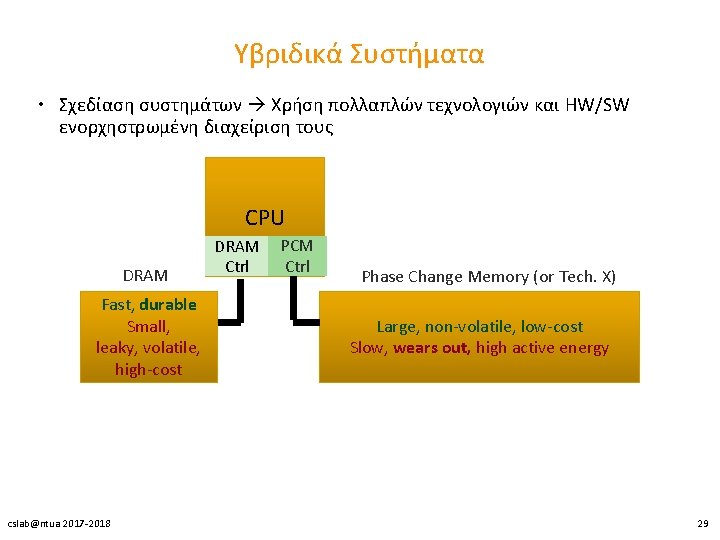

Υβριδικά Συστήματα • Σχεδίαση συστημάτων Χρήση πολλαπλών τεχνολογιών και HW/SW ενορχηστρωμένη διαχείριση τους CPU DRAM Fast, durable Small, leaky, volatile, high-cost cslab@ntua 2017 -2018 DRAM Ctrl PCM Ctrl Phase Change Memory (or Tech. X) Large, non-volatile, low-cost Slow, wears out, high active energy 29

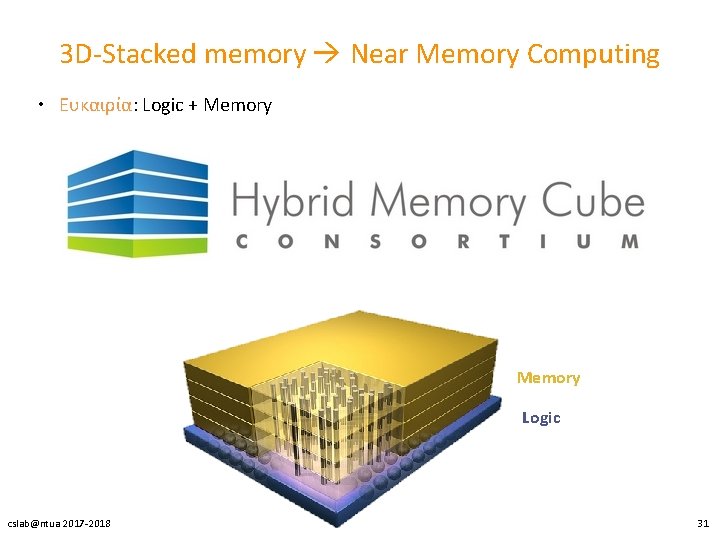

3 D-Stacked memory Near Memory Computing • Ευκαιρία: Logic + Memory Logic cslab@ntua 2017 -2018 31

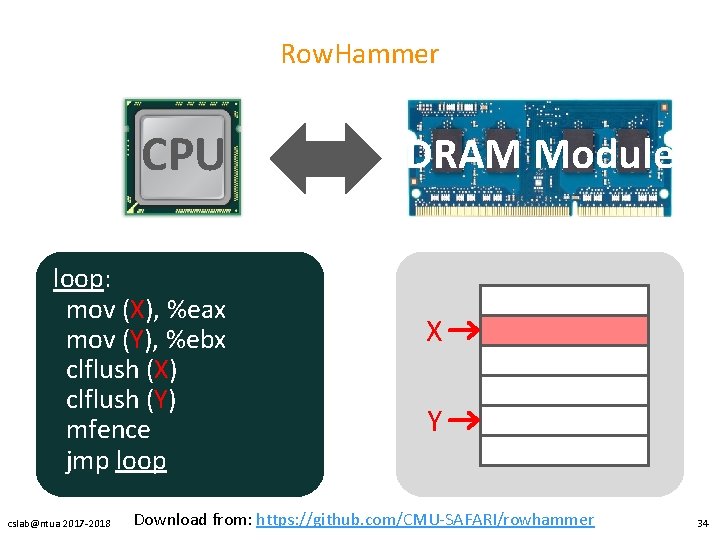

Row. Hammer CPU loop: mov (X), %eax mov (Y), %ebx clflush (X) clflush (Y) mfence jmp loop cslab@ntua 2017 -2018 Dally, Hi. PEAC 2015 DRAM Module X Y Download from: https: //github. com/CMU-SAFARI/rowhammer 34

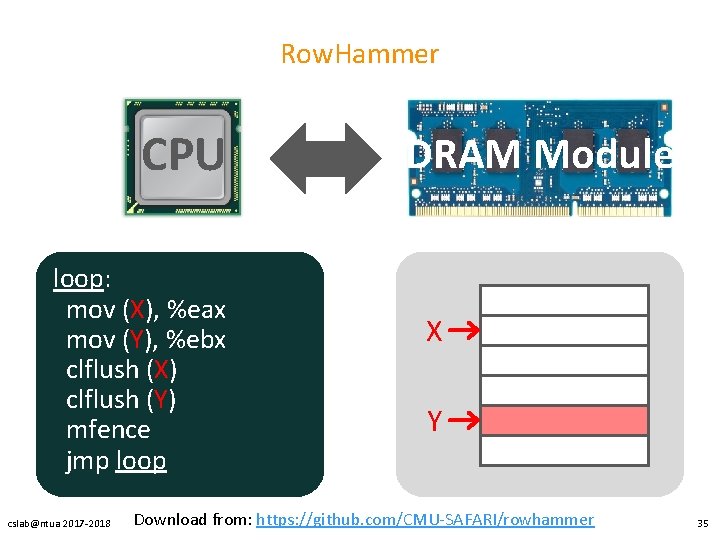

Row. Hammer CPU loop: mov (X), %eax mov (Y), %ebx clflush (X) clflush (Y) mfence jmp loop cslab@ntua 2017 -2018 DRAM Module X Y Download from: https: //github. com/CMU-SAFARI/rowhammer 35

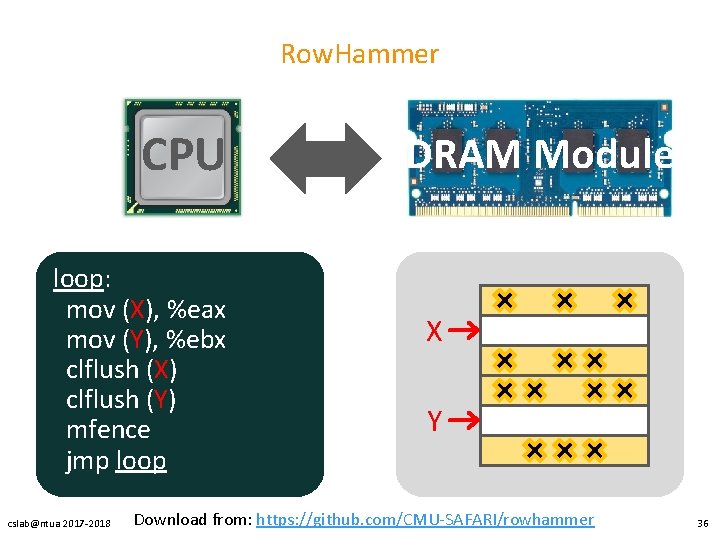

Row. Hammer CPU loop: mov (X), %eax mov (Y), %ebx clflush (X) clflush (Y) mfence jmp loop cslab@ntua 2017 -2018 DRAM Module X Y Download from: https: //github. com/CMU-SAFARI/rowhammer 36

Row. Hammer: Security Attack • Κανείς μπορεί με προβλέψιμο τρόπο να εισάγει σφάλματα σε σύγχρονα DRAM chips • Ένας απλός μηχανισμός αποτυχίας του HW μπορεί να δημιουργήσει ένα ευρύ κενό ασφαλείας στο σύστημα Induce bit flips in page table entries gain write access to the page table from user space gain read/write access to entire memory https: //googleprojectzero. blogspot. gr/2015/03/exp loiting-dram-rowhammer-bug-to-gain. html cslab@ntua 2017 -2018 38

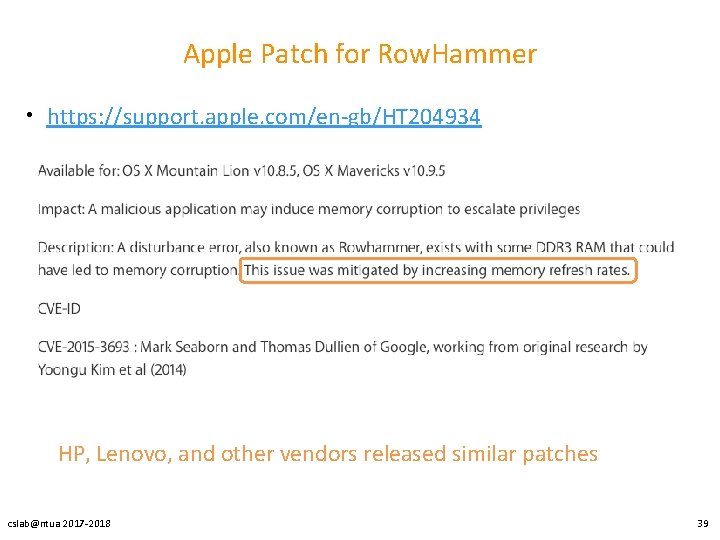

Apple Patch for Row. Hammer • https: //support. apple. com/en-gb/HT 204934 HP, Lenovo, and other vendors released similar patches cslab@ntua 2017 -2018 39

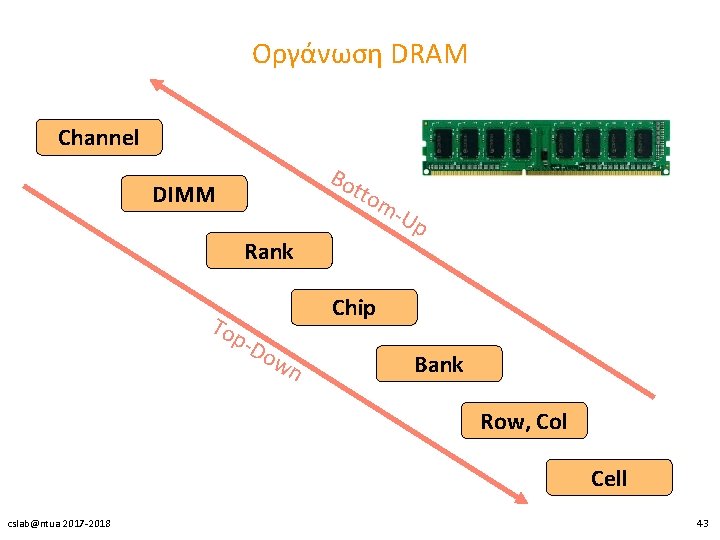

Οργάνωση DRAM cslab@ntua 2017 -2018 40

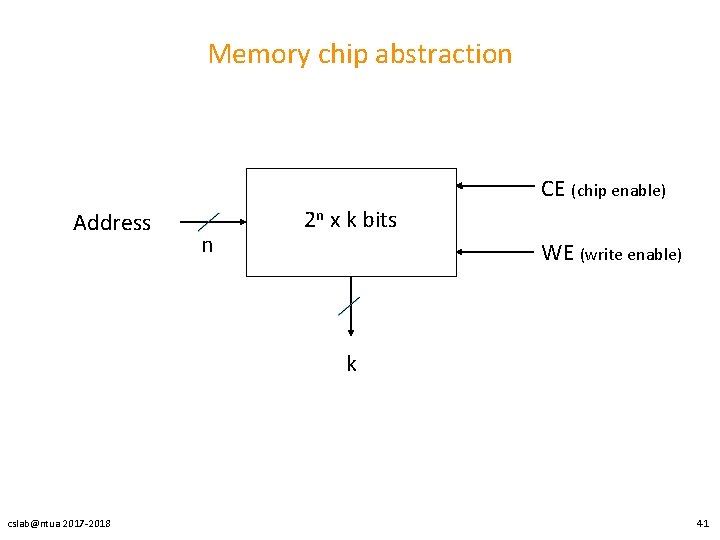

Memory chip abstraction CE (chip enable) Address n 2 n x k bits WE (write enable) k cslab@ntua 2017 -2018 41

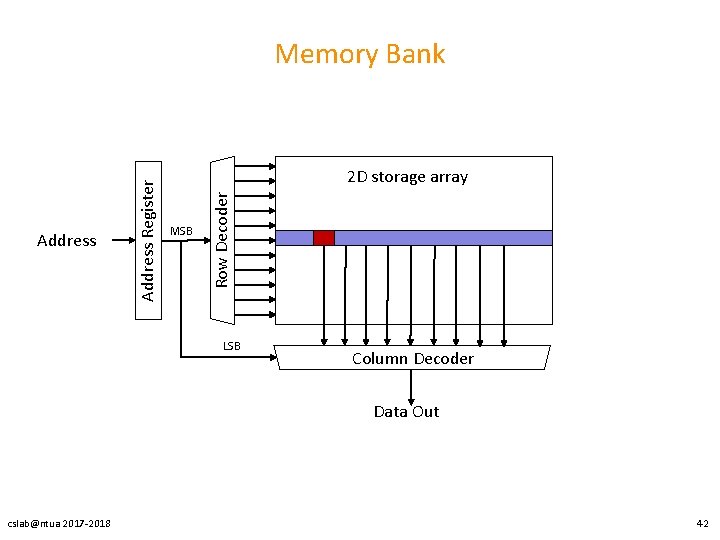

222 D storage array MSB Row Decoder Address Register Memory Bank LSB Column Decoder Data Out cslab@ntua 2017 -2018 42

Οργάνωση DRAM Channel Bo tto DIMM m- Rank Up To p Chip -Do wn Bank Row, Col Cell cslab@ntua 2017 -2018 43

Οργάνωση DRAM Bottom Up cslab@ntua 2017 -2018 44

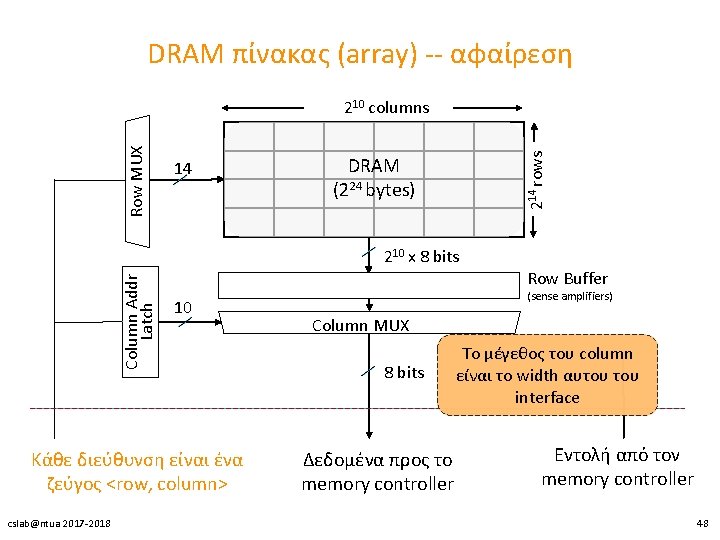

DRAM πίνακας (array) -- αφαίρεση 14 DRAM (224 bytes) Column Addr Latch 210 x 8 bits 10 DRAM διεύθυνση από το memory controller cslab@ntua 2017 -2018 214 rows Row MUX 210 columns Row Buffer (sense amplifiers) Column MUX 8 bits Δεδομένα προς το memory controller Εντολή από τον memory controller 47

DRAM πίνακας (array) -- αφαίρεση 14 214 rows Row MUX 210 columns DRAM (224 bytes) Column Addr Latch 210 x 8 bits 10 Κάθε διεύθυνση είναι ένα ζεύγος <row, column> cslab@ntua 2017 -2018 Row Buffer (sense amplifiers) Column MUX 8 bits Δεδομένα προς το memory controller Το μέγεθος του column είναι το width αυτου interface Εντολή από τον memory controller 48

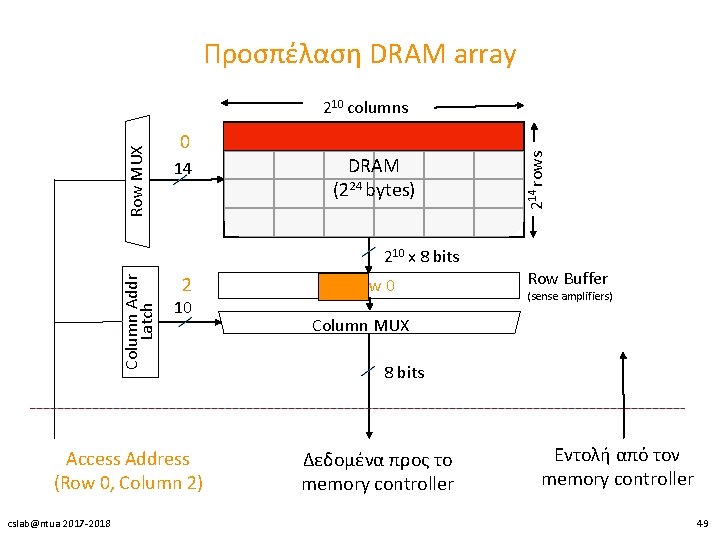

Προσπέλαση DRAM array 0 14 DRAM (224 bytes) Column Addr Latch 210 x 8 bits 2 10 Access Address (Row 0, Column 2) cslab@ntua 2017 -2018 Row 0 214 rows Row MUX 210 columns Row Buffer (sense amplifiers) Column MUX 8 bits Δεδομένα προς το memory controller Εντολή από τον memory controller 49

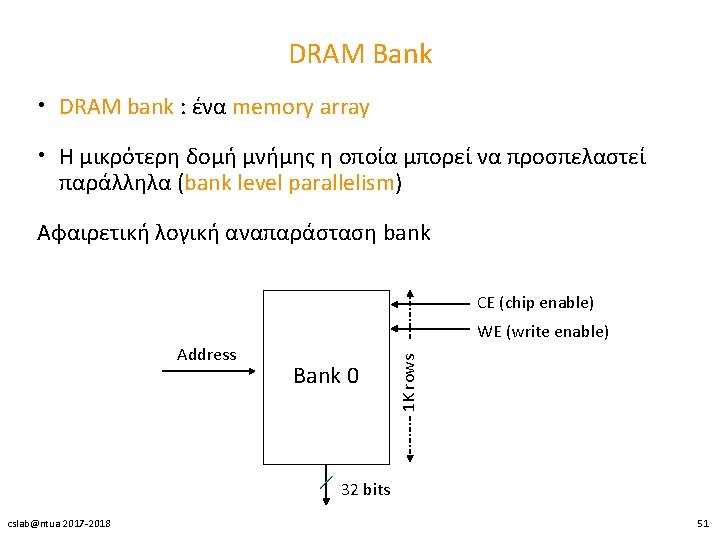

DRAM Bank • DRAM bank : ένα memory array • H μικρότερη δομή μνήμης η οποία μπορεί να προσπελαστεί παράλληλα (bank level parallelism) Αφαιρετική λογική αναπαράσταση bank CE (chip enable) Address Bank 0 1 K rows WE (write enable) 32 bits cslab@ntua 2017 -2018 51

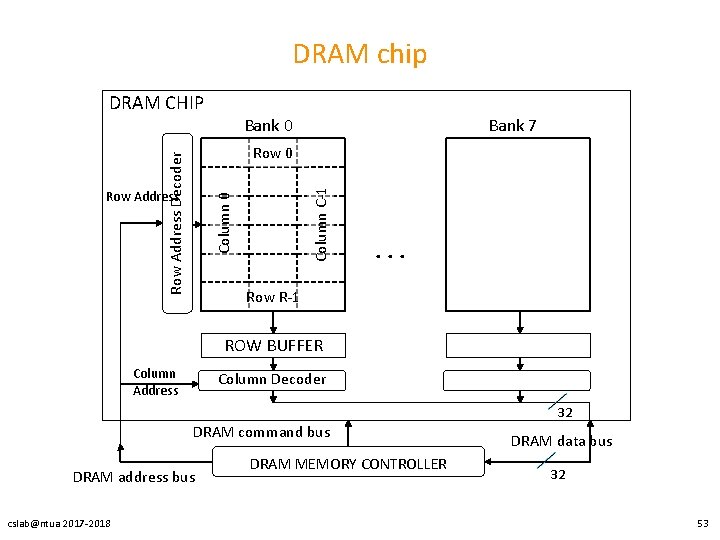

DRAM chip DRAM CHIP Bank 0 Bank 7 Column 0 Row Address Column C-1 Row Address Decoder Row 0 . . . Row R-1 ROW BUFFER Column Address Column Decoder 32 DRAM command bus DRAM address bus cslab@ntua 2017 -2018 DRAM MEMORY CONTROLLER DRAM data bus 32 53

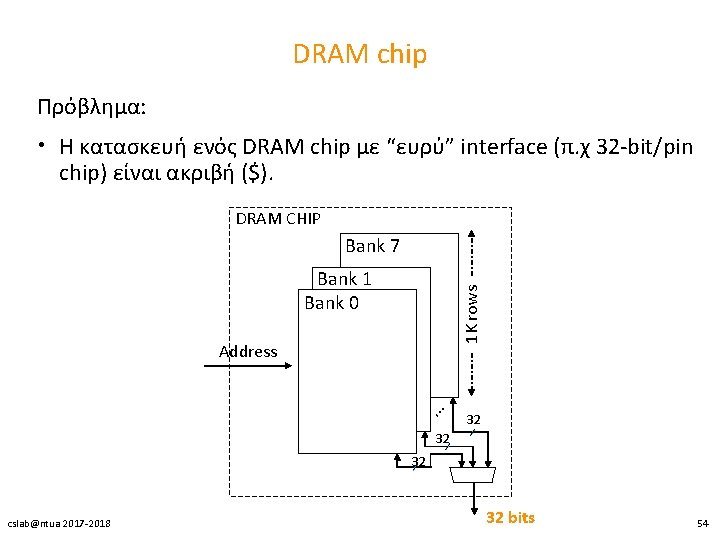

DRAM chip Πρόβλημα: • Η κατασκευή ενός DRAM chip με “ευρύ” interface (π. χ 32 -bit/pin chip) είναι ακριβή ($). DRAM CHIP Bank 7 Bank 1 … Address 1 K rows Bank 1 Bank 0 32 32 32 cslab@ntua 2017 -2018 32 bits 54

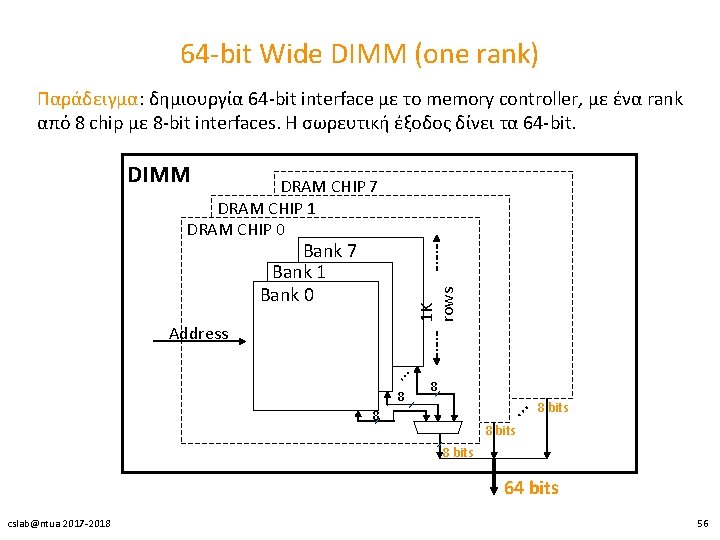

64 -bit Wide DIMM (one rank) Παράδειγμα: δημιουργία 64 -bit interface με το memory controller, με ένα rank από 8 chip με 8 -bit interfaces. Η σωρευτική έξοδος δίνει τα 64 -bit. DIMM DRAM CHIP 7 DRAM CHIP 1 DRAM CHIP 0 8 8 … Bank 1 … Address 1 K rows Bank 7 Bank 1 Bank 0 8 8 bits 64 bits cslab@ntua 2017 -2018 56

64 -bit Wide DIMM (one rank) • Ένας άλλος τρόπος να το σκεφτούμε/απεικονίσουμε είναι η κατάτμηση (partitioning) του κάθε bank στα διαφορετικά chips του ίδιου rank. Chip 0 Bank 7 Bank 0 Chip 1 Chip 7 Bank 0 Bank 7 Bank 0 Rank 0 . . . ROW BUFFER <56: 63> ROW BUFFER <8: 15> <0: 7> ROW BUFFER Data <0: 63> cslab@ntua 2017 -2018 57

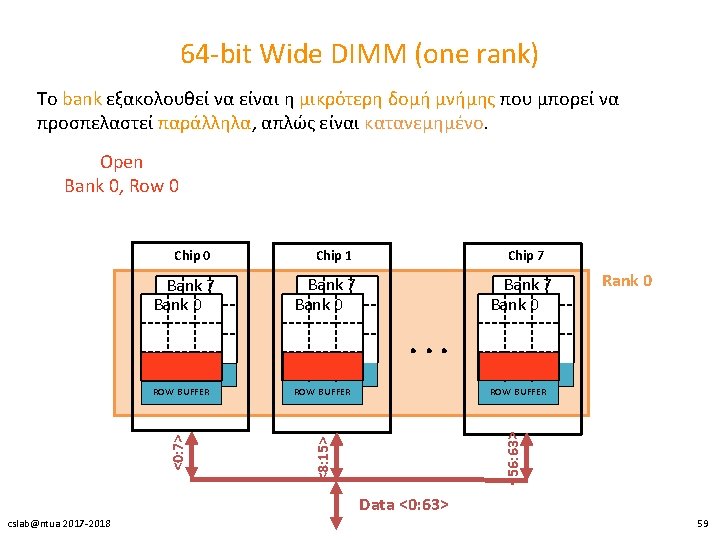

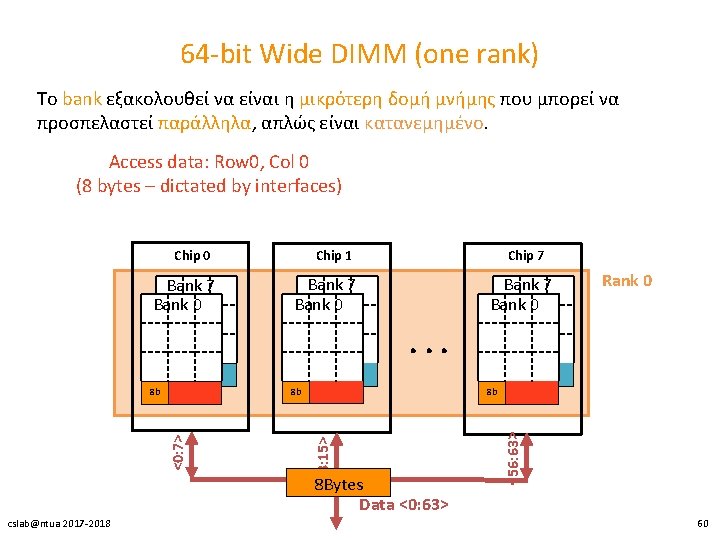

64 -bit Wide DIMM (one rank) To bank εξακολουθεί να είναι η μικρότερη δομή μνήμης που μπορεί να προσπελαστεί παράλληλα, απλώς είναι κατανεμημένο. Open Bank 0, Row 0 Chip 0 Bank 7 Bank 0 Chip 1 Chip 7 Bank 0 Bank 7 Bank 0 Rank 0 . . . ROW BUFFER <56: 63> ROW BUFFER <8: 15> <0: 7> ROW BUFFER Data <0: 63> cslab@ntua 2017 -2018 59

64 -bit Wide DIMM (one rank) To bank εξακολουθεί να είναι η μικρότερη δομή μνήμης που μπορεί να προσπελαστεί παράλληλα, απλώς είναι κατανεμημένο. Access data: Row 0, Col 0 (8 bytes – dictated by interfaces) Chip 1 Chip 0 Bank 7 Bank 0 Chip 7 Bank 0 Bank 7 Bank 0 Rank 0 . . . 8 b 8 Bytes Data <0: 63> cslab@ntua 2017 -2018 <56: 63> 8 b <8: 15> <0: 7> 8 b 60

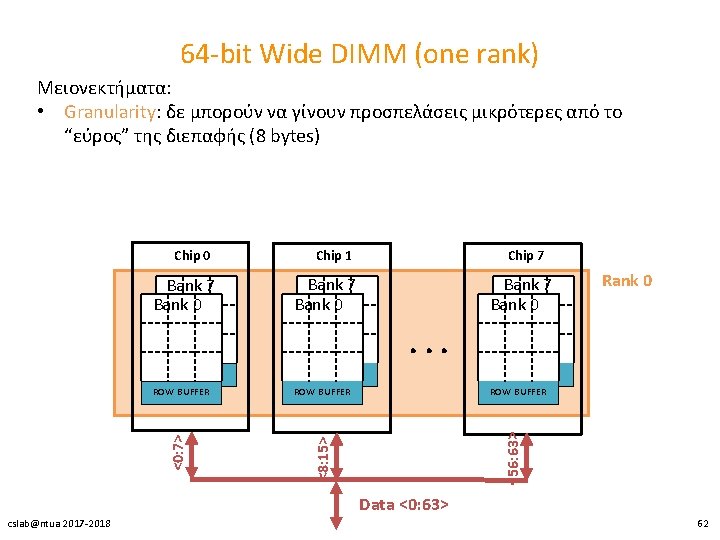

64 -bit Wide DIMM (one rank) Μειονεκτήματα: • Granularity: δε μπορούν να γίνουν προσπελάσεις μικρότερες από το “εύρος” της διεπαφής (8 bytes) Chip 0 Bank 7 Bank 0 Chip 1 Chip 7 Bank 0 Bank 7 Bank 0 Rank 0 . . . ROW BUFFER <56: 63> ROW BUFFER <8: 15> <0: 7> ROW BUFFER Data <0: 63> cslab@ntua 2017 -2018 62

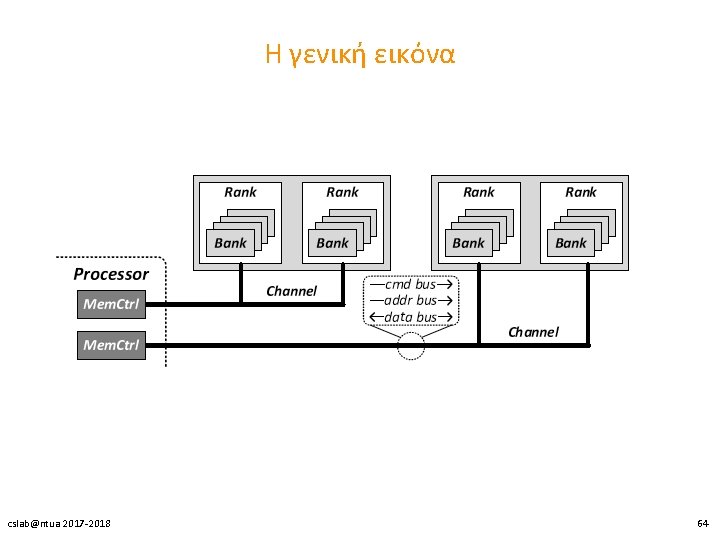

Η γενική εικόνα cslab@ntua 2017 -2018 64

Οργάνωση DRAM Top Down cslab@ntua 2017 -2018 65

Memory Channels “Channel” DIMM (Dual in-line memory module) Processor Memory channel cslab@ntua 2017 -2018 Memory channel 66

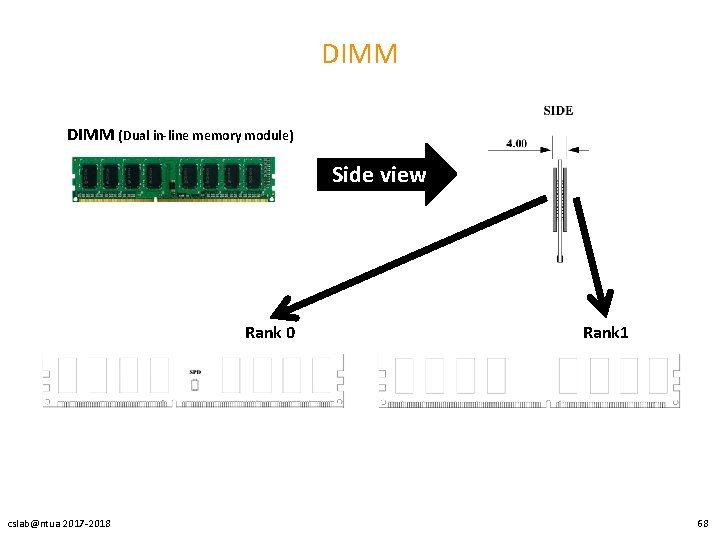

DIMM (Dual in-line memory module) Side view Front of DIMM cslab@ntua 2017 -2018 Back of DIMM 67

DIMM (Dual in-line memory module) Side view Rank 0 cslab@ntua 2017 -2018 Rank 1 68

Breaking Down a DIMM Ranks Rank 0 (Back) Rank 1 (Back) <0: 63> MUX Addr/Cmd CS <0: 1> Data <0: 63> Memory channel cslab@ntua 2017 -2018 69

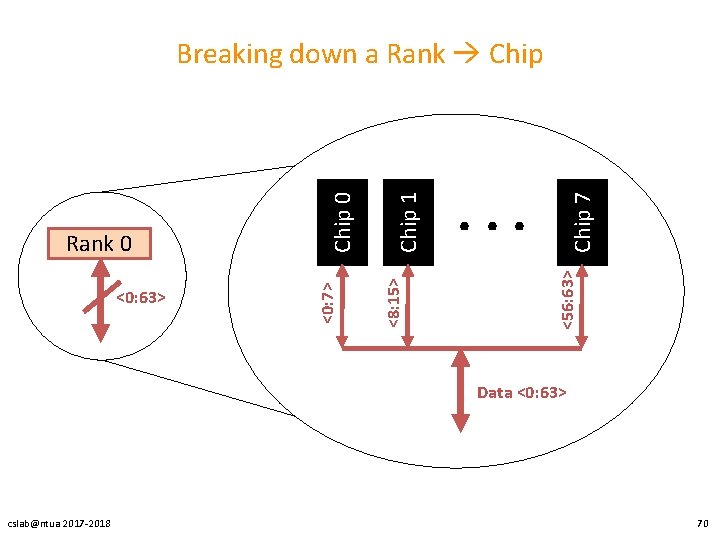

Chip 7 . . . <56: 63> Chip 1 <8: 15> <0: 63> <0: 7> Rank 0 Chip 0 Breaking down a Rank Chip Data <0: 63> cslab@ntua 2017 -2018 70

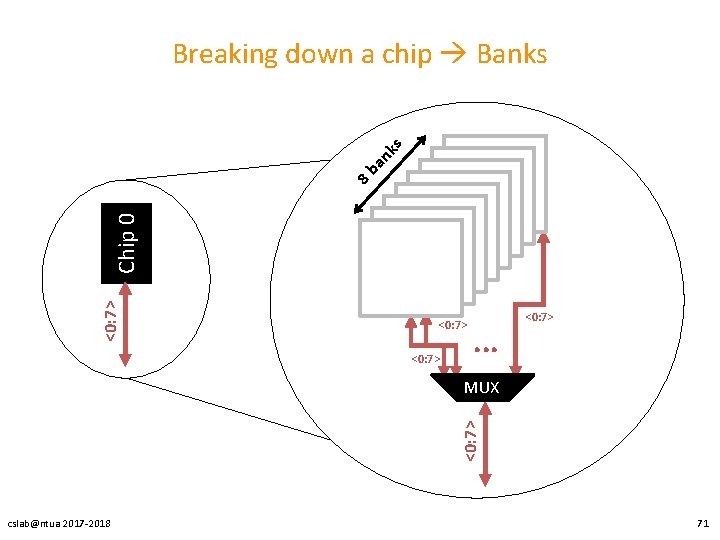

<0: 7> Chip 0 8 b an ks Breaking down a chip Banks Bank 0 <0: 7> . . . <0: 7> MUX cslab@ntua 2017 -2018 71

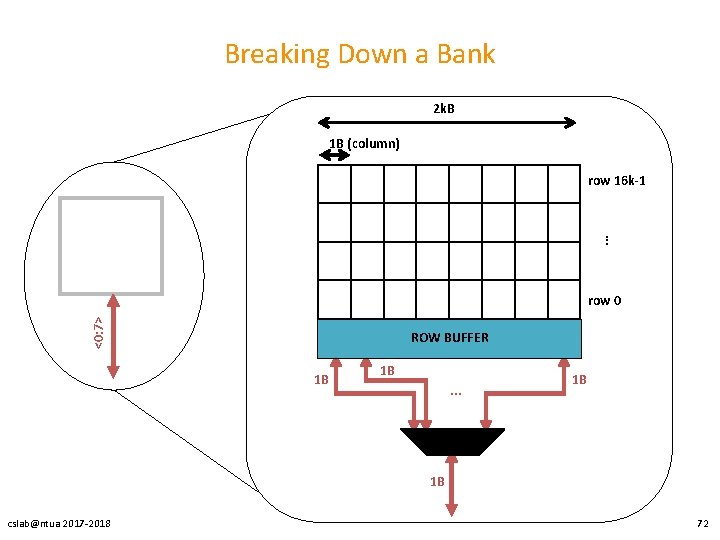

Breaking Down a Bank 2 k. B 1 B (column) row 16 k-1 . . . Bank 0 <0: 7> row 0 ROW BUFFER 1 B 1 B. . . 1 B 1 B cslab@ntua 2017 -2018 72

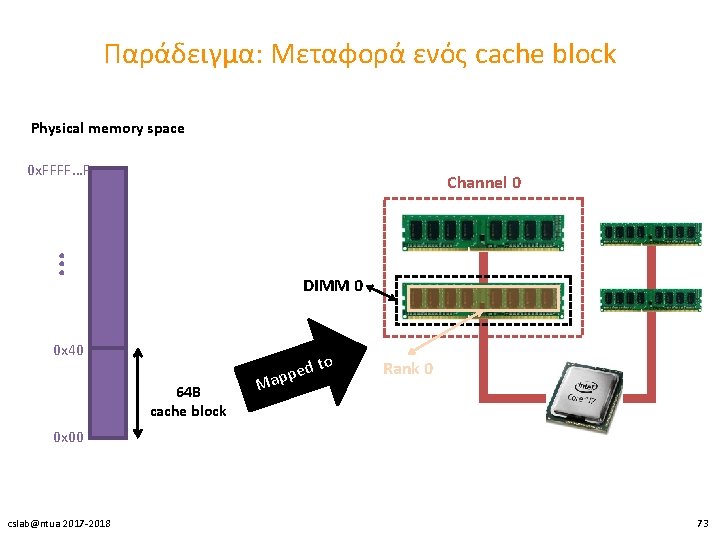

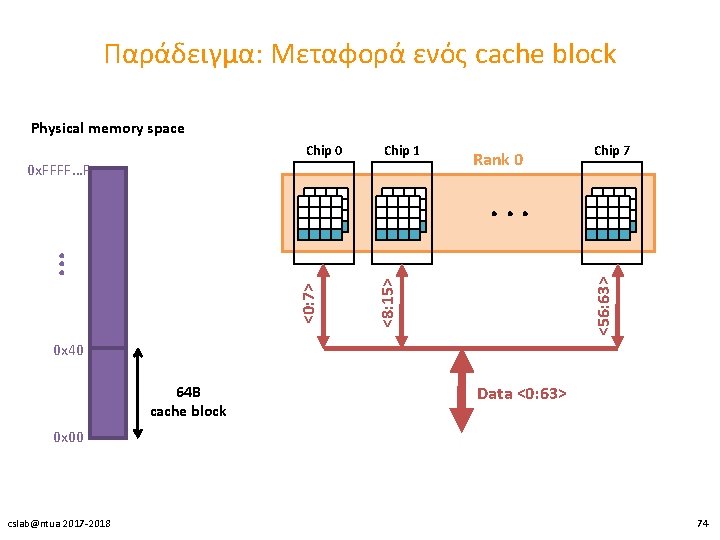

Παράδειγμα: Μεταφορά ενός cache block Physical memory space 0 x. FFFF…F . . . Channel 0 DIMM 0 0 x 40 64 B cache block ped p a M to Rank 0 0 x 00 cslab@ntua 2017 -2018 73

Παράδειγμα: Μεταφορά ενός cache block Physical memory space Chip 0 Chip 1 0 x. FFFF…F Rank 0 Chip 7 <56: 63> <8: 15> <0: 7> . . . 0 x 40 64 B cache block Data <0: 63> 0 x 00 cslab@ntua 2017 -2018 74

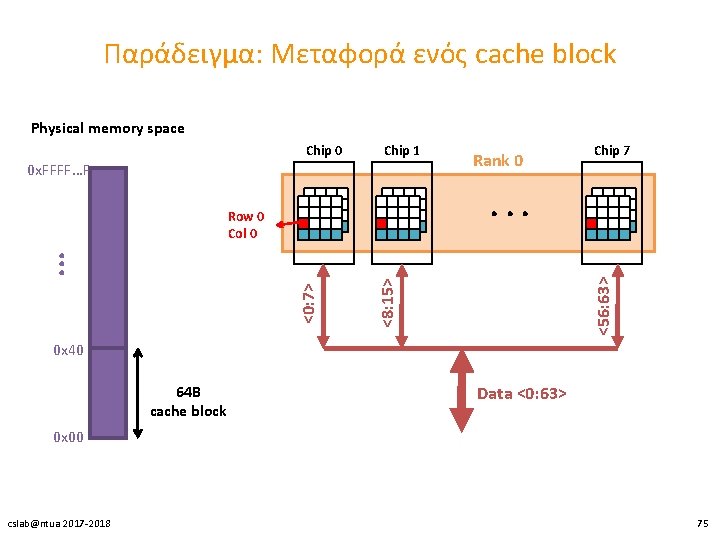

Παράδειγμα: Μεταφορά ενός cache block Physical memory space Chip 0 Chip 1 0 x. FFFF…F Rank 0 Chip 7 . . . <56: 63> <8: 15> <0: 7> . . . Row 0 Col 0 0 x 40 64 B cache block Data <0: 63> 0 x 00 cslab@ntua 2017 -2018 75

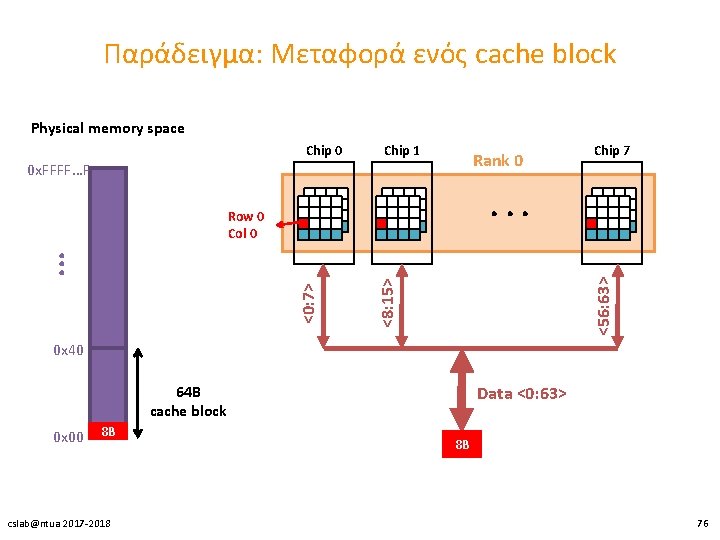

Παράδειγμα: Μεταφορά ενός cache block Physical memory space Chip 0 Chip 1 Rank 0 0 x. FFFF…F Chip 7 . . . <56: 63> <8: 15> <0: 7> . . . Row 0 Col 0 0 x 40 Data <0: 63> 64 B cache block 0 x 00 8 B cslab@ntua 2017 -2018 8 B 76

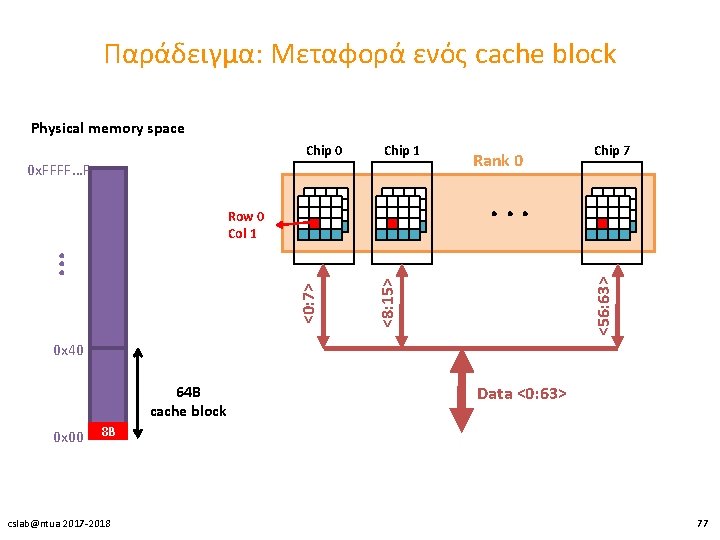

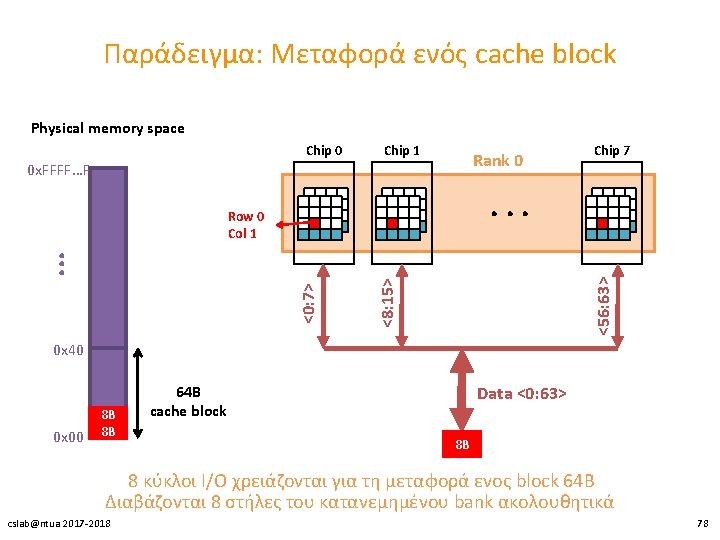

Παράδειγμα: Μεταφορά ενός cache block Physical memory space Chip 0 Chip 1 0 x. FFFF…F Rank 0 Chip 7 . . . <56: 63> <8: 15> <0: 7> . . . Row 0 Col 1 0 x 40 64 B cache block 0 x 00 Data <0: 63> 8 B cslab@ntua 2017 -2018 77

Παράδειγμα: Μεταφορά ενός cache block Physical memory space Chip 0 Chip 1 Rank 0 0 x. FFFF…F Chip 7 . . . <56: 63> <8: 15> <0: 7> . . . Row 0 Col 1 0 x 40 0 x 00 8 B 8 B Data <0: 63> 64 B cache block 8 B 8 κύκλοι I/O χρειάζονται για τη μεταφορά ενος block 64 B Διαβάζονται 8 στήλες του κατανεμημένου bank ακολουθητικά cslab@ntua 2017 -2018 78

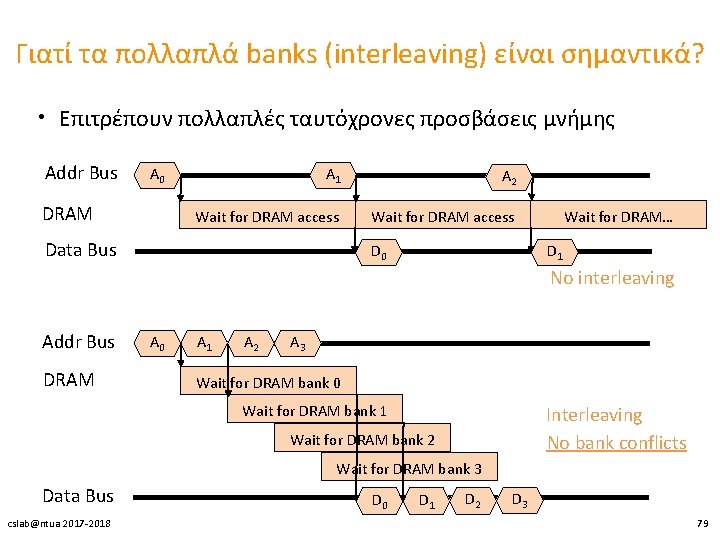

Γιατί τα πολλαπλά banks (interleaving) είναι σημαντικά? • Επιτρέπουν πολλαπλές ταυτόχρονες προσβάσεις μνήμης Addr Bus A 0 DRAM A 1 A 2 Wait for DRAM access Data Bus D 0 Wait for DRAM… D 1 No interleaving Addr Bus DRAM A 0 A 1 A 2 A 3 Wait for DRAM bank 0 Wait for DRAM bank 1 Interleaving No bank conflicts Wait for DRAM bank 2 Wait for DRAM bank 3 Data Bus cslab@ntua 2017 -2018 D 0 D 1 D 2 D 3 79

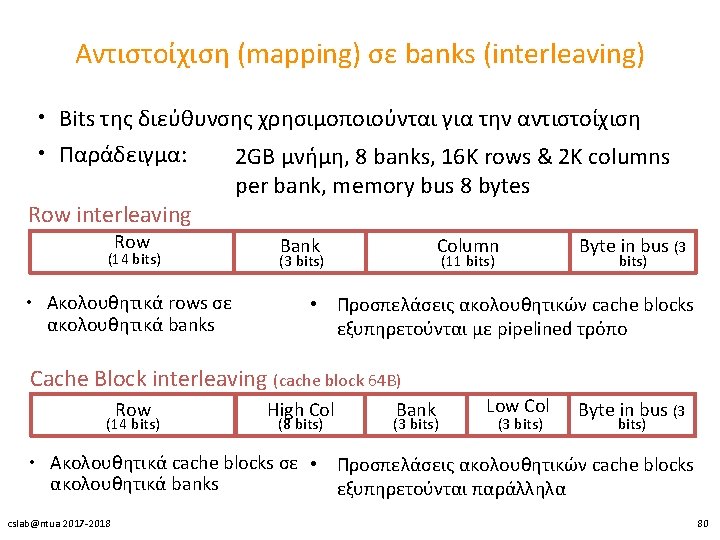

Αντιστοίχιση (mapping) σε banks (interleaving) • Bits της διεύθυνσης χρησιμοποιούνται για την αντιστοίχιση • Παράδειγμα: 2 GB μνήμη, 8 banks, 16Κ rows & 2 K columns per bank, memory bus 8 bytes Row interleaving Row (14 bits) • Ακολουθητικά rows σε ακολουθητικά banks Bank Column (3 bits) (11 bits) Byte in bus (3 bits) • Προσπελάσεις ακολουθητικών cache blocks εξυπηρετούνται με pipelined τρόπο Cache Block interleaving (cache block 64Β) Row (14 bits) High Col (8 bits) Bank (3 bits) Low Col (3 bits) Byte in bus (3 bits) • Ακολουθητικά cache blocks σε • Προσπελάσεις ακολουθητικών cache blocks ακολουθητικά banks εξυπηρετούνται παράλληλα cslab@ntua 2017 -2018 80

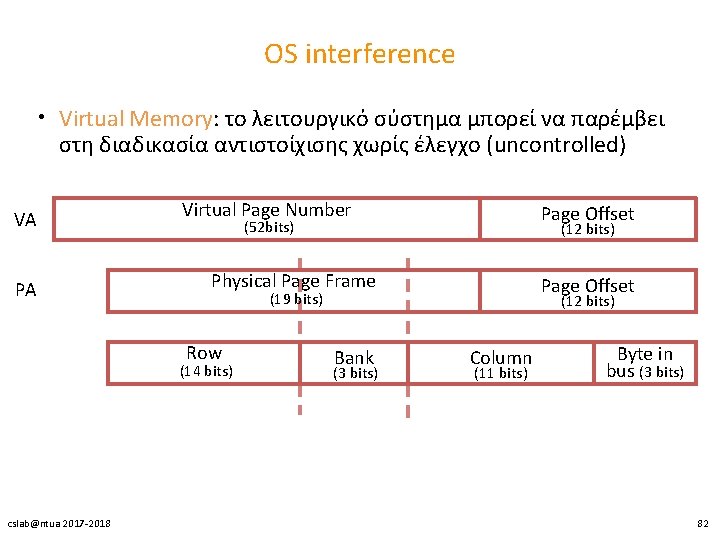

OS interference • Virtual Memory: το λειτουργικό σύστημα μπορεί να παρέμβει στη διαδικασία αντιστοίχισης χωρίς έλεγχο (uncontrolled) VA PA Virtual Page Number (12 bits) Physical Page Frame Page Offset (19 bits) Row (14 bits) cslab@ntua 2017 -2018 Page Offset (52 bits) Bank (3 bits) (12 bits) Column (11 bits) Byte in bus (3 bits) 82

Αντιστοίχιση σε multiple channels Row C (14 bits) Row Bank Column Byte in bus (3 (3 bits) C (3 bits) Bank (14 bits) (3 bits) Row Bank (14 bits) cslab@ntua 2017 -2018 (11 bits) (3 bits) (11 bits) Column (11 bits) in bus (3 C Byte bits) 84

Χρόνος απόκρισης DRAM cslab@ntua 2017 -2018 85

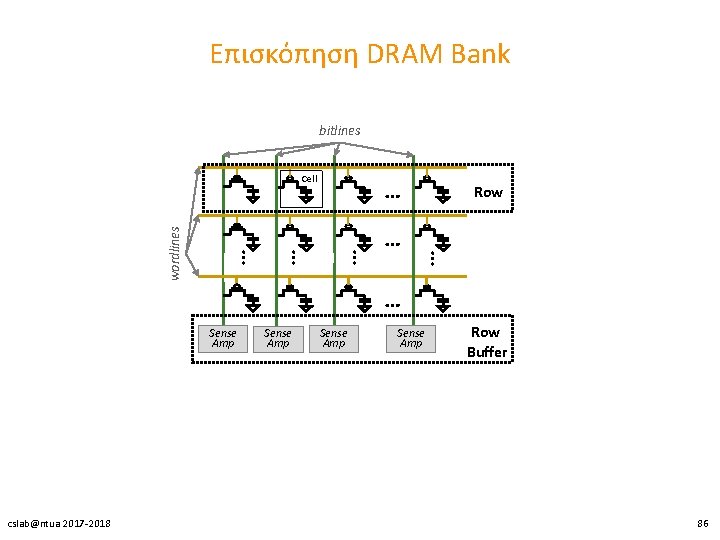

Επισκόπηση DRAM Bank bitlines … … Row … … wordlines Cell … Sense Amp cslab@ntua 2017 -2018 Sense Amp Row Buffer 86

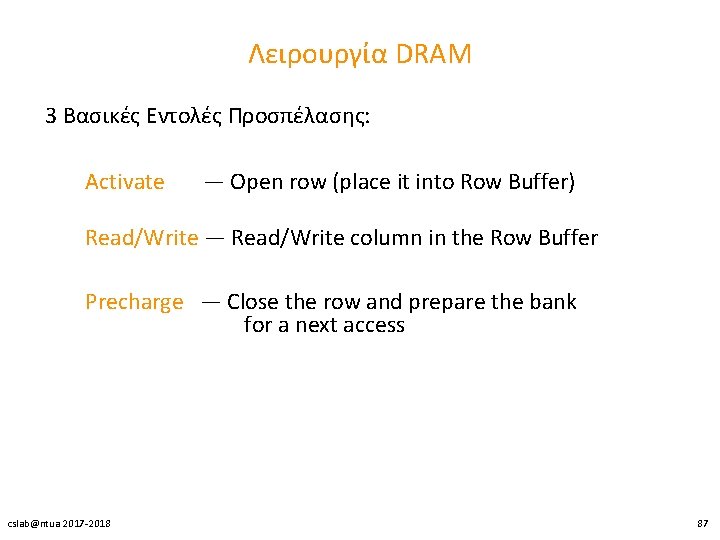

Λειρουργία DRAM 3 Βασικές Eντολές Προσπέλασης: Activate — Open row (place it into Row Buffer) Read/Write — Read/Write column in the Row Buffer Precharge — Close the row and prepare the bank for a next access cslab@ntua 2017 -2018 87

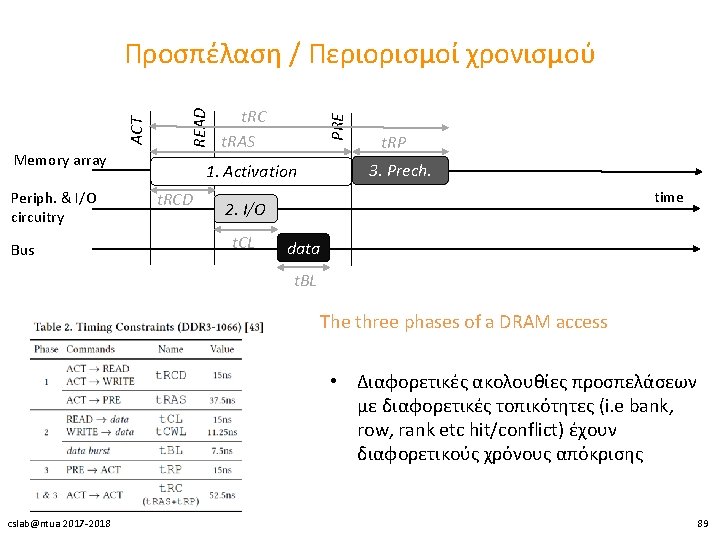

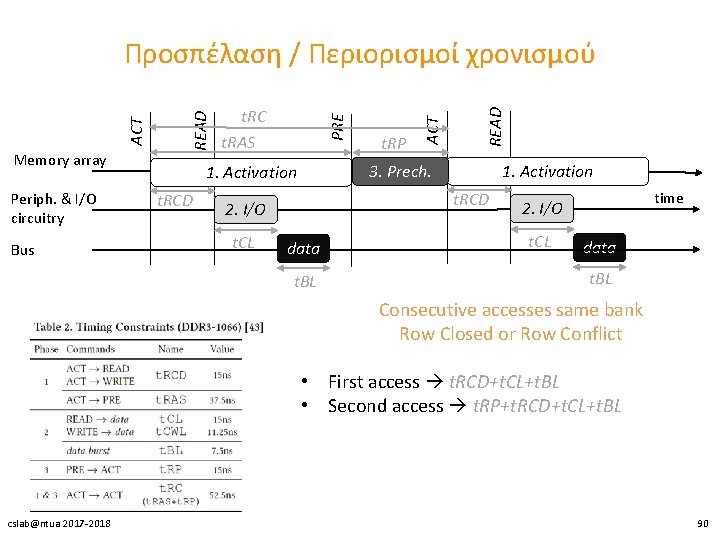

Memory array Periph. & I/O circuitry Bus t. RC t. RAS PRE READ ACT Προσπέλαση / Περιορισμοί χρονισμού 1. Activation t. RCD t. RP 3. Prech. time 2. I/O t. CL data t. BL The three phases of a DRAM access • Διαφορετικές ακολουθίες προσπελάσεων με διαφορετικές τοπικότητες (i. e bank, row, rank etc hit/conflict) έχουν διαφορετικούς χρόνους απόκρισης cslab@ntua 2017 -2018 89

Memory array Periph. & I/O circuitry Bus 1. Activation t. RCD 2. I/O t. CL READ 3. Prech. 1. Activation t. RCD t. RP ACT t. RC t. RAS PRE READ ACT Προσπέλαση / Περιορισμοί χρονισμού data t. BL time 2. I/O t. CL data t. BL Consecutive accesses same bank Row Closed or Row Conflict • First access t. RCD+t. CL+t. BL • Second access t. RP+t. RCD+t. CL+t. BL cslab@ntua 2017 -2018 90

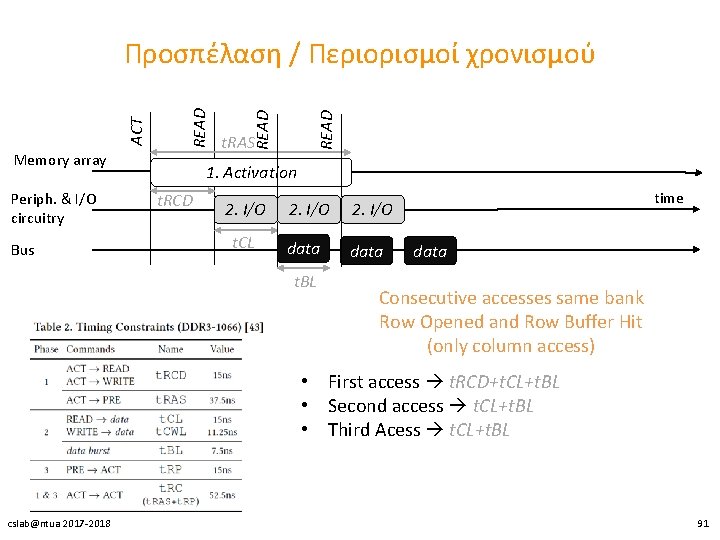

Periph. & I/O circuitry Bus READ Memory array READ ACT Προσπέλαση / Περιορισμοί χρονισμού t. RAS 1. Activation t. RCD 2. I/O t. CL 2. I/O data t. BL time data Consecutive accesses same bank Row Opened and Row Buffer Hit (only column access) • First access t. RCD+t. CL+t. BL • Second access t. CL+t. BL • Third Acess t. CL+t. BL cslab@ntua 2017 -2018 91

Ενας σύγχρονος memory controller Buffering/queueing requests per bank. Scheduling per bank & across banks cslab@ntua 2017 -2018 96

Ενας σύγχρονος memory controller cslab@ntua 2017 -2018 97

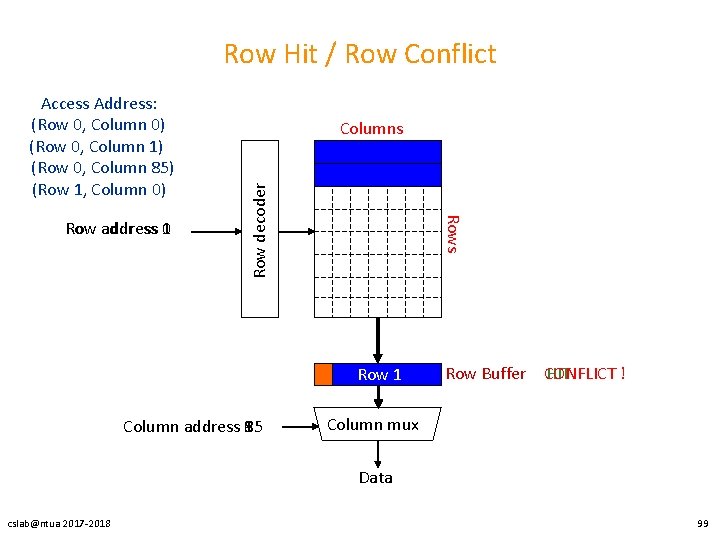

Row Hit / Row Conflict Rows Row address 01 Columns Row decoder Access Address: (Row 0, Column 0) (Row 0, Column 1) (Row 0, Column 85) (Row 1, Column 0) Row 01 Row Empty Column address 0 1 85 Row Buffer CONFLICT HIT ! Column mux Data cslab@ntua 2017 -2018 99

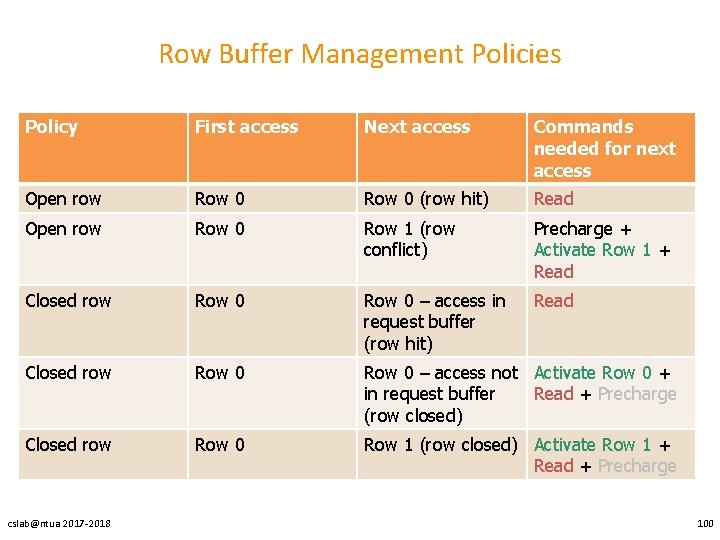

Row Buffer Management Policies Policy First access Next access Commands needed for next access Open row Row 0 (row hit) Read Open row Row 0 Row 1 (row conflict) Precharge + Activate Row 1 + Read Closed row Row 0 – access in request buffer (row hit) Read Closed row Row 0 – access not Activate Row 0 + in request buffer Read + Precharge (row closed) Closed row Row 0 Row 1 (row closed) Activate Row 1 + Read + Precharge cslab@ntua 2017 -2018 100

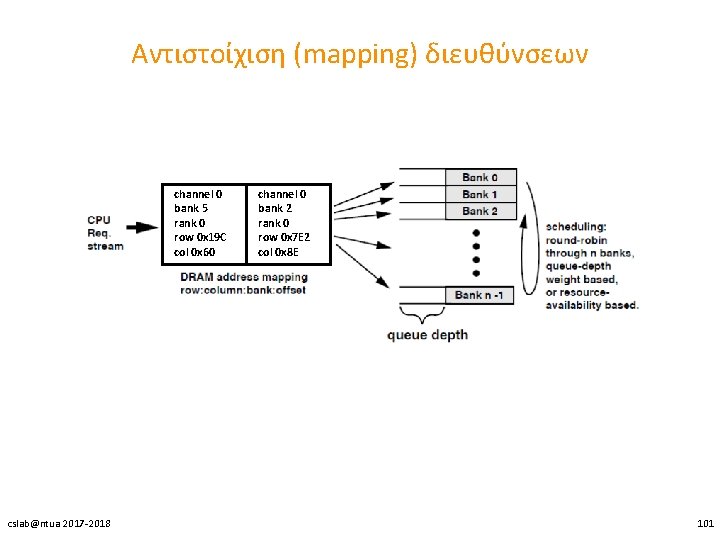

Αντιστοίχιση (mapping) διευθύνσεων channel 0 bank 5 rank 0 row 0 x 19 C col 0 x 60 cslab@ntua 2017 -2018 channel 0 bank 2 rank 0 row 0 x 7 E 2 col 0 x 8 E 101

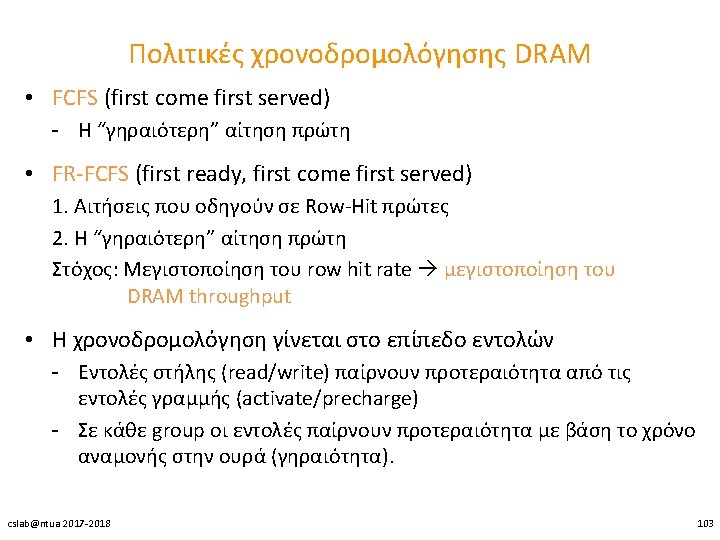

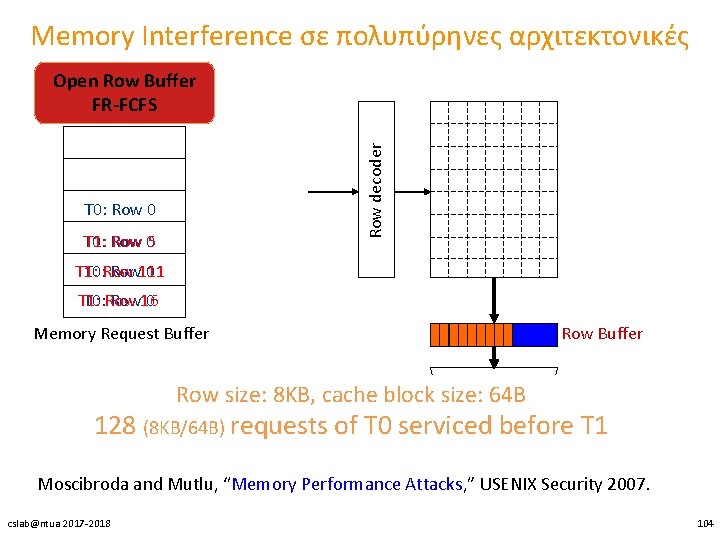

Memory Interference σε πολυπύρηνες αρχιτεκτονικές Row decoder Open Row Buffer FR-FCFS T 0: Row 0 T 0: T 1: Row 05 T 1: T 0: Row 111 0 T 1: T 0: Row 16 0 Memory Request Buffer Row 00 Row Buffer Column mux Row size: 8 KB, cache block size: 64 B T 0: STREAM 128 (8 KB/64 B) requests T 1: RANDOM of T 0 serviced before T 1 Data Moscibroda and Mutlu, “Memory Performance Attacks, ” USENIX Security 2007. cslab@ntua 2017 -2018 104

DRAM Refresh cslab@ntua 2017 -2018 106

Refresh: Κόστος σε επίδοση Liu et al. , “RAIDR: Retention-Aware Intelligent DRAM Refresh, ” ISCA 2012. cslab@ntua 2017 -2018 109

- Slides: 109