Made By Arun Branch 4 th Sem IC

Made By: Arun Branch. 4 th Sem. I&C Engg. Sub. MPMC G. B. N. Govt. Polytechnic, Nilokheri, Karnal

Contents: Introduction Block Diagram and Pin Description of the 8051 Registers Memory mapping in 8051 Stack in the 8051 I/O Port Programming Timer Interrupt

Why do we need to learn Microprocessors/controllers? n n n The microprocessor is the core of computer systems. Nowadays many communication, digital entertainment, portable devices, are controlled by them. A designer should know what types of components he needs, ways to reduce production costs and product reliable.

Different aspects of a microprocessor/controller n Hardware : Interface to the real world n Software : order how to deal with inputs

The necessary tools for a microprocessor/controller n n n n CPU: Central Processing Unit I/O: Input /Output Bus: Address bus & Data bus Memory: RAM & ROM Timer Interrupt Serial Port Parallel Port

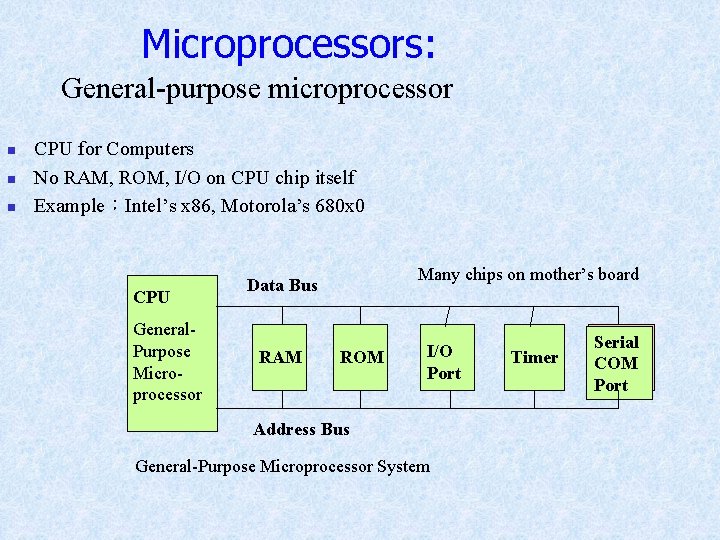

Microprocessors: General-purpose microprocessor n n n CPU for Computers No RAM, ROM, I/O on CPU chip itself Example:Intel’s x 86, Motorola’s 680 x 0 CPU General. Purpose Microprocessor Many chips on mother’s board Data Bus RAM ROM I/O Port Address Bus General-Purpose Microprocessor System Timer Serial COM Port

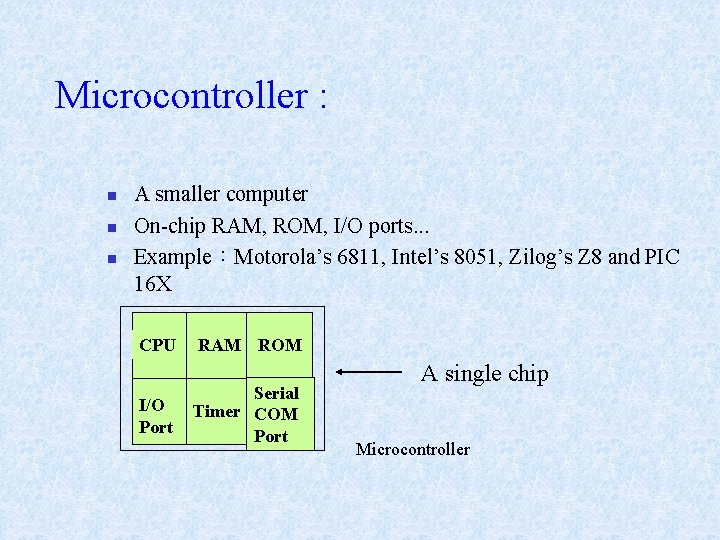

Microcontroller : n n n A smaller computer On-chip RAM, ROM, I/O ports. . . Example:Motorola’s 6811, Intel’s 8051, Zilog’s Z 8 and PIC 16 X CPU I/O Port RAM ROM Serial Timer COM Port A single chip Microcontroller

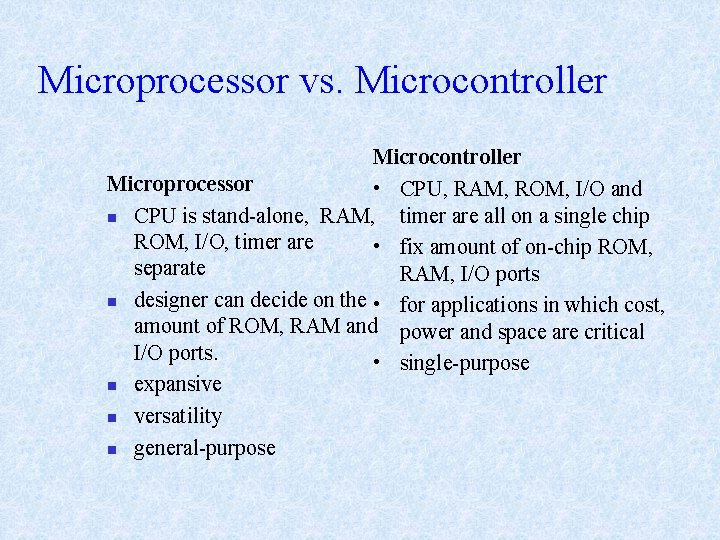

Microprocessor vs. Microcontroller Microprocessor • CPU, RAM, ROM, I/O and n CPU is stand-alone, RAM, timer are all on a single chip ROM, I/O, timer are • fix amount of on-chip ROM, separate RAM, I/O ports n designer can decide on the • for applications in which cost, amount of ROM, RAM and power and space are critical I/O ports. • single-purpose n expansive n versatility n general-purpose

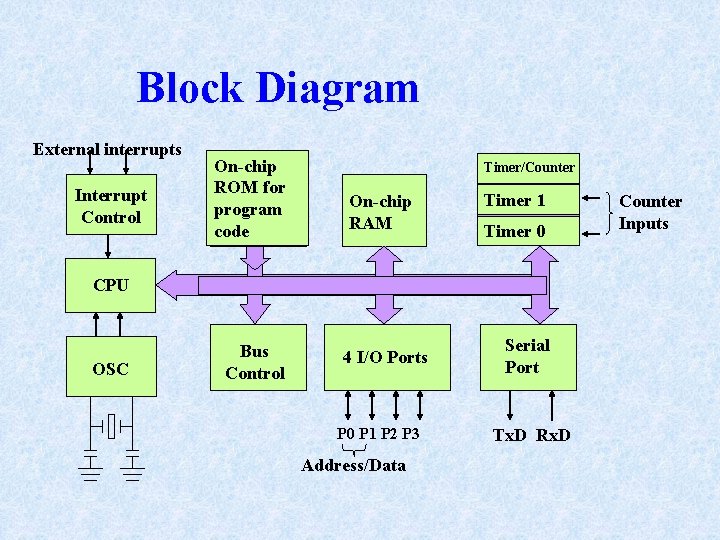

Block Diagram External interrupts Interrupt Control On-chip ROM for program code Timer/Counter On-chip RAM Timer 1 Timer 0 CPU OSC Bus Control 4 I/O Ports P 0 P 1 P 2 P 3 Address/Data Serial Port Tx. D Rx. D Counter Inputs

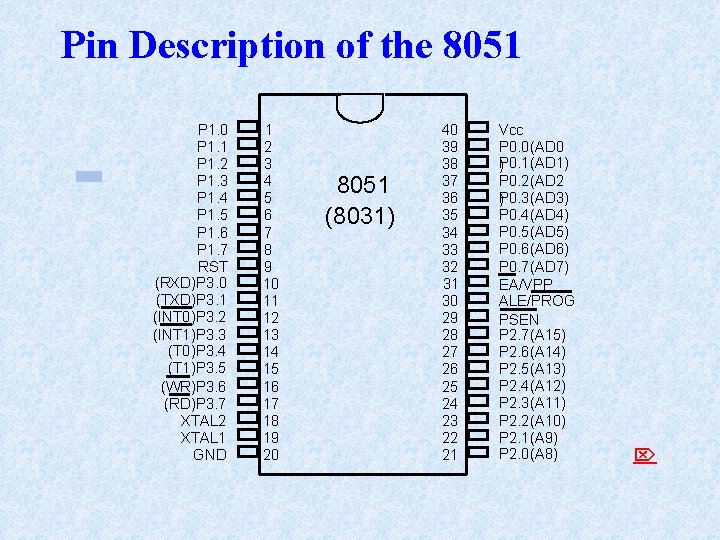

Pin Description of the 8051 P 1. 0 P 1. 1 P 1. 2 P 1. 3 P 1. 4 P 1. 5 P 1. 6 P 1. 7 RST (RXD)P 3. 0 (TXD)P 3. 1 (INT 0)P 3. 2 (INT 1)P 3. 3 (T 0)P 3. 4 (T 1)P 3. 5 (WR)P 3. 6 (RD)P 3. 7 XTAL 2 XTAL 1 GND 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 8051 (8031) 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21 Vcc P 0. 0(AD 0 P ) 0. 1(AD 1) P 0. 2(AD 2 P ) 0. 3(AD 3) P 0. 4(AD 4) P 0. 5(AD 5) P 0. 6(AD 6) P 0. 7(AD 7) EA/VPP ALE/PROG PSEN P 2. 7(A 15) P 2. 6(A 14) P 2. 5(A 13) P 2. 4(A 12) P 2. 3(A 11) P 2. 2(A 10) P 2. 1(A 9) P 2. 0(A 8)

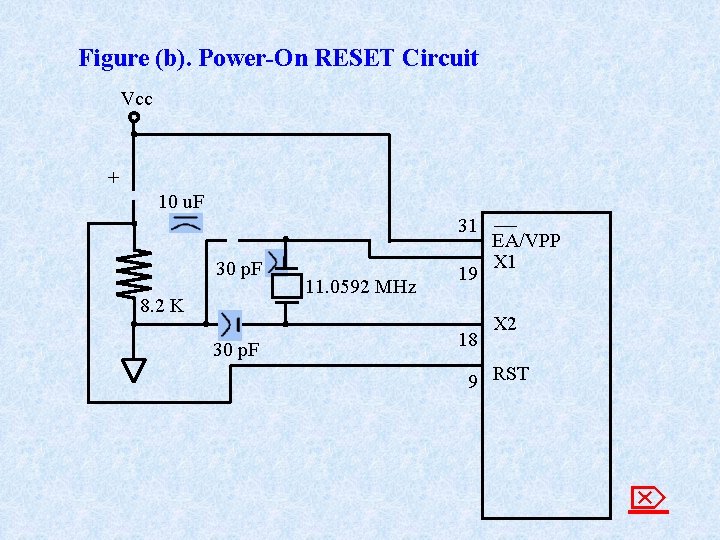

Figure (b). Power-On RESET Circuit Vcc + 10 u. F 31 30 p. F 8. 2 K 30 p. F 11. 0592 MHz 19 18 EA/VPP X 1 X 2 9 RST

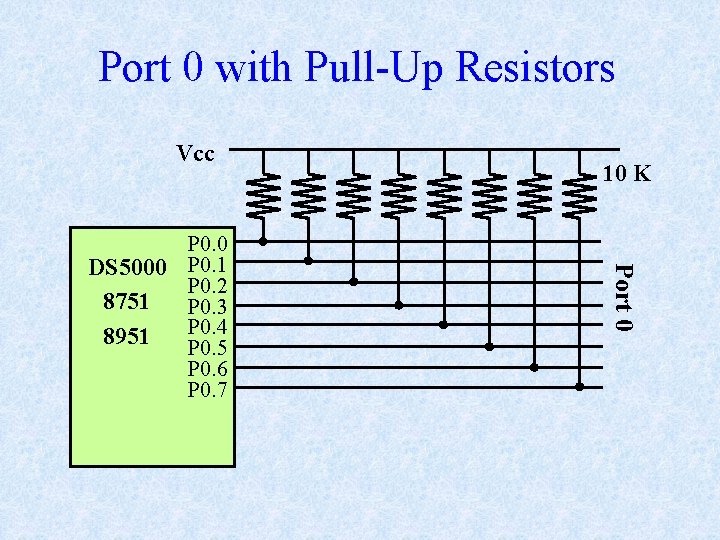

Port 0 with Pull-Up Resistors Vcc Port 0 P 0. 0 DS 5000 P 0. 1 P 0. 2 8751 P 0. 3 P 0. 4 8951 P 0. 5 P 0. 6 P 0. 7 10 K

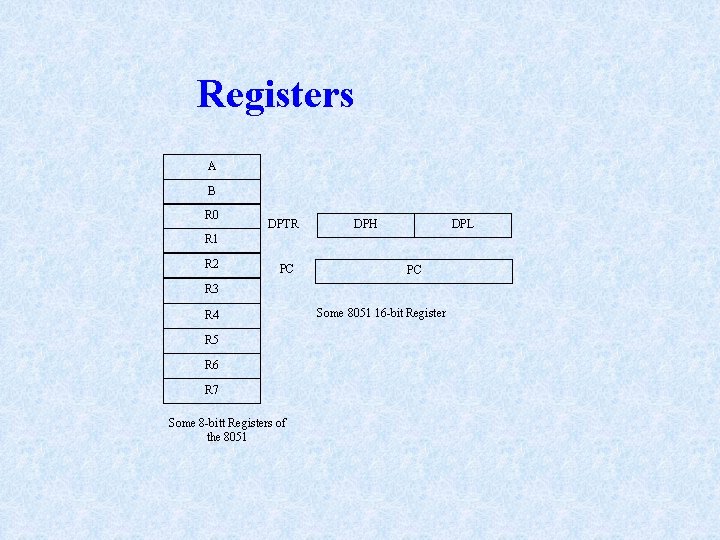

Registers A B R 0 DPTR DPH DPL R 1 R 2 PC PC R 3 R 4 R 5 R 6 R 7 Some 8 -bitt Registers of the 8051 Some 8051 16 -bit Register

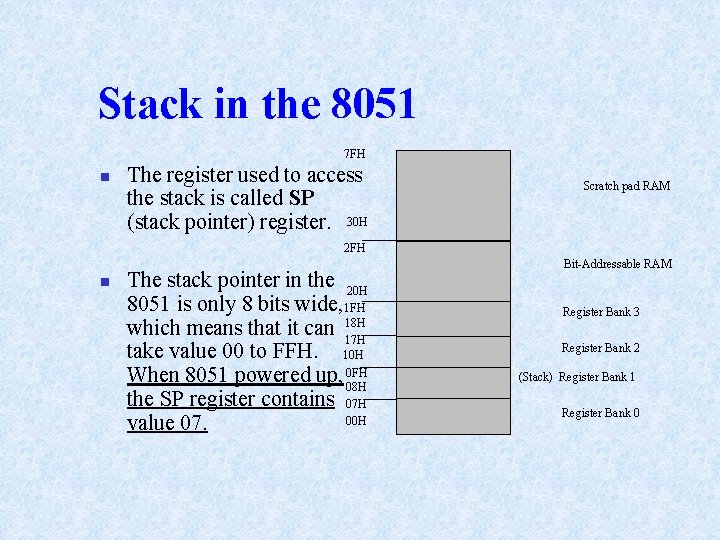

Stack in the 8051 7 FH n The register used to access the stack is called SP (stack pointer) register. 30 H Scratch pad RAM 2 FH n The stack pointer in the 20 H 8051 is only 8 bits wide, 1 FH which means that it can 18 H 17 H take value 00 to FFH. 10 H When 8051 powered up, 0 FH 08 H the SP register contains 07 H 00 H value 07. Bit-Addressable RAM Register Bank 3 Register Bank 2 (Stack) Register Bank 1 Register Bank 0

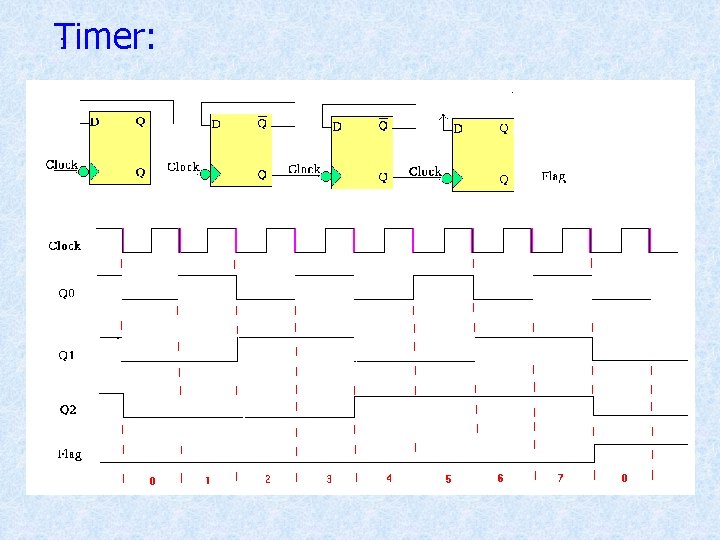

Timer: :

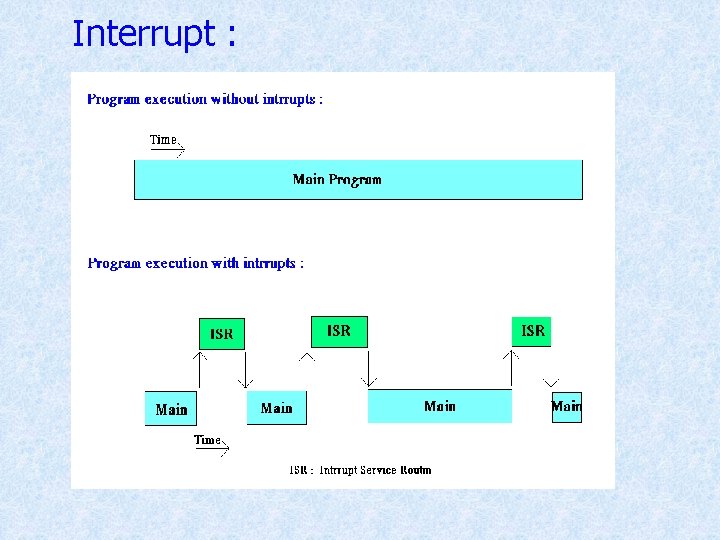

Interrupt :

Numerical Bases Used in Programming n Hexadecimal n Binary n BCD

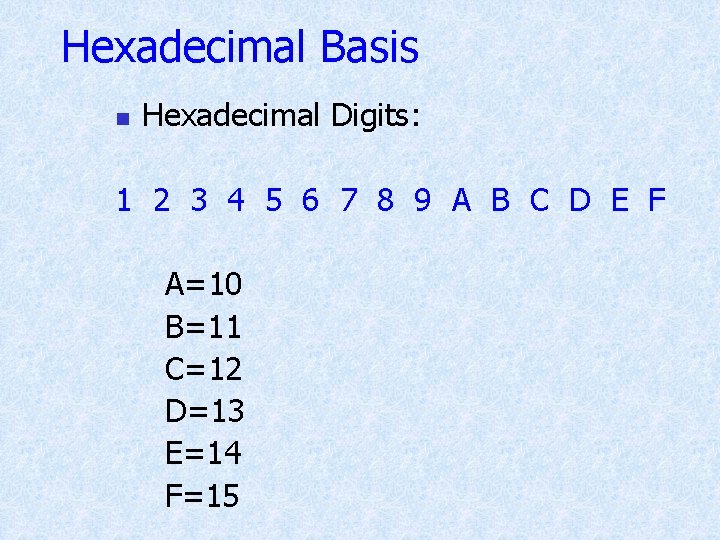

Hexadecimal Basis n Hexadecimal Digits: 1 2 3 4 5 6 7 8 9 A B C D E F A=10 B=11 C=12 D=13 E=14 F=15

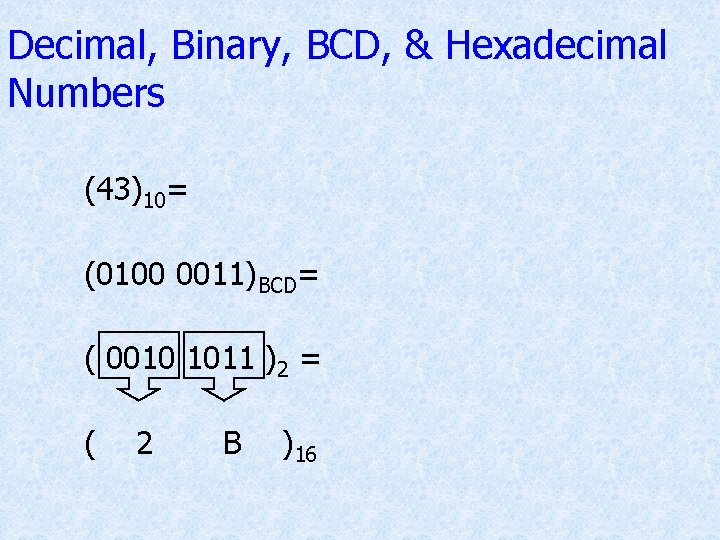

Decimal, Binary, BCD, & Hexadecimal Numbers (43)10= (0100 0011)BCD= ( 0010 1011 )2 = ( 2 B )16

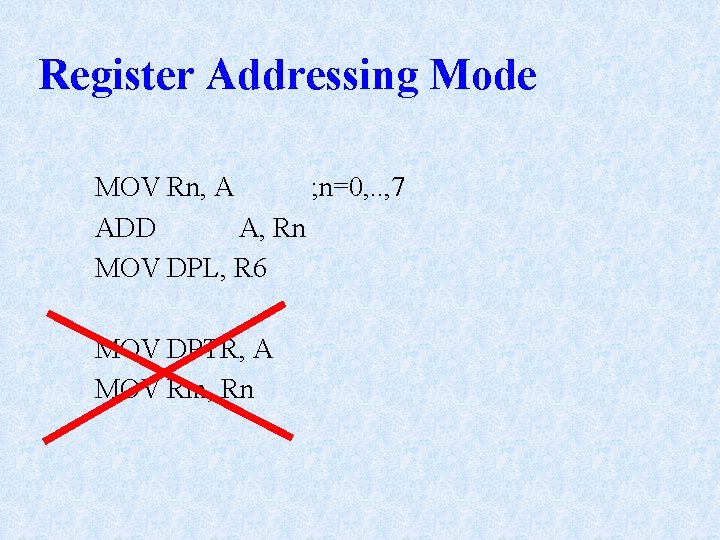

Register Addressing Mode MOV Rn, A ; n=0, . . , 7 ADD A, Rn MOV DPL, R 6 MOV DPTR, A MOV Rm, Rn

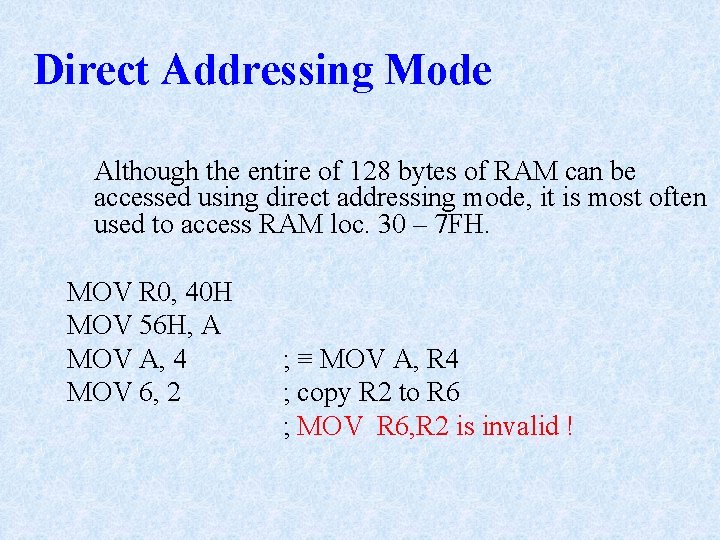

Direct Addressing Mode Although the entire of 128 bytes of RAM can be accessed using direct addressing mode, it is most often used to access RAM loc. 30 – 7 FH. MOV R 0, 40 H MOV 56 H, A MOV A, 4 MOV 6, 2 ; ≡ MOV A, R 4 ; copy R 2 to R 6 ; MOV R 6, R 2 is invalid !

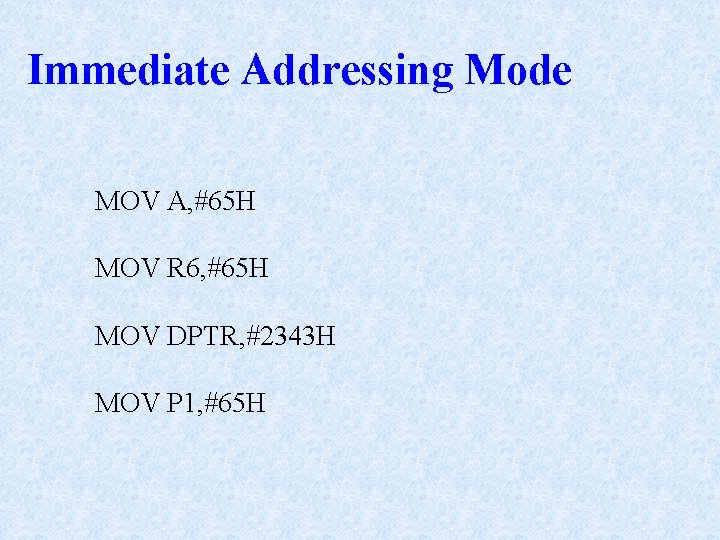

Immediate Addressing Mode MOV A, #65 H MOV R 6, #65 H MOV DPTR, #2343 H MOV P 1, #65 H

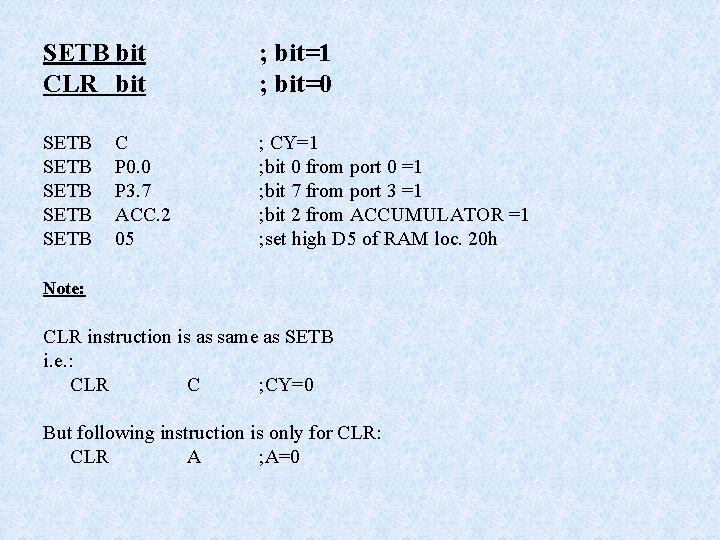

SETB bit CLR bit ; bit=1 ; bit=0 SETB SETB ; CY=1 ; bit 0 from port 0 =1 ; bit 7 from port 3 =1 ; bit 2 from ACCUMULATOR =1 ; set high D 5 of RAM loc. 20 h C P 0. 0 P 3. 7 ACC. 2 05 Note: CLR instruction is as same as SETB i. e. : CLR C ; CY=0 But following instruction is only for CLR: CLR A ; A=0

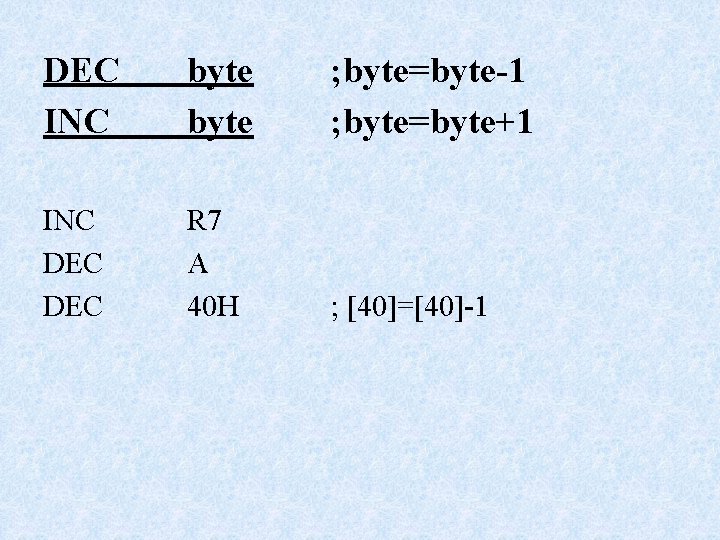

DEC INC byte ; byte=byte-1 ; byte=byte+1 INC DEC R 7 A 40 H ; [40]=[40]-1

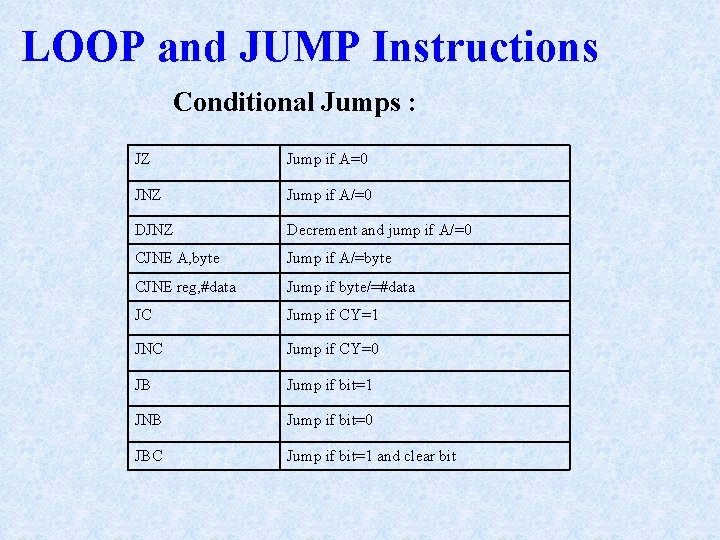

LOOP and JUMP Instructions Conditional Jumps : JZ Jump if A=0 JNZ Jump if A/=0 DJNZ Decrement and jump if A/=0 CJNE A, byte Jump if A/=byte CJNE reg, #data Jump if byte/=#data JC Jump if CY=1 JNC Jump if CY=0 JB Jump if bit=1 JNB Jump if bit=0 JBC Jump if bit=1 and clear bit

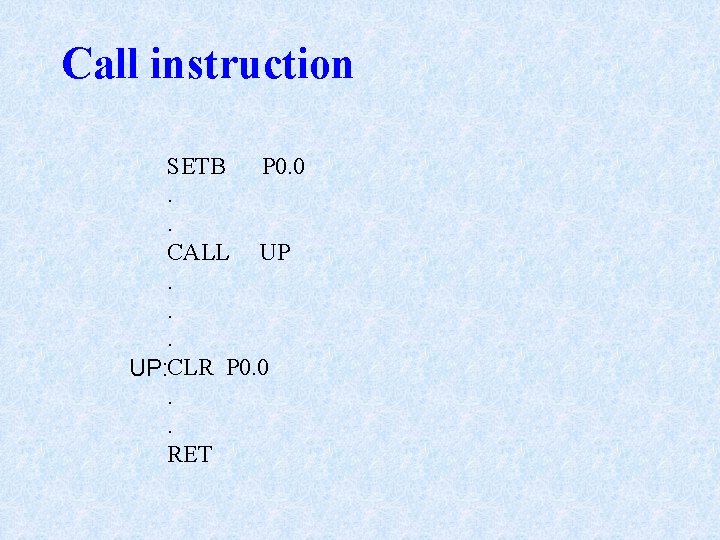

Call instruction SETB P 0. 0. . CALL UP. . . UP: CLR P 0. 0. . RET

- Slides: 26