Machine Organization Systems including computers often have STATEDEPENDENT

![Behaviour of Memory Notation for memory-related behaviour: § write(value, addr) mem[addr] : = value Behaviour of Memory Notation for memory-related behaviour: § write(value, addr) mem[addr] : = value](https://slidetodoc.com/presentation_image_h/2b7227e6dbb83778307f78e99398f014/image-13.jpg)

- Slides: 18

Machine Organization § Systems (including computers) often have STATE-DEPENDENT behaviour § response to an event at some point in time depends on previous sequence of events § current state: the net accumulated effects of the history of events § state-based models use state variables to encode state information § (have you seen this elsewhere? ) 20 -Sep-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94. 201. lecture 7 -8 -compstate 1

Machine Organization § Example: combination lock (e. g. on lockers) • • combination sequence: X, Y, Z go right past X twice, then stop at X go left past Y once, then stop at Y go right and stop at Z § model of the lock: • input events: position of dial • output events: clasp locked/unlocked 20 -Sep-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94. 201. lecture 7 -8 -compstate 2

Combination Lock § To describe behaviour: need state variables to remember the relevant history of events; E. G. : • direction of turning dial, • number of times gone past “next combination” number • “next combination” number expected • whether clasp is locked/unlocked 20 -Sep-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94. 201. lecture 7 -8 -compstate 3

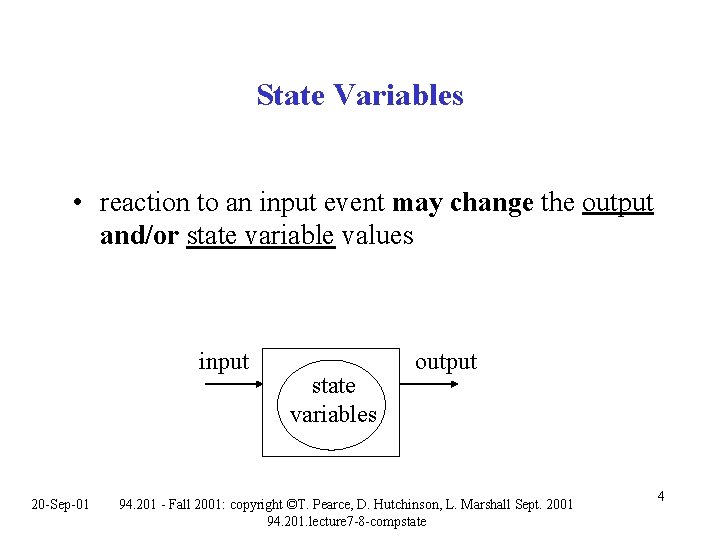

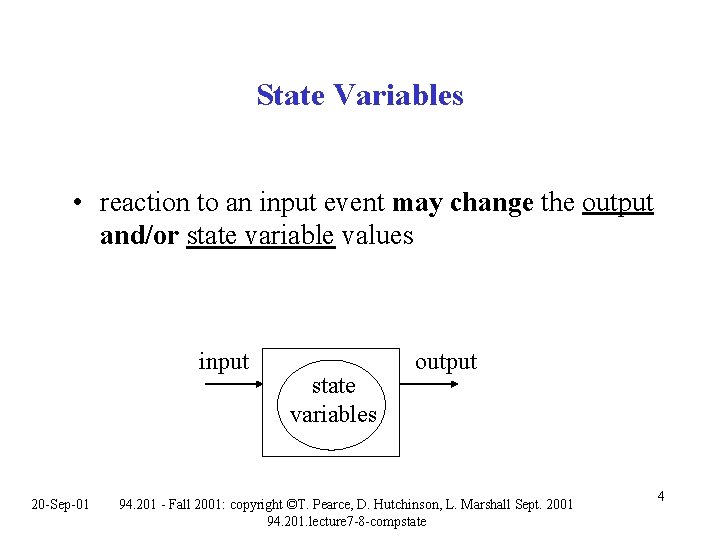

State Variables • reaction to an input event may change the output and/or state variable values input 20 -Sep-01 state variables output 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94. 201. lecture 7 -8 -compstate 4

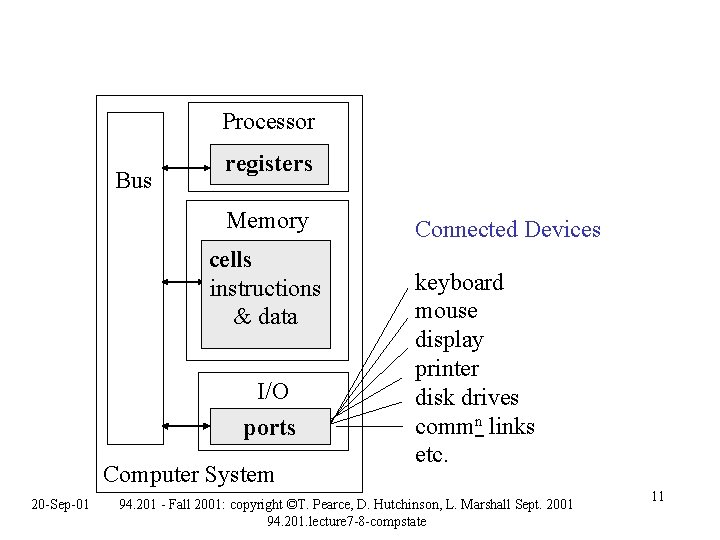

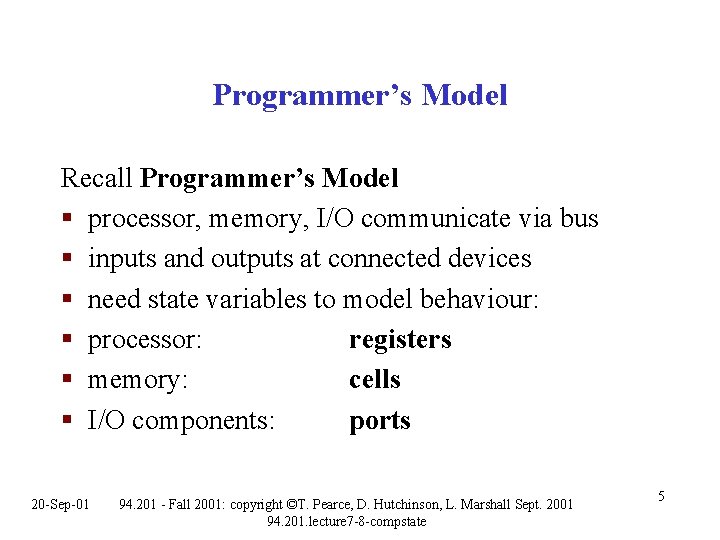

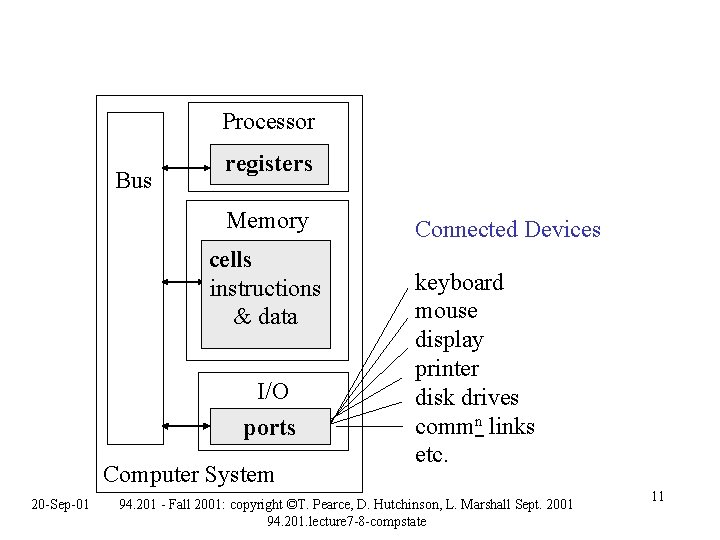

Programmer’s Model Recall Programmer’s Model § processor, memory, I/O communicate via bus § inputs and outputs at connected devices § need state variables to model behaviour: § processor: registers § memory: cells § I/O components: ports 20 -Sep-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94. 201. lecture 7 -8 -compstate 5

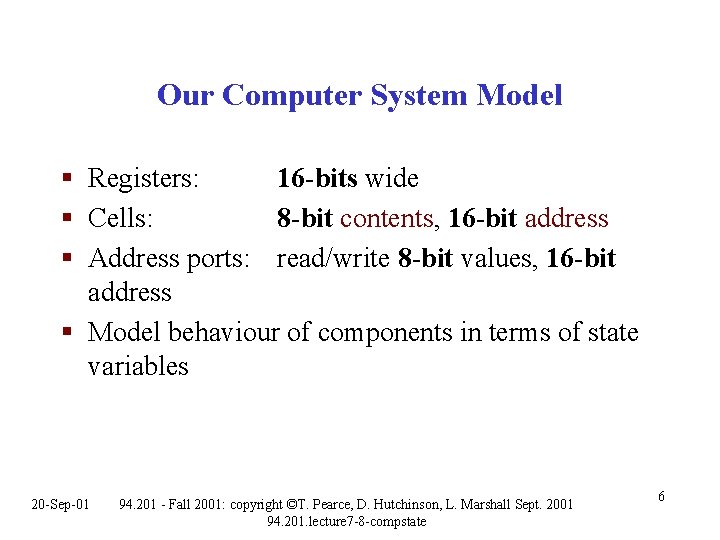

Our Computer System Model § Registers: 16 -bits wide § Cells: 8 -bit contents, 16 -bit address § Address ports: read/write 8 -bit values, 16 -bit address § Model behaviour of components in terms of state variables 20 -Sep-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94. 201. lecture 7 -8 -compstate 6

Programming at the Machine Level § at single instruction level: • instructions are executed by processor • instructions manipulate state variables • read, modify, write values § once state variables and instructions are understood, then all of the building blocks available to programmers are known! § there is nothing else !! (not rocket science) 20 -Sep-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94. 201. lecture 7 -8 -compstate 7

Programming at the Machine Level Program sequences of instructions to § generate outputs in response to inputs § manage information saved in state variables § the intellectual & creative part! 20 -Sep-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94. 201. lecture 7 -8 -compstate 8

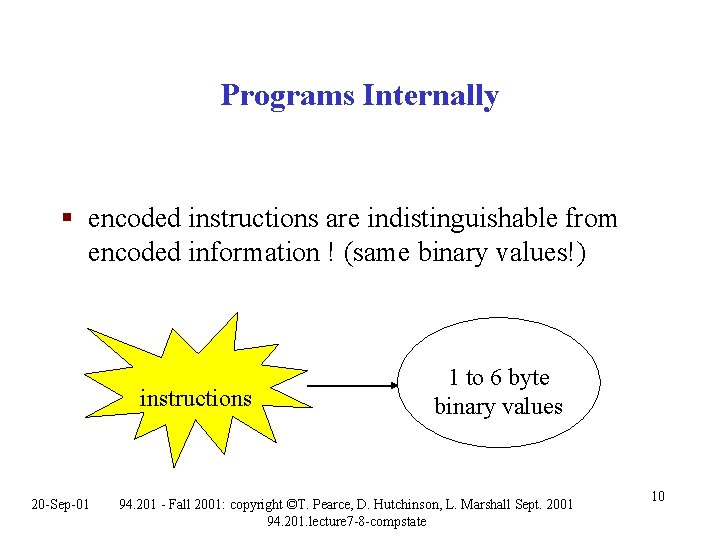

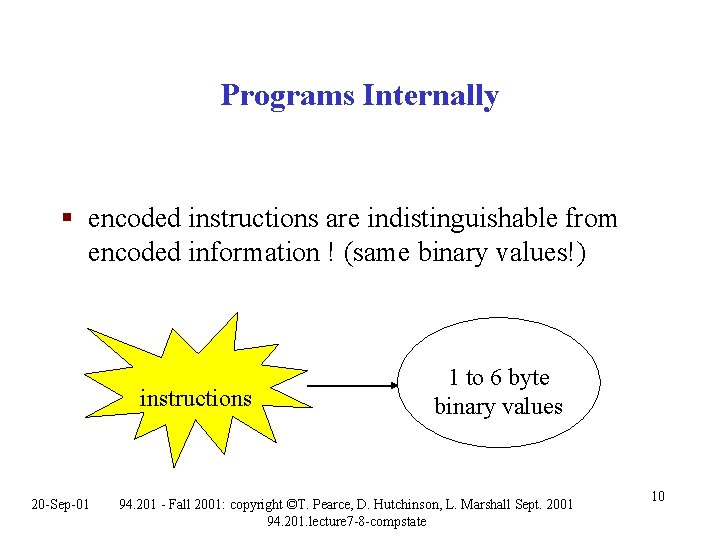

Stored Program Concept encoding details discussed later 1. instructions are encoded into binary values 2. encodings of instructions are loaded into memory 3. processor retrieves and executes instructions different! from memory (one at a time) § instructions encodings have variable length • • 20 -Sep-01 1 to 6 bytes not every binary value 1 to 6 bytes long corresponds to an instruction 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94. 201. lecture 7 -8 -compstate 9

Programs Internally § encoded instructions are indistinguishable from encoded information ! (same binary values!) instructions 20 -Sep-01 1 to 6 byte binary values 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94. 201. lecture 7 -8 -compstate 10

Processor Bus registers Memory cells instructions & data I/O ports Computer System 20 -Sep-01 Connected Devices keyboard mouse display printer disk drives commn links etc. 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94. 201. lecture 7 -8 -compstate 11

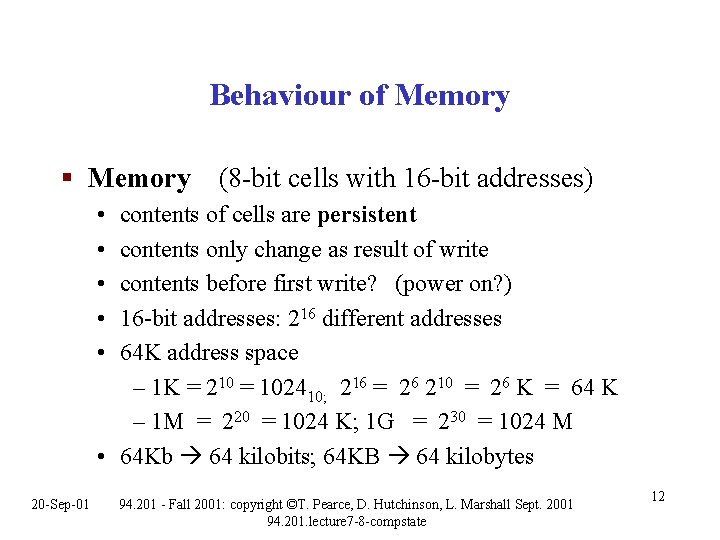

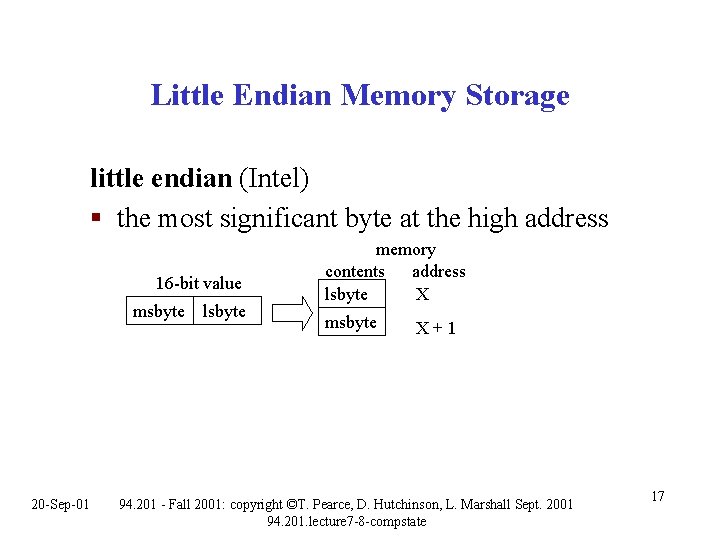

Behaviour of Memory § Memory (8 -bit cells with 16 -bit addresses) • • • contents of cells are persistent contents only change as result of write contents before first write? (power on? ) 16 -bit addresses: 216 different addresses 64 K address space – 1 K = 210 = 102410; 216 = 26 210 = 26 K = 64 K – 1 M = 220 = 1024 K; 1 G = 230 = 1024 M • 64 Kb 64 kilobits; 64 KB 64 kilobytes 20 -Sep-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94. 201. lecture 7 -8 -compstate 12

![Behaviour of Memory Notation for memoryrelated behaviour writevalue addr memaddr value Behaviour of Memory Notation for memory-related behaviour: § write(value, addr) mem[addr] : = value](https://slidetodoc.com/presentation_image_h/2b7227e6dbb83778307f78e99398f014/image-13.jpg)

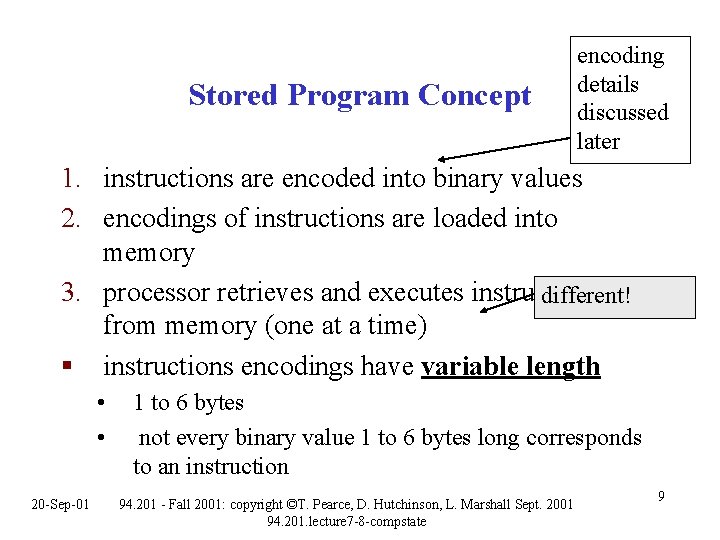

Behaviour of Memory Notation for memory-related behaviour: § write(value, addr) mem[addr] : = value § read( addr ) mem[addr] 20 -Sep-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94. 201. lecture 7 -8 -compstate 13

Some Types of Memory RAM: Read-And-Modify a. k. a. Random Access Memory § can read and write cell contents ROM: Read-Only-Memory § contents “burned in” when manufactured § can’t write new values PROM: Programmable Read-Only-Memory § contents can be programmed once using PROM Programmer (special device) EPROM: Erasable Programmable ROM § program using PROM programmer § can be “erased” by UV exposure EEPROM: Electrically Erasable PROM § reprogram in-circuit! (power-off persistence!) 20 -Sep-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94. 201. lecture 7 -8 -compstate 14

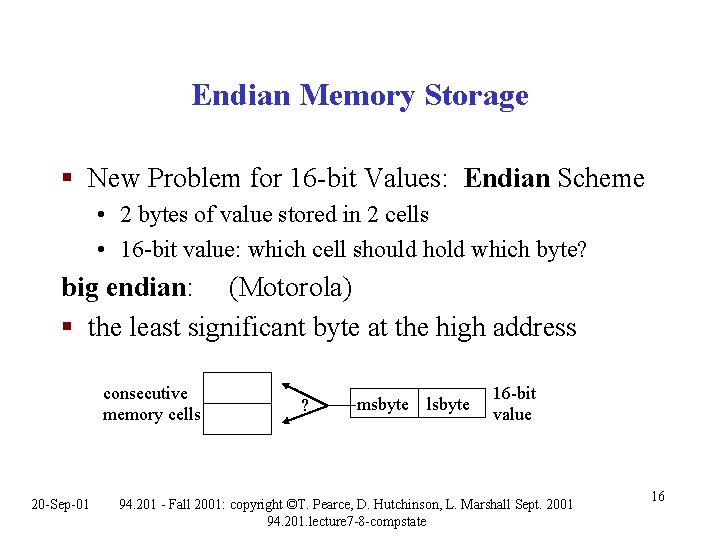

A Memory Problem § How can binary values wider than 8 -bits be stored in 8 -bit memory cells ? § Use more than one cell! • use consecutive memory cells • cannot “address” individual bits in a cell • e. g. 2 cells 16 -bit values 20 -Sep-01 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94. 201. lecture 7 -8 -compstate 15

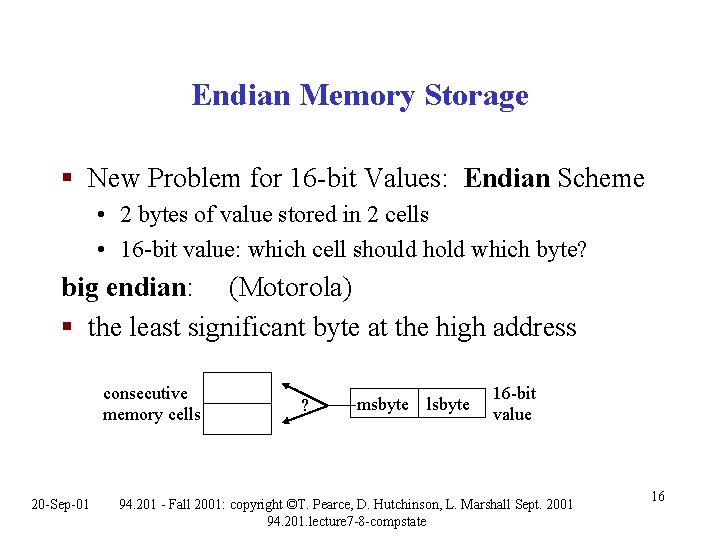

Endian Memory Storage § New Problem for 16 -bit Values: Endian Scheme • 2 bytes of value stored in 2 cells • 16 -bit value: which cell should hold which byte? big endian: (Motorola) § the least significant byte at the high address consecutive memory cells 20 -Sep-01 ? msbyte lsbyte 16 -bit value 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94. 201. lecture 7 -8 -compstate 16

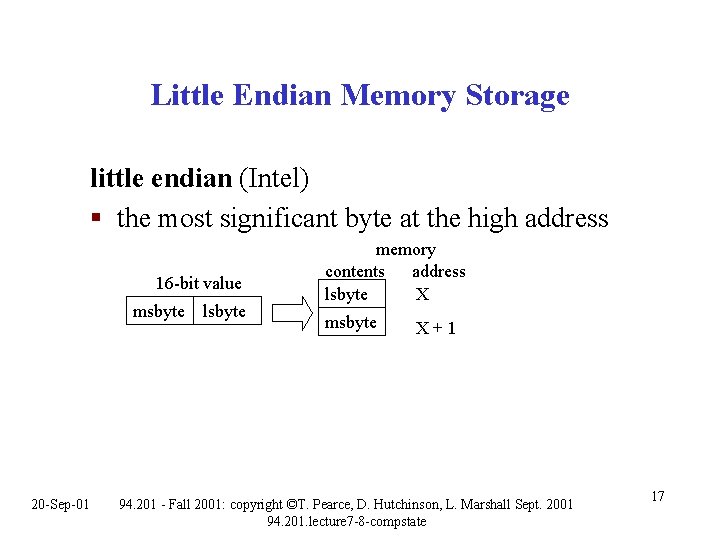

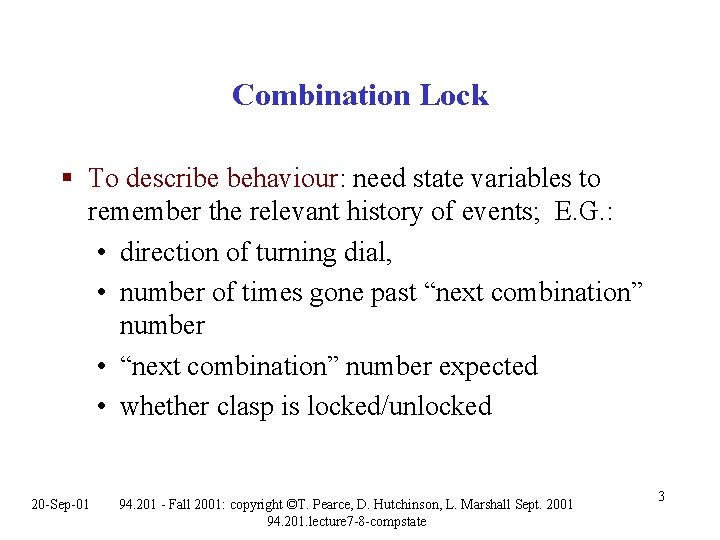

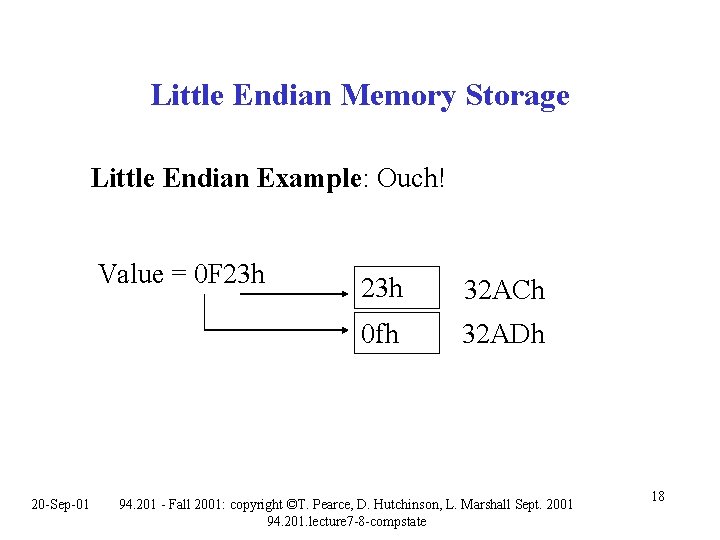

Little Endian Memory Storage little endian (Intel) § the most significant byte at the high address 16 -bit value msbyte lsbyte 20 -Sep-01 memory contents address lsbyte X msbyte X + 1 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94. 201. lecture 7 -8 -compstate 17

Little Endian Memory Storage Little Endian Example: Ouch! Value = 0 F 23 h 20 -Sep-01 23 h 32 ACh 0 fh 32 ADh 94. 201 - Fall 2001: copyright ©T. Pearce, D. Hutchinson, L. Marshall Sept. 2001 94. 201. lecture 7 -8 -compstate 18