Machine Instructions Language of the Machine Lowest level

![Load and store instructions • Example: C code: A[8] = h + A[8]; MIPS Load and store instructions • Example: C code: A[8] = h + A[8]; MIPS](https://slidetodoc.com/presentation_image/09634c42f7a250a11140409376dc5f18/image-9.jpg)

- Slides: 40

Machine Instructions: • Language of the Machine • Lowest level of programming, control directly the hardware • Assembly instructions are symbolic versions of machine instructions • More primitive than higher level languages • Very restrictive • Programs are stored in the memory, one instruction is fetched and executed at a time • We’ll be working with the MIPS instruction set architecture 1998 Morgan Kaufmann Publishers

MIPS instruction set: • Load from memory Store in memory • Logic operations – and, or, negation, shift, . . . • Arithmetic operations – addition, subtraction, . . . • Branch 1998 Morgan Kaufmann Publishers

Instruction types: • 1 operand Jump #address Jump $register number • 2 operands Multiply $reg 1, $reg 2 • 3 operands Add $reg 1, $reg 2, $reg 3 1998 Morgan Kaufmann Publishers

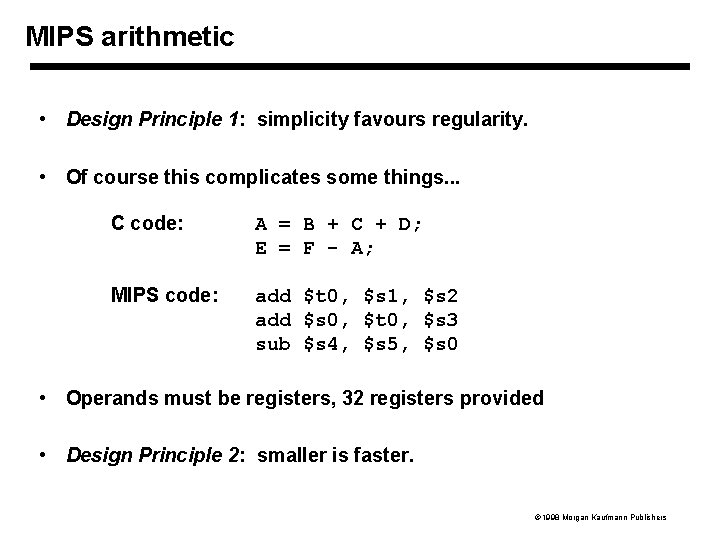

MIPS arithmetic • Instructions have 3 operands • Operand order is fixed (destination first) Example: C code: A=B+C MIPS code: add $s 0, $s 1, $s 2 $s 0, etc. are registers (associated with variables by compiler) 1998 Morgan Kaufmann Publishers

MIPS arithmetic • Design Principle 1: simplicity favours regularity. • Of course this complicates some things. . . C code: A = B + C + D; E = F - A; MIPS code: add $t 0, $s 1, $s 2 add $s 0, $t 0, $s 3 sub $s 4, $s 5, $s 0 • Operands must be registers, 32 registers provided • Design Principle 2: smaller is faster. 1998 Morgan Kaufmann Publishers

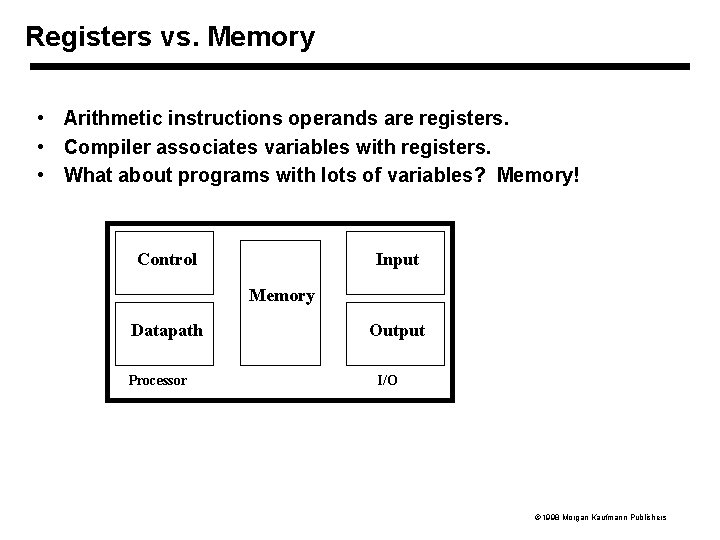

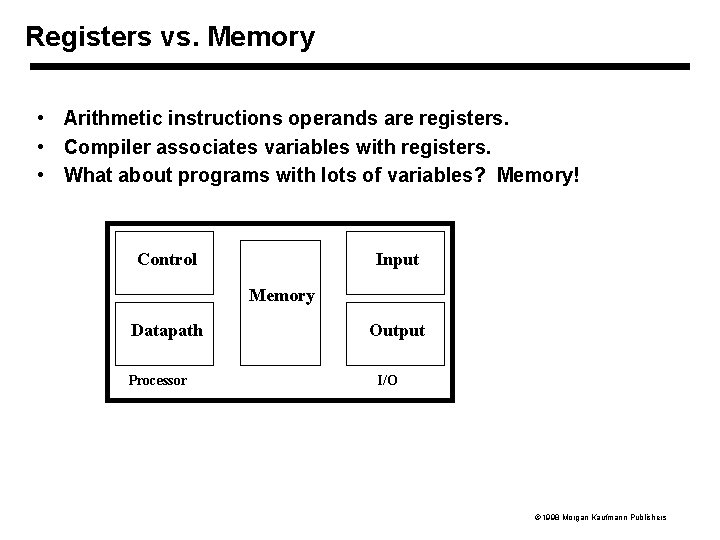

Registers vs. Memory • Arithmetic instructions operands are registers. • Compiler associates variables with registers. • What about programs with lots of variables? Memory! Control Input Memory Datapath Processor Output I/O 1998 Morgan Kaufmann Publishers

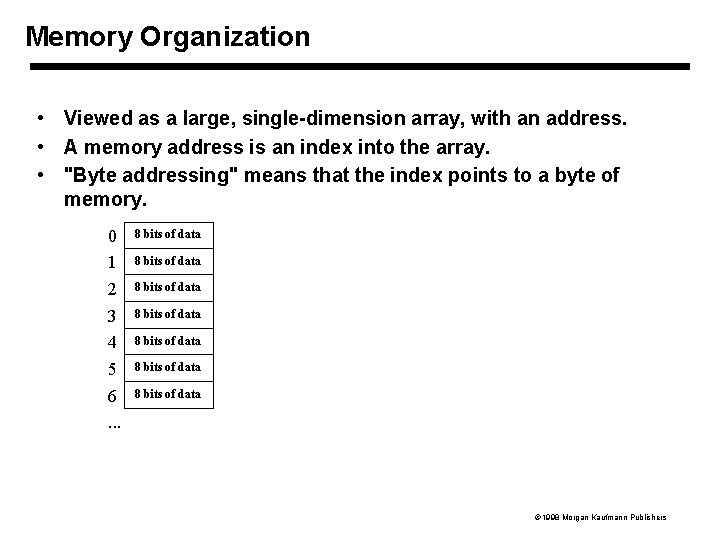

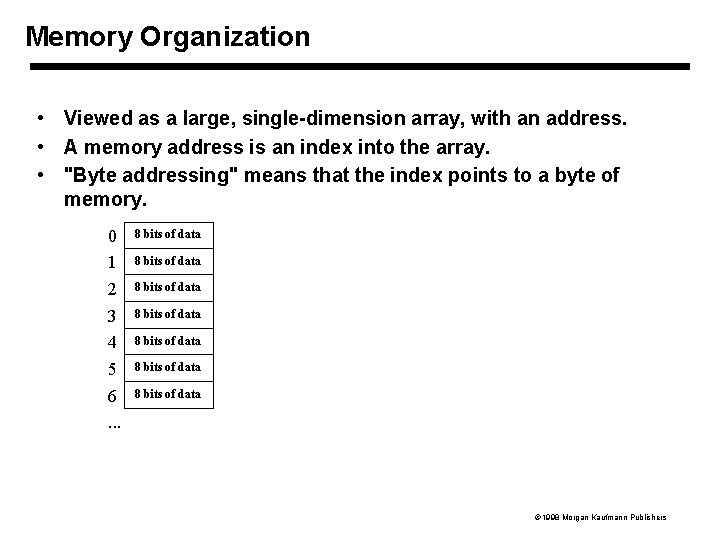

Memory Organization • Viewed as a large, single-dimension array, with an address. • A memory address is an index into the array. • "Byte addressing" means that the index points to a byte of memory. 0 1 2 3 4 5 6. . . 8 bits of data 8 bits of data 1998 Morgan Kaufmann Publishers

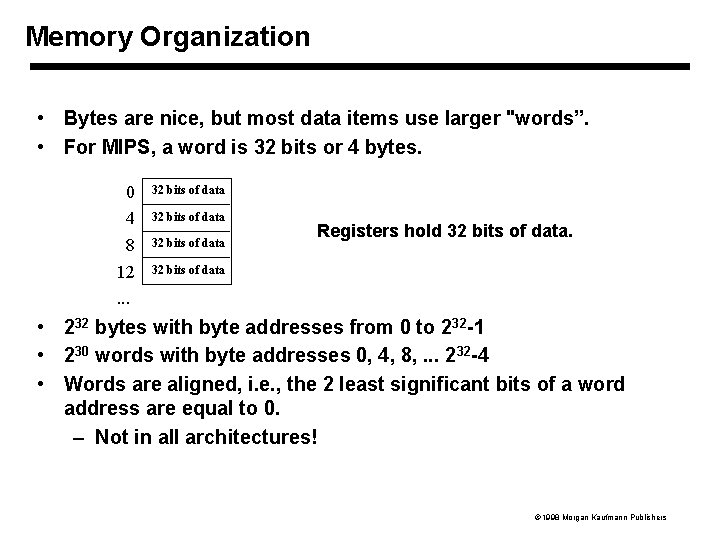

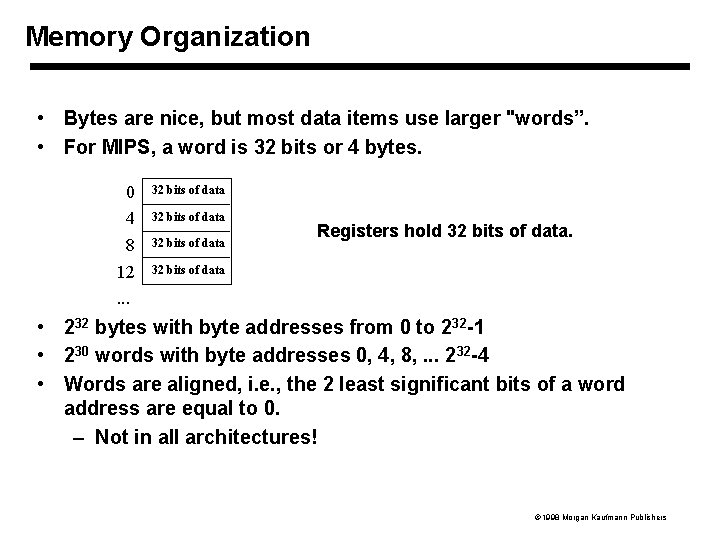

Memory Organization • Bytes are nice, but most data items use larger "words”. • For MIPS, a word is 32 bits or 4 bytes. 0 4 8 12. . . 32 bits of data Registers hold 32 bits of data • 232 bytes with byte addresses from 0 to 232 -1 • 230 words with byte addresses 0, 4, 8, . . . 232 -4 • Words are aligned, i. e. , the 2 least significant bits of a word address are equal to 0. – Not in all architectures! 1998 Morgan Kaufmann Publishers

![Load and store instructions Example C code A8 h A8 MIPS Load and store instructions • Example: C code: A[8] = h + A[8]; MIPS](https://slidetodoc.com/presentation_image/09634c42f7a250a11140409376dc5f18/image-9.jpg)

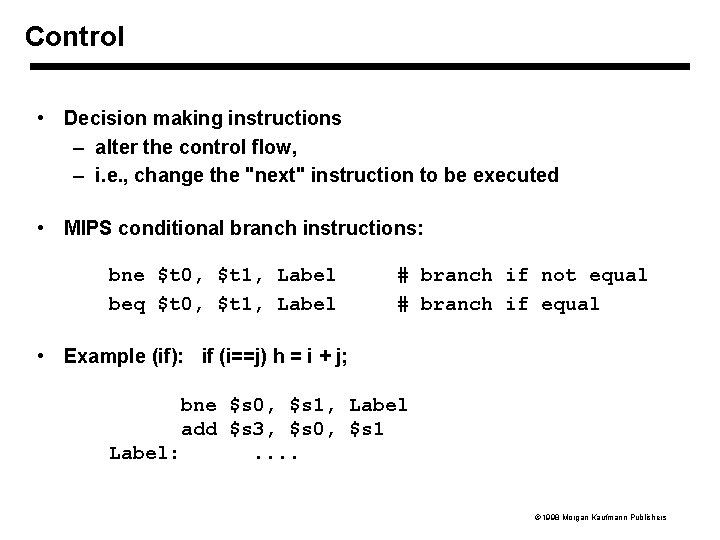

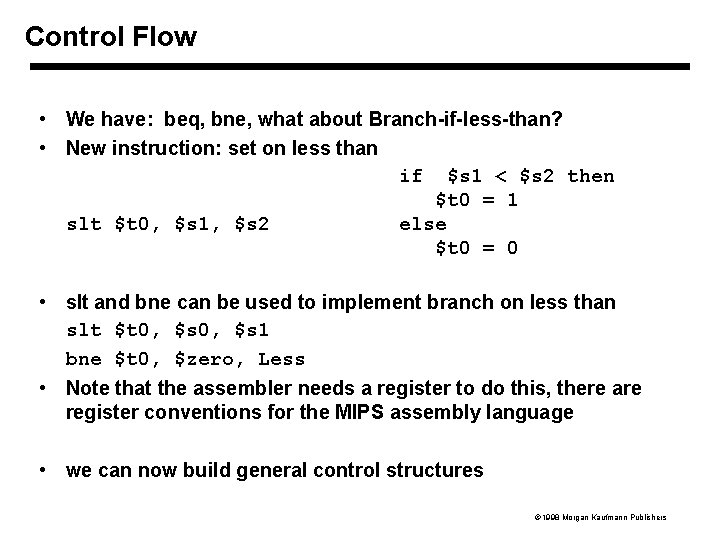

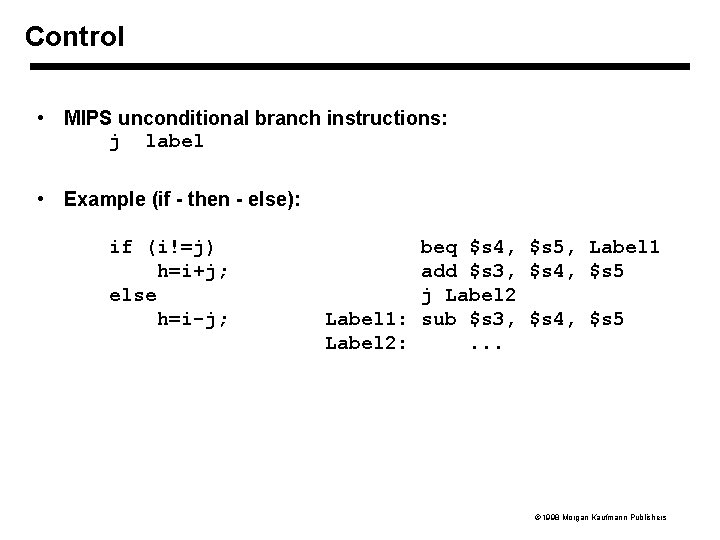

Load and store instructions • Example: C code: A[8] = h + A[8]; MIPS code: lw $t 0, 32($s 3) add $t 0, $s 2, $t 0 sw $t 0, 32($s 3) • $s 3 contains the base of the array. $s 2 contains h. • Word offset 8 equals byte offset 32. • Store word has destination last. • Remember arithmetic operands are registers, not memory! 1998 Morgan Kaufmann Publishers

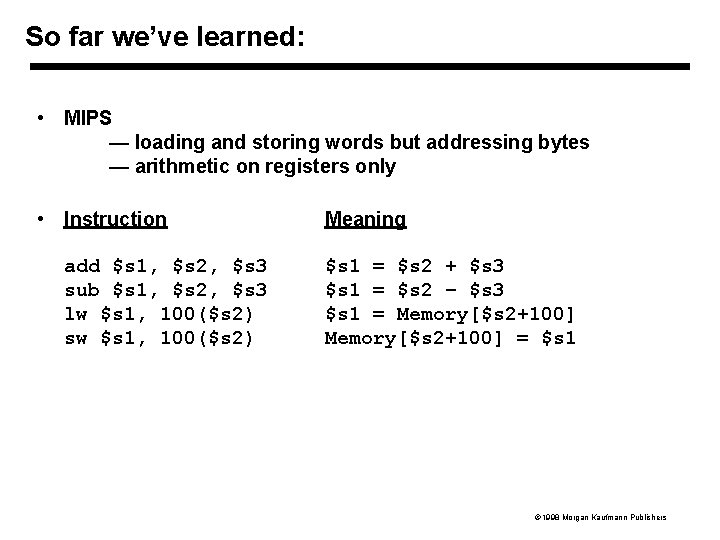

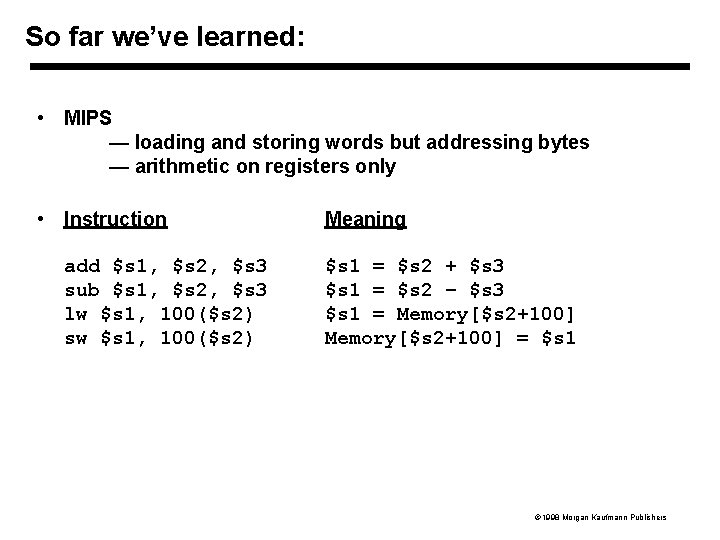

So far we’ve learned: • MIPS — loading and storing words but addressing bytes — arithmetic on registers only • Instruction add $s 1, $s 2, $s 3 sub $s 1, $s 2, $s 3 lw $s 1, 100($s 2) sw $s 1, 100($s 2) Meaning $s 1 = $s 2 + $s 3 $s 1 = $s 2 – $s 3 $s 1 = Memory[$s 2+100] = $s 1 1998 Morgan Kaufmann Publishers

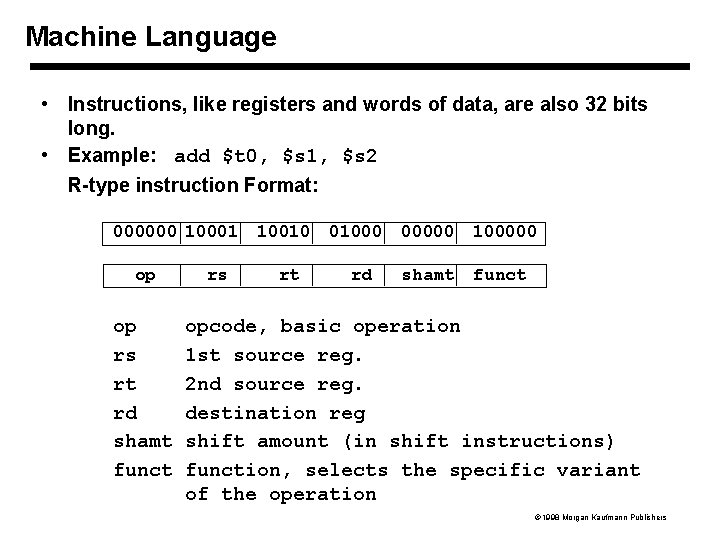

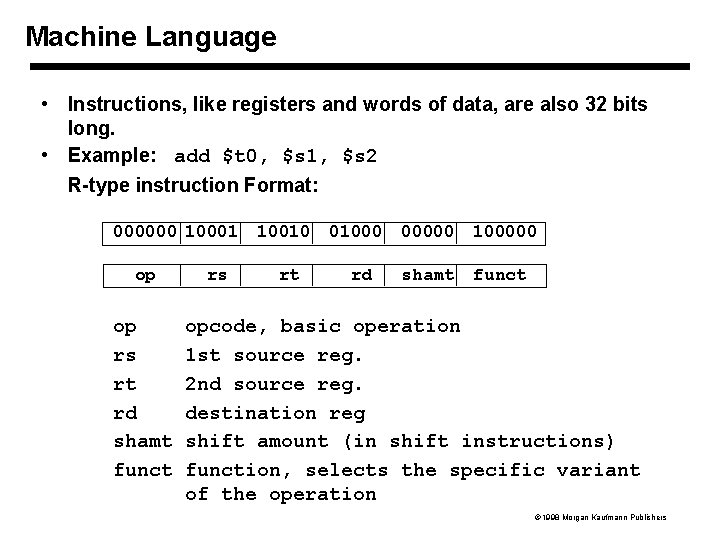

Machine Language • Instructions, like registers and words of data, are also 32 bits long. • Example: add $t 0, $s 1, $s 2 R-type instruction Format: 000000 10001 10010 01000 00000 100000 op op rs rt rd shamt funct opcode, basic operation 1 st source reg. 2 nd source reg. destination reg shift amount (in shift instructions) function, selects the specific variant of the operation 1998 Morgan Kaufmann Publishers

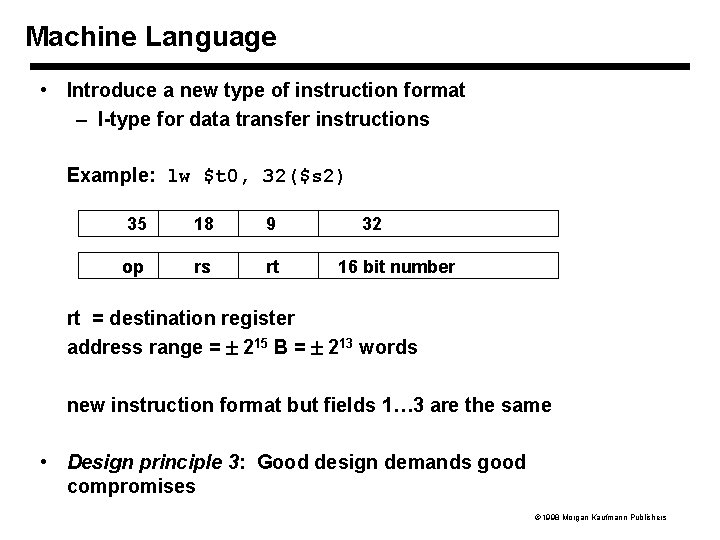

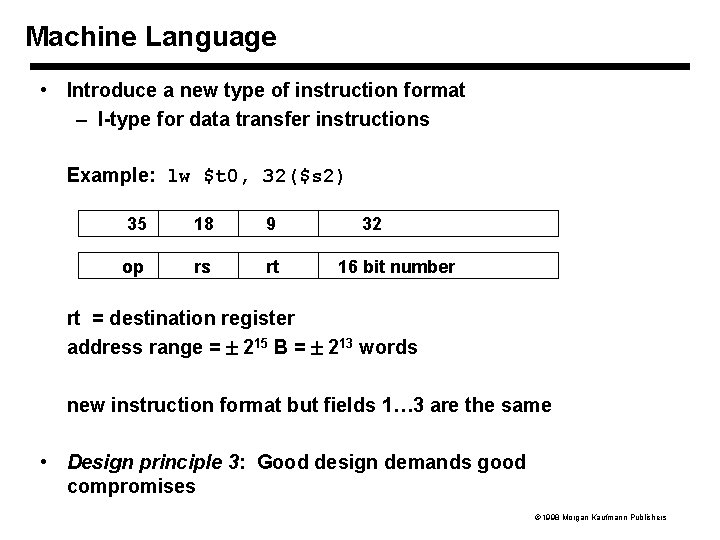

Machine Language • Introduce a new type of instruction format – I-type for data transfer instructions Example: lw $t 0, 32($s 2) 35 18 9 op rs rt 32 16 bit number rt = destination register address range = 215 B = 213 words new instruction format but fields 1… 3 are the same • Design principle 3: Good design demands good compromises 1998 Morgan Kaufmann Publishers

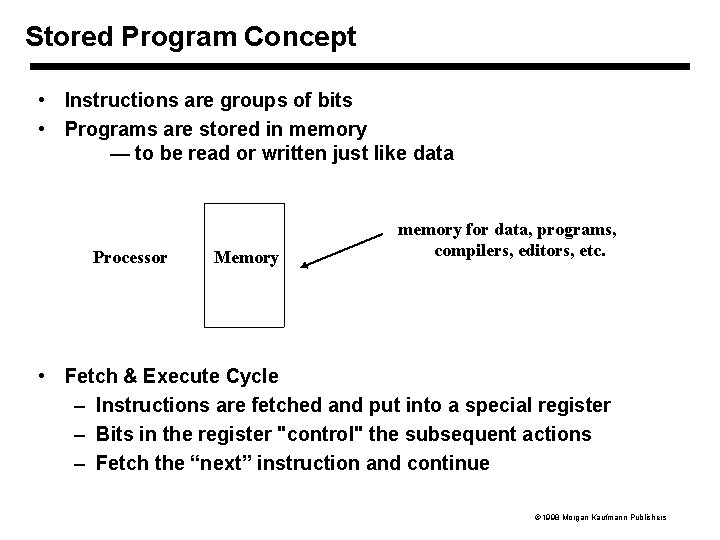

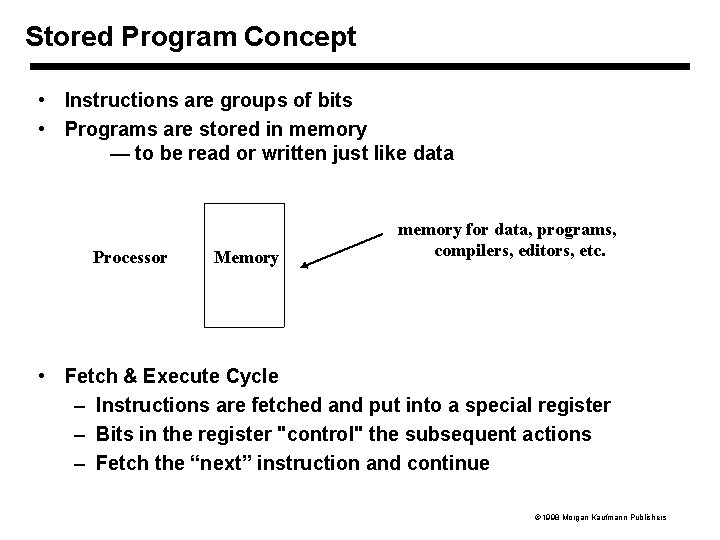

Stored Program Concept • Instructions are groups of bits • Programs are stored in memory — to be read or written just like data Processor Memory memory for data, programs, compilers, editors, etc. • Fetch & Execute Cycle – Instructions are fetched and put into a special register – Bits in the register "control" the subsequent actions – Fetch the “next” instruction and continue 1998 Morgan Kaufmann Publishers

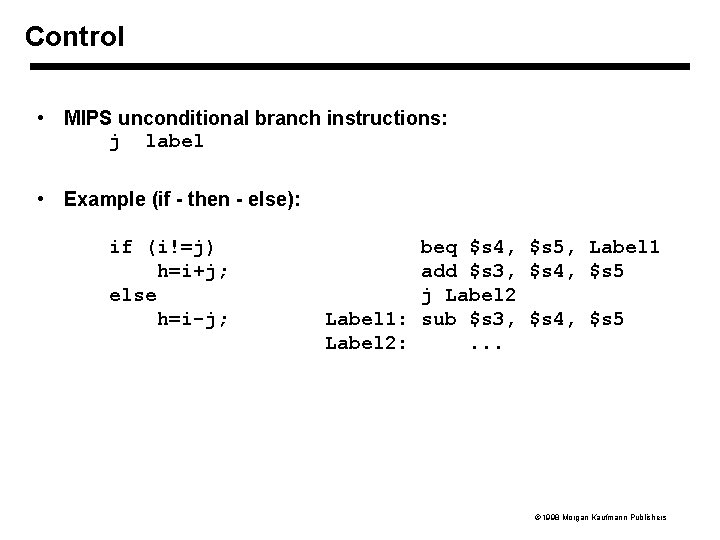

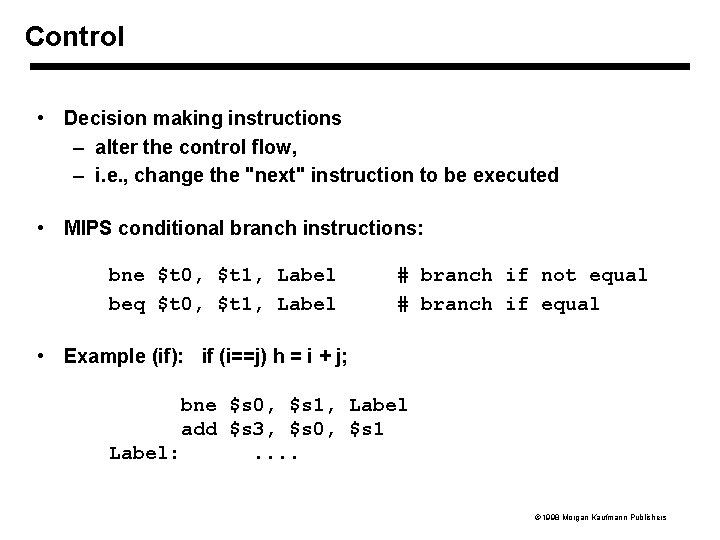

Control • Decision making instructions – alter the control flow, – i. e. , change the "next" instruction to be executed • MIPS conditional branch instructions: bne $t 0, $t 1, Label beq $t 0, $t 1, Label # branch if not equal # branch if equal • Example (if): if (i==j) h = i + j; bne $s 0, $s 1, Label add $s 3, $s 0, $s 1 Label: . . 1998 Morgan Kaufmann Publishers

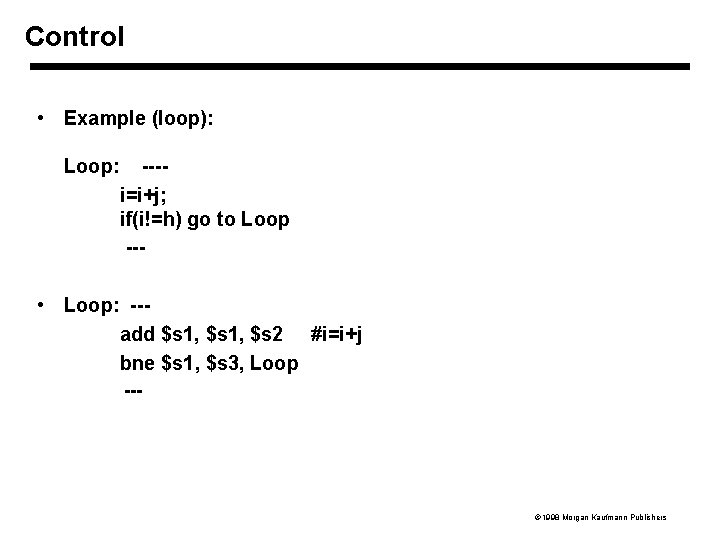

Control • MIPS unconditional branch instructions: j label • Example (if - then - else): if (i!=j) h=i+j; else h=i-j; beq $s 4, $s 5, Label 1 add $s 3, $s 4, $s 5 j Label 2 Label 1: sub $s 3, $s 4, $s 5 Label 2: . . . 1998 Morgan Kaufmann Publishers

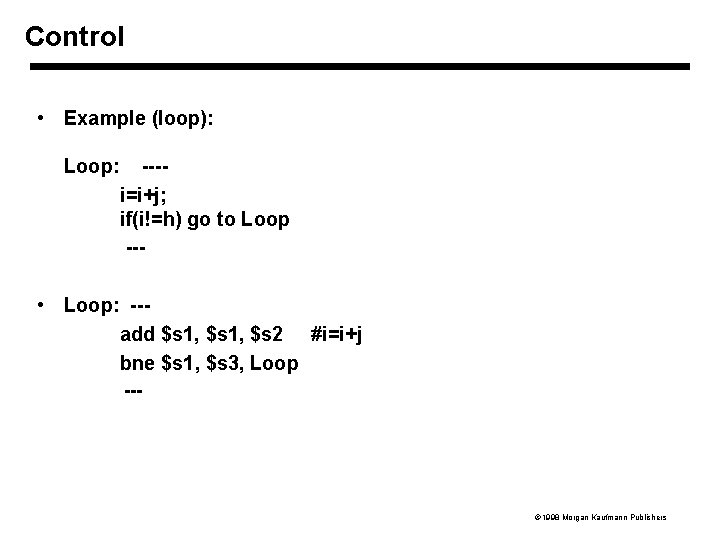

Control • Example (loop): Loop: ---i=i+j; if(i!=h) go to Loop --- • Loop: --add $s 1, $s 2 #i=i+j bne $s 1, $s 3, Loop --- 1998 Morgan Kaufmann Publishers

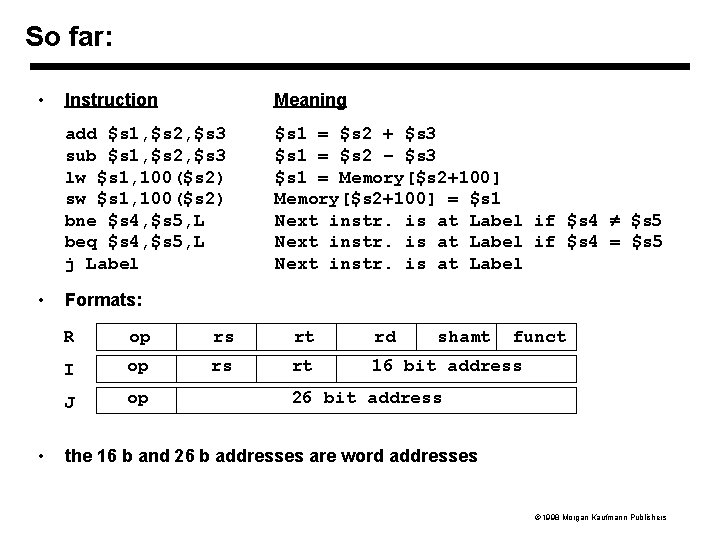

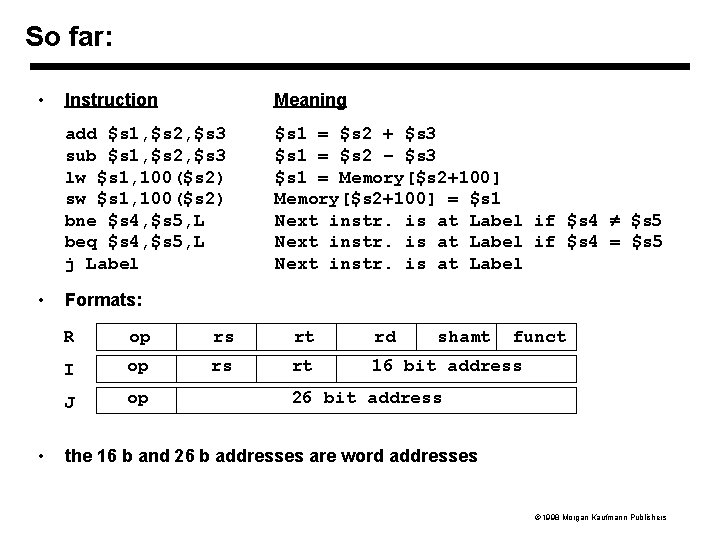

So far: • • • Instruction Meaning add $s 1, $s 2, $s 3 sub $s 1, $s 2, $s 3 lw $s 1, 100($s 2) sw $s 1, 100($s 2) bne $s 4, $s 5, L beq $s 4, $s 5, L j Label $s 1 = $s 2 + $s 3 $s 1 = $s 2 – $s 3 $s 1 = Memory[$s 2+100] = $s 1 Next instr. is at Label if $s 4 $s 5 Next instr. is at Label if $s 4 = $s 5 Next instr. is at Label Formats: R op rs rt rd I op rs rt 16 bit address J op shamt funct 26 bit address the 16 b and 26 b addresses are word addresses 1998 Morgan Kaufmann Publishers

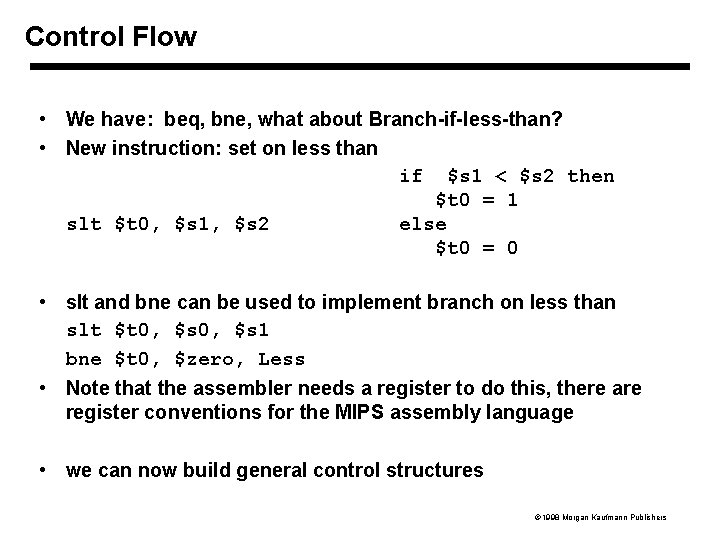

Control Flow • We have: beq, bne, what about Branch-if-less-than? • New instruction: set on less than if $s 1 < $s 2 then $t 0 = 1 slt $t 0, $s 1, $s 2 else $t 0 = 0 • slt and bne can be used to implement branch on less than slt $t 0, $s 1 bne $t 0, $zero, Less • Note that the assembler needs a register to do this, there are register conventions for the MIPS assembly language • we can now build general control structures 1998 Morgan Kaufmann Publishers

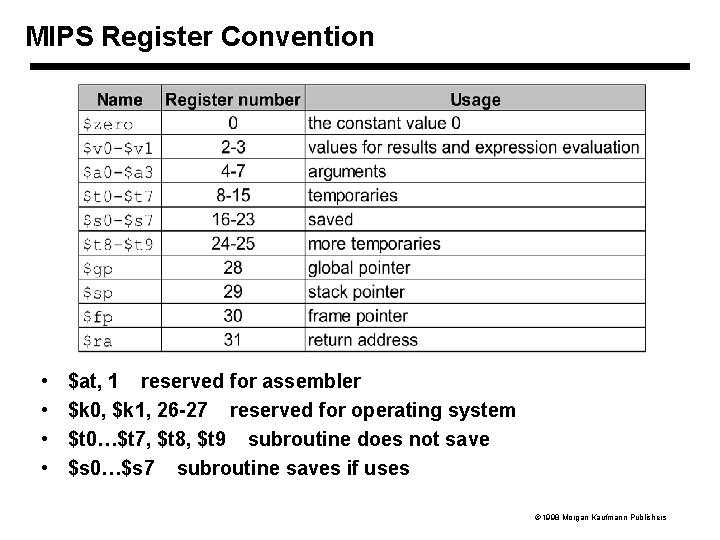

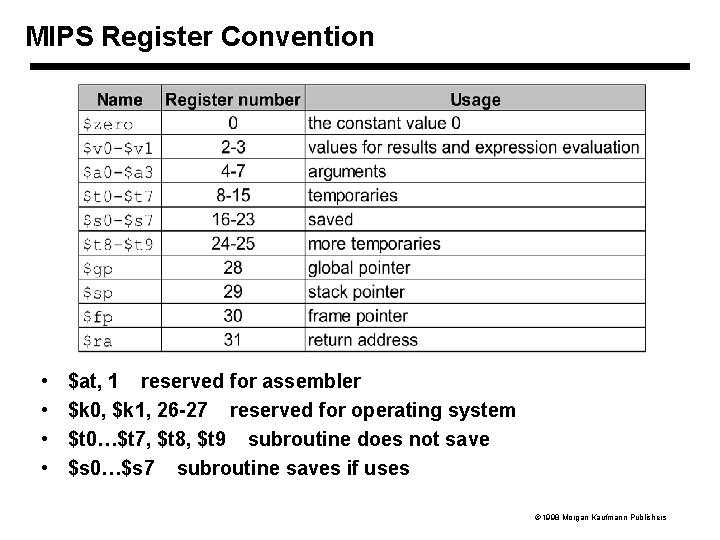

MIPS Register Convention • • $at, 1 reserved for assembler $k 0, $k 1, 26 -27 reserved for operating system $t 0…$t 7, $t 8, $t 9 subroutine does not save $s 0…$s 7 subroutine saves if uses 1998 Morgan Kaufmann Publishers

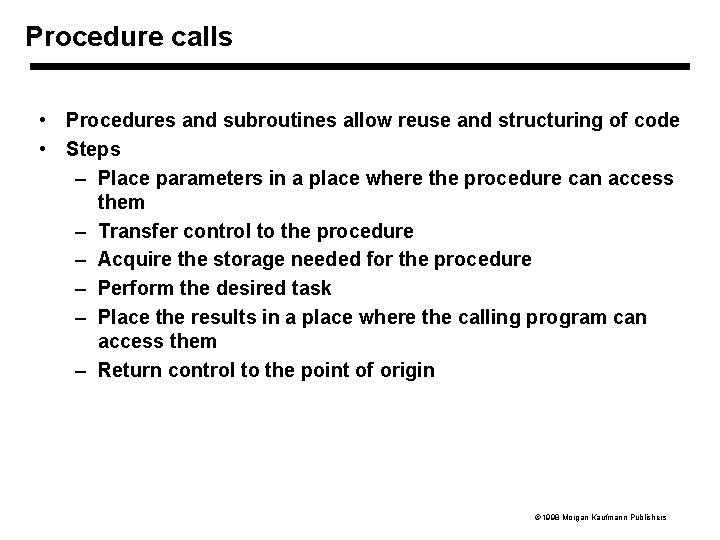

Procedure calls • Procedures and subroutines allow reuse and structuring of code • Steps – Place parameters in a place where the procedure can access them – Transfer control to the procedure – Acquire the storage needed for the procedure – Perform the desired task – Place the results in a place where the calling program can access them – Return control to the point of origin 1998 Morgan Kaufmann Publishers

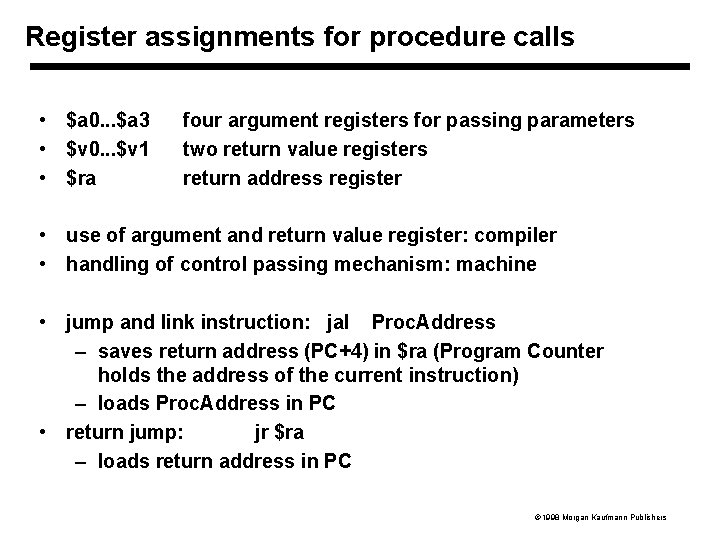

Register assignments for procedure calls • $a 0. . . $a 3 • $v 0. . . $v 1 • $ra four argument registers for passing parameters two return value registers return address register • use of argument and return value register: compiler • handling of control passing mechanism: machine • jump and link instruction: jal Proc. Address – saves return address (PC+4) in $ra (Program Counter holds the address of the current instruction) – loads Proc. Address in PC • return jump: jr $ra – loads return address in PC 1998 Morgan Kaufmann Publishers

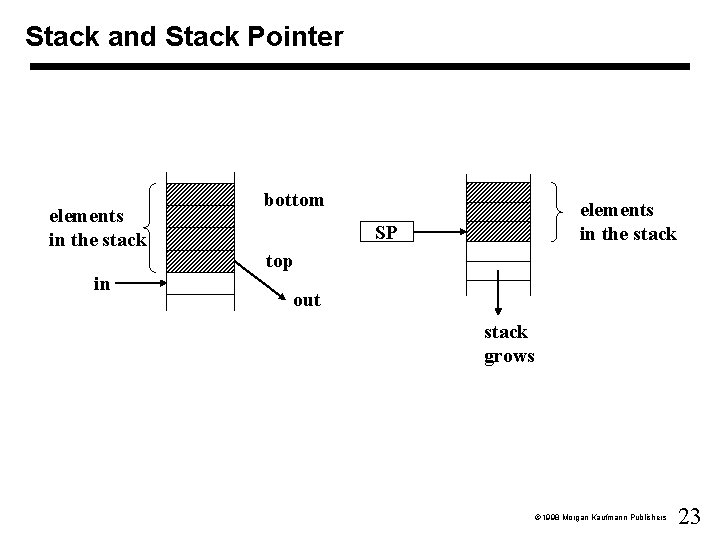

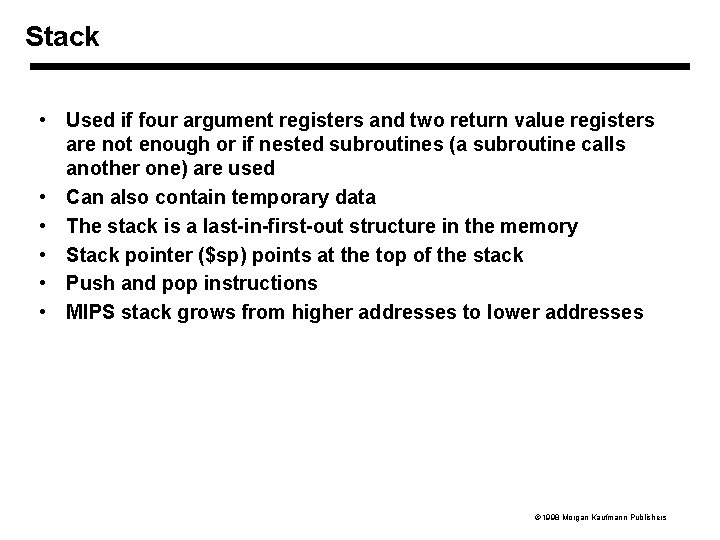

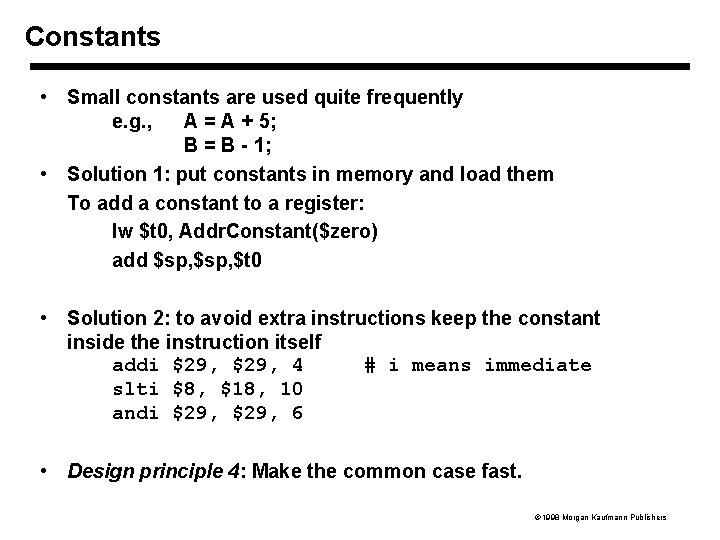

Stack • Used if four argument registers and two return value registers are not enough or if nested subroutines (a subroutine calls another one) are used • Can also contain temporary data • The stack is a last-in-first-out structure in the memory • Stack pointer ($sp) points at the top of the stack • Push and pop instructions • MIPS stack grows from higher addresses to lower addresses 1998 Morgan Kaufmann Publishers

Stack and Stack Pointer elements in the stack in bottom elements in the stack SP top out stack grows 1998 Morgan Kaufmann Publishers 23

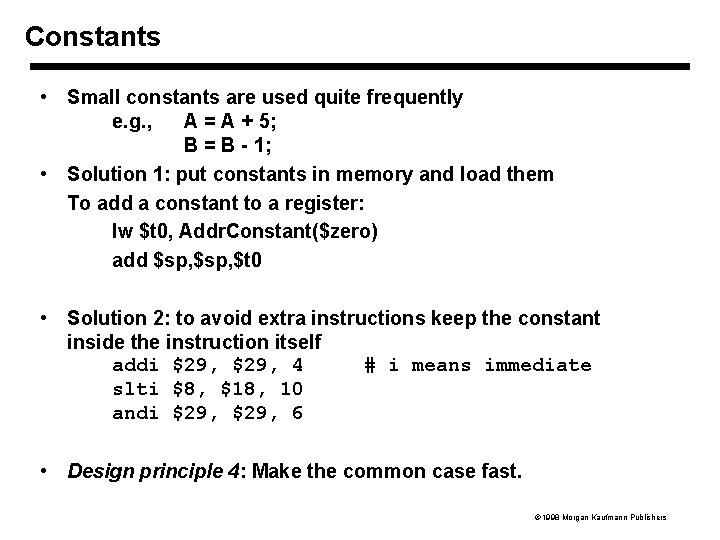

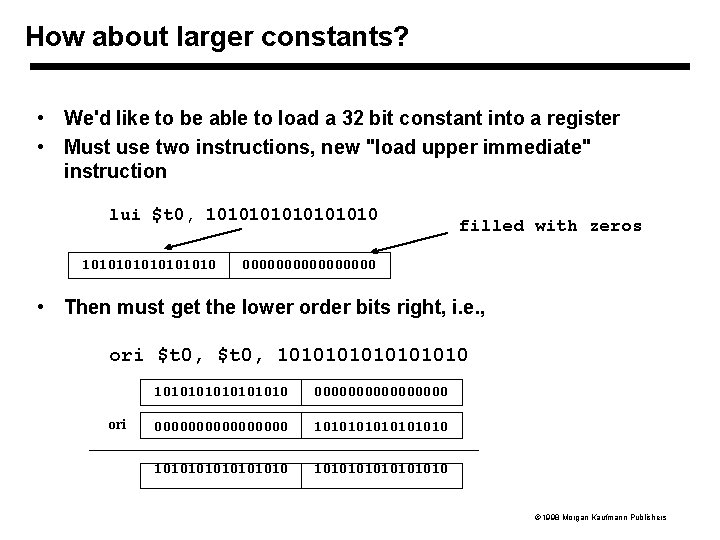

Constants • Small constants are used quite frequently e. g. , A = A + 5; B = B - 1; • Solution 1: put constants in memory and load them To add a constant to a register: lw $t 0, Addr. Constant($zero) add $sp, $t 0 • Solution 2: to avoid extra instructions keep the constant inside the instruction itself addi $29, 4 # i means immediate slti $8, $18, 10 andi $29, 6 • Design principle 4: Make the common case fast. 1998 Morgan Kaufmann Publishers

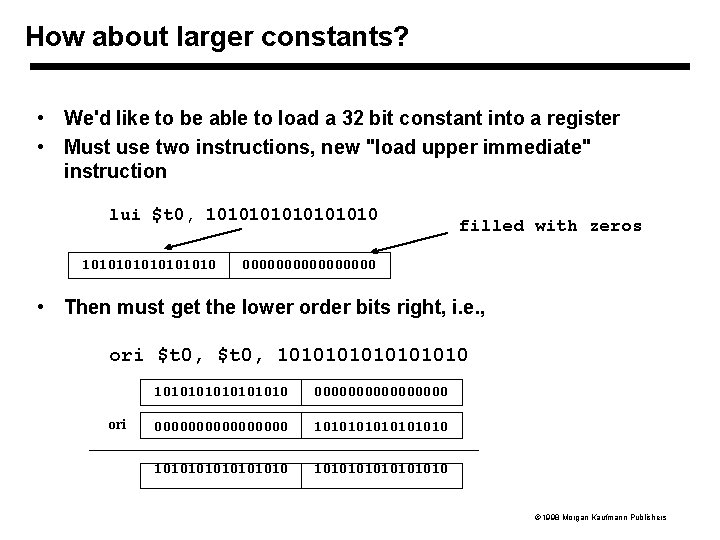

How about larger constants? • We'd like to be able to load a 32 bit constant into a register • Must use two instructions, new "load upper immediate" instruction lui $t 0, 1010101010101010 filled with zeros 00000000 • Then must get the lower order bits right, i. e. , ori $t 0, 10101010 ori 10101010 0000000000000000 1010101010101010 1998 Morgan Kaufmann Publishers

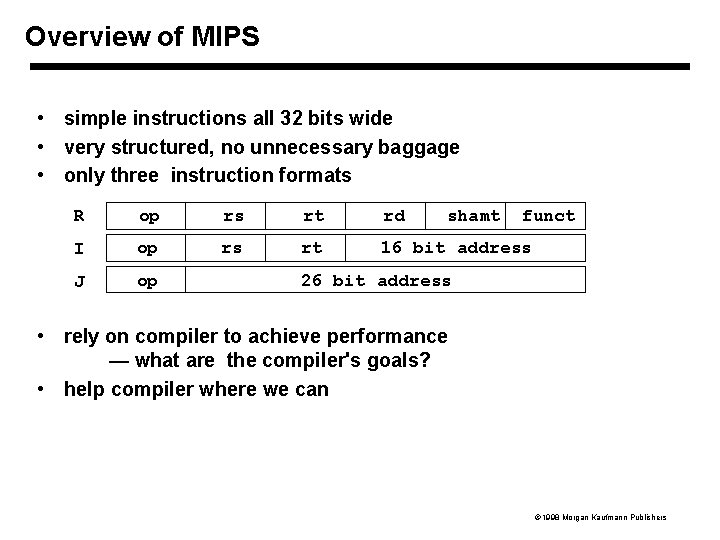

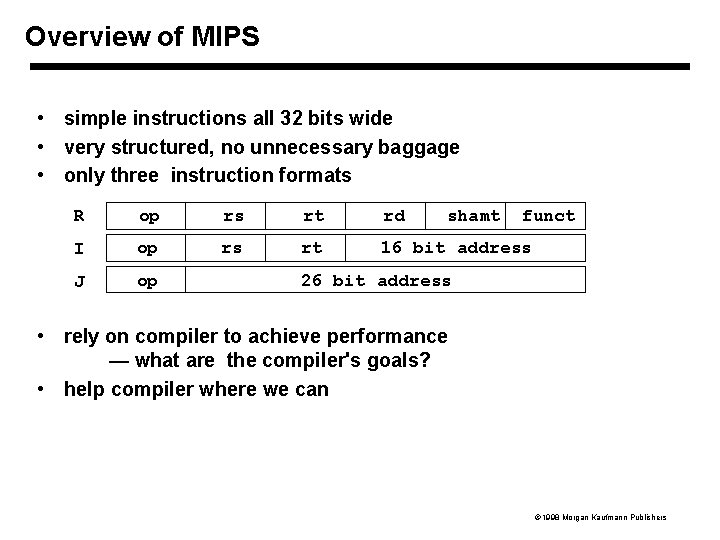

Overview of MIPS • simple instructions all 32 bits wide • very structured, no unnecessary baggage • only three instruction formats R op rs rt rd I op rs rt 16 bit address J op shamt funct 26 bit address • rely on compiler to achieve performance — what are the compiler's goals? • help compiler where we can 1998 Morgan Kaufmann Publishers

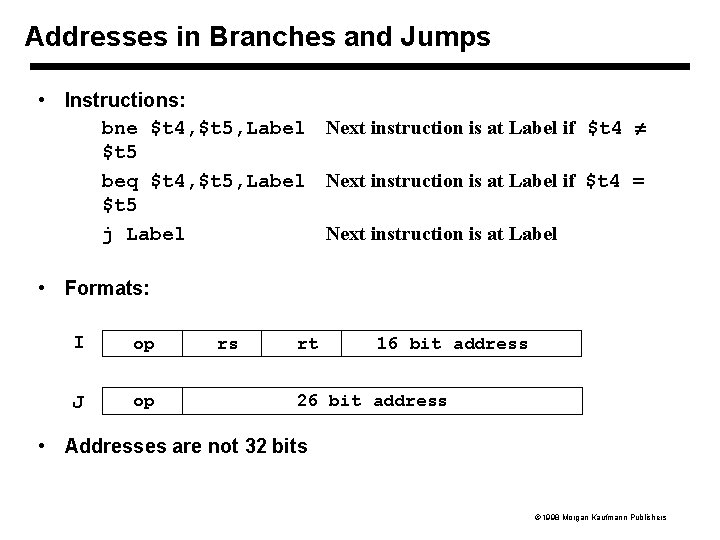

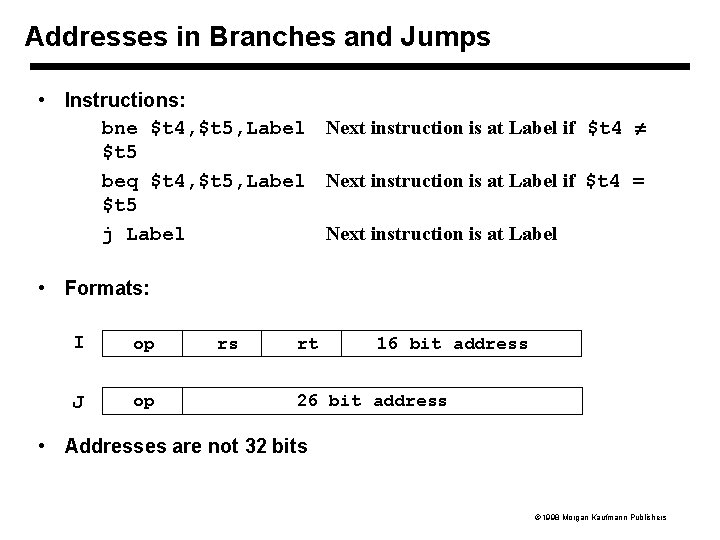

Addresses in Branches and Jumps • Instructions: bne $t 4, $t 5, Label Next instruction is at Label if $t 4 $t 5 beq $t 4, $t 5, Label Next instruction is at Label if $t 4 = $t 5 j Label Next instruction is at Label • Formats: I op J op rs rt 16 bit address 26 bit address • Addresses are not 32 bits 1998 Morgan Kaufmann Publishers

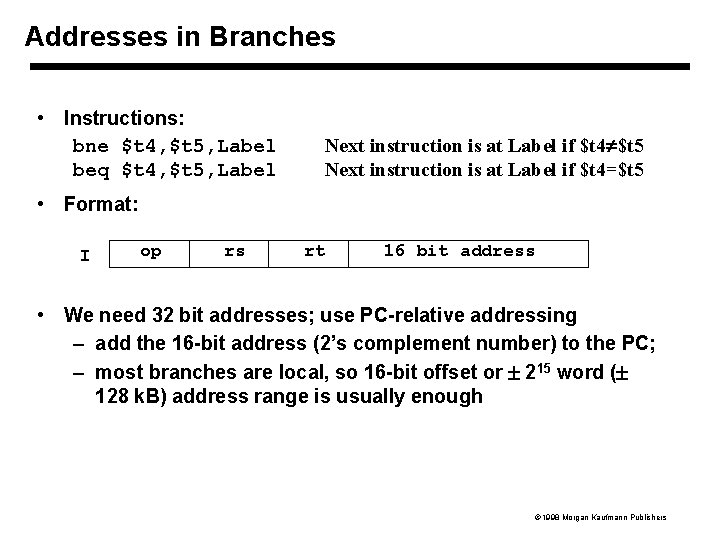

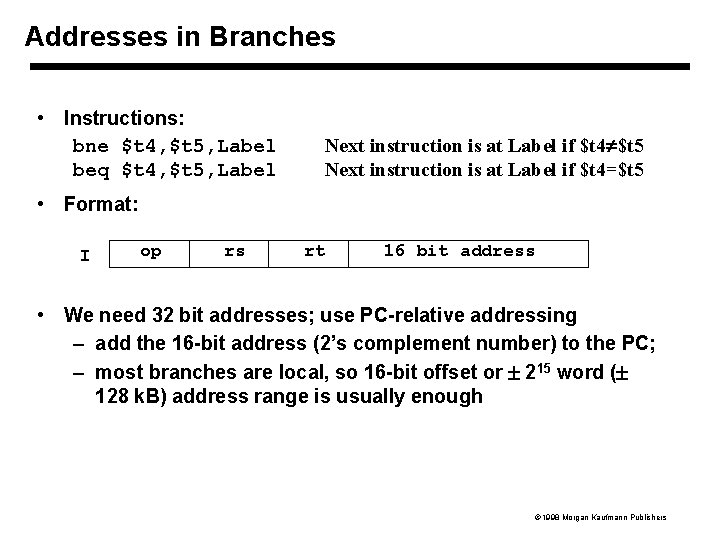

Addresses in Branches • Instructions: bne $t 4, $t 5, Label beq $t 4, $t 5, Label Next instruction is at Label if $t 4 $t 5 Next instruction is at Label if $t 4=$t 5 • Format: I op rs rt 16 bit address • We need 32 bit addresses; use PC-relative addressing – add the 16 -bit address (2’s complement number) to the PC; – most branches are local, so 16 -bit offset or 215 word ( 128 k. B) address range is usually enough 1998 Morgan Kaufmann Publishers

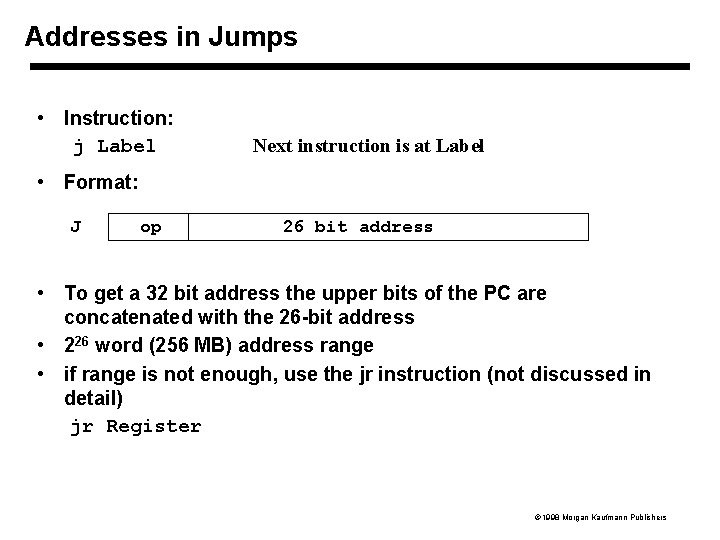

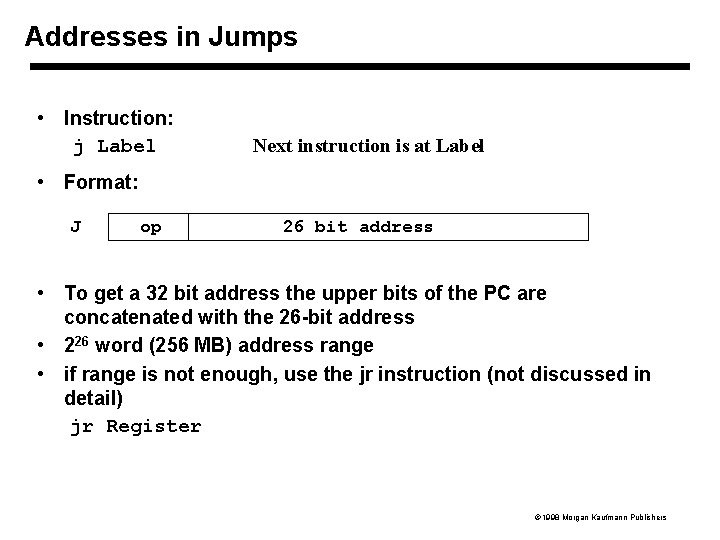

Addresses in Jumps • Instruction: j Label Next instruction is at Label • Format: J op 26 bit address • To get a 32 bit address the upper bits of the PC are concatenated with the 26 -bit address • 226 word (256 MB) address range • if range is not enough, use the jr instruction (not discussed in detail) jr Register 1998 Morgan Kaufmann Publishers

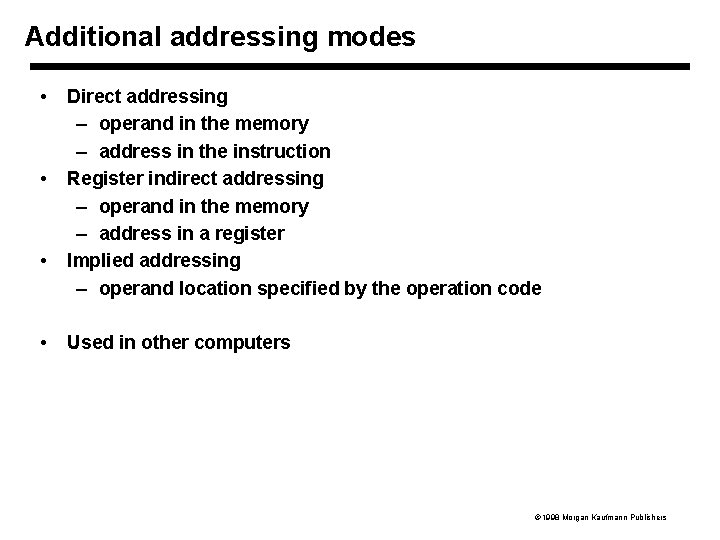

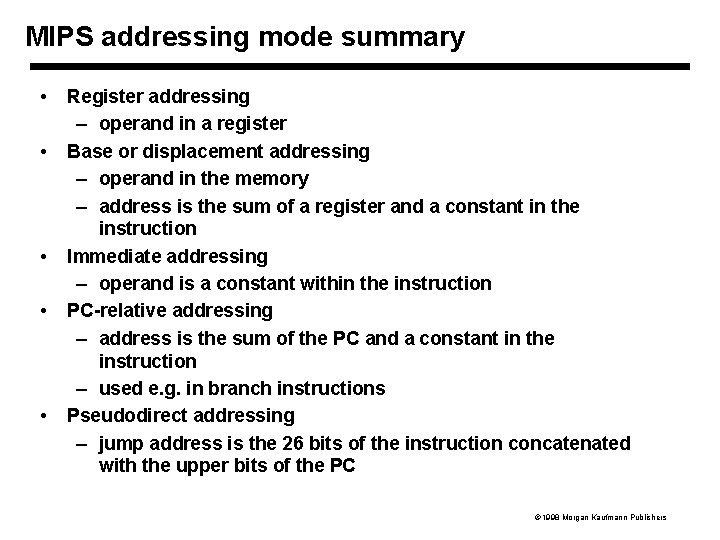

MIPS addressing mode summary • • • Register addressing – operand in a register Base or displacement addressing – operand in the memory – address is the sum of a register and a constant in the instruction Immediate addressing – operand is a constant within the instruction PC-relative addressing – address is the sum of the PC and a constant in the instruction – used e. g. in branch instructions Pseudodirect addressing – jump address is the 26 bits of the instruction concatenated with the upper bits of the PC 1998 Morgan Kaufmann Publishers

MIPS addressing mode summary 1998 Morgan Kaufmann Publishers 31

Additional addressing modes • • Direct addressing – operand in the memory – address in the instruction Register indirect addressing – operand in the memory – address in a register Implied addressing – operand location specified by the operation code Used in other computers 1998 Morgan Kaufmann Publishers

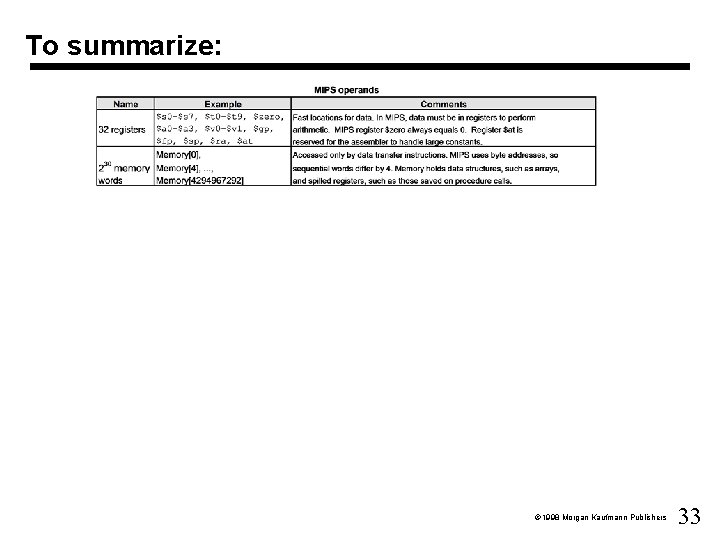

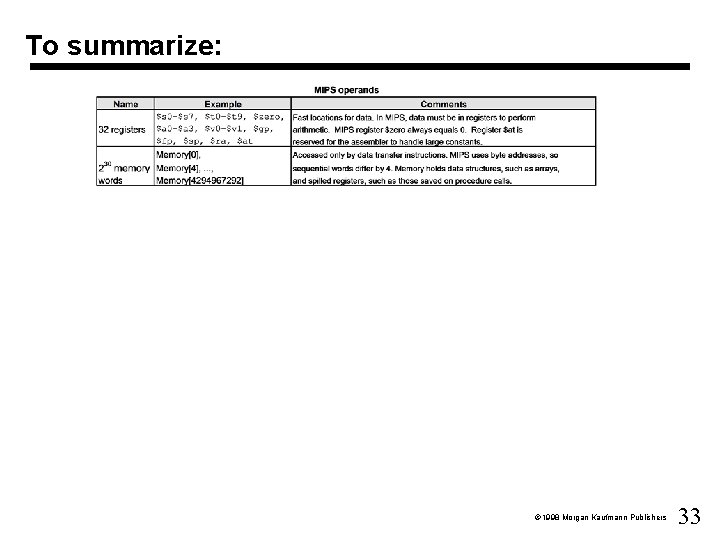

To summarize: 1998 Morgan Kaufmann Publishers 33

Assembly Language vs. Machine Language • Assembly provides convenient symbolic representation – much easier than writing down numbers – e. g. , destination first • Machine language is the underlying reality – e. g. , destination is no longer first • Assembly can provide 'pseudoinstructions' – e. g. , “move $t 0, $t 1” exists only in Assembly – would be implemented using “add $t 0, $t 1, $zero” • When considering performance you should count real instructions 1998 Morgan Kaufmann Publishers

Alternative Architectures • Design alternative: – provide more powerful operations than found in MIPS – goal is to reduce number of instructions executed – danger is a slower cycle time and/or a higher CPI • Sometimes referred to as “RISC vs. CISC” – Reduced Instruction Set Computers – Complex Instruction Set Computers – virtually all new instruction sets since 1982 have been RISC 1998 Morgan Kaufmann Publishers

Reduced Instruction Set Computers • Common characteristics of all RISCs – Single cycle issue – Small number of fixed length instruction formats – Load/store architecture – Large number of registers • Additional characteristics of most RISCs – Small number of instructions – Small number of addressing modes – Fast control unit 1998 Morgan Kaufmann Publishers

An alternative architecture: 80 x 86 • 1978: The Intel 8086 is announced (16 bit architecture) • 1980: The 8087 floating point coprocessor is added • 1982: The 80286 increases address space to 24 bits, +instructions • 1985: The 80386 extends to 32 bits, new addressing modes • 1989 -1995: The 80486, Pentium Pro add a few instructions (mostly designed for higher performance) • 1997: MMX is added 1998 Morgan Kaufmann Publishers

An alternative architecture: 80 x 86 • Intel had a 16 -bit microprocessor two years before its competitors’ more elegant architectures which led to the selection of the 8086 as the CPU for the IBM PC • “This history illustrates the impact of the “golden handcuffs” of compatibility” “an architecture that is difficult to explain and impossible to love” 1998 Morgan Kaufmann Publishers

A dominant architecture: 80 x 86 • See your textbook for a more detailed description • Complexity: – Instructions from 1 to 17 bytes long – one operand must act as both a source and destination – one operand can come from memory – complex addressing modes e. g. , “base or scaled index with 8 or 32 bit displacement” • Saving grace: – the most frequently used architectural components are not too difficult to implement – compilers avoid the portions of the architecture that are slow 1998 Morgan Kaufmann Publishers

Summary • Instruction complexity is only one variable – lower instruction count vs. higher CPI / lower clock rate • Design Principles: – simplicity favours regularity – smaller is faster – good design demands good compromises – make the common case fast • Instruction set architecture – a very important abstraction indeed! 1998 Morgan Kaufmann Publishers